Gui

# IBM 3090 Processor Complex Functional Characteristics

Publication Number SA22-7121-6

File Number S370-01 Federal Communications Commission (FCC) Statement

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### Seventh Edition (April 1988)

This major revision obsoletes SA22-7121-5 and Technical Newsletters SN22-5134 and SN22-5148. Changes or additions to the text and illustrations are indicated by a vertical line to the left of the change.

Changes are made periodically to the information herein; before using this publication in connection with the operation of IBM equipment, refer to the latest *IBM System/370, 30xx, 4300, and 9370 Processors Bibliography*, GC20-0001, for the editions that are applicable and current.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to IBM Corporation, Product Publications, Department B98, PO Box 390, Poughkeepsie, NY, USA 12602. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

c Copyright International Business Machines Corporation 1985, 1986, 1987, 1988

## **Preface**

1

This manual is intended for management, programming, and operations personnel; it describes the components, functions, and models of the IBM 3090 Processor Complex.

Readers of this manual should be familiar with IBM System/370 (S/370), IBM System/370 extended architecture (370-XA), and IBM Enterprise Systems Architecture/370<sup>TM</sup> (ESA/370<sup>TM</sup>) as defined in the *IBM System/370 Principles of Operation*, GA22-7000, the *IBM System/370 Extended Architecture Principles of Operation*, SA22-7085, and the *IBM Enterprise Systems Architecture/370 Principles of Operation* (to be available at a later date).

This manual contains information on the 3090 Processor Complex Models 120E, 150, 150E, 180, 180E, 200, 200E, 280E, 300E, 400, 400E, 500E, and 600E. This manual contains seven chapters, two appendixes, a glossary, and a bibliography.

- Chapter 1, "Introduction" summarizes the model configurations, design highlights, and programming support of the 3090 Processor Complex.

- Chapter 2, "3090 Processor Complex" describes the characteristics of the 3090 Processor Complex.

- Chapter 3, "3090 Processor Unit" describes the logical components of the processor unit.

- Chapter 4, "Consoles and Displays" describes the interactive consoles and displays in the 3090 Processor Complex and, in particular, the facilities provided by the system console.

- Chapter 5, "3092 Processor Controller" describes the processor controller.

- Chapter 6, "Error Handling" describes error recovery procedures that are performed automatically by the processor controller, the customer problem analysis procedures, and the remote support facility procedures.

- Chapter 7, "3090 Features" describes the standard and optional features provided by the 3090 Processor Complex.

- Appendix A, "3090 Architectural Deviations" contains exceptions to the IBM System/370 Principles of Operation, the IBM System/370 Extended Architecture Principles of Operation, and the IBM Enterprise Systems Architecture/370 Principles of Operation.

Enterprise Systems Architecture/370 and ESA/370 are trademarks of the International Business Machines Corporation.

- Appendix B, "Summary of 3090 Model Configurations" is a table that shows the 3090 Processor Complex model configurations.

- "Glossary of Terms and Abbreviations" defines the technical terms and abbreviations used in this manual.

)

Sand

• "Bibliography" lists the manuals that are recommended for use with this manual.

## Contents

1

I

**Chapter 1. Introduction** 1-1 1-2 Summary of 3090 Model Configurations **Design Highlights** 1-6 **High-Level Performance** 1.7 **Optional Expanded Storage** 1.7 Improved Technology 1-7 Improved Reliability, Availability, and Serviceability 1-7 Choice of Architectural Modes of Operation 1-8 **Optional Logically Partitioned Operating Mode** 1-9 **Engineering and Scientific Capabilities** 1-10 Vector Facility Feature 1-10 **Programming Compatibility** 1-11 **Programming Support** 1-12 **Control Programs for Basic Modes** 1-12 **Guest Control Programs** 1-13 **Control Programs for Logically Partitioned Operation** 1-14 Chapter 2. 3090 Processor Complex 2-1 2-1 **Processor Complex Machine Requirements Standard Machine Requirements**  $2 \cdot 3$ **Corequisite Machine Requirements** 2-3 **Optional Machines and Features** 2-4 2-6 **Console and Display Configuration** Power and Cooling 2-7 Power 2-7 Cooling 2-7 Input/Output Operations 2-7 S/370 Mode 2-8ESA/370 and 370-XA Modes 2-8Channel-to-Channel Connection 2-9Storage Operations 2-9 Data Representation 2 - 10System Security 2 - 10**Data Integrity** 2-10 System Access Control 2-11 Technology 2-11 **Processor Controller** 2-11 Reliability, Availability, and Serviceability Considerations 2 - 12Chapter 3. 3090 Processor Unit 3-1 **CPU ID** 3-2 Central Processors 3-4 Instruction Element 3-4 Execution Element 3-5 **Control Storage Element** 3-6 Buffer Control Element 3-6 **Vector Facility Feature** 3-6 Storage 3-7 **Central Storage** 3-8 Hardware System Area 3-8 **Error Checking and Correction** 3-9

**Frame Deallocation** 3-9**Key-Controlled Storage Protection** 3-9 Expanded Storage 3-9 **Error Checking and Correction** 3-9 Channel Subsystem 3 - 10**Channel Control Element** 3-12 Channels 3-12 System Control Element 3 - 12

Chapter 4. Consoles and Displays 4-1 System Console Interactive Facilities 4-2 System Definition 4-3 System Activity Display 4-3 I/O Configuration Data Set Content 4-3 I/O Problem Determination Information 4-4

5-1

Niiiii

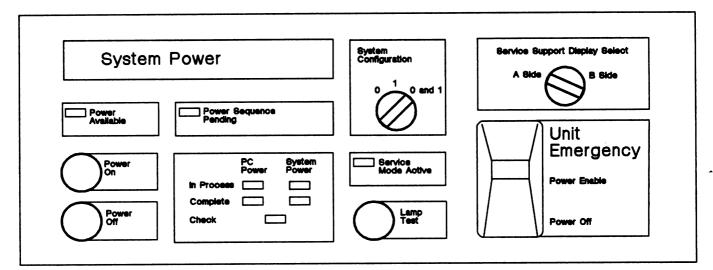

Chapter 5. 3092 Processor Controller Corequisites 5-2System Power Panel 5-3 **Dual Support Processors** 5-3 **Operation Monitoring and Control** 5-4 Error Recovery 5-4 Configuration 5-4 **Remote Support Facility** 5-5**RSF** Configuration 5-5 **RSF** Authorization 5 - 5**RSF Call Details** 5-6

### Chapter 6. Error Handling 6-1 Automatic Error Recovery 6-1 Error Checking and Correction 6-1 Machine-Check Handling 6-1 I/O Operations 6-3 Problem Analysis 6-4 Power Malfunction 6-4

Other Malfunctions 6-4 Remote Support Facility 6-5

### Chapter 7. 3090 Features 7-1

Features Dependent on Architectural Mode 7-3 Programming Assists Dependent on Architectural Mode 7-5 Features Not Dependent on Architectural Mode 7-6 **Feature Descriptions** 7-6 **Basic Control Mode** 7-6 **Bimodal Addressing** 7-7 Branch and Save 7-7 **Byte-Oriented Operand** 7-7 **Channel Indirect Data Addressing** 7-7 Channel-Set Switching 7-7 Channel Subsystem 7-7 Channels 7-8 Clear I/O 7-8 **Command Retry** 7-8 **Conditional Swapping** 7-8

7-8 **Control-Switch Assist** CPU Retry 7-8 **CPU** Timer and Clock Comparator 7-8 7-9 **Data Streaming** 7-9 Error Checking and Correction Expanded Storage 7-10 **Extended-Precision Divide** 7-10 **Extended-Precision Floating Point** 7-10 **Extended Real Addressing** 7-10 **Fast Release** 7-10 **Floating Point** 7-10 Halt Device 7-10 High-Speed Buffer Storage 7-11 Incorrect-Length-Indication-Suppression Facility 7-11 Interpretive Execution 7-11 Interval Timer 7-11 I/O Error Alert 7-11 I/O Power Sequence Control 7-11 **Key-Controlled Storage Protection** 7-12 Limited Channel Logout 7-12 Monitoring 7-12 7-12 Processor Resource/Systems Manager Additional Byte-Multiplexer Channels 7-12 Logical Partitioning 7-12 **Multiple High Performance Guests** 7-13 Multiprocessing 7-13 **CPU Address Identification** 7-13 **CPU** Signaling and Response 7-13 Prefixing 7-13 Shared Main Storage 7-13 7-13 **TOD Clock Synchronization** Page Protection 7-14 **Preferred Machine Assist** 7-14 **PSW-Key Handling** 7-14 7-14 **Recovery Extensions** Segment Protection 7-14 Service Signal 7-14 SIE Assist 7-15 Sorting Instructions 7-15 Storage Key Instruction Extensions 7-15 Storage Key Instructions 7-15 7-15 Storage-Key 4K-Byte Block System/370 Extended Facility 7-15 System/370 I/O Instructions 7-16 Test Block 7-16 **Time-of-Day Clock** 7-16 Tracing 7-17 Translation 7-17 **Dynamic Address Translation** 7-17 **Extended Control Mode** 7-18 Program-Event Recording 7-18 Set-System-Mask Suppression 7-18 Store Status 7-18 **Vector Facility Feature** 7-18

1

1

Virtual-Machine Assist 7-18 VM Assists for the CPU Timer 7-19 3033 Extension 7-19 **Dual-Address Space** 7-19 Start-I/O-Fast Queuing 7-19 Suspend and Resume 7-20 31-Bit Indirect Data Address Word 7-20 31-Bit Real Addressing 7-20

Appendix A. 3090 Architectural DeviationsA-1Concurrent Indication of PER Events with Operand-Access ExceptionA-1Protection Violation Instead of Delayed Access ExceptionA-1Fetch Protection IgnoredA-1

in and

Appendix B. Summary of 3090 Model Configurations B-1

Glossary of Terms and Abbreviations X-1

Bibliography X-7

Index X-9

# Figures

1

- 1-1. IBM 3090 Processor Complex Model 400 with Other Devices 1-2

- 2-1. IBM 3090 Model 600E Plan View 2-2

- 2-2. Optional Machines and Features 2-5

- 3-1. IBM 3090 Processor Unit Logical Components (Model 600E) 3-2

- 3-2. Elements of a Central Processor 3-4

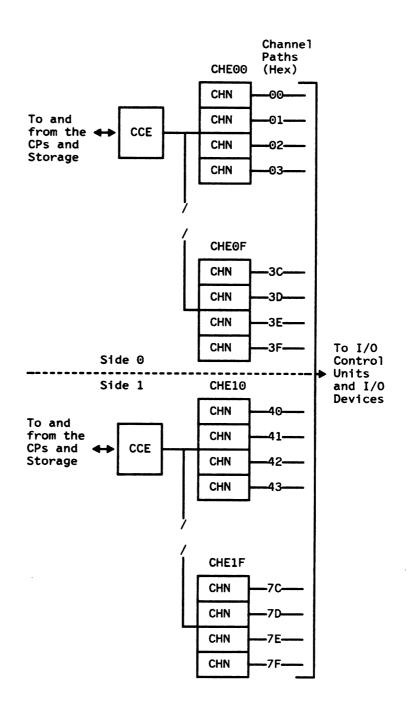

- 3-3. Channel Subsystem for 3090 Model 600E 3-12

- 4-1. IBM 3180 Display Station Model 140 4-2

- 4-2. IBM 3206 Display Station Model 100 4-2

- 5-1. IBM 3092 Processor Controller Model 1 5-1

- 5-2. 3092 Model 1 or Model 2 System Power Panel 5-3

- 6-1. Machine-Check Interruption Code (MCIC) 6-3

) -• ·...) ---

# **Chapter 1. Introduction**

1

ł

1

1

The IBM 3090 Processor Complex is a general-purpose data processing system. The IBM 3090 base models (Models 150, 180, 200, and 400) provide for operation in System/370 (S/370) mode or in System/370 extended architecture mode. The enhanced IBM 3090 Models 120E, 150E, 180E, 200E, 280E, 300E, 400E, 500E, and 600E are the most recent models of the IBM 3090 Processor Complex and can operate in S/370 mode or in Enterprise Systems Architecture/370 (ESA/370) mode. These systems provide reliability, performance, and ease of use for commercial, engineering, and scientific applications.

The 3090 is a compatible growth system for the IBM 3081, 3083, and 3084 Processor Complexes.

The enhanced Model 150E corresponds to the base Model 150, the enhanced Model 180E corresponds to the base Model 180, the enhanced Model 200E corresponds to the base Model 200, and the enhanced Model 400E corresponds to the base Model 400. Upgrade progression for the models is shown in the following table:

| Model | Upgrade<br>Progression |

|-------|------------------------|

| 120E  | 150E                   |

| 150   | 180 or 180E            |

| 150E  | 180E                   |

| 180   | 200 or 200E or 280E    |

| 180E  | 200E or 280E           |

| 200   | 300E or 400 or 400E    |

| 200E  | 300E or 400E           |

| 280E  | 400E                   |

| 300E  | 400E or 500E or 600E   |

| 400   | 600E                   |

| 400E  | 500E or 600E           |

| 500E  | 600E                   |

Figure 1-1 on page 1-2 shows a view of a 3090 Processor Complex Model 400.

Figure 1-1. IBM 3090 Processor Complex Model 400 with Other Devices

## Summary of 3090 Model Configurations

- The **3090 Model 120E** is a uniprocessor; it contains one central processor (CP). The CP has access to central storage, expanded storage, and channels. The 3090 Model 120E provides:

- One CP

- A vector facility feature (optional) for the CP

- 32M bytes of central storage

- Expanded storage (optional):

- 64M bytes

- 128M bytes

- 16 or 24 integrated channels (16 are standard)

- Logically partitioned operation (optional) with as many as four logical partitions

- The **3090 Model 150** is a uniprocessor; it contains one CP. The CP has access to central storage and channels. The 3090 Model 150 provides:

- One CP

- A vector facility feature (optional) for the CP

- 32M or 64M bytes of central storage

- 16 or 24 integrated channels (16 are standard)

- The **3090 Model 150E** is a uniprocessor; it contains one CP. The CP has access to central storage, expanded storage, and channels. The 3090 Model 150E provides:

- One CP

- A vector facility feature (optional) for the CP

- 32M or 64M bytes of central storage

- Expanded storage (optional):

- 64M bytes

- 128M bytes

- 16 or 24 integrated channels (16 are standard)

- Logically partitioned operation (optional) with as many as four logical partitions

- The **3090 Model 180** is a uniprocessor; it contains one CP. The CP has access to central storage, expanded storage, and channels. The 3090 Model 180 provides:

- One CP

1

1

- A vector facility feature (optional) for the CP

- 32M or 64M bytes of central storage

- Expanded storage (optional):

- 64M bytes

- 128M bytes

- 192M bytes

- 256M bytes

- 16, 24, or 32 integrated channels (16 are standard)

- The **3090 Model 180E** is a uniprocessor; it contains one CP. The CP has access to central storage, expanded storage, and channels. The 3090 Model 180E provides:

- One CP

- A vector facility feature (optional) for the CP

- 32M or 64M bytes of central storage

- Expanded storage (optional):

- 64M bytes

- 128M bytes

- 192M bytes

- 256M bytes

- 16, 24, or 32 integrated channels (16 are standard)

- Logically partitioned operation (optional) with as many as four logical partitions

- The **3090 Model 200** is a two-way (dyadic) processor; it contains two integrated CPs, each having access to a common central storage, expanded storage, and channels. The 3090 Model 200 provides:

- Two integrated CPs

- A vector facility feature (optional) for each CP

- 64M bytes of shared central storage

- Shared expanded storage (optional):

- 64M bytes

- 128M bytes

- 192M bytes

- 256M bytes

- 32, 40, or 48 integrated channels (32 are standard)

- The **3090 Model 200E** is a two-way (dyadic) processor; it contains two integrated CPs, each having access to a common central storage, expanded storage, and channels. The 3090 Model 200E provides:

- Two integrated CPs

- A vector facility feature (optional) for each CP

- 64M or 128M bytes of shared central storage

- Shared expanded storage (optional):

- 64M bytes

- 128M bytes

- 192M bytes

- 256M bytes

- 512M bytes

- 1024M bytes

- 32, 40, 48, or 64 integrated channels (32 are standard)

- The **3090 Model 280E** is a two-way processor; it contains two integrated CPs, each having access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. The 3090 Model 280E provides:

- Two integrated CPs

- A vector facility feature (optional) for each CP

- 64M or 128M bytes of shared central storage

- Shared expanded storage (optional):

- 128M bytes

- 256M bytes

- 384M bytes

- 512M bytes

- 32, 48, or 64 integrated channels (32 are standard)

- Capability to be operated in a physically partitioned configuration as two uniprocessors similar to two Model 180Es

- Logically partitioned operation (optional) with as many as four logical partitions (as many as eight when in a physically partitioned configuration)

- The **3090 Model 300E** is a three-way (triadic) processor; it contains three integrated CPs, each having access to a common central storage, expanded storage, and channels. The 3090 Model 300E provides:

- Three integrated CPs

- A vector facility feature (optional) for each CP

- 64M or 128M bytes of shared central storage

- Shared expanded storage (optional):

- 64M bytes

- 128M bytes

- 192M bytes

- 256M bytes

- 512M bytes

- 1024M bytes

- 32, 40, 48, or 64 integrated channels (32 are standard)

- Logically partitioned operation (optional) with as many as four logical partitions

- The **3090 Model 400** is a four-way (dual-dyadic) processor; it contains four integrated CPs, each having access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. The 3090 Model 400 provides:

- Four integrated CPs

I

- A vector facility feature (optional) for each CP

- 128M bytes of shared central storage

- Shared expanded storage (optional):

- 128M bytes

- 256M bytes

- 384M bytes

- 512M bytes

- 64, 80, or 96 integrated channels (64 are standard)

- Capability to be operated in a physically partitioned configuration as two dyadic processors similar to two Model 200s

- The **3090 Model 400E** is a four-way (dual-dyadic) processor; it contains four integrated CPs, each having access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. The 3090 Model 400E provides:

- Four integrated CPs

- A vector facility feature (optional) for each CP

- 128M or 256M bytes of shared central storage

- Shared expanded storage (optional):

- 128M bytes

- 256M bytes

- 384M bytes

- 512M bytes

- 1024M bytes

- 2048M bytes

- 64, 80, 96, or 128 integrated channels (64 are standard)

- Capability to be operated in a physically partitioned configuration as two dyadic processors similar to two Model 200Es

- Logically partitioned operation (optional) with as many as four logical partitions (as many as eight when in a physically partitioned configuration)

- The **3090 Model 500E** is a five-way (triadic-dyadic) processor; it contains five integrated CPs, each having access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. The 3090 Model 500E provides:

- Five integrated CPs

- A vector facility feature (optional) for each CP

- 128M or 256M bytes of shared central storage

- Shared expanded storage (optional):

- 128M bytes

- 256M bytes

- 384M bytes

- 512M bytes

- 1024M bytes

- 2048M bytes

- 64, 80, 96, or 128 integrated channels (64 are standard)

- Capability to be operated in a physically partitioned configuration as a triadic processor (similar to a Model 300E) and as a dyadic processor (similar to a Model 200E)

- Logically partitioned operation (optional) with as many as four logical partitions (as many as eight when in a physically partitioned configuration)

- The **3090 Model 600E** is a six-way (dual-triadic) processor; it contains six integrated CPs, each having access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. The 3090 Model 600E provides:

- Six integrated CPs

- A vector facility feature (optional) for each CP

- 128M or 256M bytes of shared central storage

- Shared expanded storage (optional):

- 128M bytes

- 256M bytes

- 384M bytes

- 512M bytes

- 1024M bytes

- 2048M bytes

- 64, 80, 96, or 128 integrated channels (64 are standard)

- Capability to be operated in a physically partitioned configuration as two triadic processors similar to two Model 300Es

- Logically partitioned operation (optional) with as many as four logical partitions (as many as eight when in a physically partitioned configuration)

### **Design Highlights**

The 3090 provides high performance and flexibility of use with improved design and technology. The design of the 3090 incorporates:

- High-level performance

- Optional expanded storage (except on the Model 150)

- Improved technology

- Improved reliability, availability, and serviceability

- Choice of architectural modes of operation

- Optional logically partitioned operating mode (except on Models 150, 180, 200, and 400)

- Engineering and scientific capabilities

### **High-Level Performance**

1

1

1

The 3090 achieves high-level performance by:

- A 17.2-nanosecond (ns) machine cycle time for Models 180E, 200E, 280E, 300E, 400E, 500E, and 600E.

- A 17.75-ns machine cycle time for Model 150E.

- An 18.5-ns machine cycle time for Models 120E, 150, 180, 200, and 400.

- A high-speed 64K-byte buffer in each CP.

- Buffer-to-buffer data paths.

- The use of emitter-coupled logic (ECL) in the thermal conduction modules (TCMs).

- Optional expanded storage (except Model 150) to extend central storage capacity, to reduce paging, and to improve response time for all 3090 models.

- Optional vector facility feature on each CP for improved performance of engineering and scientific applications.

## **Optional Expanded Storage**

Optional high-speed, high-capacity expanded storage is available as an integrated part of the 3090 Processor Complex. Expanded storage improves system response and system performance balancing. Models 400E, 500E, and 600E offer as much as 2G bytes (2 147 483 648 bytes) of optional storage. Optional expanded storage for the 3090 models is shown in "Optional Machines and Features" on page 2-4.

### Improved Technology

The 3090 uses large-scale integration that permits as many as 132 high-density silicon chips to be mounted on a multilayered ceramic substrate in a helium-filled module called a thermal conduction module (TCM). TCMs plug into a supporting multilayered circuit board. The use of TCMs and the boards significantly reduces requirements for power, space, cabling, and cooling, while enhancing reliability. Performance is improved because the TCMs use a faster-circuit family of emitter-coupled logic (ECL) instead of transistor-to-transistor logic (TTL).

### Improved Reliability, Availability, and Serviceability

The 3090 offers improved reliability, availability, and serviceability (RAS) by providing:

Additional online error detection and fault isolation techniques

- Deferred maintenance capability

- Enhanced remote support strategy

RAS improvements are implemented by the processor controller, which (except for the Model 120E) contains two integrated processor elements. The dual processor elements provide backup in single-image configuration for critical processor controller functions and for improved 3090 availability.

### **Choice of Architectural Modes of Operation**

The 3090 base models (Models 150, 180, 200, and 400) can operate either in System/370 (S/370) mode or in System/370 extended architecture (370-XA) mode. The 3090 enhanced models (Models 120E, 150E, 180E, 200E, 280E, 300E, 400E, 500E, and 600E) can operate either in S/370 mode or in Enterprise Systems Architecture/370 (ESA/370) mode. The mode is selected when the 3090 is initialized. In S/370 mode, the 3090 has full compatibility with System/370. In 370-XA mode, the 3090 base models have the advantages of System/370 extended architecture and have problem-program compatibility with System/360, System/370, and 4300 processors. In ESA/370 mode (which includes the functions of 370-XA mode), the 3090 enhanced models can access virtual storage in multiple address spaces and data spaces. This significantly extends addressability for system, subsystem, and application functions that use ESA/370.

#### Notes:

- The 3090 Model 400 in single-image configuration operates only in 370-XA mode. The 3090 Models 280E and 400E in single-image configuration and the 3090 Models 300E, 500E, and 600E operate only in ESA/370 mode.

- 2. The 3090 Model 400 in a physically partitioned configuration is similar to two 3090 Model 200s, and each side independently can operate either in S/370 or 370-XA mode. The 3090 Models 280E and 400E in physically partitioned configuration are similar to two 3090 Model 180Es and 200Es, respectively, and each side independently can operate either in S/370 or ESA/370 mode, or be logically partitioned.

### S/370 mode provides:

- System/370 extended facility

- 3033 extension

- Extended addressing

- As many as 16 channels for Multiple Virtual Storage/System Product (MVS/SP<sup>TM</sup>) for each channel set or as many as 32 channels for Virtual

Machine/System Product High Performance Option (VM/SP HPO) for each channel set

370-XA mode provides:

- 31-bit addressing that provides a capability of a virtual address range of 2G bytes (2 147 483 648 bytes).

- Bimodal addressing that allows programs written with S/370 mode 24-bit addressing to execute and coexist with programs written with 370-XA mode 31-bit addressing.

- Channel path selection and I/O-busy-condition management as hardware functions (rather than system control program functions) that provide:

- As many as four channel paths available to each I/O device.

- Increased I/O device accessibility by allowing each central processor to initiate operations with any of the I/O devices and to handle any I/O interruption conditions.

- Support for the Start Interpretive Execution (SIE) instruction, allowing support of guest S/370 or 370-XA virtual machines.

ESA/370 mode provides:

- All of the functions of 370-XA mode

- A significantly extended addressability through access to multiple address spaces and data spaces while maintaining compatibility with existing 24-bit and 31-bit subsystems and user applications. Each address space can contain as many as 2G bytes of programs and data. Each data space can contain as many as 2G bytes of data.

- Support for the SIE instruction, allowing support of guest S/370 or ESA/370 virtual machines. On Models 120E, 150E, 180E, 200E, 280E, 300E, 400E, 500E, and 600E, the benefits of VM assist are provided to an interpretively executed S/370 mode guest virtual machine.

### **Optional Logically Partitioned Operating Mode**

L

1

1

1

The optional Processor Resource/Systems Manager<sup>TM</sup> (PR/SM<sup>TM</sup>) feature offers the capability to enable the event-driven, logical partitioning function of the 3090 Processor Complex. When the PR/SM feature is installed, three modes can be enabled: S/370, ESA/370 (which supports 370-XA and ESA/370 operating systems), and logically partitioned (LPAR) mode. When the logically partitioned mode of operation is chosen, the operator can define the resources that are to be allocated to each logical partition. Most resources can be reconfigured without requiring a power-on reset. After an S/370 or ESA/370 logical partition is defined and

Processor Resource/Systems Manager and PR/SM are trademarks of the International Business Machines Corporation.

activated, a supporting operating system can be loaded into that logical partition. Central storage and optional expanded storage are defined to logical partitions before partition activation. When a logical partition is activated, the storage resources are allocated in 1M-byte contiguous blocks. These allocations are static upon activation. Sharing of allocated central storage or expanded storage among multiple logical partitions is not allowed.

Individual channel paths may be allocated to each logical partition. A channel path can be allocated only to one logical partition at a time. A device can be shared between logical partitions by using a separate channel path from each logical partition. Channel paths can be dynamically reconfigured between logical partitions.

CPs can be dedicated to a single logical partition or shared among multiple logical partitions. The allocation of CPs to a logical partition is made when the partition is activated. The use of CP resources shared between logical partitions can be modified by operator commands while the logical partitions are active.

An optional vector facility that is installed on a CP is available for use by all partitions that will perform on that CP. CPs that are dedicated to a logical partition (including associated vector facilities) are available only to that logical partition.

### **Engineering and Scientific Capabilities**

Improved engineering and scientific computational performance in a general-purpose architecture are implemented by:

- Rapid floating-point arithmetic

- Very large storage

- High performance channels

- Improved availability

- A powerful instruction set

- Optional vector facility feature

### Vector Facility Feature

The vector facility feature is optional for each of the central processors of the 3090 Processor Complex; the vector facility feature is available on all 3090 models. Central processors with the optional vector facility feature provide significantly increased levels of performance for many compute-intensive engineering and scientific applications.

### **Programming Compatibility**

1

1

The information in this topic applies to all 3090 models in single-image configuration, independently to each side of a 3090 in physically partitioned configuration, and to operation in a logical partition.

Any program (including its programming support) written for S/370 mode, 370-XA mode, or ESA/370 mode operates on a 3090 operating in that mode, provided that the program:

- Is not time dependent.

- Does not depend on the presence of system facilities (such as storage capacity, I/O equipment, or optional features) when the facilities are not included in the configuration.

- Does not depend on the absence of system facilities when the facilities are included in the configuration.

- Does not depend on results or functions that are defined in the appropriate *Principles of Operation* manual (see "Bibliography" on page X-7) as being unpredictable or model dependent.

- Does not depend on results or functions that are defined in this manual (or, for logically partitioned operation, in the 3090 Processor Complex: Processor Resource/Systems Manager Planning Guide) as being differences or deviations from the appropriate Principles of Operation manual.

- Does not depend (for programs written for 370-XA mode) on the contents of instruction parameter fields B and C on interception of the SIE instruction. See IBM System/370 Extended Architecture Interpretive Execution for additional information.

- Does not depend (for S/370 mode) on the presence of the 2K-byte page size, or the presence of storage protection keys associated with 2K-byte blocks of storage.

Any program written for 370-XA mode operates in ESA/370 mode, any problem state program written for S/370 operates in ESA/370 mode or 370-XA mode, and any problem state program written for S/360 operates in ESA/370 mode, 370-XA mode, or S/370 mode, provided that the program:

- Observes the limitations in the preceding statements.

- Does not depend on any programming support facilities that are not provided or that have been modified.

- Takes into account other changes made that affect compatibility between modes. These changes are described in the IBM System/370 Extended Architecture Principles of Operation, in the IBM System/370 Principles of Operation, and in the IBM Enterprise Systems Architecture/370 Principles of Operation.

### **Programming Support**

Control program support is dependent on the mode in which the 3090 Processor Complex is operating. For example, a 3090 operating in 370-XA mode requires a control program for 370-XA mode.

*Note:* The term *basic modes* is used throughout this manual to refer to processor complex modes of operation other than logically partitioned mode. S/370, 370-XA, and ESA/370 are examples of basic modes.

### **Control Programs for Basic Modes**

Control program support for the 3090 Processor Complex includes:

- S/370 control programs for operation in S/370 mode

- MVS/SP Version 1 Release 3.5 (expanded storage and vectors are not supported; the maximum number of channels for each channel set is 16 and the maximum central storage supported is 64M bytes)

- VM/SP High Performance Option Release 4.2 (the maximum central storage supported is 64M bytes)

- TPF Version 2 Release 3

- 370-XA control programs for operation in ESA/370 mode or 370-XA mode

- MVS/SP Version 2 Release 1.3 (supports Models 400 and 400E in physically partitioned configuration only; supports only the two-processor side (side 1) of Model 500E in a physically partitioned configuration; and does not support Model 300E or 600E)

- MVS/SP Version 2 Release 1.7

- VM/XA Systems Facility Release 1 (does not support vector facilities or Models 300E, 500E, and 600E; Models 280E, 400, and 400E are supported only in physically partitioned configuration)

- VM/XA Systems Facility Release 2

- VM/XA System Product (the Processor Resource/Systems Manager feature is a prerequisite for the VM/XA SP Enhancement for Multiple Preferred Guests)

- TPF Version 2 Release 4

- ESA/370 control programs for operation in ESA/370 mode

- MVS/SP Version 3

### **Guest Control Programs**

1

1

Start Interpretive Execution (SIE) support is provided by VM/XA for the following guest environments, when the 3090 is operating in ESA/370 mode or 370-XA mode:

- Using VM/XA Systems Facility as host:

- MVS/SP Version 1 Release 1 with Release 1 Enhancement

- MVS/SP Version 1 Release 3

- MVS/SP Version 2 Release 1

- VM/SP Release 2.1

- VM/SP High Performance Option Release 3

- VM/XA Migration Aid Release 1 (V = V only)

- VM/XA Systems Facility (V=V only)

- OS/VS1 Release 7 with Basic Programming Extensions Release 3

- VSE/Advanced Function Release 3

- Using VM/XA System Product as host:

- MVS/SP Version 1 Release 3.5

- MVS/SP Version 2 Release 1.3

- MVS/SP Version 3 (requires VM/XA System Product Release 2 and operation in ESA/370 mode)

- VM/SP Release 4

- VM/SP High Performance Option Release 4.2

- OS/VS1 Release 7 with Basic Programming Extensions Release 4

- VSE/Advanced Function Version 2

- VSE/SP Version 2 and Version 3

- VM/XA Systems Facility (V = V only)

- VM/XA System Product (V = V only)

- TPF Version 2 Release 3 (if TPF-specific processor and DASD control unit RPQs are not required; requires VM/XA SP Enhancement for Multiple Preferred Guests)

### | Control Programs for Logically Partitioned Operation

• S/370 control programs for operation in S/370 mode in a logical partition.

Note: When operating in a logical partition, an S/370 mode control program is limited to the use of a single channel set.

- MVS/SP Version 1 Release 3.5

- VM/SP Release 5

- VM/SP High Performance Option Release 5

- VSE/Advanced Function Version 2

- VSE/SP Version 2 and Version 3

- TPF Version 2 Release 3 (if TPF-specific processor and DASD control unit RPQs are not required)

- 370-XA control programs for operation in ESA/370 mode in a logical partition:

- MVS/SP Version 2 Release 1.3

- VM/XA System Product Release 2 (for test and development purposes only; V = V guests only)

- TPF Version 2 Release 4 (if TPF-specific processor and DASD control unit RPQs are not required)

- ESA/370 control program for operation in ESA/370 mode in a logical partition:

- MVS/SP Version 3

# Chapter 2. 3090 Processor Complex

The following 3090 characteristics are described in this chapter:

- Processor complex machine requirements

- Optional machines and features

- Console and display configuration

- Power and cooling

- I/O operations

- Storage operations

- Data representation

- System security

- Technology

- Processor controller

- RAS considerations

# **Processor Complex Machine Requirements**

Ginit

The 3090 Processor Complex machine requirements fall into two categories:

- Standard machine requirements of the 3090 Processor Complex.

- Corequisite machine requirements for the operation and maintenance of the processor complex that are ordered separately.

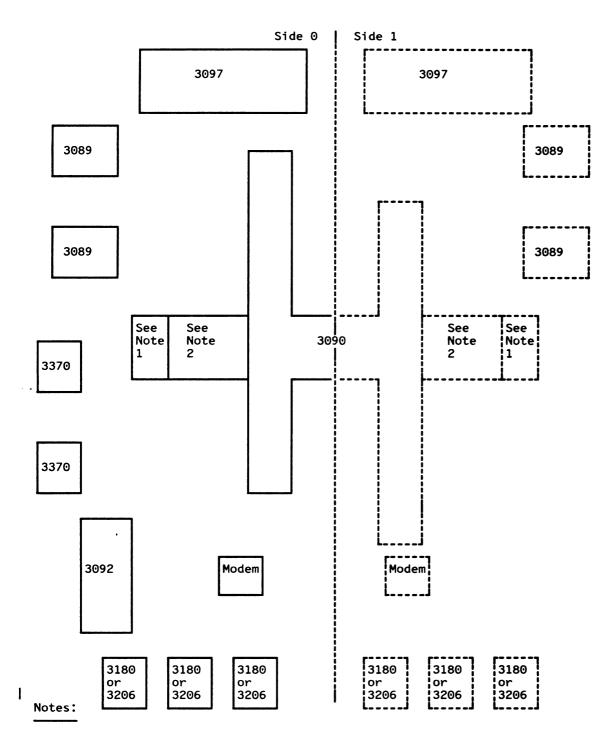

See Figure 2-1 on page 2-2 for a plan view of 3090 Model 600E.

iun!

- 1. This frame is present if 64 channels are installed on this side of the 3090.

- This frame is present if any vector facility feature, or three CPs, or 64 channels are installed on this side of the 3090.

- 3. This drawing is not to scale.

Figure 2-1. IBM 3090 Model 600E Plan View

### **Standard Machine Requirements**

1

1

1

1

1

The standard machine requirements for the 3090 Processor Complex are:

- One IBM 3090 Processor Unit Model 120E, 150, 150E, 180, 180E, 200, 200E, 280E, 300E, 400, 400E, 500E, or 600E.

- One IBM 3092 Processor Controller Model 1, 2, or 3. The 3092 Model 2 is for Models 280E, 400, 400E, 500E, or 600E; the 3092 Model 3 is for the Model 120E; all other 3090 models require the 3092 Model 1.

- One or two IBM 3097 Power and Coolant Distribution Units Model 1 or 2. Two 3097s are required for the 3090 Models 280E, 400, 400E, 500E, or 600E; one is required for the other 3090 models.

- Two or three IBM 3180 Display Stations Model 140 or IBM 3206 Display Stations Model 100. Three display stations are required for the 3090 Model 280E, 400, 400E, 500E, or 600E; two are required for the other 3090 models. See Chapter 4, "Consoles and Displays" on page 4-1 for more information.

### **Corequisite Machine Requirements**

The corequisite machine requirements for the 3090 Processor Complex are:

- Two IBM 3370 Direct Access Storage Model A2 units (or equivalent), each with a string-switch feature, except for the 3090 Model 120E that requires one 3370 Direct Access Storage Model A2 (string-switch feature not required).

- Access to one of the following:

- A path to one IBM 3803 Tape Control Unit Model 2 (or equivalent). The tape control unit must have an IBM 3420 Magnetic Tape Unit Model 4, 6, or 8 or an equivalent 6250 bit-per-inch tape unit with a maximum data rate of 1.25 megabytes per second. A 3090 Model 280E, 400, 400E, 500E, or 600E requires access to two channel paths to the magnetic tape unit.

- A path to an IBM 3422 Magnetic Tape Subsystem. A 3090 Model 280E, 400, 400E, 500E, or 600E requires access to two channel paths to the magnetic tape subsystem.

- A path to an IBM 3480 Magnetic Tape Unit Model B11 or Model B22 (or equivalent). A 3090 Model 280E, 400, 400E, 500E, or 600E requires access to two channel paths to the magnetic tape subsystem.

- One or two IBM 3864 Modems Model 2 (or equivalent) with an automatic calling unit feature. The 3090 Models 280E, 400, 400E, 500E, and 600E require two modems; all other 3090 models require one modem.

- One to four IBM 3089 Power Units Model 3 (or other 400-Hz power source):

- 3090 Models 120E, 150, and 150E: one 3089 Power Unit is required.

- 3090 Models 180 and 180E: two 3089 Power Units are required if the processor complex has both a vector facility feature and more than 128M bytes of expanded storage; otherwise, one 3089 Power Unit is required.

- 3090 Models 200, 200E, and 300E: two 3089 Power Units are required.

- 3090 Model 280E: four 3089 Power Units are required if the processor complex has two vector facility features and more than 256M bytes of expanded storage; three 3089 Power Units are required if the processor complex has one vector facility feature and more than 256M bytes of expanded storage; otherwise, two 3089 Power Units are required.

- 3090 Models 400, 400E, 500E, and 600E: four 3089 Power Units are required.

- One or two channel-attached operator display stations for communication with the control program. Two display stations are required for 3090 Models 280E, 400, 400E, 500E, and 600E in physically partitioned configuration and one for all other models. See Chapter 4, "Consoles and Displays" on page 4-1 for more information.

### **Optional Machines and Features**

Optional features for expanding the size, function, or performance of the system are ordered separately and are added to the processor complex at the customer's request.

Optional machines and features that may be included are shown in Figure 2-2.

To augment the standard machine requirement of two or three display stations, as many as three additional 3180 Display Stations Model 140 or 3206 Display Stations Model 100 may be attached to all 3090 models, except the 3090 Model 120E to which one additional display station may be attached. The 3180 Models 140 and 145 and the 3206 Models 100 and 110 can all be used interchangeably. Nam

| Optional                       |      |     |      |     |      |     |      |      |      |     |      |      |            |

|--------------------------------|------|-----|------|-----|------|-----|------|------|------|-----|------|------|------------|

| Machines<br>and Features       | 120E | 150 | 150E | 180 | 180E | 200 | 200E | 280E | 300E | 400 | 400E | 500E | 600E       |

| Vector Facility:               |      |     |      |     |      |     |      |      | 0-+  |     |      | 0-+  | 0-+        |

| VEO                            | -    | -   | -    | -   |      |     | -    | -    | Opt  | -   | -    | Opt  | Opt        |

| VE1                            | 0pt  | 0pt | 0pt  | 0pt | 0pt  | Opt | Opt  | 0pt  | Opt  | Opt | Opt  | Opt  | Opt        |

| VE2                            | -    | -   | -    | -   | -    | 0pt | 0pt  | -    | Opt  | Opt | Opt  | Opt  | Opt        |

| VE3                            | -    | -   | -    | -   | -    | -   | -    | 0pt  | -    | Opt | Opt  | Opt  | Opt<br>Opt |

| VE4                            | -    | -   | -    | -   | -    | -   | -    | -    | -    | 0pt | Opt  | 0pt  | •          |

| VE5                            | -    | -   | -    | -   | -    | -   | -    | -    | -    | -   | -    | -    | 0pt        |

| Central Storage:               |      |     |      |     |      |     |      |      |      |     |      |      |            |

| 32M bytes                      | Std  | Std | Std  | Std | Std  | -   | -    | -    | -    | -   | -    | -    | -          |

| 64M bytes                      | -    | 0pt | 0pt  | 0pt | 0pt  | Std | Std  | -    | Std  | -   | -    | -    | -          |

| 64M bytes                      | -    | -   | -    | -   | -    | -   | -    | Std  | -    | -   | -    | -    | -          |

| (32M bytes/side)               |      |     |      |     |      |     |      |      |      |     |      |      | -          |

| 128M bytes                     | -    | -   | -    | -   | -    | -   | 0pt  | -    | 0pt  | -   | •    | -    |            |

| 128M bytes<br>(64M bytes/side) | -    | -   | -    | -   | -    | -   | -    | Opt  | -    | Std | Std  | Std  | Std        |

| 256M bytes                     | _    | _   | -    | -   | -    | -   | -    | -    | -    | -   | 0pt  | Opt  | Opt        |

| (128M bytes/side               | )    |     |      |     |      |     |      |      |      |     |      |      |            |

| Expanded Storage:              |      |     |      |     |      |     |      |      |      |     |      |      |            |

| 64M bytes                      | Opt  | Opt | Opt  | 0pt | 0pt  | Opt | 0pt  | -    | 0pt  | -   | -    | -    | -          |

| 128M bytes                     | 0pt  | -   | Opt  | 0pt | Opt  | 0pt | 0pt  | -    | 0pt  | -   | -    | -    | -          |

| 128M bytes<br>(64M bytes/side) | -    | -   | -    | -   | -    | -   | -    | 0pt  | -    | 0pt | 0pt  | 0pt  | 0pt        |

| 192M bytes                     | -    | -   | -    | Opt | Opt  | 0pt | Opt  | -    | Opt  | -   | -    | -    | -          |

| 256M bytes                     | -    | -   | -    | Opt | Opt  | 0pt | Opt  | -    | 0pt  | -   | -    | -    | -          |

| 256M bytes                     | -    | -   | -    | -   | -    | -   | -    | Opt  | -    | 0pt | Opt  | Opt  | Opt        |

| (128M bytes/side               | )    |     |      |     |      |     |      |      |      | -   |      |      |            |

| 384M bytes                     | _    | -   | -    | -   | -    | -   | -    | 0pt  | -    | 0pt | 0pt  | 0pt  | Opt        |

| (192M bytes/side               | )    |     |      |     |      |     |      | •    |      | -   |      |      |            |

| 512M bytes                     |      | -   | -    | -   | -    | -   | 0pt  | -    | 0pt  | -   | -    | -    | -          |

| 512M bytes                     | -    | -   | -    | -   | -    | -   | -    | 0pt  | -    | 0pt | 0pt  | 0pt  | 0pt        |

| (256M bytes/side               | )    |     |      |     |      |     |      | ·    |      | -   |      |      |            |

| 1024M bytes                    | -    | -   | -    | -   | -    | -   | 0pt  | -    | Opt  | -   | -    | -    |            |

| 1024M bytes                    | -    | -   | -    | -   | -    | -   | -    | -    | -    | -   | 0pt  | 0pt  | 0pt        |

| (512M bytes/side               | )    |     |      |     |      |     |      |      |      |     | -    |      |            |

| 2048M bytes                    | -    | -   | -    | -   | -    | -   | -    | -    | -    | -   | 0pt  | 0pt  | 0pt        |

| (1024M bytes/sid               | e)   |     |      |     |      |     |      |      |      |     | -    |      |            |

| (102.11 2) 000/014             | -,   |     |      |     |      |     |      |      |      |     |      |      |            |

### Legend:

Cil

Opt Optional Std Standard - Not available

Figure 2-2 (Part 1 of 2). Optional Machines and Features

| Optional<br>Machines                              | Mode1            |               |                 |              |       |       |      |       |       |      |      |      |      |

|---------------------------------------------------|------------------|---------------|-----------------|--------------|-------|-------|------|-------|-------|------|------|------|------|

| Machines<br>and Features                          | 120E             | 150           | 150E            | 180          | 180E  | 200   | 200E | 280E  | 300E  | 400  | 400E | 500E | 600E |

| Processor<br>Resource/Systems<br>Manager Feature: | Opt              | -             | Opt             | -            | Opt   | -     | Opt  | 0pt   | Opt   | -    | 0pt  | 0pt  | Opt  |

| Channels:                                         |                  |               |                 |              |       |       |      |       | T     |      |      |      |      |

| 16                                                | Std              | Std           | Std             | Std          | Std   | -     | -    | -     | -     | -    | -    | -    | -    |

| 24                                                | 0pt              | 0pt           | 0pt             | 0pt          | 0pt   | -     | -    | -     | -     | -    | -    | -    | -    |

| 32                                                | -                | -             | -               | Opt          | Opt   | Std   | Std  | -     | Std   | -    | -    | -    | -    |

| 32 (16/side)                                      | -                | -             | -               | -            | -     | -     | -    | Std   | -     | -    | -    | -    | -    |

| 40                                                | -                | -             | -               | -            | -     | 0pt   | 0pt  | -     | 0pt   | -    | -    | -    | -    |

| 48                                                | -                | -             | -               | -            | -     | Opt   | Opt  | -     | 0pt   | -    | -    | -    | -    |

| 48 (24/side)                                      | -                | -             | -               | -            | -     | -     | -    | 0pt   | -     | -    | -    | -    | -    |

| 64                                                | -                | -             | -               | -            | -     | -     | 0pt  | -     | 0pt   | -    | -    | -    | -    |

| 64 (32/side)                                      | -                | -             | -               | -            | -     | -     | -    | 0pt   | -     | Std  | Std  | Std  | Std  |

| 80 (40/side)                                      | -                | -             | -               | -            | -     | -     | -    | -     | -     | Opt  | Opt  | Opt  | Opt  |

| 96 (48/side)                                      | -                | -             | -               | -            | -     | -     | -    | -     | -     | 0pt  | 0pt  | •    | 0pt  |

| 128 (64/side)                                     | -                | -             | -               | -            | -     | -     | -    | -     | -     | -    | 0pt  |      | 0pt  |

| Printers: IBM 328<br>201 or                       | 7 Prim<br>202, c | nter<br>or eq | Model<br>uivale | 1 or<br>ent. | 2, 01 | ∽ IBM | 4224 | Print | er Mo | odel |      |      |      |

| First Printer                                     | 0pt              | Opt           | 0pt             | 0pt          | Opt   | 0pt   | 0pt  | 0pt   | Opt   | 0pt  | 0pt  | Opt  | Opt  |

| Second Printer                                    | -                | -             | -               | -            | -     | -     | -    | 0pt   | _     | Opt  | Opt  | •    | Opt  |

Legend:

Opt Optional Std Standard - Not available

Figure 2-2 (Part 2 of 2). Optional Machines and Features

## **Console and Display Configuration**

A console is a logical device that performs logical functions. A display is a hardware device and is attached to particular ports of the processor controller. See "Standard Machine Requirements" on page 2-3 and "Optional Machines and Features" on page 2-4 for standard and optional consoles available for the 3090. See Chapter 4, "Consoles and Displays" on page 4-1 for more information.

The system and service support displays are controlled by the processor controller and the operator display is channel attached to the 3090 Processor Complex.

Optional displays are used for one or more of the following console functions:

- System console

- Service console

- Program mode console

- System monitor console

• Service monitor console

### **Power and Cooling**

Power and cooling are combined in one unit, the 3097 Power and Coolant Distribution Unit (PCDU) Model 1 or 2.

**Power**

The 3097 PCDU Model 1 or 2 distributes the 50-Hz or 60-Hz power and the 400-Hz power to the 3090 Processor Complex.

The 3097 PCDU Model 1 contains an I/O power sequence control. It can power on and off as many as 64 control units. With the optional, additional power sequence control, as many as 128 control units can be powered on and off. The 3097 PCDU Model 2 has reduced floor space requirements and does not include I/O power sequence control.

A Model 280E, 400, 400E, 500E, or 600E with two 3097 PCDUs Model 1 provides I/O power sequence control for 128, 192, or 256 control units.

### Cooling

1

The cooling system consists of a closed-loop, distilled water circulating system. Most of the heat generated by the 3090 Processor Complex is removed by this cooling system. The coolant is circulated throughout the frames and is returned to the 3097 PCDU for cooling in a heat exchanger, where external connections to customer-supplied chilled water absorb the heat from the cooling system water loop.

The 3097 PCDU maintains a controlled temperature for the densely packed circuits in the 3090 Processor Complex. The 3097 PCDU contains the necessary controls to maintain the correct temperature within the processor complex. The correct temperature is maintained through use of the water system in the 3097, which is a self-contained closed-loop system, and the customer-supplied chilled-water system.

If a cooling problem occurs because of a malfunction in the operating pump, an alternate pump is switched automatically into the coolant circuit for continued operation.

### **Input/Output Operations**

The following information describes 3090 Models 200 and 200E I/O operations. The other 3090 models operate similarly, but the number of central processors and channels differs. For a summary of these differences, see "Summary of 3090 Model Configurations" on page 1-2.

I/O operations are handled by the channel subsystem in the processor complex. All channels can be configured for block multiplex mode of

operation and as many as four channels (eight on the Models 280E, 400, 400E, 500E, and 600E) can be configured for byte multiplex mode of operation. If the PR/SM feature is installed, as many as eight channels (16 on the Models 280E, 400E, 500E, and 600E) can be configured for byte multiplex mode of operation. Any channel not needed for byte multiplex mode of operation can be configured for block multiplex mode of operation.

Failing channels can be removed from the operating configuration. As many as eight control units can be physically attached to a channel, and each channel can address as many as 256 I/O devices. However, for any 3090 model, the total number of devices attached is 4096 minus the number of channels defined by using the I/O Configuration Program (IOCP). The way in which the channel subsystem performs I/O operations differs depending on the mode of operation (S/370, 370-XA, or ESA/370 mode). Models 300E, 500E, and 600E do not support the S/370 mode of operation, except when operating in a logical partition.

### S/370 Mode

In S/370 mode, any channel may be assigned any valid channel address without concern for priority. Logically, channels are organized into two sets (one set for each central processor) with as many as 16 channels allowed in one set for MVS/SP operation and as many as 32 channels allowed in one set for VM/SP HPO operation. Channel-set switching is a standard feature. If one central processor fails, its channel set can be reassigned (under program control) to the other central processor. The other central processor can then use the two channel sets alternately to continue data processing (with some performance degradation).

*Note:* Operation in a logical partition is limited to the use of one channel set.

### + ESA/370 and 370-XA Modes

In ESA/370 mode or 370-XA mode, as many as four channel paths are available to any attached I/O device. During any I/O operation, one of the available channel paths to any specific I/O device is selected. Channel path selection is a hardware function rather than a function of the system control program.

At the start of an I/O operation, a central processor signals the channel subsystem (instead of a single channel, as in S/370 mode) that an I/O operation to a given I/O device is needed. An I/O request is posted to a queue; meanwhile, instruction execution in the central processor continues. Channel path management and the queuing of I/O requests eliminate all busy-condition I/O interruptions encountered in S/370-mode operations.

### **Channel-to-Channel Connection**

Channel-to-channel connection between multiple 3090 Processor Complexes is accomplished by using the IBM 3088 Multisystem Channel Communication Unit (MCCU) Model A1, 1, or 2. Channel-to-channel connection between 3090 Processor Complexes and other IBM processors can be accomplished by using the channel-to-channel adapter (CTCA) feature on those processors that offer it or by using the 3088 MCCU.

Both data-streaming and interlock modes are standard on the 3088 MCCU. Data-streaming mode provides for data transfers of as many as 4.5 megabytes per second, independent of cable length. Cable distances of 122 meters (400 feet) between the processor and the 3088 MCCU are supported in both data-streaming and interlock modes.

The 3088 MCCU Model A1 provides two-processor connectivity and as many as 63 logical CTCA links. The 3088 Model A1 can be field upgraded to a 3088 Model 1 or Model 2. The 3088 MCCU Model 1 can interconnect as many as four processor channels and can provide the equivalent function of as many as 126 CTCAs. The 3088 MCCU Model 2 can interconnect as many as eight processor channels and can provide the equivalent function of as many as 252 CTCAs.

### **Storage Operations**

1

1

1

A hierarchical storage structure increases performance and contributes to system reliability. Each central processor contains a 64K-byte high-speed buffer (cache) that handles instruction, operand, and data fetches.

Central storage provides storage capacity for the 3090 Processor Complex as shown in "Summary of 3090 Model Configurations" on page 1-2. Central storage is shared by all central processors. Expanded storage (an optional feature) is available for 3090 models as shown in the table in Appendix B, "Summary of 3090 Model Configurations" on page B-1.

Expanded storage is controlled by the control program and transfers 4K-byte pages to and from central storage. The control program can use expanded storage to reduce the paging and swapping load to channel-attached paging devices in a storage constrained environment and a heavy paging environment.

In ESA/370 mode and 370-XA mode, storage addressing is extended from 24 bits to 31 bits, which represents an address range of 2G bytes (2 147 483 648 bytes). In addition, these modes permit the use of either 24-bit or 31-bit addressing, under program control, and permits existing application programs to run with current control programs.

In ESA/370 mode and 370-XA mode, an additional channel command word (CCW) format is provided to permit direct addressing of storage of more than 16M bytes for I/O operations. With this format, channel programs may also reside in storage of more than 16M bytes.

## **Data Representation**

The basic addressable data unit is an 8-bit byte that may be used as one character, two decimal digits, or 8 binary bits. The 3090 provides the following data representation features:

- Efficient use of storage and effective I/O rates for decimal data

- Variable-length fields

- Broad and flexible code conversion

- Decimal arithmetic

- Fixed-point and floating-point arithmetic

- 32-bit words, 64-bit doublewords, and 128-bit extended words (for floating-point arithmetic)

- Instructions for functions such as translate, edit, convert, move, and compare

## System Security

Data integrity features and a two-level system access control contribute to a high level of system security. Customer planning and management are responsible for the implementation and adequacy of the following controls and for the use of the privileged operator controls such as display and alter storage.

MIII.

### **Data Integrity**

1

Data integrity is maintained through:

- Key-controlled storage protection (store and fetch)

- Low-address storage protection

- Storage error checking and correction

- Parity and other internal error checking

- Segment protection (S/370 mode only)

- Page protection (ESA/370 mode and 370-XA mode only)

- Block-multiplexer channel command retry

- Remote support authorization

- Clear reset of registers and main storage

### System Access Control

System access control protects against inadvertent system damage by restricting commands and the use of display frames only to persons at specified authorization levels. System access control is implemented through a hierarchical structure such that a user will have access to functions at a specified level as well as all levels below the specified level. Access levels can be defined for the system console and the service console.

Also, the 3180 and 3206 Display Stations provide the following:

- A security keylock on the display that allows authorized access and that prevents unauthorized access.

- User authorization for remote access (remote support facility) necessitates the matching of a user-assigned access code, as well as enablement of automatic dialing.

### Technology

1

The 3090 Processor Complex uses several logic-circuit technologies. The central processor logic is implemented by using emitter-coupled logic (ECL) in thermal conduction modules (TCMs). However, central storage and the processor controller function are implemented by a mixture of monolithic technologies.

The TCM is a helium-filled, encapsulated module that is covered by a cold plate through which chilled water circulates to absorb heat. The TCM measures 125 by 134 by 35 millimeters (4.9 by 5.3 by 1.4 inches) and contains as many as 132 silicon chips mounted on a multilayered ceramic substrate that produces a package containing tens of thousands of logic circuits. TCMs plug into a multilayered circuit board that provides TCM powering and TCM-to-TCM connections. Each central processor consists of nine TCMs and the associated circuit board. Therefore, the major element of a processor complex is designed so that no external wiring or cabling is required.

### **Processor Controller**

1

The 3092 Processor Controller is a stand-alone support unit that includes dual processors, except for the 3092 Model 3 used with the 3090 Model 120E that has one processor. One processor is active and the other is backup in the Model 150, 150E, 180, 180E, 200, 200E, or 300E; or in the Model 280E, 400, 400E, 500E, or 600E in single-image configuration. Both processors are active in Models 280E, 400, 400E, 500E, and 600E in physically partitioned configuration. The backup processor monitors the active processor to provide a high level of availability.

All models of the 3092 continuously monitor the 3090 Processor Complex operation through direct communication with each component in the processor complex. The 3092 initializes the system, distributes microcode to writable control storage at initialization, monitors voltage levels and coolant temperature, and provides the control unit function for the attached display stations.

The 3092 also provides extensive error recording, recovery, and diagnostic support for the processor complex.

**Microcode:** The 3090 microcode is a fundamental component of the 3090 Processor Complex and is copyrighted by IBM. Each 3090 processor is delivered with a set of microcode that is customized to the machine ordered. The microcode enables the 3090 to operate in accordance with its functional specifications, and is provided in accordance with the following procedures.

Customers who order a 3090 Processor Complex that includes two 3370-A2s plant merged with the 3090 Processor Complex will receive the 3090 microcode stored on each of the 3370 Model A2s (or on one 3370-A2 for the Model 120E).

If 3370-A2s are not plant merged with the 3090 Processor Complex, the customer must coordinate their availability with the 3090 for installation. The 3090 microcode is loaded on the 3370-A2s as part of the installation of the 3090.

Model upgrades, feature additions, and system engineering changes needed by the customer may require updated microcode for the 3090. The updated microcode replaces the existing microcode which must be returned to IBM or erased.

Vinn'

Relocation of the 3090 Processor Complex requires that the 3370-A2s containing the microcode will be reinstalled with the 3090 processor at the new location. The microcode may be shipped on the 3370-A2s, when they will be reinstalled with the 3090 processor at its new location. When the 3370-A2s will not be reinstalled with the 3090 processor at its new location, the microcode must be removed from the 3370-A2s and packaged on appropriate media for shipment with the 3090 processor. After the microcode has been removed and placed on the appropriate media, the 3370-A2s must be erased.

## Reliability, Availability, and Serviceability Considerations

Reliability, availability, and serviceability (RAS) are improved in the 3090 by the reduction of downtime and by using standard features.

### **Reliability:**

- ECL/TCM technology that provides a low intrinsic failure rate

- A dual processor controller (except for the 3090 Model 120E) that incorporates switchover and initialization of the functional side in single-image configuration

- Dual 3370 Direct Access Storage Model A2 units (except for the 3090 Model 120E) that support switchover in single-image configuration

• Multiple consoles for monitoring functional console activity and for backup

#### Availability:

- Two or more central processors available on certain models

- Automatic error detection and correction in both central storage and expanded storage

- Single-bit error correction and double-bit error detection in central storage

- Single-bit and double-bit error correction and triple-bit error detection in expanded storage

- Storage deallocation

- In 2M-byte increments under system program control for Models 120E, 150, 150E, 180, 200, and 400

- In 4M-byte increments under system program control for Models 180E, 200E, 280E, 300E, 400E, 500E, and 600E

- The ability to vary channels offline in single channel increments

- Customer problem analysis to effect recovery without a service call

#### Serviceability:

1

- The location of many functional elements on power boundaries

- Automatic fault isolation (analysis routines) concurrent with operation

- Automatic remote support capability

- On-site problem isolation

- Field-replaceable unit (FRU) isolation

- Trace tables

- Error logout recording

) • • • • .

### Chapter 3. 3090 Processor Unit

1

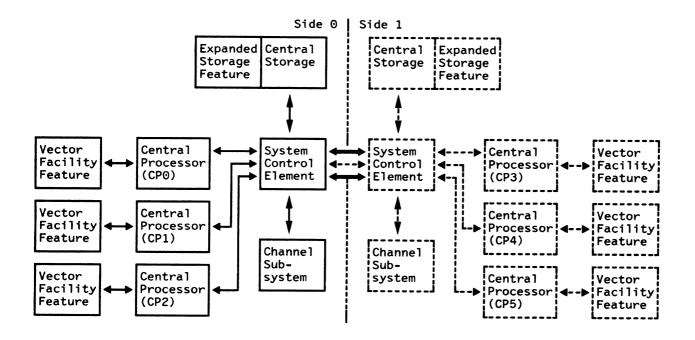

1

1

The 3090 Processor Unit consists of logical components (see Figure 3-1 on page 3-2) that execute instructions and commands and that perform storage and channel operations. The 3090 logical components are:

- One or more central processors

- Central storage

- Optional expanded storage (except Model 150)

- One or two channel subsystems

- One or two system control elements

Note: For Models 280E, 400, 400E, 500E, and 600E, central storage, expanded storage, and channels are installed symmetrically, as shown in Figure 2-2 on page 2-5.

The vector facility feature is an optional feature that is available for each central processor.

The 3090 Models 120E, 150, 150E, 180, 180E, 200, 200E, and 300E have one processor unit. The central processors, central storage, and the channel subsystem are contained in the processor unit.

The 3090 Models 280E, 400, 400E, 500E, and 600E have one processor unit with two sides (side 0 and side 1). The central processors, processor storage, and the channel subsystems are each associated with either side 0 or side 1. In a single-image configuration, the two sides function as one. In a physically partitioned configuration, the two sides are logically and physically separate.

Figure 3-1. IBM 3090 Processor Unit Logical Components (Model 600E)

### **CPU ID**

1

A doubleword designated by the second operand address of the Store CPU ID (STIDP) instruction provides information about the 3090 Processor Complex. More information can be found in the IBM System/370 Principles of Operation, the IBM System/370 Extended Architecture Principles of Operation, and the IBM Enterprise Systems Architecture/370 Principles of Operation. A summary of the contents of the doubleword follows:

VV A SSSSS 3090 0000

- VV is the version code (two hexadecimal digits):

- 03 (Model 120E)

- 05 (Model 150)

- 06 (Model 150E)

- 09 (Model 280E)

- 10 (Model 180)

- 11 (Model 180E)

- 20 (Model 200)

- 21 (Model 200E)

- 31 (Model 300E)

- 40 (Model 400)

- 41 (Model 400E)

- 51 (Model 500E)

1

I

L

- 61 (Model 600E)

- ASSSSS is the central processor (CPU) identification number (six hexadecimal digits):

- The first digit (A) is the central processor address, as stored by the Store CPU Address (STAP) instruction (see "CPU Address Identification" on page 7-13):

| Digit                                                                                                                                                                                                                                                                                                       | Model                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>1<br>1<br>1 or 2<br>1 or 2<br>1                                                                                                                                                                                                                                                                   | 120E<br>150<br>150E<br>180<br>180E<br>200<br>200E<br>280E (side 0)                                                                                          |

| $\begin{array}{c} 3\\ 0 \text{ or } 1 \text{ or } 2\\ 1 \text{ or } 2\\ 3 \text{ or } 4\\ 1 \text{ or } 2\\ 3 \text{ or } 4\\ 0 \text{ or } 1 \text{ or } 2\\ 3 \text{ or } 4\\ 0 \text{ or } 1 \text{ or } 2\\ 3 \text{ or } 4\\ 0 \text{ or } 1 \text{ or } 2\\ 3 \text{ or } 4 \text{ or } 5\end{array}$ | 280E (side 1)<br>300E<br>400 (side 0)<br>400 (side 1)<br>400E (side 0)<br>400E (side 1)<br>500E (side 0)<br>500E (side 1)<br>600E (side 0)<br>600E (side 1) |

- The next five digits (SSSSS) are selected from the serial number of the 3090 Processor Unit.

- The next four digits are 3090 (for the processor complex).

- The last four hexadecimal digits are 0000.

Note: When the processor complex is operating in a logical partition, the CPU ID presented to that logical partition is not the same as when the processor complex is operating in the S/370 or ESA/370 mode. See the IBM 3090 Processor Complex: Processor Resource/Systems Manager Planning Guide for more information.

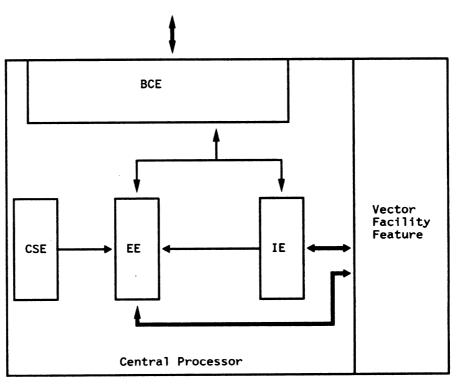

### **Central Processors**

Each central processor (Figure 3-2) is microcode controlled and contains an instruction element (IE), execution element (EE), control storage element (CSE), and buffer control element (BCE). The CSE fetches microinstructions that control instruction execution in the IE and EE. The BCE controls the transfer of data between central storage and the central processor containing that BCE. Dynamic address translation is an automatic function of the BCE. Machine cycle times for the 3090 central processors are shown in Appendix B, "Summary of 3090 Model Configurations" on page B-1.

SCE

Legend:

- BCE Buffer control element

- CSE Control storage element

- EE Execution element

- IE Instruction element

- SCE System control element

#### Figure 3-2. Elements of a Central Processor

### **Instruction Element**

The instruction element (IE) controls the sequencing of all instructions. The IE performs the following operations:

- Decodes instructions

- Calculates addresses

- Sends fetch requests to the BCE (for instructions and data) in central storage

- Determines fetch priority

- Controls storage requests

- Provides the EE with:

- Operation codes

- Operands

- Operand addresses

The IE can process multiple instructions at the same time by handling the instructions in steps. As one instruction is fetched, decoded, and sent to a queue, the IE begins processing another instruction.

### **Execution Element**

1

The execution element (EE) executes instructions set up by the IE and operates in parallel with the IE. The EE performs the following operations:

- Processes instructions

- Processes interruptions

- Overlaps operations with the IE

- Initiates control functions

The EE performs the logical decisions, arithmetic functions, and many control functions of S/370, 370-XA, and ESA/370 architecture instructions. Arithmetic results provided by the EE include the following:

- Fixed point

- Fixed-point multiply

- Convert to binary

- Convert to decimal

- Floating point

- Extended-precision floating point

### **Control Storage Element**

The control storage element (CSE) is the logical element that controls microcode execution in the central processor and contains the supporting control storages and registers that are used by the central processors. The EE is primarily microcode controlled and the CSE contains the microcode that is used for controlling the EE operation.

### **Buffer Control Element**

The buffer control element (BCE) handles all central processor references to and from central storage, performs dynamic address translation, and controls the high-speed buffer.

The BCE includes:

- A 64K-byte high-speed buffer

- A buffer directory

- A translation lookaside buffer (TLB)

- Dynamic address translation (DAT) hardware

The high-speed buffer provides much faster access to data than if the data were stored in central storage. The high-speed buffer is transparent to programs that are being executed. When data is referred to during instruction execution, the high-speed buffer, the buffer directory, and the TLB are accessed for address comparison.

1441111<sup>11</sup>

The buffer directory contains the absolute addresses of central storage for data in the high-speed buffer.

The translation lookaside buffer stores the real address of the referenced page for a translated virtual address in central storage. Therefore, subsequent translations for the same virtual address are not required because the real address is immediately available in the TLB.

**Dynamic address translation** performs high-speed translation from virtual to real addresses for loading the TLB.

### **Vector Facility Feature**

The vector facility feature is optional for each central processor of the 3090 Processor Complex and is available on all 3090 models.

Central processors with the optional vector facility feature provide significantly increased levels of performance for many numerically-intensive engineering and scientific applications. The vector facility feature is an extension of the instruction and execution elements of a central processor. Some of the vector facility feature characteristics follow

- The vector facility feature performs vector arithmetic and logical operations on as many as 128 sets of operands with a single instruction.

- Arithmetic and logical units can produce a 32-bit or 64-bit sum, difference, or product each cycle.

- Compound operations can produce both a product and sum each cycle.

System/370 vector architecture provides:

- Sixty-three instructions with 171 new operation codes (104 operation codes are for floating point)

- Storage vector addressing

- Contiguous, noncontiguous, and indirect element selection

- Compound multiply-and-add instructions

- Vector results placed in vector registers

- Scalar results placed in scalar registers

- Logical, binary, short floating-point, and long floating-point operands

The vector facility feature is supported by:

- MVS/SP Versions 2 and 3, MVS/XA, VM/XA SF, VM/XA SP, and VM/SP HPO including automatic support for asymmetric configurations

- Multitasking facility (MTF) under MVS/SP Versions 2 and 3 for assignment of multiple processors to a job

- VS FORTRAN Version 2 with auto-vectoring capabilities

- APL2 Release 3: no modifications of existing APL2 application programs are required

- Engineering and Scientific Subroutine Library (ESSL): a set of high-performance mathematical routines compatible with the vector facility feature of the 3090 Processor Complex

Additional information on the vector facility feature is available in the IBM System/370 Vector Operations.

### Storage

1

1

Storage in the 3090 is implemented in monolithic and large-scale-integration technologies. The 3090 has three levels of storage: a high-speed buffer storage in each central processor, central storage, and optional expanded storage (the 3090 Model 150 is not available with expanded storage). The high-speed buffer is described under "Buffer Control Element" on page 3-6.