Technical Refere

Communications Interfaces

#### **Notice**

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

The terms and conditions governing the sale of DGC hardware products and the licensing of DGC software consist solely of those set forth in the written contracts between DGC and its customers. no representation or other affirmation of fact contained in this document including but not limited to statements regarding capacity, response-time performance, suitability for use or performance of products described herein shall be deemed to be a warranty by DGC for any purpose, or give rise to any liability of DGC whatsoever.

In no event shall DGC be liable for any incidental, indirect, special or consequential damages whatsoever (including but not limited to lost profits) arising out of or related to this document or the information contained in it, even if DGC has been advised, knew or should have known of the possibility of such damages.

CEO, DASHER, DATAPREP, ECLIPSE, ENTERPRISE, INFOS, microNOVA, NOVA, PROXI, SUPERNOVA, ECLIPSE MV/4000, ECLIPSE MV/8000, TRENDVIEW, MANAP, SWAT, GENAP, and PRESENT are U.S. registered trademarks of Data General Corporation, and AZ-TEXT, DG/L, DG/XAP, ECLIPSE MV/10000, GW/4000, GDC/1000, REV-UP, UNX/VS, XODIAC, DEFINE, SLATE, microECLIPSE, DESKTOP GENERATION, BusiPEN, BusiGEN, and BusiTEXT are U.S. trademarks of Data General Corporation.

Ordering No. 014-000769

© Data General Corporation, 1983 All Rights Reserved Printed in the United States of America Rev. 00, October 1983

# **Preface**

The technical reference manuals for Desktop Generation  $^{TM}$  computers and their peripherals are written for assembly language programmers, systems analysts, and engineers. This set of manuals, together with two companion programmer's references, contains the information you need to: 1) write assembly language software, including I/O subroutines; 2) knowledgeably expand your system; 3) learn how your system operates at the card level; and 4) design custom interfaces.

This manual discusses the functional and physical organization of the asynchronous/synchronous communications interfaces available for Desktop Generation systems.

# **Organization**

This book includes two chapters, and an index. It is organized so that portions of it can be read selectively.

- Chapter 1 discusses the functional and physical organization of the universal synchronous/asynchronous multiplexors (USAM), defines their I/O instruction sets, offers guidelines for writing assembly language I/O subroutines, and contains theory of operation.

- Chapter 2 discusses the functional and physical organization of the Model 4207 asynchronous controller card, defines its I/O instruction set, offers guidelines for writing assembly language I/O subroutines, and contains theory of operation.

A documentation comment form follows the index. It invites you to help Data General improve its publications by commenting on this book.

# **Related Manuals**

A comprehensive documentation set supports all the hardware and software products available for Desktop Generation computers. The hardware-related books listed below fall into three categories: the technical reference series; the user guides for operating, installing, and testing; and the introductory guide for Desktop Generation computers.

The following technical and programmer's references address the needs of assembly language programmers and engineers.

#### 16-bit Real Time ECLIPSE Assembly Language Programming

Global in nature, this book explains the processor-independent concepts, functions, and instruction sets of 16-bit ECLIPSE computers. DGC ordering no. 014-000688.

#### Model 10 and 10/SP Computer Systems

**Technical Reference**

In addition to the functional and physical organization of Model 10 and 10/SP computers and their technical specifications, this manual explains their processor-unique concepts, functions, and instruction set features. Also included are guidelines for programming the I/O devices, including the diskette subsystem, and explains the theory of operation for the basic components of Models 10 and 10/SP. DGC odering no. 014-000766.

#### Model 10 and 10/SP System Console

Programmer's Reference

Describes the organization and alphanumeric and graphic features of the system console. Defines the command sets and includes guidelines for programming the monochrome and optional color monitors at assembly and high-level language levels. DGC ordering no. 014-000770.

#### Model 20 and 30 Computer Systems

**Technical Reference**

In addition to the functional and physical organization of Model 20 and 30 computers and their technical specifications, this manual explains their processor-unique concepts, functions, and instruction set features. Also included are guidelines for programming the I/O devices, including the diskette subsystem, and explains the theory of operation for the basic components of Models 20 and 30. DGC ordering no. 014-000767.

#### I/O and Interfacing

Technical Reference

Introduces the microI/O bus and describes the I/O interface required to communicate with this bus and its host Desktop Generation computer. Discusses the I/O instruction set and the I/O program interrupt and data channel facilities. Includes a chapter about the 4210 general-purpose interface, useful to those designing a custom I/O interface for their system. DGC ordering no. 014-000774.

For more detailed information about the microI/O bus and Data General integrated circuits used in the I/O interface, refer to *microNOVA Integrated Circuits Data Manual DGC* ordering no. 014-000074.

#### Disk Subsystem

Technical Reference

Describes the functional and physical organization of the Model 6271 disk subsystem. Defines the I/O instruction set and provides guidelines for programming the subsystem. DGC ordering no. 014-000768.

#### Sensor I/O

Technical Reference

Defines instruction sets, offers guidelines for writing assembly language I/O subroutines, describes theory of operation at an overview level, and explains how to connect field wiring for the 4222 digital I/O interface, 4223 analog-to-digital interface, 4224 digital-to-analog interface, and 4335 analog subsystem. DGC ordering no. 014-000775.

#### **IEEE-488 Bus Interface**

**Technical Reference**

Provides the information needed to interface, program in assembly language, and troubleshoot this card in a Desktop Generation system. Reviews the contents of the IEEE-488 bus standard, summarizing its commands, messages, and states, and includes a theory of operation. DGC ordering no. 014-000773.

The following books are how-to manuals written for anyone who needs to know how to install, operate, and test a Desktop Generation system.

#### Installing Model 10 and 10/SP Systems

The first book that a Model 10 or 10/SP owner should read, explains how to unpack and install either system and its optional peripherals. Simple instructions and ample illustrations make the book accessible to any reader. DGC ordering no. 014-000901.

#### Operating Model 10 and 10/SP Systems

A logical follow-on to Model 10 and 10/SP installation, this guide takes you from powering up the system and its optional peripherals through performing such routine operations as loading paper in a printer and inserting or removing diskettes. Brings you to the point of loading the system software. Amply illustrated and written for users at any level of experience. DGC ordering no. 014-000900.

#### Testing Model 10 and 10/SP Systems

Follows the installation and operating manuals with instructions for verifying the operation of Model 10 or 10/SP systems and their optional peripherals. Steps you through the power-up test and Customer Diagnostics and explains how to troubleshoot customer-replaceable components. Simple instructions and diagrams make the book accessible to any user. Includes phone numbers for Data General assistance. DGC ordering no. 014-000902.

#### Installing Model 20 and 30 Systems

The first book a Model 20 or 30 owner should read, explains how to unpack and install either system and its optional peripherals. Accessibly written and illustrated, for users at any level of experience. DGC ordering no. 014-000904.

#### Operating Model 20 and 30 Systems

Follows Model 20 and 30 installation, leading you from powering up the system and its optional peripherals through performing such routine operations as loading paper in a printer and inserting or removing diskettes. Brings you to the point of loading the system software. The simple instructions and generous illustrations are suitable for any reader. DGC ordering no. 014-000903.

#### Testing Model 20 and 30 Systems

A follow-on to the installation and operating manuals, explains how to verify the operation of Model 20 or 30 systems and their optional peripherals. Simple instructions and diagrams lead you through the power-up test, Customer Diagnostics, and trouble-shooting of customer-replaceable components. Includes phone numbers for Data General assistance. DGC ordering no. 014-000905.

This last book is a product overview, addressed to all Desktop Generation users.

#### The Desktop Generation

Introduces the Desktop Generation, summarizing each model of the family, and describes its many hardware and software products, features, and capabilities. Includes a brief history of Data General, a sampling of applications, and an overview of the customer service and support programs available to you as a Desktop Generation user. DGC ordering no. 014-000751.

# **Conventions**

The following conventions are used throughout this manual.

MNEMONIC Uppercase sans serif letters indicate a signal name or instruction

mnemonic. When a signal is active low, it is barred—for example,

FDCHE.

argument Italicized lowercase letters mean that a particular instruction

takes an argument. In your program, you must replace this symbol

with the exact code for the argument you need.

[optional] Brackets signify an optional argument. If you decide to use this

argument, do not include the brackets in your code; they only set

off the choice.

In dialogs between system and user, we use this typeface to show your input:

**USER INPUT**

and this typeface to show the system's response:

SYSTEM RESPONSE.

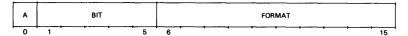

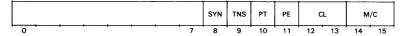

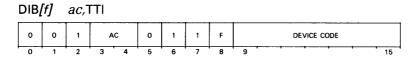

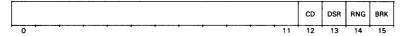

In addition, we use the following diagram to show the arrangement of the 16 bits in an instruction. The diagram is always divided into 16 boxes, numbered 0 through 15.

# **Contents**

|   | Preface                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                       |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|   | Organization Related Manuals Conventions                                                                                                                                                                                                                                                                                                                                                                                         | ii                                                                                                                                    |

| 1 | Universal Synchronous/ Asynchronous Multipl                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |

| - | Multiplexor Models Technical Specifications Programming Summary Registers Interrupts Instruction Set Specify Comm Line and Operation Write Data Read Data Read Interrupt Line Contents of the PCI Registers Programming Considerations PCI Registers with Shared Addresses Non-PCI Registers Sharing PCI Register Addresses Setting Up the Interface Controlling the Modem Transmitting Data Receiving Data Servicing Interrupts | 1-2<br>1-3<br>1-4<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10<br>1-12<br>1-13<br>1-14<br>1-19<br>1-20<br>1-21<br>1-25<br>1-26<br>1-28<br>1-28 |

|   | Reading Status Information                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                       |

|   | Timing                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                       |

|   | Power-Up Response                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                       |

|   | Electrical Interfacing                                                                                                                                                                                                                                                                                                                                                                                                           | 1-32                                                                                                                                  |

|   | Installation/Configuration      | 1-32 |

|---|---------------------------------|------|

|   | Theory of Operation             |      |

|   | I/O Bus Interface               |      |

|   | The PCIs                        |      |

|   |                                 |      |

|   | Control Circuitry and Registers |      |

|   | Interrupt Control Circuitry     |      |

|   | Block Check Circuitry           | 1-39 |

| 2 | Asynchronous Controller         |      |

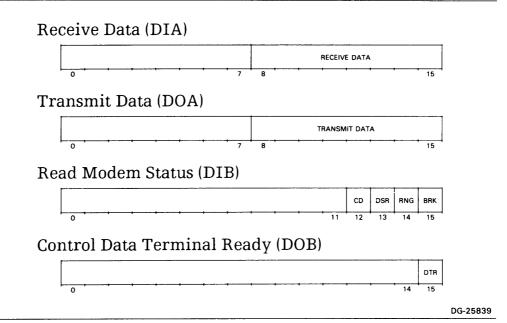

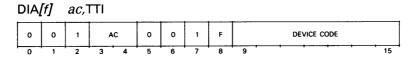

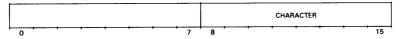

|   | Programming Summary             | 2-2  |

|   | Registers                       |      |

|   | Interrupts                      | 2-3  |

|   | Instruction Set                 | 2-4  |

|   | Read Receive Data Register      | 2-5  |

|   | Read Modem Status               |      |

|   | Transmit Character              | 2-7  |

|   | Control Data Terminal Ready     | 2-8  |

|   | Programming Considerations      | 2-8  |

|   | Transmitting                    | 2-8  |

|   | Receiving                       | 2-10 |

|   | Timing                          | 2-10 |

|   | Power-Up Response               |      |

|   | Installation and Jumpering      |      |

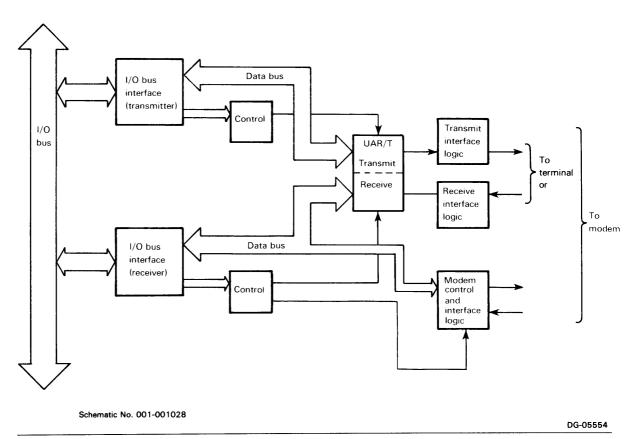

|   | Theory of Operation             |      |

|   |                                 |      |

# Universal Synchronous/ Asynchronous Multiplexor

1

The Universal Synchronous/Asynchronous Multiplexors (USAM) are a series of communications multiplexors for use in Desktop Generation  $^{TM}$  or Microproducts systems. The USAM cards operate in any I/O slot of the system's computer chassis. They are commonly used as multiterminal controllers or for network interfacing in applications where flexible communications multiplexors are required.

This chapter tells how to program the USAM cards and provides an overview of their theory of operation.

# **Multiplexor Models**

There are two basic designs available: a four-line USAM and a one-line USAM. Their model numbers are:

- 4463-Z four-line USAM (USAM-4) used in Desktop Generation systems

- 4463-ZC four-line USAM (USAM-4) used in Microproducts systems

- 4463-W one-line USAM (USAM-1) used in Desktop Generation systems

- 4463-WC one-line USAM (USAM-1) used in Microproducts systems

The 4463-Z and 4463-ZC models have two asynchronous communications lines and two lines that can be used for either synchronous or asynchronous communications. The asynchronous lines have modem control (RS-232-C) and support asynchronous byte control protocols in full-duplex operation. The two synchronous/asynchronous communications lines are program-selectable, have modem control (RS-232-C), and support both asynchronous and synchronous byte control protocols in full-duplex operation. They also include CRC error checking hardware that supports four program-selectable block check calculation modes when operating in synchronous mode.

The 4463-W and 4463-WC models are single-line, program-selectable, synchronous/asynchronous controllers. The asynchronous features are the same as those described for the USAM-4. The synchronous features are also the same except there are no hardware CRC capabilities. If CRC is required, it must be incorporated into the software.

All line interfaces are individually switch selectable for EIA RS-232-C, EIA RS-422, or 20-mA current loop characteristics for local connection. The RS-232-C interface can also feature remote connection through a modem. Other line characteristics are fully programmable, and operating speeds range from 50 to 19,200 bits per second. The asynchronous data structure may consist of 5 to 8 data bits per character; 1, 1 1/2, or 2 stop bits; and even, odd, or no parity. The synchronous data structure may consist of 5 to 8 data bits per character and even, odd, or no parity. Modem control and associated status signals are supported only on the RS-232-C interface lines.

# **Technical Specifications**

Technical specifications for the USAM series are listed in Table 1-1.

Table 1-1 USAM technical specifications

| Gen | eral | Features |

|-----|------|----------|

|     |      |          |

Physical Dimensions 7 x 9-inch PCB (approx.)

Power Requirements Volts dc Amperes +5 1.62

-5 0.10 (0.05 for USAM-1) +12 0.20 (0.05 for USAM-1) -12 0.20 (0.05 for USAM-1)

Host Interface Microl/O bus

Number of Lines USAM-4 Models USAM-1 Models

2 asynchronous; 1 synchronous/ asynchronous

2 synchronous/ asynchronous (lines 0 and 1)

Line Interfacing Switch selectable; RS-232-C, RS-422, and 20-mA current loop

Asynchronous Features

Lines

USAM-4 0 thru 3 USAM-1 0

Data Structure Program selectable; 1 start bit; 5, 6, 7, or 8 data bits

Stop Bits Program selectable; 1, 1 1/2, or 2

Data Buffering Two characters for both transmit and receive

Character Checking Parity, overrun, and framing errors

Parity Type Program selectable; Even, odd, or none

Synchronous Features

Lines

USAM-4 0 and 1 USAM-1 0

Data Structure Program selectable; 5, 6, 7, or 8 data bits

Data Buffering Two characters for both transmit and receive

Synchronization Single or double SYN operation; transparent or non- transparent

mode; automatic SYN or DLE-SYN insertion; automatic SYN or

DLE stripping;

Block Checking (USAM-4 models only)

Program selectable; CRC-16, CCITT-16, CRC-12, or LRC-8 error

checking

Character Checking Parity and overrun errors

Parity Type Program selectable; Even, odd, or none

# **Programming Summary**

Functionally, each line of the USAM operates as an independent, programmed I/O interface. Each interface is based on a programmable communications interface (PCI) integrated circuit. The PCI contains two independent devices, a transmitter and a receiver, which provide the capability for full-duplex communications between the CPU and any serial-based data terminal equipment with the following interfaces: 20-mA current loop, EIA RS-232-C, and EIA RS-422. In addition to the PCIs, the USAM-4 contains block checking circuitry that can be programmed to accumulate a separate block check sum, calculated with a separate BCP polynomial, for each synchronous interface.

The USAM-4 can generate the following types of block checksums:

- CRC-16 (cyclic redundancy checking with 8-bit character transmission codes).

- 2. CRC-12 (cyclic redundancy checking with 6-bit character transmission codes).

- 3. VRC/LRC-8 (vertical redundancy checking/longitudinal redundancy checking with 8-bit transmission codes).

- 4. CCITT-16 (cyclic redundancy checking with 8-bit transmission codes).

With the USAM-1, if a block check function is required, it must be incorporated into the software.

Table 1-2 Programming summary: USAM specifications

| Device Codes        |                                                            |

|---------------------|------------------------------------------------------------|

| Primary             | 34 <sub>8</sub>                                            |

| Secondary           | 748                                                        |

| Mnemonics           |                                                            |

| Primary             | ASLM                                                       |

| Secondary           | ASLM1                                                      |

| Priority Mask       |                                                            |

| Bit                 | 118                                                        |

| Transmission        |                                                            |

| Baud Rates          | program selectable;                                        |

| (bits/second)       | 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000,       |

|                     | 2400, 3600, 4800, 7200, 9600, 19200                        |

| Modem Control       |                                                            |

| Functions           | Carrier Detect                                             |

| (RS-232-C interface | Data Set Ready                                             |

| only)               | Ring Indicator                                             |

|                     | Clear to Send                                              |

|                     | Request to Send                                            |

|                     | Data Terminal Ready                                        |

|                     | Transmit Timing Out                                        |

|                     | Transmit Timing In Synchronous lines only                  |

|                     | Receiver Timing                                            |

| Maximum Allowable   |                                                            |

| I/O Latency         | Data structure and transmission rate dependent (Table 1-5) |

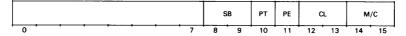

#### Read Data (DIA)

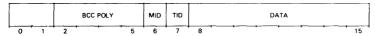

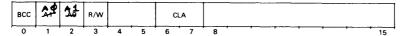

Context: Second instruction in 2-instruction sequence (DOB/DIA). BCC Accumulation Register

# PCI Register and Modem Status Register\*

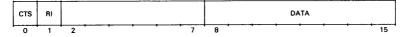

<sup>\*</sup> The modem status register contains the status of the CTS (Clear to Send) and RI (Ring Indicator) modem control lines and is addressed only when the PCI status register is addressed.

#### Write Data (DOA)

Context: Second instruction in 2-instruction sequence (DOB/DOA). BCC Accumulation Register

### PCI and Other Registers\*

<sup>\*</sup>Other registers refer to the BCC polynomial select register, addressed only when the PCI mode registers are addressed, and the interrupt disable registers, addressed only when the PCI command register is addressed.

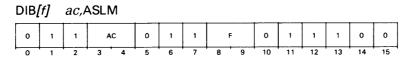

#### Read Interrupt Line (DIB)

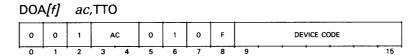

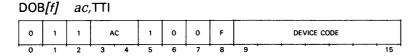

#### Specify Comm Line and Operation (DOB)

Context: First instruction in 2-instruction sequence (DOB/DIA or DOB/DOA).

|   | Bi | its |   |                                            | Bi                        | ts |        |

|---|----|-----|---|--------------------------------------------|---------------------------|----|--------|

| 0 | 1  | 2   | 3 |                                            | 6                         | 7  |        |

| 0 | 0  | 0   | 0 | Read receiver holding register.            | 0                         | 0  | Line 0 |

| 0 | 0  | 0   | 1 | Write transmitter holding register.        | 0                         | 1  | Line 1 |

| 0 | 0  | 1   | 0 | Read status register.                      | 1                         | 0  | Line 2 |

| 0 | 0  | 1   | 1 | Write SYN1/SYN2/DLE registers.             | 1                         | 1  | Line 3 |

| 0 | 1  | 0   | 0 | Read mode register 1, 2.                   |                           |    |        |

| 0 | 1  | 0   | 1 | Write mode register 1, 2.                  | Write mode register 1, 2. |    |        |

| 0 | 1  | 1   | 0 | Read command register.                     |                           |    |        |

| 0 | 1  | 1   | 1 | Write command register.                    |                           |    |        |

| 1 | X  | х   | 0 | Receiver BCC accumulation (read/write).    |                           |    |        |

| 1 | х  | Х   | 1 | Transmitter BCC accumulation (read/write). |                           |    |        |

#### Table 1-3 Programming summary: START, CLEAR, PULSE, and IORST functions

| f = S | Sets the Busy flag to 1 and the Done flag to 0. Enables interrupts when the |

|-------|-----------------------------------------------------------------------------|

|       | Interrupt Disable flag is set to 0.                                         |

f = C Sets both the Busy and Done flags to 0. Disables interrupts.

f= P Sets the Done flag to 0 and causes the last data transferred to or from the USAM to be used in an error checking calculation (USAM-4 models only).

IORST Sets the Busy and Done flags to 0 and resets the USAM by clearing all internal registers except the non-PCI modern status and interrupt line registers and the BCC accumulation register. Disables interrupts and sets the Interrupt Disable flag to 0.

## Registers

Each USAM card has two sets of program-accessible registers. One set consists of eight registers that are shared by the communications lines. The other set consists of the nine internal registers of each PCI that governs an interface.

Shared Registers The names and uses of the eight shared registers (external to the PCI) are:

- Current line address register used to select the address of the line to be affected by the DIA, DOA, and IOPLS instructions. This is a 2-bit write-only register.

- Operation address register used to determine which type of information data, control, status, error checking, or parameter - is to be passed to or from the line specified in the current line address register. This is a 4-bit write-only register.

- Interrupt line register used to hold the address of the highest-priority line requesting service. This is a 2-bit read-only register.

- Modem status register used to hold the status of the modem signals Ring Indicator and Clear to Send for each of the communications lines. This is a 4 x 2-bit read-only register.

- Transmitter interrupt disable register used to hold one interrupt disable bit for each of the four communications lines. This is a 4-bit write-only register.

- Modem change/transmitter empty interrupt disable register used to hold one interrupt disable bit for each of the four communications lines. This is a 4-bit write-only register.

- BCC polynomial select register used to determine which error checking polynomial LRC-8, CRC-12, CRC-16, or CCITT-16 is to be used to calculate a block check sum for the line. This is a 4 x 4-bit register and is write-only. (Not present on the USAM-1.)

- BCC accumulation register used to hold the 16-bit accumulated block check sum for the receiver and transmitter sections of each of the four communications lines. This is an 8 x 16-bit, read/write register. (Not present on the USAM-1.)

PCI Registers The names and primary uses of the nine 8-bit PCI registers are as follows:

- Mode register 1 used to set up the PCI for asynchronous or (lines 0 and 1) synchronous operations and to define the following line characteristics: parity, character length, number of SYN characters and transparency mode (for synchronous operation), and baud rate factor. This is a read/write register.

- Mode register 2 used to set up the PCI timing by choosing internal or external clocks for the receiver and transmitter and by choosing the baud rate. This is a read/write register.

- Command register used to enable and disable transmitter and receiver sections and to activate certain modem control functions. This is a read/write register.

- Status register used to monitor receiver and transmitter conditions and modem status. This is a read-only register.

- Transmitter (data) holding register used to hold the character supplied by the CPU in parallel form until the transmitter shift register is ready to convert the data to the specified serial bit stream and send it over the communications line. This is a write-only register.

- Receiver (data) holding register used to hold the character supplied by the receiver shift register in parallel form. The holding register latches the character and makes it available to the CPU until the next received character overwrites it. This is a read-only register.

- SYN1, SYN2, and DLE registers used to hold the synchronization and transparency mode characters defined by the program for synchronous operation. These are write-only registers (lines 0 and 1 only).

### Interrupts

The USAMs use a combination of Busy and Done logic. If the Interrupt Disable flag is set to 0, interrupts are requested when Done is set to 1. The Done flag is set to 1 if one of the following interrupt conditions occurs while the USAM Busy flag is 1:

Receiver Ready — One of the receiver data holding registers has a character ready for the CPU.

Transmitter Ready — One of the transmitter holding registers is ready to accept a character from the CPU.

Modem Status Change/Transmitter Empty — The transmitter holding register for one of the transmitters is empty, modem signal Data Set Ready or Carrier Detect has changed state, or the modem signal Ring Indicator (if enabled by switch) is asserted.

The transmitter ready and modem change/transmitter empty interrupts can be disabled by setting the appropriate bits in their respective interrupt disable registers.

**Priorities** The USAM uses the following priority scheme to resolve conflicts among sections (transmitter/receiver/modem) requesting service at the same time.

- Each line is assigned a relative priority based on its address. Line 0 has the highest priority and line 3 the lowest.

- Receiver sections have priority over any other sections.

- Modem changes and transmitters have equal priority.

The priorities are implemented by a priority encoder, which sets the system Done flag to 1 when it receives an interrupt from any section. The priority encoder will then respond to a Read Interrupt Line instruction DIB by supplying the address of the highest priority line requesting service.

### **Instruction Set**

The communications interfaces respond to four input/output (I/O) instructions. One selects the communications line and the operation to be performed for that line. After this instruction is executed, two instructions are available for the actual transfer of data between the selected register (or registers) and a specified CPU accumulator. The last instruction of the four transfers the contents of the interrupt line register to a specified CPU accumulator.

The mnemonics and device codes as well as the effects of the device flag commands and I/O Reset instruction (IORST) are defined in the programming summary.

# Specify Comm Line and Operation

DOB[f] ac,ASLM

Context: First instruction in 2-instruction sequence (DOB/DIA or DOB/DOA).

Loads the contents of the specified accumulator into the current line address register and the operation address register. The contents of the specified accumulator remain unchanged. After the data transfer, performs the function specified by f. The format of the specified accumulator is:

| Bits | Name                    | Contents or Function                                                                                                                                                                                                                                                                                            |

|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Block Check             |                                                                                                                                                                                                                                                                                                                 |

| 1    | Address 0               |                                                                                                                                                                                                                                                                                                                 |

| 2    | Address 1               |                                                                                                                                                                                                                                                                                                                 |

| 3    | Read/Write              | Bits  0 1 2 3  0 0 0 0 = Read receiver holding register  0 0 0 1 = Write transmitter holding register  0 0 1 0 = Read PCI status register and modem status register  0 0 1 1 = Write SYN1/SYN2/DLE registers  0 1 0 0 = Read mode 1/2 registers  0 1 0 1 = Write mode 1/2 registers and BCC polynomial register |

|      |                         | 0 1 1 0 = Read command register 0 1 1 = Write command register, transmitter interrupt disable register, and modem change/transmitter empty interrupt disable register                                                                                                                                           |

|      |                         | 1 X X 0 = Read or write BCC accumulation * register - receiver section 1 X X 1 = Read or write BCC accumulation * register - transmitter section                                                                                                                                                                |

| 4-5  |                         | Reserved for future use.                                                                                                                                                                                                                                                                                        |

| 6-7  | Current Line<br>Address | Bits 6 7 0 0 = Line 0 0 1 = Line 1 1 0 = Line 2 1 1 = Line 3                                                                                                                                                                                                                                                    |

| 8-15 |                         | Reserved for future use.                                                                                                                                                                                                                                                                                        |

$<sup>^*</sup>$ An X indicates that the bit can be either 0 or 1 - a "don't care" bit.

### Write Data

DOA[f] ac,ASLM

Context: Second instruction in 2-instruction sequence (DOB/DOA).

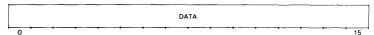

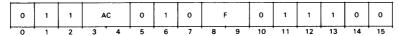

Loads the contents of the specified accumulator into the register(s) specified by the preceding Specify Line and Operation instruction (DOB). The contents of the accumulator remain unchanged. After the data transfer, performs the function specified by f. The format of the specified accumulator for the BCC accumulation register is:

| Bits | Name | Contents or Function                                                                                |

|------|------|-----------------------------------------------------------------------------------------------------|

| 0-15 | BCC  | The block check accumulation to be loaded into the BCC accumulation register for the specified line |

The format of the specified accumulator for PCI registers and shared registers is:

| Bits             | Name                                                       | Contents or Function                                                                                                                                                                                                |

|------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-1              |                                                            | Reserved for future use.                                                                                                                                                                                            |

| 2-5 <sup>1</sup> | BCC polynomial select                                      | If either PCI mode register is addressed, bits 2-5 contain the contents of the BCC polynomial register for the current line:  Bits                                                                                  |

|                  |                                                            | 2 3 4 5                                                                                                                                                                                                             |

|                  |                                                            | 0 0 0 1 = LRC-8                                                                                                                                                                                                     |

|                  |                                                            | 0  0  1  0 = CRC-12                                                                                                                                                                                                 |

|                  |                                                            | 0  1  0  0 = CRC-16                                                                                                                                                                                                 |

|                  |                                                            | 1 0 0 0 = CCITT-16                                                                                                                                                                                                  |

| 6 <sup>2</sup>   | Modem Change/<br>Transmitter<br>Empty Interrupt<br>Disable | If the PCI command register is addressed, bit 6 contains the contents of the transmitter empty interrupt disable register for the current line:  O = interrupt enabled  1 = interrupt disabled                      |

| 7 <sup>2</sup>   | Transmitter<br>Interrupt<br>Disable                        | If the PCI command register is addressed, bit 7 contains the contents of the transmitter interrupt disable register for the current line:  0 = interrupt enabled  1 = interrupt disabled                            |

| 8-15             | Data                                                       | The contents of the specified PCI register; if the specified register is the transmitter holding register, the character should be right justified and any unused bits are set to 0 (see contents of PCI Registers) |

<sup>&</sup>lt;sup>1</sup>Loaded at the same time that either PCI mode register is loaded; otherwise, these bits are reserved for future use.

NOTE If the BCC polynomial register is loaded with a combination of bits other than those listed above, the results of any BCC calculations will be indeterminate.

<sup>&</sup>lt;sup>2</sup>Loaded at the same time that the PCI command register is loaded; otherwise, these bits are reserved for future use.

# Read Data

DIA[f] ac,ASLM

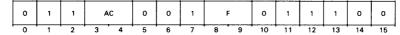

Context: Second instruction in 2-instruction sequence (DOB/DIA).

Loads the contents of the register specified by the preceding Specify Comm Line and Operation instruction (DOB) into the specified accumulator. The previous contents of the accumulator are lost. After the data transfer, performs the function specified by f. The format of the specified accumulator for the BCC accumulation register is:

| Bits | Name                | Contents or Function                                    |

|------|---------------------|---------------------------------------------------------|

| 0-15 | BCC<br>Accumulation | The contents of the specified BCC accumulation register |

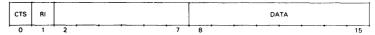

The format of the specified accumulator for the PCI registers is:

| Bits | Name           | Contents or Function                                                                                                                                                         |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-1* |                | The contents of the modem status register, if specified, for the current line:                                                                                               |

| 0*   | Clear to Send  | <ul><li>0 = Clear to Send not asserted</li><li>1 = Clear to Send asserted</li></ul>                                                                                          |

| 1*   | Ring Indicator | <ul><li>0 = Ring Indicator not asserted</li><li>1 = Ring Indicator asserted</li></ul>                                                                                        |

| 2-7  | _              | Reserved for future use All bits are set to 1                                                                                                                                |

| 8-15 | Data           | The 8-bit control word or character; if reading the receiver holding register, the character is right justified and unused bits are set to 0 (see contents of PCI registers) |

<sup>\*</sup>These bits are set to 1 if the modem status register is not specified.

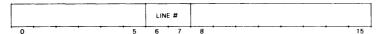

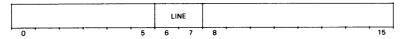

# Read Interrupt Line

Loads the 2-bit contents of the interrupt line register into the specified accumulator. The previous contents of the accumulator are lost. After the data transfer, performs the function specified by f. The format of the specified accumulator is:

| Bits | Name        | Contents or Function                                                                                               |  |  |  |

|------|-------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0-5  |             | Reserved for future use; all bits are set to 1                                                                     |  |  |  |

| 6-7  | Line number | Address of highest-priority line requesting service:  Bits 6 7 0 0 = Line 0 0 1 = Line 1 1 0 = Line 2 1 1 = Line 3 |  |  |  |

| 8-15 | _           | Reserved for future use All bits are set to 1                                                                      |  |  |  |

# Contents of the PCI Registers

A description of the contents and accumulator formats of the nine PCI registers referred to in the instruction set follows:

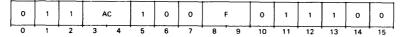

Mode Register 1 (Asynchronous Mode)

Mode Register 1 (Synchronous Mode)

| Bits  | Name                         | Contents or Function                                                                                                                                                                  |  |  |  |  |

|-------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0-7   |                              | Reserved for shared registers external to PCI                                                                                                                                         |  |  |  |  |

| 8-9   | Stop Bits (Async)            | Bits  8 9  0 0 = Invalid  0 1 = 1 stop bit  1 0 = 1 1/2 stop bits  1 1 = 2 stop bits                                                                                                  |  |  |  |  |

| 8     | Number of SYNs<br>(Sync)     | 0 = 2 SYN characters<br>1 = 1 SYN character (lines 0 and 1)                                                                                                                           |  |  |  |  |

| 9     | Transparency<br>(Sync)       | <ul><li>0 = Nontransparent mode</li><li>1 = Transparent mode</li></ul>                                                                                                                |  |  |  |  |

| 10    | Parity Type                  | 0 = Odd<br>1 = Even                                                                                                                                                                   |  |  |  |  |

| 11    | Parity Enable                | <ul><li>0 = Parity disabled</li><li>1 = Parity enabled</li></ul>                                                                                                                      |  |  |  |  |

| 12-13 | Character Length             | Bits  12   13  0   0 = 5 bits  0   1 = 6 bits  1   0 = 7 bits  1   1 = 8 bits                                                                                                         |  |  |  |  |

| 14-15 | Mode and Baud<br>Rate Factor | Bits  14    15  0    0 = Synchronous, 1x clock rate (lines 0, 1)  0    1 = Asynchronous, 1x clock rate*  1    0 = Asynchronous, 16x clock rate  1    1 = Asynchronous, 64x clock rate |  |  |  |  |

<sup>\*</sup> Baud rate factor in asynchronous mode applies only when external clocks are selected. The factor is 16x clock rate when internal clocks are selected.

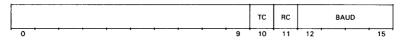

## Mode Register 2

| Bits  | Name              | Contents or Function                                                 |        |        |         |                    |  |

|-------|-------------------|----------------------------------------------------------------------|--------|--------|---------|--------------------|--|

| 0-7   |                   | Reserved for shared registers external to PCI                        |        |        |         |                    |  |

| 8-9   | _                 | Rese                                                                 | rved f | or fut | ure use | )                  |  |

| 10    | Transmitter Clock | 0 = External (lines 0 and 1 only)<br>1 = Internal (Programmable)     |        |        |         |                    |  |

| 11    | Receiver Clock    | 0 = External (lines 0 and 1 only)<br>1 = Internal (Programmable)     |        |        |         |                    |  |

| 12-15 | Baud Rate         | Programmable baud rates when bit 10 and/or bit 11 are set to 1: Bits |        |        |         |                    |  |

|       |                   | 12                                                                   | 13     | 14     | 15      | Bits/second (baud) |  |

|       |                   | 0                                                                    | 0      | 0      | 0       | 50                 |  |

|       |                   | 0                                                                    | 0      | Ö      | 1       | 75                 |  |

|       |                   | Ö                                                                    | 0      | 1      | Ó       | 110                |  |

|       |                   | 0                                                                    | 0      | 1      | 1       | 134.5              |  |

|       |                   | 0                                                                    | 1      | 0      | 0       | 150                |  |

|       |                   | 0                                                                    | 1      | 0      | 1       | 300                |  |

|       |                   | 0                                                                    | 1      | 1      | 0       | 600                |  |

|       |                   | 0                                                                    | 1      | 1      | 1       | 1200               |  |

|       |                   | 1                                                                    | 0      | 0      | 0       | 1800               |  |

|       |                   | 1                                                                    | 0      | 0      | 1       | 2000               |  |

|       |                   | 1                                                                    | 0      | 1      | 0       | 2400               |  |

|       |                   | 1                                                                    | 0      | 1      | 1       | 3600<br>4800       |  |

|       |                   | 1<br>1                                                               | 1<br>1 | 0<br>0 | 0<br>1  | 4800<br>7200       |  |

|       |                   | 1                                                                    | 1      | 1      | 0       | 9600               |  |

|       |                   | 1                                                                    | 1      | 1      | 1       | 19200              |  |

|       |                   | •                                                                    |        |        |         |                    |  |

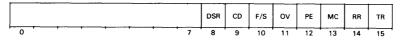

### Status Register

| Bits | Name                                 | Meaning when 1                                                                                                                                                             |

|------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-7  |                                      | Reserved for shared registers external to PCI                                                                                                                              |

| 8    | Data Set Ready                       | Data Set Ready asserted                                                                                                                                                    |

| 9    | Carrier Detect                       | Carrier Detect asserted                                                                                                                                                    |

| 10   | Framing Error<br>(Async)             | No valid stop bit detected in last character received                                                                                                                      |

| 10   | SYN Detect (Sync)                    | SYN character was received. (Lines 0 and 1 only)                                                                                                                           |

| 11   | Overrun                              | Lost data; character in receiver holding register was overwritten before it was retrieved by CPU                                                                           |

| 12   | Parity Error<br>(Async)              | Parity error detected in last character received                                                                                                                           |

| 12   | Parity Error (Sync)                  | Parity error detected in last character received (with parity enabled); or, in transparent mode (with parity disabled), a DLE character was received. (Lines 0 and 1 only) |

| 13   | Modem<br>Change/Transmitter<br>Empty | Data Set Ready or Carrier Detect changed state, and/or transmitter shift register empty                                                                                    |

| 14   | Receiver Ready                       | Receiver holding register has a character available to the program                                                                                                         |

| 15   | Transmitter Ready                    | Transmitter holding register is ready to receive a character from the program                                                                                              |

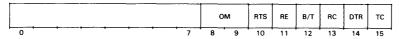

### Command Register

| Bits | Name                   | Contents or Function                                                                                                                                                  |

|------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-7  |                        | Reserved for shared registers external to PCI                                                                                                                         |

| 8-9  | Operating Mode         | Bits  8 9  0 0 = Normal operation  0 1 = Asynchronous: echo mode                                                                                                      |

| 10   | Request to Send        | 1 = Assert Request to Send                                                                                                                                            |

| 11   | Reset                  | 1 = Reset error bits in status register (framing, overrun, and parity) and DLE character detect bit                                                                   |

| 12   | Force Break<br>(Async) | <ul> <li>1 = At the end of the current character transmission,</li> <li>the transmit line is placed in the spacing state until bit</li> <li>12 is set to 0</li> </ul> |

| 12   | Transmit DLE<br>(Sync) | <ul> <li>1 = Transmit contents of DLE register prior to transmitting character in transmitter holding register. (Lines 0 and 1 only)</li> </ul>                       |

| 13   | Receive Control        | <ul><li>0 = Disable receiver</li><li>1 = Enable receiver</li></ul>                                                                                                    |

| 14   | Data Terminal<br>Ready | 1 = Assert Data Terminal Ready                                                                                                                                        |

| 15   | Transmit Control       | <ul><li>0 = Disable transmitter</li><li>1 = Enable transmitter</li></ul>                                                                                              |

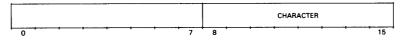

# Transmitter and Receiver Holding Registers

| Bits Name |           | Contents or Function                   |  |  |

|-----------|-----------|----------------------------------------|--|--|

| 0-7       |           | Reserved for future use                |  |  |

| 8-15      | Character | 5- to 8-bit character, right justified |  |  |

### SYN1, SYN2, DLE Registers (lines 0 and 1 only)

| Bits | Name      | Contents or Function                                                |

|------|-----------|---------------------------------------------------------------------|

| 0-7  |           | Reserved for future use                                             |

| 8-15 | Character | SYN1, SYN2, or DLE character, as applicable to appropriate register |

# **Programming Considerations**

Programming each communications interface proceeds in six steps:

- Set up the interface for asynchronous or synchronous operations;

- Manipulate and monitor the modem control lines, when applicable;

- Set up the error checking routine for synchronous operation, when applicable;

- Enable the transmitter and/or receiver and transfer data;

- Service interrupt requests;

- Monitor status conditions.

To implement these steps, the program must address the PCI registers and the shared registers external to the PCI and must transfer information between these shared registers and one or more of the CPU accumulators. Each information transfer, except reading the interrupting line number, requires two I/O instructions that are executed in sequence — Specify Comm Line and Operation (DOB) followed either by a Write Data instruction (DOA) or by a Read Data instruction (DIA).

NOTE Any number of nonrelated instructions, except for I/O reset (IORST), may be executed between the two instructions of the sequence.

The first instruction of the sequence, Specify Comm Line and Operation (DOB), loads the operation address register. This register, which is shared by the four communications interfaces, performs the following functions:

- It selects the interface 0, 1, 2, or 3;

- It addresses either the BCC accumulation register (USAM-4 only) or a particular register within the PCI of the selected interface;

- In some cases, it also addresses one or more shared registers whose contents are loaded along with the chosen PCI register;

- It prepares the registers for a read or write operation when the appropriate second instruction in the sequence is executed.

Table 1-4 lists the USAM registers and specifies their read/write capabilities. Notice in particular the following features of the registers:

- 1. Some registers are read only or write only; an instruction sequence that addresses a read-only register and specifies a write operation will result in incorrect register addressing. The second instruction in a 2-instruction sequence must move data in the direction specified by the first instruction. Otherwise, the data read or written is indeterminate.

- 2. Some registers share the same address. There are two categories of such registers; PCI registers that share the same address, and registers external to the PCI that have the same address as a PCI register.

# PCI Registers with Shared Addresses

Mode registers 1 and 2 share address 10 binary, and the SYN1, SYN2, and DLE registers share address 01 binary. These registers are addressed sequentially that is, successive transfers to the given address will result in transfers to the registers sharing that address one after another. For example, if the first instruction of a sequence specifies a mode register, then the mode register addressed is mode register 1; the next transfer to that address will reference mode register 2, the next will reference mode register 1, and so on. Similarly, the first instruction that specifies the SYN1/SYN2/DLE registers addresses the SYN1 register; the next, the SYN2 register; the next, the DLE register; the next, the SYN1 register; and so on. An I/O Reset instruction (IORST) or a read PCI command register instruction sequence resets the pointers for the mode and SYN registers - that is, it causes the first register to be addressed thereafter as the mode 1 register or the SYN1 register.

# Non-PCI Registers Sharing PCI Register Addresses

The following registers external to the PCIs share addresses with PCI registers.

- The BCC polynomial select register has the same address as the PCI mode registers.

- The modem status register has the same address as the PCI status register.

- The transmitter interrupt disable register and the modem change/transmitter empty interrupt disable registers have the same address as the PCI command register.

The nonPCI registers are loaded at the same time as the PCI registers that have the same addresses; the PCI registers are loaded by bits 8-15 of the specified accumulator and the nonPCI registers are loaded by a subset of bits 0-7.

Note in particular that the BCC polynomial select register has the same address as both mode registers. This means that the BCC polynomial select bits must be loaded with the last set of mode register bits; that is, loading the mode registers without specifying the contents of the BCC polynomial register will result in indeterminate data being passed to the BCC polynomial register.

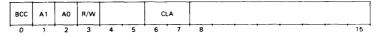

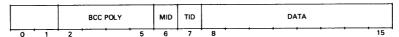

Table 1-4 USAM registers

| Register Address                                                                |     |            |    |            |                            |

|---------------------------------------------------------------------------------|-----|------------|----|------------|----------------------------|

| Register Names                                                                  | BCC | <b>A</b> 1 | A0 | Read/Write | Read / Write<br>Capability |

| Receiver holding register (PCI)                                                 | 0   | 0          | 0  | 0          | Read only                  |

| Transmitter holding register (PCI)                                              | 0   | 0          | 0  | 1          | Write only                 |

| Status register (PCI) and modem status register (nonPCI) 1                      | 0   | 0          | 1  | 0          | Read only                  |

| SYN1 register (PCI)                                                             | 0   | 0          | 1  | 1          | Write only                 |

| SYN2 register (PCI)                                                             | 0   | 0          | 1  | 1          | Write only                 |

| DLE register (PCI)                                                              | 0   | 0          | 1  | 1          | Write only                 |

| Mode register 1 (PCI)                                                           | 0   | 1          | 0  | 0/1        | Read and write             |

| Mode register 2 (PCI)                                                           | 0   | 1          | 0  | 0/1        | Read and write             |

| BCC polynomial select register (nonPCI) <sup>2</sup>                            | 0   | 1          | 0  | 0          | Write only                 |

| Command register                                                                | 0   | 1          | 1  | 0/1        | Read and write             |

| Transmitter interrupt disable register (nonPCI) <sup>3</sup>                    | 0   | 1          | 1  | 1          | Write only                 |

| Modem change/transmitter empty interrupt disable register (nonPCI) <sup>3</sup> | 0   | 1          | 1  | 1          | Write only                 |

| BCC accumulation register - receiver section <sup>4</sup>                       | 1   | x          | X  | 0          | Read/write                 |

| BCC accumulation register - transmitter section <sup>4</sup>                    | 1   | Х          | X  | 1          | Read/write                 |

<sup>&</sup>lt;sup>1</sup>The modern status register is automatically read when the PCI status register is read.

# Setting Up the Interface

Before data communications can begin, the program must define the PCI's operational mode by setting the appropriate bits in both the mode and command registers. When synchronous mode is selected, the SYN1 register, and optionally the SYN2 and DLE registers, must be loaded; the BCC polynomial and the initial BCC accumulation must be loaded if error checking is to be performed (USAM-4).

Because the interpretation of some PCI command fields depends upon the mode of operation selected, asynchronous and synchronous setup information is explained separately below.

<sup>&</sup>lt;sup>2</sup>The BCC polynomial select register is automatically written into when either PCI mode register is loaded.

<sup>&</sup>lt;sup>3</sup>The transmitter interrupt disable register is automatically written into when the PCI command register is loaded.

<sup>&</sup>lt;sup>4</sup>The read/write bit does not determine for these registers the direction of transfer; instead, this bit selects the section (transmitter or receiver). The direction of transfer is determined by the instruction issued (DOA or DIA).

NOTE To interpret the fields of the PCI registers, refer to the contents of PCI Registers section.

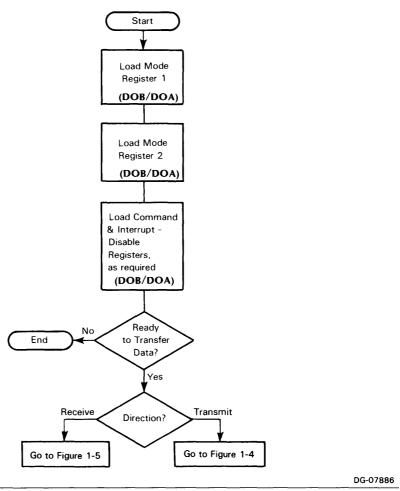

Figure 1-2 Asynchronous mode setup

### Asynchronous Mode

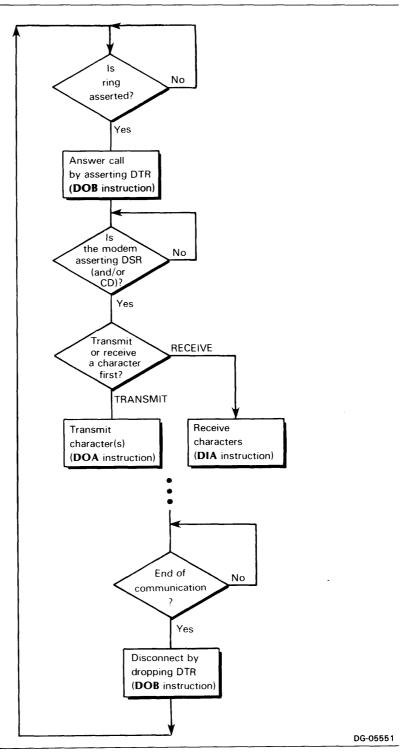

Figure 1-2 is a flowchart of events required to set up a PCI for asynchronous operations. It involves three steps:

- Load mode register 1 to select the data structure (5 to 8 data bits; 1, 1 1/2, or 2 stop bits; optional parity bit), asynchronous mode, and clock rate factor. If programmable baud rates will be used, select 16x the asynchronous clock rate.

- Load mode register 2 to select internal or external clocks. If internal clocks are selected, choose the baud rate (50 to 19,200 bits per second).

- Load the command register to select type of operation (normal, echo, local loop back, or remote loop back) and to activate the Data Terminal Ready signal, as required; and, in the same step, load the interrupt disable registers to determine whether transmitter interrupts are to be disabled and whether modem change/transmitter empty interrupts are to be disabled.

This manual assumes the use of the normal mode; that is, the transmitter and receiver operate independently while sharing the line characteristics defined by the contents of the mode registers. For information about other operating modes, refer to the Signetics data sheet for the 2661 programmable communications interface (PCI) circuit. The Signetics data sheet should also be referenced when an external clock source (e.g., modem clocks) will be used.

Notice that in the asynchronous mode the PCI automatically inserts 1 start bit at the beginning of each character bit stream.

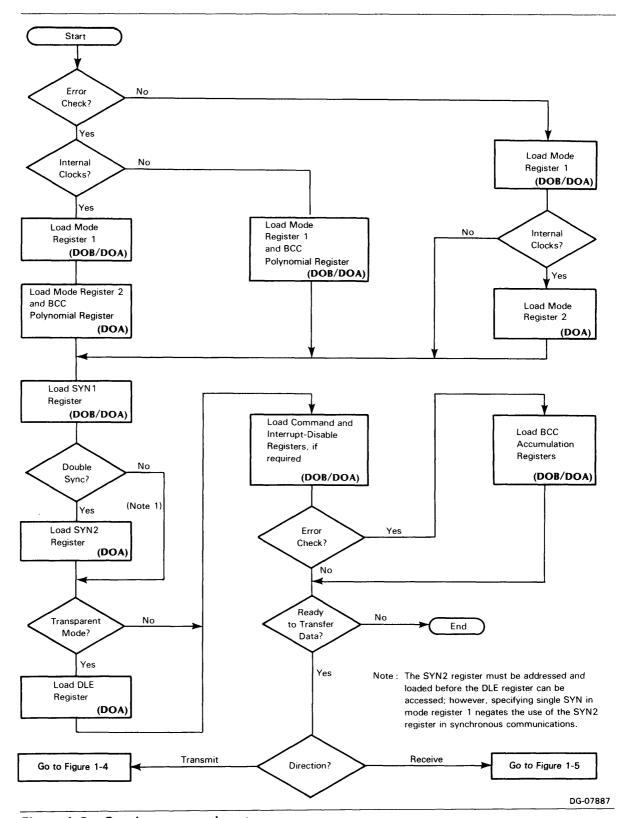

### Synchronous Mode

These steps apply only to lines 0 and 1. Figure 1-3 is a flowchart of events required to set up the PCI and the error checking logic for synchronous operations on one line. It involves four steps (five, if error checking is performed):

- Load mode register 1 to select the data structure (5 to 8 data bits and optional parity bit), synchronous mode, number of synchronization characters (1 or 2), and transparent or normal mode.

- Load mode register 2 and the BCC polynomial select register to select the internal clocks and to choose the baud rate (50 to 19,200 bits per second), and to select the BCC polynomial to be used for error checking, when used. If external clocks will be used, mode register 2 selects external clocks by default and this step can be eliminated. However, when this step is eliminated, the BCC polynomial selection must be made when mode register 1 is addressed.

- Load synchronization character register(s). Load the SYN1 register to select the first, or only, synchronization character; load the SYN2 register to select the second synchronization character, when used; load the DLE register to select the transparency mode character, when used.

- Load the command register to select type of operation (normal, automatic SYN/DLE stripping, local loop back, or remote loop back) and to activate the Data Terminal Ready signal, as required; and, in the same step, load the interrupt disable registers to determine whether transmitter interrupts are disabled and whether modem change/transmitter empty interrupts are disabled.

- Load the BCC accumulation register with the initial value of the BCC accumulation for the receiver and for the transmitter, when used.

The number of synchronization characters selected in mode register 1 has the following effect: it determines the number of synchronization characters that will be used to establish synchronization and provide character fill when transparent mode is selected. When transparent mode is selected, the same number of synchronization characters will be used to establish synchronization, but DLE-SYN1 characters will be used to provide character fill.

This manual assumes the use of either normal or automatic SYN/DLE stripping modes. For information about the other operating modes, refer to the Signetics data sheet for the 2661 programmable communications interface (PCI) circuit. The Signetics data sheet should also be referenced when an external clock source (e.g., modem clocks) will be used.

In normal mode, the transmitter and receiver operate independently while sharing the line characteristics defined by the contents of the mode registers.

Figure 1-3 Synchronous mode setup

In the automatic SYN/DLE stripping mode, the transmitter and receiver operate independently, and a character stripping function is performed by the PCI on incoming data. The character(s) stripped depends upon the selection of the number of synchronization characters and normal/transparent mode as follows:

- If single SYN and nontransparent mode are specified in mode register 1, characters received from the transmission line that match the contents of the SYN1 register are not transferred to the receiver holding register. Thus, these characters are stripped from the data stream.

- If double SYN and nontransparent mode are specified in mode register 1, characters received from the transmission line that match the contents of the SYN1 and SYN2 registers and that appear in the appropriate sequence (that is, SYN1-SYN2) are not transferred to the receiver holding register. However, only the first SYN1 character of a SYN1-SYN1 sequence is stripped. Also, SYN2 characters that are not preceded by a SYN1 character are not stripped.

- If transparent mode is specified in mode register 1, characters received from the transmission line that match the contents of the DLE register (and the SYN1 register, if immediately preceded by a DLE) are not transferred to the receiver holding register. However, only the first DLE character of a DLE-DLE sequence is stripped.

Notice that the automatic stripping mode does not affect the setting of the SYN Detect and DLE Detect bits in the PCI status register.

#### Setup Change

The operating mode of the 0 and 1 lines in the USAM can be changed at any time by the program. Before implementing a setup change, disable the transmitter and receiver of the appropriate line by setting its Transmit Control and Receiver Control bits in the command register to 0.

### Controlling the Modem

Each communications interface supports six standard EIA modem control functions: Clear to Send, Request to Send, Data Terminal Ready, Data Set Ready, Carrier Detect, and Ring Indicator. All but the Ring Indicator line are PCI related. Circuitry external to the PCI tracks the state of modem signals Clear to Send and Ring Indicator, and this circuitry can be configured (switch selected) to allow Ring Indicator to initiate interrupt requests.

The PCI uses two modem control functions — Clear to Send and Carrier Detect — as conditions for transmitting and receiving. When modem is not present, the hardware asserts them automatically.

The state of two modem control lines — Request to Send and Data Terminal Ready — are under direct program control. These lines can be activated/deactivated by manipulating the Request to Send and Data Terminal Ready bits in the PCI command register. The use of these control lines, as well as the Data Set Ready line, is modem dependent. Consult your modem manual for specific information.

### Transmitting Data

Before transmission can begin, the Clear to Send line must be asserted and the program must enable the transmitter by setting the Transmit Control bit in the command register to 1. When these conditions are present, the Transmitter Ready status bit is set to 1, which in turn sets the Done flag to 1 (if the Busy flag has been set to 1 initially). The Done condition initiates an interrupt request when interrupts are enabled.

The program responds to the interrupt by reading the interrupt line register and clearing the Done condition with a Read Interrupt Line instruction (DIBC) accompanied by a Clear command. After reading the PCI status register and determining that it was the transmitter section that caused the interrupt, it sends a character to the transmitter holding register. If a USAM-4 is being used in the synchronous mode with error checking, the program indicates at the same time (with an I/O Pulse command) whether or not the character is to be included in the error checking calculation. Sending a character to the transmitter holding register sets the Transmitter Ready bit to 0 and, if error checking was specified and a P command issued, causes the hardware to calculate a new BCC accumulation at the same time that the character is being transmitted.

As the PCI moves the character from the holding register to the transmitter shift register, the Transmitter Ready bit is set to 1 again and initiates an interrupt request (if Busy has been set to 1). If the program fails to respond to the interrupt by sending another character to the holding register before the shift register completes the previous character transmission, the Transmitter (Shift Register) Empty status bit is set to 1.

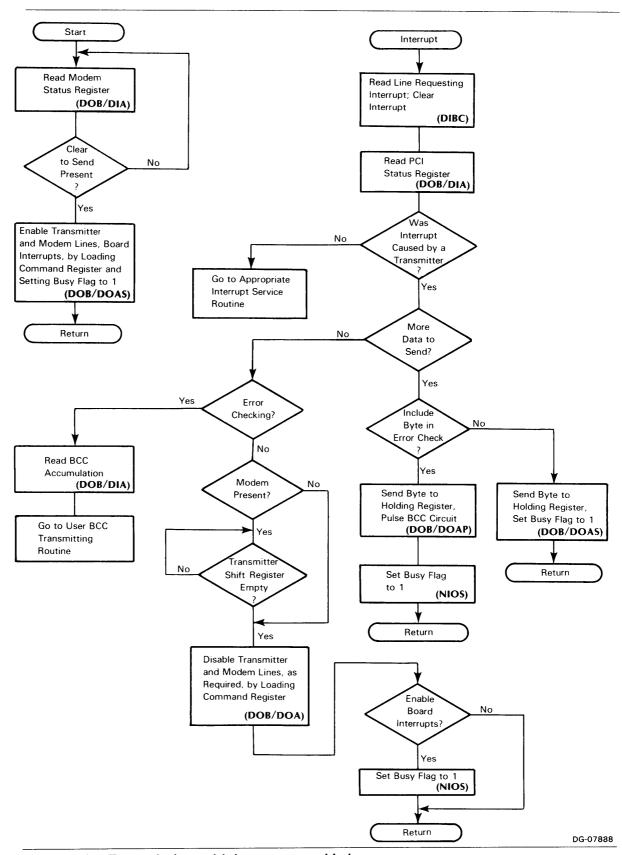

Figure 1-4 shows the sequence of events required to transmit data in both asynchronous and synchronous modes with interrupts enabled. When the interrupt facility is used, the program determines which communications line requested an interrupt by issuing a Read Line instruction. Once the line address is established, the program must issue a Specify Comm Line and Operation/Read Data instruction sequence (DOB/DIA) specifying the PCI status register to determine whether the interrupt was caused by the receiver, transmitter, or modem.

When the interrupt facility is not used, the program can check the status of a transmitter in any communications interface by issuing a DOB/DIA instruction sequence specifying the PCI status register of that interface.

When operating in synchronous mode, the PCI does not automatically transmit synchronization (or idle fill) characters until the program loads the first character into the holding register. Hence, the first character sent by the program to the transmit holding register is normally a synchronization character. After the first character is transmitted, the PCI automatically inserts the appropriate idle fill character(s) each time the transmitter is idle, that is, when the program fails to load the holding register before the current character transmission is completed by the shift register. None of these idle fill characters are included in the BCC accumulation.

After the last character in a synchronous transmission block is transmitted, the block check accumulation must be read into a CPU accumulator with a DOB/DIA instruction sequence specifying the BCC accumulation register if error checking is being performed. Then the program can transmit the 16-bit block check character one byte at a time.

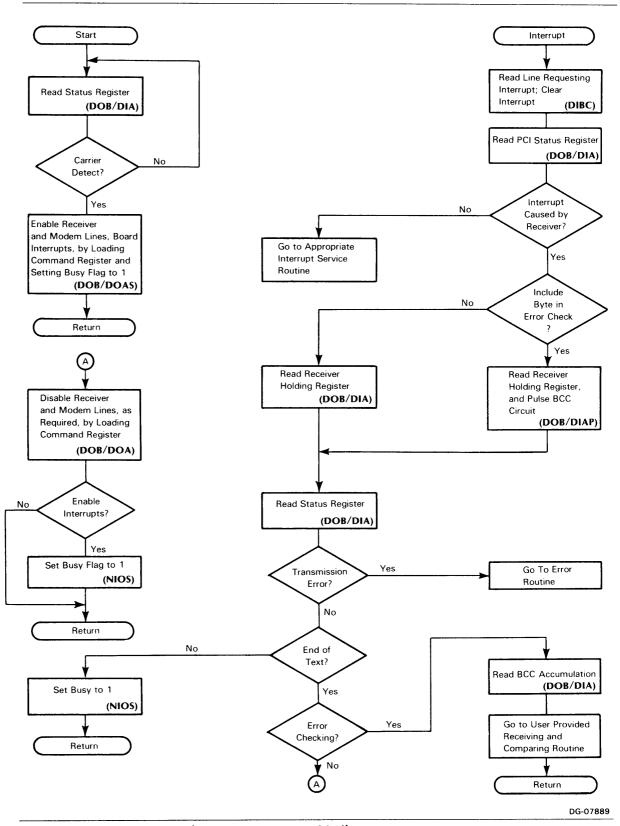

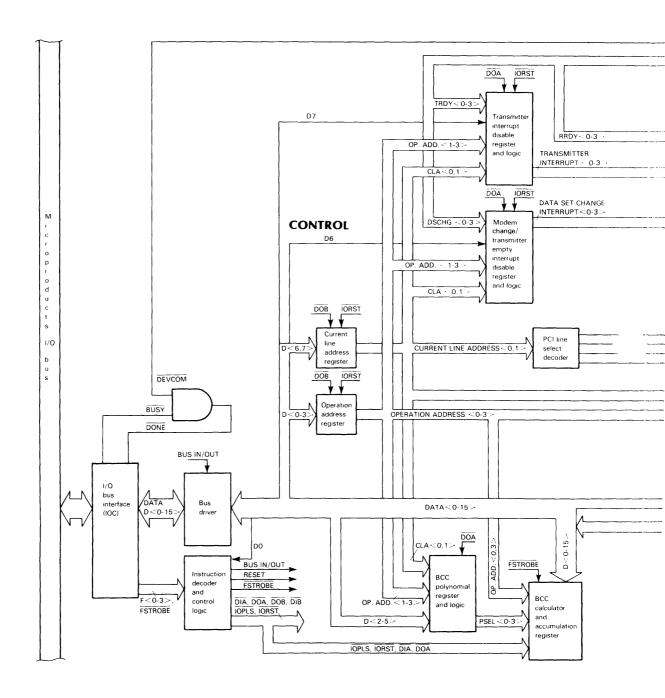

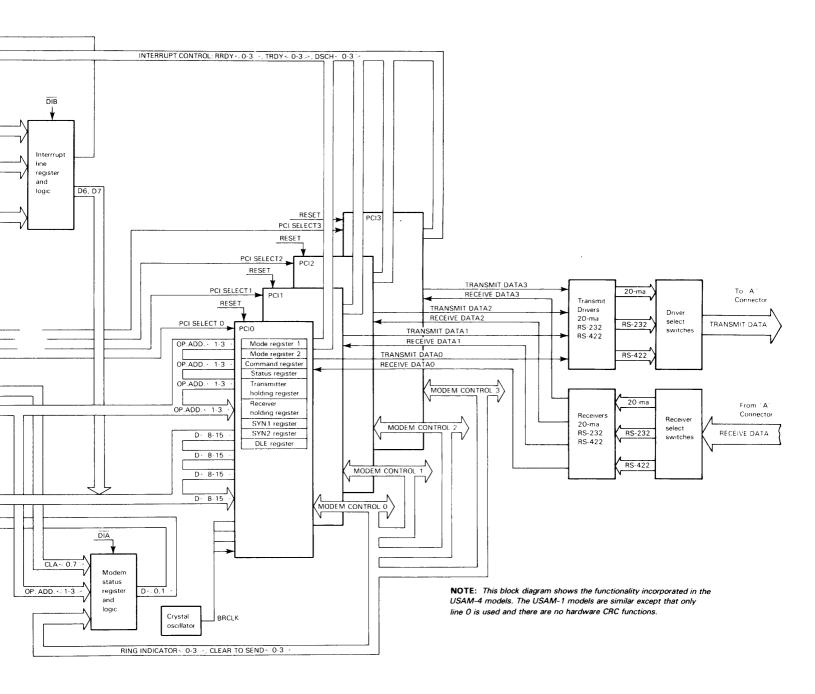

Figure 1-4 Transmit data with interrupts enabled