PUBLICATION

# understanding IC operational amplifiers

20855

by Roger Melen and Harry Garland

### Understanding IC Operational Amplifiers

#### by Roger Melen and Harry Garland

#### FIRST EDITION

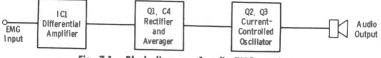

#### THIRD PRINTING-1974

Copyright © 1971 by Howard W. Sams & Co., Inc., Indianapolis, Indiana 46268. Printed in the United States of America.

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-20855-5 Library of Congress Catalog Card Number: 79-173228 Preface

Integrated-circuit technology has made possible the new, low-cost, integrated-circuit operational amplifier—"IC op amp." This book explains how IC op amps work and how they can be used in many practical circuits.

In Chapter 1, the ideal op amp is described. The following three chapters discuss the origin and implications of the nonideal characteristics found in IC op amps: Chapter 2 reviews basic semiconductor electronics; Chapter 3 explains how integrated op-amp circuitry works; and Chapter 4 discusses practical design considerations in circuits using IC op amps. In these chapters new terms such as *input offset current, output offset voltage, common-mode rejection, slew rate,* and *latch-up* are clearly defined. Many practical circuits are discussed in Chapter 5 and 6, and all component values are given. The final chapter demonstrates how circuits using IC op amps can be in-terconnected to form complete electronic systems.

In this book the explanation of how IC op amps work is developed from the fundamental concepts of semiconductor electronics. Once this information is clearly understood, these versatile devices can be used in many new and exciting applications.

No book can be written without the help of many people. We would especially like to thank Jim McVittie, Chris Riesbeck, and John Linn for their suggestions and criticisms; Yasuto Miyazawa for his grammatical advice; Margaret Hogan for her help with the drafting; and Sue Hodge for her excellent job of typing and proofreading.

> ROGER MELEN HARRY GARLAND

## Contents

#### CHAPTER 1

#### **CHAPTER 2**

#### CHAPTER 3

#### **CHAPTER 4**

#### **CHAPTER 5**

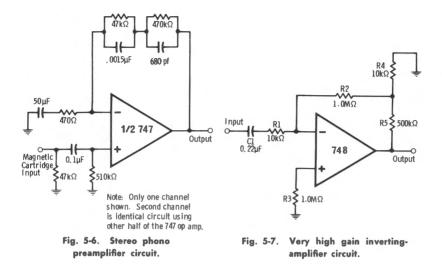

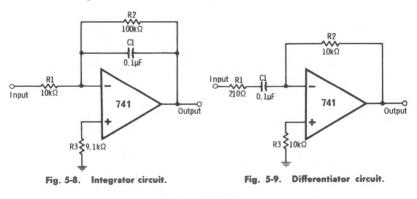

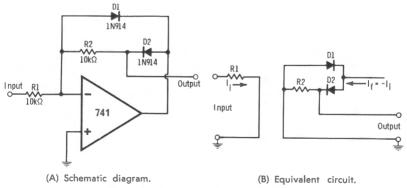

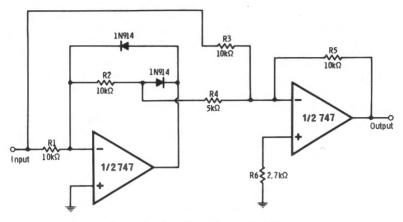

| LINEAR APPLICATIONS                                                | 72 |

|--------------------------------------------------------------------|----|

| General Design Considerations-Inverting Amplifier-Inverting Am-    |    |

| plifier With External Compensation-Summing Amplifier-Differen-     |    |

| tial Amplifier-Voltage Follower-Stereo Phono Preamplifier-Very     |    |

| High Gain Amplifier—Integrator—Differentiator—Precision Half-      |    |

| Wave Rectifier—Precision Full-Wave Rectifier—Voltage-Regulated     |    |

| Power Supply—Peak Detector—Logarithmic Amplifier—Sine-Wave         |    |

| Oscillator—Active Filters: General Considerations—Low-Pass Filters |    |

| -High-Pass Filters-Bandpass Filters-Notch Filters                  |    |

#### CHAPTER 6

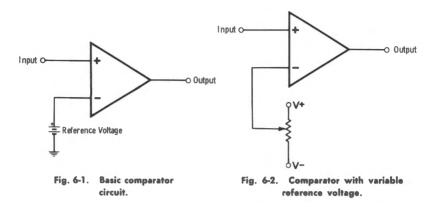

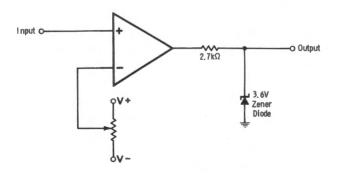

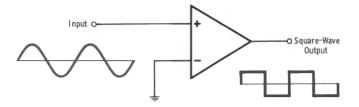

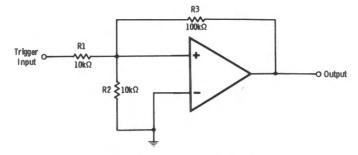

| NONLINEAR APPLICATIO  | NS                    |                     | 96 |

|-----------------------|-----------------------|---------------------|----|

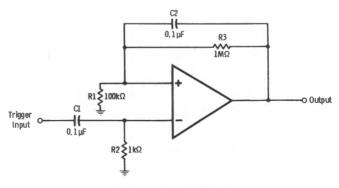

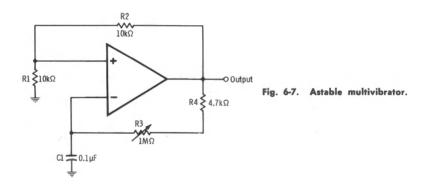

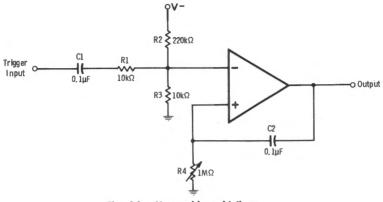

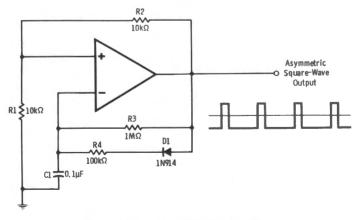

| Comparator—Bistable   | Multivibrator—Astable | Multivibrator-Mono- |    |

| stable Multivibrator- | Variations            |                     |    |

#### CHAPTER 7

| OP-AMP SYSTEMS  | 103 |

|-----------------|-----|

|                 |     |

| <b>Appendix</b> | 13  |

| GLOSSARY 1      | 125 |

| INDEX           | 127 |

#### **CHAPTER** 1

# The Ideal Op Amp

Twenty years ago operational amplifiers were heavy, costly, fragile tube amplifiers used almost exclusively in analog computers. Today an entire op amp can be fabricated on a tiny chip of silicon for less than a dollar, and these new integrated-circuit op amps have found hundreds of new uses.

In this first chapter we will consider the ideal op amp, since in many circuits IC op amps do behave ideally. Later we will consider the nonideal idiosyncrasies of IC op amps and learn how to work with these characteristics in practical circuit design.

#### **OP-AMP BASICS**

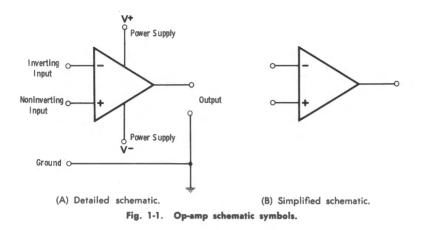

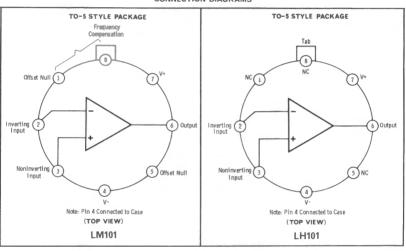

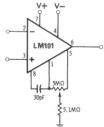

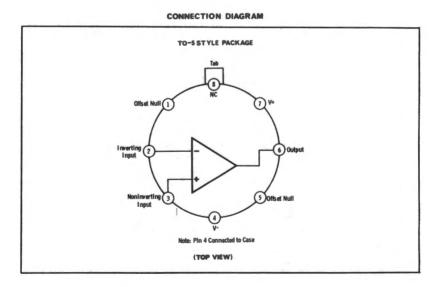

An op amp is a very high gain dc amplifier. IC op amps typically have voltage gains in the range of 20,000 to 1,000,000. The schematic symbol of an op amp is shown in Fig. 1-1A. For convenience, the power-supply connections and the ground connection are often not shown, resulting in the simplified symbol of Fig. 1-1B.

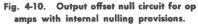

As seen in Fig. 1-1, the -input of the op amp is called the *inverting input*, and the +input is called the *noninverting* input. If an input signal is applied to the -input, with the +input grounded, the polarity of the output signal will be opposite to that of the input signal. If an input signal is applied to the +input, with the -input grounded, the polarity of the output signal will be the same as that of the input signal. For an ac signal, this means that the output of the op amp will be 180° out of phase with a signal applied to the -input.

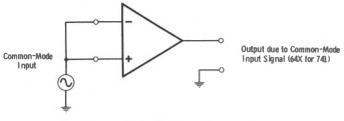

If the same signal is applied to both the +input and the -input of the op amp, the two amplified output signals will be  $180^{\circ}$  out of

phase and will completely cancel each other. Since the op amp responds only to differences between its two inputs, it is said to be a *differential amplifier*. The voltage difference between the +input and the -input is called the *differential input voltage*. Since a differential amplifier amplifies only the differential input voltage and is unaffected by signals common to both inputs, it is said to have *common-mode rejection*. Common-mode rejection can be very useful, for example, when measuring small signals in the presence of 60-Hz noise. The 60-Hz noise common to both inputs is rejected, and the op amp amplifies only the small signal difference between the two inputs.

#### **IDEAL OP AMPS WITH NEGATIVE FEEDBACK**

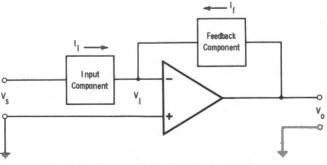

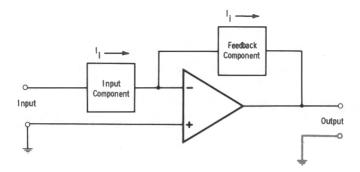

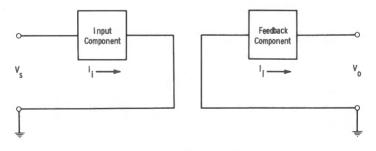

The most common op-amp circuit configuration uses two external components: (1) an input component and (2) a feedback component (Fig. 1-2). When the feedback component is between the op-amp output and the -input, the circuit is said to have *negative feedback*. When

Fig. 1-2. Op-amp circuit with negative feedback.

the feedback component is between the op-amp output and the +input, the circuit is said to have *positive feedback*.

In Fig. 1-2, an op amp is shown in a circuit with negative feedback.  $V_s$  is the input signal,  $V_i$  is the differential input to the op amp, and  $V_o$  is the op-amp output. The *open-loop gain* is defined as the ratio of  $V_o$  to  $V_i$ :

**OPEN-LOOP** GAIN

$$=\frac{V_o}{V_i}$$

The closed-loop gain is defined as the ratio of  $V_0$  to  $V_s$ :

CLOSED-LOOP GAIN

$$= \frac{V_o}{V_s}$$

The open-loop gain is the gain of the op amp, and this gain is independent of the input and feedback components. The closed-loop gain, however, depends only on the values of the input and feedback components when the closed-loop gain of the circuit is much less than the large open-loop gain of the op amp.

#### **Input Current and Feedback Current**

When an input signal  $(V_s)$  is applied to the circuit of Fig. 1-2, a current  $(I_i)$  flows through the input component, and a voltage  $(V_i)$  develops across the input terminals of the op amp. The very high gain op amp amplifies the differential input voltage  $(V_i)$  producing an output voltage  $(V_o)$  with a polarity opposite to that of  $V_i$ . This output is fed back through the feedback component and opposes the input voltage that produced it.

Because the negative feedback signal opposes the input signal,  $V_1$  is very small. The higher the gain of the op amp, the smaller is  $V_1$ . In fact, for some calculations,  $V_1$  can be assumed equal to zero and the inverting input at virtually the same potential as the noninverting input.

The relationship between the input current  $(I_i)$  and the feedback current  $(I_r)$  is most important. Assuming that  $V_i$  is equal to zero<sup>\*</sup>, it follows from Ohm's law that no current can flow into the op amp. By applying Kirchhoff's current law to the inverting-input terminal of the op amp, it can be seen that the input current must be equal and opposite to the feedback current. Extensive use will be made of this important result:

$$I_f = -I_i$$

<sup>\*</sup>If  $V_1$  were actually equal to zero, the output of the op amp would also be zero, and our op amp would be about as useful as a blown fuse. In reality,  $V_1$  is a very small voltage (usually less than a millivolt). But for the purpose of calculating input and feedback currents, very little error is introduced by approximating  $V_1$  as equal to zero.

Fig. 1-3. Negative-feedback op-amp circuit with equivalent feedback current shown.

#### The Equivalent Circuit

The schematic diagram of the op amp with negative feedback may be simplified using the above results. This simplification is called an *equivalent circuit*. The equivalent circuit may be obtained by recalling that  $I_1$  is equal and opposite to  $I_f$ , and so Fig. 1-2 can be relabeled as shown in Fig. 1-3.

Since  $V_1$  is nearly zero, the inverting input of the op amp can be considered to be at ground potential, and the schematic diagram of Fig. 1-3 is further simplified to the important equivalent circuit of Fig. 1-4.

The equivalent circuit (Fig. 1-4) suggests why op amps with negative feedback are so useful. The input circuit is electrically isolated from the output circuit, yet the current flowing through the input component dictates what current must flow through the feedback component. By choosing different input and feedback components, different circuit functions can be performed. The circuit functions listed in Table 1-1 will be discussed in this chapter, and many more examples will be given in Chapter 5.

Fig. 1-4. Equivalent circuit of Fig. 1-3.

| <b>Circuit Function</b> | Input Component | Feedback Component |

|-------------------------|-----------------|--------------------|

| Amplification           | Resistor        | Resistor           |

| Integration             | Resistor        | Capacitor          |

| Differentiation         | Capacitor       | Resistor           |

#### Table 1-1. Table of Circuit Functions

#### **NEGATIVE-FEEDBACK CIRCUITS**

Most op-amp applications are in negative-feedback circuits. To understand how these circuits work, it is helpful to analyze them in terms of the equivalent circuit of Fig. 1-4. In this section, we will look at four basic negative-feedback circuits using the ideal op amp.

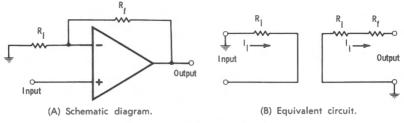

#### **The Inverting Amplifier**

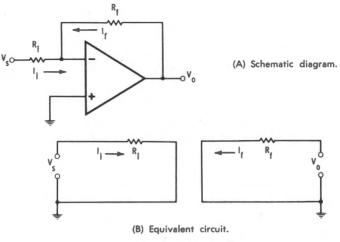

An op amp is a very high gain amplifier, but it is rare that so much gain is needed *per se*. This section will show how to use an op amp to build an amplifier with any gain we choose. For an amplifier, both the input component and the feedback component are resistors as shown in Fig. 1-5A. Fig. 1-5A can be simplified by the equivalent circuit shown in Fig. 1-5B.

The gain (G) of the amplifier circuit is given by:

$$G = \frac{V_o}{V_s}$$

So to determine the gain of the amplifier, we need only to find  $V_o$  and  $V_s$ , which are given by Ohm's law:

$$V_o = I_f R_f$$

$$V_s = I_i R_i$$

Remembering the important result that:

$$\mathbf{I}_{t} = -\mathbf{I}_{t}$$

The voltage equations become:

$$V_o = -I_i R_f$$

$$V_s = I_i R_i$$

The gain of the amplifier is then given by:

$$\mathbf{G} = \frac{\mathbf{V}_{\mathbf{o}}}{\mathbf{V}_{\mathbf{s}}} = \frac{-\mathbf{I}_{\mathbf{i}} \ \mathbf{R}_{\mathbf{f}}}{\mathbf{I}_{\mathbf{i}} \ \mathbf{R}_{\mathbf{i}}} = -\frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}_{\mathbf{i}}}$$

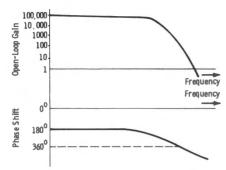

This important result states that the gain of the amplifier is equal to the feedback resistance divided by the input resistance. The minus sign indicates that the output is  $180^{\circ}$  out of phase with the input, and

Fig. 1-5. Inverting amplifier.

for this reason the circuit is called an *inverting amplifier*. It can be seen from the equivalent circuit (Fig. 1-5B) that the input impedance of the amplifier is just equal to the input resistance  $R_i$ . The output impedance of this circuit is zero since the output voltage is determined by the feedback current which, for the ideal op amp, is not affected by the load.

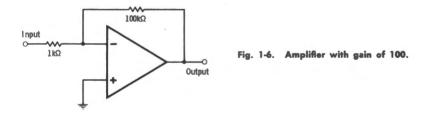

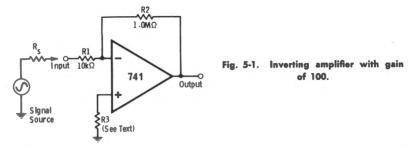

Now let us see how easy it is to design an amplifier stage using an op amp with feedback. For example, suppose we want to build an amplifier with an input impedance of 1000 ohms and a gain of 100. It takes just three components: (1) an op amp, (2) a 1000-ohm input resistor, and (3) a 100,000-ohm feedback resistor. This circuit is shown in Fig. 1-6.

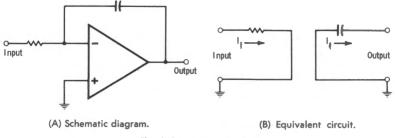

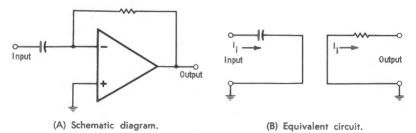

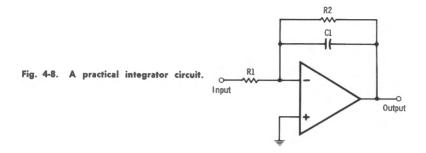

#### Integrators

An *integrator* is a circuit that "integrates," or takes the sum of, the input signal over a period of time. For an integrator, the input component is a resistor, and the feedback component is a capacitor, as seen

Fig. 1-7. Integrator circuit.

in Fig. 1-7A. The equivalent circuit in Fig. 1-7B shows that the charging current of the capacitor is equal to the current flowing in the input resistor, and that the output voltage is equal to the voltage across the capacitor. The output of the op-amp integrator is proportional to the negative of the integral of the input.

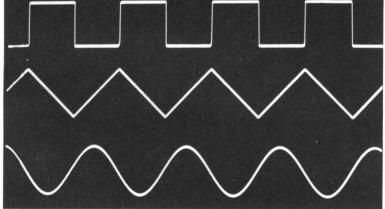

When a constant voltage is applied to the input of the integrator, a constant capacitor-charging current will flow, and the voltage across the capacitor will increase linearly. The capacitor is "integrating" or "adding up" the input voltage. So, for example, when the input to the integrator is a square wave, the output is a triangular wave. The op-amp integrator is most commonly used in analog computers.

#### Differentiators

A *differentiator* is a circuit that responds only to differences, or changes, in the input signal. The input component is a capacitor, and the feedback component is a resistor, as shown in Fig. 1-8A.

The operation of the differentiator can be seen from the equivalent circuit (Fig. 1-8B). A capacitor will not pass direct current. Only changes in the input signal will result in current flow through the input capacitor, and so only changes in the input signal will result in current flow through the feedback resistor. The output of the differentiator is equal to the voltage drop across the feedback resistor and is proportional to the negative of the derivative of the input.

Fig. 1-8. Differentiator circuit.

Fig. 1-9. Noninverting amplifier.

A differentiator always does the exact opposite of an integrator. When the input to a differentiator is a triangle wave, the output is a square wave. When the input to a differentiator is a square wave, the output is a series of voltage spikes corresponding to the square-wave voltage changes. The op-amp differentiator is useful in instrumentation for determining the rate of change of voltage variables.

#### **Noninverting Amplifier**

A noninverting amplifier is an amplifier for which the output signal is in phase with the input signal. By simply applying the input signal to the +input of the op amp, the inverting amplifier described earlier becomes a noninverting amplifier. A schematic is shown in Fig. 1-9A.

Since the output signal is referenced to the grounded end of  $R_i$ , the voltage drop across  $R_i$  is in series with the output. So in the equivalent circuit (Fig. 1-9B),  $R_i$  and  $R_f$  are shown in series in the output circuit. The calculation of the gain of the noninverting amplifier is straightforward:

$$G = \frac{V_{o}}{V_{s}} = \frac{I_{i} (R_{i} + R_{f})}{I_{i} R_{i}} = \frac{R_{i} + R_{f}}{R_{i}}$$

The gain of the noninverting amplifier is equal to the sum of the input and feedback resistances, divided by the input resistance.

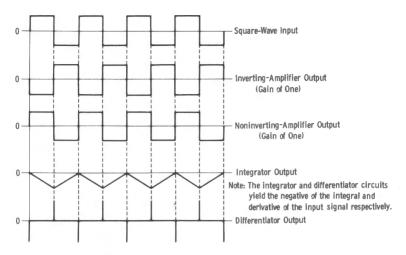

#### Summary

Four circuits have been described to illustrate the use of ideal op amps with negative feedback. A summary of the output waveforms of these circuits for a square-wave input is given in Fig. 1-10. In these four examples it can be seen that the analysis of op-amp circuits with negative feedback can be greatly simplified by using the equivalent circuit of Fig. 1-4.

#### NONIDEAL CHARACTERISTICS

IC op amps, like all real op amps, do have some nonideal characteristics. Often these nonideal characteristics have a negligible effect

Fig. 1-10. Summary of output waveforms for a square-wave input.

on circuit performance, and the IC op amps behave ideally. Sometimes these nonideal characteristics have a profound effect on circuit performance, however, and cause the unwary circuit designer unnecessary consternation and confusion.

Fortunately, once the nonideal characteristics of IC op amps are understood, it is easy to design circuits that are not adversely affected by these characteristics. The purpose of the next three chapters is to explain how an IC op amp works and just exactly what these nonideal characteristics are.

#### CHAPTER 2

# **IC Electronics**

An elementary knowledge of IC electronics is essential to a thorough understanding of IC op amps. This chapter is an introduction to the fundamentals of IC electronics—semiconductor physics, semiconductor devices, and integrated-circuit technology.

#### SEMICONDUCTOR PHYSICS

A semiconductor is a crystalline material with specific electrical properties. Silicon and germanium are the most popular semiconductors in use today. All integrated circuits presently being built use silicon.

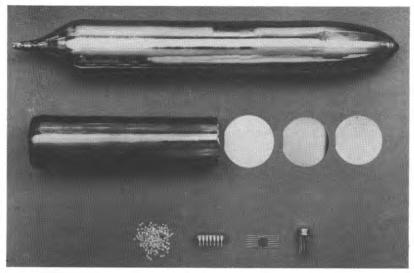

Figure 2-1 shows a silicon ingot which has been grown for use in integrated circuits. These ingots are usually several inches in diameter and several feet long. The ingots are sliced, like bologna, into wafers about 0.01-inch thick. These silicon wafers are used as the starting material in the IC fabrication process.

#### **Semiconductor Conduction**

Metals provide a very simple illustration of the process of electrical conduction. When a voltage is applied across a metal, a "sea of electrons" drifts in response. Even though high currents may flow in a metal, the average velocity of the electrons is slow (typically less than  $\frac{1}{2}$ -inch per second) because of the large number of electrons participating in the conduction. While the "sea-of-electrons" idea provides a clear picture of conduction in metals, it needs modification before it can be extended to semiconductors. Just as in metals, though, electrons are the only type of charge that contributes to semiconductor conduction.

Courtesy Fairchild Semiconductor

Fig. 2-1. The monolithic fabrication process from silicon ingot to packaged IC.

Electrons in semiconductors have certain specific energies. The allowed energies are grouped, and these groups of energy levels are called *energy bands*, or just *bands*. In nature, systems tend to exist in the lowest energy state. Consequently, electrons tend to occupy mostly the lower energy bands. The two highest energy bands containing elec-

Fig. 2-2. Semiconductor energy levels.

trons are called the *valence band* and the *conduction band* (Fig. 2-2), and it is these bands that are important to conduction in semiconductors.

The conduction band is the higher of these two bands. It is only slightly filled. The electrons in this energy band act quite similarly to electrons in a metal during conduction. When a voltage is applied across a semiconductor, these electrons drift in response, similar to the sea of electrons. The current identified with the flow of electrons in this band is called *electron current*, and the *carriers*, or type of charge said to be "carrying" the current, are electrons.

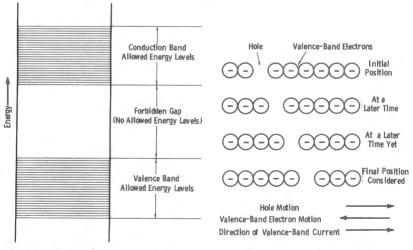

The valence band is just below the conduction band. The energy levels in this band are mostly filled. There are very few vacant energy levels available. It has been shown with quantum mechanics that these vacancies (or *holes*) behave very much like the electrons in the conduction band, except that they act as though they are positively charged. This can be seen more clearly by looking at conduction in the valence band, called *hole conduction*. When a voltage is applied across a semiconductor, electrons in the valence band jump into nearby vacancies, leaving a vacancy at the energy level from which they came. As seen in Fig. 2-3, the electrons are moving toward the left, but from another point of view, the vacancy, or hole, has moved toward the right. Thus, conduction in the valence band can be considered in terms of holes moving in the direction opposite to the electrons in the band.

In summary, when a voltage is placed across a semiconductor, there are two forms of current: (1) current due to electrons in the conduction band, and (2) current due to holes in the valence band. Unless otherwise noted, the term *electrons* will be used to describe only the current carriers in the conduction band, and the conduction-band current will be referred to as *electron current*. Similarly, the term *holes* will be used to describe current carriers in the valence band, and the valence band, and the valence band current will be referred to as *hole current*.

#### N-Type and P-Type Semiconductors

The concentration of electrons and holes in a semiconductor can be controlled. Two classes of impurity atoms are used to control the number of electrons and holes in semiconductors: (1) *donors* and (2) *acceptors*. Donor atoms have excess electrons which they are willing to "donate" when placed in a semiconductor. Acceptor atoms are the opposite of donors in that they "accept" electrons from the valence band when placed in a semiconductor. Most donors increase the number of electrons by one for every donor atom, and most acceptors increase the number of holes by one for every acceptor atom. By *selective doping* (injecting impurity atoms into a semiconductor), it is possible to have a large number of holes in one area of a piece of semiconductor material and a large number of electrons in another. A large number of both holes and electrons cannot exist in the same area in a semiconductor, and if the number of holes in a certain area is increased tenfold by doping, the number of electrons in this area will be decreased by tenfold. An area of semiconductor material with more electrons than holes is called *n*-type, and an area with more holes than electrons is called *p*-type.

Both n-type and p-type semiconductors can be fabricated on the same semiconductor wafer by selective doping. In fact, a p-type semiconductor can be changed to an n-type by *counterdoping* acceptor-doped material with a greater number of donor atoms. Counterdoping can likewise be used to change n-type material to p-type material.

#### **Semiconductor Doping**

Semiconductors are typically doped at two different times during IC fabrication. During the growth of the semiconductor crystals, a *dopant* is added to make the entire crystal n-type or p-type. After the crystal is sliced into wafers, it may be doped by a process called *diffusion*.

Diffusion is simply the migration of atoms from an area of high concentration to an area of low concentration. Many people have observed atomic diffusion when smelling perfume across the room from its source. The diffusion-doping process is carried out by passing a dopant-rich gas over the surface of a semiconductor wafer that has been heated to about 2000°F. The dopant atoms are absorbed on the surface of the semiconductor and diffuse deep into the semiconductor.

#### SEMICONDUCTOR DEVICES

#### The Diode

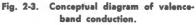

The diode is the simplest integrated-circuit structure. It consists of an n-type doped-semiconductor area adjacent to a p-type dopedsemiconductor area, as shown in Fig. 2-4A. The diode V-I (voltagecurrent) characteristic curve and schematic symbol are also shown in Fig. 2-4. A diode may be fabricated by counterdoping part of an n-type silicon wafer to be p-type through a diffusion process.

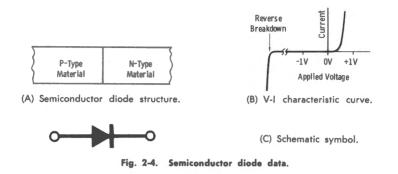

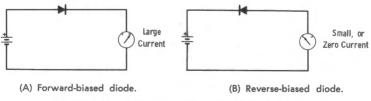

A diode ideally passes current in only one direction, as shown diagrammatically in Fig. 2-5. In order to understand how this diode action occurs in a semiconductor, it is first necessary to understand a balance that goes on in semiconductors.

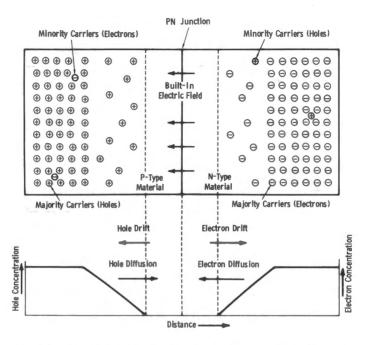

This balance exists between the two types of current that can exist in a semiconductor: (1) *drift current* and (2) *diffusion current*. Drift current is caused by the flow of carriers in an electric field.

Diffusion current is caused by the migration (or diffusion) of carriers from an area of high carrier concentration to an area of lower concentration of the same type of carrier. Carrier diffusion is similar to the atomic diffusion of impurity atoms discussed previously; however, there is a major difference between these two types of diffusion: Carriers at room temperature diffuse readily, whereas dopant atoms at room temperature diffuse at a rate which, for all practical purposes, is zero. This is fortunate, since it is undesirable to have the dopant atoms move once they are initially placed.

When there is a difference in hole concentration between two adjacent areas in a semiconductor, a diffusion current will flow from the area of high hole concentration to the area of low hole concentration. Since the holes are diffusing from an electrically neutral area, an electric field is created between the holes that have diffused and the negatively charged area they created in leaving. This electric field causes a drift current to flow, as shown in Fig. 2-6. At equilibrium, the diffusion current is equal and opposite to the drift current, and there is no net current flow.

The balance between drift and diffusion current is very important at the junction between the p-type and the n-type material in a semiconductor diode. On the p-type side of the junction there are a large number of holes, while on the n-type side there are few. Thus, there is a balance between drift and diffusion currents for both the electrons and the holes. The amount of diffusion current that would flow, if it

Fig. 2-6. Pictorial drawing of semiconductor diode, and plot of majoritycarrier concentration.

were not restrained by the electric field, would be several thousand amperes for a typical diode. Yet in a silicon diode, this current is restrained by the electric field, which is only 600 millivolts (0.6 volt). Note that electrons and holes are trying to diffuse in opposite directions across the junction, yet due to their being oppositely charged, the same polarity of electric field restrains both types of carriers.

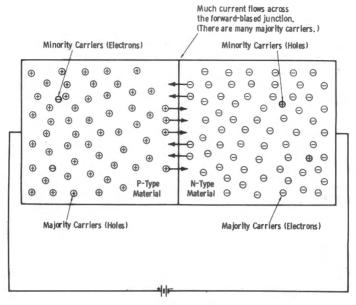

The diode action of a semiconductor junction may now be understood in terms of the drift/diffusion balance. In the conduction, or forward-biased direction, (Fig. 2-7A), the voltage applied from a circuit to the diode decreases the built-in electric field, releasing part of the potentially large diffusion current. For a silicon diode, several thousand amperes of diffusion current would flow if 600 millivolts were applied across the junction. This is nearly impossible to do in practice, because a very high voltage would have to be applied to the leads of the diode in order to overcome the resistive voltage drop in the semiconductor material as the current flows to and from the junction. The diode would probably overheat long before this current could be achieved.

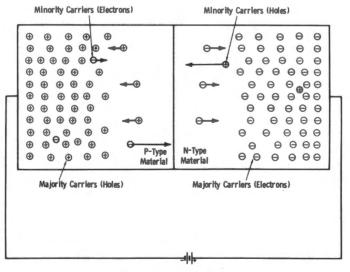

In the nonconducting, or reverse-biased direction (Fig. 2-7B), the applied voltage acts to upset the balance between drift and diffusion

(A) Forward-biased diode.

Little current can flow across the junction. (There are few minority carriers on either side of the junction, )

(B) Reverse-biased diode.

Fig. 2-7. Pictorial representation of diode action.

currents in favor of the drift current. The current flowing in this direction is limited by the diffusion of the minority carriers, on either side of the junction. Upon diffusing to the junction, the minority carriers are swept across by the bias-aided electric field. These few minority carriers drifting across the junction constitute an imbalance between drift and diffusion currents at the junction. This small reverse current is not dependent on reverse-bias voltage, because it is limited by the rate of diffusion of minority carriers to the junction.

If the reverse-bias voltage is large, the diode will undergo reverse breakdown. Reverse breakdown is the phenomenon which causes a large increase in reverse current corresponding to a small increase in reverse bias above the breakdown, or zener, voltage of the diode (Fig. 2-4B). (Zener diodes are ordinary pn-junction diodes that have been designed and sorted for their reverse-breakdown characteristics.) When a diode breaks down, the reverse current must be limited in order to prevent excessive power dissipation by the diode. If the power is limited to the designed dissipation of the diode and package (typically  $\frac{1}{4}$  to  $\frac{1}{2}$  watt), the reverse breakdown of the diode will be nondestructive. If the power is not limited, the diode will overheat and be permanently damaged.

Although it is often called *zener breakdown*, reverse breakdown in a diode actually may be due to either zener breakdown or *avalanche multiplication*. Zener breakdown occurs in a diode when an area near the junction, which has been swept free of carriers, has a large enough electric field to "rip" electrons and holes from the atoms in that area. These electrons and holes are the carriers of the large reverse current resulting from zener breakdown.

With an electric field less than that required for zener breakdown, avalanche multiplication can occur. Avalanche multiplication is the effect which causes an increase in the reverse current by the collision of the carriers constituting the reverse current (which are accelerated by the large electric field near the junction) with the crystal lattice near the junction. These collisions "knock loose" hole-electron pairs from the silicon atoms which, depending on the location of the original collision, may be accelerated to cause more carrier-generating collisions. It is the electrons and holes knocked off by collisions that constitute carriers of the large reverse current due to avalanche breakdown.

It is interesting to note that the variation of the breakdown voltage with temperature is in a different direction for the two effects. Since zener breakdown usually occurs with silicon diodes that break down at less than 6 volts, while avalanche breakdown occurs with silicon diodes that break down at 6 volts or more, a diode with approximately a 6-volt breakdown may be used as a stable voltage reference that has little variation with temperature.

To summarize, silicon diodes conduct large currents in the forward-

Fig. 2-8. Transistor data.

biased direction with roughly 600 millivolts applied to them. In the reverse-biased direction, only a little current flows, unless the bias is large enough to cause reverse breakdown. Reverse breakdown will not harm a diode as long as the power dissipated in the diode is limited to the designed level.

#### The Transistor

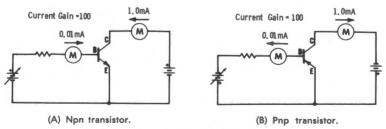

The transistor is a semiconductor device that can be used to proportionally control large currents with small currents. There are two

basic types of transistors: (1) the npn transistor and (2) the pnp transistor. Figure 2-8 shows the schematic symbol and semiconductor structure for each type of transistor.

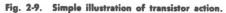

The operation of a transistor with a current gain  $(\beta)$  of 100 is shown in Fig. 2-9 for both types of transistors. It can be seen from Fig. 2-9 that the current allowed to flow into the collector is 100 times that put into the base.

From the structure of the transistor, it becomes apparent that the transistor actually is two closely spaced diodes arranged "back-to-back." The transistor can be explained in terms of a coupling between the forward-biased, emitter-base diode, and the reverse-biased, base-collector diode. A little further understanding of how diodes work beyond that given in the previous section is necessary before *transistor action* (the coupling between the diodes) can be fully understood.

In a forward-biased junction, the majority carriers on both sides of the junction diffuse across the junction. Once across the junction, these carriers may be considered minority carriers. Thus, holes diffuse across the junction from the p-type side to the n-type side to join the holes on the n-type side. For small forward currents, called the low-level injection case, the hole concentration on the n-type side of the forward-biased junction will remain much less than the electron concentration. This increase in the number of minority carriers on both sides of the junction disturbs the proportion of electrons and holes set by the doping. It is because of this imbalance that electrons on the n-type side tend to leave the conduction band and fill up the excess holes as the holes diffuse away from the junction they just crossed. It is generally true that whenever the proportioning of holes and electrons is altered from that set by the doping, the semiconductor will act in the direction to restore the proper proportioning. The process of an electron leaving the conduction band to go to the valence band, or vice versa, is called recombination. Excess electrons on the p-type side of this forward-biased junction also recombine. The length of time it takes before these excess minority carriers recombine is called the *minority carrier lifetime*.

By heavily doping the n-type side of the junction, and lightly doping the p-type side, it is possible to have the electron diffusion current across the junction be much greater than the hole diffusion current across the junction. The operation of this n+p junction ("+" refers to high doping density, not charge) could be considered as only having electrons *injected* into the p-type side, neglecting the small hole current diffusing across the junction.

The operation of an npn transistor can be easily understood if the n+pn transistor shown in Fig. 2-10 is considered. The forward biased n+p diode injects electrons into the p-type side, called the base of the npn transistor. If the lifetime of the electrons is long enough (i.e.,

Fig. 2-10. Operation of the n + pn transistor.

they do not have time to recombine), the electrons diffuse across the base to the other junction, which is reverse biased. These electrons that have diffused across the base are swept across the reverse-biased, base-collector junction into the collector, where they are once again majority carriers.

There are two components of the base-emitter current that must be supplied in order to allow the collector-emitter current to flow: (1) the small hole current which diffuses across the forward-biased base-emitter junction, and (2) the current which recombines with the electrons that did not have sufficient lifetime to diffuse all the way across the base. Both of these currents are small. For a high- $\beta$ transistor, the base-emitter current can typically be 1/500 that of the collector-emitter current.

#### **Other Types of Transistors**

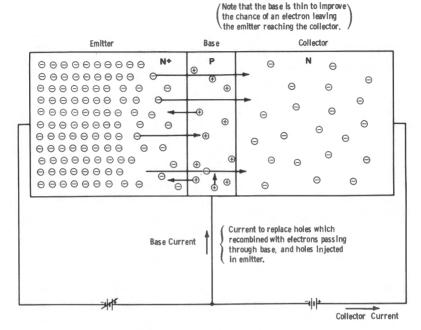

What is commonly called a transistor (or *bipolar* transistor) is not the only type of transistor. *Unipolar*, or *field-effect* transistors (*FETs*) constitute the remainder of devices that are currently called transistors.

There are two basic types of field-effect transistors: (1) junction field-effect transistors (JFETs) and (2) metal-oxide semiconductor field-effect transistors (MOSFETs). Both of these devices have a

Fig. 2-11. Simple illustration of JFET operation.

source-drain resistance that is controlled by a gate-source voltage (Fig. 2-11B). This is in contrast to the bipolar transistor, which has the collector-emitter current controlled by the base-emitter current.

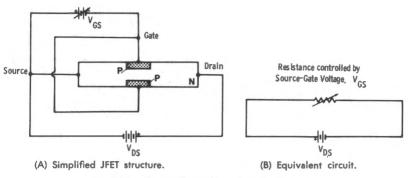

In the JFET shown in Fig. 2-11A, a reverse bias is applied between the gate and the source. The reverse bias creates an area around the junction that is swept free of carriers. The carrier-free area increases with increasing reverse bias. Only the section of the channel that has carriers participates in conduction. Thus, increasing the reverse bias increases the source-drain resistance by narrowing the effective channel width. Applying a voltage across the source-drain resistance further reverse biases the gate-channel junction, narrowing even more the portion of the channel with carriers. If a sufficiently large source-drain voltage is applied, the increasing source-drain resistance prevents a further increase in the source-drain current as the source-drain voltage is increased. The V-I characteristic curves for the JFET (Fig. 2-12) are similar to a pentode vacuum tube.

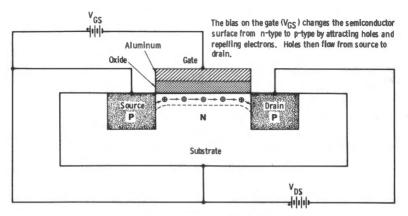

The MOSFET is quite similar to the JFET. Biasing the aluminum gate of the MOSFET negatively (Fig. 2-13) will attract holes to the surface of the silicon and repel electrons away from the surface. By heavily biasing the gate, more holes than electrons will be at the surface, effectively changing the doping from n-type to p-type. This

Fig. 2-12. Typical JFET characteristic curves.

Fig. 2-13. Simple illustration of MOSFET operation.

changed (or *inverted*) area provides a resistive conduction path between the source and drain. The depth of the channel, hence the source-drain resistance, is dependent on the gate-source bias.

Note that in both types of FET devices, virtually no current is required to control the source-drain resistance. Since the input and output impedances of these devices are both very high, field-effect transistors are sometimes used in the input stage and in current-source applications in operational amplifiers. Due to their relatively low transconductance, poor compatibility with conventional integrated-circuit processing, and low current-delivering capability, however, they are not used frequently.

#### THE MONOLITHIC FABRICATION PROCESS

This section explains how integrated circuits containing diodes and transistors are built. The IC fabrication process is called *monolithic* because the integrated circuit is fabricated on a single piece of silicon.

#### **The Process**

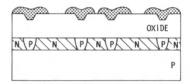

A typical monolithic fabrication starts with a p-type silicon wafer with a thin n-type layer on top, as shown in Fig. 2-14A. The p-type bulk is called the *substrate*, and the thin n-type layer is called an *epitaxial layer*. The doping atoms used in both these areas are chosen for their slow atomic-diffusion rates, even at high temperatures, so that the dopant atoms may be assumed not to move with subsequent processing.

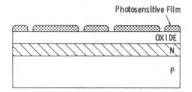

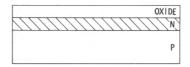

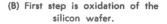

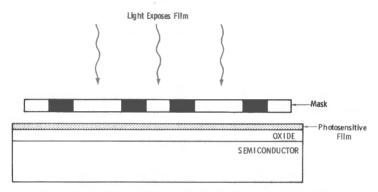

The first processing step (Fig. 2-14B) is the oxidation of the silicon wafer by heating it in a high-temperature furnace and simultaneously passing oxygen across the surface of the semiconductor. The oxidized wafer is then covered with a photographic film (which is applied in

(A) Monolithic fabrication starting material.

(C) A photosensitive film is applied, exposed, and developed on the oxide surface (using a mask to determine the pattern).

(E) Impurity atoms are diffused into the epitaxial layer through windows in the oxide.

(G) Oxide is etched through windows in the film, and p-type impurity atoms are diffused into the epitaxial layer through the windows in the oxide.

(I) An aluminum film is evaporated everywhere on the surface and selectively removed to create contacts to the semiconductor areas and to the interconnecting wires. (A photosensitive film and an etchant are used to achieve this.)

(D) Oxide is etched through windows in the photosensitive film.

(F) Additional oxide is grown, a photosensitive film is applied, exposed, and developed (using a mask to determine

the pattern).

(H) Additional oxide is grown, windows are etched in the oxide using the photosensitive film, and impurity atoms are diffused into the epitaxial layer through the windows in the oxide.

Fig. 2-14. The monolithic fabrication process.

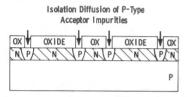

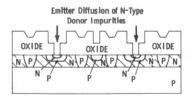

liquid form) after the wafer has cooled to room temperature. A photographic negative plate, called a mask (Fig. 2-15), is placed on top of the silicon wafer, and the film is exposed and developed. The areas of the film exposed to light by the mask remain, while the other areas are removed, as seen in Fig. 2-14C. The wafer is next immersed in an acid which removes only the silicon oxide, and only from areas not covered by the film. Once the remainder of the film is removed, the silicon wafer is placed in a p-type diffusion furnace which dopes the silicon through the windows just etched (as well as doping the top of the silicon oxide). Note that the mask has been used to determine the areas of the semiconductor to be doped. This first diffusion is called the *isolation diffusion* because it separates the n-type epitaxial layer into *isolation islands*. These islands constitute the separation of the components used in an integrated circuit. Transistors, resistors, and capacitors are built in their own isolation islands.

Fig. 2-15. Masking procedure for integrated-circuit fabrication.

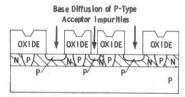

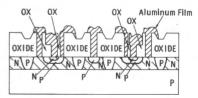

The base diffusion (Fig. 2-14G) and the emitter diffusion (Fig. 2-14H) are made in an oxidation-masking-diffusion process similar to the isolation diffusion. The length of time the diffusion is carried on is varied in each case to vary the diffusion depths. Note that each successive diffusion will be more heavily doped in order to effectively counterdope the previous diffusion. The emitter diffusion, being the final diffusion, is the most heavily doped, as it should be to get the  $n^+p$  junction discussed in the section on the transistor.

The final step of the fabrication is to connect the components fabricated together to form the circuit. This is done by evaporating aluminum on the wafer and then removing aluminum with a mask-ing/etching step from wherever it is not desired. The aluminum forms the interconnecting wires of the circuit as well as large square areas called *bonding pads*, which are to be connected to the leads of the package it is put into (Fig. 2-16).

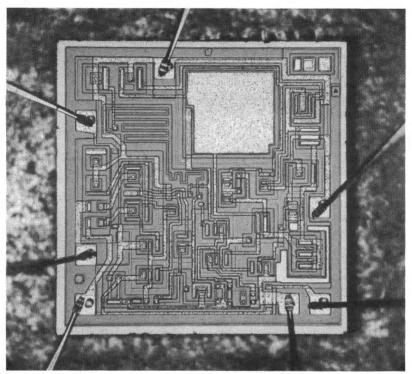

Courtesy Fairchild Semiconductor Fig. 2-16. A 741 op-amp chip with bonding wires attached.

Three diffusions and five masking operations have been used to create an integrated circuit. Typically, one wafer has several hundred integrated circuits fabricated on it at once. The masks determine the circuit that is built. The number of circuits built on a wafer depends on the number of times the pattern is repeated on the mask, the area of each pattern, and the area of the silicon wafer.

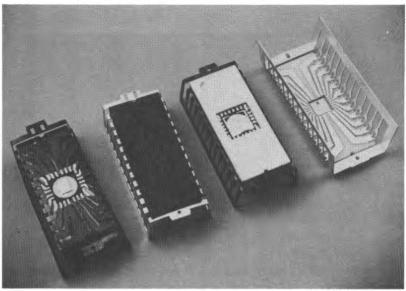

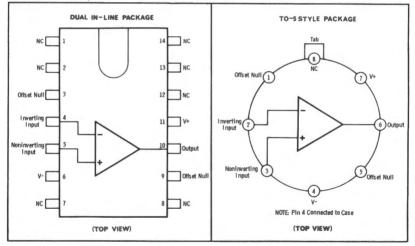

An automatic testing machine probes each circuit individually with small electrodes, and performs many tests before the wafer is broken up into individual circuits. Usually, fewer than one third of the circuits are good at this point. The good ones, which have been marked by the testing machine, are put into packages such as those shown in Figs. 2-1 and 2-17. Once the circuits are affixed to the package, little wires are connected between the aluminum bonding pads on the integrated circuit and the lead posts of the package. The wires, which have a diameter roughly that of a human hair, are affixed either through the use of heat and pressure or through the use of ultrasonic vibration and pressure. This process of attaching the connecting wires is called *bonding*.

Courtesy Fairchild Semiconductor

Fig. 2-17. Dual in-line IC packages.

#### Fabrication of Integrated-Circuit Resistors and Capacitors

Resistors and capacitors are required, in addition to diodes and transistors, to make an integrated circuit. These devices are made concurrent with the transistor fabrication discussed above.

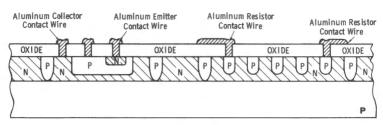

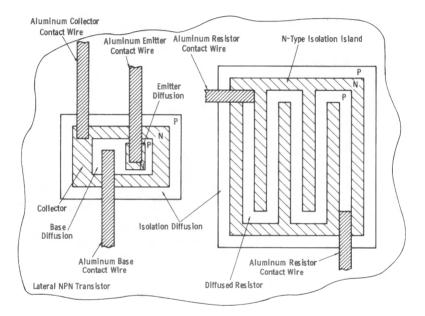

The structure of an integrated-circuit resistor is shown in Fig. 2-18. This p-type diffusion used to fabricate the resistor is the same diffusion that is used as a base diffusion in the npn transistors. All semiconductors have a resistance associated with them, which can be large if the resistor is made long with a small cross section. A typical resistor, when viewed from the top of the wafer, is long and skinny, and meanders for denser packing. Note that the n-type island in which the resistor is embedded must be connected to the highest voltage in the circuit to keep the resistor-island junction reverse biased, thereby constraining the resistor current to the confines of the resistor material.

Integrated-circuit capacitors can be fabricated in several ways. One common technique is to use the capacitance associated with the junction of a reverse-biased diode. The diffused resistor just discussed has a significant capacitance between it and the n-type island. This capacitance is dependent on the reverse voltage. (This variation of capacitance with voltage is the principle of voltage-variable capacitors, called *varactors*.)

Another technique used to build capacitors is to leave an aluminum plate on top of the silicon oxide above a diffused area when doing the

(A) Cross-sectional view.

(B) Top view.

Fig. 2-18. Monolithic lateral npn transistor and diffused resistor.

aluminum interconnection masking/etching step. This type of capacitor is called a MOS (metal-oxide semiconductor) capacitor. Since the MOS capacitor can be designed to have a capacitance which is independent of voltage, it is used wherever variations in capacitance cannot be tolerated.

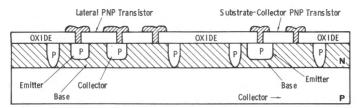

## The Lateral PNP Transistor and Substrate-Collector PNP Transistor

Although it is possible to build almost anything with only npn transistors, it sometimes becomes very attractive to use a simpler circuit that uses a pnp transistor.

(A) Cross-sectional view.

(B) Top view. Fig. 2-19. Monolithic pnp transistor structures.

Unfortunately, the standard fabrication process is npn-transistor oriented. Additional processing steps are expensive and compromise the quality of the npn transistor. As shown in Fig. 2-19, it is possible to realize two types of pnp transistors using the standard process: (1) the lateral pnp transistor and (2) the substrate-collector transistor.

The lateral pnp transistor meets the requirements for a pnp transistor in that it has two p-type regions separated by an n-type region, but it lacks the characteristics necessary for good performance. The width of the base region is typically 20 times that of the vertical npn transistor, and the base-emitter junction is not optimally doped as  $p^+$ as it should be to make a good  $p^+n$  base-emitter junction. These factors contribute to the low gain and small bandwidth of the lateral pnp transistor. The substrate-collector pnp transistor has disadvantages similar to the lateral pnp transistor and, in addition, it may only be used in circuits that have the collector of a pnp transistor connected to the negative-voltage power supply. However, the substrate-collector pnp transistor does have the advantage that it can be built in a smaller area than the lateral pnp transistor.

#### SUMMARY

The material presented in this chapter provides the background necessary for the understanding of the circuitry used in IC op amps. The lateral pnp transistor, for example, is frequently used in the opamp output stages discussed in Chapter 3. For another example, the MOS capacitor is commonly used for internal frequency compensation, as explained in Chapter 4.

## CHAPTER 3

## Monolithic Op-Amp Circuitry

During the past twenty years, there have been many different circuit realizations of operational amplifiers. Several common circuits have evolved, especially since the incorporation of op amps into integrated circuitry. The circuits used in monolithic IC op amps may be put into one of the following five circuit classes: (1) amplifiers, (2) current sources, (3) voltage references, (4) level shifters, and (5) output stages. This chapter will cover the design rules of integrated circuits, which overcome the shortcomings and exploit the advantages of integrated circuits, and show how these rules lead to effective designs in each of the circuit classes. The chapter will culminate in an example of how these circuits may be joined to form an IC operational amplifier.

## DESIGN RULES FOR INTEGRATED-CIRCUIT OPERATIONAL AMPLIFIERS

A set of "rules" for IC design has evolved out of the capabilities of silicon monolithic-fabrication technology. The following constitute the more significant rules:

## Minimization of the Number of Leads Coming out of the Package

One of the major production costs of integrated circuits is the attaching of leads to the silicon chip. To keep costs down, as well as to improve circuit performance by reducing package-induced parasitic capacitances, it is important to keep the amount of external circuitry, and hence the number of leads, to a minimum.

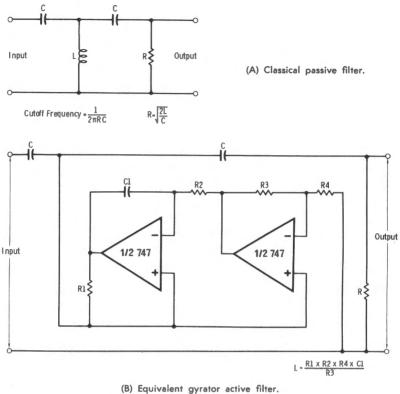

#### No Integrated Inductors Allowed

Since integrated circuits are built in one plane, it is very difficult and expensive to fabricate inductors as part of the integrated circuit. Only external inductors may be used, and then only when mandatory.

## Minimization of the Total Capacitance of Integrated Capacitors

As discussed in the last chapter, capacitors may be fabricated on the silicon wafer in a standard monolithic-fabrication process. Since capacitance is proportional to the area of the plates of a capacitor, the total surface area taken up by capacitors in an integrated circuit is proportional to the total capacitance used in the circuit design. The area taken up by an integrated circuit can greatly affect the cost of that integrated circuit. Since capacitors, except for very small ones, can take up a large area in comparison to the area of a diode or transistor, the total capacitance used in IC design should be minimized.

#### Minimization of the Total Resistance of Integrated Resistors

As discussed in the previous chapter, IC resistors are diffused into the silicon wafer at the same time as the bases of the vertical npn transistors. Even though some area savings may be made over capacitors by being able to put all resistors in the same n-type isolation island, resistors have to be long to achieve a large resistance. Since a mediumlarge resistor (100,000 ohms, for instance) is much larger than a transistor or a diode, the total resistance of integrated resistors should be minimized.

### Maximization of the Use of the Matching of Components

The predictability of the values of resistance, capacitance, and current gain in IC components is poor. Resistance may vary by more than 20%. Current gain may vary by more than a factor of 4. These numbers are the variations from the desired values. On a single silicon wafer, however, the matching between similar components is much better than this because all the components on the wafer were fabricated at the same time and received identical treatment. A good IC design will exploit this excellent "within-the-wafer matching" by making the design, whenever possible, dependent largely on the ratio of values of components and not on their absolute values. This is an important reason for the frequent use of differential circuits, which will be discussed in detail later in the chapter.

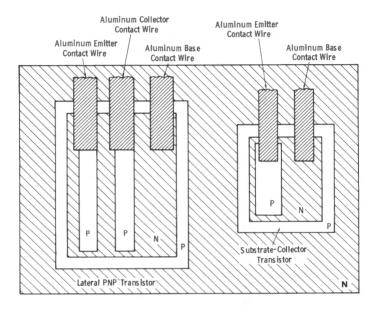

## Maximization of the Substitution of Transistors and Diodes for Larger-Area Components

Diodes and transistors are typically small structures by comparison to the other components on the silicon chip. Transistors that have col-

lectors in common with other transistors, and diodes that have n-type sides in common with other diodes or transistors can be made even smaller by sharing the same n-type island. Before being integrated, a design is checked to see if it is possible to change the circuit to use diodes or transistors in place of larger-area capacitors and resistors. As shown in Fig. 3-1, it may save area and improve performance to replace a large resistor with two smaller resistors and two transistors. In some applications, the junction field-effect transistor can be used almost as a direct replacement for high values of resistance, as shown in Fig. 3-2.

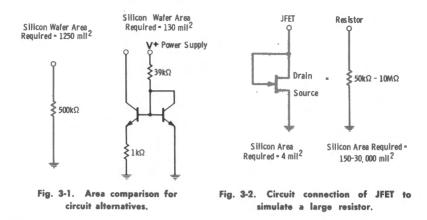

#### Maximization of the Use of Built-In Voltage References

A voltage reference is a device that can be used to create a voltage that, among other things, may be considered constant and independent of power-supply voltage. In integrated circuits, there are two common sources of voltage references: (1) the breakdown of reverse-biased diodes and (2) the voltage drop across forward-biased diodes.

The reverse-biased diode, discussed in Chapter 2, is shown in a typical circuit in Fig. 3-3A. In an integrated circuit, the diode would be the base-emitter junction of a vertical npn transistor. For typical ICs, this junction breaks down at around 5 volts. The other junction, the vertical npn transistor collector-base junction, built during the standard fabrication procedure, has too high a breakdown voltage to be useful in integrated-circuit design.

The forward-biased silicon diode does not pass much current until the built-in, diffusion-current retarding electric field is nearly canceled out. If the ohmic resistance of the diode can be neglected, the current through the diode increases tenfold for every 60-millivolt increase in bias voltage. If a low-resistance diode passes 1 milliampere of current with 0.6-volt bias, it will pass 1 ampere with 0.78-volt bias. For most

Fig. 3-3. Constant-voltage reference sources.

practical purposes, the voltage across a forward-biased diode may be assumed constant, regardless of the current being passed through it. Though it may vary from device to device, 0.7 volt is a reasonable approximation for the value of this constant voltage drop. If, as shown in Fig. 3-3B, one or more diodes is put in series, a very good and convenient reference voltage may be obtained.

A voltage reference creates noise, regardless of the type of device used to generate it. The breakdown of the reverse-biased diode inherently has substantially more noise output than the forward-biased diode. Hence, the breakdown of reverse-biased diodes should not be utilized in a signal path or where the minimization of noise is important.

Integrating the reference-voltage device on the same silicon chip reduces the number of leads leaving the package and results in a lessexpensive unit. Having the reference device on the same silicon chip also allows closer temperature tracking, and hence less drift.

## IC OP-AMP CIRCUITS

Although it is impossible to show all circuits used in IC op amps, it is relatively easy to classify parts of all op-amp circuits. The following is a description of a complete group of circuit classes which are used in almost all op amps:

#### **Differential Amplifiers**

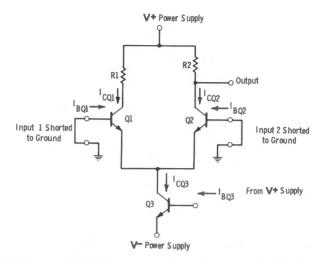

A differential amplifier amplifies the difference between two input signals. A circuit for a typical differential-amplifier stage is shown in Fig. 3-4.

The current-source transistor (Q3) is biased from the power supply. To a good degree of approximation, the current flowing in the collec-

Fig. 3-4. A typical differential-amplifier circuit with inputs grounded.

tor  $(I_{CQ3})$  is a constant value set by the base current  $(I_{BQ3})$  times the current gain  $(\beta)$  of transistor Q3. When both inputs are grounded, one half of  $I_{CQ3}$  will flow through transistor Q1, and the other half will flow through transistor Q2, if the transistors are well matched. Since one half of current  $I_{CQ3}$  is flowing through Q1, a base-emitter current  $(I_{BQ1})$  will flow, allowing the much larger collector-emitter current  $(I_{CQ1})$  to flow. Both  $I_{BQ1}$  and  $I_{CQ1}$  add to make up half of  $I_{CQ3}$ . Likewise, a base-emitter current  $(I_{BQ2})$  and collector-emitter current  $(I_{CQ2})$  will flow through transistor Q2, comprising the other half of  $I_{CQ3}$ . These base currents  $(I_{B01} \text{ and } I_{B02})$  are called the *input-bias currents*.

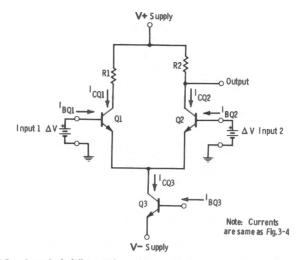

If, as shown in Fig. 3-5, both inputs 1 and 2 are raised by  $\Delta V$  (called a *common-mode input signal*), the output remains unchanged because both inputs were treated identically and the circuit is symmetrical. The only change that does occur in the circuit is that  $V_{OQ3}$  increases by  $\Delta V$ . Note that  $I_{OQ3}$  does not change because the collectoremitter current is dependent only on the base-emitter current, and not on the collector-emitter voltage.

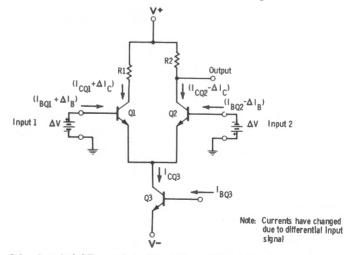

If, as shown in Fig. 3-6, input 1 is raised by  $\Delta V$  and input 2 is lowered by  $\Delta V$  (called a *differential-mode input signal*), the current flowing through Q1 will increase, while the current flowing through Q2 will decrease by the same amount, because the sum of the currents coming out of the emitters of Q1 and Q2 must remain equal to  $I_{CQ3}$ , which is constant. Voltage  $V_{CQ3}$  does not change from the case where both inputs were grounded, because one input was raised while the other was lowered. This constant ( $V_{CQ3}$ ) can be thought of as being similar to the pivot point of a teeter-totter, and the input signals as the ends of the teeter-totter.

Fig. 3-5. A typical differential amplifier with a common-mode input signal.

Since the current through Q1 has increased and the current through Q2 has decreased, there is a change in the voltage drop across the load resistors. Since the output of this amplifier is the power-supply voltage less the voltage drop across R2, the output will have a response to the change in current flowing into the collector of Q2. The gain of the stage is determined by the size of resistor R2 and the magnitude of the change in collector current for a given change in input voltage.

Assuming that  $I_{CQ3}$  remains constant and that the components are well matched, it is clear that this differential-amplifier circuit will

Fig. 3-6. A typical differential amplifier with a differential-mode input signal.

(A) A simple constant-current source.

(B) An improved constant-current source.

(C) An improved constant-current source for small currents.

Fig. 3-7. Constant-current sources.

amplify a differential-mode input signal but will not amplify a common-mode input signal. In practical circuits it is impossible to match components perfectly and to keep  $I_{CQ3}$  absolutely constant as a function of collector-emitter voltage. These nonideal factors cause the amplifier to have some output signal in response to a common-mode signal as well as to a differential-mode signal. Typically, however, the amplifier amplifies a differential-mode signal 10,000 times more than it amplifies an equivalent common-mode signal. Yet this performance can only be achieved with well-matched transistors, such as those that were fabricated at the same time, side by side, on the same silicon wafer.

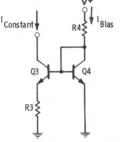

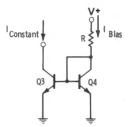

#### **Constant-Current Sources**

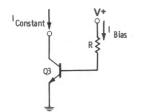

Often in operational-amplifier design there is a need to maintain a constant current flowing. An example is  $I_{CQ3}$ , discussed in the previous section. Usually, integrated-circuit constant-current sources are constant-current *sinks*. They are designed using a simple transistor model that is based on the assumption that the collector-emitter current of a transistor is equal to the base-emitter current times the current gain of the transistor, and that the current gain is virtually independent of the collector-emitter voltage.

The simple current source referred to in the previous section is shown in Fig. 3-7A. This circuit requires large values of resistance and depends on the value of the transistor current gain to determine the level of the constant current. Both of these constraints are intolerable in good integrated-circuit design.

Fig. 3-7B shows a design for an integrated-circuit current source which overcomes the disadvantages of the simpler current source just discussed. Since the base-emitter bias voltage of both of the wellmatched transistors is identical, the base currents of both transistors (I<sub>BQ3</sub> and I<sub>BQ4</sub>) must be identical. The current I<sub>BLAS</sub> has three components:  $I_{BO3}$ ,  $I_{BO4}$ , and  $I_{CO4}$ . If the transistors have high current gains, the collector current  $(I_{004})$  will be much greater than the base currents (I<sub>B03</sub> and I<sub>B04</sub>). Hence, the collector current (I<sub>C04</sub>) will be approximately equal to IBIAS. Since the base currents of both wellmatched transistors are equal, the collector currents should be equal, and also approximately equal to IBIAS. Thus, the collector current of Q3. which is the current being kept constant, is equal to and dependent only on IBIAS. Since IBIAS is not amplified, it is a larger current than supplied in the simpler current source shown in Fig. 3-7A. Hence, for a given power-supply voltage, a smaller, space-conserving resistor may be used than in the simpler circuit. In applications where a very small constant current is desired, I<sub>CONSTANT</sub> may be made less than  $I_{BIAS}$  by placing a resistor in series with the emitter of Q3, as shown in Fig. 3-7C. This resistor serves to decrease bias across the base-emitter iunction. which decreases the base-emitter current. This in turn decreases the collector current, which is the current being controlled.

The goal of these designs is to utilize the matching of transistors to achieve a stable, current-gain independent, current source.

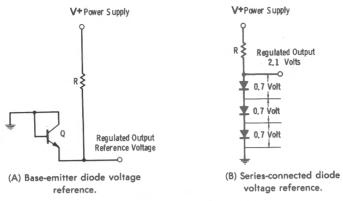

#### **Voltage References**

There are two types of voltage references: (1) the forward-biased diode and (2) the reverse-biased diode. The voltage drop across the forward-biased diode is the most popularly used reference in operational amplifiers.

43

The current source shown in Fig. 3-7B, and discussed in the last section, is biased by the base-emitter junction voltage of transistor Q4 being applied to the base-emitter junction of Q3. The base-emitter junction of Q4 is acting like a special type of forward-biased diode. The application of this built-in reference voltage results in a very high-performance circuit, because any changes due to temperature, for instance, cancel out if the transistors are well matched.

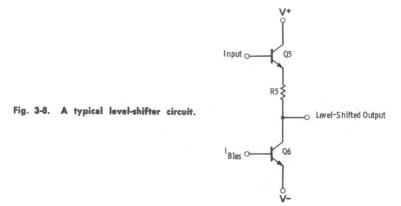

## **Level Shifters**

In a typical operational amplifier there often are stages of differential amplifiers, followed by a level shifter which drives an output stage. There is a need for level shifters because there is a dc offset in the output of a differential amplifier, such as shown in Fig. 3-4 for the case of no input.

The exact type of level shifting required depends on the exact circuit used in the preceding amplifier stages and on the output stage it drives. A typical level-shifting circuit, which provides no voltage gain, is shown in Fig. 3-8.

Transistor Q6 acts as a current source which maintains  $V_{CQ6}$  constant. The voltage drop across resistor R5, using Ohm's law, is:

$$V_{R5} = I_{CQ6} \times R5$$

This voltage drop is a constant since  $I_{CQ6}$  and R5 are constant. The voltage drop across the base-emitter junction of Q5 ( $V_{BQ5}$ ) is simply a forward-biased diode voltage drop (approximately 0.7 volt), which is also constant. Since the output voltage is just the input voltage less the drop across the base-emitter junction of Q5 and the drop across R5, the output of this stage can be thought of as the input voltage shifted in dc level by the sum of the two voltage drops. These drops can be designed to make the dc output of the entire amplifier zero when the input to the amplifier is zero.

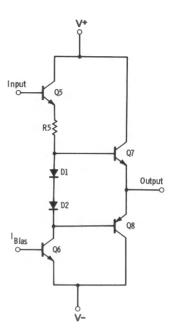

#### **Output Stages**

The output stage of an operational amplifier should be capable of driving large loads. It is actually a small power amplifier.

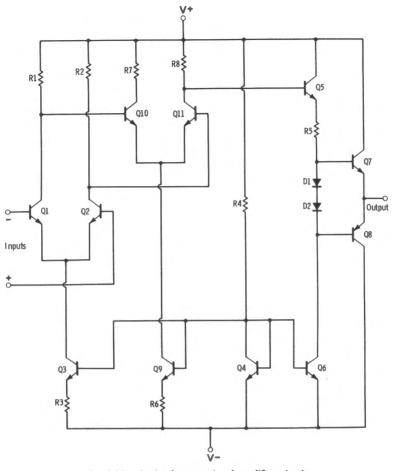

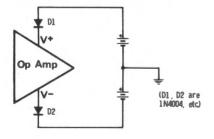

A typical npn/pnp complementary transistor output stage is shown in Fig. 3-9. The operation of this circuit may be understood by realizing that the output voltage is different from the base voltages of output transistors Q7 and Q8 by just a forward-biased, base-emitter diode voltage drop (0.7 volt). Thus, any signal appearing at the connection of diodes D1 and D2 will appear at the output. These diodes are incorporated into the level-shifter circuit of Fig. 3-8 so that the output voltage is just equal to the input voltage shifted in dc level. Although the output stage has no voltage gain, it does have power gain and is able to drive large loads.

Fig. 3-9. A typical npn/pnp complementary output stage.

This configuration is capable of delivering large currents to a load, yet has small stand-by currents flowing if no input signal is applied. If a large (low-resistance) load is placed on the output, the output voltage will not drop significantly. This is because a small drop in the output voltage tends to increase and decrease the appropriate output-transistor base-emitter biases in such a direction as to supply more current to the load. This circuit may be thought of as incorporating a form of negative feedback to increase the load-driving capability of the output stage.

Since the output stage of an integrated-circuit operational amplifier can heat up, it is often placed as far away from the differential input stage as possible on the silicon chip, to reduce drifts in the output voltage due to temperature effects.

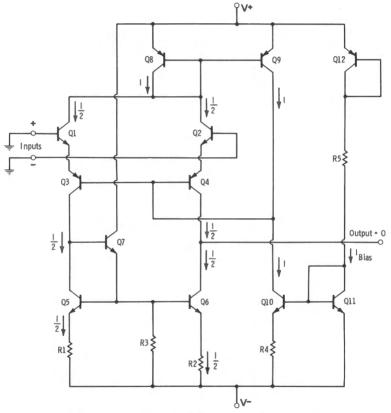

## A SIMPLE INTEGRATED-CIRCUIT OPERATIONAL AMPLIFIER

Thus far this chapter has covered the design rules of integrated circuits and a sampling of the circuits used in operational amplifiers. It can be seen that the circuits exemplify the philosophy behind the rules.

The circuits described in this chapter have been chosen to be representative of those used in operational amplifiers. A complete operational amplifier that utilizes these circuits is shown in Fig. 3-10. The operation of this circuit should be apparent from the previous descrip-

Fig. 3-10. A simple operational-amplifier circuit.

tions. (Notice that voltage reference Q4 is shared by Q3, Q6, and Q9, and that resistors R3 and R6 are used to reduce the currents flowing through Q3 and Q9 to their optimal values. Also notice that the input differential amplifier has outputs taken from both collector resistors R1 and R2.)

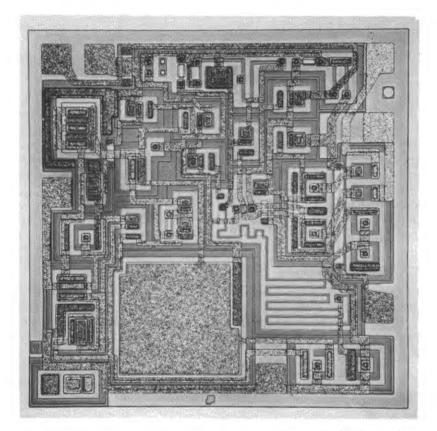

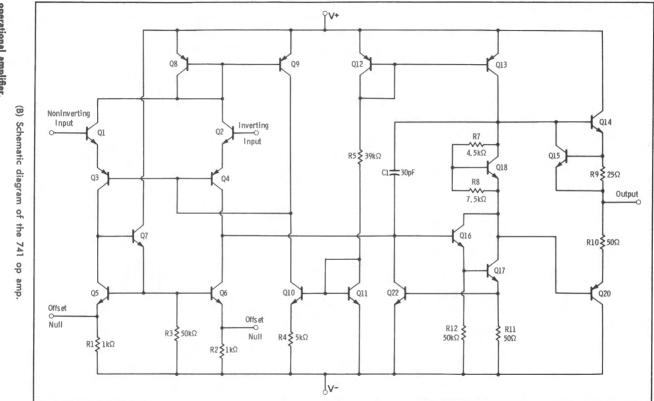

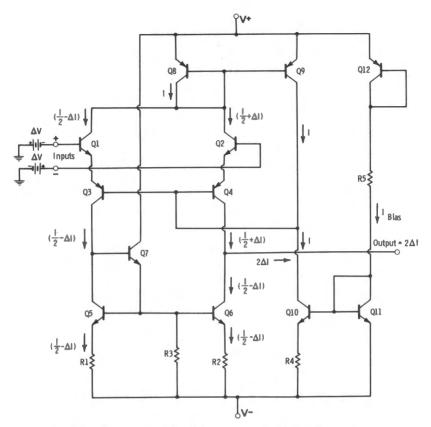

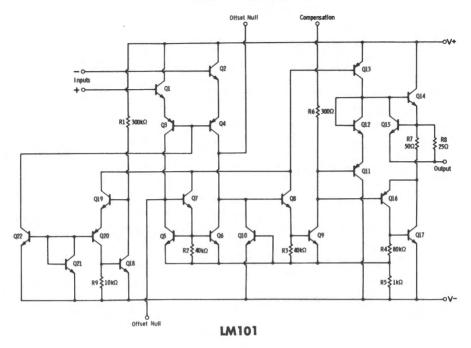

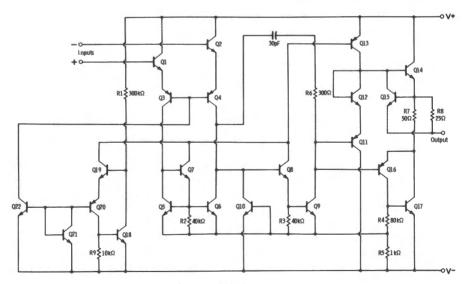

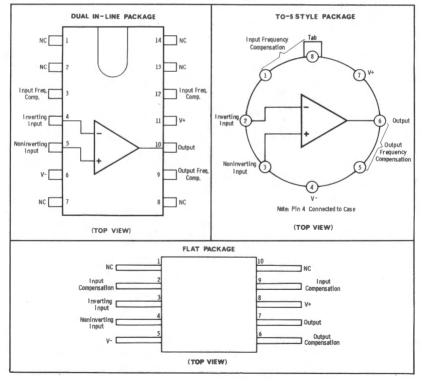

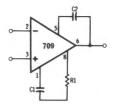

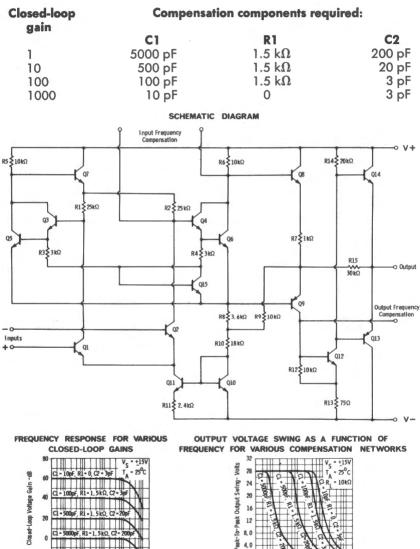

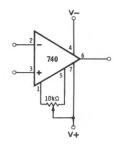

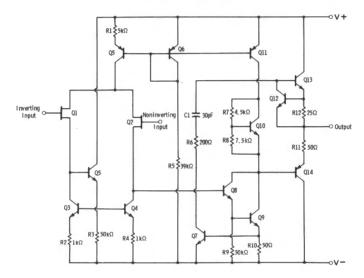

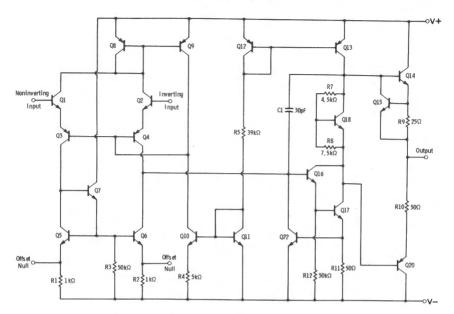

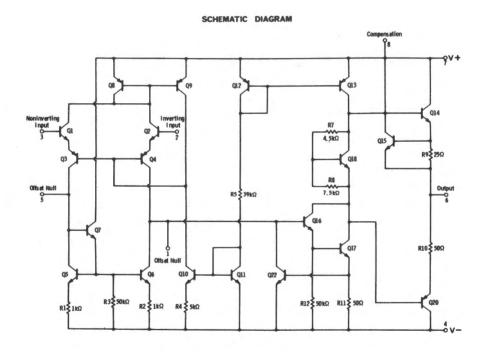

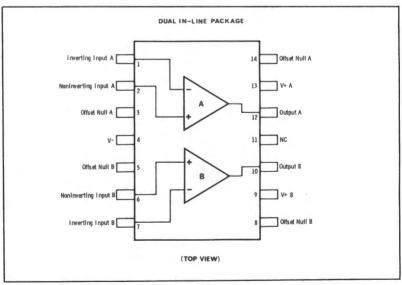

## THE 741 OPERATIONAL AMPLIFIER

Commercially manufactured operational amplifiers can be analyzed in terms of the circuit classes discussed in this chapter. The actual circuits used in the commercially fabricated devices may be simpler or far more complex than the circuits that have been discussed. The same general design philosophy of integrated-circuit technology is used in all the circuits, however. In addition to being a widely used, high-performance, general-purpose operational amplifier, the 741, shown in Fig. 3-11, is a good example of an op amp that can be analyzed in terms of the concepts introduced in this chapter; yet it is a fairly different circuit from the simple circuit of Fig. 3-10.

## **Differential-Amplifier Input Stage**

The differential-amplifier input stage of the 741 is shown in Fig. 3-12. Transistor Q11 acts as a voltage reference for current-source transistor Q10, and transistor Q8 acts as a voltage reference for currentsource transistor Q9. It is easy to identify this type of voltage reference from the connection between the collector and base terminal of the transistor.

Since the two current sources are connected together, the currents flowing through them will be approximately equal, assuming that the collector-emitter current flowing through them (I) is much larger than the current going into the bases of transistors Q3 and Q4. As discussed previously in the constant-current section, the current flowing through the voltage-reference diode is approximately equal to this constant current I. The other voltage reference (Q11) has a current I<sub>BIAS</sub> (which is greater than I due to resistor R4) flowing through it. Since I<sub>BIAS</sub> is determined by the power supply voltage, it may be considered constant. Note that I<sub>BIAS</sub> determines all the currents flowing through the differential-amplifier input stage by adjusting the base current flowing in transistors Q3 and Q4, which in turn equalizes the current flowing through current-source transistors Q9 and Q10.

If both inputs are grounded and the transistors are well matched, the currents will be distributed as shown in Fig. 3-12. Since the current gain of the transistors is high, the base currents are small in comparison to the collector and emitter currents and may be ignored when analyzing the collector and emitter currents.

This differential amplifier will ideally have no response in the output, due to a common-mode input signal. That is, raising or lowering both inputs will result in no change in the currents flowing through transistors Q1 and Q2 because both inputs are treated equally.

Analyzing the response of the input stage to a differential-mode input signal is a bit more complex, as shown in Fig. 3-13. Transistors Q5 and Q6 must always have the same collector-emitter current flowing through them since they receive, by symmetry, the same baseemitter bias, which comes from transistor Q7. Transistor Q7 is in turn controlled by the collector voltage on transistor Q5. Thus, the collector-emitter current flowing through transistor Q6 is always equal to the collector-emitter current flowing through transistor Q5. This circuit may be thought of as a modified current source. If a differential-

**Courtesy Fairchild Semiconductor**

(A) Photomicrograph of 741 op-amp silicon chip.

Fig. 3-11. The 741

operational amplifier.

49

mode input signal causes the collector-emitter current in Q1 to decrease by  $\Delta I$ , and the collector-emitter current of Q2 to increase by  $\Delta I$ , the output current will be two times  $\Delta I$  because the collector-emitter current of Q4 will increase by  $\Delta I$ . The amount of current allowed to flow in Q6 will decrease by  $\Delta I$  because the base-emitter current of Q5 decreased by  $\Delta I$ . Thus, the output current, in response to a differential input signal, is affected by the changes in collector-emitter current through both input transistors Q1 and Q2.

Fig. 3-12. Input stage of the 741 op amp with inputs grounded.

This circuit has the advantage of a large, maximum allowable, differential input signal because a differential input signal would have to "break down" two reverse-biased emitter-base junctions in comparison with one junction of the previously discussed differential amplifiers. The additional junction is the base-emitter of a lateral pnp transistor. This junction has a large reverse-biased breakdown voltage. The combination of the two junctions in series then increases the maximum

Fig. 3-13. Input stage of the 741 op amp with differential input signal.

nondestructive input signal many times. This improvement is very important, especially in integrator and comparator applications, and makes the input-stage transistors virtually indestructible.

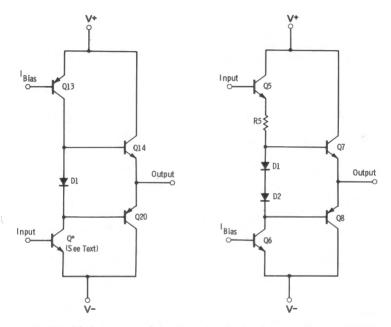

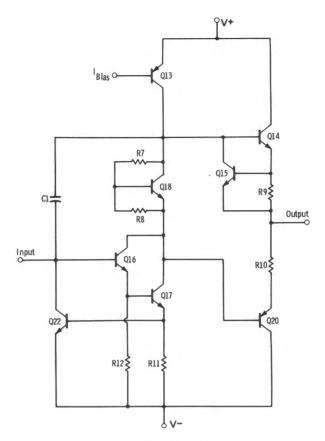

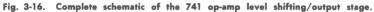

## Level Shifter and Output Stage

As seen in the simplified circuit shown in Fig. 3-14, the level shifter and output stage of the 741 are very similar to the circuit of Fig. 3-9, previously discussed in this chapter and shown again in Fig. 3-15. Due to the input stage configuration, the level shifting of the 741 is in the opposite direction (in the direction of higher voltages) to that of the previous circuit. The transistor-resistor configuration of Q18, R7, and R8, shown in the complete level-shifting/output-stage circuit of the 741 (Fig. 3-16), may be thought of as a diode with a little resistance added to increase the voltage drop across it. This voltage drop is a little more than the drop across the single diode (D1) of Fig. 3-14, and a little less than the drop across the two diodes (D1 and D2) of Fig. 3-15. This is a compromise in biasing the output stage between distortion and power consumption. The transistor  $(Q^*)$  in the simplified circuit of Fig. 3-14 represents transistors Q16 and Q17 in the complete circuit of Fig. 3-16. This configuration of transistors, which is known as the Darlington configuration, simulates a very high current gain transistor by injecting the emitter current of the first transistor (Q16) into the base of the second transistor (Q17). Since the amplified current of the first transistor is put into the input of the second, the two transistors are roughly equivalent to a single transistor with a current gain equal to the current gain of the first transistor. This type of level shifting/output stage has a signal-voltage gain, in contast to the configuration of Fig. 3-8, which has unity gain.

Fig. 3-14. Simplified schematic of the 741 op-amp level shifting/output stage.

Fig. 3-15. A typical npn/pnp complementary output stage.

Transistors Q22 and Q15, shown in the complete circuit of Fig. 3-16, act as output-current limiting transistor "switches" that turn on whenever the currents flowing through resistors R11 and R9 respectively, reach their threshold voltage (approximately 0.7 volt). When turned on, these switches short out the base-emitter current of the output transistors. These protection transistors, in effect, limit the output current to some predetermined amount.

The 741 is one of the more advanced and sophisticated operational amplifiers, yet it and all other integrated-circuit operational amplifiers may be analyzed in terms of the circuit concepts and classes discussed in this chapter.

## **CHAPTER 4**

# The Integrated-Circuit Op Amp

Circuits that use operational amplifiers are often designed using the concept of the ideal op amp discussed in Chapter 1. It is often possible to obtain an operational amplifier that will behave as an ideal op amp for the application of interest. Integrated-circuit operational amplifiers do have limitations, however, and it is the purpose of this chapter to identify them, show their origin, and show how to predict their effect from a manufacturer's specification sheet.

## **OUTPUT OFFSET**

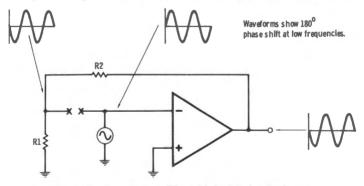

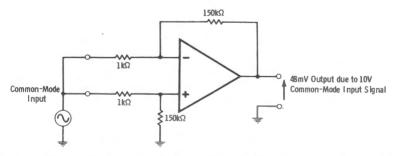

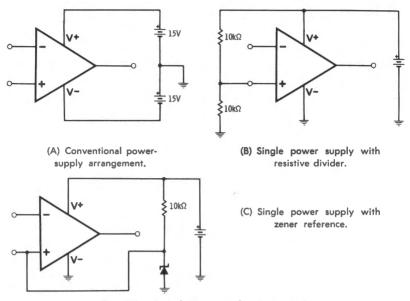

The steady-state output of an ideal op-amp negative-feedback circuit is zero when the input is zero. In the same circuit, however, an IC op amp may have a dc output voltage, called the *output offset voltage*. If the output offset voltage is large, it may adversely affect circuit performance. Output offset voltage is due to two sources: (1) *input bias current* and (2) *input offset voltage*.

#### **Bias-Current Offset**

The input bias currents were discussed in the section on differential amplifiers in Chapter 3. They are essentially the currents that must be supplied to the two inputs of the operational amplifier to assure proper biasing of the differential input-stage transistors. Since bipolar transistors are current-amplifying devices (as opposed to unipolar transistors [FETs], which are voltage-amplifying devices), input bias currents must always be supplied, even with perfect component matching.

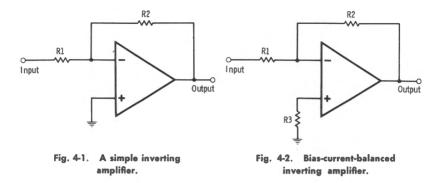

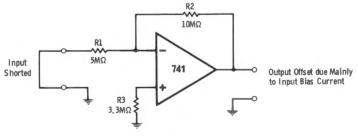

The input bias current, in the simple inverter circuit shown in Fig. 4-1, flows through resistors R1 and R2, causing a voltage to be de-

veloped across them. This voltage appears at the input of the op amp as a differential input signal because there is no corresponding voltage appearing at the other (grounded) input terminal of the IC. It is this differential input signal that is amplified by the op amp. The output offset voltage due to input bias current in this simple inverter circuit is approximately:

$$\mathbf{E}_{\mathrm{os}} = \mathbf{I}_{\mathrm{b}} \times \mathbf{R2}$$

where,

$E_{os}$  is the output offset voltage in volts,  $I_b$  is the input bias current in amperes, R2 is in ohms.

This equation is derived assuming that the differential input signal is virtually zero for any output voltage.

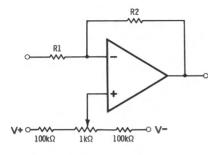

A simple way to correct for output offset due to bias currents is to place a resistor (R3) between the +input and ground, as shown in Fig. 4-2. The voltage drop across R3 (due to bias current) must be equal to the voltage at the -input caused by bias currents flowing through R1 and R2. To have an output offset of zero, the value of R3 would be:

$$R3 = \frac{R1 \times R2}{R1 + R2}$$

assuming that the bias currents flowing into each lead are equal.

But even though the bias currents are well matched, they are not *exactly* equal. In the circuit of Fig. 4-2, there will still be an output offset voltage due to the difference between the two bias currents. The difference between the bias currents flowing into the two inputs, when the output is at zero volts, is defined as the *input offset current*. The output offset voltage due to the input offset current is approximately:

$$E_{os} = I_{os} \times R2$$

where,

$E_{os}$  is the output offset voltage in volts,  $I_{os}$  is the input offset current in amperes, R2 is in ohms.

The addition of resistor R3 will reduce the output offset voltage because the difference in the bias currents flowing into the op-amp inputs (i.e., the input offset current) is less than either of the bias currents. The output offset voltage using this technique may be of either polarity, depending on the internal mismatches in the op amp.

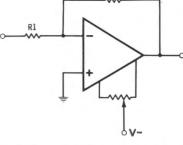

#### Input Offset Voltage

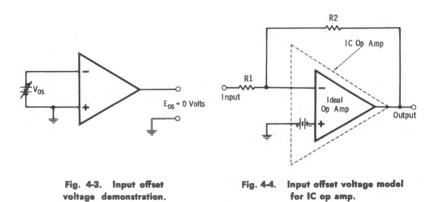

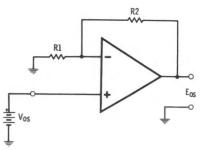

The *input offset voltage* is the other source of output offset. The input offset voltage, as shown in Fig. 4-3, is defined as equal to the differential input voltage that must be applied across the inputs of the op amp in order to make the output voltage zero. The input offset voltage is not zero due to slight mismatches in the internal components of the IC op amp.

The input offset voltage may be modeled as a voltage source in series with the +input lead of an ideal op amp, as seen in the invertingamplifier circuit of Fig. 4-4. For this inverting-amplifier circuit, the output offset voltage due to the input offset voltage can be calculated as the response of a noninverting amplifier (Fig. 1-9A) to the input offset voltage, as shown in Fig. 4-5:

$$\mathbf{E}_{\rm os} = \frac{\mathbf{R}\mathbf{1} + \mathbf{R}\mathbf{2}}{\mathbf{R}\mathbf{1}} \times \mathbf{V}_{\rm os}$$

where,

$E_{os}$  is the output offset voltage in volts,  $V_{os}$  is the input offset voltage in volts, R1 and R2 are in ohms.

Fig. 4-5. Noninverting amplifier model for simple inverting or noninverting amplifier calculations.

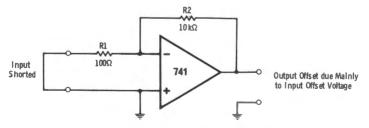

## **Example Calculation of Output Offset Voltage**

Figure 4-6 shows an actual inverting-amplifier circuit using a 741 op amp. The output offset is due to two sources, as discussed in the previous sections.

Using the typical 741 data given in the Appendix:

Input bias current =

$$80 \text{ nA} = 8 \times 10^{-8}$$

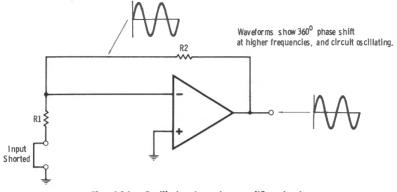

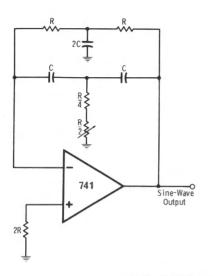

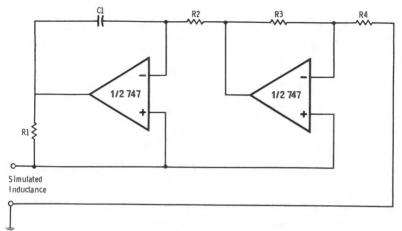

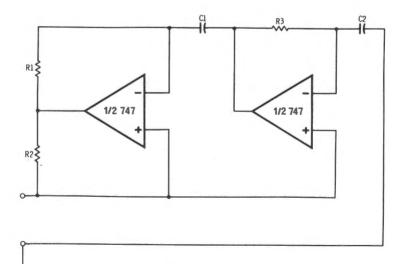

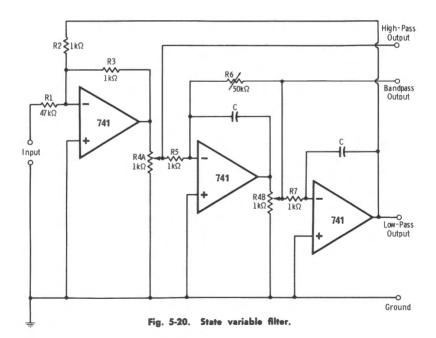

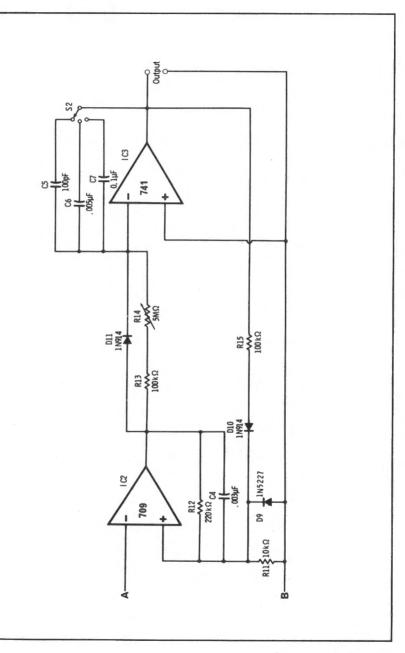

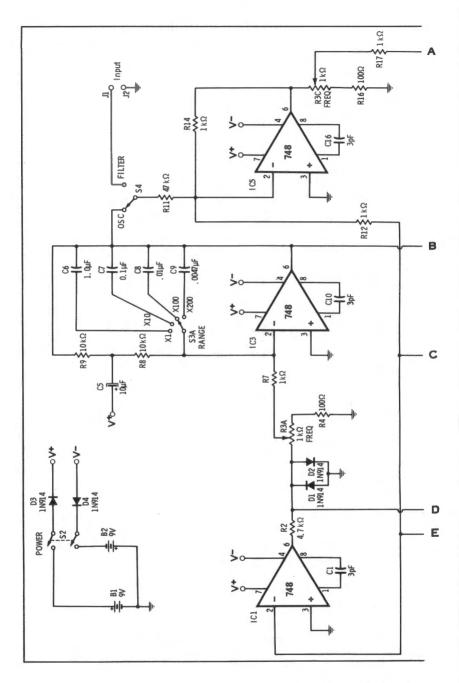

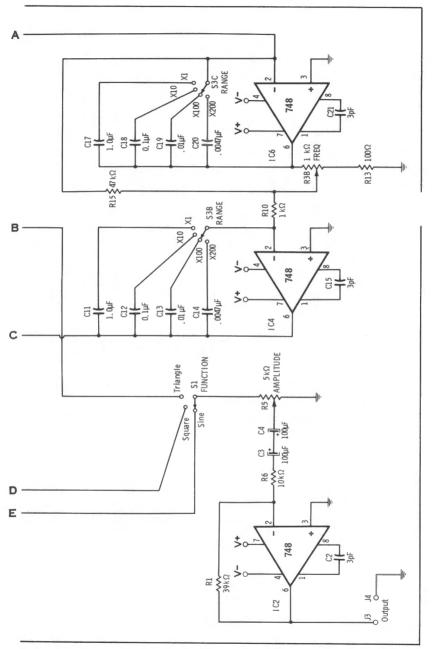

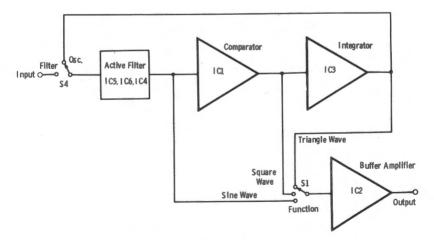

ampere