# IC TIMER COOKBOOK

WALTER G. JUNG

## IC TIMER COOKBOOK

by Walter G. Jung

Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANA POLIS, INDIANA 46268 USA Copyright © 1977 by Howard W. Sams & Co., Inc., Indianapolis, Indiana 46268

#### FIRST EDITION THIRD PRINTING-1978

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21416-4 Library of Congress Catalog Card Number: 77-72622

Printed in the United States of America.

## Preface

Before the 555 timer was introduced in 1972, most monostable and astable RC timing circuits were designed from the ground up, using either discrete semiconductors or ICs as the active elements. The advent of the 555 has changed all of that, making timer designs for most applications a simple hookup of four to five low-cost components. Currently, a 555 (or one of its derivatives) can satisfy about 75% or more of timing requirements with precision, simplicity, and low cost.

Although nothing was revolutionary in its basic concept or theory, the 555 caught on very quickly after its introduction. Perhaps it was just an IC idea whose time had come in terms of getting the right ingredients into a single chip. Nevertheless, its popularity is probably rivaled by no other linear circuit (with the exception of the op amp), and circuit designers are continually producing new and previously undocumented uses for it.

Success, of course, spawns growth in even greater dimensions; the IC timer idea soon became available in duals, then in more sophisticated and wide-range versions, and also in timer/counter combinations. This book discusses all of these types of timers, using representative industry standard devices as examples.

Today the IC timer is king of virtually all RC-timer applications with periods greater than 10  $\mu$ s, and timing periods can readily be extended into days, weeks, or even months, if desired. The devices are available from many sources, they are versatile, easy to design with, easily programmed or controlled, and interface readily with digital devices. The IC timer represents another milestone of progress in solid-state electronics, and is certainly a tool from which we can all benefit. Some of the circuits contained in this book have been published previously. In these cases, a specific reference is given accompanying the discussion. The author gratefully acknowledges the work of the authors who have provided the concepts discussed. A general bibliography of timer circuit designs is also contained in Appendix D.

WALTER G. JUNG

## **Acknowledgments**

In the course of preparing this book, the author was aided by various sources of information. For the use of their technical material, the author is grateful to the following companies:

Exar Integrated Systems Intersil, Inc. National Semiconductor Corp. Signetics Corp.

Also, the following industry publications were helpful in allowing use of their copyrighted material:

Electronics Electronic Design EDN

The author is also grateful to the following individuals who commented critically on various portions of the manuscript: Bob Zwicker and Alan Grebene of Exar, Bill O'Neil of Intersil, Carl Nelson and Bob Pease of National, and Russ Long and Ted Vaeches of Signetics.

Finally, to my wife Anne goes a special note of thanks for the typing of the manuscript. Thanks also to my research assistants, Jeannie and Mark.

W.G.J.

To Mom

## Contents

## Part I–Introducing the IC Timer

#### CHAPTER 1

| RC | Тім | ER BASICS . |        |     |     |    |  | • |   |  |  |    | 11 |

|----|-----|-------------|--------|-----|-----|----|--|---|---|--|--|----|----|

|    | 1.1 | The Monosta | able 1 | RC  | Tim | er |  |   |   |  |  | 11 |    |

|    | 1.2 | The Astable | RC '   | Tim | er  |    |  |   | • |  |  | 14 |    |

#### **CHAPTER 2**

| IC | Тіме | TYPES                                                |    | 19 |

|----|------|------------------------------------------------------|----|----|

|    | 2.1  | The 555 Single-Unit General-Purpose Timer            | 19 |    |

|    | 2.2  | The 556 Dual-Unit General-Purpose Timer              | 33 |    |

|    | 2.3  | The 322 and 3905 Wide-Range, Precision,              |    |    |

|    |      | Monostable Timers                                    | 36 |    |

|    | 2.4  | The 2240, 2250, and 8260 Programmable Timer/Counters | 46 |    |

#### **CHAPTER 3**

| GENERA | L OPERATING PROCEDURES AND                 |  |   |    |    |

|--------|--------------------------------------------|--|---|----|----|

| PRECAU | TIONS IN USING IC TIMERS                   |  |   |    | 63 |

| 3.1    | Standard Pinouts and Terminal Designations |  |   | 63 |    |

| 3.2    | Timing Component Considerations            |  |   | 65 |    |

| 3.3    | General Design Precautions                 |  | • | 70 |    |

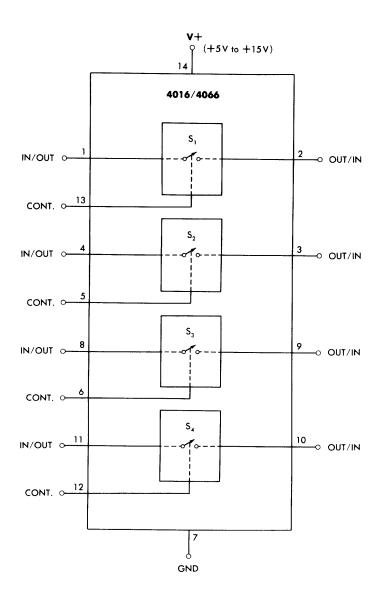

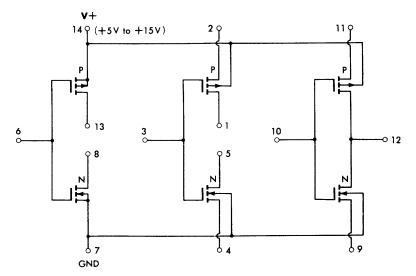

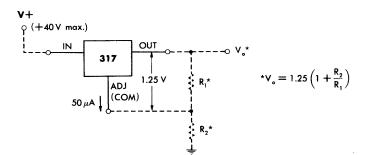

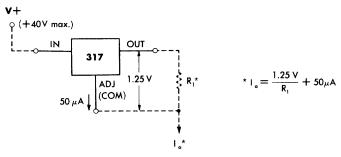

| 3.4    | Peripheral Devices                         |  |   | 71 |    |

### Part II–IC Timer Applications

#### CHAPTER 4

| Monosta | ABLE TIMER CIRCUITS                       |   |   |         | 85 |

|---------|-------------------------------------------|---|---|---------|----|

| 4.1     | 555 Monostable With Auxiliary Output .    |   |   | <br>86  |    |

| 4.2     | Inverted Monostable                       |   |   | <br>87  |    |

| 4.3     | Improved Inverted Monostable              |   |   | <br>89  |    |

| 4.4     |                                           |   | • | <br>89  |    |

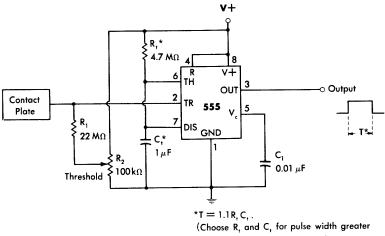

| 4.5     | Touch Switch                              |   |   | <br>91  |    |

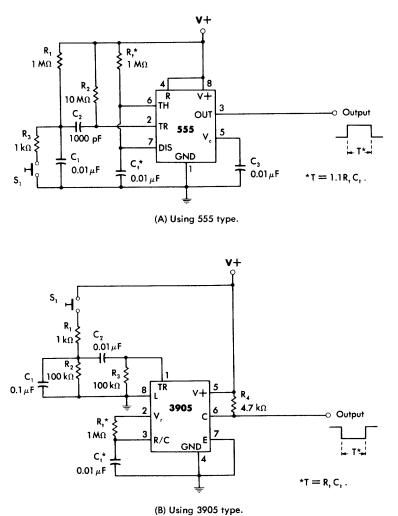

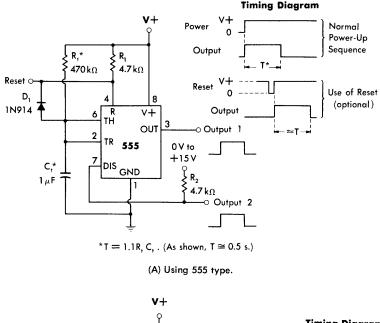

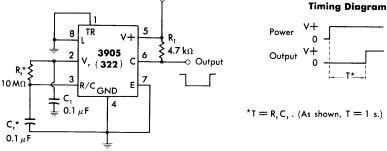

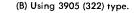

| 4.6     | Power-Up One-Shots                        |   |   | <br>92  |    |

| 4.7     | Restartable One-Shot                      |   |   | <br>94  |    |

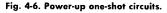

| 4.8     | Retriggerable One-Shot                    |   | • | <br>96  |    |

| 4.9     | Delayed-Pulse Generation                  |   |   | <br>97  |    |

| 4.10    | Programmable Monostables                  |   |   | <br>98  |    |

|         |                                           | • |   | 102     |    |

| 4.12    | Voltage-Controlled Monostables            |   |   | <br>105 |    |

|         | Linear-Ramp Monostables                   |   |   | 107     |    |

| 4.14    | Fast Voltage-to-Pulse-Width Converter .   |   | • | <br>109 |    |

| 4.15    | Long-Period Voltage-Controlled Timer .    |   |   | <br>110 |    |

|         | Ratiometric Voltage-to-Pulse-Width Conver |   |   | 112     |    |

|         |                                           |   |   |         |    |

#### **CHAPTER 5**

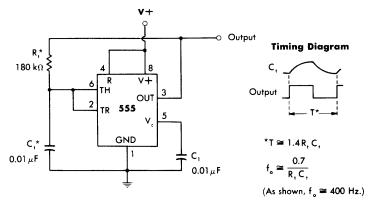

| 5.1  | Minimum-Component Astable                            | 115 |

|------|------------------------------------------------------|-----|

| 5.2  | Improved Minimum-Component Astable                   | 116 |

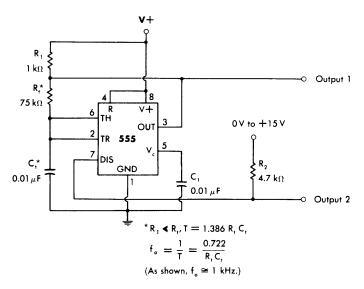

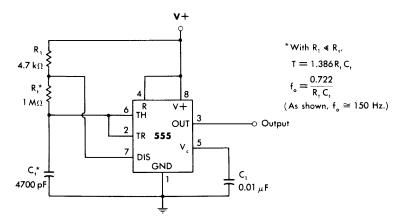

| 5.3  | Square-Wave Astables                                 | 116 |

| 5.4  | Square-Wave Astables With Extended Range             | 118 |

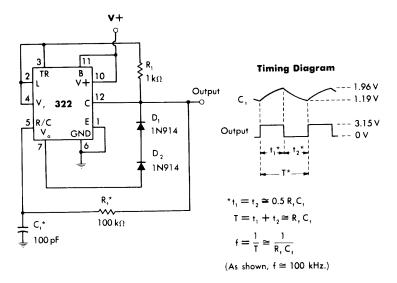

| 5.5  | Type 322 Square-Wave Astable                         | 121 |

| 5.6  | Type 2240 "Guaranteed" Square-Wave Astables          | 123 |

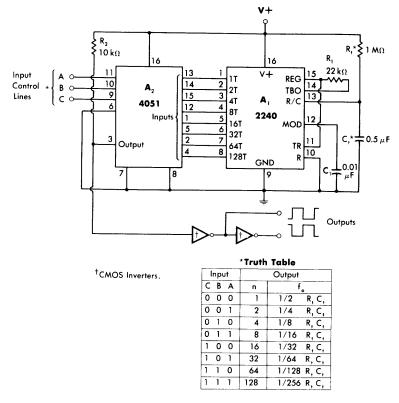

| 5.7  | "Dual One-Shot" Astable                              | 124 |

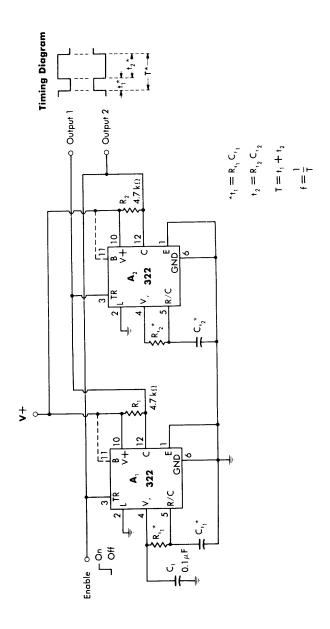

| 5.8  | "Chain" Astable                                      | 125 |

| 5.9  | Extending Control Over the Timing Periods of the 555 | 128 |

| 5.10 | Simplified Astable                                   | 134 |

| 5.11 | Gated Simplified Astable                             | 135 |

| 5.12 | Selectable-Frequency Astable                         | 136 |

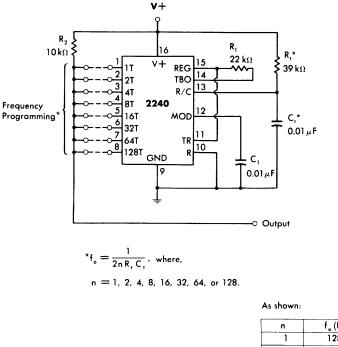

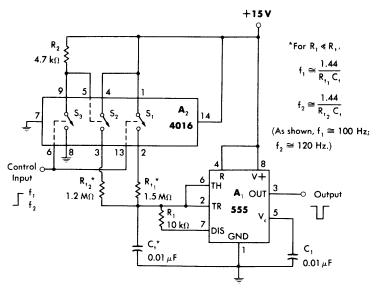

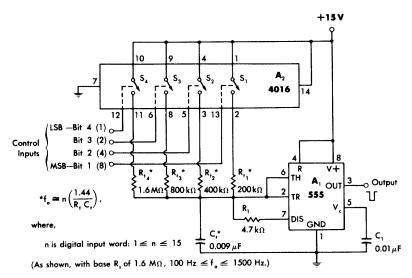

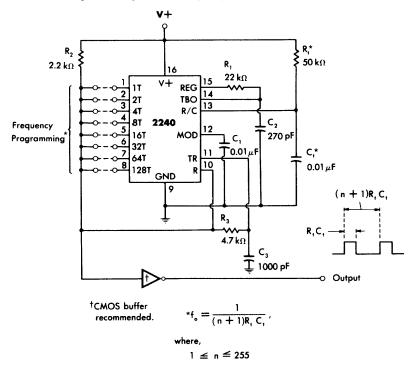

| 5.13 | Programmable-Frequency Astables                      | 137 |

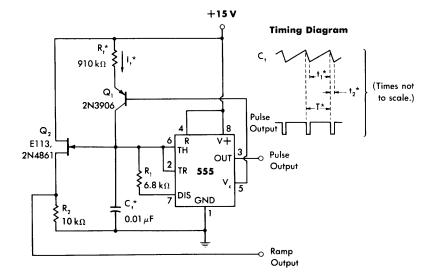

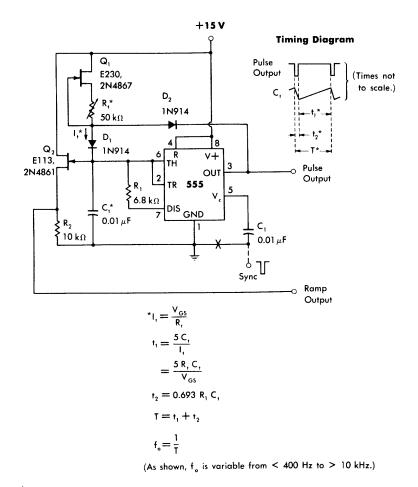

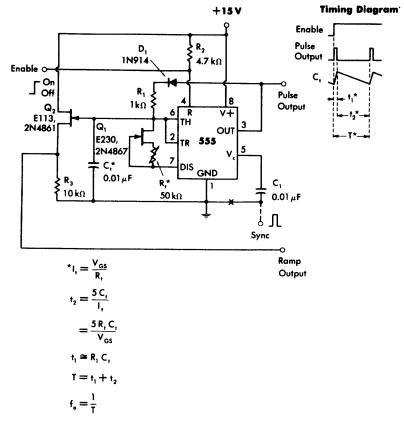

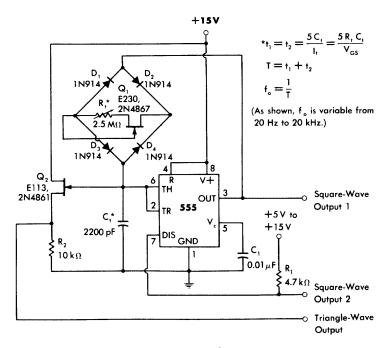

|      | Linear-Ramp Astables                                 | 139 |

#### CHAPTER 6

| IC | Тімн | ER SYSTEMS APPLICATIONS             |   |   |   |   |   |   |       | 147 |

|----|------|-------------------------------------|---|---|---|---|---|---|-------|-----|

|    | 6.1  | Using Timers for Logic Functions    |   |   |   |   |   |   | . 147 |     |

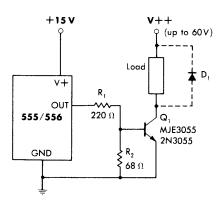

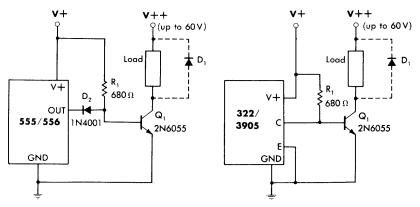

|    | 6.2  | Output Drive Circuits               |   |   |   |   |   |   | . 158 |     |

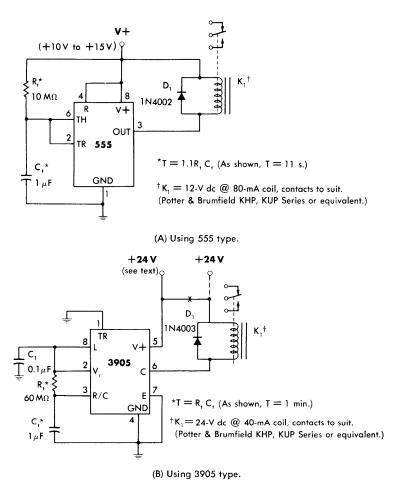

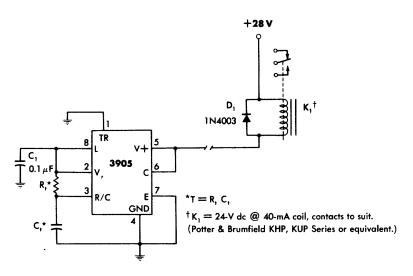

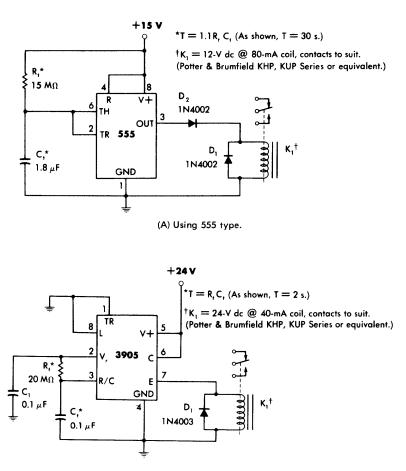

|    | 6.3  | Time-Delay Relay Circuits           |   |   |   |   |   |   | . 164 |     |

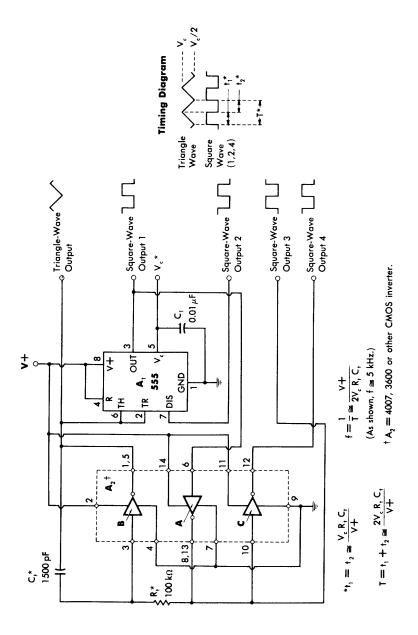

|    | 6.4  | Function Generators                 |   |   |   |   |   |   |       |     |

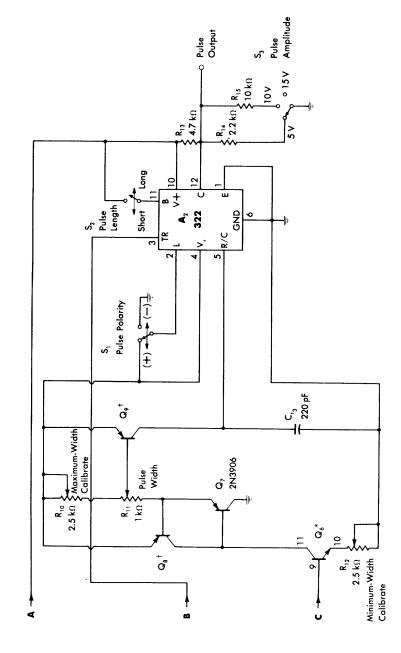

|    | 6.5  | Wide-Range Pulse Generator .        |   |   |   |   |   |   | . 180 |     |

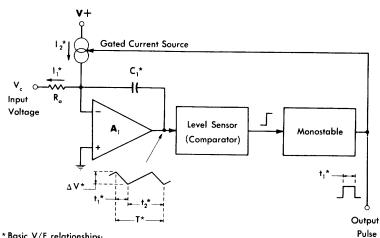

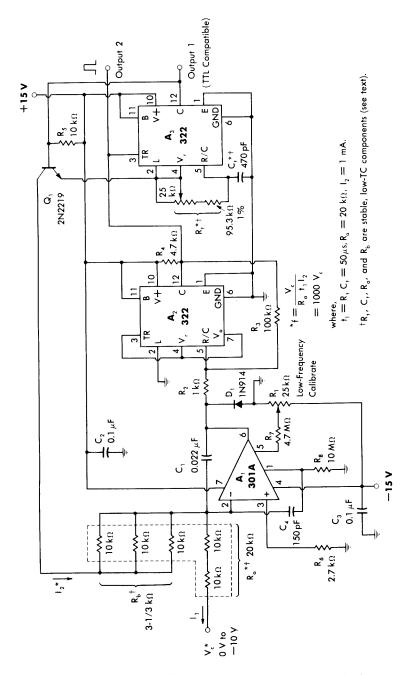

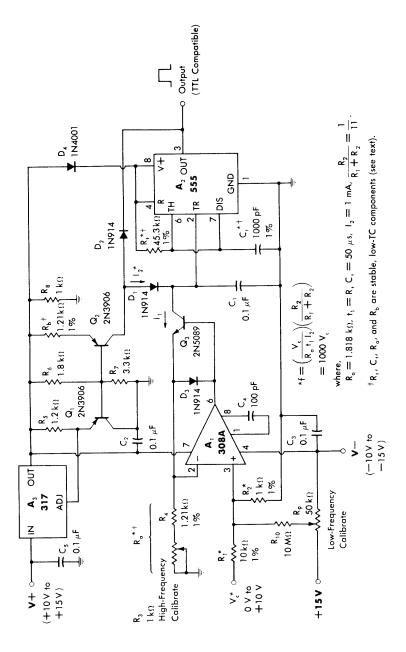

|    | 6.6  | Voltage-to-Frequency Converters     |   |   |   |   |   |   |       |     |

|    | 6.7  | Frequency-to-Voltage Converters .   |   |   |   |   |   |   | . 192 |     |

|    | 6.8  | DC/DC Converters                    |   |   |   |   |   |   |       |     |

|    | 6.9  | Freewheeling, Power-Fail Oscillator |   |   |   |   |   |   |       |     |

|    | 6.10 | Sine-Wave/Square-Wave Oscillator    |   |   |   |   |   |   | . 203 |     |

|    | 6.11 | More-Precise Clock Sources          |   |   |   |   |   |   | . 204 |     |

|    |      | Universal Appliance Timer           |   |   |   |   |   |   | . 214 |     |

|    |      | Time-Mark Generator                 |   |   |   |   |   |   |       |     |

|    | 6.14 | Phase-Locked Loops                  |   |   | • |   |   |   | . 220 |     |

|    | 6.15 | Bipolar Staircase Generator         |   |   |   |   |   |   | . 224 |     |

|    |      | A/D Converter                       |   |   |   |   | • |   | . 226 |     |

|    | 6.17 | Speed Alarm                         |   |   | • |   |   |   |       |     |

|    |      |                                     |   |   | • |   | • |   | . 230 |     |

|    |      | Burglar Alarm                       |   |   |   |   |   |   | . 231 |     |

|    | 6.20 | Alarm Indicators                    | • | • | • | • | • | • | . 232 |     |

|    |      |                                     |   |   |   |   |   |   |       |     |

## Part III–Appendixes

#### APPENDIX A

| MANUFACTURERS' DATA SHEETS           | •  | • | <br>• | <br> | • | 239 |

|--------------------------------------|----|---|-------|------|---|-----|

| APPENDIX                             | В  |   |       |      |   |     |

| Second-Source Guide                  |    | • | <br>• | <br> |   | 267 |

| APPENDIX                             | С  |   |       |      |   |     |

| TIMING COMPONENT MANUFACTURERS .     |    |   |       | <br> |   | 271 |

|                                      | D  |   |       |      |   |     |

| BIBLIOGRAPHY OF IC TIMER DESIGN IDE. | AS | • |       | <br> |   | 275 |

| Index                                |    | • |       | <br> | • | 281 |

## INTRODUCING THE IC TIMER

## 1

### **RC Timer Basics**

The best place to begin a discussion of RC timing circuits is with the basic theory of their operation. By absorbing this fundamental knowledge, we will be better prepared to deal with actual IC devices in practical designs.

#### 1.1 THE MONOSTABLE RC TIMER

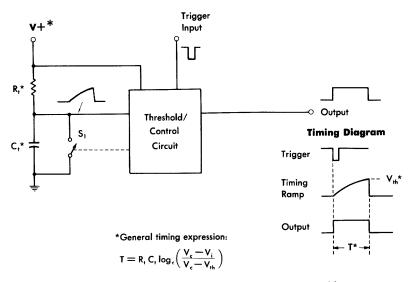

The basic operation of a monostable RC timer is illustrated in block diagram form in Fig. 1-1. There are four separate components that make up this timer: a timing resistor  $(R_t)$ , a timing capacitor  $(C_t)$ , a switch  $(S_1)$ , and a threshold/control circuit. The circuit operates as follows:

In its untriggered or quiescent condition, the timer output is low or near zero, and switch  $S_1$  is "on," clamping capacitor  $C_t$  to ground. Upon the arrival of a trigger pulse at the input, the control circuit causes switch  $S_1$  to open and causes the output to switch to a high level. The timer is now in its unstable state (i.e., the timing period has begun).

With  $S_1$  now open, capacitor  $C_t$  will start to charge through resistor  $R_t$ . This causes the voltage across  $C_t$  to rise exponentially, forming a timing ramp (see the timing diagram in Fig. 1-1). This voltage continues to rise until it reaches the threshold voltage,  $V_{th}$ , which is a voltage that is some fraction of V+. When the timing-ramp voltage reaches  $V_{th}$ , the threshold circuit is then reset, the output falls to zero, and the monostable has timed out. The circuit has now returned to its standby (or stable) state.

The output pulse of a monostable timing circuit is said to have a pulse width, T, which is its timing period. This timing period is re-

Fig. 1-1. Block diagram illustrating the basic operation of a monostable RC timer.

lated to  $R_t$ ,  $C_t$ , the charging voltage (which in general is  $V_c$ ; here it is V+), and the threshold voltage,  $V_{th}$ . The general expression for T is simply

$$\mathrm{T} = \mathrm{R_t}\mathrm{C_t}\mathrm{log}_\epsilon \left( rac{\mathrm{V_c} - \mathrm{V_i}}{\mathrm{V_c} - \mathrm{V_{th}}}

ight)$$

,

where  $V_c$  is the charging voltage, and  $V_i$  is the initial voltage on  $C_t$ . Since  $C_t$  starts at an initial voltage of zero, we can simplify the expression for this specific case and also substitute V+ for  $V_c$ . The new expression is

$$T = R_t C_t \log_{\epsilon} \left( \frac{V+}{(V+) - V_{th}} \right).$$

In this generalized example we have, for the sake of simplicity, purposely avoided any specific references to actual resistor or capacitor values. And, although an example of a positive source voltage (V+) was shown, in theory we could just as well have a negative supply, a negative ramp, a negative  $V_{\rm th}$ , etc.

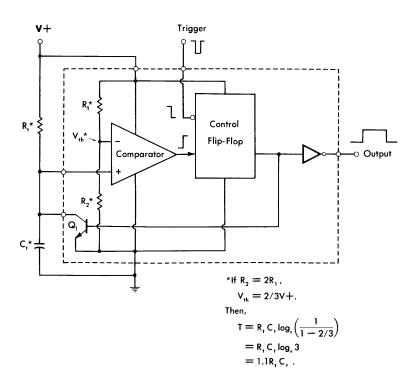

Fig. 1-2 illustrates how an actual circuit could be connected to implement this monostable timer. Here  $R_t$  and  $C_t$  are as they were in Fig. 1-1, but  $S_1$  is replaced by a transistor switch,  $Q_1$ . The function of  $Q_1$  is to short  $C_t$  in the standby state, and to open during the timing period. The control function is implemented by a flip-flop, whose output is to be the monostable timing pulse of width T. This flip-flop also controls transistor  $Q_1$ ;  $Q_1$  is "on" when the output is low, and is

Fig. 1-2. Circuit implementation of the basic monostable RC timer.

"off" when the output is high. The threshold function is performed by the comparator and the voltage divider,  $R_1-R_2$ . The voltage divider is connected across V+ (the supply line), and its output voltage is V<sub>th</sub>, the threshold voltage. The output of the comparator will change states when the timing ramp is equal to V<sub>th</sub>.

The sequence of operation of this circuit is precisely as described before, but a deeper appreciation of it may be gained from an example of operation. For instance, if resistors  $R_2$  and  $R_1$  are chosen to have a ratio of 2:1 ( $R_2 = 2R_1$ ), the voltage divider output of  $V_{\rm th}$ will be 2/3 of V+. With this fact in mind, we can write a specific equation for period T. All the voltages can be expressed in terms of V+, since  $V_{\rm th} = 2/3$ V+. We then write

$$\mathbf{T} = \mathbf{R}_{t}\mathbf{C}_{t}\log_{\epsilon}\left(\frac{\mathbf{V}+}{(\mathbf{V}+)-2/3\mathbf{V}+}\right),$$

which simplifies to

$$\mathbf{T} = \mathbf{R}_{\mathsf{t}} \mathbf{C}_{\mathsf{t}} \log_{\epsilon} \left( \frac{1}{1 - 2/3} \right),$$

$$T = R_t C_t \log_{\epsilon} 3$$

= 1.0986 R\_t C\_t.

We can then round this off to  $T = 1.1R_tC_t$ , which is the basic equation for the period of a monostable timer having a threshold voltage that is 2/3 of the charging voltage.

One interesting thing to note about this type of circuit is that the period is not dependent upon the absolute level of V+, because  $V_{th}$  is derived as a fraction of V+. Mathematically speaking, it can be said that the V+ term divides out. Electrically speaking, it can be said that the capacitor is both charged from and compared to a fixed fraction of the same voltage. Either way it is an important advantage (as we will soon see) to have a basic timing equation that does not critically depend upon the supply voltage.

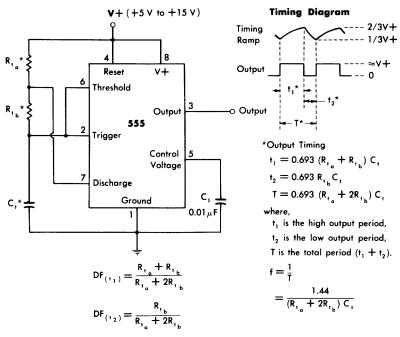

#### 1.2 THE ASTABLE RC TIMER

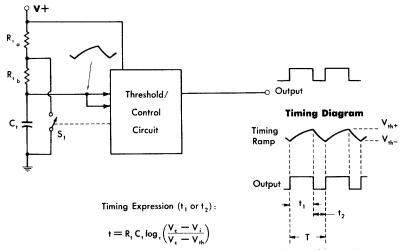

The astable RC timer is shown in block diagram form in Fig. 1-3. Note that this diagram is in many ways similar to Fig. 1-1; it does, however, have two timing resistors and two threshold connections since there are two threshold levels associated with this type of circuit. The two thresholds are the voltage levels  $V_{th+}$  and  $V_{th-}$ . Voltage  $V_{th+}$  is some fraction of the supply voltage, while  $V_{th-}$  is a smaller fraction of the same supply voltage. This is just another way of saying that  $V_{th+}$  is more positive than  $V_{th-}$ , a necessary condition for circuit operation. Operation of the circuit is as follows:

Fig. 1-3. Block diagram illustrating the basic operation of an astable RC timer.

or

At the beginning, assume switch  $S_1$  to be open. In this state, the output will be high and capacitor  $C_t$  will charge toward V+ through resistors  $R_{t_a}$  and  $R_{t_b}$ . This portion of the cycle is somewhat similar to that described previously in the case of the monostable timer. When the timing ramp across  $C_t$  reaches the voltage level of  $V_{th+}$ , the circuit changes states. The output now goes low, which causes switch  $S_1$  to close. With  $S_1$  closed, the  $R_{t_a}$ - $R_{t_b}$  node is grounded, which places  $R_{t_b}$  in parallel with  $C_t$ , and effectively removes  $R_{t_a}$  from the circuit.  $C_t$  now begins to discharge through  $R_{t_b}$ , and the timing ramp decays exponentially toward ground. When the voltage across  $C_t$  reaches the lower threshold of  $V_{th-}$ , the circuit once again will revert to its high output state, with  $S_1$  opening and  $C_t$  charging toward V+.

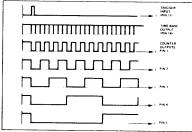

The circuit will continue to oscillate between the two threshold voltage points of  $V_{th+}$  and  $V_{th-}$ , with the output changing state with each threshold crossing. Referring to the timing diagram in Fig. 1-3, the positive-going timing period is termed  $t_1$ , and the output is high during this period. The negative-going timing period is  $t_2$ , and the output is low during this period. The total timing period of a single cycle is called T, which is simply the sum of the individual timing periods,  $t_1$  and  $t_2$ . For each of the two timing periods, the general expression will again be

$$\mathbf{t} = \mathbf{R}_{t} \mathbf{C}_{t} \log_{\epsilon} \left( \frac{\mathbf{V}_{e} - \mathbf{V}_{i}}{\mathbf{V}_{e} - \mathbf{V}_{th}} \right).$$

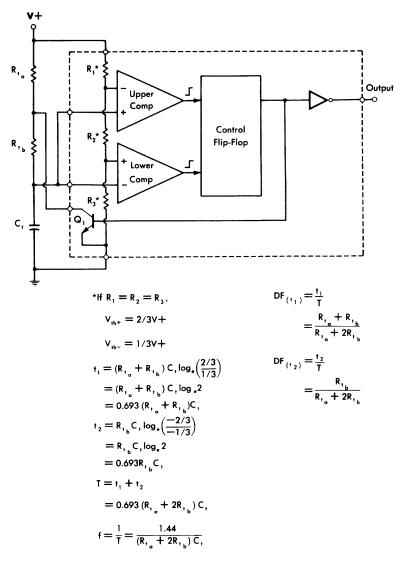

A circuit implementation of this astable timer is illustrated in Fig. 1-4. Here we note that there are two comparators, the upper comp and the lower comp. These comparators establish the two threshold voltages,  $V_{th+}$  and  $V_{th-}$ , as the fractions of V+ determined by the divider resistor string,  $R_1-R_2-R_3$ . The upper comp is referenced to the higher voltage,  $V_{th+}$ . The lower comp is referenced to the lower voltage,  $V_{th-}$ . Transistor  $Q_1$  performs a function similar to that of switch  $S_1$  in Fig. 1-3, while the control flip-flop drives  $Q_1$  and the output buffer as directed by the comparator inputs.

In operation, the circuit performs just as described for Fig. 1-3, with an output and timing ramp in accordance with the timing diagram. The voltage across  $C_t$  is made to oscillate between the two comparator thresholds,  $V_{th+}$  and  $V_{th-}$ .  $R_{t_a} + R_{t_b}$  and  $C_t$  control timing period  $t_1$ , while  $R_{t_b}$  and  $C_t$  control timing period  $t_2$ . The general timing expression for either of these periods is as noted in Fig. 1-3. In this case, with comparator thresholds  $V_{th+} = 2/3V_{+}$  and  $V_{th-} = 1/3V$ , the equations for  $t_1$  and  $t_2$  are as follows:

For  $t_i$ , the voltage across  $C_t$  starts at a voltage of  $V_{th-}$  (which is  $V_i$ ), charges toward V+ (which is  $V_c$ ), and reaches its upper limit at  $V_{th+}$ . Then,

轡

Fig. 1-4. Circuit implementation of the basic astable RC timer.

$$\mathbf{t}_{1} = (\mathbf{R}_{t_{a}} + \mathbf{R}_{t_{b}}) \mathbf{C}_{t} \log_{\epsilon} \left( \frac{(\mathbf{V}+) - \mathbf{V}_{th-}}{(\mathbf{V}+) - \mathbf{V}_{th+}} \right).$$

With  $V_{th+}$  and  $V_{th-}$  as fractions of V+ as noted, this may be written as

$$\mathbf{t}_{1} = (\mathbf{R}_{t_{\bullet}} + \mathbf{R}_{t_{\bullet}}) \mathbf{C}_{t} \log_{\epsilon} \left(\frac{2/3\mathrm{V}+}{1/3\mathrm{V}+}\right),$$

which reduces to

$$\begin{aligned} \mathbf{t}_1 &= (\mathbf{R}_{t_a} + \mathbf{R}_{t_b}) \mathbf{C}_t \log_{\epsilon} 2 \\ &= 0.693 (\mathbf{R}_{t_a} + \mathbf{R}_{t_b}) \mathbf{C}_t. \end{aligned}$$

For t<sub>2</sub>, the equations are similar:

$$t_2 = R_{t_b} C_t \log_{\varepsilon} \left( \frac{0 - V_{th+}}{0 - V_{th-}} \right),$$

which simplifies to

$$t_{2} = R_{t_{b}} C_{t} \log_{\epsilon} \left( \frac{-2/3V+}{-1/3V+} \right)$$

=  $R_{t_{b}} C_{t} \log_{\epsilon} 2$

= 0.693  $R_{t_{b}} C_{t}$ .

The total period, T, is simply the sum of periods  $t_1$  and  $t_2$ , or

$$\begin{split} \Gamma &= t_1 + t_2 \\ &= 0.693 \; (R_{t_a} + R_{t_b}) \; C_t + 0.693 \; R_{t_b} \; C_t \\ &= 0.693 \; (R_{t_a} + 2R_{t_b}) \; C_t. \end{split}$$

Since time and frequency are related reciprocally, we can now also write an equation for the operating frequency, f:

$$\begin{split} f &= \frac{1}{T} \\ &= \frac{1}{0.693 (R_{t_a} + 2R_{t_b}) C_t} \\ &= \frac{1.44}{(R_{t_a} + 2R_{t_b}) C_t} \,. \end{split}$$

The ratio of the individual periods  $(t_1 \text{ or } t_2)$  to the total period is called the duty factor, DF. With respect to period  $t_1$ , the duty factor is

$$DF_{(t_i)} = \frac{t_i}{T}$$

$$= \frac{R_{t_a} + R_{t_b}}{R_{t_a} + 2R_{t_b}},$$

and for period t<sub>2</sub>, the duty factor is

$$DF_{(t_{u})} = \frac{t_{2}}{T}$$

$$= \frac{R_{t_{b}}}{R_{t_{a}} + 2R_{t_{b}}}.$$

17

In summary, there are a number of important features that characterize the astable RC timer. The timing period is governed by  $C_t$  and resistors  $R_{t_a}$  and  $R_{t_b}$ , as is the operating frequency. The duty cycle is controlled by the ratio of timing resistors. And, for this type of timer as well as for the monostable, the timing period is independent of the supply voltage.

What has been described in this chapter is a concept that allows (in theory at least) a very simple and predictable form of monostable and/or astable timer design based only on R and C values to define operation. With this groundwork, we are now ready to examine IC timer types and their modes of operation.

## **IC Timer Types**

The first chapter, while not an all-encompassing treatise on RC timing circuits, does provide sufficient background for the understanding of those ICs that use the principles outlined. Specifically, these include the 555 general-purpose timer and also others based either wholly or in part on its operating theory. In this chapter, we begin a more detailed examination of the internal workings of the 555. This examination, in conjunction with the first chapter, will lay a foundation for the entire book.

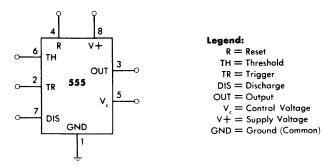

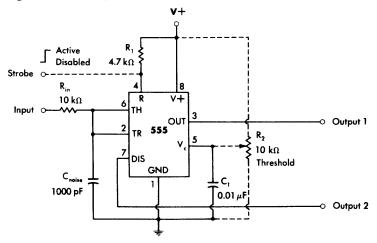

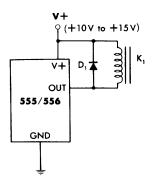

#### 2.1 THE 555 SINGLE-UNIT GENERAL-PURPOSE TIMER

The NE555 timer, manufactured by Signetics, was not only the first IC timer introduced (in 1972), but also the trendsetter for most of the devices that have been designed since. The 555 is a general-purpose unit, capable of both the monostable and astable operating modes over wide ranges. Actually, the operating principles of the 555 are the same as those described in Chapter 1, with but few differences in practice. Most manufacturers supply the 555 in both the 8-lead TO-99 metal can and the 8-pin dual in-line (MINIDIP) packages, while some manufacturers also offer the unit in a 14-pin dual in-line (DIP) package.

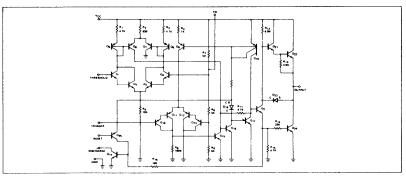

#### 2.1.1 Functional Diagram and Schematic

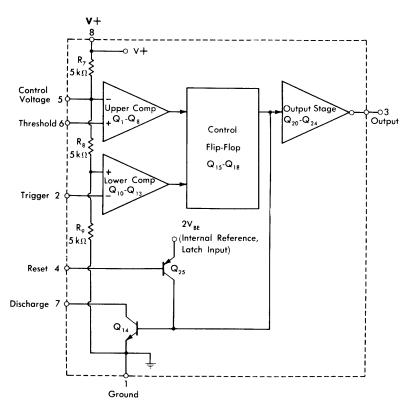

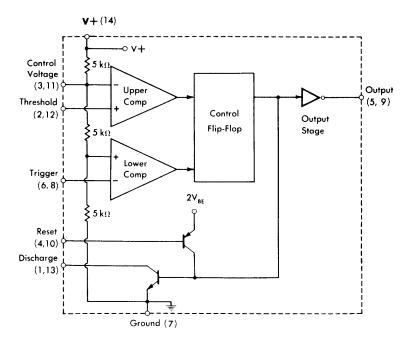

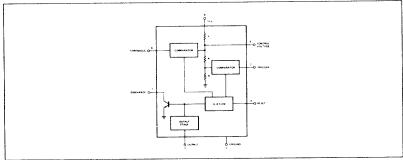

The 555 timer can be functionally diagrammed as shown in Fig. 2-1. The reader will note a similarity to the circuit diagram of Fig. 1-4. In actuality, the basic theory of the 555 has already been explained. The implementation of the various circuit functions within the device will now be described.

Fig. 2-1. Functional block diagram of the 555 timer.

In Fig. 2-1, note the resistive divider string across the V+ line comprising equal-value resistors  $R_7$ ,  $R_8$ , and  $R_9$ . This voltage divider provides the reference voltages for the upper and lower comparators of 2/3V+ and 1/3V+, respectively. In the schematic<sup>•</sup> of Fig. 2-2, this divider may also be noted, biasing  $Q_4$  and  $Q_{13}$ . Transistors  $Q_1-Q_8$  make up the upper comparator, while  $Q_{10}-Q_{13}$  form the lower comparator. In both comparators, Darlington differential input stages are used for low (100 nA) input currents, which in turn allows a wide range of (external) timing resistor values to be used. The upper comparator point of 2/3V+ is brought outside the IC package (via pin 5) to allow external control of the timing period (when desired).

<sup>&</sup>lt;sup>o</sup> Some variation in internal circuitry is evident between different manufacturers of 555 devices; therefore, reference designations and exact circuit details may vary from that shown here when compared with a given data sheet.

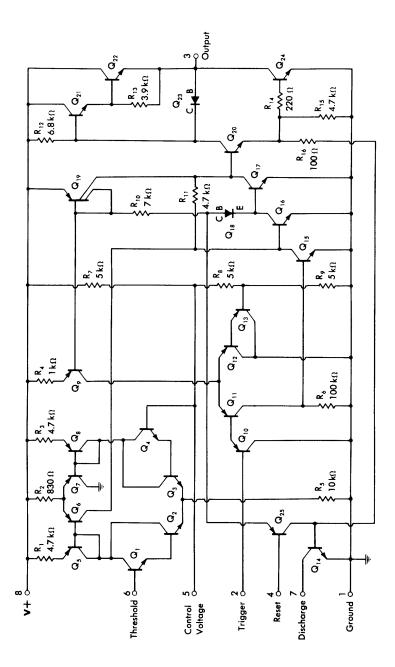

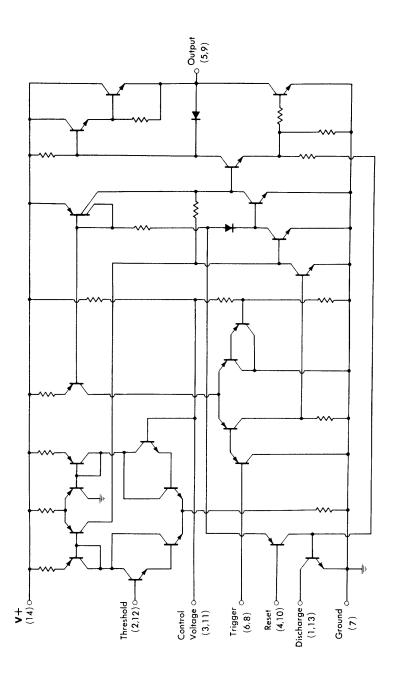

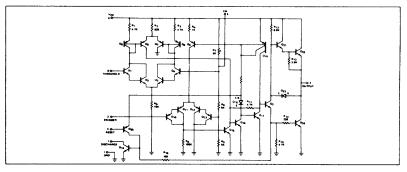

Fig. 2-2. Schematic of the 555 timer.

The two comparator outputs are taken from transistors  $Q_6$  and  $Q_{10}-Q_{11}$ ; these in turn are fed to the control flip-flop, which is a latch formed by  $Q_{16}-Q_{17}$  ( $Q_{18}$  is an additional input whose function will be described shortly). In operation, a low input to the trigger pin (base of  $Q_{10}$ ) causes a positive-going output from  $Q_{10}-Q_{11}$ . This causes the latch to be set by pulling the collector of  $Q_{15}$  low. This then causes  $Q_{17}$  (and the input to  $Q_{20}$  and  $Q_{24}$ ) to also go low, and the output (pin 3) to go high. This set condition of the latch will remain until the circuit is reset.

To reset the flip-flop back to its original state, either of two conditions can be satisfied. If the output of  $Q_6$  goes high, the latch will be reset via the input to the base of  $Q_{16}$ , removing drive from  $Q_{17}$ . The latch may also be reset by taking the base of  $Q_{25}$  low, via the reset input (pin 4). This removes base drive from  $Q_{17}$  by biasing diodeconnected  $Q_{18}$  "off." Regardless of the method, the reset state turns  $Q_{20}$  (and  $Q_{24}$ ) "on" once again, causing an output-low condition.

The output stage formed by  $Q_{20}-Q_{24}$  is a totem-pole design, which has the virtue of being a high current drive for either source or sink

Courtesy Signetics Corp.

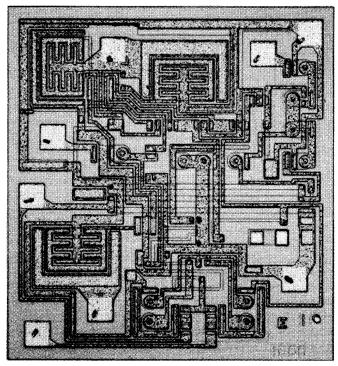

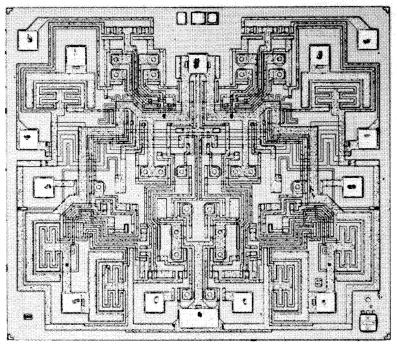

Fig. 2-3. Photomicrograph of the 555 silicon chip.

loads. This design is a versatile one, as it can readily drive TTL inputs with a chip supply of 5 volts, yet it can also sink or source 200 mA when operated from 15 volts. A photomicrograph of the 555 silicon chip layout is shown in Fig. 2-3.

#### 2.1.2 Definition of Pin Functions

As an aid to understanding the 555 more completely, this section provides a short description of the functional characteristics of each pin. This not only will serve as an aid to understanding the use of the 555 as a timer, but will also greatly facilitate its use in some of the more imaginative nontimer uses of which it is capable. To amplify this discussion, the reader is referred to the 555 data sheet reproduced in Appendix A.

#### V+ (Pin 8)

The V+ pin (referred to as  $V_{CC}$  by some manufacturers) is the positive supply voltage terminal of the device. Supply-voltage operating range for the 555 is +4.5 volts (minimum) to +16 volts (maximum), and it is specified for operation between +5 volts and +15 volts. The device will operate essentially the same over this range of voltages without change in timing period. Actually, the most significant operational difference is the output drive capability, which increases for both current and voltage range as the supply voltage is increased. Sensitivity of time interval to supply voltage change is low, typically 0.1% per volt.

#### Ground (Pin 1)

The ground (or common) pin is the most-negative supply potential of the device, which is normally connected to circuit common when operated from positive supply voltages.

#### Output (Pin 3)

The output of the 555 comes from a high-current totem-pole stage made up of transistors  $Q_{20}$ - $Q_{24}$ . Transistors  $Q_{21}$  and  $Q_{22}$  provide drive for source-type loads, and their Darlington connection provides a high-state output voltage about 1.7 volts less than the V+ supply level used. Transistor  $Q_{24}$  provides current-sinking capability for low-state loads referred to V+ (such as typical TTL inputs). Transistor  $Q_{24}$  has a low saturation voltage, which allows it to interface directly, with good noise margin, when driving current-sinking logic. Exact output saturation levels vary markedly with supply voltage, however, for both high and low states. At a V+ of 5 volts, for instance, the low state  $V_{CE (sat)}$  is typically 0.25 volt at 5 mA. Operating at 15 volts, however, it can sink 100 mA if an output-low voltage level of 2 volts is allowable (power dissipation should be considered in such a case, of course). High-state level is typically 3.3 volts at V + = 5 volts; 13.3 volts at V + = 15 volts. Both the rise and fall times of the output waveform are quite fast, typical switching times being 100 ns.

The state of the output pin will always reflect the inverse of the logic state of the latch, and this fact may be seen by examining Fig. 2-1 (or Fig. 2-2). Since the latch itself is not directly accessible, this relationship may be best explained in terms of latch-input trigger conditions. To trigger the output to a high condition, the trigger input is momentarily taken from a higher to a lower level. [The exact voltage levels are discussed under "Trigger (Pin 2)."] This causes the latch to be set and the output to go high. Actuation of the lower comparator is the only manner in which the output can be placed in the high state. The output can be returned to a low state by causing the threshold to go from a lower to a higher level [exact levels are discussed under "Threshold (Pin 6)"], which resets the latch. The output can also be made to go low by taking the reset to a low state near ground [exact levels are discussed under "Reset (Pin 4)"].

#### Control Voltage (Pin 5)

This pin allows direct access to the 2/3V+ voltage-divider point, the reference level for the upper comparator. It also allows indirect access to the lower comparator, as there is a 2:1 divider ( $R_8-R_9$ ) from this point to the lower-comparator reference input,  $Q_{13}$ . Use of this terminal is the option of the user, but it does allow extreme flexibility by permitting modification of the timing period, resetting of the comparator, etc.

When the 555 timer is used in a voltage-controlled mode, its voltage-controlled operation ranges from about 1 volt less than V+ down to within 2 volts of ground (although this is not guaranteed). Voltages can be safely applied outside these limits, but they should be confined within the limits of V+ and ground for reliability.

In the event the control-voltage pin is not used, it is recommended that it be bypassed with a capacitor of about 0.01  $\mu$ F for immunity to noise, since it is a comparator input.

#### Trigger (Pin 2)

This pin is the input to the lower comparator and is used to set the latch, which in turn causes the output to go high. This is the beginning of the timing sequence in monostable operation. Triggering is accomplished by taking the pin from above to below a voltage level of 1/3V+ (or, in general, one-half the voltage appearing at pin 5). The action of the trigger input is level-sensitive, allowing slow rate-of-change waveforms, as well as pulses, to be used as trigger sources. One precaution that should be observed with the trigger input signal is that it must not remain lower than 1/3V+ for a period of time *longer* than the timing cycle. If this is allowed to happen, the timer will retrigger itself upon termination of the first output pulse. Thus, when the timer is driven in the monostable mode with input pulses longer than the desired output pulse width, the input trigger should effectively be shortened by differentiation.

The minimum-allowable pulse width for triggering is somewhat dependent upon pulse level, but in general if it is greater than 1  $\mu$ s, triggering will be reliable (see data sheet in Appendix A).

A second precaution with respect to the trigger input concerns storage time in the lower comparator. This portion of the circuit can exhibit normal turn-off delays of several microseconds after triggering; that is, the latch can still have a trigger input for this period of time *after* the trigger pulse. In practice, this means the minimum monostable output pulse width should be on the order of 10  $\mu$ s to prevent possible double triggering due to this effect.

The voltage range that can safely be applied to the trigger pin is between V+ and ground. A dc current, termed the *trigger* current, must also flow from this terminal into the external circuit. This current is typically 500 nA and will define the upper limit of resistance allowable from pin 2 to ground. For an astable configuration operating at V+ = 5 volts, this resistance is 3 M $\Omega$ ; it can be greater for higher V+ levels.

#### Threshold (Pin 6)

This pin is one input to the upper comparator (the other being pin 5) and is used to reset the latch, which causes the output to go low. Resetting via this terminal is accomplished by taking the terminal from below to above a voltage level of 2/3V+ (the normal voltage on pin 5). The action of the threshold pin is level sensitive, allowing slow rate-of-change waveforms.

The voltage range that can safely be applied to the threshold pin is between V+ and ground. A dc current, termed the *threshold* current, must also flow into this terminal from the external circuit. This current is typically 100 nA, and will define the upper limit of total resistance allowable from pin 6 to V+. For either timing configuration operating at V+ = 5 volts, this resistance is 16 M $\Omega$ .

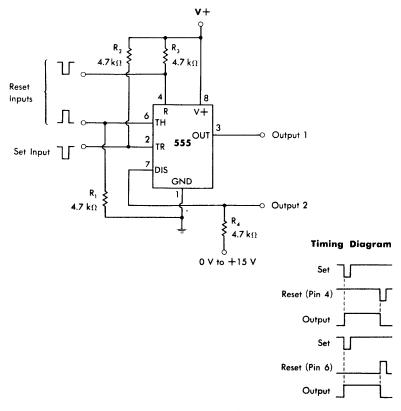

#### Reset (Pin 4)

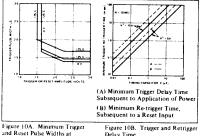

This pin is also used to reset the latch and return the output to a low state. The reset voltage threshold level is 0.7 volt, and a sink current of 0.1 mA from this pin is required to reset the device. These levels are relatively independent of operating V+ level; thus the reset input is TTL compatible for any supply voltage. The reset input is an overriding function; that is, it will force the output to a low state regardless of the state of either of the other inputs. It may thus be used to terminate an output pulse prematurely, to gate oscillations from "on" to "off," etc. Delay time from reset to output is typically on the order of 0.5  $\mu$ s, and the minimum reset pulse width is 0.5  $\mu$ s. Neither of these figures are guaranteed, however, and may vary from one manufacturer to another. When not used, it is recommended that the reset input be tied to V+ to avoid any possibility of false resetting.

#### Discharge (Pin 7)

This pin is the open collector of an npn transistor ( $Q_{14}$ , Fig. 2-2), the emitter of which goes to ground. The conduction state of this transistor is identical in timing to that of the output stage. It is "on" (low resistance to ground) when the output is low and "off" (high resistance to ground) when the output is high.

In both the monostable and astable timer modes, this transistor switch is used to clamp the appropriate nodes of the timing network to ground. Saturation voltage is typically below 100 mV for currents of 5 mA or less, and off-state leakage is about 20 nA (these parameters are not specified by all manufacturers, however).

Maximum collector current is internally limited by design, thereby removing restrictions on capacitor size due to peak pulse-current discharge. In certain applications, this open collector output can be used as an auxiliary output terminal, with current-sinking capability similar to the output (pin 3).

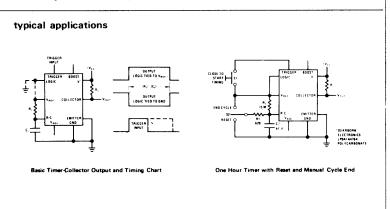

#### 2.1.3 Basic Operating Modes

With the definition and functional description of the 555 timer just completed, we have now reached a point where the basic modes of operation of the device can be discussed in more detail. In essence, this amounts to only two modes: the monostable (or one-shot) mode and the astable (or free-running) mode. Both of these modes of operation have been discussed at length in conceptual terms; this section relates the practical operating points of the 555 to the previous material.

The two basic operating modes have a great number of variations; these are treated as specific design examples within the applications section (Part II). The 555, being such a versatile device, also has a virtually limitless number of possible operating options not necessarily directly related to the monostable and astable modes. These are much more difficult to categorize, but they will also in some way be dependent upon the internal structure just described. These more esoteric operating modes are also treated as specific design examples in the applications section.

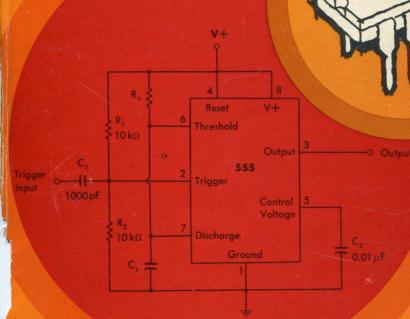

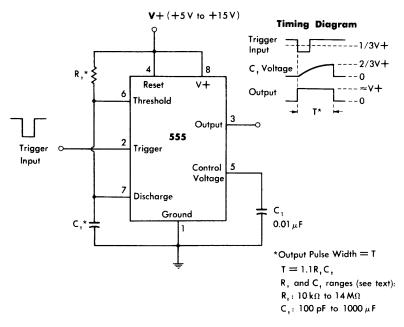

Fig. 2-4. The 555 timer connected as a triggered monostable—its most basic mode of operation.

#### **Monostable Mode**

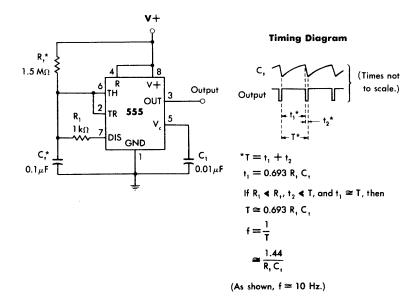

In Fig. 2-4, the 555 is shown connected in its most basic mode of operation—as a triggered monostable. One immediate observation to be made is the utter simplicity of this circuit; it consists of only the two timing components,  $R_t$  and  $C_t$ ; the timer itself; and bypass capacitor  $C_1$  ( $C_1$  is not absolutely essential for operation but is recommended for noise immunity).

When the trigger input terminal is held higher than 1/3V+, the timer is in its standby state and the output is low. When a trigger pulse appears with a level less than 1/3V+, the timer is triggered and starts its timing cycle. The output rises to a high level near V+; at the same time C<sub>t</sub> begins to charge toward V+. When the C<sub>t</sub> voltage crosses 2/3V+, the timing period ends with the output falling once again to zero, ready for another input trigger. This action is graphically illustrated in the timing diagram of Fig. 2-4.

In this most simple circuit it should be noted that there are no trigger input conditioning components used. The implication of this is that the driving source in itself must be capable of satisfying the trigger voltage requirements. If the timer is operated from +5 volts in a TTL system, for instance, the input drive will automatically be TTL compatible since 1/3V + = 1.6 volts, which is centered in the

TTL output swing. Under this type of condition there are no restrictions on the input pulse, other than that it have a width of less than T. (Other forms of drive can be dealt with also, and will be covered later.) Due to the internal latching mechanism, the timer will always time out once triggered, regardless of any subsequent noise (such as bounce) on the input trigger. This factor is a great asset in interfacing the 555 with noisy sources.

The output pulse width is defined as  $1.1R_tC_t$ , and with relatively few restrictions,  $R_t$  and  $C_t$  can have a wide range of values. There is actually no theoretical upper limit on T, only practical ones. The lower limit is 10  $\mu$ s. You may then consider the range of T to be 10  $\mu$ s to infinity, bounded only by R and C limits. Techniques covered in a later section of this chapter will illustrate how T can be effectively multiplied by virtually any number to achieve periods of days, weeks, and even months if desired.

A reasonable lower limit for  $R_t$  is on the order of 10 k $\Omega$ , mainly from the standpoint of power economy. (Although  $R_t$  can be lower than 10 k $\Omega$  without harm, there is no need for this from the standpoint of achieving a short pulse width.) A practical minimum for  $C_t$ is about 100 pF; below this the effects of stray capacitance become noticeable, limiting accuracy and predictability. Since it is obvious that the product of these two minimums yields a T that is less than 10  $\mu$ s, there is much flexibility in the selection of  $R_t$  and  $C_t$ . Usually  $C_t$  is selected first to minimize size (and expense); then  $R_t$  is chosen.

The upper limit for  $R_t$  is on the order of 13 M $\Omega$  but should be less than this if all of the accuracy of which the 555 is capable is to be achieved. The absolute upper limit of  $R_t$  is determined by the threshold current plus the discharge leakage when the operating voltage is +5 volts. For example, with a threshold plus leakage current of 120 nA, this gives a maximum value of 14 M $\Omega$  for  $R_t$  (even this value may be optimistic). Also, if the  $C_t$  leakage current is such that the sum of the threshold current and the leakage current is in excess of 120 nA, the circuit will never time out because the upper threshold voltage will not be reached. Therefore, it is good practice to select a value for  $R_t$  so that, with a voltage drop of 1/3V+ across it, the current through it will be much larger than the threshold current plus total leakage currents. This current value should be at least 10 times the threshold current plus leakage current. For best accuracy, the value should be 100 times more, if practical.

From the preceding, it should be obvious that the real limit to be placed on  $C_t$  is its leakage, not its capacitance value. In practice, however, this becomes one of capacitance value, since larger-value capacitors have higher leakages as a fact of life. Low-leakage types are available in values up to about 10  $\mu$ F, however, and are preferred for long timing periods. If low-leakage units higher than this can be found, there is no limit from a circuit standpoint to using them, even up to 1000  $\mu$ F.

The ultimate criterion of the components selected for  $R_t$  and  $C_t$  is the degree of accuracy desired (or expected). In general, the selection of  $R_t$  and  $C_t$  is not a trivial task because the inherent precision of the 555 is better than that of most resistors and capacitors. A detailed discussion of the selection rationale for timing components is taken up in Chapter 3, and this should be carefully studied before designs are attempted.

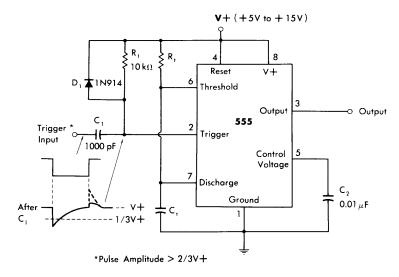

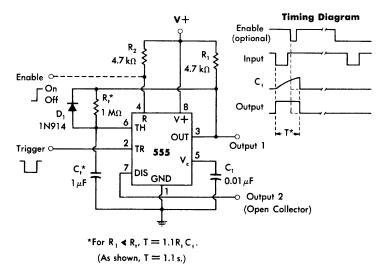

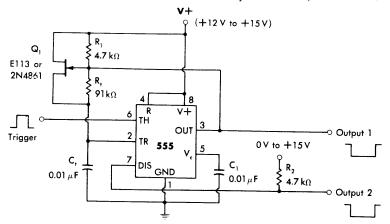

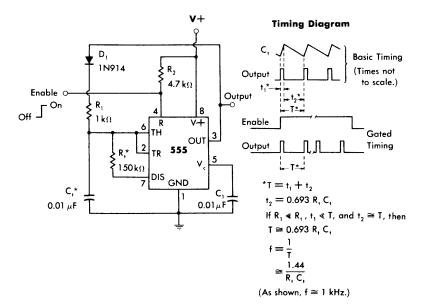

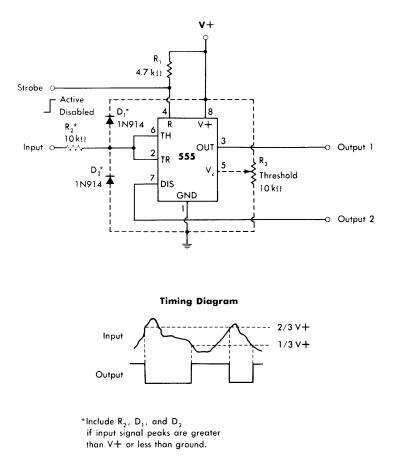

As previously mentioned, input trigger source conditions can exist that will necessitate some type of signal conditioning to ensure compatibility with the triggering requirements of the 555. One example of such a conditioning circuit is shown in Fig. 2-5. Here, input components  $C_1$ ,  $R_1$ , and  $D_1$  have been added, for two reasons.  $C_1$  and  $R_1$ form a pulse differentiator to shorten the input trigger pulse to a width less than 10  $\mu$ s (in general, less than T). Their values (and relative quality) are not critical; the main criterion is that the width of the resulting differentiated pulse (after  $C_1$ ) should be *less* than the desired output pulse for the period of time it is below the 1/3V+trigger level. This effect is shown in the waveform sketch in Fig. 2-5.

The pulse as it exists at the  $R_1-C_1$  junction will rest quiescently at the base line of V+, since  $R_1$  is referred to V+. Therefore, the positive-going edge of the pulse would result in a voltage rise above V+, were it not for  $D_1$ . Diode  $D_1$  is simply a switching diode connected to clamp positive excursions to the V+ level. This circuit will

Fig. 2-5. The basic 555 monostable circuit with input trigger conditioning components added.

operate satisfactorily if the input pulse has the same amplitude as V+ and has a fast fall time.

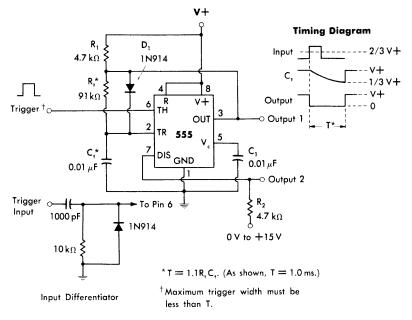

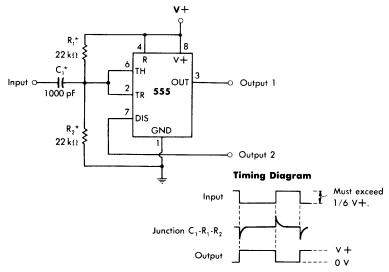

Some further refinement of the input trigger circuit may be necessary if the input pulse has a peak amplitude that is less than the 555 supply voltage. For example, the circuit of Fig. 2-5 will not work when driven from a 5-volt TTL source with a timer V+ of 15 volts, since the 5-volt p-p amplitude is less than 2/3V + (10 volts). In this type of situation, the trigger input can be biased to a level closer to the 1/3V+ threshold, thus increasing sensitivity. Fig. 2-6 illustrates this solution to the problem. Here, resistor R<sub>2</sub> has been added to the previously described differentiator, forming a voltage divider that will have a dc base line of 1/2V+. This biases the trigger input at this level; therefore, the amplitude of the trigger pulse need only be the difference in this dc level and 1/3V+, or simply 1/6V+. In the example mentioned, a 5-volt TTL source with a timer V+ of 15 volts, will work satisfactorily, as the 5-volt p-p amplitude is greater than 1/6 of 15 volts. The exact  $R_1-R_2$  bias level used is not critical and may be adjusted to suit differing input requirements.

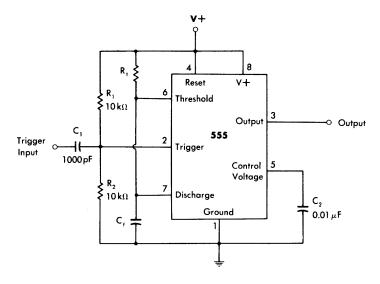

#### Astable Mode

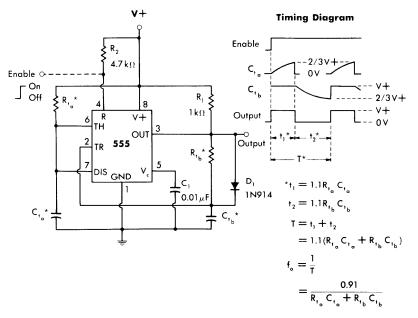

The 555 connected as an astable timer is diagrammed in Fig. 2-7. This circuit also uses a minimum number of parts: the three timing components— $R_{t_a}$ ,  $R_{t_b}$ , and  $C_t$ ; the timer itself; and bypass capacitor  $C_1$ . Upon startup, the voltage across  $C_t$  will be low, which causes

Fig. 2-6. The addition of  $R_2$  improves the sensitivity of the input trigger conditioning circuit.

the timer to be triggered via pin 2. This forces the output high, turning off the discharge transistor and providing a current path for charging  $C_t$  via  $R_{t_a}$  and  $R_{t_h}$ .  $C_t$  charges toward V+ until the voltage reaches a level of 2/3V+, whereupon the upper threshold is reached, causing the output to go low. Capacitor  $C_t$  then discharges toward ground via  $R_{t_b}$  until its voltage reaches 1/3V+, the lower trigger point. This triggers the timer once again, beginning a new cycle. The timer then continues to oscillate between the 2/3V+ and 1/3V+ comparator threshold levels, forming a triangular timing ramp. The

Fig. 2-7. The 555 timer connected for astable operation.

time duration of the high output period is  $t_1$ , and the low output period is  $t_2$ . Their sum is the total period, T. The frequency of operation is simply the reciprocal of T. The duty factor for either the high or low output state is simply that period divided by the total period.

Operating restrictions of the astable mode are few, and some are similar to monostable operation. The upper frequency limit is on the order of 100 kHz for reliable operation, due to internal storage times. There is no theoretical limit on the lower frequency, only that imposed by  $R_t$  and  $C_t$  limitations.

The limits on  $C_t$  are identical to those in the monostable mode. The maximum value of  $R_{t_1} + R_{t_2}$  is the same as that for  $R_t$  of the monostable, as they are functionally equivalent. This limit is 14  $\mbox{M}\Omega$  or less.

Many applications may demand specific duty factors, which can be programmed (within limits) by the ratios of  $R_{t_a}$  and  $R_{t_b}$ . As  $R_{t_b}$ becomes large with respect to  $R_{t_a}$ , the duty factor approaches 50% (or square-wave operation), which can be noted from the duty factor expression. Conversely, as  $R_{t_a}$  becomes large with respect to  $R_{t_b}$ , the duty factor increases toward unity (100%) as  $R_{t_b}$  approaches zero.<sup>•</sup>  $R_{t_b}$  must not be allowed to reach zero, however. The practical range of duty factors, therefore, is from nearly 50% to about 99%; or, in terms of  $R_{t_a}$ - $R_{t_b}$  ratios,  $R_{t_b}$  may be 1/100 of  $R_{t_a}$ . There is no limit to what fraction  $R_{t_a}$  may be of  $R_{t_b}$ , except for the absolute value restrictions. If  $R_{t_a}$  is to be a very small fraction of  $R_{t_b}$ , its value can be as low as 1 k $\Omega$ , if desired, the ultimate limit being power dissipation.

There are a multitude of variations that can be applied to this astable circuit, but it is shown here in its simplest form. The variations will be covered in a special section of the applications portion of the book (Part II).

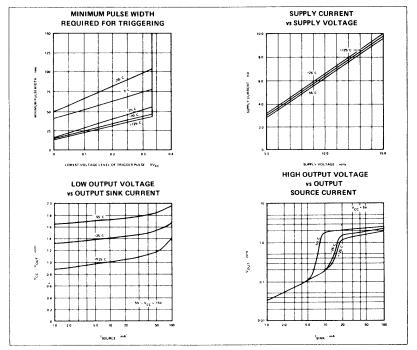

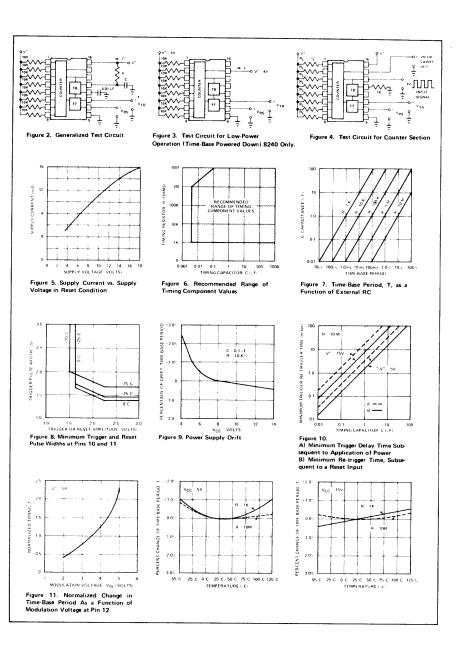

#### 2.1.4 Specifications

A brief discussion of the performance specifications of the 555 is appropriate at this point in order to bring the overall operating capabilities of the device into proper perspective.

Although the 555 is basically a simple and low-cost device, it is capable of an unusual degree of accuracy. Its performance capabilities are, in fact, such that it can be used in all but the most sophisticated of applications. This discussion covers only the highlights of its performance; the detailed specifications are contained in Appendix A. The specifications discussed here are in terms of commercial  $(0^{\circ}C \text{ to } +70^{\circ}C)$  devices, as are the application discussions throughout the book for all devices.

First of all, consider the basic accuracy of the 555 in terms of the fundamental monostable timing expression,  $T = 1.1R_tC_t$ . There is a typical initial error of only 1% due to timer imperfections ( $R_t$  and  $C_t$  tolerance errors must be considered separately). For astable operation the error is somewhat greater, typically about 2% (this parameter is not specified by all 555 manufacturers, however).

Drift with temperature is typically only 50 ppm/°C (or 0.005%/ °C) for the monostable mode. Drift in the astable mode, like the initial accuracy, is somewhat greater, or about 150 ppm/°C (not

$<sup>^{\</sup>circ}$  This definition of duty factor is based on the ratio of output high time (true in a logical sense) which is t<sub>1</sub>, to total time, T.

specified by all manufacturers). These parameters apply for operation at a V+ of both +5 volts and +15 volts.

The drift with supply voltage, by design ideally zero, does have an error coefficient due to device limitations. This is typically 0.1%of timing error per volt of supply voltage change, which is still quite small.

The output-current drive capability has already been mentioned; i.e., the ability to drive both sink and source loads of up to 200 mA, and TTL compatibility when operated from 5 volts.

The input trigger and timing nodes are operable at low currents, which permits a wide range of timing resistor values. In addition, the reset function is available and it is also TTL compatible.

Finally, the device consumes a moderate amount of power, ranging from 3 mA at 5 volts to 10 mA at 15 volts (exclusive of load current).

Many of the specifications and performance features of the 555 have carried over to other similar timers; thus they are obviously well accepted. This is specifically reflected in the next device to be discussed—the 556.

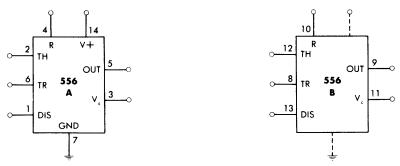

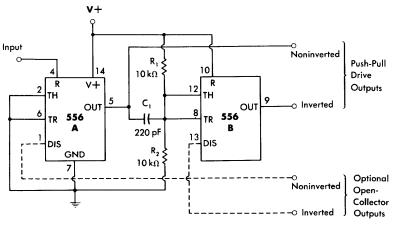

#### 2.2 THE 556 DUAL-UNIT GENERAL-PURPOSE TIMER

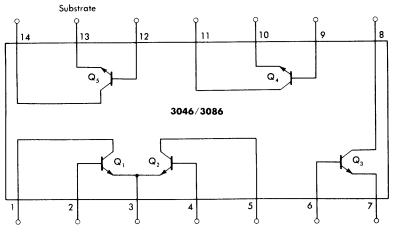

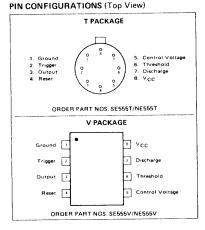

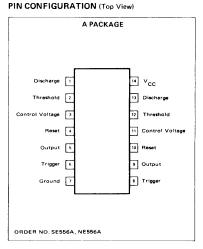

The NE556 timer, also first introduced by Signetics, contains two 555-type timers in the same package, with common power-supply and ground pins. It is supplied in a 14-pin dual in-line package, and each half has virtually identical electrical specifications.

#### 2.2.1 Functional Diagram and Schematic

A functional block diagram of the 556 is shown in Fig. 2-8, and as will be noted, it is identical to the 555. Pin connections are the sole difference, since the 556 is in a 14-pin package and, being a dual unit, has duplicate pins for all but the power-supply and ground leads.

In the diagram shown, the first pin designated refers to the "A" side of the 556; the second pin refers to the "B" side. The schematic of the 556 is shown in Fig. 2-9. This also is identical to the 555 (only one-half of the dual circuit is shown). A photomicrograph of the 556 silicon chip layout is shown in Fig. 2-10.

#### 2.2.2 Definition of Pin Functions

Without exception, all pins of each half of the 556 perform a function exactly like their 555 counterparts. Therefore, it is valid to use the descriptions given in Section 2.1.2 (the specific 555 pin functions) as applicable to the 556; the only differences will be the pin numbers.

Fig. 2-8. Functional block diagram of the 556 dual timer (one-half of circuit shown).

#### 2.2.3 Basic Operating Modes

The basic operation of the 556 in both the monostable and astable modes is identical to the 555, with the difference of duality, of course.

#### 2.2.4 Specifications

The area of specifications is one in which there are minor differences between the 555 and 556. In general, it may be said that each half of the 556 will match or exceed the performance of a 555. With the 556, some specifications have been improved, while others have been added. Only those specifications that differ from the 555 are discussed here; the remainder are the same. For reference, a 556 data sheet is included in Appendix A.

The initial monostable timing accuracy of the 556 is specified as 0.75% typical, which is slightly better than the 555. In addition, specifications are added for the astable-mode timing accuracy. Initial accuracy is 2.25%, and drift with temperature is 150 ppm/°C. Supply-voltage sensitivity in the astable mode is typically 0.3% per volt. Threshold current in the 556 is improved over that of the 555, typically being only 30 nA (versus 100 nA in the 555).

An additional specification for the 556 is discharge leakage current, which is typically 20 nA. In practice, this current should be

Fig. 2-9. Schematic of the 556 dual timer (one-half of circuit shown).

Courtesy Signetics Corp.

Fig. 2-10. Photomicrograph of the 556 silicon chip.

added to the threshold current to determine the total timer error current for the discharge-off period of the timing cycle.

The 556 also has specifications for matching characteristics, which define the allowable differences between sections A and B of the device. Initial timing accuracy will typically match within 0.1%, and timing drift with temperature will match within 10 ppm. Drift with supply voltage will match within 1.2%. Power drain of the 556 is double that of a 555.

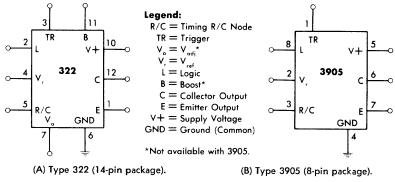

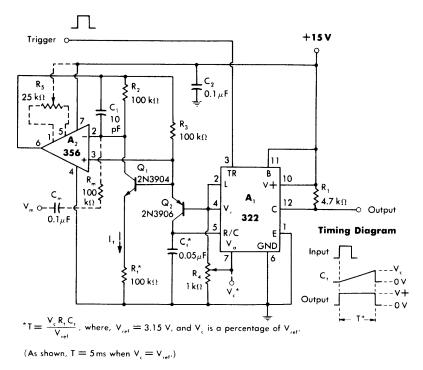

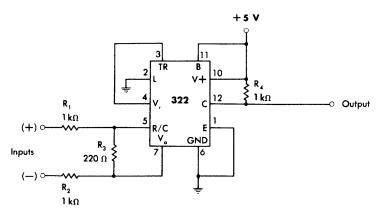

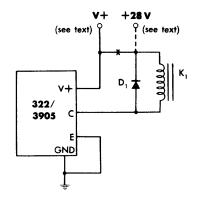

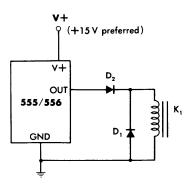

# 2.3 THE 322 AND 3905 WIDE-RANGE, PRECISION, MONOSTABLE TIMERS

The LM322 and LM3905 timers, manufactured by National Semiconductor, were the first timers introduced that departed to any great extent from the established 555 design concept. These units provide improved performance over the 555 in a number of areas: wider supply-voltage range, greater supply immunity, a more flexible and higher voltage output stage, a wider range of timing period capability, and greater timing accuracy. One feature that was sacrificed, however, was that of astable operation, as both the 322 and 3905 are basically monostable timers. Thus, although both the 322 and 3905 possess the technical performance that justifies the term *precision timers*, they are not completely general purpose in the same sense as the 555 and 556 devices are.

The 322 is available in either a 10-pin TO-5 style metal-can package, or in a 14-pin dual in-line plastic package (DIP), while the 3905 is available in an 8-pin dual in-line (MINIDIP) plastic package.

#### 2.3.1 Functional Diagram and Schematic

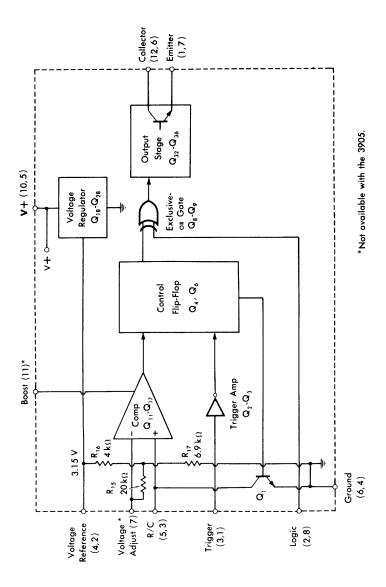

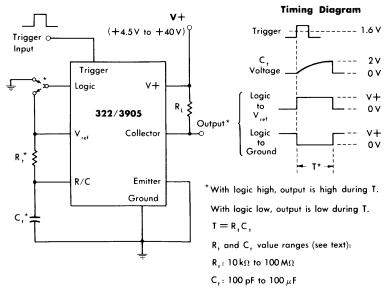

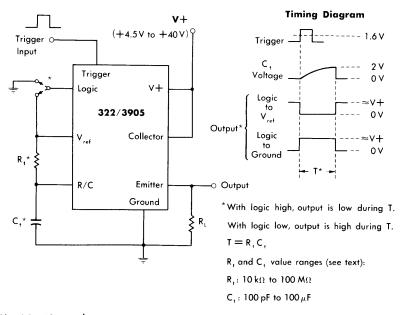

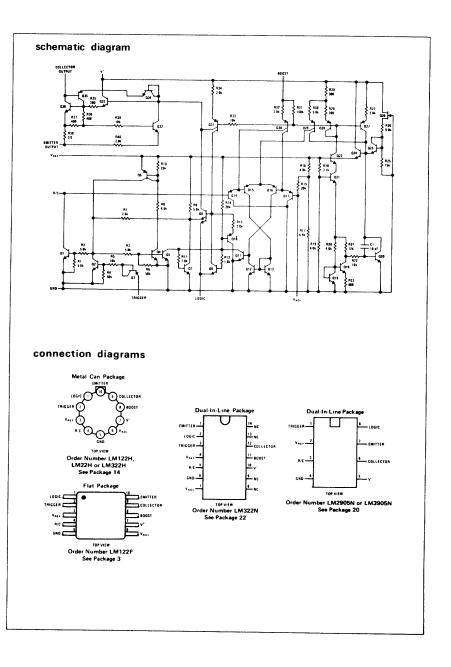

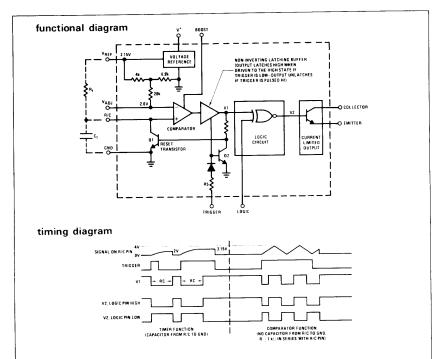

A functional block diagram of the 322/3905 is shown in Fig. 2-11. In some senses, this is similar to the 555 timer, while in others it is different. In this diagram, the first designated pin number is for the 322 (in the 14-pin DIP), while the second number pertains to the 3905.

The part of the diagram that is similar to the 555 is the arrangement of the comparator, the flip-flop, the discharge transistor  $(Q_1)$ , and the threshold reference divider  $(R_{16}-R_{17})$ . In the 322 and 3905, the timing voltage reference is made 0.632 times the timing voltage, in order to make the timing equation equal to  $T = R_t C_t$ .

An important difference from the 555 is the fact that the timing voltage in the 322/3905 comes from an on-chip voltage regulator, which supplies a constant 3.15 volts to the divider. The voltage regulator is also made available externally for the connection of a timing resistor. Although the basic timing scheme of the 555 (i.e., charging from and comparing against a fraction of the supply voltage) is in theory insensitive to supply changes, it does lose some accuracy if the supply voltage changes during the timing interval. The 322/3905 design eliminates supply voltage fluctuations as a source of error by virtue of the 3.15-volt regulator. The comparison voltage in the 322/3905 is nominally 2 volts (0.632 times 3.15 V), established by  $R_{16}$ - $R_{17}$ . In the 322, this point is made externally available; in the 8-pin 3905, it is not.

The R/C node is the junction point of the external timing resistor and capacitor, and the discharge transistor is connected internally to this point. Threshold current is very low in these devices, on the order of 300 pA for both the 322 and the 3905. In the 322, there is an optionally used terminal, the boost terminal (pin 11), which allows higher comparator speed. With the boost terminal connected externally to V+, the threshold current of the 322 becomes 30 nA.

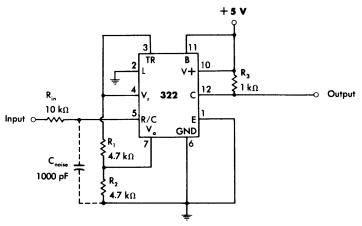

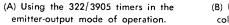

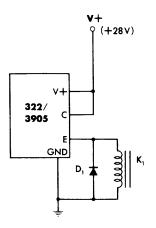

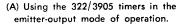

Triggering in the 322 and 3905 is accomplished by a positive pulse at the trigger input. This pulse sets the latch, starting the timing cycle. However, a difference in these timers over those types previously described is the unique output stage used. The signal from the

Fig. 2-11. Functional block diagram of the 322/3905 precision monostable timers.

latch does not simply yield a high output, as in 555-type timers, for two reasons. The first of these is an exclusive-or gate, which has as its two inputs the latch output and the logic input pin. The function of this gate is to control the relative on/off state of the output stage by the logic input. When the logic pin is low, the output stage is "on" during the timing cycle and is "off" otherwise. When the logic pin is high, the output stage is "off" during the timing cycle and is "on" otherwise.

The output stage is equivalent to a floating npn power transistor, and both collector and emitter pins are brought outside the package for external connection. Thus, the output stage can be wired in either a common-collector or a common-emitter fashion. This composite transistor has a voltage standoff capability of 40 volts, and it is also current limited internally. With the flexibility that this output stage and the gating combination possess, many different functions can be performed.

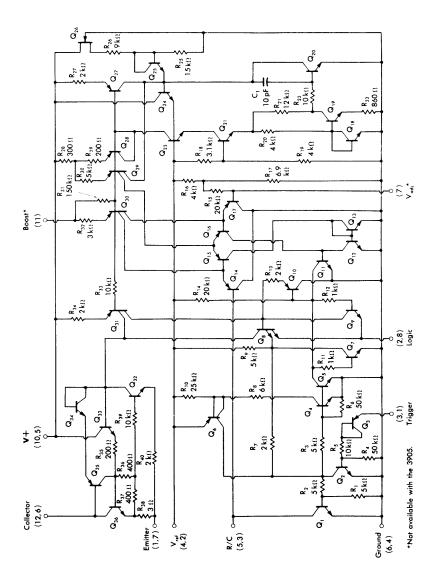

The schematic of Fig. 2-12 illustrates the internal circuitry of the 322/3905. Again, the first designated pin number refers to the 322 (in the 14-pin DIP), while the second number refers to the 3905. The trigger input amplifier is made up of  $Q_2$  and  $Q_3$ , which in turn drive the npn/pnp latch,  $Q_4$  and  $Q_6$ . The discharge transistor,  $Q_1$ , is driven from the latch and  $Q_2$ .

Transistors  $Q_{14}-Q_{17}$  form a pnp input differential comparator, and  $Q_{11}-Q_{13}$  further amplify the output of  $Q_{15}-Q_{16}$ . The comparator is interfaced to the latch by  $Q_7$ . It also drives the exclusive-oR gate,  $Q_8-Q_9$ . The boost terminal of the 322 is connected to the emitter of  $Q_{30}$  within the comparator bias circuitry. Jumpering this pin to V+ turns on  $Q_{30}$ , which increases the operating current of  $Q_{14}-Q_{17}$ , and thus the comparator speed.

Transistors  $Q_{18}-Q_{28}$  comprise the voltage regulator. The actual regulator is  $Q_{18}-Q_{24}$ ;  $Q_{25}$  and  $Q_{26}$  serve as start-up components only. The output voltage is 3.15 volts, and light external loads may be connected.

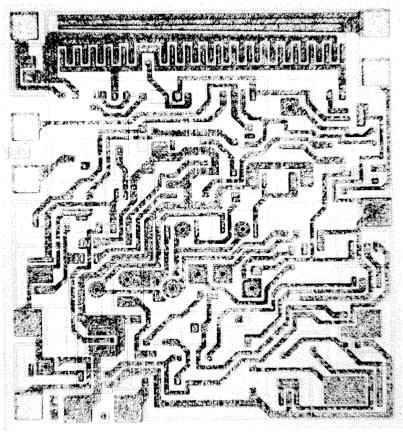

The output stage, consisting of  $Q_{32}$ – $Q_{36}$ , has a "floating" base drive supplied by  $Q_{31}$ . This drive is either passed to the output or shunted away by  $Q_8$  (the exclusive-on gate) to control the conduction state of the output. Within the output stage,  $Q_{32}$  provides current limiting at 120 mA, and  $Q_{34}$ – $Q_{35}$  serve as voltage clamps to prevent excess storage time in  $Q_{36}$ . A photomicrograph of the LM322 silicon chip is shown in Fig. 2-13.

#### 2.3.2 Definition of Pin Functions

Further insight into the operation of the 322/3905 devices may be gained by discussing each pin. Once again, the first designated pin number refers to the 322 (in the 14-pin DIP), while the second num-

Fig. 2-12. Schematic of the 322/3905 precision monostable timers.

40

ber refers to the 3905. The reader is referred to the 322/3905 data sheets in Appendix A.

# V+ (Pins 10, 5)

The V+ pin is the most positive supply terminal of the 322/3905. Operation is highly independent of the voltage applied. Supply current is typically 2.5 mA and is independent of the supply voltage (this will be higher if the reference is loaded). The current drive capability of the output stage is also independent of the supply voltage.

# Ground (Pins 6, 4)

This pin is the most negative supply potential of the device (normally connected to circuit common when operating from positive supply voltages).

# Collector (Pins 12, 6)

This output pin is the collector of the floating npn output transistor. This transistor has a minimum breakdown of 40 volts and is current-limited to 120 mA. For outputs taken from the collector, the emitter is normally grounded. The output is taken from the collector with a load referred to V+, or other positive voltage of 40 volts or less.

# Emitter (Pins 1, 7)

This output pin is the emitter of the npn output transistor. For outputs taken from the emitter, the collector is tied to V+ (or other positive voltage). The output is taken from the emitter with a load referred to ground. The collector may be connected to a voltage higher than V+, but the emitter will pull up (when "on") to a voltage somewhat less than V+.

# Voltage Reference (Pins 4, 2)

This pin is the output of the internal 3.15-volt regulator. Loads of up to 5 mA may be applied, if desired. In normal use, the timing resistor is connected from this pin to the R/C pin. Drift of the reference is typically 0.01%/°C, making this reference voltage quite useful in external circuitry.

# Voltage Adjust (Pin 7 on 322; Not Available on 3905)

This pin allows access to the 2-volt comparator reference point. Use of the pin is optional; it may be used to trim the timing period, if desired, or to prematurely end the timing cycle with a negativegoing voltage. When this pin is not used, noise immunity will be enhanced if it is bypassed with a capacitor of from 0.01  $\mu$ F to 0.1  $\mu$ F.

Courtesy National Semiconductor Corp. Fig. 2-13. Photomicrograph of the LM322 silicon chip.

The voltage-adjust pin, in conjunction with the R/C pin, allows access to both inputs to the comparator. This permits use of the device as a general-purpose, low-input-current comparator with a common-mode input range of zero up to 5 volts. External voltages applied to the voltage-adjust pin should be between zero and +5volts for safe operation.

#### R/C (Pins 5, 3)

This pin is the node where the timing resistor and capacitor are normally connected. Internally, the R/C pin is connected to the comparator input and the collector of the discharge transistor  $(Q_1)$ . The timing threshold voltage is +2 volts. When the voltage across the timing capacitor reaches +2 volts, the comparator changes states, ending the timing cycle.

The threshold current is typically 300 pA for the 322 operating in the unboosted mode, and for the 3905. When the 322 is operating in the boosted mode, the threshold current increases to 30 nA. For safe operation, external voltages applied to the R/C input should be between zero and +5 volts.

#### Trigger (Pins 3, 1)

This pin is used to start the timing cycle with a positive-going pulse. The trigger threshold is TTL compatible, with a typical threshold voltage of  $\pm 1.6$  volts. Current at threshold is 20  $\mu$ A, and the input is overvoltage protected for voltages up to  $\pm 40$  volts.

The timer will not retrigger if the trigger cycle is held high during the timing cycle but will time out. However, the timing capacitor will not be discharged until the trigger input is lowered below the threshold (this does not affect the output).

### Logic (Pins 2, 8)

This pin determines the state of conduction of the output transistor during the timing cycle. When the logic pin is high, the output transistor is "off" during the timing period ("on" otherwise). When the logic pin is low, the output transistor is "on" during the timing period ("off" otherwise).

The logic input switching threshold is 150 mV, and 150  $\mu$ A of current must be sunk by the source in the low state. Safe voltage applied to this pin is zero to +5 volts.

#### Boost (Pin 11 on 322; Not Available on 3905)

This pin increases the speed of the comparator when connected to the V+ pin. It is used when operating at short timing periods ( $\leq 1.0$  ms) for greater accuracy.

#### 2.3.3 Basic Operation

The basic mode of operation for the 322/3905 is that of a monostable timer. Astable operation can be achieved with some additional circuitry, if desired. This section deals with the practical points of applying the device in its basic mode.

# **Monostable Mode**

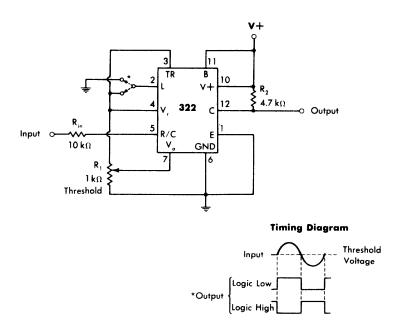

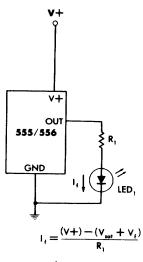

There are two different ways that the 322/3905 timer can be used in the monostable mode of operation: with the output taken from the collector, or with the output taken from the emitter. Fig. 2-14 illustrates the collector-output option, where the emitter of the output transistor is connected to common (ground). R<sub>L</sub> is the load re-

Fig. 2-14. The 322/3905 connected in the basic monostable mode of operation, with the output taken from the collector terminal.

sistor, and is referred here to V+.  $R_t$  and  $C_t$  are the timing components, and the logic pin may be connected to either  $V_{ref}$  or ground (high or low), depending on the desired output state.

When the input trigger exceeds  $\pm 1.6$  volts, the timer fires and begins a timing cycle. Capacitor C<sub>t</sub> charges toward V<sub>ref</sub> and, assuming the logic pin to be high, the output goes high during the timing cycle. When the C<sub>t</sub> voltage crosses  $\pm 2$  volts (0.632 times V<sub>ref</sub>), the timing cycle ends, C<sub>t</sub> discharges, and the output returns to its low state. Had the logic pin been wired low, the timing period would be identical but the output state would be reversed (see the timing diagram in Fig. 2-14). This collector-output option is useful when current-sinking loads, such as TTL logic, are to be driven.

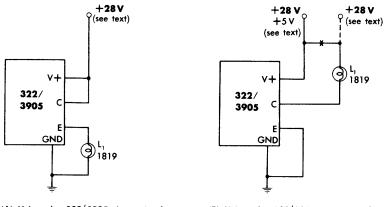

Fig. 2-15 shows the emitter-output option. This is similar to the collector-output option, but the load resistor,  $R_L$ , is placed between the emitter and ground, and the collector is wired to V+. With the logic input high, the output of this circuit is low during the timing cycle. If the logic input is low, the output is high during the timing cycle. The high-state output will typically pull up to within 1.8 to 2 volts of V+ in this circuit, depending on the load current. This circuit is useful for current-source-type loads.

Limitations on timing and timing components are identical for both circuits, and are generally few. The 322 (with the boost option) is useful down to a few microseconds in pulse width. At the other

Fig. 2-15. The 322/3905 connected in the basic monostable mode of operation, with the output taken from the emitter terminal.

end of the timing range, an unboosted 322 (or 3905) can achieve timing periods of hours or more, limited only by the timing components.

Due to the extremely low comparator current capability of the 322/3905, the allowable range of  $R_t$  is from 10 k $\Omega$  to 100 M $\Omega$ . The ultimate limit is more a function of the availability of high-value resistors. Capacitor  $C_t$  can range from 100 pF on the low end (a practical limit due to stray capacitance) up to 100  $\mu$ F on the high end. The real limit on  $C_t$  will also be one of availability. With the 322 and 3905 timers, the operating range is essentially unrestricted from the standpoint of the device itself; the limitations are practical ones set by  $R_t$  and  $C_t$ .

#### Astable Mode

Because these devices do not offer the capability of astable operation by themselves, this mode will not be treated in this section but will be covered in the applications section of the book.

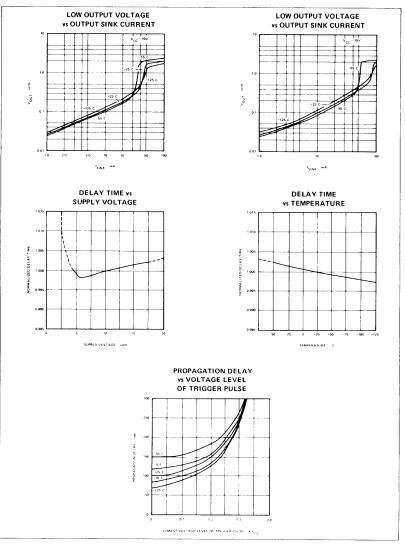

#### 2.3.4 Specifications

A discussion of the specifications of the 322 and 3905 will serve to bring their performance capability into overall focus. Of all the devices discussed thus far, these two are capable of the highest degree of performance and best overall accuracy, in addition to their basic flexibility. For reference, data sheets are included in Appendix A.

Initial timing error for the 322/3905 is specified differently than for 555-type devices, which simply have a lumped percentage error. The 322/3905 units break the error down into its several different components, such as timing-ratio tolerances, Ct saturation voltage, etc. Furthermore, some of the error is specified for a minimum and maximum, whereas the 555 error is only specified as typical.

Timing ratio error for the 322/3905 is listed as a worst-case limit of  $\pm 3.2\%$ . Normally it will be much better than this and more comparable to the 1% typical of the 555. Temperature drift is listed as 30 ppm/°C typical, which is an excellent figure. Supply-voltage sensitivity is not listed separately but is included in the total error for timing ratio. By itself it would be about 50 ppm/V.

Output drive capability of the 322/3905 is quite different than that of the 555 devices, because of the floating transistor. The 322/ 3905 can withstand voltages of 40 volts and can handle currents up to 50 mA. Drive capability in the collector-output mode is typically 0.25 volt at 8 mA; 0.7 volt at 50 mA. In the emitter-output mode, the drive capability is 1.8 volts at 3 mA; 2.1 volts at 50 mA. A big point in favor of the uncommitted output arrangement is the ability to drive loads that are referred to voltages higher than V+, up to 40 volts.

Trigger voltage is typically 1.6 volts which is TTL compatible and requires 25  $\mu$ A of source current. Minimum trigger pulse width is 0.25 µs.

A significant difference between 555 devices and the 322/3905 is their very low input threshold currents. For the 3905 (and the 322 unboosted) this is only 300 pA typical. For the 322 in the boosted mode, the threshold current rises to 30 nA.

Another major point of usefulness for the 322/3905 is the 3.15-volt reference output. Although this voltage has no influence on the timing accuracy, it has a specified tolerance of  $\pm 5\%$  and good regulation. This feature can be a valuable asset in system design.

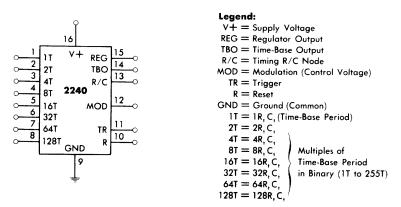

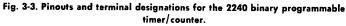

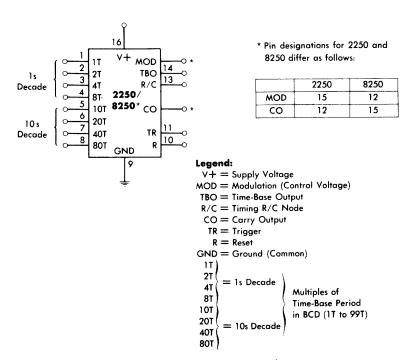

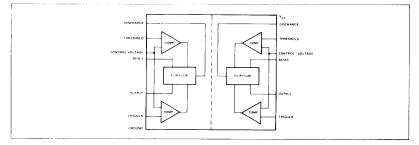

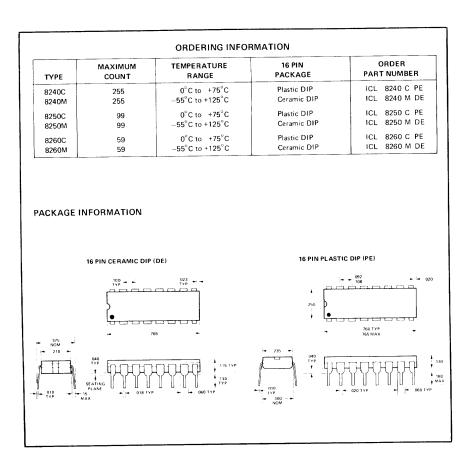

#### THE 2240, 2250, AND 8260 2.4 PROGRAMMABLE TIMER/COUNTERS

The 2240, 2250, and 8260 are three different types of devices which fall into a special class of timer ICs-that of programmable timer/ counters. These units include a timing section made up of a 555-type oscillator, followed by a counter section. The timing period of the counter is externally programmable by the user. In simplest block diagram terms, the timer portion generates a

basic timing pulse of a period, T. This is then multiplied (or

counted) by the counter to effectively increase the timing period by a desired multiplication factor. The multiplication factor can be made externally variable, thus the term *programmable timer/ counter*. Differences between the various devices mentioned are generally in terms of the functioning of the counter section, the timer sections all being similar.

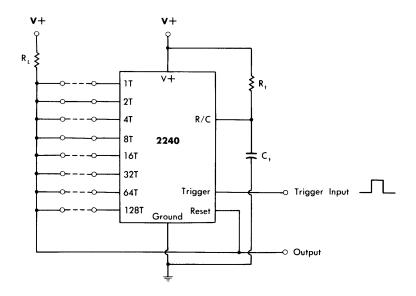

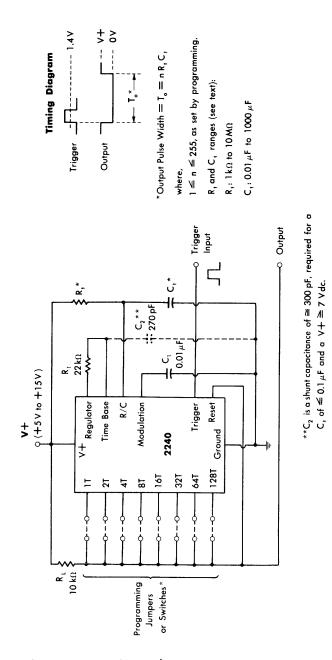

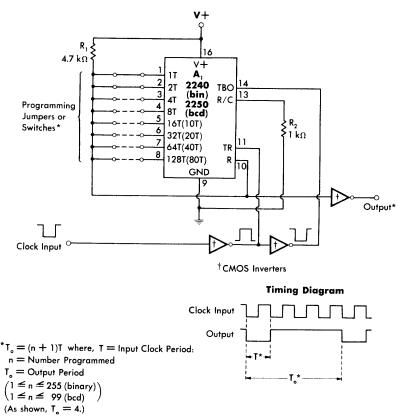

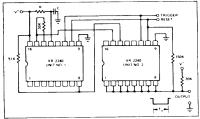

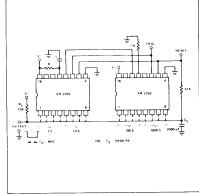

The XR-2240 is manufactured by Exar Integrated Systems, who pioneered the concept of the timer/counter. It is a binary programmable device with an 8-bit counter section. Timing is programmable from  $1R_tC_t$  to 255  $R_tC_t$ , where  $R_t$  and  $C_t$  are the timing components that define the basic timing interval, which is  $T = R_tC_t$ . Two or more 2240 devices can be cascaded to extend the timing interval indefinitely, counting in binary fashion.

The XR-2250, also manufactured by Exar, is a bcd (binary-coded decimal) programmable device. The time-base section of the 2250 is similar to the 2240, but the counter is an 8-bit design arranged to count in decimal fashion over two decades. It is programmable from  $IR_tC_t$  to  $99R_tC_t$ . Two or more 2250 devices can be cascaded to extend the timing interval indefinitely, counting in decimal fashion.

The ICL 8260, manufactured by Intersil, is designed for seconds/ minutes/hours counting applications. The time-base section is similar to the 2240 and 2250, and the counter section is programmable from 1 to  $59R_tC_t$ . Two 8260s can be cascaded to count seconds and minutes.

This programmable timer/counter section is somewhat larger in scope than the previous sections of this chapter because it discusses an entire family of timing devices, each of which is a large-scale system in itself. Although there are differences between the timers covered, these are differences of detail rather than concept. Therefore, the 2240 will be discussed initially in detail, and when its operation is understood, it will be relatively easy to transfer your thinking to the 2250 and 8260 types.

# 2.4.1 The 2240 Binary Programmable Timer/Counter

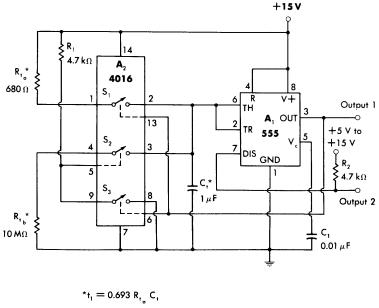

The XR-2240 is produced by Exar, as mentioned previously, and it is second-sourced by others under the 2240 part-number designation. It is also second-sourced by Intersil under the 8240 designation. The 2240 can be operated in either the basic monostable or astable timing modes, as well as a variety of other modes. It is packaged in a 16-pin dual in-line package.

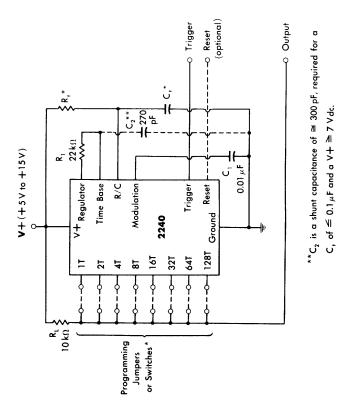

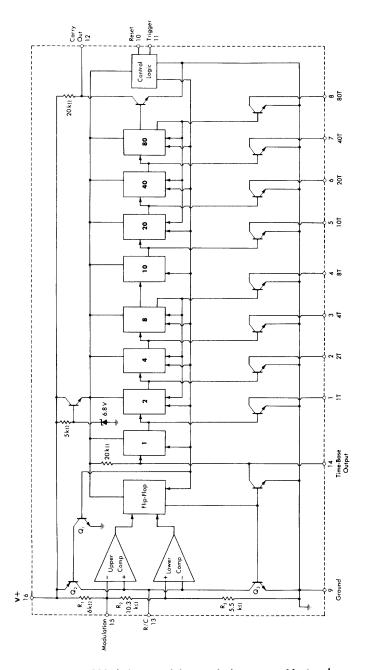

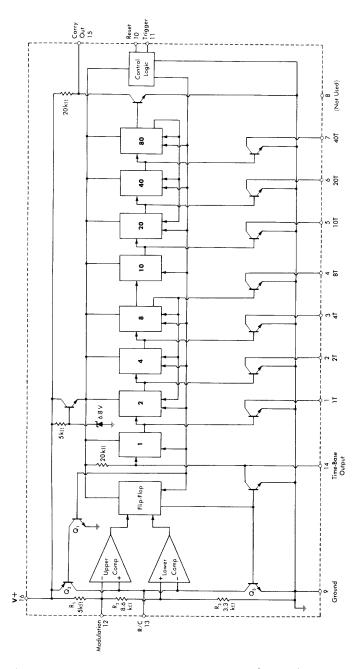

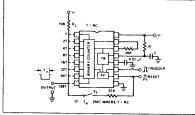

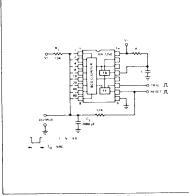

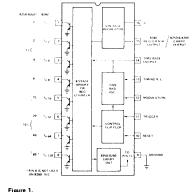

# **Functional Diagram**

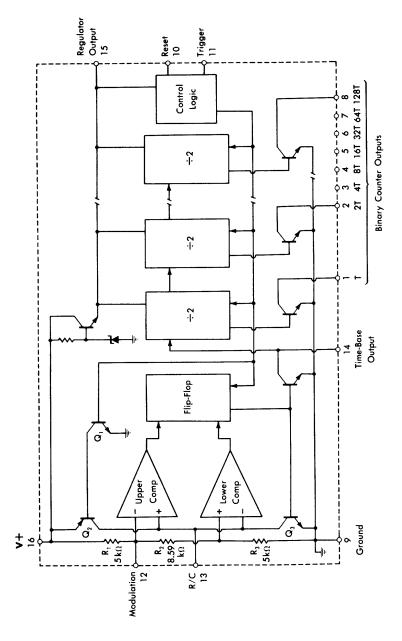

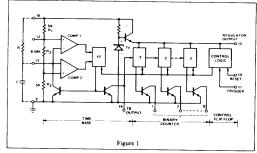

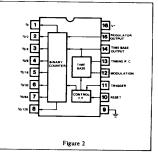

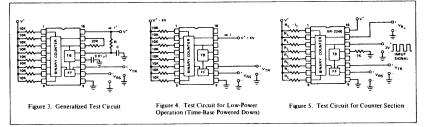

A functional block diagram of the 2240 is shown in Fig. 2-16A. The two main functional portions of this diagram are the time-base section and the counter. The time-base section may be seen at the left

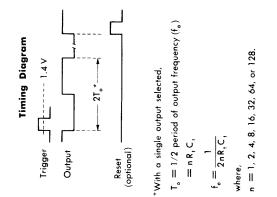

(A) Functional block diagram.

of the diagram and is made up of a 555-type astable oscillator, with a buffered output at pin 14. The counter is seen at the right and consists of 8 binary stages, with a buffered output available from each. Each output is low for the multiple of the time-base period shown. The T output (pin 1), for instance, is low for a period, T, while the 2T output (pin 2) is low for a period, 2T, etc.

A third subsection is the control logic, a circuit consisting of a latch that is set and reset by pins 11 and 10, respectively. This circuit controls the timer/counter, resetting all counter stages when commanded, and starting the timer circuit upon command by a trigger.

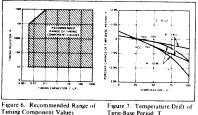

The control functions and counter stages are powered by an onchip voltage regulator, which produces a nominal 4- to 6-volt output. This is made available at pin 15. The time-base portion of the circuit is connected directly across V+ and uses the 555 scheme of charging from and comparing against the same (V+) voltage, for timingperiod supply-voltage independence.

In operation, an external timing resistor and capacitor are connected to the R/C node, somewhat similarly to the connection for the 555 monostable. The capacitor is charged toward V+ via  $R_t$ , and the timing ramp is compared to a fraction of V+ generated by the  $R_1$ - $R_2$ - $R_3$  divider. The upper threshold is 0.731 of V+. Capacitor C<sub>t</sub> is discharged toward ground by the discharge transistor, and the lower threshold is 0.269 of V+.

Although on the surface this scheme appears similar to the 555 astable timing mode, there are some important differences. First is

programmable timer/counter.

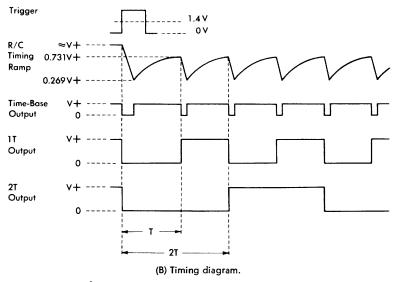

the fact that this circuit is a *triggered* astable, and will always operate in an astable mode, even if the timer/counter as a whole is used as a monostable. An understanding of how the circuit functions may be gained from the timing diagram of Fig. 2-16B.

In the reset or standby state, the time-base oscillator is inhibited by  $Q_2$ , which clamps the R/C node to nearly the V+ level. This may be noted on the timing diagram in the sketch for the timing ramp. When the circuit is triggered,  $Q_2$  turns off, removing the clamp. The discharge transistor,  $Q_3$ , then rapidly brings the capacitor voltage down to the lower comparator threshold. This changes the state of the oscillator flip-flop, and C<sub>t</sub> now charges toward V+. When the upper threshold is reached,  $Q_3$  discharges C<sub>t</sub> again. The oscillator will then continue to cycle until the control logic is reset.

Although the time-base operation is astable, the timing is highly asymmetrical because  $Q_3$  discharges  $C_t$  very rapidly but is charged slowly through  $R_t$ . It is for this reason that the timing expression for T is stated simply as a single period—the discharge time is short enough to be neglected. This discharge time period generates the short negative-going time-base output pulses. Note that the very first discharge cycle is from V+, rather than 0.731 of V+. This factor will result in only a slightly longer first timing period than the rest because the discharge current for  $C_t$  is high. The timing scale is exaggerated in the diagram to illustrate this point. In practice, the error due to this effect is minimal, particularly for multiple time counts.

In the 2240, the values of resistors  $R_1$  and  $R_2$  are chosen such that

$$\frac{\mathbf{R}_1 + \mathbf{R}_2}{\mathbf{R}_1} = \boldsymbol{\epsilon} = 2.7183.$$

This makes the threshold voltage exactly equal to one time constant so the timing period, T, is then simply:

$$\mathbf{T} = \mathbf{R}_{\mathsf{t}}\mathbf{C}_{\mathsf{t}}.$$

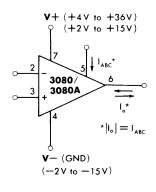

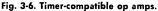

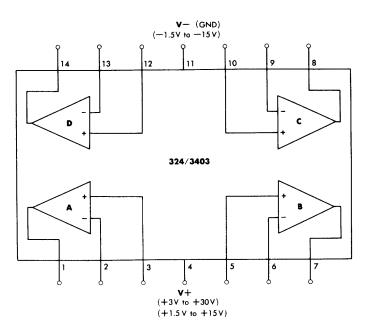

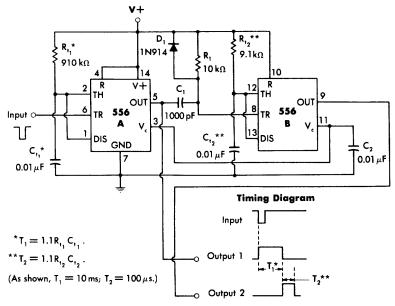

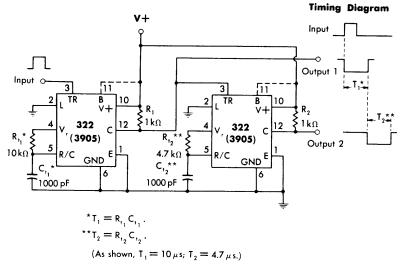

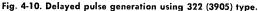

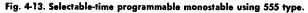

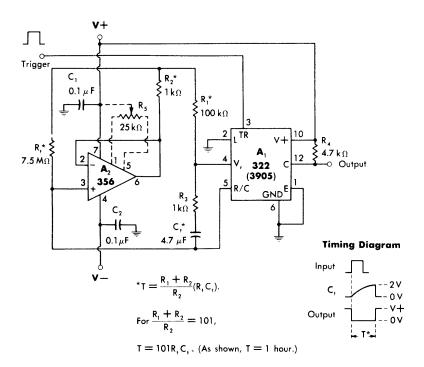

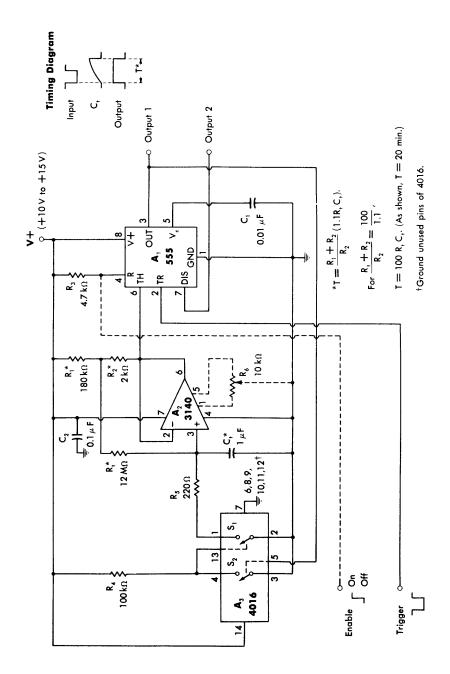

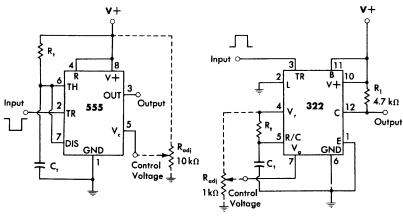

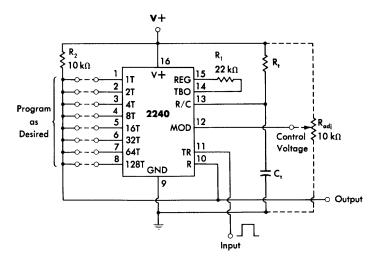

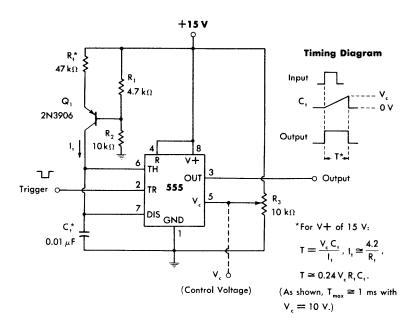

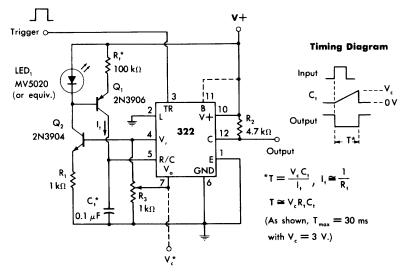

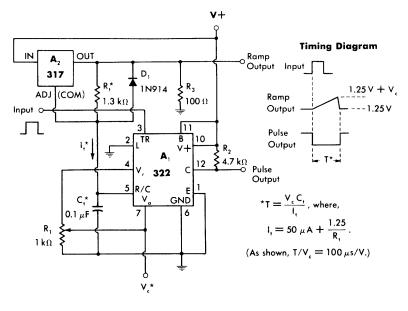

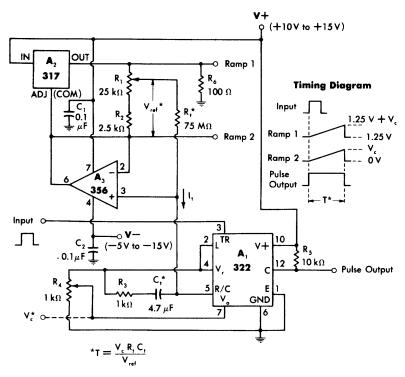

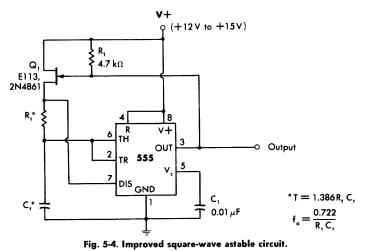

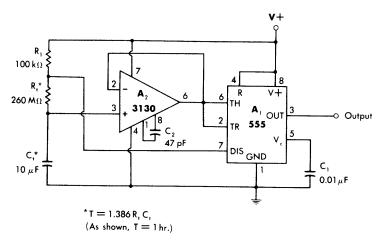

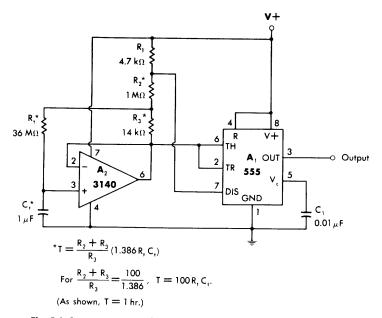

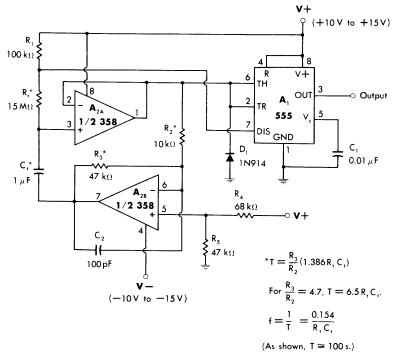

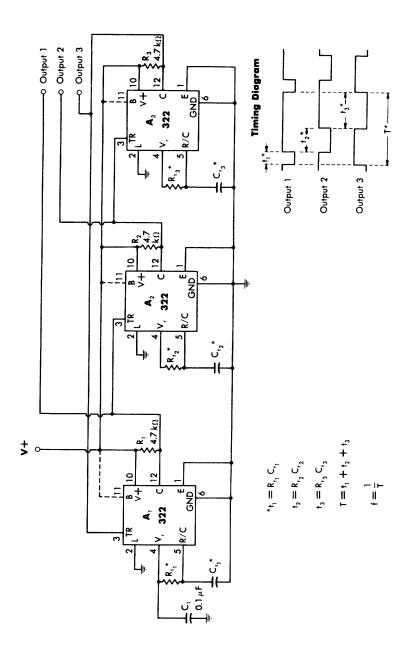

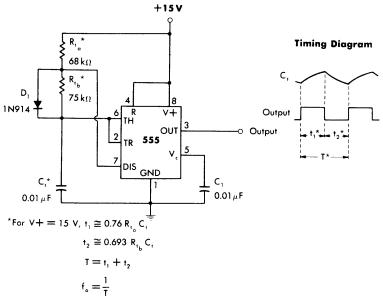

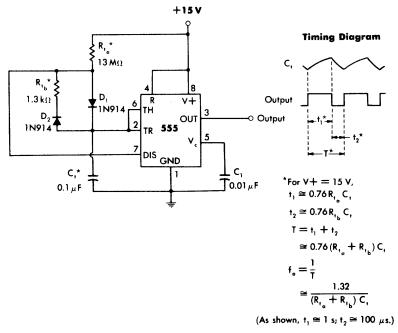

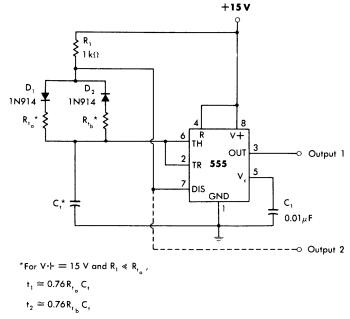

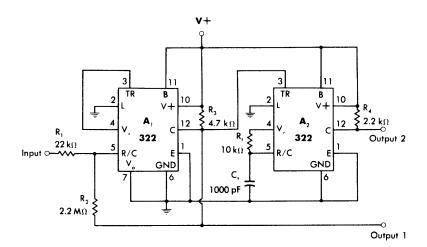

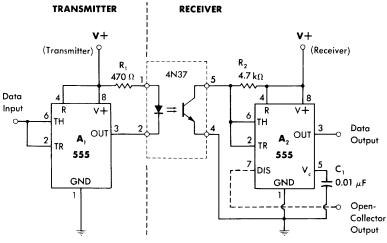

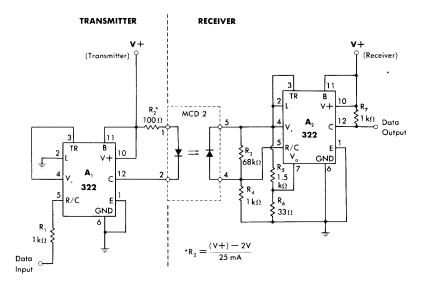

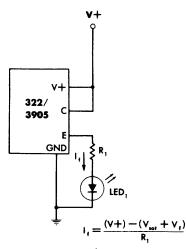

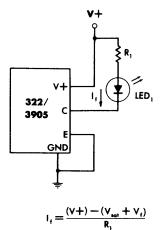

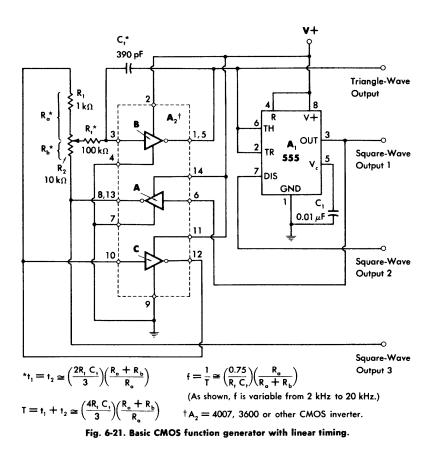

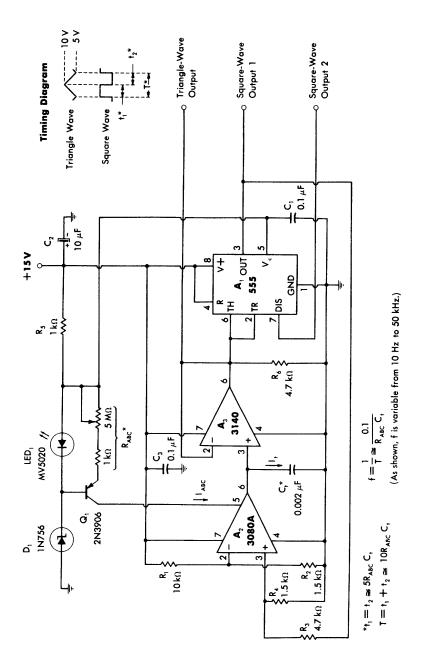

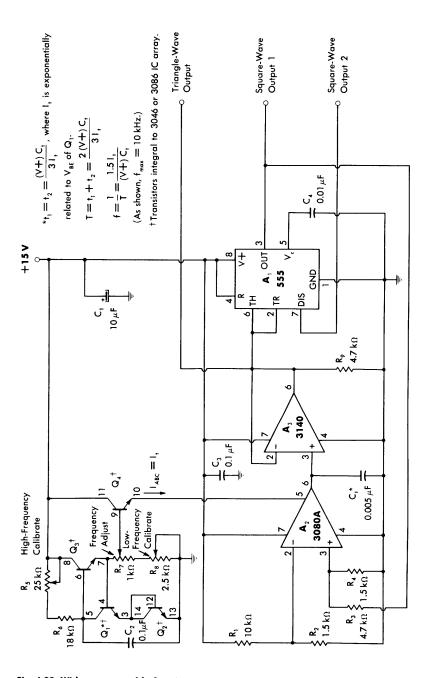

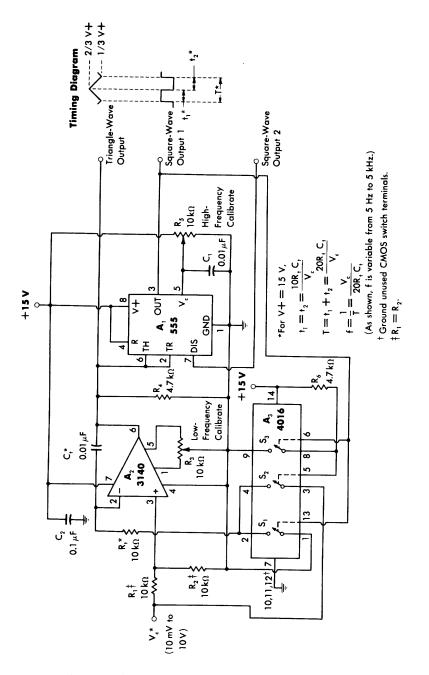

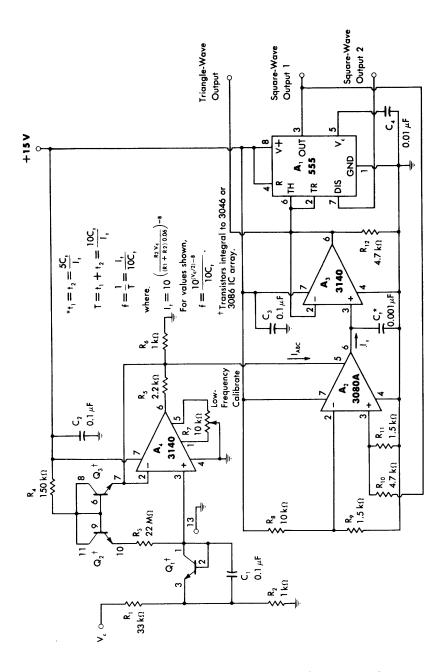

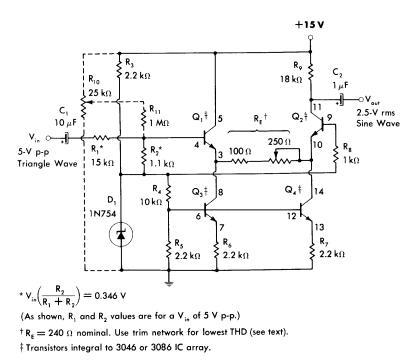

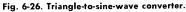

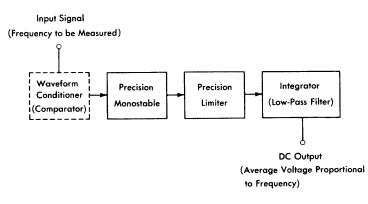

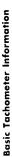

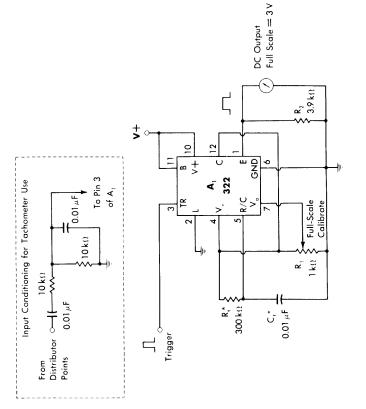

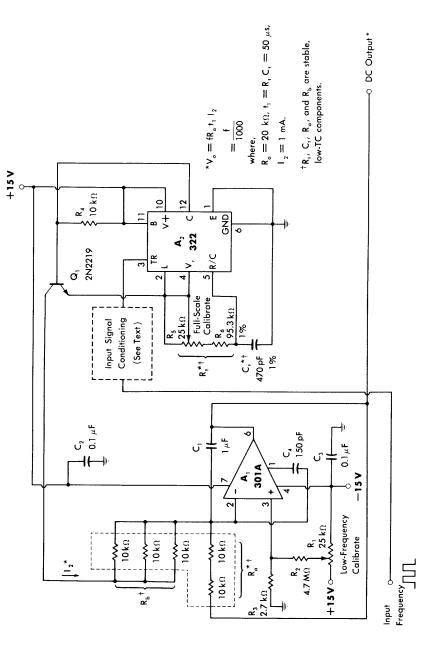

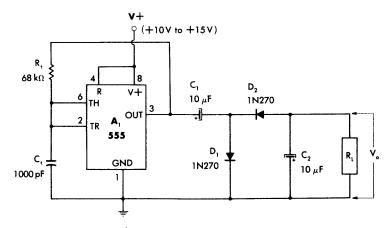

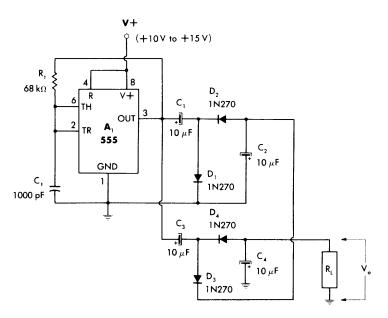

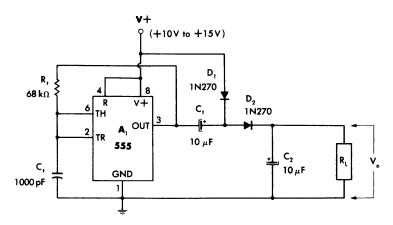

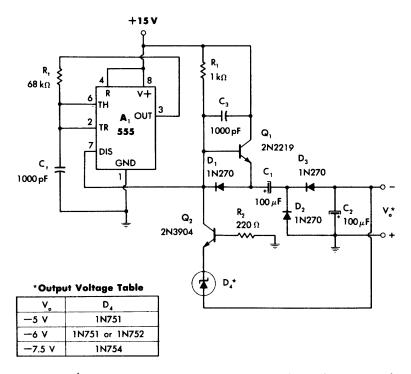

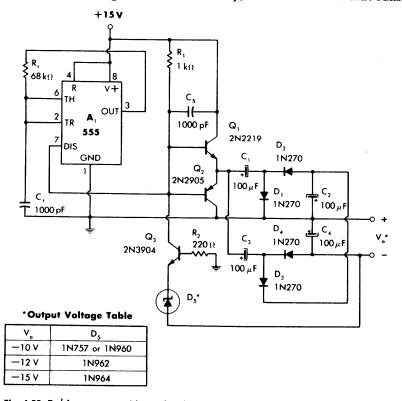

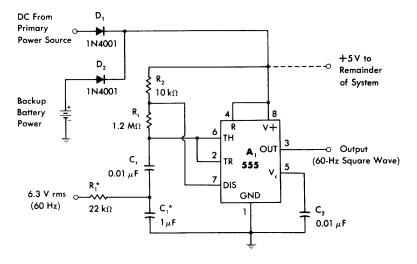

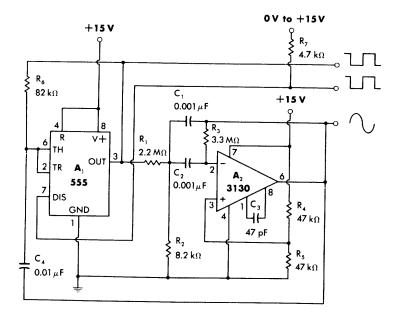

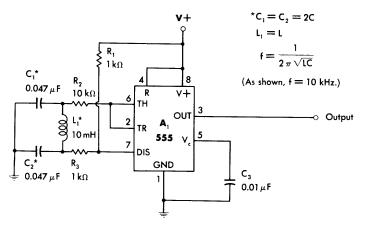

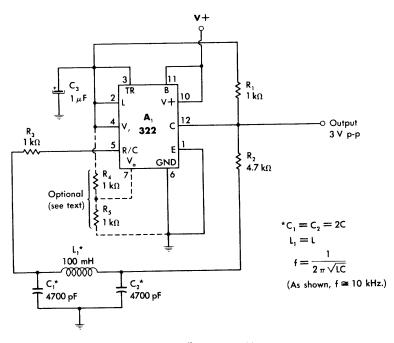

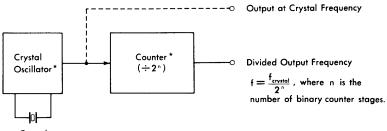

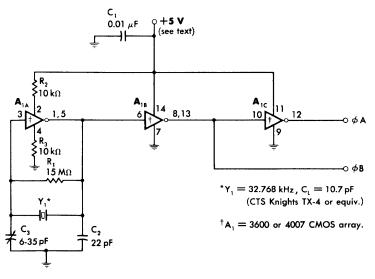

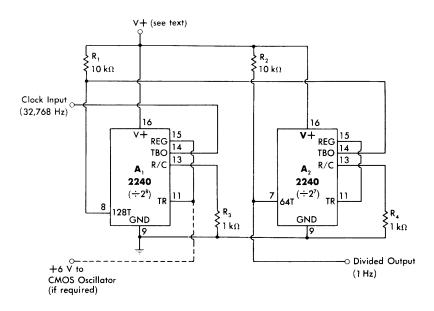

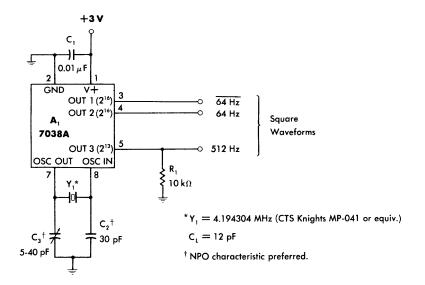

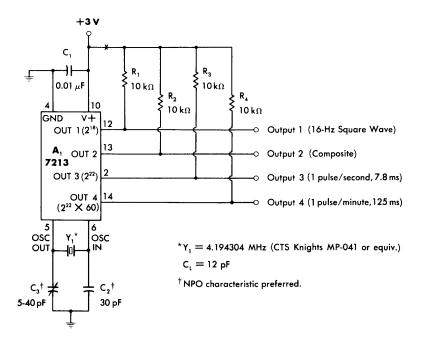

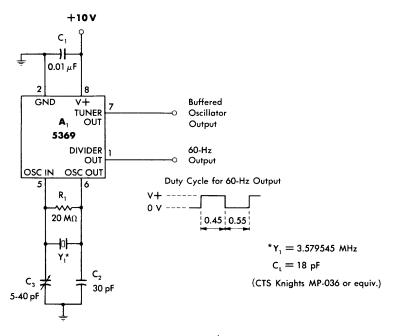

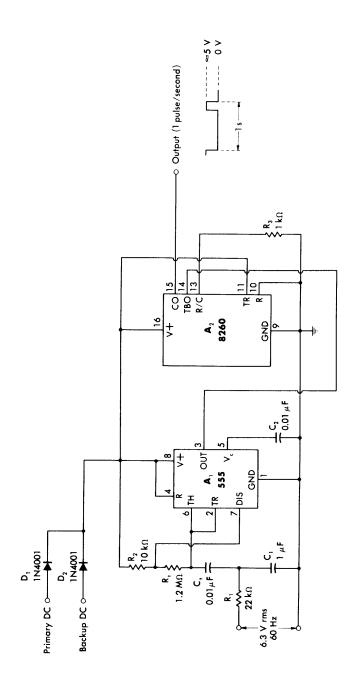

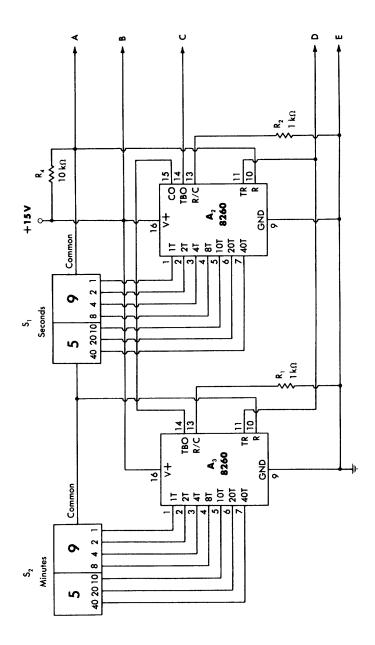

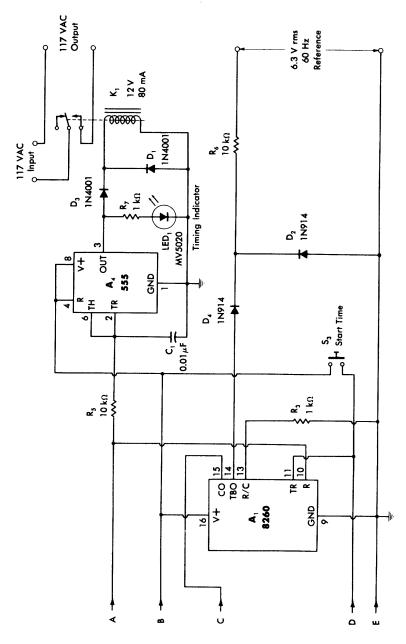

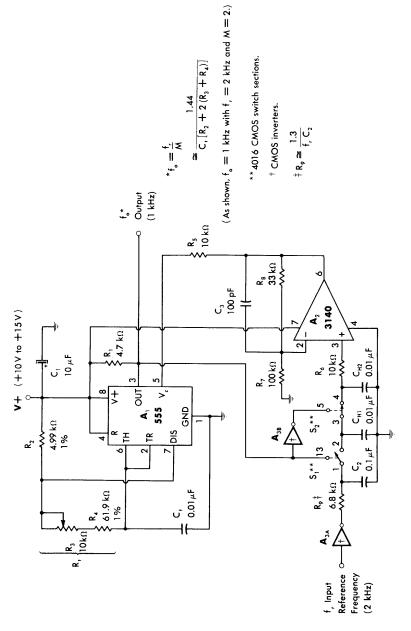

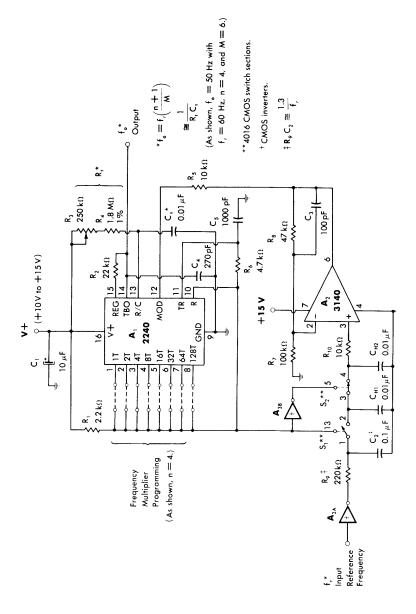

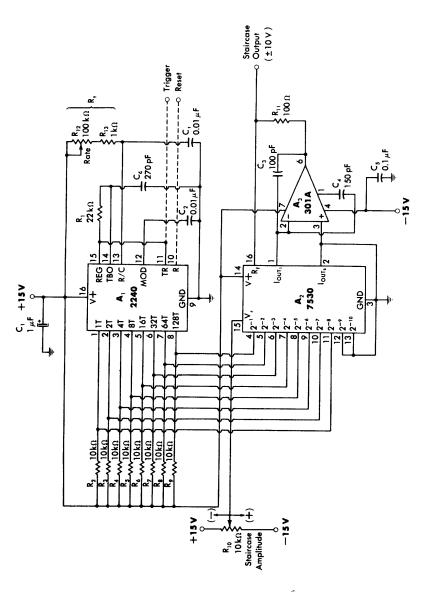

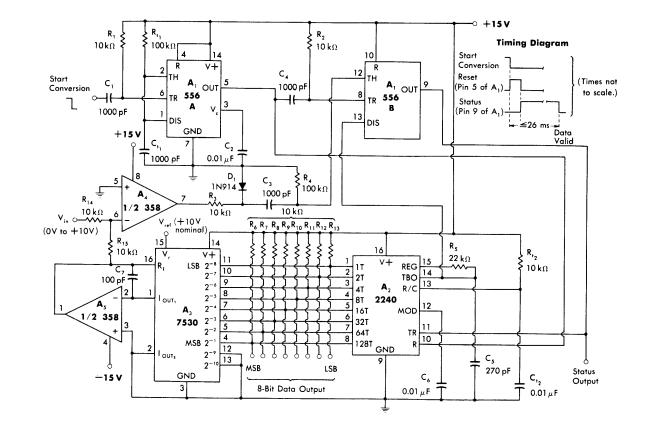

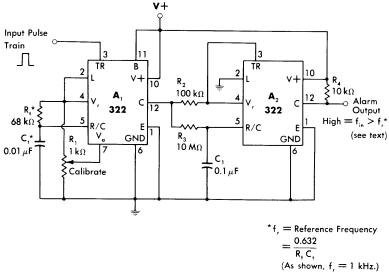

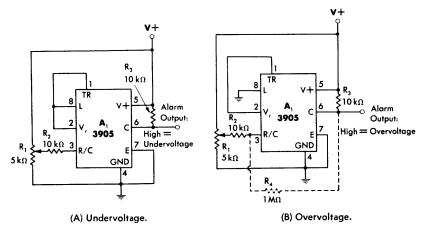

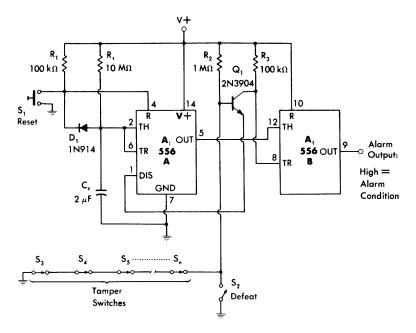

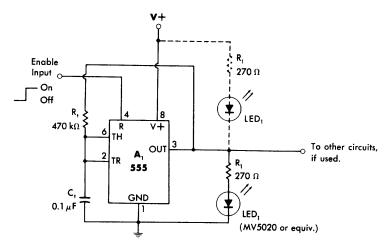

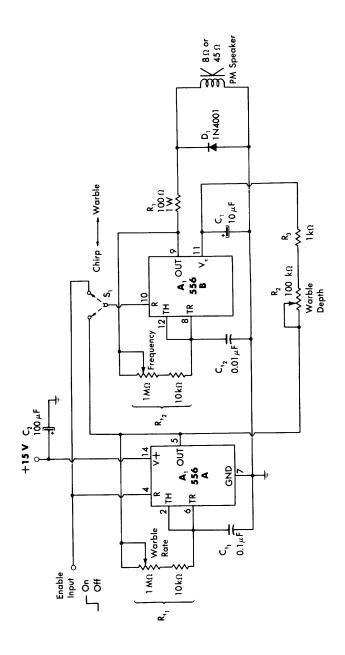

In the timing diagram of Fig. 2-16B, two of the eight available counter outputs are shown. The 1T output is low for one time-base period; the 2T output is low for two time-base periods; and the remaining outputs, although not shown, follow a similar progression (4T, 8T, 16T, etc.).