# VECTOR MZ5 HARDWARE MANUAL

REFERENCE GUIDE

Revision A

June 19, 1981

P/N Manual-7200-9120-00-00

Copyright 1980, 1981 Vector Graphic Inc.

Made in U.S.A.

# Copyright 1980, 1981 by Vector Graphic Inc. All rights reserved.

#### Disclaimer

Vector Graphic makes no representations or warranties with respect to the contents of this manual itself, whether or not the product it describes is covered by a warranty or repair agreement. Further, Vector Graphic reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Vector Graphic to notify any person of such revision or changes, except when an agreement to the contrary exists.

#### Revisions

The date and revision of each page herein appears at the bottom of each page. The revision letter such as A or B changes if the MANUAL has been improved but the PRODUCT itself has not been significantly modified. The date and revision on the Title Page corresponds to that of the page most recently revised. When the product itself is modified significantly, the product will get a new revision number, as shown on the manual's title page, and the manual will revert to revision A, as if it were treating a brand new product. EACH MANUAL SHOULD ONLY BE USED WITH THE PRODUCT IDENTIFIED ON THE TITLE PAGE.

#### REPAIR AGREEMENT

The MZ5 sold hereunder is sold "as is", with all faults and without any warranty, either expressed or implied, including any implied warranty of fitness for intended use or merchantability. However, the above notwithstanding, VECTOR GRAPHIC, INC., will, for a period of ninety (90) days following delivery to customer, repair or replace any MZ5 that is found to contain defects in materials or workmanship, provided:

- 1. Such defect in material or workmanship existed at the time the MZ5 left the VECTOR

- GRAPHIC, INC., factory;

2. VECTOR GRAPHIC, INC., is given notice of the precise defect claimed within ten (10) days after its discovery;

- 3. The MZ5 is promptly returned to VECTOR GRAPHIC, INC., at customer's expense, for examination by VECTOR GRAPHIC, INC., to confirm the alleged defect, and for subsequent repair or replacement if found to be in order.

Repair, replacement or correction of any defects in material or workmanship which are discovered after expiration of the period set forth above will be performed by VECTOR GRAPHIC, INC., at Buyer's expense, provided the MZ5 is returned, also at Buyer's expense, to VECTOR GRAPHIC, INC., for such repair, replacement or correction. In performing any repair, replacement or correction after expiration of the period set forth above, Buyer will be charged in addition to the cost of parts the then-current VECTOR GRAPHIC, INC., repair rate. At the present time the applicable rate is \$35.00 for the first hour, and \$18.00 per hour for every hour of work required thereafter. Prior to commencing any repair, replacement or correction of defects in material or workmanship discovered after expiration of the period for no-cost-to-Buyer repairs, VECTOR GRAPHIC, INC., will submit to Buyer a written estimate of the expected charges, and VECTOR GRAPHIC, INC., will not commence repair until such time as the written estimate of charges has been returned by Buyer to VECTOR GRAPHIC, INC., signed by duly authorized representative authorizing VECTOR GRAPHIC, INC., to commence with the repair work involved. VECTOR GRAPHIC, INC., shall have no obligation to repair, replace or correct any MZ5 until the written estimate has been returned with approval to proceed, and VECTOR GRAPHIC, INC., may at its option also require prepayment of the estimated repair charges prior to commencing work.

Repair Agreement void if the enclosed card is not returned to VECTOR GRAPHIC, INC. within ten (10) days of end consumer purchase.

#### FOREWORD

Audience

This manual is intended for computer distributors, or others with at least a moderate technical knowledge of small computers.

Scope

It will describe what the Vector Graphic MZ5 does in the context of a subsystem of other Vector microcomputer syste. It considers the power supply, motherboard and chassing eneral. It does not cover any of the disk drive subassemblies. The manual describes the hardware and its function and provides procedures for troubleshooting, testing and adjusting the subject components.

Organization

This manual is divided into 4 parts. "Perspective" describes how the MZ5 fits into the Vector product line. "Mainframe" explains the function of the main subassemblies. "Troubleshooting" shows how to test the power supply and motherboard to assure they are providing the correct voltages to the circuit boards. "Appendix" contains a listing of the S-100 bus pins, illustrations of the chassis components and schematics showing the circuitry of the power assembly and disk regulator board.

# TABLE OF CONTENTS

| Sect | ion                             |                                                                                                         | Page                       |

|------|---------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------|

|      | Repa                            | air Agreement                                                                                           | 3                          |

|      | Fore                            | eword                                                                                                   | 4                          |

|      | Tabl                            | e of Contents                                                                                           | 5                          |

|      | Spec                            | cifications                                                                                             | 6                          |

| 1.   | Pers                            | pective                                                                                                 | . 7                        |

| н.   | Main                            | frame                                                                                                   | 7                          |

|      | 2.1<br>2.2<br>2.3               | Power Supply Motherboard S-100 Bus Termination                                                          | 7<br>7<br>8                |

| 111. | Trou                            | ubleshooting                                                                                            | 8                          |

|      | 3.1<br>3.2<br>3.3               | Troubleshooting the Power Supply Preliminary Checkout (Without Power) Preliminary Checkout (With Power) | 8<br>8<br>9                |

| Appe | ndix                            | A - Illustrations and Schematics                                                                        |                            |

|      | A.1<br>A.2<br>A.3<br>A.4<br>A.5 | MZ5 Backpanel<br>MZ5 Motherboard                                                                        | 10<br>12<br>13<br>14<br>15 |

#### **SPECIFICATIONS**

#### POWER

For one unit (5005 configuration for three users)

Voltage option Frequency Current, Operating Current, Surge 115 VAC +10% 60 Hz +.5% 3 Amps 15 Amps

220 VAC +10% 50 Hz ±.5% 1.5 Amps 7.5 Amps

### DIMENSIONS AND WEIGHT\*

Height inches/cm Depth inches/cm Width inches/cm Weight lbs/kg 43.2/19.6

Mainframe

7.5/18.0

20.5/52 16.75/42.5

\* Does not include requirements for cabling (typically 4 in./10.2 cm)

#### ENVIRONMENT

Temperature Humidity (non-condensing) Operating 10 to 320 C 20-80%

Storage -34 to 65° C 20-80%

#### I. PERSPECTIVE

The Vector MZ5 serves as the mainframe for the 3105 and 5005 Vector Graphic computer systems. The advantage of purchasing an MZ5 based system lies in the units expandability. When shipped as part of the 3105 system only 4 of the motherboards 18 connectors are occupied. This allows 14 additional boards to be inserted for future expansion. For example, you could include boards for video based systems or expanded memory systems.

The MZ5 Hardware Manual covers the hardware components contained within the MZ5 chassis with the exception of the disk drive units. This includes the Mainframe, Power Supply, and the Motherboard.

For information on other components see the specific hardware manual. For information on installation, use, and maintenance of a System printer as part of an MZ5 based system, see the NEC 7700Q manual that comes with the printer.

#### II. MAINFRAME

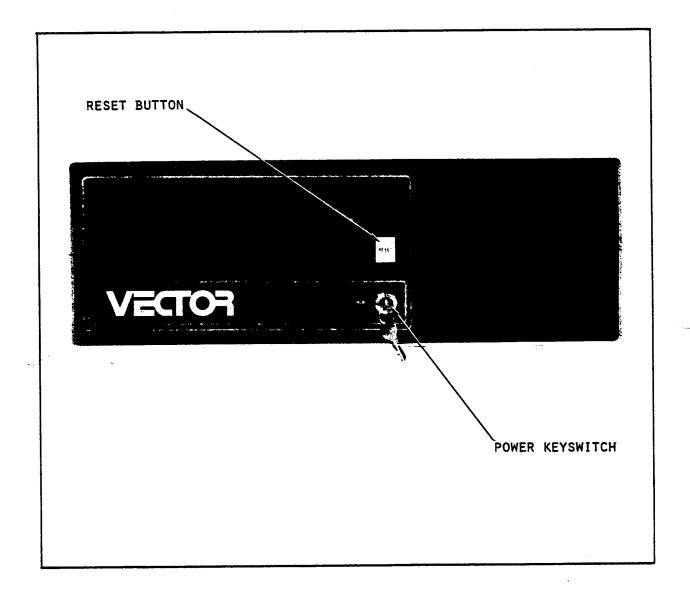

The Vector MZ5 Mainframe's front panel (see Appendix A.2) contains a POWER keyswitch and a RESET button (connected to pin 75 and ground on S-100), along with a disk drive subsystem. Current configurations include:

- 1. 3105: One Seagate 5-1/4" hard disk drive, one Tandon 5-1/4" double-sided floppy disk drive, and one Dualmode Disk Controller, one Flashwriter II, one ZCB, and one 64K Dynamic RAM memory boards.

- 3. 5005: Same drives as used in 3105 with one Dualmode Disk Controller, one Flashwriter II, one ZCB, one 64K Dynamic RAM memory and one Bitstreamer II boards. For each additional user another pair of Flashwriter and 64K RAM boards is added (up to five users can be serviced by one MZ5 mainframe).

The boards used in the 5005 system are modified for a multi-user environment. These modifications are discussed in the 5005 SYSTEMS OVERVIEW MANUAL.

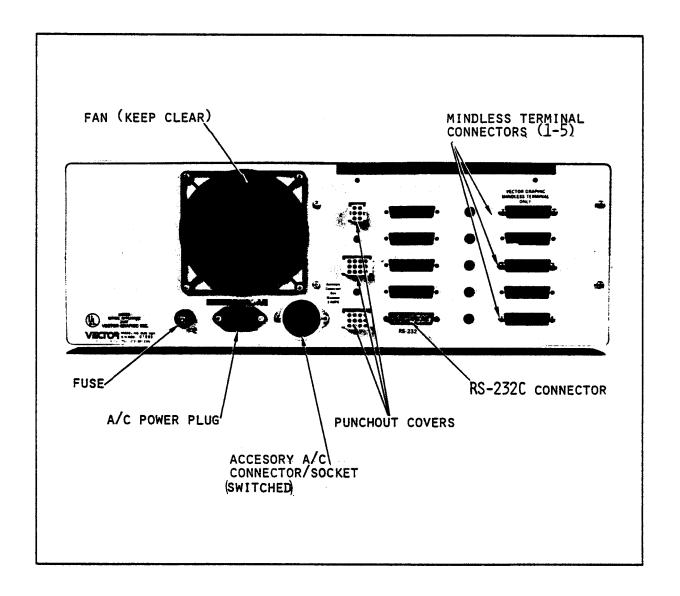

On the backpanel of the MZ5 (see Appendix A.3) is found a fuse holder, a plug for AC power and an accessory AC receptacle. The backpanel also has a RS-232C connector and the appropriate number of Mindless Terminal connectors.

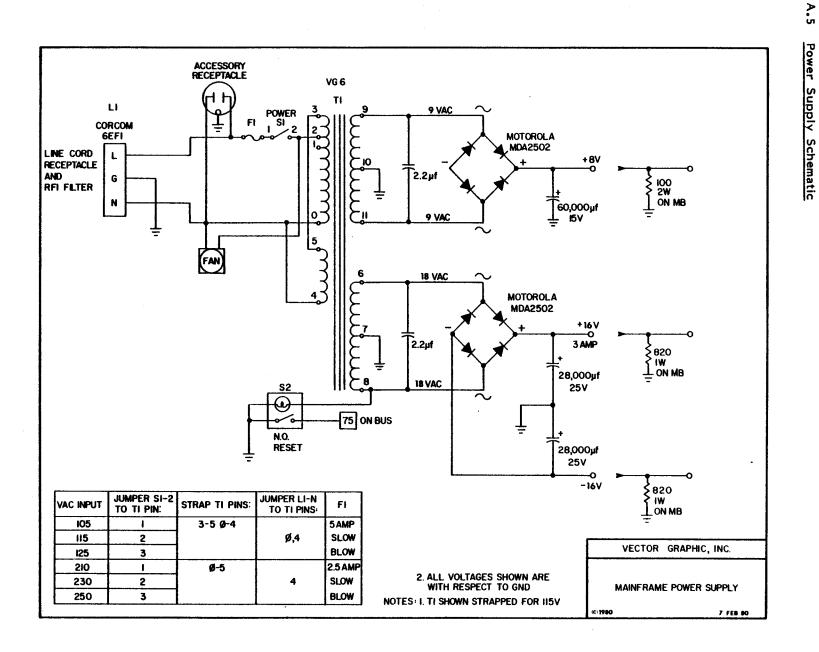

Mounted on the inside of the MZ5 backplane is a fan assembly. When replacing the fan assembly, make sure that the flow of air is moving out of the mainframe to the rear, and not being sucked into the mainframe. Also on the inside of the mainframe is the power supply module (see Appendix A.5), disk regulator assembly (see Appendix A.6) and an 18-slot motherboard based on the S-100 bus (see Appendix A.4).

#### 2.1 Power Supply

The Vector MZ5 Power Supply is located on the inside of the mainframe. It consists of two 28,000 uF computer grade capacitors, a 60,000 uF computer grade capacitor, two bridge rectifiers and a 110V/220V switchable transformer. Instructions on how to rewire the transformer for a different source voltage are found on the power supply schematic in the Appendix of this manual. The MZ5 Power Supply provides +8, +16, and -16 VDC unregulated power to the computers Motherboard, the Mindless Terminal, and the Disk Drives Regulator Board. NOTE: In order to attach a printer it is necessary that the printer have an independent power supply.

#### 2.2 Motherboard

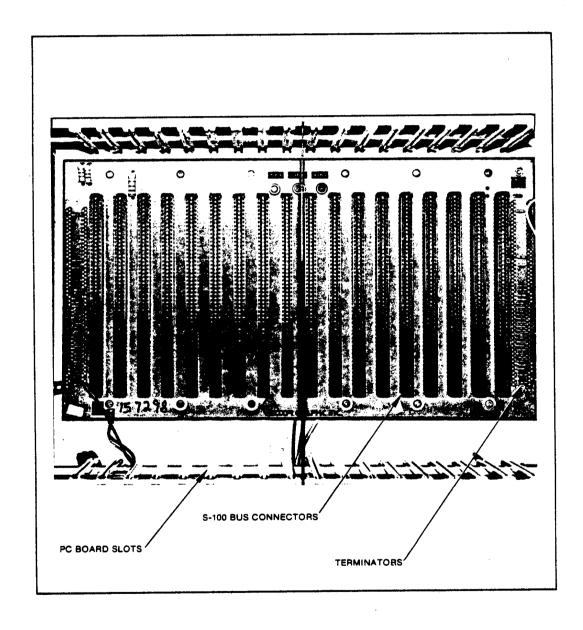

All S-100 boards used in Vector Microcomputer Systems send and receive bus signals via the S-100 bus assembly on the Motherboard located in the MZ5 Mainframe (see Appendix A.4).

Rev. A (6-19-81) 7200-9120-00-00 Page 7

The Motherboard contains 18 slots and can accommodate all the boards used in various Vec. Systems. Since all boards access the same S-100 bus signals from the Motherboard, they can be arranged in any desired sequence, contiguous or noncontiguous. The Motherboard is supplied with bus terminators so full-time termination is provided.

#### 2.3 S-100 Bus Termination

The bus terminators provided on the Motherboard are 220 ohm pull-up (to +5V) and 330 ohm pull-down (to GND). See Appendix A.1.

| T     | ABLE | 1     |

|-------|------|-------|

| LINES | TERM | NATED |

|       |      |       |

| 24 - 2   | 38 - DO4     | 76 - PSYNC | 86 - A14 |

|----------|--------------|------------|----------|

| 25 - 1   | 39 - DO5     | 77 - PWR   | 87 - A11 |

| 29 - A5  | 40 - DO6     | 78 - PDBIN | 88 - D02 |

| 30 - A4  | 41 - D12     | 79 - A0    | 89 - DO3 |

| = -      |              | 80 - A1    | 90 - D07 |

| 31 - A3  | 42 - D13     |            | 91 - D14 |

| 32 - A15 | 43 - D17     | 81 - A2    |          |

| 33 - A12 | 47 - SMEMR   | 82 - A6    | 92 - D15 |

| 34 - A9  | 49 - CLK     | 83 - A7    | 93 - D16 |

| 35 - DO1 | 54 - EXT CLR | 84 - A8    | 94 - DI1 |

|          |              | 85 - A13   | 95 - DIO |

| 36 - DO6 | 66 - RFSH    | 65 - A13   | 33 4 DIO |

| 37 - A10 | 68 - MWRITE  |            |          |

#### III. TROUBLESHOOTING

#### 3.1 Troubleshooting the Power Supply

This section is provided for reference. The MZ5 mainframe has been completely tested at the factory.

#### WARNING

This power supply uses 110V AC, which is a potentially lethal voltage level. Extreme caution must be exercised when working with these circuits when power is applied. It is suggested that the user always keep one hand in his pocket while working with the power supply. Never make ohmmeter or continuity measurements while the power is applied.

#### 3.2 Preliminary Checkout (Without Power)

#### WARNING

Do not apply power during these tests as high voltages are present.

Review Power Supply schematic diagram to ensure that the power supply is wired correctly. Check all connectors for mechanical integrity, such as the screw terminals on the electrolytic capacitors and the motherboard. A loose or unterminated wire can cause serious damage to the computer and present a safety hazard to the user.

Using an ohmmeter, check the continuity between the linecord receptacle ground terminal and the negative terminal of either of the 28,000 uF capacitors. Continuity (0 ohms) should be indicated between these points. Now measure from the capacitor to some bare metal portion of the chassis. Continuity should also be indicated here.

With the ohmmeter on the X1 scale, measure across the 60,000 uF capacitor. If a short indicated, reverse the leads of the ohmmeter and repeat the measurement. The corr

Rev. A (6-19-81)

indication of the ohmmeter will be a slowly increasing value of resistance (in the order of minutes) to a final value of infinity. If a short is indicated at both times, then either the capacitor is shorted or there is a wiring error.

Repeat the above test on each of the two 28,000 uF capacitors. The final value of resistance for these tests should be 820 ohms +/-20%. Therefore, adjust the scale of the ohmmeter accordingly. The response time will be much shorter for these capacitors.

#### 3.3 Preliminary Checkout (With Power)

Before applying power to the computer, remove all plug-in circuit boards. Ensure that the fuse is installed and that the power switch is off. Connect the AC linecord and turn on the power switch. Listen for any crackling sounds or very loud buzzing in the transformer. Immediately disconnect power by unplugging the linecord if any unusual sounds are noted or if arcing or smoke is apparent.

Correct operation of the power supply shall be indicated by the fan running and the RESET light lit. Using a voltmeter, check each of the power supply voltages. They should read as follows:

| Nominal Voltage | Acceptable Limits |

|-----------------|-------------------|

| +8 Volts        | 7.5 to +11 Volts  |

| +16 Volts       | +15 to +20 Volts  |

| - 16 Volts      | -15 to -20 Volts  |

Any voltage reading out of the acceptable limits indicates a failure in that circuit. The most likely failures, after wiring errors have been eliminated, are defective rectifiers or transformer.

After the voltages have been tested at the power supply, carefully check for these voltages on the motherboard. They can be found on the following pins:

| Bus Voltage | Bus Pin |

|-------------|---------|

| +8 Volts    | 1, 51   |

| +16 Volts   | 2       |

| - 16 Volts  | 52      |

| GND         | 50. 100 |

Incorrect reading here could damage circuit boards when they are installed. If any wrong voltages are found, carefully check wiring to the motherboard.

# APPENDIX A - ILLUSTRATIONS AND SCHEMATICS

# A.1 S-100 Bus Pin List

| PIN NO.    | SIGNAL & TYPE                             | ACTIVE LE | S-:          | DESCRIPTION                                                                                                                                                                      |

|------------|-------------------------------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          |                                           | -CIITE LE |              | Instantaneous minimum greater than 7 volts, instantaneous maximum less                                                                                                           |

| 2          | +6 VOLTS (8)<br>+16 VOLTS (8)             |           |              | than 25 volts, average maximum less than 11 volts. Instantaneous minimum greater than 14.5 volts, instantaneous maximum                                                          |

| 3          | XRDY (S)                                  | н         |              | less than 35 volts, average maximum less than 21.5 volts.  One of two ready inputs to the current bus master. The bus is ready wine both these ready inputs are true. See pm 72. |

| 4          | V10*(S)                                   | L         | 0.C.         | Vectored interrupt line 0.                                                                                                                                                       |

| 5          | V11*(S)                                   | ī         | 0.C.         | Vectored interrupt line 1.                                                                                                                                                       |

| 6          | V12*(S)                                   | L         | 0.C.         | Vectored interrupt line 2.                                                                                                                                                       |

| 7          | VI3*(S)                                   | Ļ         | O.C.         | Vectored interrupt line 3.                                                                                                                                                       |

| 8          | V14*(S)                                   | Ļ         | 0.C.         | Vectored interrupt line 4.                                                                                                                                                       |

| 9          | VI5*(S)                                   | L<br>L    | 0.C.<br>0.C. | Vectored interrupt line 5. Vectored interrupt line 6.                                                                                                                            |

| 10<br>11   | VI6*(S)<br>VI7*(S)                        | Ľ.        | 0.C.         | Vectored interrupt line 7.                                                                                                                                                       |

| 12         | HMI*(S)                                   | ì         | 0.C.         | Non-maskable interrupt.                                                                                                                                                          |

| 14<br>15   | A18 (M)                                   | н         |              | Extended address bit 18.                                                                                                                                                         |

| 16         | A15 (M)                                   | H         |              | Extended address bit 16.                                                                                                                                                         |

| 17         | A17 (M)                                   | H         |              | Extended address bit 17.                                                                                                                                                         |

| 18         | SDS8* (M)                                 | L         | 0.C.<br>0.C. | The control signal to disable the 8 status signals.  The control signal to disable the 5 control output signals.                                                                 |

| 19<br>20   | COS8* (M)<br>GND (B)                      | L         | 4.5.         | Common with pin 100.                                                                                                                                                             |

| 21         | NDEF                                      |           |              | Not to be defined. Manufacturer must specify any use in detail.                                                                                                                  |

| 22         | ADSB* (M)                                 | L         | 0.C.         | The control signal to disable the 15 address signals.                                                                                                                            |

| 23         | DODS8° (M)                                | L         | O.C.         | The control signal to disable the 8 data output signals.                                                                                                                         |

| 24         | ◆ (B)                                     | H         |              | The master timing signal for the bus.                                                                                                                                            |

| 25<br>26   | pstval*(M)<br>phlda (M)                   | L<br>H    |              | Status valid strobe. A control signal used in conjunction with HOLD* to coordinate bus maste transfer operations.                                                                |

| 27<br>28   | RFU<br>RFU                                |           |              | Reserved for future use. Reserved for future use.                                                                                                                                |

| 29         | A5 (M)                                    | H         |              | Address bit 5.                                                                                                                                                                   |

| 30         | A4 (M)                                    | Ĥ         |              | Address bit 4.                                                                                                                                                                   |

| 31         | A3 (M)                                    | H         |              | Address bit 3.                                                                                                                                                                   |

| 32         | A15 (M)                                   | H         |              | Address bit 15 (most significant for non-extended addressing.)                                                                                                                   |

| 33<br>34   | A12 (M)<br>A9 (M)                         | H         |              | Address bit 12. Address bit 9.                                                                                                                                                   |

| 35         | DO1 (M)/DATA1 (M/S)                       | Ĥ         |              | Data out bit 1, bidirectional data bit 1.                                                                                                                                        |

| 36         | DOD (M)/DATAG (M/S)                       | H         |              | Data out bit 0, bidirectional data bit 0.                                                                                                                                        |

| 37         | A10 (M)                                   | H         |              | Address bit 10.                                                                                                                                                                  |

| 38         | DO4 (M)/DATA4 (M/S)                       | Н         |              | Data out bit 4, bidirectional data bit 4.                                                                                                                                        |

| 39         | DOS (M)/DATAS (M/S)                       | H         |              | Data out bit 5, bidirectional data bit 5.                                                                                                                                        |

| 40         | DOG (M)/DATAS (M/S)                       | H         |              | Data out bit 6, bidirectional data bit 6. Data in bit 2, bidirectional data bit 10.                                                                                              |

| 41<br>42   | DI2 (S)/DATA10 (M/S)                      | H         |              | Data in bit 3, bidirectional data bit 11.                                                                                                                                        |

| 42         | DI3 (S)/DATA11 (M/S) DI7 (S)/DATA15 (M/S) | Ä         |              | Data in bit 7, bidirectional data bit 15.                                                                                                                                        |

| 44         | sM1 (M)                                   | H         |              | The status signal which indicates that the current cycle is an<br>op-code fetch.                                                                                                 |

| 45         | sOUT (M)                                  | Н.,       |              | The status signal identifying the data transfer bus cycle to an output device.                                                                                                   |

| 46         | siNP (M)                                  | H         |              | The status signal identifying the data transfer bus cycle from an<br>input device.  The status signal identifying bus cycles which transfer data from memor                      |

| 47         | sMEMR (M)                                 | H         |              | to a bus master, which are not interrupt acknowledge instruction teach cycle(s).                                                                                                 |

| 48         | SHLTA (M)                                 | Ħ         |              | The status signal which acknowledges that a HLT instruction has been executed.                                                                                                   |

| 49         | CLOCK(B)                                  |           |              | 2 MHz (0.5%) 40-60% duty cycle. Not required to be synchronous with any other bus signal.                                                                                        |

| 50         | GND (B)                                   |           |              | Common with pin 100. Common with pin 1.                                                                                                                                          |

| 51<br>52   | +8 VOLTS (B)<br>-16 VOLTS (B)             |           |              | Instantaneous maximum less than —14.5 volts, instantaneous minimum greater than —35 volts, average minimum greater than —21.5 volts.                                             |

| 53 .<br>54 | GND (B)                                   |           |              | Common with pin 100.                                                                                                                                                             |

| PIN NO. | SIGNAL & TYPE        | ACTIVE LE | VEL  | DESCRIPTION                                                                                                                                               |

|---------|----------------------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56      |                      |           |      |                                                                                                                                                           |

| 57      |                      |           |      |                                                                                                                                                           |

|         |                      |           |      |                                                                                                                                                           |

| 58      | sXTRQ* (M)           | Ļ         |      | The status signal which requests 16-bit slaves to assert SIXTN*.                                                                                          |

| 59      | A19 (M)              | Ħ         |      | Extended address bit 19.                                                                                                                                  |

| 60      | SIXTN* (S)           | Ĺ         | 0.C. | The signal generated by 16-bit slaves in response to the 16-bit request signal sXTRQ*.                                                                    |

| 61      | A20 (M)              | н         |      | Extended address bit 20.                                                                                                                                  |

| 62      | A21 (M)              | Н         |      | Extended address bit 21.                                                                                                                                  |

| 63      | A22 (M)              | H         |      | Extended address bit 22.                                                                                                                                  |

| 64      | A23 (M)              | H         |      | Extended address bit 23.                                                                                                                                  |

| 65      | NDEF                 |           |      | Not to be defined signal.                                                                                                                                 |

| 66      | NDEF                 |           |      | Not to be defined signal.                                                                                                                                 |

| 67      | PHANTOM® (M/S)       | L         | 0.C. | A bus signal which disables normal stave devices and enables phantom<br>staves—primarily used for bootstrapping systems without hardware<br>front panets. |

| 88      | MWRT (B)             | н         |      | pWR* - sQUT (logic equation). This signal must follow pWR* by not morthan 30 ns. (See note, Section 2.7.5.3)                                              |

| 69      | RFU                  |           |      | Reserved for future use.                                                                                                                                  |

| 70      | GND (B)              |           |      | Common with pin 100.                                                                                                                                      |

| 71      | RFU                  |           |      | Reserved for future use.                                                                                                                                  |

| 72      | RDY (S)              | H         | O.C. | See comments for pin 3.                                                                                                                                   |

| 73      | INT* (S)             | Ë         | O.C. | The primary interrupt request bus signal.                                                                                                                 |

| 74      | HOLD" (M)            | ĩ         | 0.C. | The control signal used in conjunction with pHLDA to coordinate bus master transfer operations.                                                           |

| 75      | RESET*(B)            | L         | Q.C. | The reset signal to reset bus master devices. This signal must be active with POC* and may also be generated by external means.                           |

| 76      | oSYNC (M)            | H         |      |                                                                                                                                                           |

| π       | pWR" (M)             | ï         |      | The control signal signifying the presence of<br>valid data on 00 ous or data ous.                                                                        |

| 78      | pDSIN (M)            | н         |      | The control signal that requests data on the Di<br>bus or data bus from the currently addressed slave.                                                    |

| 79      | AO (M)               | н         |      | Address bit 0 (least significant).                                                                                                                        |

| 80      | A1 (M)               | Ĥ         |      | Address bit 1.                                                                                                                                            |

| 81      | A2 (M)               | H         |      | Address bit 2.                                                                                                                                            |

| 82      | A6 (M)               | H         |      | Address bit 6.                                                                                                                                            |

| 83      | A7 (M)               | Ĥ         |      | Address bit 7.                                                                                                                                            |

| 84      | AB (M)               | Ĥ         |      | Address bit 8.                                                                                                                                            |

| 85      | A13 (M)              | Ĥ         |      | Address bit 13.                                                                                                                                           |

| 86      | A14 (M)              | Ж         |      | Address bit 14.                                                                                                                                           |

| 87      | A11 (M)              | Ä         |      | Address bit 11.                                                                                                                                           |

| 88      | DO2 (M)/DATA2 (M/S)  | H         |      | Data out bit 2, bidirectional data bit 2.                                                                                                                 |

| 89      | DO3 (M)/DATA3 (M/S)  | H         |      | Data out bit 3, bidirectional data bit 3.                                                                                                                 |

| 90      | DO7 (M)/DATA7 (M/S)  | H         |      | Data out bit 7, bidirectional data bit 7.                                                                                                                 |

| 91      | DI4 (S)/DATA12 (M/S) | Ä         |      | Data in bit 4 and bidirectional data bit 12.                                                                                                              |

| 92      | 015 (S)/DATA13 (M/S) | Ä         |      | Data in bit 5 and bidirectional data bit 13.                                                                                                              |

| 93      | DIS (S)/DATA14 (M/S) | Ä         |      | Data in bit 5 and bidirectional data bit 14.                                                                                                              |

| 94      | DI1 (S)/DATA9 (M/S)  | H         |      | Data in bit 1 and bidirectional data bit 9.                                                                                                               |

| 95      | DIO (S)/DATAS (M/S)  | Я         |      | Data in bit 0 (least significant for 8-bit data) and bidirectional data bit 8.                                                                            |

| 96      | sinta (M)            | H         |      | The status signal identifying the bus input cycle(s) that may follow an accepted interrupt request presented on INT*.                                     |

| 97      | sW0* (M)             | F         |      | The status signal identifying a bus cycle which transfers data from a bus master to a slave.                                                              |

| 98      |                      |           |      |                                                                                                                                                           |

| 99      | POC* (8)             | L         |      | The power-on clear signal for all bus devices; when this signal goes low, it must stay low for at least 200 nanoseconds.                                  |

| 100     | GND (8)              |           |      | System ground.                                                                                                                                            |

7200-9120-00-00

Rev. A (6-19-0-7