# CPU OPERATION

PolyMorphic Systems

460 Ward Drive Santa Barbara California 93111 (805) 967-2351

This manual is PolyMorphic Systems part number 810112 Copyright 1977, Interactive Products Corporation.

# Central Processor Unit Theory of Operation

## TABLE OF CONTENTS

|    |                                                                                                                                                                                               | PAGE                                               |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1. | INTRODUCTION                                                                                                                                                                                  | 1                                                  |

| 2. | OPERATIONAL THEORY 2.1 CPU 2.1.1 Interrupt Sequences 2.1.2 Halt Sequences 2.1.3 Start-Up Sequence 2.1.4 Central Processor Unit Architectur 2.1.5 8080 Instruction Set                         | 2<br>7<br>9<br>9<br>9                              |

|    | 2.2 USART OPTION 2.2.1 Communications Format 2.2.2 Receiver 2.2.3 Transmitter 2.2.4 Modem Control 2.2.5 I/O Control 2.2.6 Mode Selection 2.2.7 USART Programming Hints 2.2.8 USART Addressing | 22<br>23<br>26<br>27<br>28<br>28<br>29<br>31<br>32 |

|    | 2.3 BAUD RATE GENERATOR OPERATION 2.3.1 Baud Rate 2.3.2 USART Interrupts 2.3.3 Device Number                                                                                                  | 33<br>33<br>35<br>35                               |

|    | 2.4 REAL-TIME CLOCK                                                                                                                                                                           | 36                                                 |

|    | 2.5 SINGLE-STEP LOGIC                                                                                                                                                                         | 36                                                 |

|    | 2.6 VECTORED INTERRUPTS                                                                                                                                                                       | 36                                                 |

| 3. | CUSTOMER INSTALLED OPTIONS 3.1 SINTA 3.2 PINT 3.3 PHANTOM MEMORY 3.4 RELOCATION OF CPU ONBOARD MEMORY 3.5 REAL-TIME CLOCK JUMPER                                                              | 38<br>38<br>38<br>38<br>40<br>41                   |

| 1. | POLYMORPHIC SYSTEMS 8080 CPU CARD BUS                                                                                                                                                         | 41                                                 |

|    | FUNCTIONAL LISTING, 8080 INSTRUCTION SET                                                                                                                                                      | 46                                                 |

|    | NUMERICAL LISTING, 8080 INSTRUCTION SET                                                                                                                                                       | 49                                                 |

|    | HEY - ASCIT TARIE                                                                                                                                                                             | <b>E</b> 1                                         |

#### 1. INTRODUCTION

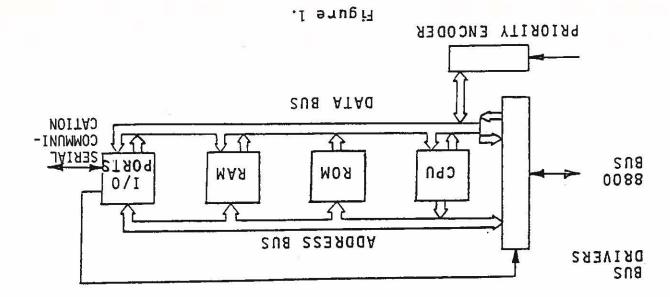

The 8080 CPU card is a member of PolyMorphic Systems' complete line of microcomputer system components. The CPU card is compatible with the industry standard S-100 bus. In addition to the 8080 CPU chip, the card also contains 512 bytes of read-write memory, sockets for 3072 bytes of read-only memory, an optional serial I/O port, a real-time clock interrupt, an instruction single-step interrupt, and a priority encoder for the 8-level priority interrupt system.

The 8080 CPU contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. The 8080 has a 16-bit program counter, allowing direct addressing of up to 64K bytes of memory. A 16-bit stack pointer addresses an external last in/first out stack which may be located in any part of memory. The program counter, flags, accumulator, or general purpose registers may be stored and retreived from this stack. The 8080 instruction set includes arithmetic and logical operations between the accumulator and generalpurpose registers, immediate data, or memory. Data may be moved between the accumulator, general purpose registers, and memory in 8 or 16-bit words. Double precision arithmetic and stack manipulation operators extend the capability of the 8080. Conditional and unconditional jump and call instructions are provided, as are computed jumps. Instructions are variable length and execute in 2-18 microseconds.

The CPU card provides 512 bytes of 450 nS RAM and sockets for three 2308 ROMs or 2708 EPROMs. The ROM sockets normally hold the resident portion of the operating system on the POLY 88 and System 88 microcomputer systems. They may be used for the user's own software in custom applications.

A programmable serial communications interface using an 8251 USART is included on the card (optional when CPU card is purchased separately as a kit). The mode of operation (synchronous or asynchronous), data format, control character format, parity, and transmission rate are all under program control. Two sockets on the CPU card allow the connection of minicards providing RS-232 or current loop, and Byte or Polyphase cassette interfaces.

A 50 or 60 Hertz real time clock interrupt is provided on the card along with a single step interrupt. The single step interrupt allows single insruction execution, for debugging purposes, under software control. Eight vectored interrupts are provided on the card for use with these or external interrupts.

#### 2. OPERATIONAL THEORY -

#### 2.1 CPU

The 8080 CPU, 8224 clock generator, and 74LS174 status latch perform all system processing operations and provide a timing reference for all other circuitry on the card and the S-100 bus. The CPU generates all of the address and control signals necessary to access memory and I/O ports both on the CPU card and the S-100 bus. The CPU responds to interrupts originating from devices on the bus or the CPU card. The priority encoder forms RST (restart) instructions vectoring the CPU to a different location in response to each interrupt.

The activities of the CPU set are cyclical. The CPU fetches an instruction, performs the operations required, fetches the next instruction, and so on. This orderly sequence of events requires precise timing. The 8224 clock generator provides the primary timing reference for the system. The 8224 produces the two-phase timing inputs (01 and 02) for the 8080. The 01 and 02 signals define a cycle of approximately 540ns duration. All processing activities of the CPU set are referred to the period of 01 and 02 clock signals.

Within the 8080 CPU set, an instruction cycle is defined as the time required to fetch and execute an instruction. During the fetch, a selected instruction (one, two, or three bytes) is extracted from memory and deposited in the CPU's operating registers. During the execution part, the instruction is decoded and translated into specific processing activities.

Every instruction cycle consists of one, two, three, four, or five machine cycles. A machine cycle is required each time the CPU accesses memory or an I/O port. The fetch portion of an instruction cycle requires one machine cycle for each byte to be fetched. The duration of the execution portion of the instruction cycle depends on the kind of instruction that has been fetched. Some instructions do not require any machine cycles other than those necessary to fetch the instruction; other instructions, however, require additional machine cycles to write or read data to or from memory or I/O devices.

Each machine cycle consists of three, four, or five states. A state is the smallest unit of processing activity and is defined as the interval between two successive positive-going transitions of the 01 clock pulse.

There are three exceptions to the defined duration of a state. They are the WAIT state, the hold(HLDA) state and the halt(HLTA) state. Because WAIT, HLDA, and HLTA states depend upon external events, they are by their nature of indeterminate length. Even these exceptional states, however, must be synchronized with the pulses of the driving clock. Thus the duration of all states, including these, are integral multiples of the clock pulse.

To summarize, then, each clock period marks a state; three to

Tive states comprise a machine cycle; and one to five machine cycles comprise an instruction cycle. A full instruction cycle requires anywhere from four to seventeen states for its completion, depending on the kind of instruction involved.

There is just one consideration that determines how many machine cycles are required in any given instruction cycle: the number of times that the processor must reference a memory address or an I/O address, in order to fetch and execute the instruction. Like many processors, the 8080 is so constructed that it transmits one address per machine cycle. Thus, if the fetching and execution of an instruction requires two memory references, then the instruction cycle associated with that instruction consists of two machine cycles. If five such references are called for, then the instruction cycle contains five machine cycles.

Every instruction cycle has at least one reference to memory, during which the instruction is fetched. An instruction cycle must always have a fetch, even if the execution of instruction requires no further references to memory. The first machine cycle in every instruction cycle is therefore a FETCH. Beyond that, there are no fast rules. It depends on the kind of instruction. The input (INP) and the output (OUT) instructions each require the input (INP) and the output (OUT) instructions each require the instruction; a MEM-CALL of the cycles: a FETCH, to obtain the instruction; a MEM-CALL of the cycles of the object peripheral; and an INPUT of an OUTPUT machine cycle, to complete the transfer.

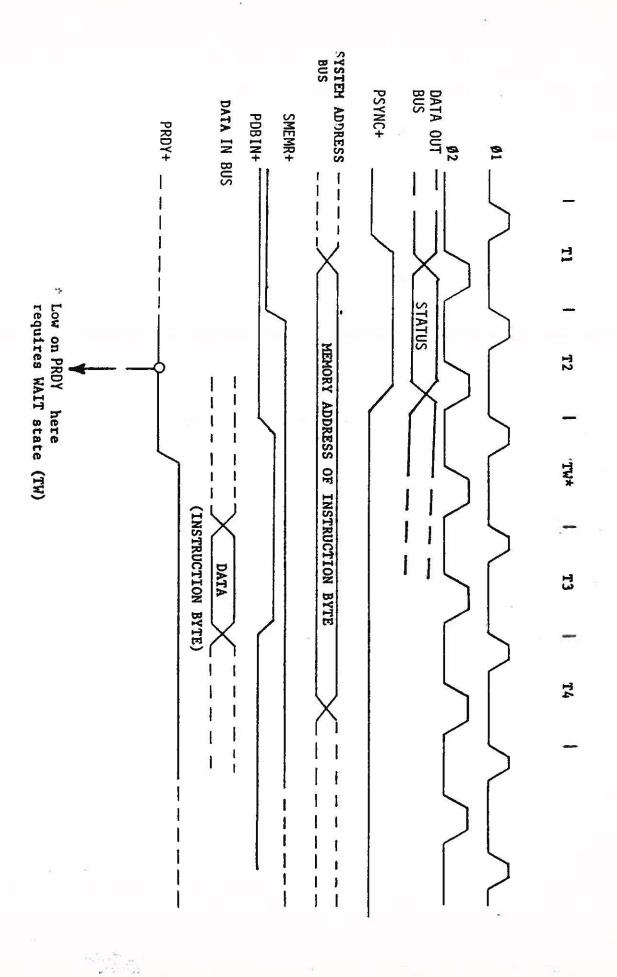

Every machine cycle within an instruction cycle consists of three to five active states (referred to as Tl, T2, T3, T4, and T5). The actual number of states depends upon the instruction being executed, and on the particular machine cycle within the greater instruction cycle. Figure 2 shows the timing relationships in a typical FETCH machine cycle. Events that occur in each state are referred to transitions of the 01 and 02 clock pulses.

At the beginning of each machine cycle (in state Tl), the 8080 activates its SYNC output and issues status information onto the status bus just after the rising edge of 01 of state T2. The status information is also available on the data bus during T1.

FIGURE 2 . TYPICAL FETCH MACHINE CYCLE

The status information indicates the type of machine cycle in progress. SINTA goes high during an interrupt acknowledgement cycle; SMEMR, when high, signals a memory read cycle; SINP and SOUT, respectively, indicate input and output data transfers. SWO goes low during output or memory write cycles, and HLTA is active (high) only when the CPU is halted. Note that there is not a separate status line for a memory write cycle. This may be generated by the logic SWO -SOUT. After PSYNC returns low, PDBIN goes high, indicating the CPU is expecting data on the Data In Bus.

The rising edge of 02 during Tl loads the address lines A0-Al5. These lines become stable within a brief delay of the 02 clocking pulse, and they remain stable until the first 02 pulse after state T3. This gives the processor ample time to read the data returned from memory.

Once the processor has sent an address to memory, there is an opportunity for the memory to request a WAIT. This it does by pulling the PRDY+ line low. As long as the PRDY line remains low, the CPU Set will idle, giving the memory time to respond to the addressed data request. The processor responds to a wait request by entering an alternative state (TW) at the end of T2, rather than proceeding directly to the T3 state. A wait period may be of indefinite duration. The 8080 remains in the waiting condition until its READY line again goes high. The cycle may then proceed, beginning with the rising edge of the next Ol clock. A WAIT interval will therefore consist of an integral number of TW states and will always be a multiple of the clock period.

The events that take place during the T3 state are determined by the kind of machine cycle in progress. In a FETCH machine cycle, the CPU interprets the data on the Data In Bus as an instruction. During a MEMORY READ, signals on the same bus are interpreted as a data word. The CPU itself outputs data on this bus during a MEMORY WRITE machine cycle. And during I/O operations, the CPU may either transmit or receive data, depending on whether an IN-PUT or an OUTPUT operation is involved. Consider the following two examples.

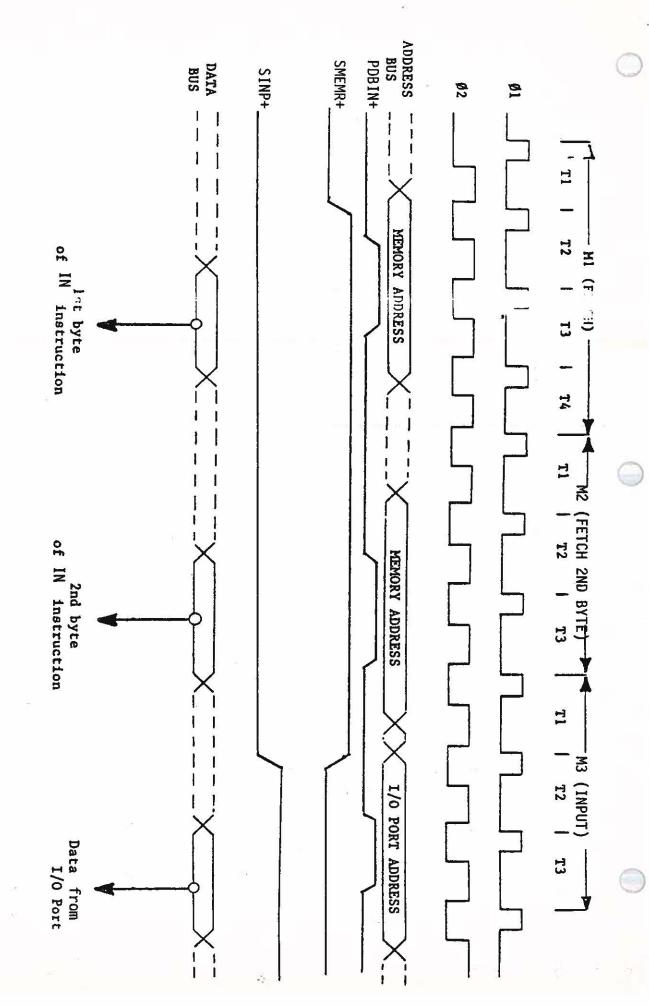

Figure 3 illustrates the timing that is characteristic of an input instruction cycle. During the first machine cycle M1), the first byte of the two-byte IN instruction is fetched from memory. The 8080 places the 16-bit memory address on the address bus near the end of state T1. The memory read status signal (SMEMR) during state T2. During the next machine cycle (M2), the second byte of instruction is fetched. During the third machine cycle (M3), the IN instruction is executed. The 8080 duplicates the 8-bit I/O address on address lines A0-7 and A8-15. The 8080 activates the I/O read status signal (SINP) during states T2 of this cycle.

FIGURE 3. INPUT INSTRUCTION CYCLE

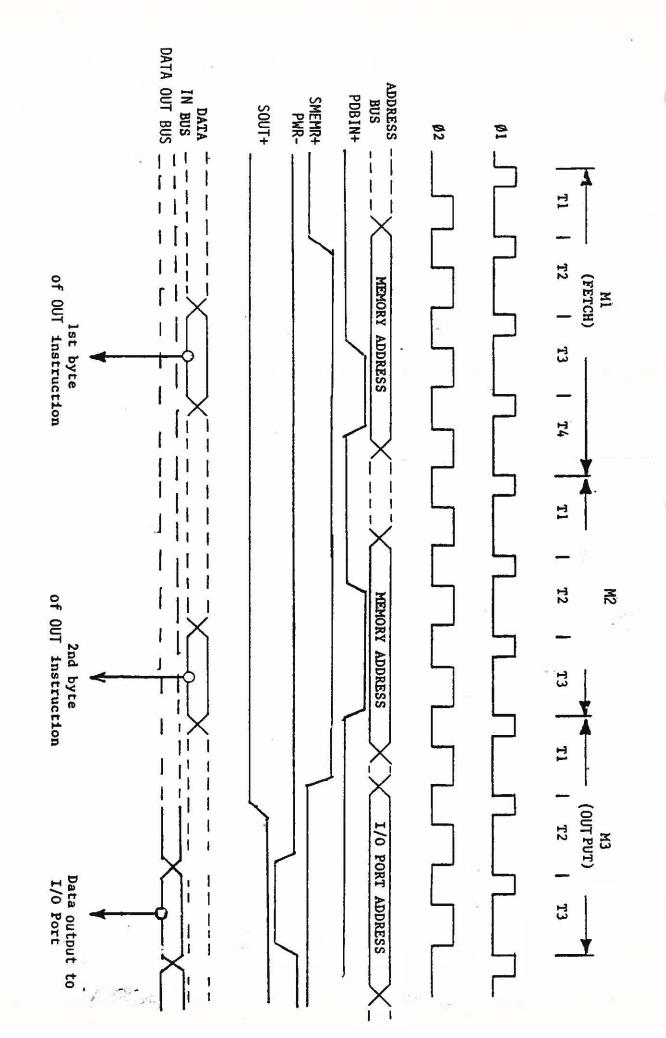

Figure 4 illustrates an instruction cycle during which the CPU outputs data. During the first two machine cycles (Ml and M2), the CPU fetches the two-byte OUT instruction. During the third machine cycle (M3), the OUT instruction is executed. The 8080 duplicates the 8-bit I/O address on lines A0-7 and A8-15. The 8080 activates the I/O address on status signal (SOUT) at the beginning of state T2 of this cycle. The 8080 outputs the data onto the Data Out Bus at the end of state T2. Data on the bus remains stable throughout the remainder of the machine cycle.

Observe that a PRDY signal is necessary for completion of an output machine cycle. Unless such an indication is present, the processor enters the TW state, following the T2 state. Data on the output lines remains stable in the interim, and the processing cycle will not proceed until the PRDY line again goes high.

The negative-going leading edge of WR is referred to the rising edge of the first 01 clock pulse following T2. Thus, WR coincides with the appearance of stable data on the system bus. WR remains low until re-triggered by the leading edge of 02, during the state following T3. Note that any TW states intervening between T2 and T3 of the output machine cycle will necessarily extend WR/.

All processor machine cycles consist of at least three states: T1, T2, and T3, as just described. If the CPU has to wait for a PRDY response, then the machine cycle may also contain one or more TW ferred to or from the CPU.

After the T3 state, however, it becomes difficult to generalize. T4 and T5 states are available, if the execution of a particular instruction requires them. But not all machine cycles make use of these states. It depends upon the kind of instruction being executed, and on the particular machine cycle within the instruction cycle. The processor will terminate any machine cycle as soon as its processing activities are completed, rather than proceeding through the T4 and T5 states every time. Thus the 8080 may exit a machine cycle following the T3, the T4, or the T5 state and proceed directly to the T1 state of the next machine cycle.

#### 2.1.1 INTERRUPT SEQUENCES

The 8080 has the built-in capacity to handle external interrupt requests. Peripheral logic can initiate an interrut simply by driving any vectored interrupt line low. The interrupt input is asynchronous, and a request may therefore originate at any time during any instruction cycle. An interrupt request acts in coincidence with the 02 clock to set the internal interrupt latch. This event takes place during the last state of the instruction cycle in which the request occurs, thus ensuring that any instruction in progress is completed before the interrupt can be processed.

The INTA (Interrupt Acknowledge) machine cycle which follows the arrival of an enabled interrupt request resembles an ordinary FETCH machine cycle in most respects. The contents of the program counter are latched onto the address lines during Tl, but the counter itself is not incremented during the INTA machine

FIGURE 4 . OUTPUT INSTRUCTION CYCLE

cycle, as it otherwise would be. In this way, the pre-interrupt status of the program counter is preserved, so that data in the counter may be saved in the stack. This in turn permits an orderly return to the interrupted program after the interrupt request has been processed.

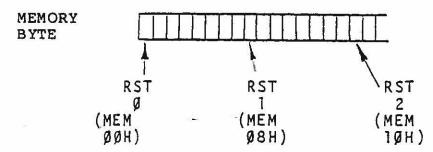

The INTA output is used to gate an "interrupt instruction" onto the system data bus during state T3. The interrupt instruction is a one-byte RST which causes program control to branch to an interrupt routine. The RST interrupt instruction is supplied by the priority encoder.

#### 2.1.2 HALT SEQUENCES

When a halt instruction (HLT) is executed, the 8080 enters the halt state after state T2 of the next machine cycle. There are only three ways in which the 8080 can exit the halt state:

-A low on the reset input (PRESET) will always reset the 8080 to state T1; reset also clears the program counter. -An interrupt will cause the 8080 to exit the halt state and enter state T1 on the rising edge of the next 01 clock pulse.

Note: The interrupt enable (INTE) flag must be set when the halt state is entered; otherwise, the 8080 will only be able to exit via a reset signal.

## 2.1.3 START-UP SEQUENCE

When power is applied initially to the 8080, the processor begins operating immediately. The slow transition of the power supply rise is sensed by an internal Schmitt Trigger which produces a synchronized RESET signal which restores the processor's internal program counter to zero. Program execution thus begins with memory location zero.

#### 2.1.4 8080 CENTRAL PROCESSOR ARCHITECTURE

The next few paragraphs discuss the functional structure of the 8080 Central Processor Unit. Throughout this discussion we have assumed that you have had some experience with assembly language programming; the purpose of Section 2.1.4 is merely to familiarize you with the particular structure of the 8080.

The 8080 CPU contains six general purpose registers which can either be used as single registers (containing 8 bits of data) or as register pairs (containing 16 bits of data). These registers are: B, C, D, E, H, and L. (The register pairs are BC, DE, and HL). Single bytes of data (8-bits) can be transferred between these registers, and between these registers and memory. In addition, one data byte can be moved from these registers into a special register called the accumulator, and from the accumulator into any register. These general purpose registers are used to store data and memory addresses. When used as pairs, the B, D, and H registers contain the most significant byte of the 16-bit contents of the register pair, and the C, E, and L registers contain the least significant byte.

The accumulator (register A) is a special register used by the arithmetic and logical unit of the computer. Whenever an arithmetic operation is performed on data, the data to be operated upon is usually placed in the accumulator, the operation performed, and the result of the operation then left in the accumulator.

EXAMPLE: SUB B

The above instruction tells the machine to subtract the contents of the B register from the contents of the accumulator, and leave the results in the accumulator. Besides the contents of other registers, you may move the contents of a memory location into the accumulator. (For more information on the 8080 instruction set, see Section 2.1.5, 8080 INSTRUCTION SET.)

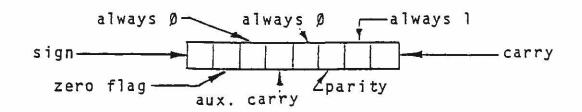

Special one-bit registers are called "flags," which signal certain conditions which may arise as a result of arithmetic operations. The contents of these five flags and the contents of the accumulator are contained within a special register called the PSW (Program Status Word).

EXAMPLE:

PUSH PSW

The above instruction tells the machine to put (or "push") the contents of the flags and the contents of the accumulator onto the "stack."

Another special register is the PC register (Program Counter). This register contains the address of the next program instruction to be executed. Another register, the SP (Stack Pointer) register, contains the address of the most recent stack entry.

You can also use the general purpose register pairs as addressing registers; that is, to point to the memory location whose contents you want to move into a register. For example, the contents of the HL register pair are always used as the address of the memory byte to be accessed when the symbol M appears in an instruction.

**EXAMPLE:**

MOV B,M

The above instruction says: move the contents of the memory byte whose address is in the HL register pair into the B register.

Other instructions use the B and D register pairs to address memory bytes whose contents are to be moved into the accumulator. (Note: these kinds of instructions always move one byte only.)

2.1.5 8080 INSTRUCTION SET

In the 8080 CPU there are five flags.

Page 11 Central Processor Unit Theory of Operation PolyMorphic Systems

#### CARRY FLAG

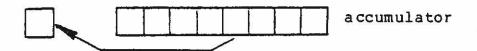

When a number is added to the value in the accumulator, the result may include a carry out of the left-hand bit, the bit of highest significance. This carry "sets" the carry flag to 1.

accumulator

When an addition does not result in a carry out of the most significant accumulator bit, the carry flag is 0.

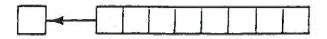

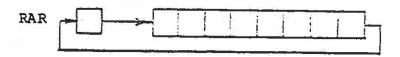

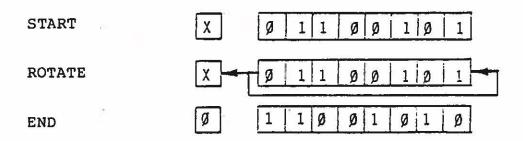

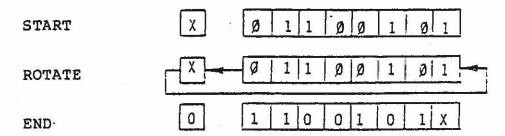

The carry flag can be set to 0 or 1 by other operations. For instance, the instructions RAR (rotate accumulator right) and RAL (rotate accumulator left) affect the carry flag. In RAR, the least significant bit in the accumulator moves into carry, the bit that was in carry goes into the most significant place in the accumulator, and all other accumulator bits move one place to the right.

RAL is the opposite of RAR.

The carry flag can be affected by logical operations as well as addition, subtraction, and rotation.

#### AUXILIARY CARRY FLAG

A carry out of the "third bit" (fourth place -- 2^3) sets the auxiliary carry flag:

The auxiliary carry flag cannot be tested directly, and exists only to enable the DAA instruction for decimal conversion.

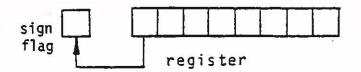

#### SIGN FLAG

The sign flag is set by certain instructions to duplicate the most significant bit in a register. The most significant bit in a register can be interpreted as the sign of the data quantity when the quantity is considered to be two's complement.

#### ZERO FLAG

The zero flag is set to 1 at the end of certain operations if the byte resulting from the operations is all zeroes; the zero bit is reset to 0 if the result is not zero.

A result that consists of eight zeroes plus a carry out of the seventh bit sets the zero flag to 1, and also sets the carry flag to 1.

#### PARITY FLAG

"Parity" refers to whether the number of l's in a byte is even or odd. Byte parity is checked after certain operations. If the number is even, parity is "even" and the parity flag is set to 1; if there is an odd number of l's, parity is "odd" and the parity flag is reset to 0.

#### INSTRUCTIONS

Following is a complete list with discussion of all the operations built into the Poly central processor. The discussion divides the operations into groups of related instructions. Each operation is identified by a "mnemonic" which corresponds to an instruction in machine language ("opcode"). For a chart showing all assembly mnemonics and the associated opcodes, see appendix.

CARRY FLAG INSTRUCTIONS. Two instructions affect the carry flag alone:

CMC (complement carry). Complement the carry flag -- Set it to 0 if it is 1 or to 1 if it is 0.

STC (set carry). Set the carry bit to 1.

SINGLE REGISTER INSTRUCTIONS. These instructions affect the contents of one memory address or any one of the CPU registers -- one byte. If memory, the instruction affects the byte addressed by pair H.

INR (increment register or memory). Increment the affected register or memory byte by 1 -- add 1 to it.

DCR (decrement register or memory). Decrement register or memory byte by 1. This instruction is th opposite of INR -- it is identical to it except that it reduces the affected byte by 1. All flags may be affected.

CMA (complement accumulator). Complement the byte in the accumulator -- change every 1 to 0 and 0 to 1. No flags are affected.

DAA (decimal adjust accumulator). Adjust the byte in the accumulator to form two groups of four bits, each representing one decimal digit. This instruction is rather complicated, treating as it does the awkard relationship between binary and decimal. It is used -- infrequently -- when a decimal output is desired. DAA adjusts the first four bits and second four bits of the accumulator byte separately. First, the less significant four bits of the accumulator byte are compared to 1001 to see if they are greater than nine. If they are (or if the auxiliary carry flag is set to 1), then the accumulator is incremented by six -- which reduces the value of the four bits to nine or less. Next, if the four more significant bits of the accumulator byte represent a number greater than nine (or if the carry flag is set to 1), then these four bits are incremented by six, so that they will represent a value of nine or less. Note that either of these two adjustments may have produced a carry. A carry out of the four less significant bits sets the auxiliary carry flag to 1; otherwise, it is reset. A carry out of the accumulator byte sets the carry flag to 1; otherwise, it retains its previous value. All other flags may be affected.

#### NO-OPERATION INSTRUCTION:

One instruction results in no operation.

NOP (no operation). Move on to the next instruction in sequence. No flags are affected.

#### DATA TRANSFER INSTRUCTIONS:

These instructions transfer data between registers or between memory and registers.

MOV (move). Move one byte of data from an indicated register or memory to another individual register or memory. The data also remains in its original location.

Format example: MOV B,A. "Move the byte in A (accumulator) into register B." Note that the format states the affected register first. Data cannot be moved from one memory address to another in a single operation. Data moved out of memory is always taken from the location addressed by H & L. No flags are affected.

STAX (store accumulator). Store the contents of the accumulator into the memory location addressed by register pair B or pair D. No flags are affected.

LDAX (load accumulator). Store the contents of the memory location addressed by the indicated register pair (pair B or pair D) into the accumulator. No flags are affected.

REGISTER OR MEMORY TO ACCUMULATOR INSTRUCTIONS.

These instructions operate on the accumulator using a byte taken from a register or from memory. Memory is taken from the memory location addressed by the data pointer (H & L). Results are left

in the accumulator.

ADD (add register or memory to accumulator). Add the byte in one register or in memory to the value in the accumulator. ADD A doubles the accumulator. All flags may be affected.

ADC (add register or memory and carry flag bit to accumulator). Add the byte from a specified location, plus the value of the carry flag, to the value in the accumulator. All flags may be affected.

SUB (subtract register or memory from accumulator). Subtract the byte in a specified register or memory location from the value in the accumulator. SUB A subtracts the accumulator from itself, leaving it (and the carry flag) at zero. All flags may be affected.

SBB (subtract register or memory and carry flag bit -- "borrow" -- from accumulator). Subtract the byte taken from a specified location, plus the value of the carry flag, from the accumulator. All flags may be affected.

ANA (AND register or memory with accumulator). AND the specified byte with the accumulator. ANA is often used to zero part of the accumulator. Carry, zero, sign, and parity flags may be affected.

XRA (XOR register or memory with accumulator). XOR the specified byte with the value in the accumulator. XRA A zeroes the accumulator. Then a MOV from A to a register zeroes that register. All flags may be affected.

ORA (OR register or memory with accumulator). OR the specified byte with the value in the accumulator. This instruction is often used to set part of the accumulator to 1's. Flags affected: carry flag is zeroed; zero, sign, and parity flags may be affected.

CMP (compare register or memory with accumulator). Compare the specified byte to the contents of the accumulator. In effect, this determines if the specified byte is smaller than, equal to, or larger than the accumulator byte. Flags: the zero flag is l if the quantities are equal, and 0 if they are unequal. The carry flag is l if the register or memory byte is larger than the accumulator byte, and 0 otherwise (but when the two compared values differ in sign, the sense of the carry flag is reversed). All other flags may also be affected.

ROTATE ACCUMULATOR INSTRUCTIONS.

These instructions rotate the contents of the accumulator -- move a bit from one end, and shift the other bits one place. Rotation can be to the left or to the right, and involves the carry flag bit (but no other).

RLC (rotate accumulator left and into carry). Move the most significant bit in the accumulator (left-hand bit) into the carry flag and into the least significant place in the accumulator.

Page 15 Central Processor Unit Theory of Operation PolyMorphic Systems

All other bits shift one place to the left.

RRC (rotate accumulator right and into carry). Move the least significant bit from the accumulator into carry and into the most significant place; the opposite of the instruction above.

RAL (rotate accumulator left, through carry). Move the most significant accumulator bit into carry, and the carry flag bit into the least significant place; shift all other accumulator bits left.

RAR (rotate accumulator right, through carry). Move the least significant bit to carry, and move carry into the most significant place; the opposite of the instruction above.

REGISTER PAIR INSTRUCTIONS.

These instructions operate on the register pairs.

PUSH (push data onto stack). Store the value in the specified register pair into the two bytes of memory addressed by the stack pointer. Such data is said to be "pushed" onto "the stack." The more significant byte goes into address SP-1, the less significant into address SP-2. Indicating PSW (processor status word) stores the current accumulator value at SP-1 and a byte incorporating all the flags in SP-2:

The stack pointer is left pointing to the address where the second byte has been stored. Flags are not affected.

POP (pop data off stack). Store data from the stack into the indicated register pair. The byte of data at SP is stored into the less significant register; the byte at SP+1 goes into the more significant register. If register pair PSW is indicated, the byte at SP provides the bits of the flags, and the byte at SP+1 goes into the accumulator. This instruction is the opposite of the one above.

DAD (double add). Add the two-byte value in the indicated register pair (B, D, or H) to the two-byte value in pair H, and leave the result in pair H. Flag affected: carry.

INX (increment extended register pair). Increment the value in a register pair by 1 -- add 1 to it. No flags are affected.

DCX (decrement extended register pair). Subtract 1 from a register pair. The opposite of the above. No flags are affected.

XCHG (exchange registers). Move the value in pair H to pair D and vice versa. No flags are affected.

XTHL (exchange H & L with stack). Exchange the value in L with the value in the memory location addressed by the stack pointer and exchange the value in H with the value in that memory address plus one (SP plus 1). No flags are affected.

SPHL (load SP from H & L). Load the value in register pair H into the stack pointer register. That value is now the stack address pointed to by the stack pointer. No flags are affected.

#### IMMEDIATE INSTRUCTIONS.

These instructions operate on one or two bytes of data, included in the instruction itself. The data immediately follows the opcode (hence "immediate").

LXI (load extended immediate). Load the indicated register pair with the two bytes immediately following. The first byte goes into the lower-order register, the second into the higher-order register. No flags are affected.

MVI (move immediate). Move the following byte into the specified register or into the memory location addressed by the data pointer. This instruction resembles LXI except that it enters only one byte of data (and therefore can be used to load a memory location. No flags are affected.

ADI (add immediate to accumulator). Add the following byte to the value in the accumulator, and leave the result in the accumulator. All flags may be affected.

ACI (add immediate, plus the carry bit, to accumulator). Add the following byte, plus the value of the carry flag bit, to the value in the accumulator, and leave the result in the accumulator. All flags may be affected.

SUI (subtract immediate from accumulator). Subtract the following byte from the value in the accumulator, and leave the result in the accumulator. All flags may be affected. This instruction is the subtraction equivalent of ADI above.

SBI (subtract immediate, and "borrow," from accumulator). Subtract the byte immediately following, and the value of the carry flag bit, from the value in the accumulator, and leave the result in the accumulator. This is the subtraction equivalent of ACI above. All flags may be affected.

ANI (AND immediate with accumulator). AND the byte immediately following with the value in the accumulator, and leave the result in the accumulator. Carry, zero, sign, and parity flags may be affected.

XRI (XOR immediate with accumulator). XOR the byte immediately following with the value in the accumulator, and leave the result in the accumulator. The carry flag is set to 0. Zero, sign, and parity flags may also be affected.

ORI (OR immediate with accumulator). OR the byte immediately following with the value in the accumulator, and leave the result in the accumulator. The carry flag is set to 0. Zero, sign, and parity flags may also be affected.

CPI (compare immediate data with accumulators). Compare the following byte to the value in the accumulator. The zero flag is set to 1 if the two values are equal and 0 if they are unequal. The carry flag is set to 1 if the immediate data value is larger than the accumulator value, and set to 0 otherwise. (But if the two values differ in sign, the sense of the carry flag is reversed.) All other flags may be affected.

#### DIRECT ADDRESSING INSTRUCTION.

These instructions involve the contents of memory addresses; the addresses are included as part of the instruction. The instruction states the address "backwards" -- first the less significant address byte, then the more significant. These instructions do not affect flags.

STA (store accumulator direct). Store the value in the accumulator into the memory location addressed in the instruction.

LDA (load accumulator direct). Load the contents of the memory location addressed in the instruction into the accumulator. No flags are affected. This instruction is the opposite of STA above.

SHLD (store H and L direct). Store the contents of register pair H into the memory location addressed in the instruction. No flags are affected.

LHLD (load accumulator direct). Load the contents of the memory location addressed by the instruction into the L register, and the contents of the next higher address into the H register. This

is the opposite of SHLD above.

#### JUMP INSTRUCTIONS

These instructions cause the computer to "jump" to another part of a program rather than continue to perform instructions in sequence. None of these instructions affects flags.

PCHL (load program counter with H & L). Load the contents of register H into the more significant byte of te program counter, and the contents of register L into the less significant byte. The next instruction executed will be the one now addressed by the program counter. Note that this instruction does not itself contain an address. All other jump instructions do.

JMP (jump). Execute the instruction located at the address given in the instruction, and continue sequentially. This is called an "unconditional jump." All the following jump instructions are "conditional."

JC (jump if carry). Jump to the instruction addressed by this instruction if the carry flag is set to 1. If the carry flag is 0, move on to the next instruction in sequence.

JNC (jump if no carry). Jump to the instruction addressed by this instruction if the carry flag is set to 0. If the carry flag is 1, move on to the next instruction in sequence. This instruction is the opposite of the above.

JZ (jump if zero). Jump to the instruction addressed by this instruction if the zero flag is set to 1. If the zero flag is set to 0, move on to the next instruction in sequence. Compare to JC. (Note that the "if zero" condition is met if the register in question is all zeroes, so that the zero flag is set to 1.)

JNZ (jump if not zero). Jump to the instruction addressed by this instruction if the zero flag is set to 0. If the zero flag is set to 1, move on to the next instruction in sequence. This instruction is the opposite of JZ above. Compare to JNC.

JM (jump if minus). Jump to the instruction addressed by this instruction if the sign flag is set to 1 ("minus"). If the sign flag is set to 0, move on to the next instruction in sequence. Compare to JC and JZ above.

JP (jump if plus). Jump to the instruction addressed by this instruction if the sign flag is set to 0 ("plus"). If the sign flag is set to 1, move on to the next instruction in sequence. This instruction is the opposite of JM above. Compare to JNC and JNZ.

JPE (jump if parity even). Jump to the instruction addressed by this instruction if the parity flag is set to 1 ("even parity"). If it is set to 0, move on to the next instruction in sequence. Compare to JC, JZ, and JM above.

JPO (jump if parity odd). Jump to the instruction addressed by this instruction if the parity flag is set to 0 ("parity odd").

If the parity flag is 1, move on to the next instruction in sequence. This instruction is the opposite of JPE above. Compare to JNC, JNZ, and JP above.

#### CALL SUBROUTINE INSTRUCTIONS

Like jump instructions, call instructions cause the computer to depart from sequential execution of instructions. Also like jump instructions, most are "conditional" -- most operate only if some condition is met. And as with jump instructions, execution of instructions continues in sequence starting with the instruction at the address called (stated in the call instruction). The two types of instructions also resemble one another in that the address included is stated "backwards" -- first the less significant address byte, then the more significant. Also, these instructions do not affect flags.

The two kinds of instructions differ in that a call instruction "pushes" an address onto "the stack" -- namely, the address of the instruction to which the computer will "return" when it has finished the subroutine.

CALL. Go to the subroutine addressed by this instruction, and begin sequential execution there. This is an "unconditional call," and corresponds to an unconditional jump. All other call instructions are conditional, and correspond to the conditional jump instructors, each triggered by the state of one of the flags.

CC (call if carry). Go to the subroutine addressed by this instruction if the carry flag is set to 1. If the carry flag is 0, move on to the next instruction in sequence.

CNC (call if no carry). Go to the subroutine addressed in this instruction if the carry flag is set to 0. If the carry flag is 1, move on to the next instruction in sequence. This instruction is the opposite of CC above.

CZ (call if zero). Go to the subroutine addressed by this instruction of the zero flag is set to 1. If the zero flag is 0, move on to the next instruction in sequence. Compare to CC.

CNZ (call if not zero). Go to the subroutine addressed by this instruction if the zero flag is set to 0. If the zero flag is 1, move on to the next instruction in sequence. This instruction is the opposite of CZ above. Compare to CNC.

CM (call if minus). Go to the subroutine addressed by this instruction if the sign flag is set to 1 ("minus"). If the sign flag is 0, move on to the next instruction in sequence. Compare to CC and CZ above.

CP (call if plus). Go to the subroutine addressed by this instruction if the sign flag is set to 0 ("plus"). If the sign flag is 1, move on to the next instruction. This instruction is the opposite of CM above. Compare to CNC and CNZ above.

CPE (call if parity even). Go to the subroutine addressed by this

instruction if the parity flag is set to 1 ("even parity"). If the parity flag is 0, move on to the next instruction in sequence. Compare to CC, CZ, and CM above.

CPO (call if parity odd). Go to the subroutine addressed in this instruction if the parity flag is set to 0. If the parity flag is 1, move on to the next instruction. This instruction is the reverse of CPE above. Compare to CNC, CNZ, and CP above.

### RETURN FROM SUBROUTINE INSTRUCTIONS.

These instructions get the computer back from subroutines to the instruction following the call instruction that caused it to depart. Specifically, they "pop" an address previously "pushed" onto "the stack" off of the stack and into the program counter, causing the computer to next execute the instruction located at that address. Execution then continues sequentially from there. Each return instruction is associated with a previous call insruction, i.e. the program counter always returns eventually to the point in a program that it previously departed from (to an instruction following a call instruction). Therefore the number of returns executed is always equal to the number of calls executed is always equal to the number of calls executed is always equal to the number of calls executed is always equal to the number of calls executed is always equal to the number of calls executed is always equal to the number of calls executed is always equal to the number of calls executed (unless the machine halts).

Since these instructions always "pop" addresses in the order opposite that in which they were "pushed," they can be said always to operate on the "next available address" in the stack, so that the address need not be stated in the instruction.

Like "jump" and call instructions, all but one of the return instructions are conditional upon the state of one of the flags. Flags are not affected by return instructions.

RET (return). Return to the most recently pushed address. This is an "unconditional return."

RC (return if carry). Return to the next address on the stack if the carry flag is 1. If the carry flag is 0, move on to the next instruction in sequence.

RNC (return if no carry). Return to the next address on the stack if the carry flag is 0. If the carry flag is 1, move on to the next instruction in sequence. This instruction is the opposite of RC above.

RZ (return if zero). Return to the next address on the stack if the zero flag is 1. If the zero flag is 0, move on to the next instruction in sequence. Compare to RC above.

RNZ (return if not zero). Return to the next address on the stack if the zero flag is 0. If the zero flag is 1, move on to the next instruction in sequence. This instruction is the opposite of RZ above. Compare to RNC above.

RM (return if minus). Return to the next address on the stack if the sign flag is 1 ("minus"). If the sign flag is 0, move on to

the next instruction in sequence. Compare to RC, RZ above.

RP (return if plus). Return to the next address on the stack if the sign flag is 0 ("plus"). If the sign flag is 0, move on to the next instruction in sequence. This instruction is the opposite of the instruction above. Compare to RNC, RNZ above.

RPE (return if parity even). Return to the next address on the stack if the parity flag is 1 ("even parity"). If the parity flag is 0, move on to the next instruction in sequence. Compare to RC, RZ, RM above.

RPO (return if parity odd). Return to the next address on the stack if the parity flag is 0 ("odd parity"). If the parity flag is 1, move on to the next instruction in sequence. This instruction is the opposite of RPE above. Compare to RNC, RNZ, RP above.

#### RESTART INSTRUCTION.

One special instruction, RST, resembles the call instructions in that it pushes a return address onto the stack and sends the computer off to another location. The address of the instruction following the RST instruction sequentially is pushed onto the stack, so that the computer will eventually return to its point of departure. Note that the RST instruction pushes the address of the instruction following RST — otherwise the computer would return to the RST instruction itself and be trapped in an endless loop.

RST sends the computer (i.e. the program counter) off to one of eight pre-determined memory locations, each the first of a sequence of eight bytes, making up the first sixty-four bytes of memory.

etc. through RST 7, at memory address 38H.

Actually, the eight bytes associated with each RST can be reached by means of other kinds of instructions — jump and call instructions — and need not comprise individual routines. In the POLY 88, all sixty-four of these bytes are used in the monitor (discussed later).

The CPU executes an RST at one of two times. An RST instruction may be written into a program, in which case the instruction is in effect a "call" instruction in shorter form -- one byte instead

of three. More usually, the CPU executes an RST when the running of a program is interrupted "from the outside". For instance, saving onto tape is a very slow process for the POLY 88, which can output data much faster than the tape recorder can properly record it. So the computer outputs data to the tape on an interrupt basis -- it occupies itself with other tasks until the output port electronics indicate that it is time to output another data item to the tape. This forces a restart, which puts a book marker into the program so the computer will be able to get back to its point of departure, and sends the program counter off to a pre-determined location to begin execution of a brief routine that causes the computer to output a data item to the tape.

#### INTERRUPT FLIP-FLOP INSTRUCTIONS.

Sometimes it is important not to permit interruptions of a program. For that reason, interrupts can be disabled—input or output electronics can be prevented from forcing a restart. Whether or not interrupts are disabled depends upon the state of a single flip—flop, called the interrupt flip—flop is reset to 0, from which time interrupts are disabled till the flip—flop is once again set to 1. No flags are affected.

EI (enable interrupt). Set the interrupt flip-flop to 1.

DI (disable interrupt). Reset the interrupt flip-flop to 0.

INPUT/OUTPUT INSTRUCTIONS.

These instructions cause the computer to input data from or output data to a device external to the computer -- like a keyboard.

To be precise, the instruction causes the CPU to open an input or output port, which is assumed to provide a connection with some device. No flags are affected.

IN (input). Load one byte from the designated input port into the accumulator.

OUT (output). Send the byte in the accumulator out to the designated output port.

#### HALT INSTRUCTION.

This instruction brings computer operations to a stop. It first increments the program counter -- adds 1 to it -- so that the computer will resume with the next instruction. No flags are affected.

HLT (halt). Increment the program counter, then stop.

#### 2.2 CPU USART OPTION

The USART is included on every assembled CPU card. It is an option which may be ordered separately for use with CPU card bits.

The USART option for the 8080 CPU card provides a very flexible

serial communications interface for the POLY 88 and system 88. The USART option and a software controllable baud rate generator. The USART may interface to two serial I/O devices. The device and its baud rate may be changed under the control of one output port. These interface through two "minicards" which mount to the rear of the POLY 88 or system 88 chassis. Interface cards are available for RS-232-C, current loop, Kansas City (Byte) Standard audio cassette, and the 2400 baud Polyphase cassette.

This note describes the USART option from a functional standpoint and then describes the various operating modes of the USART and how the USART may be programmed.

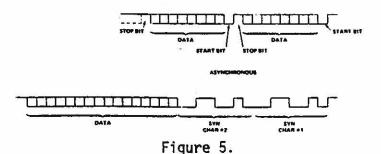

#### COMMUNICATIONS FORMATS

Serial communications, either on a data link or with a local peripheral, occurs in one of two basic formats: asynchronous or synchronous. These formats are similar in that they both require framing information to be added to the data to enable proper detection of the character at the receiving end. The major difference between the two formats is that the asynchronous format requires framing information to be added to each character, while the synchronous format adds framing information to blocks of data, or messages. Since the synchronous format is more efficient than the asynchronous format but requires more complex decoding it is typically found on high-speed data links, while the asynchronous format is used on lower-speed lines.

The asynchronous format starts with the basic data bits to be transmitted and adds a "START" bit to the front of them and one or more "STOP" bits behind them as they are transmitted. The START bit is a logical zero, or SPACE, and is defined as the positive voltage level by RS-232-C. The STOP bit is a logical one, or MARK, and is defined as the negative voltage level by RS-232-C.

In current loop applications, current flow normally indicates a MARK and lack of current a SPACE. The START bit tells the receiver to start assembling a character and allows the receiver to synchronize itself with the transmitter. Since this synchronization only has to last for the duration of the character (the next character will contain a new START bit), this method works quite well assuming a properly designed receiver. One or more STOP bits are added to the end of the character to ensure that the START bit of the next character will cause a transition on the communication line and to give the receiver time to "catch up" with the transmitter if its basic clock happens to be running slightly slower than the transmitter clock. If, on the other hand, the receiver clock happens to be running slightly faster than the transmitter clock, the receiver wil perceive gaps between characters but will still correctly decode the data. cause of this tolerance to minor frequency deviations, it is not necessary that the transmitter and receiver clocks be locked to the identical frequency for successful asynchronous communication.

The synchronous format, instead of adding bits to each character, groups characters into records and adds framing characters to the record. The framing characters are generally known as SYN charac-

ters and are used by the receiver to determine where the character boundaries are in a string of bits. Since synchronization must be held over a fairly long stream of data, bit synchronization is normally either extracted from the communication channel by the modem or supplied from an external source.

An example of the synchronous and asynchronous formats is shown in Figure 5. The synchronous format shown is fairly typical in that it requires two SYN characters at the start of the message.

The asynchronous format, also typical, requires a START bit preceding each character and a single STOP bit following it. In both cases, two 8-bit characters are to be transmitted. In the asynchronous mode, 10 x n bits are used to transmit n characters, and in the synchronous mode, 8n + 16 bits are used. For the example shown, the asynchronous mode is actually more efficient, using 20 bits versus 32. Transmitting a thousand characters in the asynchronous mode, however, takes 10,000 bits, versus 8,016 for the synchronous mode. For long messages, the synchronous format becomes much more efficient than the asynchronous format; the crossover point for the examples shown in Figure 5 is eight characters, for which both formats require 80 bits.

In addition to the differences in format between synchronous and asynchronous communication, there are differences with regards to the type of modems that can be used. Asynchronous modems typically employ Frequency Shift Keying (FSK) techniques which simply generate one audio tone for a MARK and another for a SPACE. The receiving modem detects these tones on the telephone line, converts them to logic signals, and presents them to the receiving terminal. Since the modem itself is not concerned with the transmission speed, it can handle baud rates from zero to its maximum speed. Synchronous modems, in contrast to asynchronous modems, supply timing information to the terminal and require data to be presented to them synchronized with this timing information. Synchronous modems, because of this extra clocking, are only capable of operating at certain preset baud rates. The receiving mode, which has an oscillator running at the same frequency as the transmitting modem, phase-locks its clock to that of the transmitter and interprets changes of phase as data. The PolyMorphic PolyPhase cassette interface operates in a synchronous mode.

In some cases it is desirable to operate in a hybrid mode which involves transmitting data with the asynchronous format using a synchronous modem. This occurs when an increase in operating speed is required without a change in the basic protocal of the

system. This hybrid technique is known as isosynchronous and involves the generation of the start and stop bits associated with the synchronous format, while still using the modem clock for bit synchronization. The Byte standard cassette interface operates in an isosynchronous mode.

The 8251 USART (Universal Synchronous/Asynchronous Receiver-Transmitter) has been designed to meet a broad spectrum of requirements in the synchronous, asynchronous, and isosynchronous In the synchronous modes it operates with 5, 6, 7, or 8-Even or odd parity can be optionally appended bit characters. Synchronization can be achieved internally via SYN and checked. character detection. SYN detection can be based on one or two characters which may or may not be the same. The single or double SYN characters are inserted into the data stream automatically if the software fails to supply data in time. The automatic generation of SYN characters is required to prevent the loss of synchronization. In the asynchronous mode the USART operates with the same data and parity structures as it does in the synchronous In addition to appending a START bit to this data, it apprends 1, 1 1/2, or 2 STOP bits. Proper framing is checked by the receiver and a status flag set if an error occurs. In the asynchronous mode the USART can be programmed to accept clock rates of 1, 16, or 64 times the required baud rate. Note that X1 operation is only valid if the clocks of the receiver and transmitter are synchronized.

The USART can transmit the three formats in half or full duplex mode and is double-buffered internally (i.e., the software has a complete character time to respond to a service request). Although the USART supports basic data set control signals (DTR, RST, etc.), it does not fully support the signaling described in EIA RS-232-C. Examples of unsupported signals are Ring Indicator (CE), and the second channel signals. The serial option does not interface to the voltage levels required by EIA RS-232-C; this function is provided by the Printer Interface Card. (This card also provides an optically isolated current loop interface.)

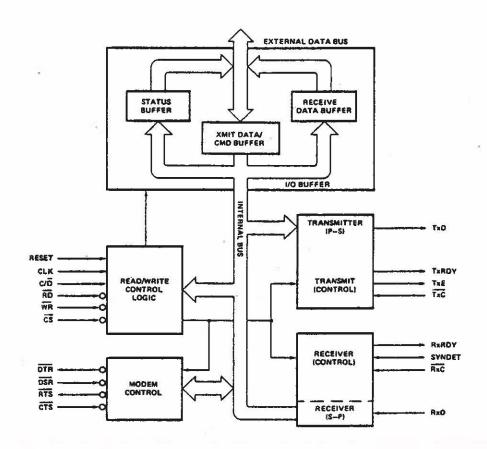

A block diagram of the USART is shown in Figure 6. As can be seen in the figure, the USART consists of five major sections which communicate with each other on an internal data bus. The five sections are the receiver, transmitter, modem control, read/write control, and I/O buffer. In order to facilitate discussion, the I/O buffer has been shown broken down into its three major subsections: the status buffer, the transmit data/command buffer, and the receive data buffer.

#### RECEIVER

The receiver accepts serial data on the RxD pin and converts it to parallel data according to the appropriate format. When the

USART is in the asynchronous mode, and it is ready to accept a character (i.e., it is not in the process of receiving a character), it looks for a low level on the RxD line. When it sees the low level, it assumes that it is a START bit and enables an internal counter. At a count equivalent to one-half of a bit time, the RxD line is sampled again. If the line is still low, a valid START bit has probably been received and the USART proceeds to assemble the character. If the RxD line is high when it is sampled, then either a noise pulse has occurred on the line or the receiver has become enabled in the middle of the transmission of a character. In either case, the receiver aborts its operation and prepares itself to accept a new character.

After the successful reception of a START bit, the USART clocks in the data, parity, and STOP bits, and then transfers the data on the internal data bus to the receive data register. When operating with less than 8 bits, the characters are right-just-ified. The RxRDY signal is asserted to indicate that a character is available.

In the synchronous mode, the receiver simply clocks in the specified number of data bits and transfers them to the receiver buffer register, setting RxRDY. Since the receiver blindly groups data bits into characters, there must be a means of synchronizing the receiver to the transmitter so that the proper character boundaries are maintained in the serial data stream. This synchronization is achieved in the HUNT mode.

In the HUNT mode the USART shifts in data on the RxD line one bit at a time. After each bit is received, the receiver register is compared to a register holding the SYN character (program loaded). If the two registers are not equal, the USART shifts in another bit and repeats the comparison. When the registers compare as equal, the USART ends the HUNT mode and raises the SYNDET line to indicate that it has achieved synchronization. has been programmed to operate with two SYN characters, the process is as described above, except that two contiguous characters from the line must compare to the two stored SYN characters before synchronization is declared. Parity is not checked. USART enters the HUNT mode when it is initialized into the synchronous mode or when it is commanded to do so by the command instruction. Before the receiver is operated, it must be enabled by the RxE bit (D2) of the command instructions. If this bit is not set, the receiver will not assert the RxRDY bit.

#### TRANSMITTER

The transmitter accepts parallel data from the processor, adds the appropriate framing information, serializes it, and transmits it on the TxD pin. In the asynchronous mode the transmitter always adds a START bit; depending on how the unit is programmed, it also adds an optional even or odd parity bit, and either 1, 1 1/2, or 2 STOP bits. In the asynchronous mode no extra bits (other than parity, if enabled) are generated by the transmitter unless the computer fails to send a character to the USART. If the USART is ready to transmit a character and a new character has not been supplied by the computer, the USART will transmit a

SYN character. This is necessary since synchronous communications, unlike asynchronous communications, does not allow gaps between characters. If the USART is operating in the dual SYN mode, both SYN characters will be transmitted before the message can be resumed. The USART will not generate SYN characters until the software has supplied at least one character; i.e., the USART will "fill holes" in the transmission but will not initiate transmission itself. The SYN characters which are to be transmitted by the USART are specified by the software during the initialization procedure. In either the synchronous or asynchronous modes, transmission is inhibited until TxEnable and the -CTS input are asserted.

An additional feature of the transmitter is the ability to transmit a BREAK. A BREAK is a period of continuous SPACE on the communication line and is used in full duplex communication to interrupt the transmitting terminal. The USART will transmit a BREAK condition as long as bit 3 (SBRK) of the command register is set.

#### MODEM CONTROL

The modem control section provides for the generation of -RTS and the reception of -CTS. In addition, a general-purpose output and a general-purpose input are provided. The output is labeled -DTR and the input is labeled -DSR. -DTR can be asserted by setting bit 2 of the command instruction; -DSR can be sensed as bit 7 of the status register. Although the USART itself attaches no special significance to these signals, -DTR (Data Terminal Ready) is normally assigned to the modem, indicating that the terminal is ready to communicate and -DSR (Data Set Ready) is a signal from the modem indicating that it is ready for communications.

#### I/O CONTROL

The Read/Write Control Logic decodes control signals on the 8080 control bus into signals which gate data on and off the USART's internal bus and controls the external I/O bus (DB0 DB7). The receiver and transmitter buffers are located at port #0, while the status and command buffers are port #1. The I/O buffer contains the STATUS buffer, the RECEIVE DATA buffer, and the TRANSMIT DATA/COMMAND buffer, as shown in Figure 7. Note that although there are two registers which store data for transfer to the CPU (STATUS and RECEIVE DATA), only one register stores data being transferred to the USART. The sharing of the input register for both transmit data and command makes it important to ensure that the USART does not have data stored in this register before sending a command to the device. TxRDY signal can be monitored to accomplish this. Neither data nor commands should be transferred to the USART if TxRDY is low. Failure to perform this check can result in erroneous data being transmitted.

| CE | C/D | READ | WRITE | Function                      |

|----|-----|------|-------|-------------------------------|

| 0  | 0   | 0    | 1     | CPU Reads Data from USART     |

| 0  | 1   | 0    | 1     | CPU Reads Status from USART   |

| 0  | 0   | 1    | 0     | CPU Writes Data to USART      |

| 0  | 1   | 1    | 0     | CPU Writes Command to USART   |

| 1  | ×   | ×    | ×     | USART Bus Floating<br>(NO-OP) |

Figure 7.

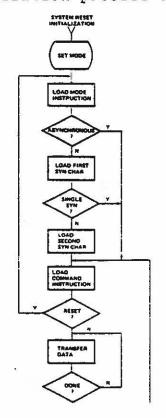

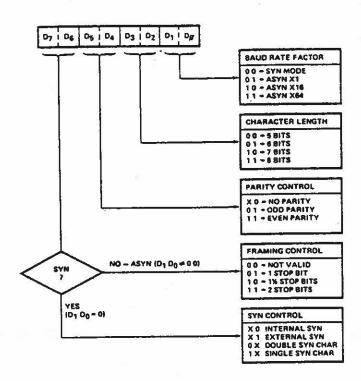

#### MODE SELECTION

The USART is capable of operating in a number of modes (e.g., synchronous or asynchronous). In order to keep the hardware as flexible as possible (both at the chip and end product levels), these operating modes are selected via a series of control outputs to the USART. These mode control outputs must occur between the time the USART needs this information to structure its internal logic it is essential to complete the initialization before any attempts are made at data transfer (including reading status).

A flowchart of the initialization process appears in Figure 8.

The first operation which must occur following a reset is the loading of the mode control register. The mode control register is loaded by the first control output following a reset. The format of the mode control instruction is shown in Figure 9.

The instruction can be considered as four 2-bit fields. The first 2-bit field (Dl D0) determines whether the USART is to operate in the synchronous (00) or asynchronous mode. In the asynchronous mode this field also controls the clock scaling factor. As an example, if Dl and D0 are both ones, the -RxC and -TxC will be divided by 64 to establish the baud rate. The second field, D3 D2, determines the number of data bits in the character, and the third, D5 D4, controls parity generation. Note that the parity bit (if enabled) is added to the data bits and is not considered as part of them when setting up the character length. As an example, standard ASCII transmission, which is seven bits plus even parity, would be specified as:

#### X X 1 1 1 0 X X

The last field, D7 D6, has two meanings, depending on whether operation is to be in the synchronous or asynchronous mode. For the asynchronous mode (i.e., Dl D0 = OO), it controls the number of STOP bits to be transmitted with the character. Since the receiver will always operate with only one STOP bit, D7 and D6 only control the transmitter. In the synchronous mode (Dl D0 = OO), this field controls the synchronization process. Note that the choice of single or double SYN characters is independent of the choice of internal or external synchronization. This is because even though the receiver may operate with external synchronization logic, the transmitter must still know whether to send one or two SYN characters should the CPU fail to supply a character in time.

Following the loading of the mode instruction, the appropriate SYN character (or characters) must be loaded if synchronous mode has been specified. The SYN character(s) are loaded by the same control output instruction used to load the mode instruction. The USART determines from the mode instruction whether no, one, or two SYN characters are required and uses the control output to load SYN characters until the required number are loaded.

# USART PROGRAMMING HINTS

Output of a command to the USART can destroy the integrity of a transmission in progress if timed incorrectly.

Sending a command into the USART will overwrite any character which is stored in the buffer waiting for transfer to the parallel-to-serial converter in the device. This can be avoided by not sending a command if transmission is taking place. Due to the internal structure of the USART, it is also possible to disturb the transmission if a command is sent while SYN character is being generated by the device. (The USART generates a SYN if the software fails to respond to TxRDY.) If this occurence is possible in a system, commands should be transferred only when a positive-going edge is detected on the TxRDY line.

- 2. RxE only acts as a mask to RxRDY; it is possible for the USART internal data buffers to already contain one or two characters. These characters should be read and discarded when the RxE bit is first set. Because of these extraneous characters, the proper sequence for gaining synchronization is as follows:

- 1. Disable interrupts.

- Issue a command to enter hunt mode, clear errors, and enable the receiver (EH,ER,RxE=1).

- Read USART data port twice(it is not necessary to check status).

- 4. Enable interrupts.

The first RxRDY that occurs after the above sequence will indicate that the SYN character or characters have been detected and the next character has been assembled and is ready to be read.

3. Loss of CTS or dropping TxEnable will immediately clamp the serial output line.

TxEnable and RTS should remain asserted until the transmission is complete. Note that this implies that not only has the USART completed the transfer of all bits of the last character, but also that they have cleared the modem. A delay of 1 msec following a proper occurence of TxEmpty is usually sufficient (see Item 4). An additional problem can occur in the synchronous mode because the loss of TxEnable clamps the data in at a SPACE instead of the normal MARK. This problem, which does not occur in the asynchronous mode, can be corrected by an external gate combining RTS and the serial output data.

4. Extraneous transitions can occur on TxEmpty while data (including USART generated SYNs) is transferred to the parallel-to-serial converter.

This situation can be avoided by ensuring that TxEmpty occurs during several consecutive status reads before assuming that the transmitter is truly in the empty state.

5. A BREAK (i.e., long space) detected by the receiver results in a string of characters which have framing errors.

If reception is to be continued after a BREAK, care must be taken to ensure that valid data is being received; special care must be taken with the last character perceived during a BREAK, since its value, including any framing error associated with it, is indeterminate.

#### USART ADDRESSING

The transmit and receive buffers are addressed as port 0 on the CPU card if it is set up for operation at 0. The command and status buffers are located at port 1. If your CPU card is not set up for operation at 0, consult the following table. (See Section 3.5 for addressing option description.)

#### USART OPTION ADDRESSING

| Address    | SERVICE SERVICES SERV |      | Data | Command          | Baud Rate          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------------|--------------------|--|

| Jumper     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | at   | port | & Status<br>Port | Generator<br>Latch |  |

| J (factory | set)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 | 0    | 1                | 4                  |  |

| T | 8000 | 80 | 81 | 84 |

|---|------|----|----|----|

| S | E000 | ΕO | El | E4 |

#### 2.3 BAUD RATE GENERATOR OPERATION

The baud rate generator may be accessed through port #4. The byte output to this port will be latched into the baud rate latch and determines the baud rate, device number, and on-card memory disable or enable. When power is applied to the CPU card or the front panel reset button is pushed, this latch is set to 0. The command format is as follows:

D7, D6 D5 D4 D3, D2, D1, D0 Unused ROM Device Baud Rate disable #

See Section 3.4, Phantom Memory, for a discussion of on-card memory disable.

#### BAUD RATE

The baud rate field may assume any value 0 through F (hex). Fifteen of these are valid baud rates; 0 disables clock generation. Note that the actual baud rate is determined by the USART mode (x1, x16, x64 clock). See Figure 12 for the available baud rates. Note the synchronous mode always uses an x1 clock.

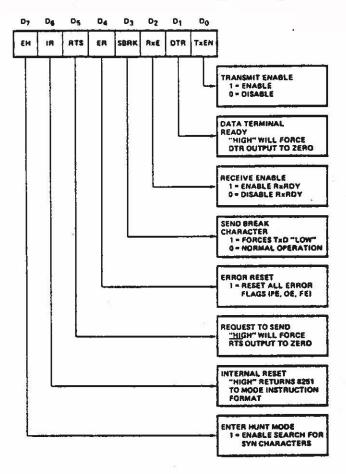

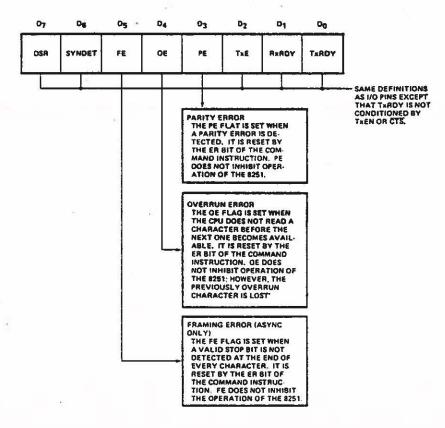

At completion of the load of SYN characters (or after the mode instruction in the asynchonous mode), a command character is issued to the USART. The command instruction controls the operation of the USART within the basic framework established by the mode instruction. The format of the command instruction is shown in Figure 10. Note that if, as an example, the USART is waiting for a SYN character load and instead is issued an internal reset command, it will accept the command as an SYN character instead of resetting. This situation, which should only occur if two independent programs control the USART, can be avoided by outputting three all zero characters as commands before issuing the internal reset command. The USART indicated its state in a status register which can be read under program control. The format of the status register read is shown in Figure 11.