# MOSTEK.

Z80 MICROCOMPUTER SYSTEMS HARDWARE

**Operations Manual**

SDB-80E SOFTWARE DEVELOPMENT BOARD SDB-80E

SOFTWARE DEVELOPMENT BOARD

**OPERATIONS MANUAL**

# **Z80 Software Development Board (SDB-80E)**

# HARDWARE FEATURES □ Available as board or complete system □ 4K bytes of RAM, expandable on board to 16K Bytes □ Four 8-bit I/O ports with handshake lines □ Serial ASCII interface (110-9600 BAUD) □ Fully buffered for system expandability □ Four counter/timer channels □ On board capacity from 5K bytes of PROM to 20K bytes of ROM □ Double euro-card format SOFTWARE FEATURES □ 2K x 8 Operating System in ROM (DDT-80)

□ 8K x 8 assembler/editor in ROM (ASMB-80)□ Channeled I/0 for user convenience

#### **GENERAL DESCRIPTION**

□ Double euro-card format

The SDB-80 is a stand-alone microcomputer designed by MOSTEK around the advanced Z80 microprocessor familiy. It contains more on-board firmware and RAM memory than any previously offered single board microcomputer, plus all the features of the industries most sophisticated microprocessor. This board represents the very latest in state-of-the-art technology by utilizing MOSTEK's new 16K Dynamic RAM memories. The SDB-80 also is the first single board microcomputer to offer a complete package of software development aids in ROM. This 10K byte firmware package is included with the SDB-80 and provides the ability to generate, edit, assemble, load, execute, and debug Z80 programs for all types of applications.

#### **USING THE SDB-80**

In addition to functioning as a stand-alone development aid, the SDB-80 is fully expandable through the addition of optional add-on circuit boards. It may also be utilized directly in OEM applications by inserting custom programmed ROM or PROM memories into the sockets provided on the board. For these OEM applications, partially populated versions of the SDB-80 (designated OEM-80) are available without the standard system firmware, and with quantity discounts.

#### SYSTEM FIRMWARE

A standard feature of the SDB-80 is a complete package of development software aids which are resident in the five MK 34000, 2k x 8 ROM memories located on the board. This firmware includes a sophisticated operating system, debug package, assembler, and text editor. The presence of this software in ROM provides instant access to these development aids, eliminating the time-consuming requirement of loading the software from some perpheral device into RAM.

Another key feature of having the development aid software in ROM is that entire RAM space is available for the user's programs,

Debug (DDT-80) includes:

- □ object program Load/Dump

- ☐ Memory or Port Examine/Change

- ☐ Breakpoint/Execute

- ☐ Logical/Physical I/O mapping (with user expandable drivers)

- □ Drivers for Standard Peripherals

The Assembler (ASMB-80) includes: In-circuit-emulation capability is added AIM-80E to the SDB-80 by using the AIM-80 board ☐ 1, 2 or 3 pass operation also provides other debugging capatibilities such as TRACE and SINGLE STEP. conditional Assembly FLP-80E The FLP-80 interfaces the SDB-80 to two ☐ Relocatable object module generation soft-sectored floppy disk drives. Full file handling software and firmware is pro-□ Relocatable linking loader vided with the card. ☐ Drivers for Silent 700 Cassette RIO-80E The RIO-80E includes 2-buffered PIO's. I-UART, I-CTC, and sockets for 16k bytes The Text Editor (EDIT-80) includes: of MK 2708 PROM. ☐ Line or character operation NON RESIDENT SOFTWARE AVAILABLE Macro commands XFOR-80 Fortran IV Cross Assembler. Assembles Z80 programs but is written in Fortran IV. **ELECTRICAL SPECIFICATIONS** It is useful for persons desiring to perform Operating Temperature Range ... 0 °C to 50 °C Z80 assembly in mini-computers such as the PDP-11. It is furnished in Fortran IV Power Supply requirements (Typical) source as a card deck or paper tape.  $+12V \pm 5\%$ 175 mA XMDS-80 8080A Cross Assembler. Performs the  $+ 5V \pm 5\%$ 1.5 A same function as the Fortran IV Cross  $-12V \pm 5\%$ 100 mA Assembler, except that it is designed to be used with an Intel MDS system. It is fur-Interface Levels . . . TTL Compatible nished as an object tape in Intel compatible Hex format. This is identical to the XMDS-80 except XMDS-80D **MECHANICAL SPECIFICATIONS** that it is compatible with Intel MDS systems which use floppy disk. It is fur-Extended double Eurocard nished as object code on an MDS com-Board Size: 250 mm x 233.4 mm x 18 mm patible floppy diskette. Connector: Dual 64 pin Eurocard Connector OTHER ACCESSORIES AVAILABLE DIN 41612 form D; A and C pinned. **PPG-08** PROM Programmer module for programming MK 2708 UV erasable PROM memories. Interfaces directly with the SDB-80. Enclosure included. **OEM USERS CARDS AVAILABLE COMPATIBLE ADD-ON BOARDS** OEM-80E SDB-80E without Software. Available with RAM-80AE Add-on RAM card for the SDB-80E. This 4 or 16k RAM Memory. 5 PROM/ROM card supplies 16k bytes of MK 4027 sockets are free for user programs. dynamic RAM Memory. Parallel This double Eurocard CRT/Keyboard Universal Interface is bus compatible with the SDB-Display 80E. A MK 3881 PlO on the card allows Interface writing to the CRT Display at up to 3.300 RAM-80BE Add-on RAM/IO card for the SDB-80E. characters per second. The CRT-80E pro-This card supplies 16k (expandable to UDI-P vides 24 lines of 80 characters. The stan-64k) bytes of MK 4116 dynamic RAM Memory, plus 4 fully buffered I/O ports dard ASCII 96 character font is provided. other fonts may be programmed using using 2 MK 3881 PlO's. On-card bank MK 2708 PROM's. The command set inswitching allows expansion of SDB-80E cludes TAB and cursor control. memory space beyond 64k bytes. Serial This is identical to the parallel except it Universal operates over a 4 wire serial current loop XRAM-80 Expansion Kit for RAM-80BE. Consists of Dislplay connection. Useful in remote terminal 8-MK 4116 RAMs. Interface applications.

**UDI-S**

BACK-80E 12 slot prewired printed circuit backplane

simplifies system construction.

for the SDB-80E family. This card greatly

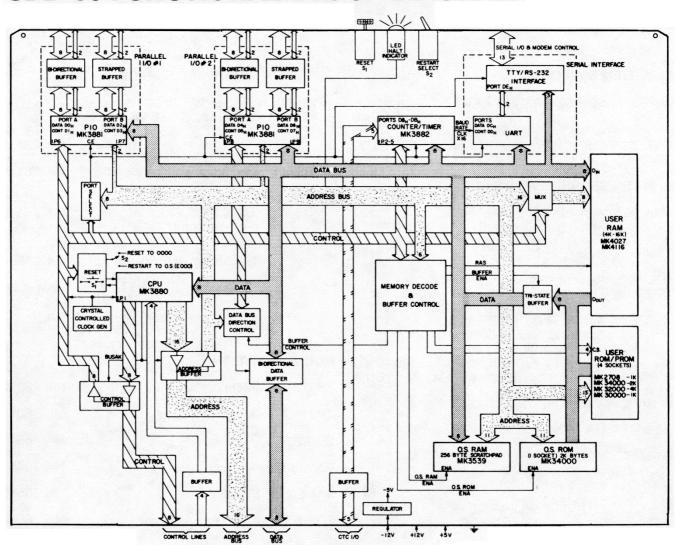

## **SDB-80 FUNCTIONAL BLOCK DIAGRAM**

BACKPLANE CARD MK 79054

| Z80 SYSTEM SUPPORT                |                                                                                        |                                    | <b>Z</b> 80 | SOFTWARE SUPPORT                                                                    |                        |

|-----------------------------------|----------------------------------------------------------------------------------------|------------------------------------|-------------|-------------------------------------------------------------------------------------|------------------------|

| SYS-80E<br>MOSTEK                 | SDB-80E with MK 78039<br>4k byte<br>16k byte<br>Complete Video Display Uni             | MK 78040<br>MK 78041<br>t MK 78037 | XFOR-80     | Fortran IV Cross Assembler<br>requires 20k, 16 bit words<br>Card Deck<br>Paper Tape | MK 78117C<br>MK 78117P |

| TERMINAL <b>Z80 PROC</b> I        | ESSOR ELEMENTS                                                                         |                                    |             | 8080 MDS Cross Assembler<br>Paper Tape                                              | MK 78115               |

| OEM-80E                           | with 4k bytes RAM<br>with 16k bytes RAM                                                | MK 78122<br>MK 78124               | XMDS-80D    | 8080 MDS Cross Assembler Soft sectored diskette                                     | MK 78116               |

| DDT-80                            | Debug 2k Byte ROM                                                                      | MK 78118                           |             | Listing for DDT-80                                                                  | MK 78534               |

| ASMB-80<br>EDIT-80                | Assembler four 2k Byte ROM (including the Editor)                                      | l's<br>MK 78119                    |             | Listing for ASMB-80                                                                 | MK 78536               |

| SDB-80E                           | with OEM-80 + DDT-80 +<br>ASMB-80 + EDIT-80 +<br>documentation                         |                                    |             |                                                                                     |                        |

|                                   | 4k byte RAM                                                                            | MK 78103                           | DOCUMEN.    | TATION                                                                              |                        |

| 700 HADDI                         | 16k byte RAM WARE SUPPORT                                                              | MK 78104                           | Z80 CPU     | Manual                                                                              | MK 78070               |

| RAM-80AE                          | 16k RAM                                                                                | MIC 70100                          | Z80 PIO     | Manual                                                                              | MK 78071               |

| RAM-80BE                          |                                                                                        | MK 78109                           | SDB-80E     | Manual                                                                              | MK 78548               |

|                                   | 16k RAM, 2 PIO                                                                         | MK 78110                           | RAM-80E     | Manual                                                                              | MK 78545               |

| XRAM-80<br>AIM-80E                | 16k expander for RAM-80BE                                                              |                                    | AIM-80E     | Manual                                                                              | MK 78546               |

| FLP-80E                           | I.C.E. (In-Circuit-Emulation)                                                          | MK 78106                           | SDB-80E     | Literature Package                                                                  | MK 78549               |

|                                   | Floppy Interface                                                                       | MK 78112                           |             | includes CPU, PIÖ, SDB-80<br>manuals plus data sheets                               |                        |

| RIO-80E                           | 16k PROM, 2 PIO, 1-CTC, UART                                                           |                                    | PPG-08      | Manual                                                                              | MK 78532               |

| Universal<br>Display<br>Interface | Serial UDI-S<br>Parallel UDI-P<br>Screen read option                                   | MK 78033<br>MK 78035<br>MK 78036   | Z80         | Pocket reference manual                                                             | MK 78516               |

|                                   | EIA Interface Cable For SDB-80E                                                        | MK 79058                           | Z80         | Programming manual                                                                  | MK 78515               |

|                                   | TTY Cable for SYS-80E                                                                  | MK 79059                           |             |                                                                                     |                        |

| PPG-08                            | PROM Programmer for<br>MK 2708 1kx8 UV PROM's<br>with enclosure (requires<br>MK 79060) | MK 79033                           |             |                                                                                     |                        |

|                                   | PPG-08 Cable for SYS-80E                                                               | MK 79060                           |             |                                                                                     |                        |

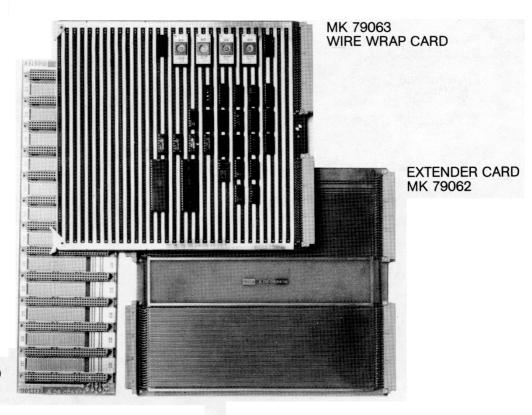

|                                   | Wire Wrap Card                                                                         | MK 79063                           |             |                                                                                     |                        |

|                                   | Extender Card                                                                          | MK 79062                           |             |                                                                                     |                        |

| BACK-80E                          | Backplane Card, 6 slot                                                                 | MK 79054                           |             |                                                                                     |                        |

|                                   | Development Station Z80 6 total slots, power supply, no                                | MK 78039<br>cards                  |             |                                                                                     |                        |

#### **MOSTEK TERMINAL MK 78037**

#### **FEATURES**

- □ Self contained visual terminal

- □ 24 line, 80 character per line display

- ☐ Baud rate selection 110-9600

- ☐ Current loop or V24

- □ Comprehensive commands

#### **GENERAL**

A keyboard and a monitor provide together a "teletype" replacement video terminal for MOSTEK development systems, that can also be used in other applications. The terminal is completely self contained with its own power supply and electronics, requiring only the serial communication lines to the computer.

#### **KEYBOARD**

The keyboard obtains its power from the display unit, the coded keyboard information and power connections are made over a 25 pin type D connector.

#### DISPLAY ELECTRONICS

The display electronics uses the MOSTEK universal display interface board (MK 78033), power being provided within the terminal itself. The set of available functions is fully described in the MK 78033 data sheet; the key features are:

- ☐ 24 lines with 80 characters per line

- ☐ Cursor movements, absolute and relative

- ☐ Serial communication, 110–9600 baud

- □ Upper and lower case characters

- ☐ Clear screen, clear line etc.

- □ Tabulate

- ☐ A 9" diagonal display is used.

#### **MECHANICAL**

The display and keyboard are separate units connected by a cable. The display dimensions are:

B 43 cm

H 26 cm

T 32 cm

The keyboard dimensions are:

B 43 cm

H 4,5 cm H 9,0 cm T 24 cm

vii

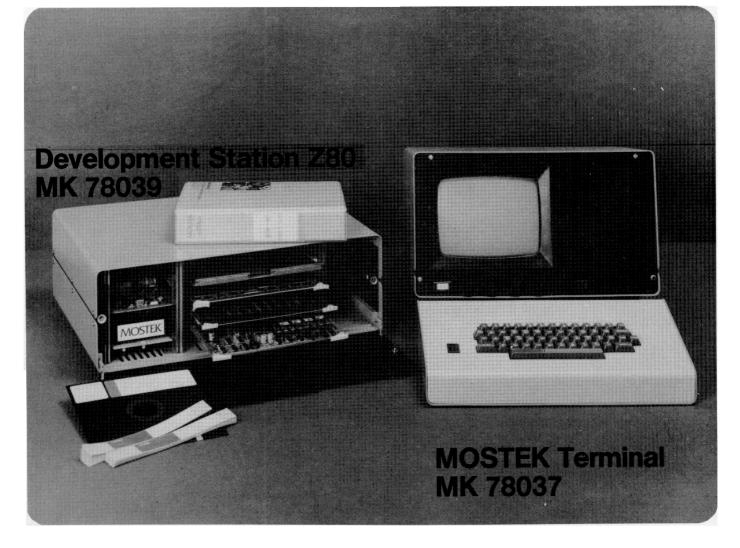

#### **DEVELOPMENT STATION Z80 MK 78039**

#### **FEATURES**

| Accepts upto 6 total boards                |

|--------------------------------------------|

| Protected power supplies                   |

| 11 I/O connectors for Peripheral equipment |

| Double Europaformat boards                 |

#### **GENERAL**

The MOSTEK development station has been designed to house and provide power for all MOSTEK boards with the double european format as in the detailed description of the SDB-80E. When used in conjunction with the MOSTEK terminal it forms a powerful development system.

INPUT/OUTPUT

11 connectors, 25 pin type D, are available for peripheral equipment. For the SDB 80E some of these are already committed as listed here below:

#### Connector SDB 80 E function

| 1  | Terminal                   |

|----|----------------------------|

| 2  | CTC                        |

| 3  | Floppy disc controller (1) |

| 4  | Uncommitted.               |

| 5  | Uncommitted.               |

| 6  | Paper tape reader          |

| 7  | Paper tape punch           |

| 8  | Line printer (2)           |

| 9  | Uncommitted.               |

| 10 | PROM programmer-PPG08      |

| 11 | Uncommitted.               |

|    |                            |

- (1) with FLP 80E

- (3) with RAM 80BE (or RIO80E or use PROM prog. Connector)

#### **POWER SUPPLIES**

Plug-in power supplies are used, the supplies being one card with  $\pm 5$  volt 7 ampere and one card with  $\pm 12$  volt 1 ampere. All supplies have overvoltage protection and current limiting.

#### **MECHANICAL**

The housing has the following dimensions:

B 52 cm

H 18 cm

T 36 cm

The front panel has quick release fastners to give free access to the boards.

#### **MOSTEK Z80 DEVELOPMENT SYSTEM**

#### Includes:

| MK 78103 | SDB-80 Package A                               | (4k byte RAM)  |

|----------|------------------------------------------------|----------------|

| , .      | or                                             | ,              |

| MK 78104 | SDB-80 Package B                               | (16k byte RAM) |

|          | with 256 byte static R<br>DDT 80 Operating Sys | KAM<br>etom    |

|          | ASMB 80 Resident As                            | ssembler       |

|          | and Text Editor and d                          |                |

| MK 78037 | MOSTEK Terminal                                |                |

| MK 78039 | Development Station                            | Z80            |

#### TABLE OF CONTENTS

| 1. | SDB-80 INTRODUCTION Figure of overall system                                                                                                                                       | PAGE<br>1-1<br>1-2                                                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

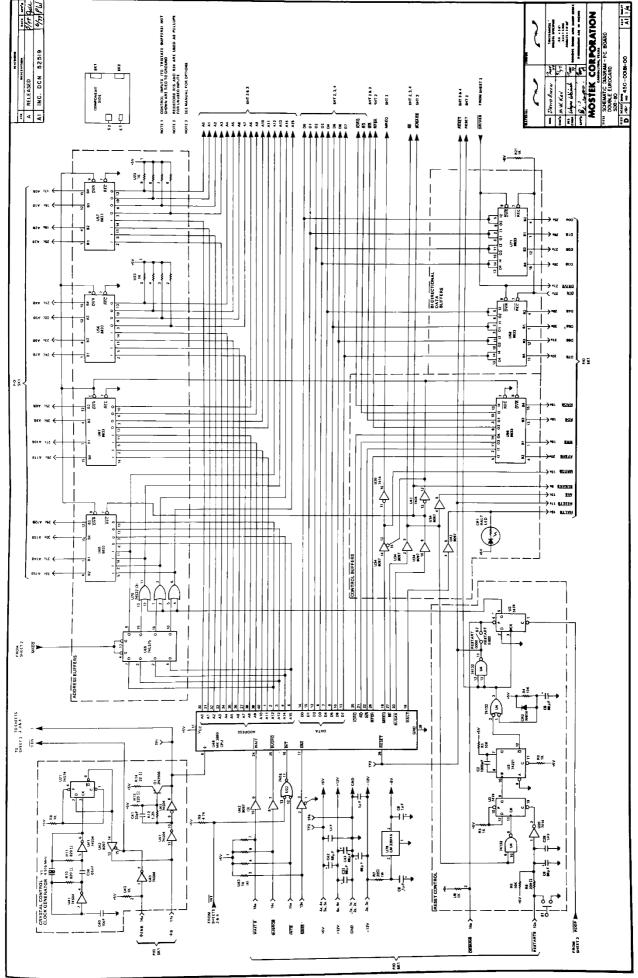

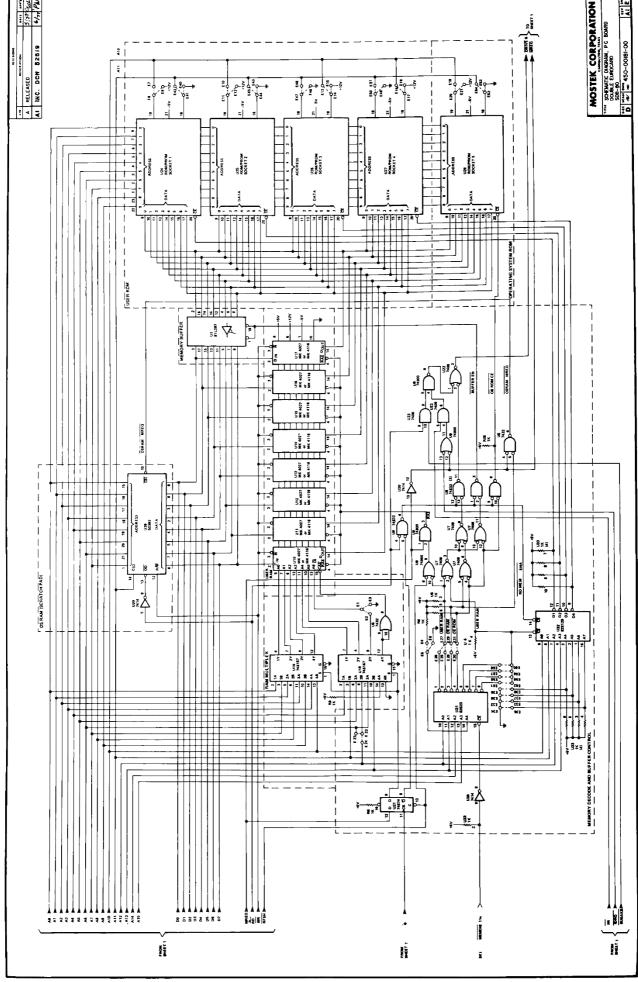

| 2. | FUNCTIONAL DESCRIPTION  System block diagram  Picture of board with major component areas                                                                                          | 2-1<br>2-2                                                         |

|    | indicated Microprocessor components Memory Parallel I/O interface Serial I/O interface Counter timing circuit Bus lines Clock generator Reset/Restart Port select                  | 2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-7<br>2-8<br>2-8<br>2-8<br>2-8 |

| 3. | INITIAL SDB-80 CHECK OUT PROCEDURE<br>Minimum equipment needed<br>Board hookup<br>Initial check out procedure                                                                      | 3-1<br>3-1<br>3-1<br>3-2                                           |

| 4. | PORTS, PERIPHERALS, AND DRIVERS Port map                                                                                                                                           | 4-1<br>4-2                                                         |

| 5. | JUMPER OPTIONS AS SHIPPED FROM THE FACTORY                                                                                                                                         | 5-1                                                                |

| 6. | SDB-80 TO PERIPHERALS  SDB-80 interface to serial terminals  SDB-80 interface to paper tape reader/punches  SDB-80 interface to line printers  SDB-80 interface to PROM programmer | 6-1<br>6-2<br>6-5<br>6-10<br>6-11                                  |

| 7. | SERIAL INTERFACE  Baud rate clock  UART  I/O buffering  Reader step  Transmit serial data  Receive serial data  Handshake lines  Silent 700 control line                           | 7-1<br>7-1<br>7-3<br>7-6<br>7-7<br>7-1<br>7-11                     |

### TABLE OF CONTENTS (CON'T)

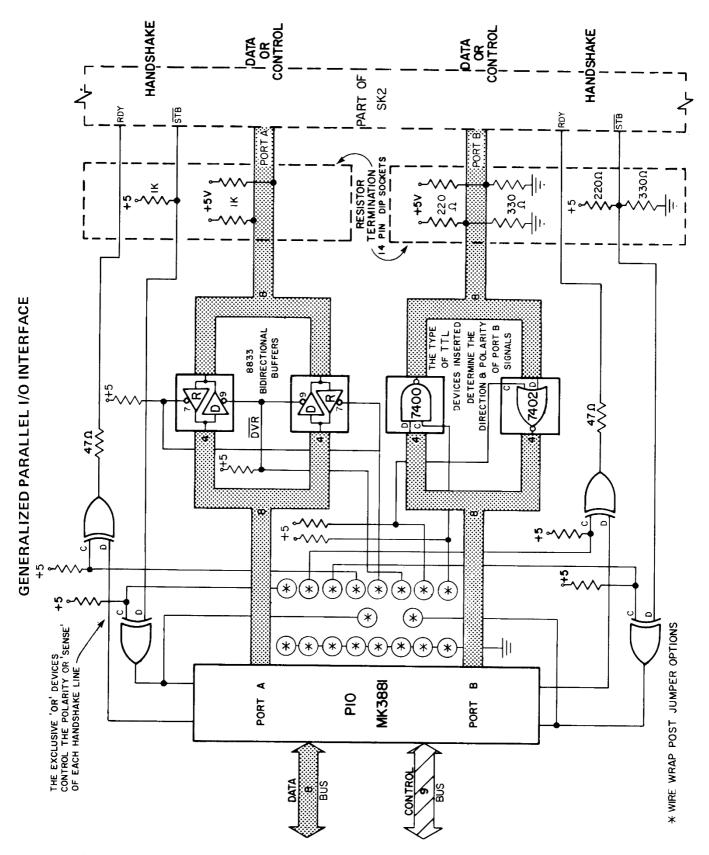

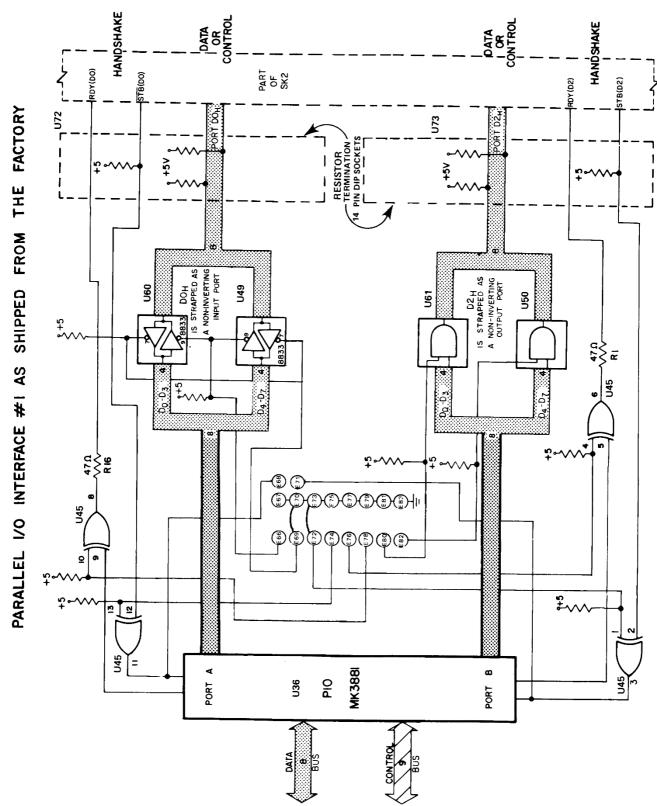

| 8.  | PARALLEL INTERFACE Connectors Resistor terminations Handshake line buffers Port A data buffer Port B data buffers Port addresses                                                                                                                                                                                                            | PAGE<br>8-1<br>8-1<br>8-1<br>8-3<br>8-4<br>8-12                                 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 9.  | MEMORY: MAPPING AND DECODING  Mapping USER RAM O. S. RAM or scratchpad RAM USER ROM/PROM O. S. ROM 32 x 8 Bipolar PROM 256 x 4 Bipolar PROM Operation of the PROM decoding Programming of the Bipolar PROMS Redundant decoding of the O. S. RAM Jumper options Blank programming charts RAM MUX, buffer control and memory Tri-state buffer | 9-1<br>9-7<br>9-7<br>9-7<br>9-9<br>9-11<br>9-12<br>9-20<br>9-26<br>9-28<br>9-41 |

| 10. | RESTART  Power up restart  Push button restart  Restart location, 0000 <sub>H</sub> OR E000 <sub>H</sub> Control line circuitry  Four bit latch function                                                                                                                                                                                    | 10-1<br>10-1<br>10-1<br>10-1<br>10-4<br>10-5                                    |

| 11. | OUTPUT BUFFERS: ADDRESS, DATA, AND CONTROL<br>Address bus buffer<br>Data bus buffer<br>System control bus                                                                                                                                                                                                                                   | 11-1<br>11-1<br>11-1<br>11-6                                                    |

| 12. | COUNTER/TIMER I/O buffers Port addresses Functional description Jumper option Counting                                                                                                                                                                                                                                                      | 12-1<br>12-1<br>12-1<br>12-1<br>12-3<br>12-4                                    |

| 13. | CLOCK GENERATOR                                                                                                                                                                                                                                                                                                                             | 13-1                                                                            |

| 14. | INTERRUPTS Modes Interrupt servicing Daisy chain                                                                                                                                                                                                                                                                                            | 14-1<br>14-1<br>14-4<br>14-5                                                    |

#### TABLE OF CONTENTS (CON'T)

|     |                                       | <u>PAGE</u>          |

|-----|---------------------------------------|----------------------|

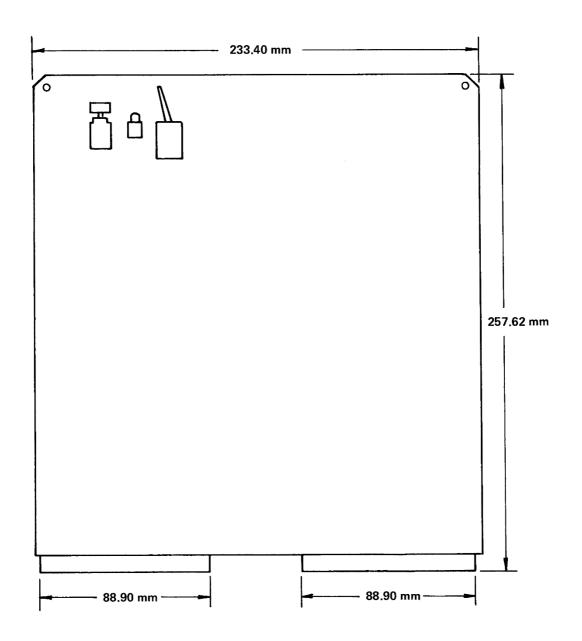

| 15. | SPECIFICATIONS Board Outline Pin Outs | 15-1<br>15-5<br>15-6 |

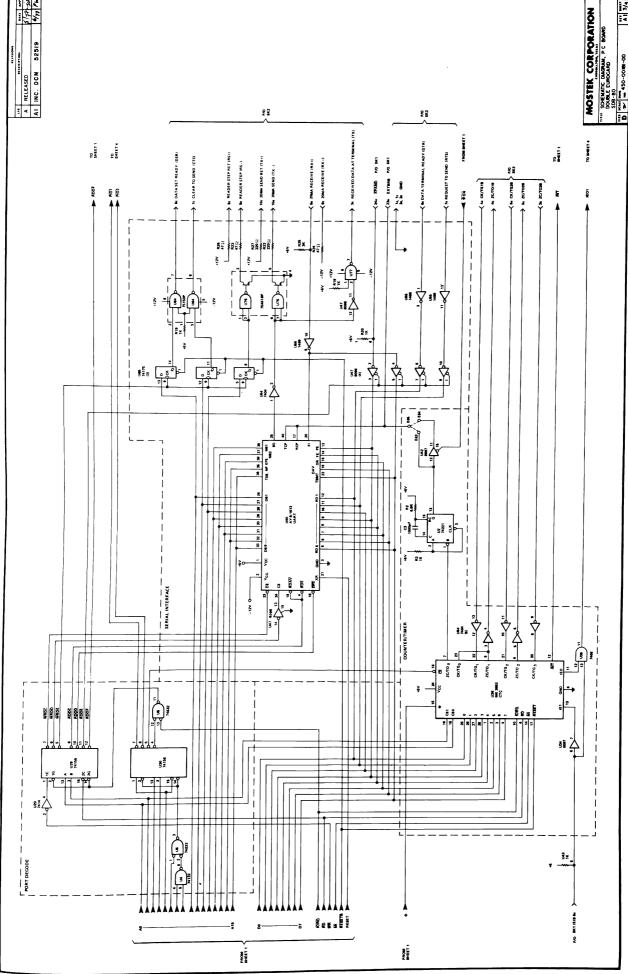

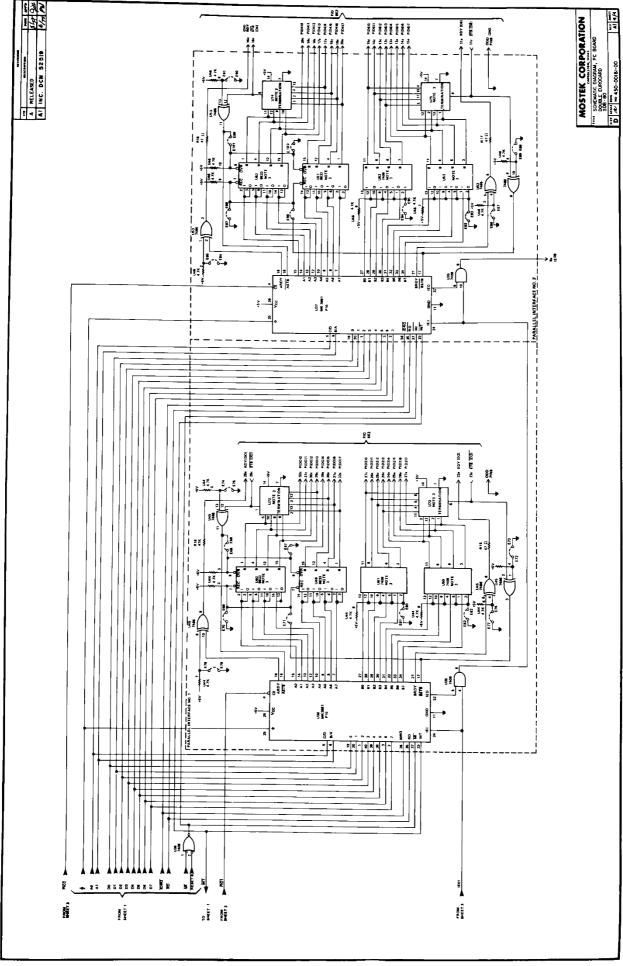

| 16. | BOARD SCHEMATICS                      | 16-1                 |

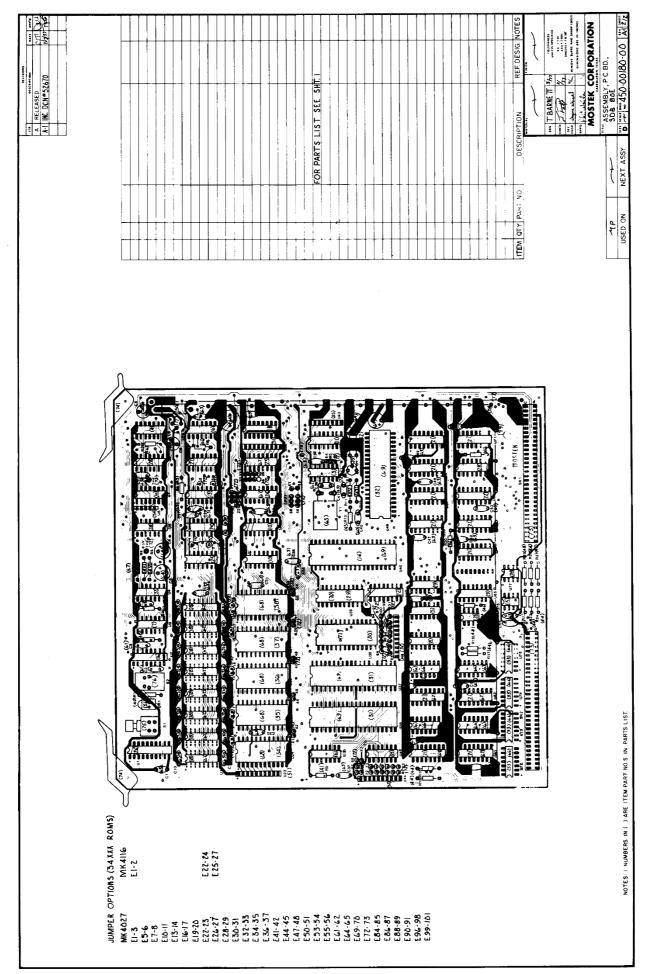

| 17. | BOARD ASSEMBLY DRAWINGS               | 17-                  |

#### LIST OF FIGURES

| 1. | SDB-80 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                      | FIGURE                               | PAGE                                                        |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------|

| 1. | Figure of overall system                                                                                                                                                                                                                                                                                                                                                                                 | 1                                    | 1-2                                                         |

| 2. | FUNCTIONAL DESCRIPTION System block diagram Picture of board with major component                                                                                                                                                                                                                                                                                                                        | 1                                    | 2-2                                                         |

|    | areas indicated                                                                                                                                                                                                                                                                                                                                                                                          | 2                                    | 2-3                                                         |

| 3. | INITIAL SDB-80 CHECK OUT PROCEDURE                                                                                                                                                                                                                                                                                                                                                                       |                                      |                                                             |

| 4. | PORTS, PERIPHERALS, AND DRIVERS<br>SDB-80 port map                                                                                                                                                                                                                                                                                                                                                       | 1                                    | 4-2                                                         |

| 5. | JUMPER OPTIONS ON SDB-80 Physical location of jumper posts SDB-80, Factory supplied configuration                                                                                                                                                                                                                                                                                                        | 1 2                                  | 5-2<br>5-3, 5-4                                             |

| 6. | SDB-80 TO PERIPHERALS  Serial port to TTY without reader step Serial port to TTY with reader step Silent 700  SDB-80 jumpers for Plessy paper tape reade Interface SDB-80 jumpers for Plessy and EECO reader/punch interface SDB-80 jumpers for Data Products line printer interface SDB-80 jumpers for Mostek PROM programmer interface Timing diagram for reader, punch and line printer data transfer | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 6-3<br>6-3<br>6-4<br>6-6<br>6-6<br>6-6<br>6-6<br>6-6<br>6-6 |

| 7. | SERIAL INTERFACE  Block diagram of serial I/O port Interconnection between SDB-80 serial port and 25 pin EIA connector Reader step interface Serial drive to the Peripheral from the SDB-80 Serial drive to the SDB-80 from the Pheripheral Schematic of handshake lines                                                                                                                                 | 1<br>2<br>3<br>4<br>5<br>6           | 7-2<br>7-5<br>7-8<br>7-9<br>7-10<br>7-12                    |

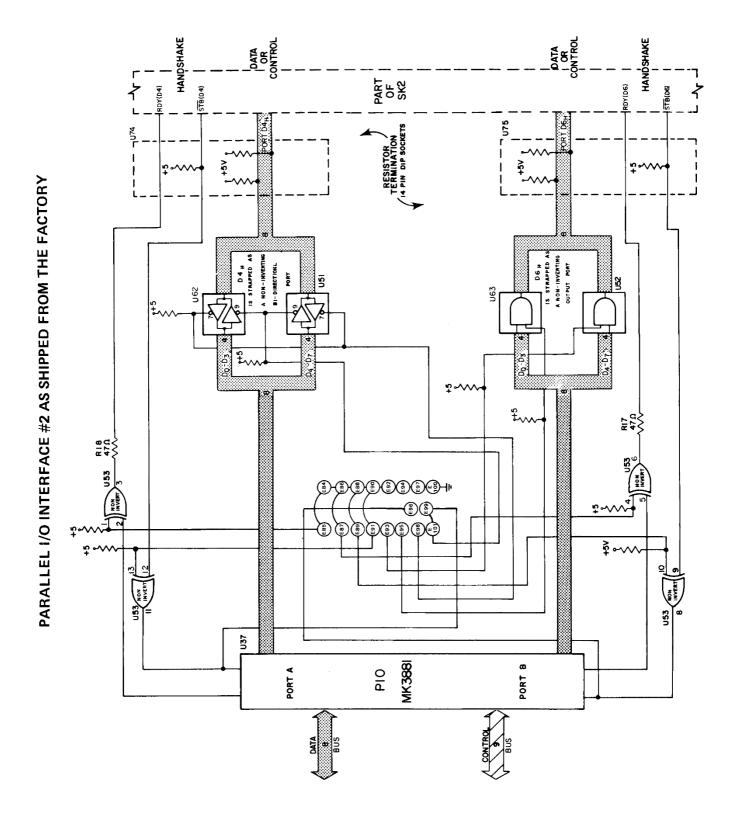

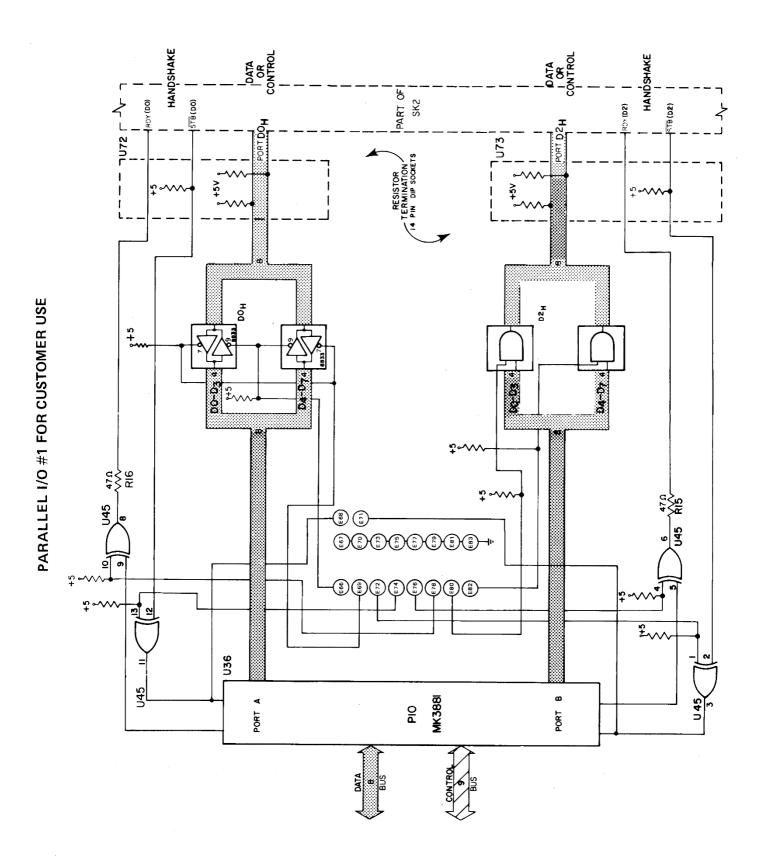

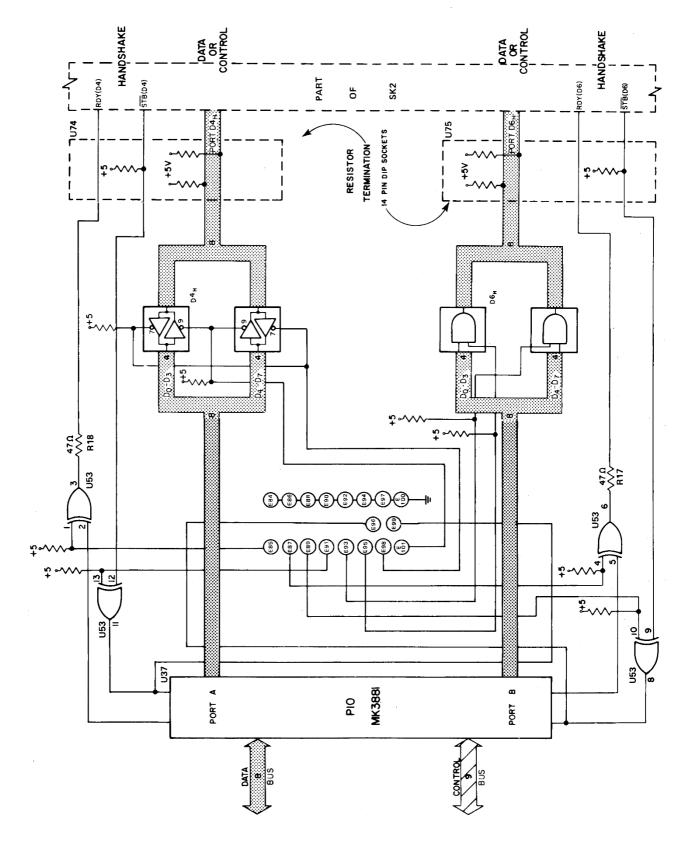

| 8. | PARALLEL INTERFACE  Generalized parallel I/O interface  Straps to control parallel ports  Parallel I/O interface #1 as shipped from factory                                                                                                                                                                                                                                                              | 1<br>2<br>3                          | 8-2<br>8-7<br>8-8                                           |

|    | Parallel I/O interface #2 as shipped from factory                                                                                                                                                                                                                                                                                                                                                        | 4                                    | 8-9                                                         |

#### LIST OF FIGURES (CON'T)

|     |                                                                                         | FIGURE | <u>PAGE</u> |

|-----|-----------------------------------------------------------------------------------------|--------|-------------|

|     | Blank programming schematic of parallel I/O # 1 Blank programming schematic of parallel | 5      | 8-10        |

|     | I/O # 2                                                                                 | 6      | 8-11        |

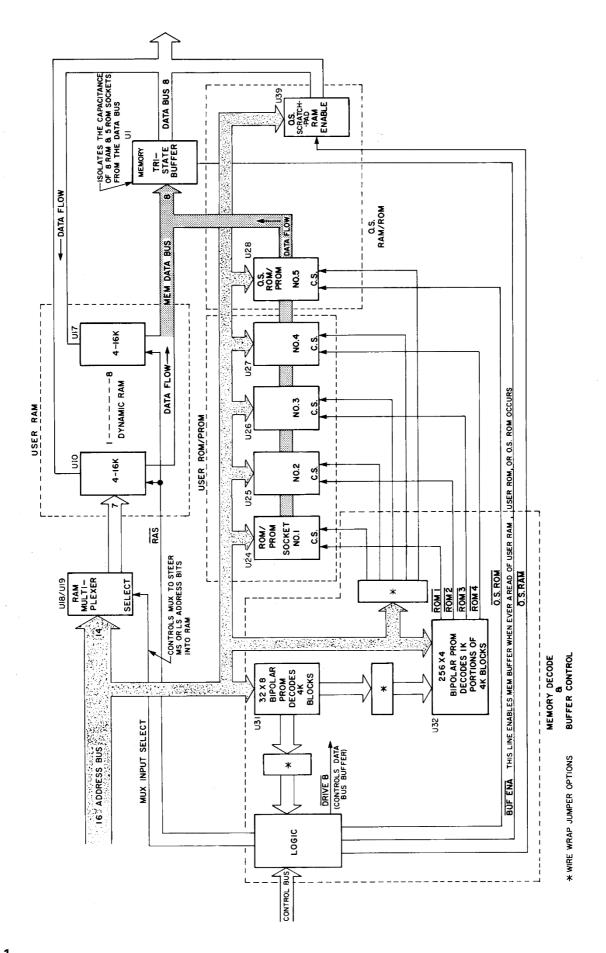

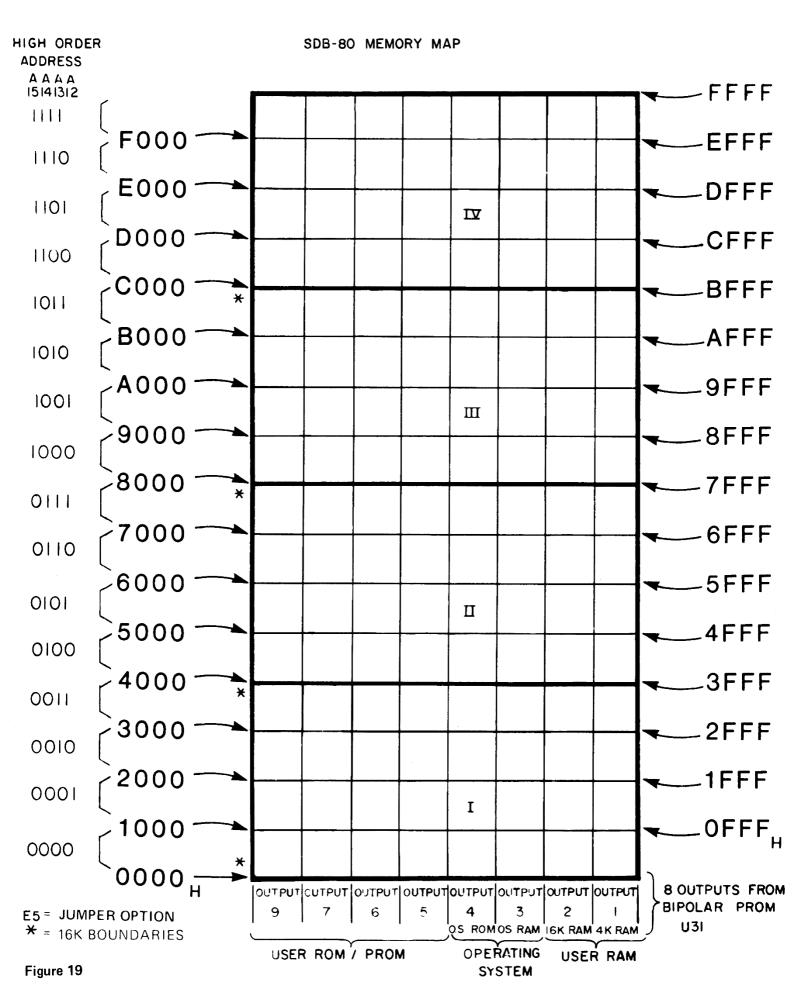

| 9.  | MEMORY: MAPPING AND DECODING                                                            |        |             |

|     | Block diagram of memory section                                                         | 1      | 9-2         |

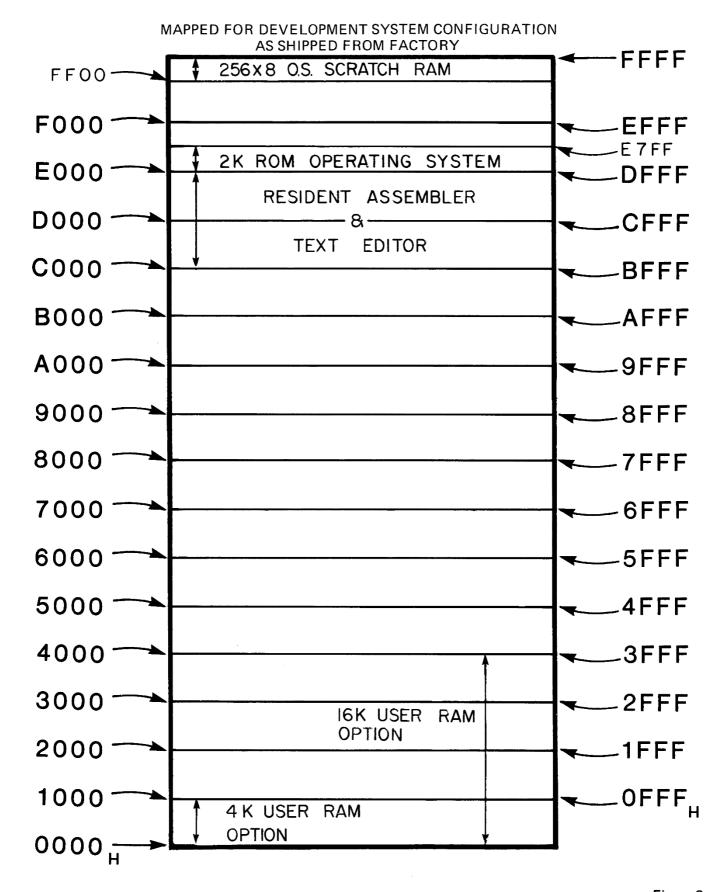

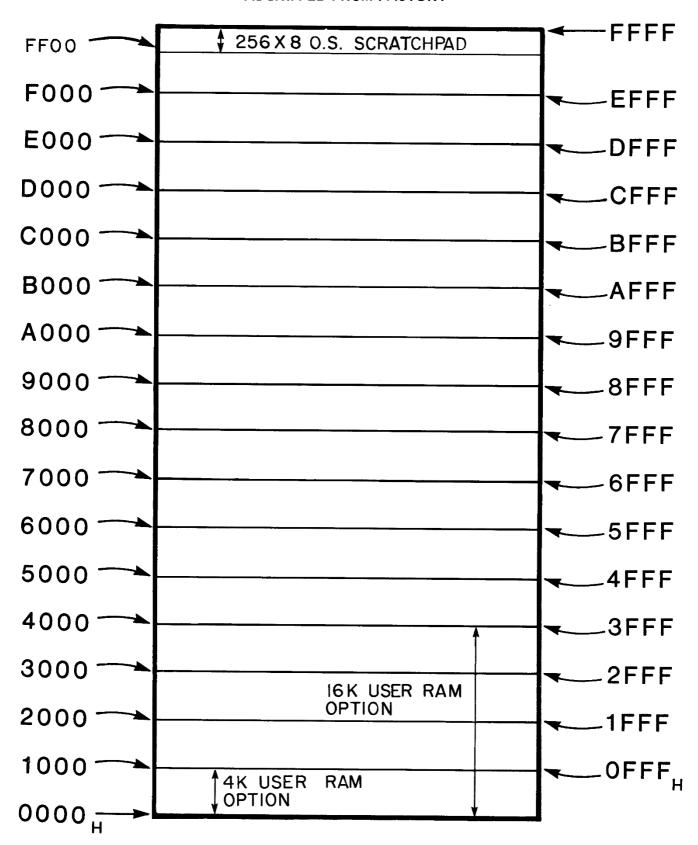

|     | Generalized memory map                                                                  | 2      | 9-3         |

|     | Memory map for SDB-80 (development system) as                                           |        |             |

|     | shipped from factory                                                                    | 3      | 9-5         |

|     | Memory map for OEM-80 (OEM) as shipped from                                             | J      | <b>J</b> -3 |

|     | factory                                                                                 | 4      | 9-6         |

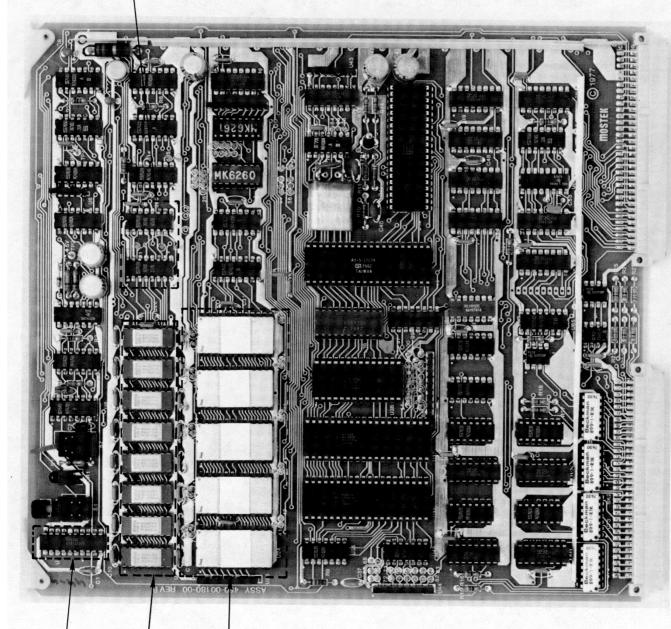

|     | Photograph of SDB-80 showing location of memo                                           |        | 3-0         |

|     | components                                                                              | 5      | 9-8         |

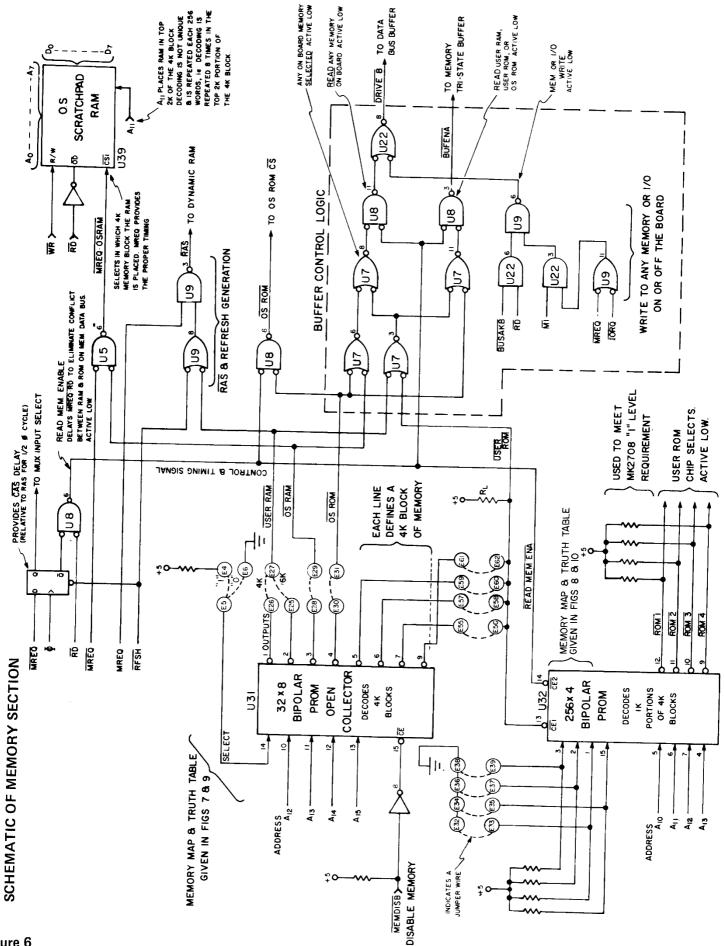

|     | Schematic of memory section                                                             | 6      | 9-10        |

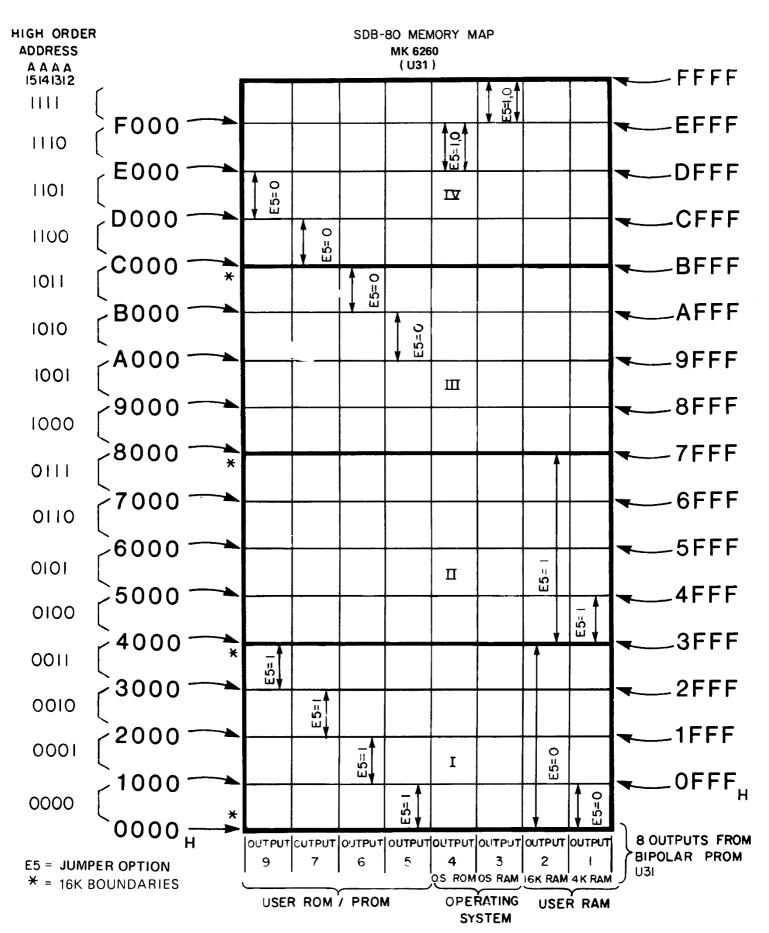

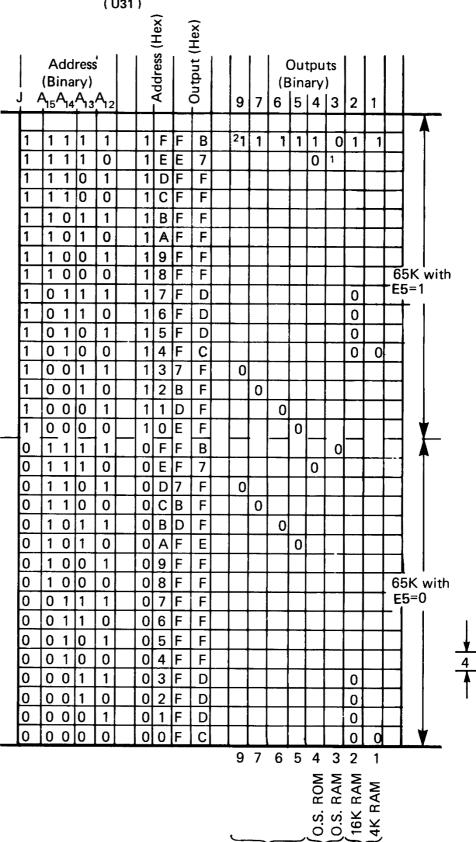

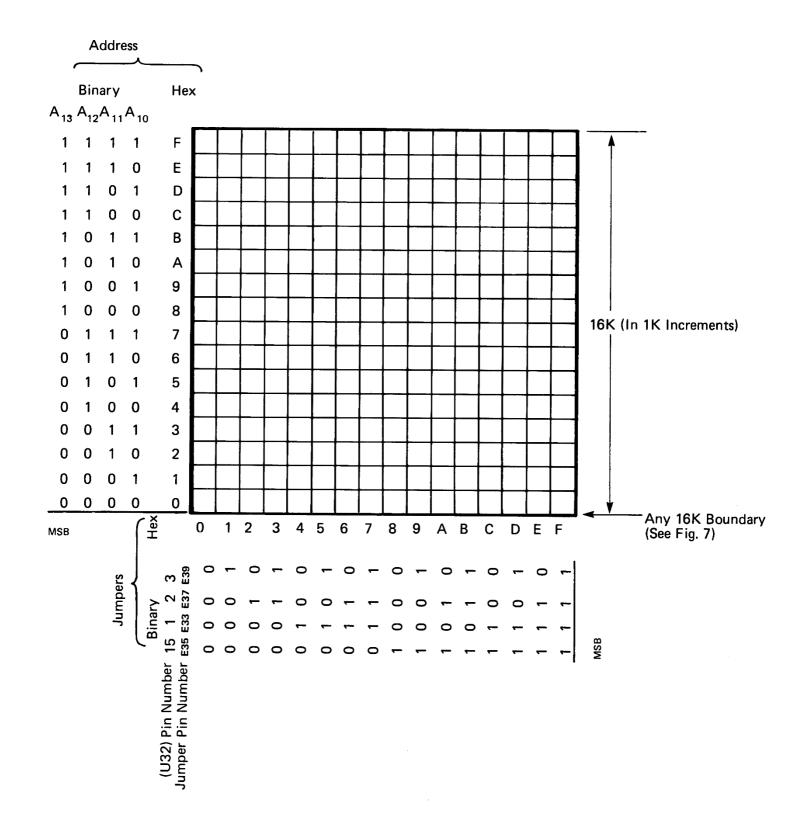

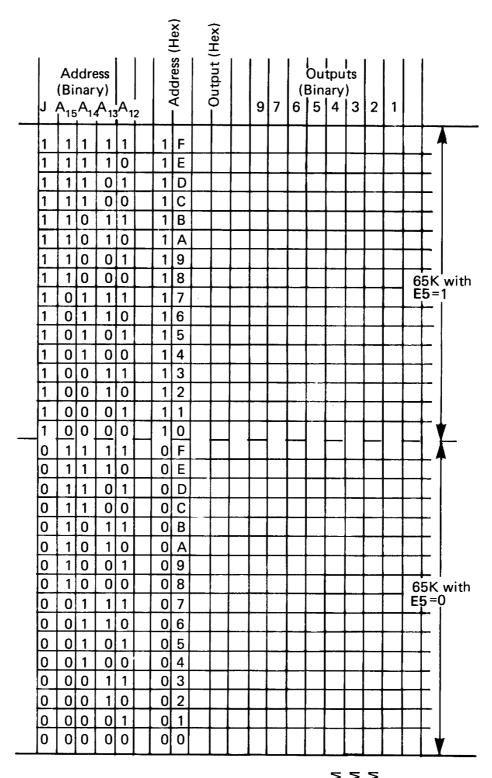

|     | Memory map of information stored in (U31)                                               | 7      | 9-13        |

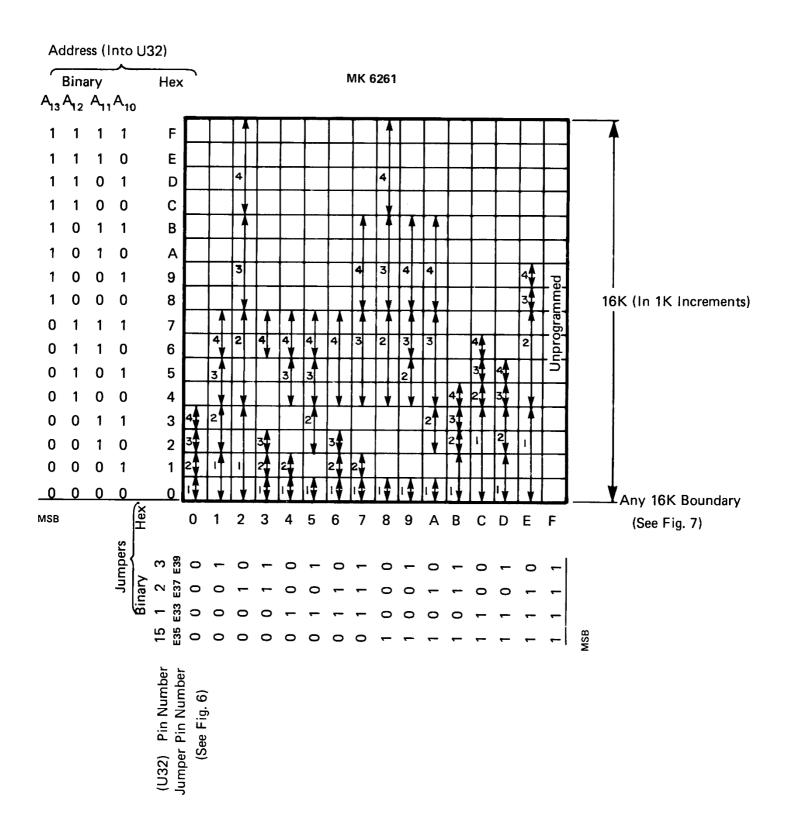

|     | Memory map of information stored in (U32)                                               | 8      | 9-16        |

|     | Truth table of information stored in (U31)                                              | 9      | 9-21        |

|     | Truth table of information stored in (U32)                                              | 10     | 9-23        |

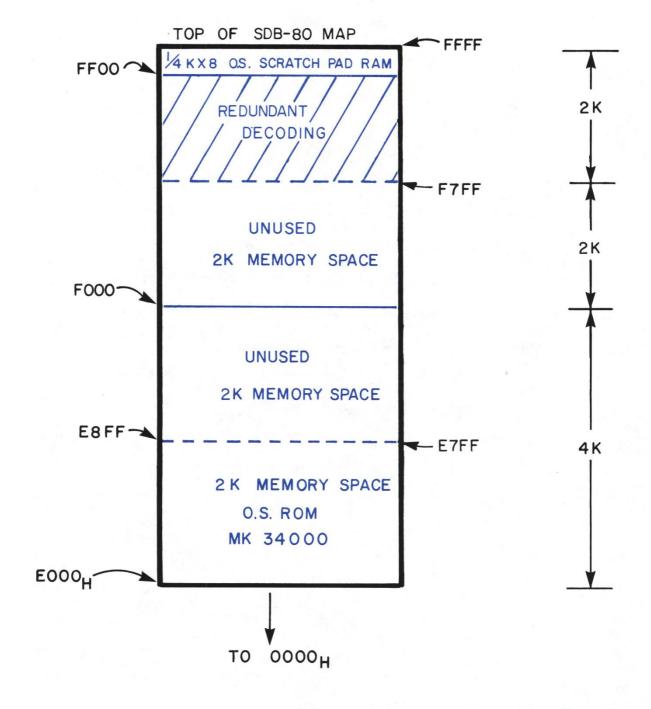

|     | Memory map showing redundant decoding of                                                | 10     | 3 20        |

|     | scratchpad RAM                                                                          | 11     | 9-27        |

|     | Memory jumper options                                                                   | 12     | 9-29        |

|     | 4K/16K wire wrap pin options                                                            | 13     | 9-31        |

|     | Jumper options                                                                          | 14     | 9-33        |

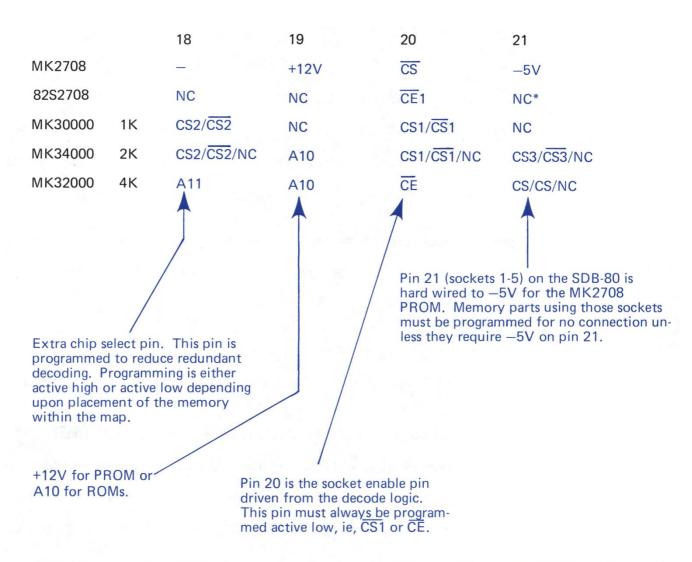

|     | MOS Chip Select                                                                         | 15     | 9-35        |

|     | Jumper Connection Examples                                                              | 16     | 9-38        |

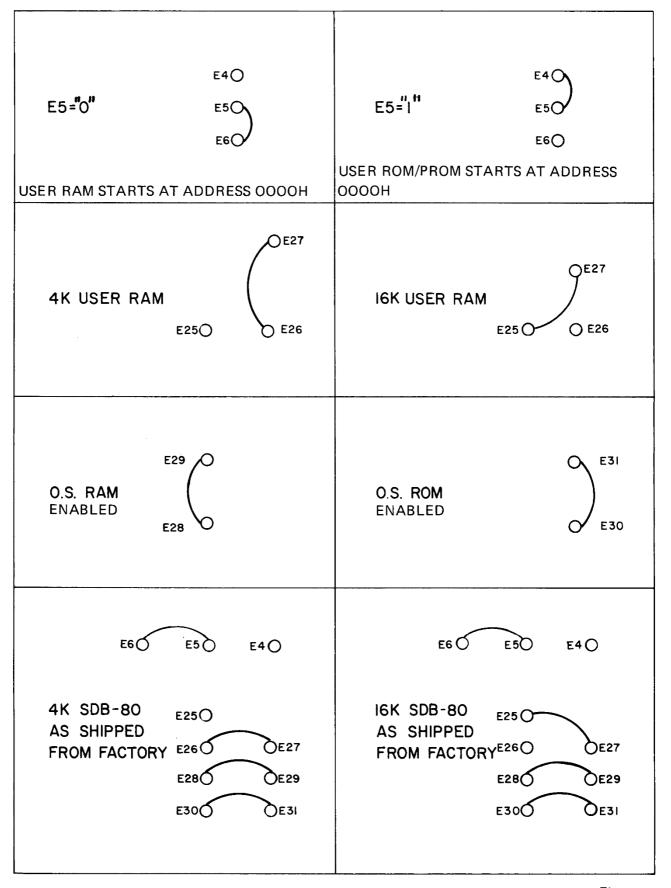

|     | User RAM and OS RAM/ROM Connections                                                     | 17     | 9-39        |

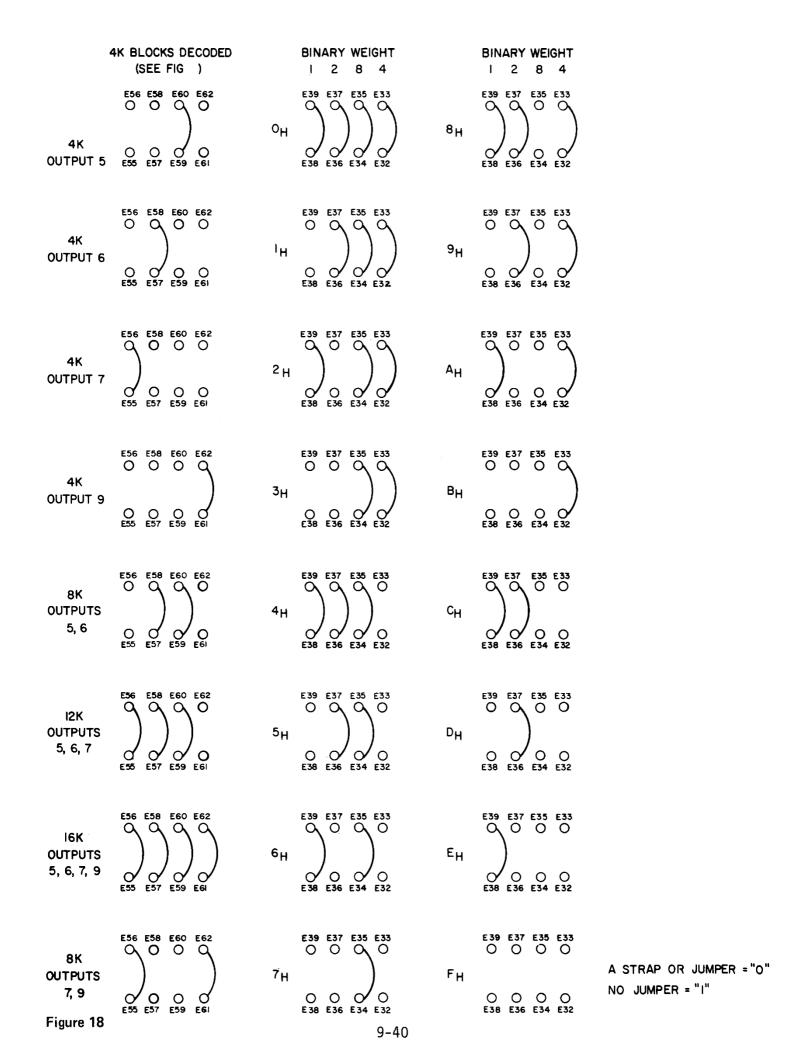

|     | Memory Space Decoded                                                                    | 18     | 9-40        |

|     | Blank Programming Charts                                                                | 19-27  | 9-42 thru   |

|     | Frank 11 ogi anmittig onat es                                                           | 13-27  | 9-51        |

| 10. | RESTART                                                                                 |        |             |

|     | Schematic of restart portion                                                            | 1      | 10-2        |

| 11. | OUTPUT BUFFERS: ADDRESS, DATA, AND CONTROL                                              |        |             |

|     | Block diagram of buffering circuits                                                     | 1      | 11-2        |

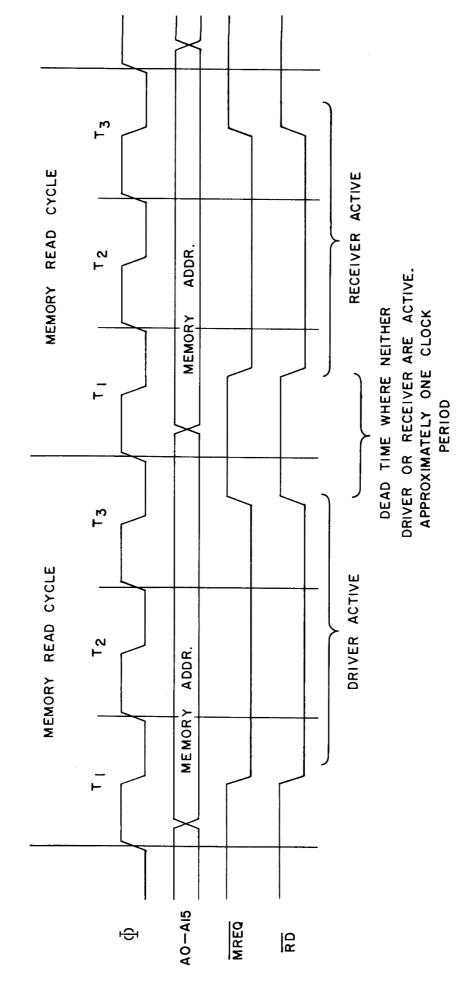

|     | Timing diagram                                                                          | 2      | 11-2        |

|     | riming dragram                                                                          | ۷      | 11-4        |

| 12. | COUNTER/TIMER                                                                           |        |             |

|     | Block diagram of counter/timer section                                                  | ]      | 12-2        |

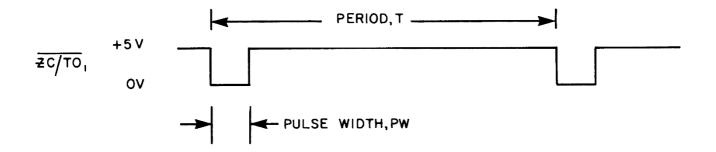

|     | Timing waveform of counter output                                                       | 2      | 12-5        |

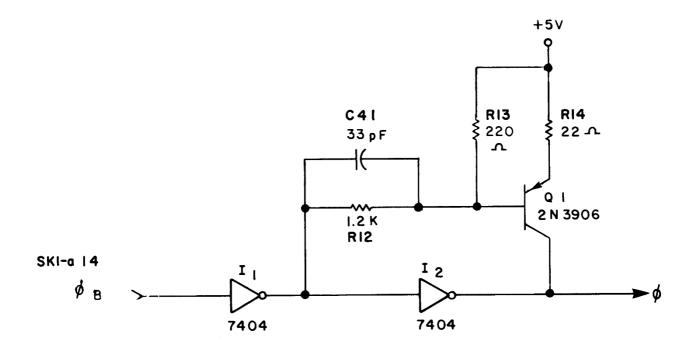

#### LIST OF FIGURES (CONT'T) FIGURE PAGE 13. **CLOCK GENERATOR** Block diagram of clock buffering 1 13-2 Schematic of clock buffer 2 13-3 14. **INTERRUPTS** Block diagram of interrupt portion 1 14-2 15. **SPECIFICATIONS** Board outline 1 15-5 Connector pin outs 15-6, 15-7 16. **BOARD SCHEMATICS** Sheets 1-4 1-4 16-1 17. **BOARD ASSEMBLY DRAWINGS** 1-2 17-1

#### SDB-80 INTRODUCTION

Mostek's SDB-80 computer board was developed for either software development or OEM board use. This approach is unique in the industry and offers several advantages.

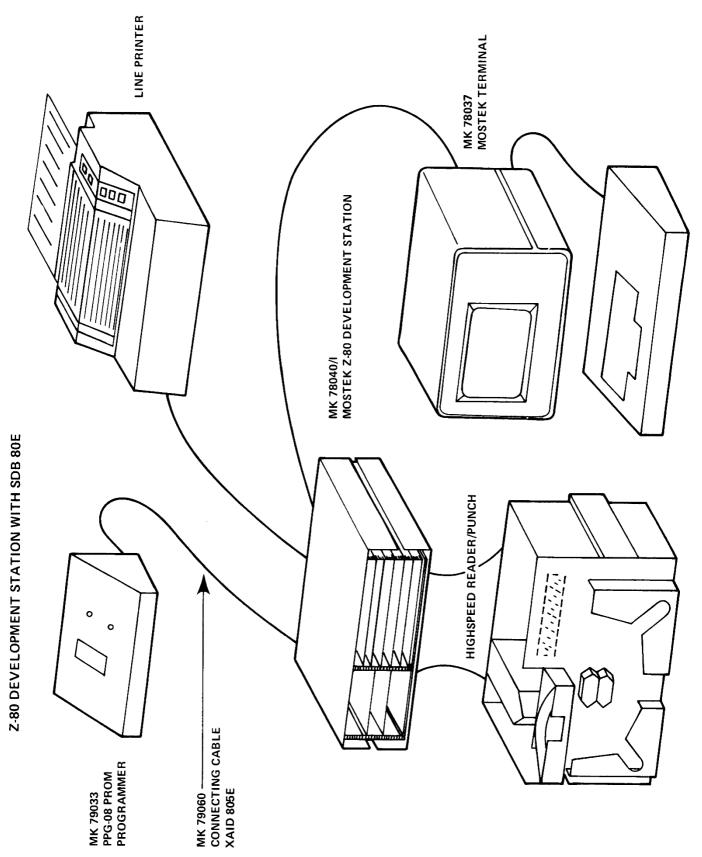

A development system configuration is illustrated in the following figure. Here we have a system that is expandable along the system bus while conveniently connecting to various peripherals through a separate connector. Driver routines are included in the operating system software that allows direct communication to the peripheral units shown. Development system firmware is located in 5 ROM/PROM sockets on the SDB-80 board.

This same board, minus the development system firmware serves as an OEM board. The OEM-80 board is a powerful stand alone computer that has uses in application areas as:

Test Equipment

Remote Data Log

Medical Electronics

Process Controllers

By using one board for both OEM and development system configurations one gains the following advantages:

Figure 1

#### 1) Versatility

For the user who builds only a few systems, the SDB-80/

0EM-80 combination can be ideal. One SDB-80

can be used to develop software which will operate on the

0EM-80. If necessary, the SDB-80 operating system can re removed and replaced by PROMs containing the user's program.

#### 2) Initial Investment is Limited

With a single card and a terminal, a complete development system can be constructed. With the Resident Assembler, Editor, Debug and Linking Loader, programs may be comfortably debugged at minimal expense.

#### 3) Total Expandability

The SDB-80 can be expanded to more comfortable development systems by the addition of Mostek support products, AIM-80 or FLP-80 for example. The user can configure the exact system he requires, and the same hardware used during development can be used in production.

# Functional Description SDB-80 Board

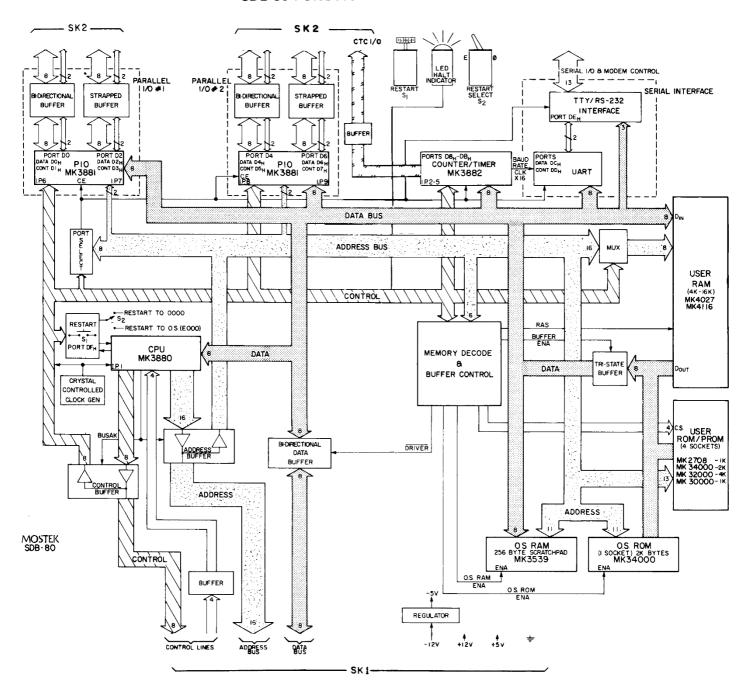

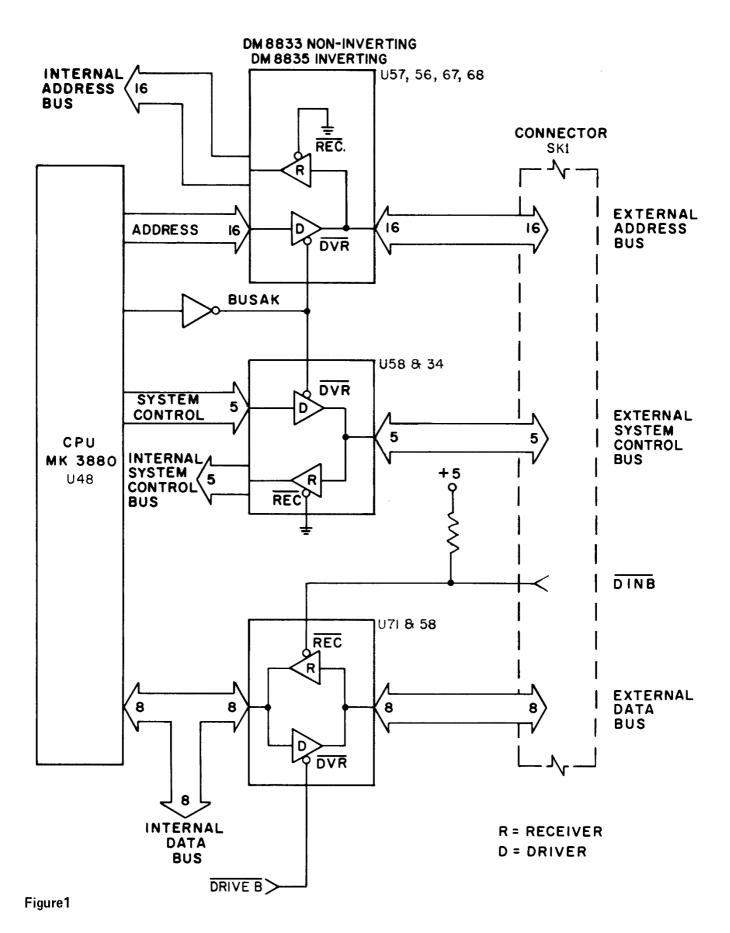

Refer to the block diagram of Fig. 1 for an overall view of the card.

#### I. Board and Connectors

The SDB-80 was placed on Mostek's standard size Eurocard based development board (233.4MM  $\times$  250MM).

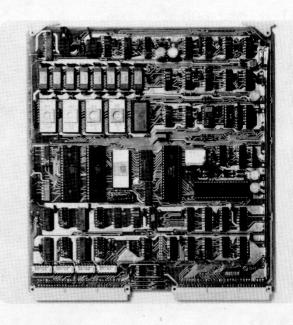

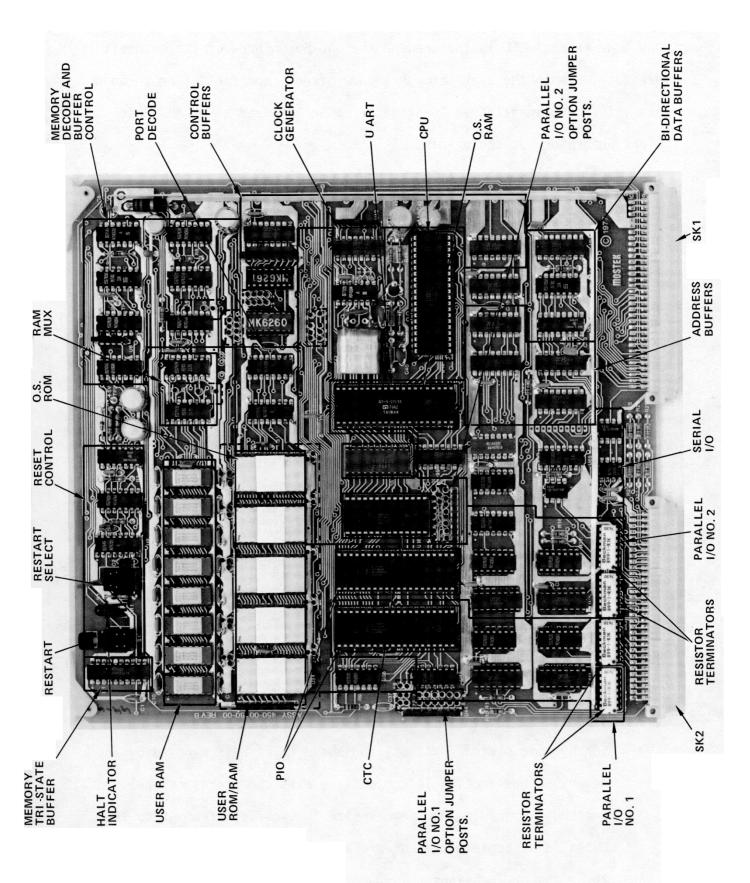

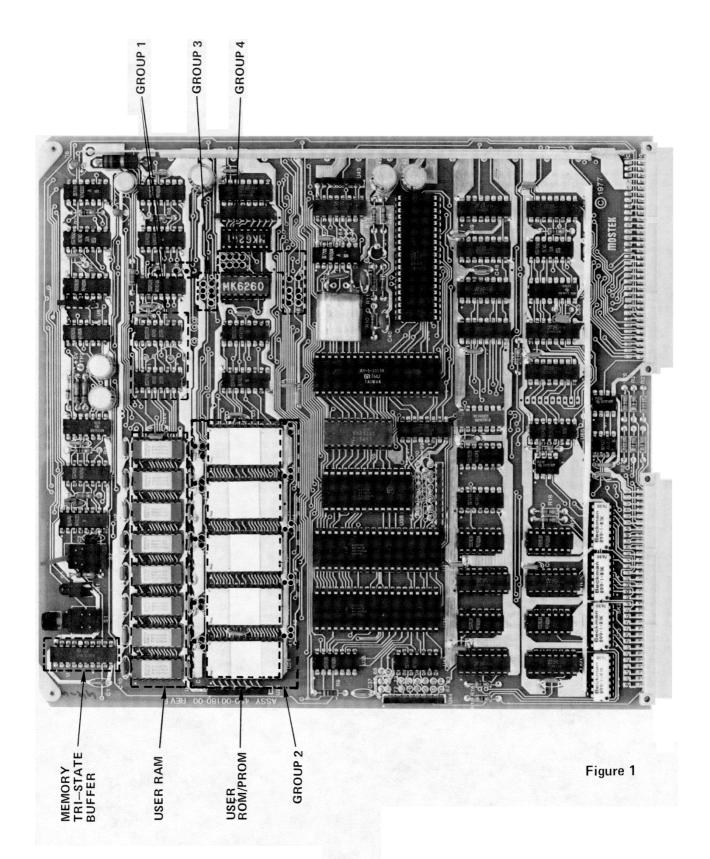

Bus/Control and peripheral lines are routed to separate 64 pin, polarized, fully protected male connectors. This functional separation facilitates system expansion in a card cage environment. Figure 2 is a photograph of the board showing the physical location of the various functional areas.

Two switches and one LED are located at the board top:

S1: initiates a reset

S<sub>2</sub>: determines the reset or restart location

LED: halt instruction indicator

#### II. Microprocessor Components

The Microprocessor complement is made up of 1 CPU (MK3880), 2 parallel I/O (MK3881), and 1 Control and Timing Circuit (MK3882). Each PIO provides two 10-bit parallel I/O Ports (8 data + 2 handshake) with bi-directional capability. The PIO is programmable under software control so as to make it as versatile as possible. In addition the chip has sophisticated interrupt capability for fast response situations.

#### SDB-80 FUNCTIONAL BLOCK DIAGRAM

Figure 1

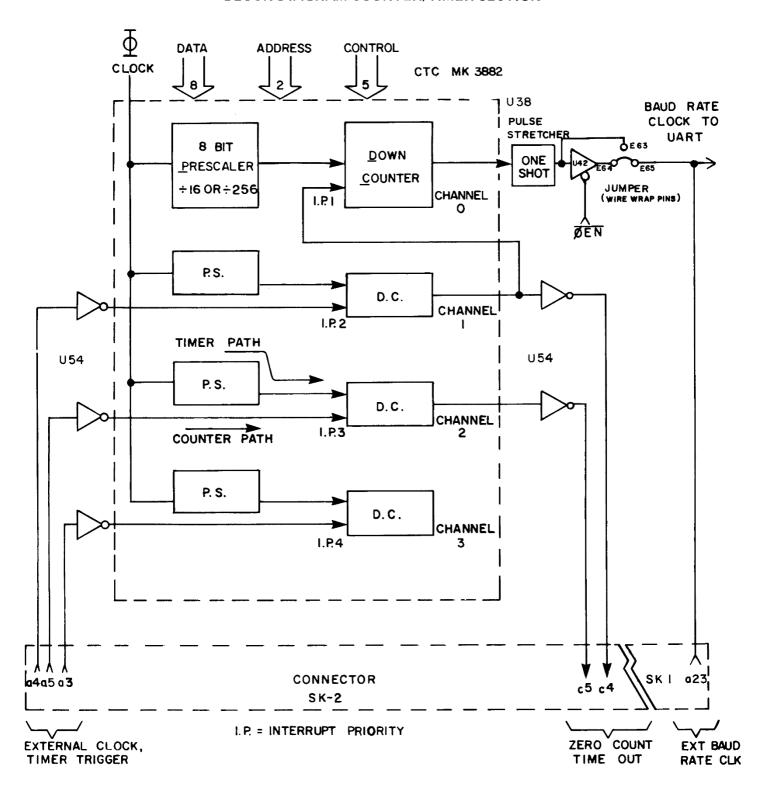

One four channel CTC is included on the SDB-80. Three of the channels are available to the user through either direct input/output or through its interrupt capability. The fourth channel is used as a BAUD Rate Clock Generator for the on-card UART.

The Z80 CPU chip with a 158 unit instruction set, single phase clock input, automatic dynamic memory refresh, and an advanced set of addressing modes is one of the most sophisticated microprocessors available today. It forms the processor for the SDB-80 computer board. This CPU generates the address and control signals, communicates with memory, I/O and peripherals, fetches and executes instructions, and provides most of the timing signals for proper operation of the board.

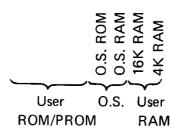

#### III. Memory

The SDB-80 has been designed to accommodate a large quantity of memory; specifically 4K or 16K bytes of dynamic RAM, 256 bytes of static RAM, and up to 5K bytes of PROM or 20K bytes of ROM. Numerous options in the memory decoding allow the placement of this memory on any 4K boundary (subdivided into 1K boundaries) within the 65K memory map. The following is a brief description of each portion of the memory section.

User RAM

Eight 16 pin sockets are provided for either 4K dynamic (MK4027) or 16K dynamic parts (MK4116) On board refresh is handled by the memory decode section in conjunction with the refresh signal from the CPU. Upgrading RAM memory size in the field from 4K to 16K bytes is a simple matter of exchanging memory parts and modifying three jumper locations.

By providing software in ROM (as opposed to loading into RAM) and through the use of a separate scratch RAM, all of the 4K or 16K USER RAM is available to the user with no restrictions.

#### ROM/PROM

Five 24 pin DIP sockets are included on the SDB-80 for development station firmware expansion and/or user program storage space. In a development system configuration one ROM socket is allocated to (and decoded as) the 2K DDT-80 operating system (MK34000 type) while the remaining four are free for accessories such as a Text Editor or Assembler. In an OEM situation all five are available to the user. Each socket can accommodate either a 1K byte PROM or a 1K, 2K, or 4K byte ROM.

#### a) 0. S. ROM

The operating system firmware is contained in 2K of ROM. The starting address for the 0. S. is fixed at  $\rm E000_{H}$ . This is entered by activating the reset switch (S1) while S2 is in the restart (TO  $\rm E000_{H}$ ) position.

#### b) User ROM/PROM

Each socket can be independently decoded anywhere within the 65K memory map. The ROM and/or PROMs can be contiguous with each other and the USER RAM or they may be separated by undecoded memory blocks. Due to the commonality of pin out, memory devices of from 1K bytes to 4K bytes can be inserted in each socket.

#### c) 0. S. RAM

A separate 256 x 8 static RAM is included to handle all scratchpad operations of the operating system. This leaves

4K/16K RAM totally free for the user and his application.

To keep the scratch RAM out of the way in a development system configuration it is decoded at the very top of the memory map;

from  $FF00_H$  to  $FFFF_H$  (location 65,279 to 65,535 in decimal).

In an OEM application this RAM is available to the user and may be decoded elsewhere in the memory map.

#### d) Memory Decode and Buffer Control

The basic information for decoding memory within the SDB-80 memory map is contained within two bi-polar Read Only Memory parts. The first ROM divides the map into 16 - 4K memory blocks while the second divides a given 4K memory block into 4 - 1K segments. Jumpers are then used to determine which 1K and 4K blocks are actually decoded.

Two control lines are generated in this logic section.

DRIVEB: Indicates Data Bus Drive by the SDB-80

during write or interval read cycles.

BUFFER ENA: Determines whether the memory data buffer is

in the active or tri-state (high impedance) condition.

#### IV. Parallel I/O Interface

Two parallel I/O chips provide four 10 bit (8 data plus 2 handshake) ports. These are available at connector SK2. Each PIO has one bi-directional port and one port that can be hard wired either as an input or as an output. Each line is TTL buffered and has providion

for a termination network. Logically each port pair looks like one of the on-board PIO divices.

#### V. Serial I/O Interface

The serial I/O interface consists basically of a UART, a baud rate clock generator, and the I/O buffering to connector SK2. Asynchronous data rates of from 110 to 9600 baud can be accepted. The baud rate clock is programmable by the CPU, a direct input to the CPU from the serial data allows the CPU to measure the baud rate of a terminal. Direct interface is provided to both teletype (20 mA current loop) and to standard RS-232 terminals (voltage drive).

#### VI. Counter and Timing Circuit (CTC)

The SDB-80 provides a four channel counter chip that operates under softward control. Interfacing to and from the CTC can be accomplished by input lines (either count or timer mode), by output signals (zero count detect), or through the Z-80 interrupt structure. All four channels are available to the user. However, channel "0" (zero) is generally used as the on board baud rate generator when the serial I/O port is used. Features such as selectable prescaler, count modules, readable down counter, and programmable interrupt are all under software control.

#### VII. Bus Lines - Data, Address, Control

All Lines going on to and off of the board are TTL buffered and/or terminated. The address and data bus lines are buffered with bidirectional divices so that data can go in both directions. Bus lines are brought out to connector SKI for ease in system expansion.

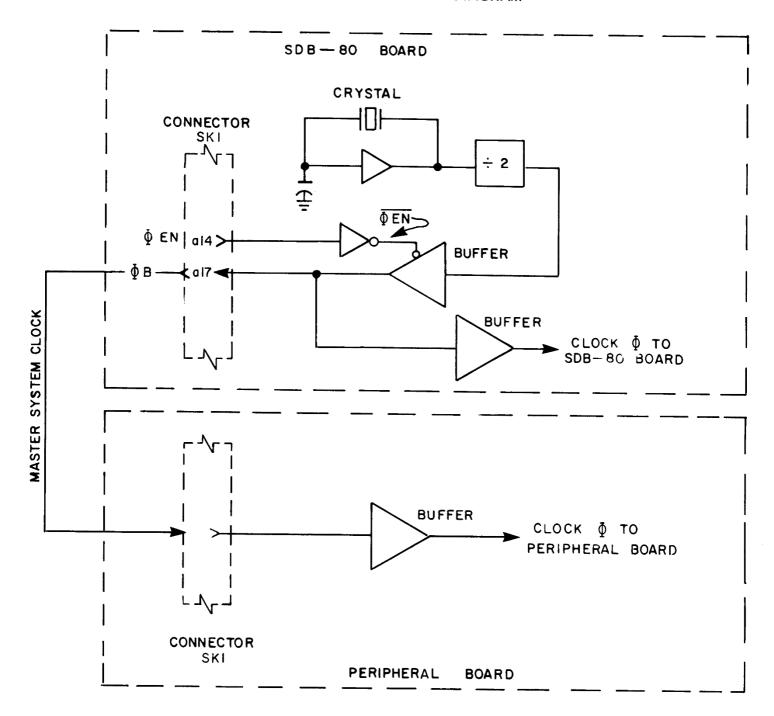

#### VIII. Clock Generator

The SDB-80 comes with a crystal controlled clock generator. This clock drives all the necessary components on the board, is buffered to drive off the board and is gated to accept an external clock. The crystal frequency of 4.916 MHz is divided and supplied to the system as 2.458 MHz. This frequency is a multiple of all the desired baud rates.

#### IX. Reset/Restart

The SDB-80 can be reset to the bottom of memory at location  $0000_{\rm H}$  or restarted to the operating system at  $E0000_{\rm H}$ . Toggle switch S2, located at the top edge of the board, is used for this function. Push button switch S1 creates the reset.

The top edge LED indicates when the CPU is executing a HALT instruction (  $OP \ code \ 76_{H}$ ).

#### X. Port Select

Two dual 2 to 4 line decoders are used for port selection and decode. This logic decodes the address and control lines for PIO, CTC, and the serial port selection. Of the possible 256 ports available, 16 are used on this board (DO through DF).

#### INITIAL SDB-80 CHECK OUT PROCEDURE

The SDB-80 board has been fully tested by MOSTEK prior to shipment. The following initial checkout procedure is simply a functional check of the board. If the board fails to perform any of the steps outlined, turn off the power, recheck the board hook up, and try the checkout procedure again. If the problem persists, contact MOSTEK for assistance.

Refer to the Figures on pages 2-3, 15-5 and 15-6 for physical layouts, pin-outs, etc.

- I) Minimum Equipment Needed (not supplied by MOSTEK) for SDB-80 Checkout.

- 1) A serial ASCII terminal i.e., TTY, Silent 700, or CRT equipment.

- Power Supplies

- + 12V @ 480 mA max

- + 5V @ 2.6 A max

- 12V @ -180 ma max

UNDER NO CIRCUMSTANCES SHOULD 115 VAC EVER BE APPLIED DIRECTLY TO THE SDB-80 BOARD!

#### II. Board Hookup

Power should be supplied to the board per the following pin out:

| POWER | <u>CONNECTOR</u> | PINS           |

|-------|------------------|----------------|

| + 12V | SK1              | a6, c6         |

| + 5V  | SK1              | a4, c4, a5, c5 |

| GND   | SK1              | al, cl, a2, c2 |

| - 12V | SK1              | a3, c3         |

The serial I/O should be connected to the appropriate peripheral as described in Section 6.

III) Initial Check Out Procedure \*

The following terminology is used in this section in reference to the terminal:

1 indicates carriage return

▲ indicates carat or up arrow (ASCII Sen).

indicates period

XXXX, WXYZ indicates hex digits

The underlined portion of the commands is entered by the user. The non-underlined portion is the system response.

- 1) Set S2 to position E (0.S. reset at OEOOOH)

- 2) Apply power

- 2a) Press reset (on SDB-80): Restart to OS at  $E000_H$

- 3) Depress (carriage return) : Restart to operating system at memory location E000<sub>H</sub>

- 4) Terminal now shows a "." as the response. A "." indicates the system is in the command mode and is ready to accept another command. The baud rate has been automatically calculated and adjusted to the proper value.

- 5) . M to 0, 20

: The display or tabulate memory command displays contents of memory from locations  $0000_{\rm H}$  through  $20_{\rm H}$ . Each two digit hex number corresponds to one 8 bit byte (binary).

<sup>\*</sup> Applies to Non-Floppy Disk Systems.

6) .M 0 )

0000 XX

: Contents of location  $0000_{\mbox{\scriptsize H}}$  displayed

0000 XX 76 ~

: Contents of location  $0000_H$  modified to contain 0P code  $76_H$ . 0P code 76 is the HALT

instruction.

0000 76

: System responds by showing that  $76_H$  is now

stored in location 0000H.

7) 0000 76.

: Period entered

: System returns to command mode

8) <u>E 0 1</u>

(No response on terminal LED lights.)

: An EXECUTE command causes the CPU to execute the instruction in memory location  $0000_{\rm H}$  - a HALT instruction. This is indicated by the LED. Notice there is complete loss of control by the keyboard.

Depress restart

button S1

: LED goes out

: Carriage return after restart causes the baud rate

to be calculated.

.

: System has been returned to the command mode

9) .M 0 🗎

: Memory location 0000H is interogated.

0000 76

: Memory location 0000H still has OP code 76H stored.

Reset does not destroy memory contents.

0000 76 .

: A period returns the system to the command mode.

10) Set S2 to O

Depress restart

button S1

(no response on terminal; LED lights).

: System has been reset to memory location  $0000_H$ . From 9) above one sees that  $76_H$  is stored at  $0000_H$ . Returning to location  $0000_H$  initiates the HALT instruction which lights the LED.

Set S2 to E Depress restart button S1 : System has been returned to command mode.

#### 11) .<u>R 1</u> )

PC AF I IF DE HL A'F' B'C' D'E' H'L' IX IY SP

XXXX WXYZ XXXX WXYZ XXXX WXYZ XXXX WXYZ XXXX WXYZ XXXX

:The REGISTER DISPLAY command prints out the register header designation along with the contents of each CPU register.

- 12) <u>.M FFE6</u> <u>)</u> :SP WXYZ <u>)</u>

- :IY WXYZ 🐊

- :IX WXYZ 🕽

- :L'XX

- :H' XX 🕽

- :E' XX **\_**

- :D' XX 🔾

- :C' XX \_**2**

- :B' XX 🕽

- :F' XX 🔾

- :A' XX 🔾

- :L XX 之

- :H XX **→**

- :E XX **→**

- :D XX 🕽

- :c xx **→**

- :B XX **→**

- IF XX 🔾

:Contents of memory location FFE6H displayed. This location is very near the top of the memory map which resides in the scratch pad RAM. This is the location where the register information is stored. Each time is depressed the display indexes to the next memory location. Notice that the memory locations in this part of memory are given mnemonics rather than in hex digits.

:I XX ]

:F XX 💃

:A XX 🕽

:PC WXYZ 🚅

: The program counter information is located in memory locations  $\mathsf{FFFE}_H$  and  $\mathsf{FFFF}_H$  (two bytes).  $\mathsf{FFFF}_H$  is the very top of memory. The next a rolls over the boundry of memory map to the start of memory - location  $\mathsf{0000}_H$ .

0000 XX

At this point the SDB-80 has been shown to be functional.

To determine the version number of the Operating System firmware, display contents of memory location  ${\rm E065}_{\rm H}.$

#### PORTS, PERIPHERALS, AND DRIVERS

The SDB-80, through its I/O ports, can communicate with many types of peripheral devices. Drivers have been included in the O.S. to make this board as easy to use and interface with as possible. The following data lists all the peripheral devices supported by a software driver in the O.S. along with specific interface port information.

|    | Peripheral                                            | Port                | Connector |

|----|-------------------------------------------------------|---------------------|-----------|

| 1) | Teletype                                              | Serial              | SK2       |

| 2) | Teletype tape reader/punch                            | Serial              |           |

| 3) | RS-232 peripheral                                     | Serial              |           |

| 4) | Silent 700 (keyboard & printer)                       | Serial              |           |

| 5) | High speed paper tape reader                          | DO, Parallel        |           |

| 6) | High speed paper tape punch                           | D2, Parallel        |           |

| 7) | Line printer                                          | D6, Parallel        |           |

| 8) | PROM programmer<br>(Software available on paper tape) | D4 and D6, Parallel | SK2       |

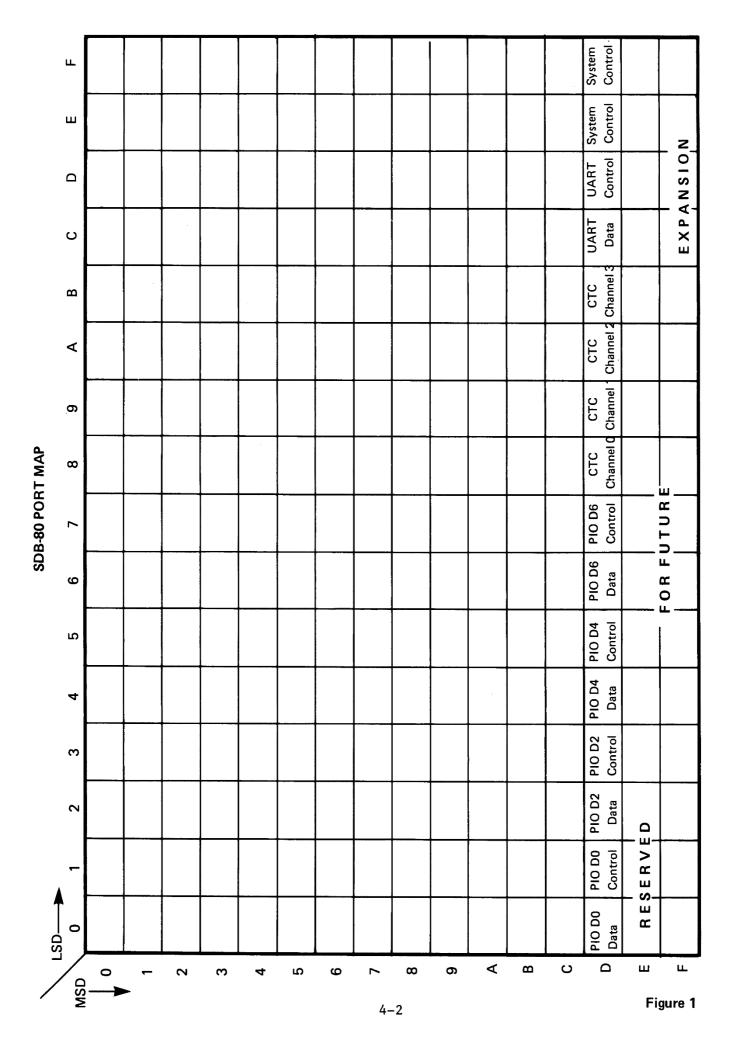

Figure 1 shows a map of all possible 256 ports available for the SDB-80. The bottom 48 ports are committed now or reserved for the over-all Z-80 development system.

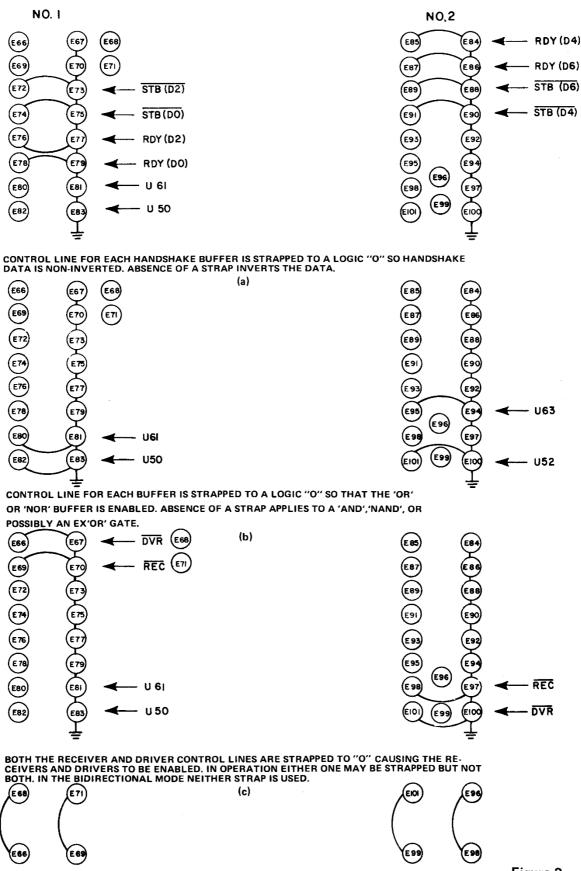

# JUMPER OPTIONS ON SDB-80 AS SHIPPED FROM THE FACTORY

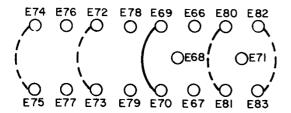

Figure 1 shows the locations and grouping of wire wrap posts that allow the SDB-80 user the flexibility of installing jumpers to achieve the format options available.

Figure 2 illustrates how that option is connected when the board is shipped from the factory.

Additional wiring options will be detailed in later sections of this manual.

# SDB-80 PRODUCTION VERSION AS SHIPPED FROM FACTORY

| RAM: 4K ROM SOCKETS: 2K                                                                                                    | RAM: 16K<br>ROM SOCKETS: 2K | SECTION WHERE OPTION IS FOUND     |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------|

| E64 O<br>E63 O<br>E65 O                                                                                                    | E64O<br>E63O<br>E65O        | CLOCK GENERATOR<br>COUNTER/TIMER  |

| E1O<br>E2O<br>E3O                                                                                                          | E1O<br>E2O<br>E3O           | MEMORY, RAM MUX                   |

| 6 0<br>E22 E23 E24                                                                                                         | E 22 E 23 E 24              | MEMORY, DECODE AND BUFFER CONTROL |

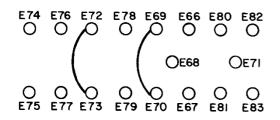

| E68 E7I<br>○ ○ ○<br>E67 E70 E73 E75 E77 E79 E8I E83<br>○ ○ ○ ○ ○ ○ ○ ○<br>○ ○ ○ ○ ○ ○ ○<br>E66 E69 E72 E74 E76 E78 E80 E82 | SAME                        | PARALLEL INTERFACE # I            |

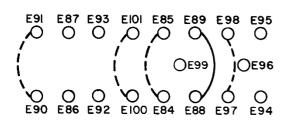

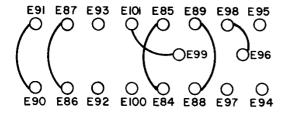

| E84 E86 E88 E90 E92 E94 E97 E100  E96 E99  E85 E87 E89 E91 E93 E95 E98 E101                                                | SAME                        | PARALLEL INTERFACE # 2            |

|                                                                                                                            | T                           |                                   |

Figure 2

# SDB-80 PRODUCTION VERSION AS SHIPPED FROM FACTORY (Cont'd)

| <del></del>                                 |                      | <del>                                     </del> |                                                |

|---------------------------------------------|----------------------|--------------------------------------------------|------------------------------------------------|

| E55 E57 E59 E6I<br>O O O<br>E56 E58 E60 E62 |                      | SAME                                             | MEMORY                                         |

| E33 E35 E3<br>O O O<br>E32 E34 E36          | )                    | SAME                                             |                                                |

| E27 E29 E3<br>O O O<br>E25 E26 E28 E3       | )                    | E27 E29 E3I<br>O O O<br>E25 E26 E28 E30          | RAM<br>MEMORY                                  |

| O<br>E <b>4</b>                             | E5 E6                | SAME                                             | O E M / development<br>ROM / PROM / RAM select |

| E9<br>O<br>E7 E8                            | E 40<br>O<br>E41 E42 | SAME                                             | ROM/ PROM I                                    |

| EI2<br>O<br>EIO EII                         | E43<br>O<br>E44 E45  | SAME                                             | ROM/ PROM 2                                    |

| E15<br>O<br>E13 E14                         | E46<br>O<br>E47 E48  | SAME                                             | ROM/ PROM 3                                    |

| E18<br>O<br>E16 E17                         | E49<br>O<br>E50 E5I  | SAME                                             | ROM/ PROM 4                                    |

| E2I<br>O<br>E19 E20                         | E52<br>O<br>E53 E54  | SAME                                             | ROM/ PROM 5                                    |

Figure 2

SDB TO PERIPHERALS

# 6

## Interface Information

The SDB-80 will interface directly with a number of different peripheral units. This section describes the interconnect cableing and the jumper options (on the SDB-80) necessary for the interface to a number of typical peripherals.

The peripherals covered in this section are:

TERMINALS - - PORT: SERIAL

- 1) Teletype model ASR-33 without reader step control

- 2) Teletype model ASR-33 with reader step control

- 3) Texas Instruments Silent 700 model 733 ASR (or any RS232 terminal)

PAPER TAPE READER/PUNCH - - PORT: PARALLEL

| 1) | Plessy model PM-750 Paper Tape Reader           | Port DO      |

|----|-------------------------------------------------|--------------|

| 2) | Plessy model PM-1000 Paper Tape Reader          | Port DO      |

| 3) | Plessy model PM C4020 Paper Tape Reader/Punch   | Ports DO, D2 |

| 4) | EECO model RPF9360B0AAA Paper Tape Reader/Punch | Ports DO, D2 |

PRINTERS - - PORT: PARALLEL

| 1) | Data Products model 2310   | Port D6 |

|----|----------------------------|---------|

| 2) | Data Printer model CT 1334 | Port D6 |

PROM PROGRAMMER - - PORT: PARALLEL

1) Mostek PPG-08 Ports D4, D6

## I. SDB-80 INTERFACE TO SERIAL TERMINALS

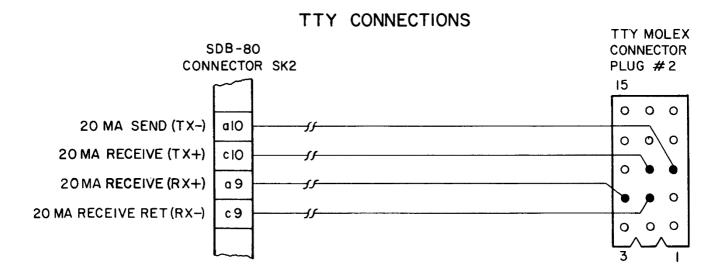

For applications <u>not</u> requiring a reader step control, an ASR-33 teletype may be connected (TTY plug #2) directly to the SDB-80. No jumper options or modifications are required on the SDB-80. The interconnect schematic is shown in Figure 1.

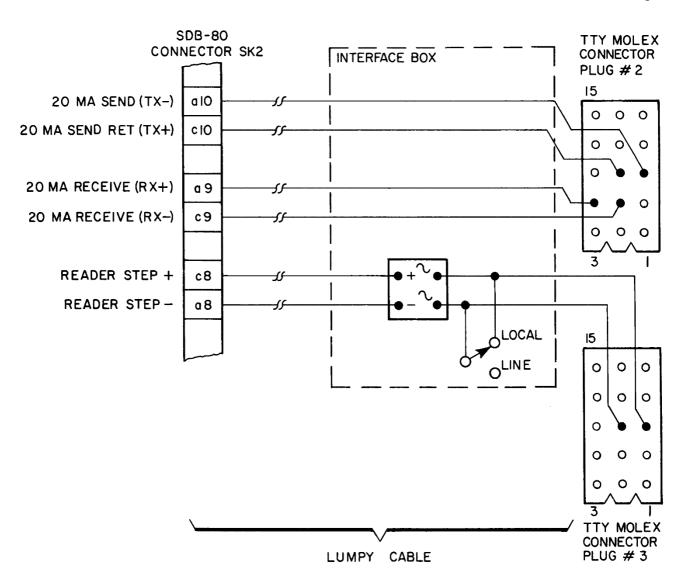

The resident assembler requires a controlled reader, for this and other applications requiring reader step control, TTY plugs # 2 and # 3 are used in conjunction with a solid state relay. No jumper options or modifications are required on the SDB-80. The interconnect schematic is shown in Figure 2. Other connections are possible but require a more thorough knowledge of the ASR-33.

A Texas Instruments model 733 ASR (silent 700) terminal will interface directly to the SDB-80. No jumper options or modifications are required on the SDB-80.

Figure 1

Figure 2

## **CABLE WIRING LIST**

| SDB-80<br>CONECTIOR SK2<br>PIN | RS-232<br>SIGNAL    | SILENT 700<br>CONNECTOR<br>PIN |

|--------------------------------|---------------------|--------------------------------|

|                                |                     | 1                              |

|                                |                     | 14                             |

| a9                             | TRANSMITTED DATA    | 2                              |

|                                |                     | 15                             |

| c3                             | RECEIVED DATA       | 3                              |

| c10                            | 20mA + SEND         | 16                             |

| а7                             | REQUEST TO SEND     | 4                              |

| a10                            | 20mA – SEND         | 17                             |

| с7                             | CLEAR TO SEND       | 5                              |

| a8                             | RDR STEP —          | 18                             |

| <b>c</b> 6                     | DATA SET READY      | 6                              |

| с8                             | RDR STEP +          | 19                             |

| a1                             | GND                 | 7                              |

| a6                             | DATA TERMINAL READY | 20                             |

| c10                            | CARRIER DETECT      | 8                              |

|                                |                     | 21                             |

|                                |                     | 9                              |

|                                |                     | 22                             |

| с9                             | 20mA – REC          | 10                             |

|                                |                     | 23                             |

|                                |                     | 11                             |

| a9                             | 20mA + RECEIVE      | 24                             |

|                                |                     | 12                             |

|                                |                     | 25                             |

|                                |                     | 13                             |

II. SDB-80 Interface to Paper Tape Reader/Punches Plessy models PM 750 and PM 1000 paper tape readers will interface to the SDB-80 as shown in wire list below.

| SDB-80   | CONNECTOR | (25 PIN "D" C | ONN. FEMALE) |

|----------|-----------|---------------|--------------|

| SIGNAL   | SK2       | PLESSY 750    | PLESSY 1000  |

| SDB (DO) | c28       | 24            | 25           |

| RDY (DO) | a28       | 22            | 17           |

| DO (0)   | c32       | 1             | 1            |

| DO (1)   | c31       | 2             | 2            |

| DO (2)   | c30       | 4             | 4            |

| DO (3)   | c29       | 5             | 5            |

| DO (4)   | a29       | 7             | 7            |

| DO (5)   | a30       | 8             | 8            |

| DO (6)   | a31       | 10            | 10           |

| DO (7)   | a32       | 11            | 11           |

The jumper options on the SDB-80 should be configured as shown in Figure 4. Jumpers shown with SOLID lines must be installed (Port DO). Jumpers shown with DASHED LINES (Port D2) do not affect the operation of the reader. Jumpers NOT SHOWN must not be installed.

The reader should be configured such that READER DATA and the READER RUN (RUN) and SPROCKET (SPK) signals are active low.

## INTERFACE JUMPERS

SECTION WHERE THE JUMPERS ARE LOCATED

PARALLEL I/O # I

FIGURE 4

PARALLEL I/O # 1

FIGURE 5

PARALLEL I/O # 2

FIGURE 6

PARALLEL I/O # 2

FIGURE 7

A Plessy model PM-C4020 or EECO model RPF9360B0AA Reader/Punch will interface to the SDB-80 as shown in wire list.

| SDB-80<br>SIGNAL | CONNECTOR<br>SK2 | PLESSY PM-C4020       | EECO PPF9360      |

|------------------|------------------|-----------------------|-------------------|

| STB (DO)         | c28              | J1-9                  | J1-9              |

| RDY (DO)         | a28              | J1-16                 | J1-5              |

| DO (0)           | c32              | J1-1                  | J111              |

| DO (1)           | c31              | J1-2                  | J1-12             |

| DO (2)           | c30              | J1-3                  | J1-13             |

| DO (3)           | c29              | J1-4                  | J1-14             |

| DO (4)           | a29              | J1-5                  | J1-15             |

| DO (5)           | a30              | J1-6                  | J1-16             |

| DO (6)           | a31              | J1-7                  | J1-17             |

| DO (7)           | a32              | J1-8                  | J1-18             |

| GND              | a1               | J1-11, 12, 13, 18, 24 | J1-22, 23, 24, 25 |

| RDY (D2)         | a23              | J2-11                 | J2-12             |

| STB (D2)         | a23              | J2-1 <b>2</b>         | J2-13             |

| D2 (0)           | c27              | J2-1                  | J2-3              |

| D2 (1)           | c26              | J2-2                  | J2-4              |

| D2(2)            | c25              | J2-3                  | J2-14             |

| D2 (3)           | c24              | J2-4                  | J2-15             |

| D2 (4)           | a24              | J2-5                  | J2-2              |

| D2 (5)           | a25              | J2-6                  | J2-1              |

| D2 (6)           | a26              | J2-7                  | J2-5              |

| D2 (7)           | a27              | J2-8                  | J2-6              |

| GND              | c1               | J2-14, 15, 18, 23, 25 | J2-20, 25         |

The jumper options on the SDB-80 should be configured as shown in Figure 5.

The reader should be configured so the READER DATA, the READER RUN SIGNAL  $(\overline{RUN})$  and the SPROCKET SIGNAL  $(\overline{SPKT})$  are active low.

The punch should be configured so the PUNCH DATA and the PUNCH READY (PRDY) are ACTIVE HIGH. The PUNCH COMMAND (PCMD) should be ACTIVE LOW.

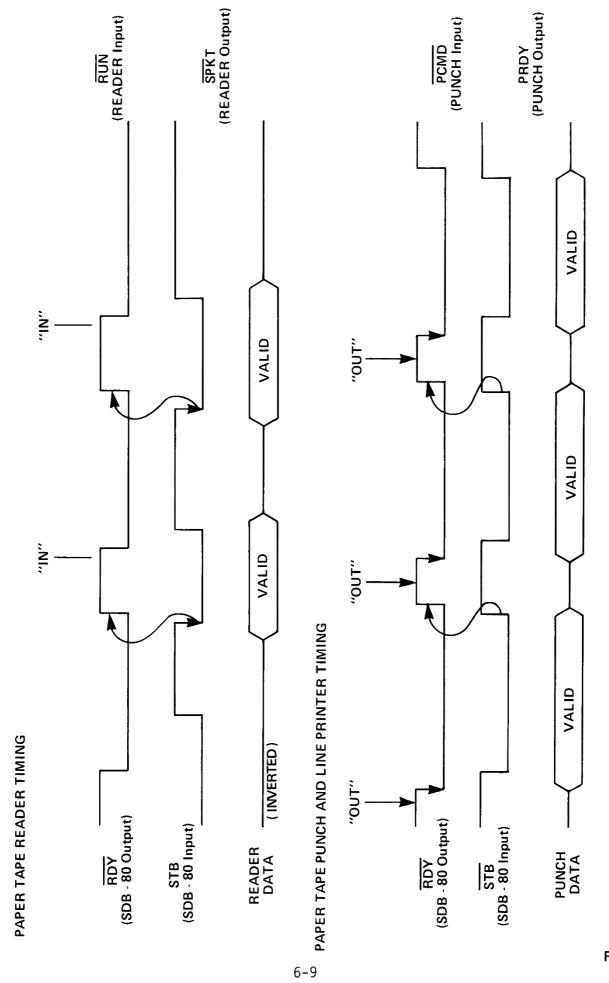

The timing for the reader and punch data transfer is shown in Figure 8.

#### Reader Timing

An "IN" instruction causes the  $\overline{\text{RUN}}$  signal to go low requesting a character. The  $\overline{\text{SPKT}}$  signal goes high indicating that data is not valid. After data becomes valid  $\overline{\text{SPKT}}$  goes low causing the  $\overline{\text{RDY}}$  line to go high. The negative edge of  $\overline{\text{SPKT}}$  generates an interrupt to the processor. The processor then reads or inputs the next word.

### Punch (or Printer) Timing

An "OUT" instruction outputs data to the paralled I/O port causing the  $\overline{PCMD}$  line to go low. The PUNCH READY (PRDY) goes low indicating the punch is busy and has not accepted data. When the punch has accepted data from the port and is ready for another character, the PRDY signal goes high causing  $\overline{PCMD}$  to go high. This action generates an interrupt to the processor. The processor then outputs the next word.

Figure 8

#### III. SDB-80 Interface to Line Printers

In this example Data Products line printer model 2310 is interfaced to the SDB -80. The jumper options on the SDB-80 should be configured as shown in Figure 6. Jumpers shown with SOLID lines must be installed (Port D6). Jumpers shown with DASHED lines (Port D4) do not affect the operation of the printer. Jumpers NOT SHOWN must not be installed.

The line printer should be configured so that the DATA and ACKNOWLEDGE lines are active high and the character strobe is negative edge triggered.

The following wire list defines the interface cable for the Data Products line printer.

| SDB-80<br>SIGNAL | CONNECTOR<br>SK2 | DATA PRODUCTS<br>WINCHESTER CONNECTOR |

|------------------|------------------|---------------------------------------|

| D6 (0)           | c15              | В                                     |

| D6 (1)           | c14              | F                                     |

| D6 (2)           | c13              | L                                     |

| D6 (3)           | c12              | R                                     |

| D6 (4)           | a12              | V                                     |

| D6 (5)           | a13              | Z                                     |

| D6 (6)           | a14              | (N)                                   |

| RDY (D6)         | a11              | (J)                                   |

| STB (D6)         | c11              | E                                     |

| GND              | a1               | D,J,N,T,X,(B),(K),(M), C              |

Timing for the line printer is the same as the punch and is shown in Figure  $8. \,$

## IV. SDB-80 Interface to PROM Programer

A Mostek PROM Programmer (PPG-08, MK 79033) for MK 2708 PROMS will interface to the SDB-80 with the PROM Programmer interface cable XAID-805 (MK79041).

The jumper options on the SDB-80 should be configured as shown in Figure 7.

No jumper options are required on the PROM Programmer.

The wire list defines the Prom Programmer interface cable.

SDB-80 to PPG-98

| SDB-80<br>SIGNAL | CONNECTOR<br>SK2 | PPG-08<br>J1 |

|------------------|------------------|--------------|

| STB (D4)         | c16              | 2            |

| RDY (D4)         | a16              | 4            |

| D4 (0)           | c20              | 6            |

| D4 (1)           | c19              | 8            |

| D4 (2)           | c18              | 10           |

| D4 (3)           | c17              | 12           |

| D4 (4)           | a17              | 14           |

| D4 (5)           | a18              | 16           |

| D4 (6)           | a19              | 18           |

| D4 (7)           | a20              | 20           |

| RDY (D6)         | a11              | 22           |

| STB (D6)         | c11              | 24           |

| D6 (0)           | c15              | 26           |

| D6 (1)           | c14              | 28           |

| D6 (2)           | c13              | 30           |

| D6 (3)           | c12              | 32           |

| D6 (4)           | a12              | 34           |

| D6 (5)           | a13              | 36           |

| D6 (6)           | a14              | 38           |

| D6 (7)           | a15              | 40           |

| GND              | a1, a2           | All Odd      |

#### SERIAL INTERFACE

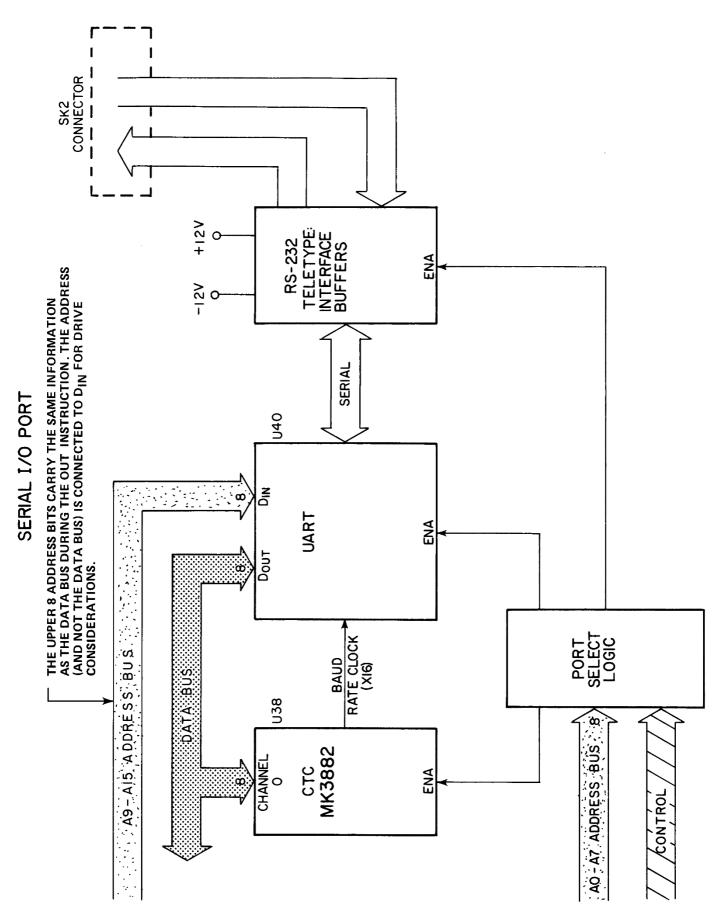

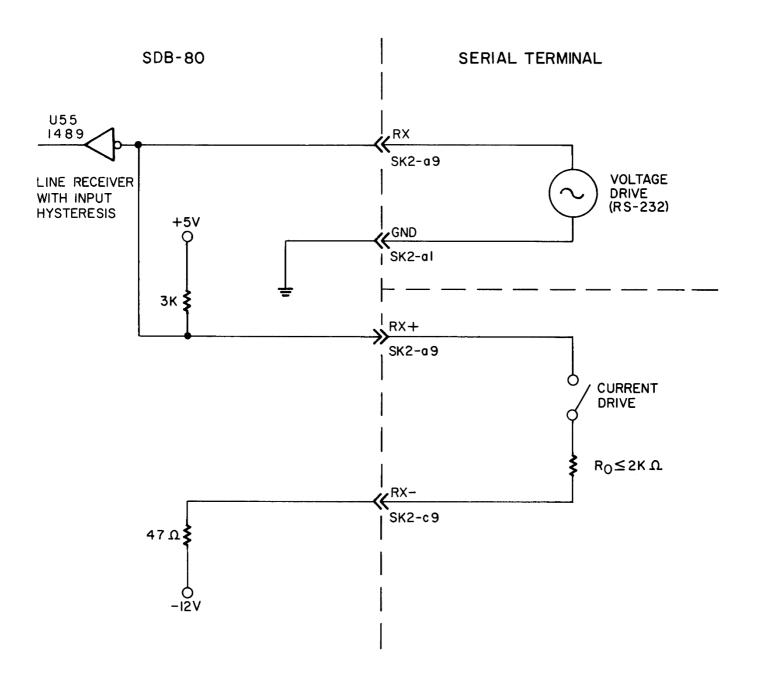

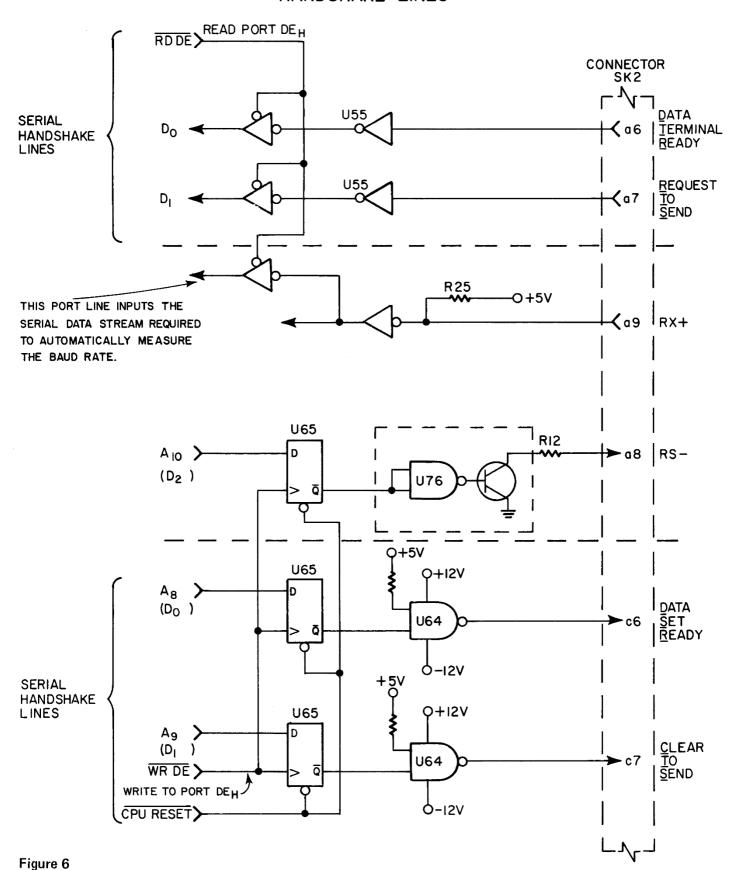

The Serial I/O Interface consists basically of a UART (AY-5-1013), a baud rate clock generator, and I/O buffering to connector SK2. Asynchronous data rates of from 110 to 9600 baud can be handled by the SDB-80. Logic is provided to allow the CPU to monitor the serial data input in order to permit automatic Baud rate calculation by software. Direct interface is provided to both teletype 20mA current loop and to standard RS-232 terminals (voltage drive). Four handshake lines are available for serial communication links. Figure 1 shows a block diagram of the serial port.

#### I. Baud Rate Clock

Channel O of the Counter/Timer circuit (U38) has been allocated as the baud rate clock generator. The CTC is driven by the master clock whose frequency (2.568 MHz) has been selected as a multiple of the baud rate frequencies. The following table lists the baud rates, baud rate clocks (16X the baud rate), CTC modulus, and percent error from the desired baud rate.

| BAUD<br>RATE                      | SYSTEM<br>CLOCK                  | CTC<br>MODULUS<br>(÷by)                  | ACTUAL BAUD<br>RATE CLOCK<br>(16X BAUD RATE) | DESIRED BAUD<br>RATE CLOCK             | % ERROR<br>FROM                                     |

|-----------------------------------|----------------------------------|------------------------------------------|----------------------------------------------|----------------------------------------|-----------------------------------------------------|

| 110<br>300<br>600<br>1200<br>2400 | ( )<br>( )<br>(2.458)<br>( MHz ) | 1392<br>512<br>256<br>1 <b>2</b> 8<br>64 | 1766<br>4801<br>9602<br>19203<br>38406       | 1760<br>4800<br>9600<br>19200<br>38400 | + 0.34%<br>+ 0.2 %<br>+ 0.2 %<br>+ 0.2 %<br>+ 0.2 % |

| 4800<br>9600                      | ( )                              | 32<br>16                                 | 76813<br>153625                              | 76800<br>153600                        | + 0.2 % + 0.2 %                                     |

Figure 1

The CTC modulus is under software control. Contained within the DDT-80 O.S. is a routine which calculates the baud rate of any peripheral interfacing to the serial port and adjusts the count modulus correspondingly.

Both transmit and receive clocks on the UART are tied together so operation is restricted to one common frequency.

#### II. UART

A full duplex UART is used to receive and transmit data at the serial port. Operation and UART options are under software control. Once the unit has been programmed no further changes are necessary unless there is a modification of the serial data format. Features of the UART include:

Full duplex operation

Start bit verification

Data word size variable from 5 to 8 bits

One or two stop bits may be selected

Odd, even, or no parity option

One word buffering on both transmit and on receive

Transmit and receive clock rates (baud clock rate) must be 16 times the desired baud rate. This clock has been brought to connector SK1. Through a jumper option (E63, 64, 65) an external clock may be supplied to the SDB-80. (See Counter/Timer Section).

A word needs to be said about the UART data interface to the CPU (Din, Dout). Refer to Figure 1 and to the main schematic. During I/O operations,

address information is carried directly by the lower 8-bit address lines. This is shown by AO - A7 going directly to the Port Select Logic block. The upper 8 bits are left free to carry information from the accumulator; the same information that is on the DATA BUS (which is connected to Dout). For loading and drive considerations the ADDRESS BUS (and not the DATA BUS) has been connected to the DATA IN port of the UART.

In addition to current loop terminals, the SDB-80 was designed to communicate with RS-232 terminals and therefore the serial interface looks like a receiving modem or computer port rather than a transmitting terminal port (such as a Silent 700). The effect of this is to exchange three pairs of signals.

## SERIAL PORT TO RS-232 CONNECTOR

## **SK2 CONNECTOR**

## **RS-232 CONNECTOR**

| PIN  | SIGNAL                                  | PIN |

|------|-----------------------------------------|-----|

| 2a 1 | Chassis GND                             | 1   |

| 2a 9 | Transmitted data (RS-232) from terminal | 2   |

| 2c 3 | Receive data (RS-232) at terminal       | 3   |

| 2a 7 | Request to send                         | 4   |

| 2c 7 | Clear to send                           | 5   |

| 2c 6 | Data set ready                          | 6   |

| 2a 1 | GND                                     | 7   |

| 2c10 | Carrier detect                          | 8   |

|      |                                         | 9   |

| 2c 9 | 20 mA receive                           | 10  |

|      |                                         | 11  |

|      |                                         | 12  |

|      |                                         | 13  |

|      |                                         | 14  |

|      |                                         | 15  |

| 2c10 | 20 mA send +                            | 16  |

| 2a10 | 20 mA send —                            | 17  |

| 2a 8 | Reader step —                           | 18  |

| 2c 8 | Reader step +                           | 19  |

| 2a 6 | Data terminal ready                     | 20  |

|      |                                         | 21  |

| 1a12 | RESET                                   | 22  |

|      |                                         | 23  |

| 2a 9 | 20 mA receive +                         | 24  |

|      |                                         | 25  |

Figure 2

For Example:

1) Transmitted Data (RS-232) from Terminal (a9) is an output signal at the terminal but it is shown as an input signal at the serial port.

Receive Data (RS-232) at Terminal (c3) is an input signal at the terminal but is shown as an output signal at the serial port.

2) Request To Send (a7) is an output signal at the terminal but is shown as an input signal at the serial port.

$\underline{C}$ lear  $\underline{T}$ o  $\underline{S}$ end (c7) is an input signal at the terminal but is shown as an output signal at the serial port.

3) Data Terminal Ready (a6) is an output signal at the terminal but is shown as an output signal at the serial port.

$\underline{D}$ ata  $\underline{S}$ et  $\underline{R}$ eady (c6) is an input signal at the terminal but it is shown as an output signal at the serial port.

To change the "sense" of this port i.e., to make it look like a transmitting terminal (as might be required in some OEM applications) the two signals in each pair above needs to be interchanged. DDT-80 will not necessary support such a change. However, such a change is normally made together with custom software.

## IV. I/O Buffering

The serial port has been designed to interface directly to both RS-232 and 20mA current loop terminals with no jumper changes. Also

brought out to the connector SK2 are four handshake control lines for modem use or general control functions. Each line making up the I/O port is catagorized below:

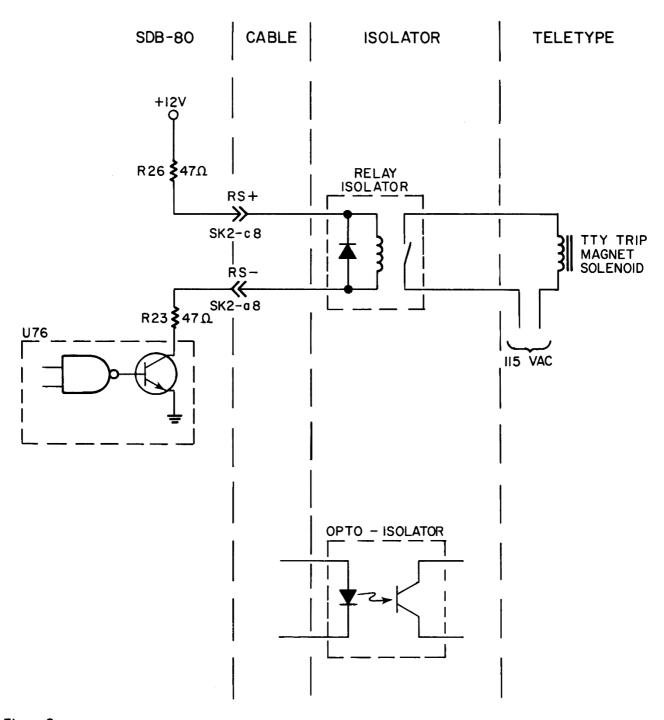

## READER STEP (RS+,RS-):

Two lines are allocated for the "Reader Step" or "Tape Reader Control" drive on a teletype machine. This is the mechanism that advances the punch tape. The interface schematic is shown in Figure 3. These lines are capable of supplying + 12V at up to 120mA for driving interface adapters which in turn control the 115VAC reader step directly. The 12V signal can drive an isolating relay or an optically isolated coupler/solid state AC switch. These adapters may be incorporated directly into a "lumpy" cable, although in many cases the isolator (which isolates 115VAC from the board) is located in the teletype machine. In this case, direct connection of RS+ and RS- to the teletype is the convenient way to interface. UNDER NO CIRCUMSTANCES SHOULD 115 VOLTS EVER BE APPLIED TO THE SDB-80 DIRECTLY!

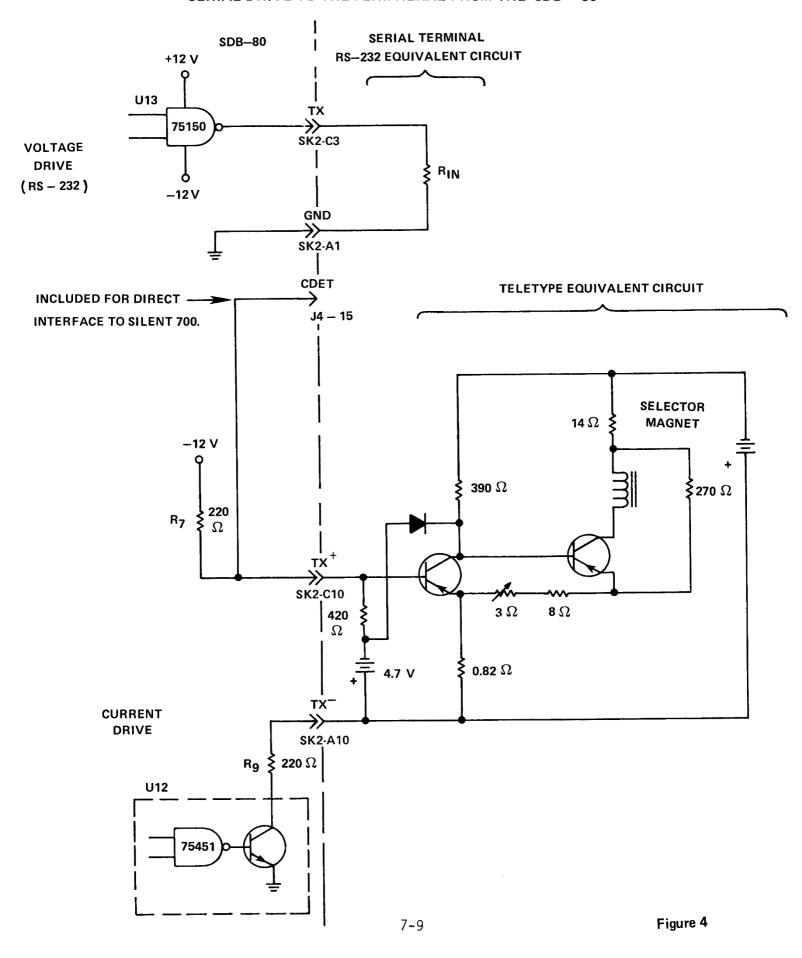

## TRANSMIT SERIAL DATA (TX, TX+, TX-):

The outgoing serial data communication link uses these three lines.

The interface schematic of both the voltage and current drive situation is shown in Figure 4.

## Voltage Drive- RS-232 (TX)

A 75150 RS-232 buffer drives this line directly. Voltage excursions are above and below ground and meet the RS-232 specification.

## READER STEP

Figure 3

## SERIAL DRIVE TO THE SDB-80 FROM THE PERIPHERAL

Figure 5

## 2) Current Drive-Teletype (TX<sup>+</sup>, TX<sup>-</sup>)