# TOSHIBA MOS MEMORY PRODUCTS

#### 2048 WORD x 8 BIT EPROM

### N CHANNEL SILICON STACKED GATE MOS.

## TMM323D TMM323D-1

## DESCRIPTION

The TMM323D is a 2048 word x 8 bit ultraviolet erasable and electrically programmable read only memory For read operation it requires a single 5-volt power supply only The maximum active power dissipation is 525mW while the maximum standby power dissipation is only 132mW, a 75% savings Programming can be executed by applying 25-volt and 5-volt at the Vpp and Vcc terminals respectively, and applying a TTL level signal at the other input terminals. Programming the one bit location requires

## **FEATURES**

- Single.5-volt power supply

- Access time TMM323D , 450ns (MAX ) TMM323D-1, 350ns (MAX )

Current 100 mA (active)

- 25mA (standby)

- Three state output

- Particular bit location programming

## **PIN CONNECTION**

## PIN NAMES

| A7 6         | 1        | 24 VCC                                      | $A_0 - A_{10}$ | Addresses              |

|--------------|----------|---------------------------------------------|----------------|------------------------|

|              | 34       | 225 A9<br>215 VPP                           | $0_0 - 0_7$    | Outputs<br>Chip Select |

| A3 0<br>A2 0 | 5        | 209 ČŠ<br>199 A <sub>10</sub><br>189 PD/PGM | PD/PGM         | Power down/            |

|              | 8        | 17P 07<br>16P 04                            |                | Program                |

| 80           | 10       | 15 05                                       | Vcc, Vpp       | Power Supply           |

|              | 11<br>12 | 14 04<br>13 03                              | GND            | Ground                 |

## MODE SELECTION

c

| PINS               | PD/PGM<br>(18)     | CS<br>(20) | Vpp<br>(21) | Vcc<br>(24) | Outputs<br>(9-11, 13-17) |

|--------------------|--------------------|------------|-------------|-------------|--------------------------|

| Read               | VIL                | VIL        | 5V          | 5V          | D out                    |

| Deselect           | •                  | ViH        | 5V          | 5V          | High Z                   |

| Power Down         | Vін                | *          | 5V          | 5V          | High Z                   |

| Program            | лл <sup>∨</sup> ін | ∨ін        | 25V         | 5V          | Din                      |

| Program<br>Verify  | VIL                | VIL        | 25V         | 5V          | D out                    |

| Program<br>Inhibit | VIL                | ∨ін        | 25V         | 5V          | High Z                   |

\* VIL or VIH

only a single pulse, and it is possible to program sequentially, individually or at random. Under the condition Vpp = 25V, read operation is permitted in the program verify mode, and also programming is inhibited by selecting the program inhibit mode.

The TMM323D is fabricated with the N-channel silicon double layer gate MOS technology and is packaged in a standard 24-pin dual-in-line cerdip package

- Programs with one 50ms pulse

- Total programming time 100 second

- Inputs and outputs TTL compatible during read and program

- Pin to pin compatible to 2716 type EPROM

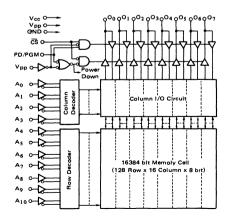

## **BLOCK DIAGRAM**

## MAXIMUM RATINGS

| ITEM                                       | SYMBOL  | RATING            | UNIT     |

|--------------------------------------------|---------|-------------------|----------|

| Vcc Supply Voltage with respect to Ground  | Vcc     | -0.3 <b>~</b> + 7 | V        |

| VPP Supply Voltage with respect to Ground  | Vpp     | 0.3 ~ + 26.5      | V        |

| All Input Voltages with respect to Ground  | Vin     | -0.3~+7           | V        |

| All Output Voltages with respect to Ground | Vout    | 0 3 ~ + 7         | V        |

| Power Dissipation                          | PD      | 15                | W        |

| Soldering Temperature Times                | TSOLDER | 260.10            | °C · sec |

| Storage Temperature                        | TSTG    | -65 ~ + 125       | °C       |

| Operating Temperature                      | TOPR    | 0~70              | °C       |

1. Col

## READ OPERATION

## D.C. and A.C. OPERATING CONDITIONS

| PARAMETER    | SYMBOL                 |           | MIN.                | TYP | MAX                   | UNIT |

|--------------|------------------------|-----------|---------------------|-----|-----------------------|------|

| Bewer events | 1 1 2                  | TMM323D   | 4 75                | 5   | 5 25                  | v    |

| Power supply | V <sub>CC</sub> (1, 2) | TMM323D-1 | 45                  | 5   | 55                    | v    |

| Power supply | V <sub>PP</sub> (2)    |           | V <sub>CC</sub> -06 | 5   | V <sub>CC</sub> + 0 6 | V    |

## D.C. and OPERATING CHARACTERISTICS

Ta = 0 ~ 70°C

| PARAMETER              | SYMBOL | MIN. | TYP. (3) | MAX.    | UNIT | CONDITIONS                                                                                                     |

|------------------------|--------|------|----------|---------|------|----------------------------------------------------------------------------------------------------------------|

| Input Load Current     | ILI.   |      |          | ±10     | μA   | VIN = 5.25V                                                                                                    |

| Output Leakage Current | ILO.   |      |          | ±10     | μA   | Vour = 5.25V/0.45V                                                                                             |

| VPP Current (Read)     | IPP1   |      |          | 5       | mA   | Vpp = 5 85V                                                                                                    |

| Vcc Current (Standby)  | ICC1   |      | 10       | 25      | mA   | PD/PGM = VIH, CS = VIL                                                                                         |

| Vcc Current (Active)   | ICC2   |      | 57       | 100     | mA   | PD/PGM = CS = VIL                                                                                              |

| Input Low Voltage      | VIL    | -01  |          | 0.8     | V    | the second s |

| Input High Voltage     | Viн    | 2.0  |          | Vcc + 1 | V    |                                                                                                                |

| Output Low Voltage     | Vol    |      |          | 0.45    | V    | IOL = 2.1mA                                                                                                    |

| Output High Voltage    | Voн    | 2.4  |          |         | V    | <sup>I</sup> он = -400µА                                                                                       |

## A.C. CHARACTERISTICS

$Ta = 0 \sim 70^{\circ}C$ ,  $V_{PP} = V_{CC} \pm 0.6V$

| PARAMETER                     | SYMBOL | TMM323D |     | TMM323D-1 |     | UNIT | CONDITIONS                        |  |

|-------------------------------|--------|---------|-----|-----------|-----|------|-----------------------------------|--|

| FARAMETER                     | STWBOL | MIN     | MAX | MIN.      | MAX |      | CONDITIONS                        |  |

| Address to Output Delay       | tACC1  |         | 450 |           | 350 | ns   | $PD/PGM = \overline{CS} = V_{IL}$ |  |

| PD/PGM to Output Delay        | tACC2  |         | 450 |           | 350 | ns   | $\overline{CS} = V_{IL}$          |  |

| Chip Select to Output Delay   | tco    |         | 120 |           | 120 | ns   | PD/PGM = VIL                      |  |

| PD/PGM to Output Float        | tpF    | 0       | 100 | 0         | 100 | ns   | $\overline{CS} = V_{IL}$          |  |

| Chip Deselect to Output Float | tDF    | 0       | 100 | 0         | 100 | ns   | PD/PGM = VIL                      |  |

| Address to Output Hold        | tон    | 0       |     | 0         |     | ns   | $PD/PGM = \overline{CS} = V_{IL}$ |  |

## • A.C. Test Conditions

· Output Load : ITTL + 100pF

· Input Rise and Fall Times (10%~90%) : ≦ 20ns

Input Pulse Levels : V<sub>IL</sub> = 0.8V, V<sub>IH</sub> = 2.2V

· Timing Measurement Reference Level Inputs 1V & 2V, Outputs 0.8V & 2V

(Note 4) CAPACITANCE

## $Ta = 25^{\circ}C, f = 1MHz$

| PARAMETER          | SYMBOL |     | LIMITS |      | UNIT | CONDITIONS |  |

|--------------------|--------|-----|--------|------|------|------------|--|

| TANAMETEN          | SYMBOL | Min | Тур    | Max. | UNTI | CONDITIONS |  |

| Input Capacitance  | CIN    |     | 4      | · 6  | pF   | VIN = 0V   |  |

| Output Capacitance | Соит   |     | 8      | 12   | pF   | Vout = 0V  |  |

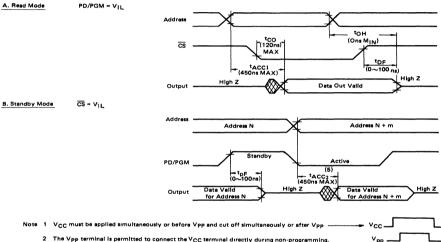

## TIMING WAVEFORMS (READ)

- 3 Typical values are at Ta = 25°C and nominal supply voltages

- 4. This parameter is periodically sampled and is not 100% tested.

- 5 The tACC2 is a output data delay time (i e. access time) from address or PD/PGM whichever changes late.

### PROGRAM OPERATION

$Ta = 25^{\circ}C \pm 5^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$ ,  $V_{PP} = 25V \pm 1V$  (Note 1, 2, 3)

## D.C. PROGRAMMING CHARACTERISTICS

| PARAMETER                                      | SYMBOL | MIN  | TYP. | MAX.    | UNIT | CONDITIONS        |

|------------------------------------------------|--------|------|------|---------|------|-------------------|

| Input Current                                  | ILI    |      |      | ±10     | μA   | VIN = 5.25V/0 45V |

| VPP Supply Current                             | IPP1   |      |      | 5       | mA   | PD/PGM = VIL      |

| VPP Supply Current<br>During Programming Pulse | IPP2   |      |      | 30      | mA   | PD/PGM = VIH      |

| Vcc Supply Current                             | Icc    |      |      | 100     | mA   | IOUT = 0 mA       |

| Input Low Level                                | VIL    | -0 1 |      | 08      | V    |                   |

| Input High Level                               | Ин     | 20   |      | Vcc + 1 | V    |                   |

## A.C. PROGRAMMING CHARACTERISTICS

| PARAMETER                          | SYMBOL      | MIN. | TYP. | MAX. | UNIT | CONDITIONS   |

|------------------------------------|-------------|------|------|------|------|--------------|

| Address Setup Time                 | tAS         | 2    |      |      | μs   |              |

| CS Setup Time                      | tcss        | 2    |      |      | μs   |              |

| Data Setup Time                    | tDS         | 2    |      |      | μs   |              |

| Address Hold Time                  | tAH         | 2    |      |      | μs   |              |

| CS Hold Time                       | tCSH        | 2    |      |      | μs   |              |

| Data Hold Time                     | tDH         | 2    |      |      | μs   |              |

| Chip Deselect to Output FloatDelay | t D F       | 0    |      | 120  | ns   | PD/PGM = VIL |

| Chip Select to Output Delay        | tco         |      |      | 120  | ns   | PD/PGM = VIL |

| Program Pulse Width                | tPW         | 45   | 50   | 55   | ms   |              |

| Program Pulse Rise Time            | <b>tPRT</b> | 5    |      |      | ns   |              |

| Program Pulse Fall Time            | tPFT        | 5    |      |      | ns   |              |

## • A.C. Test Conditions

Vpp = 25V ± 1V, VCC = 5V ± 5%

- Input Rise and Fall Times (10% ~ 90%) . ≦ 20ns

- · Input Pulse Levels : VIL = 0.8V, VIH = 2.2V

- · Timing Measurement Reference Level . Input 1V & 2V, Output 0.8V & 2V

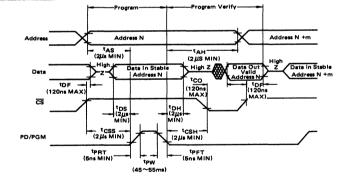

## TIMING WAVEFORMS (PROGRAM)

- Note: 1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and cut off simultaneously or after V<sub>PP</sub> \_\_\_\_\_\_ V<sub>CC</sub>\_\_\_\_\_ V<sub>cc</sub>\_\_\_\_\_

- Sometimes removing the device from socket and setting the device in socket under the condition Vpp = 25V±1V may destroy its device, so it should be noted during programming.

- VPP supply voltage is permitted up to 26V programming, so the voltage over 26V should not be applied to VPP. Particularly when switching pulse voltage is applied to Vpp, also the over-shoot voltage of its pulse should not be exceeded 26-volt.

## ERASURE CHARACTERISTICS

The TMM323D's memory cell data can be erased by applying light with wavelengths shorter than 4000 the device is exposed at a distance of 1-cm from the Å. (IÅ = 10<sup>-8</sup> cm)

Sunlight and the fluorescent lamps may include 60 minutes. 3000 ~ 4000 Å wavelength components

extended periods of time, an opaque seal (Toshiba EPROM Protecting Seal AC 901 etc.) will be required to protect the TMM323D Generally, ultraviolet light  $[\mu w/cm^2] \times (20 \times 60)$  [sec]  $\approx 15$  [w sec/cm<sup>2</sup>]) with a wavelength of 2537 Å is recommended for TMM323D-erasing, and in this case the integrated dose (ultraviolet light intensity [w/cm<sup>2</sup>] x time [sec]) should be over 15 [w sec/cm<sup>2</sup>]

When Toshiba sterilizing lamp GL-15 is used and lamp surface, erasure should be completed in about

And using a lamp whose ultraviolet light intensity Therefore when used under such lighting for is a 12000  $[\mu w/cm^2]$  will reduce the exposure time to about 20 minutes.

(In this case the integrated dose should be 12000

## OPERATING INFORMATION

TMM323D-operation-modes are classified into six types, as shown in the following table Each mode can be selected by TTL level signals only. The VCC and VPP power supplies required are only 5-volt for read operation, and the VPP power supply required is 25-volt during program operation only.

|                   | PINS            | PD/PGM | CS   | VPP  | Vcc  | Outputs       |

|-------------------|-----------------|--------|------|------|------|---------------|

| MODE              |                 | (18)   | (20) | (21) | (24) | (9-11, 13-17) |

|                   | Read            | VIL    | VIL  | 5V   | 5V   | D out         |

| Read Operation    | Deselect        | *      | Viн  | 5V   | 5V   | High Z        |

|                   | Power Down      | Vih    | *    | 5V   | 5V   | High Z        |

| Program Operation | Program         |        | ∨ін  | 25∨  | 5V   | Din           |

|                   | Program Verify  | VIL    | VIL  | 25V  | 5V   | D out         |

|                   | Program Inhibit | VIL    | Viн  | 25V  | 5V   | High Z        |

#### Read Mode

#### \* VII or VIH Deselect Mode

Assuming that PD/PGM =  $V_{IL}$  and  $\overline{CS}$  =  $V_{IL}$ , the output data is available within tACC1 (MAX.) after stabilizing of the address.

And assuming that PD/PGM =  $V_{IH}$  or  $\overline{CS} = V_{IH}$ , the outputs will become high impedance in state

When all addresses are in the fixed state and  $\overline{CS}$  = VIL, the output data is available within tACC2 (MAX.) after the PD/PGM input is changes to VII from the VIH level (Outputs change to data available state from a high impedance state.)

When all addresses are in the fixed state and PD/ PGM =  $V_{1L}$ , the output data is available within tco (MAX.) after the  $\overline{CS}$  input is changed to V<sub>II</sub> from the VIH level. (Outputs change to data available state from a high impedance state )

Assuming that  $\overline{CS} = V_{IH}$ , the outputs will be in a high impedance state So two or more TMM323Ds may be tied together on the same data bus. And the CS input of the selected chip must be at the Vii level, and that of the other chip must be at the VIH level

#### Power Down Mode

Assuming that PD/PGM = VIH, the power dissipation will be reduced to one-fourth of normal active power. (i.e. 525mW → 132mW)

Then all outputs will become high impedance in state independent of the  $\overline{CS}$  input level.

#### Program Mode

Initially when received by customers all bits of the TMM323D are in the "1" state which is the erased state

Therefore programming is carried out by electrically writing in the "0" state at the desired bit locations.

Programming can be completed by applying the TTL level pulse signal with a pulse width of from 45 to 55 ms to PD/PGM input under the condition where  $V_{PP} = 25V$  and  $\overline{CS} = V_{IH}$ .

Programming the TMM323D is permitted in any sequence and also at any particular bit location.

But the PD/PGM pulse width applied at one bit location should be over 45ms up to 55ms, and rewriting into the written location is not permitted.

When programming is carried out by applying a DC voltage (VIH level) instead of a pulse to the PD/ PGM input, erroneous writing may occur sometimes,

32 4 MAX.

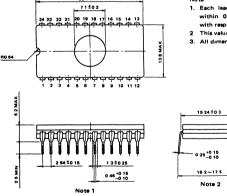

#### **ITLINE DRAWING**

so a pulse whose recommended width is 50ms shou be used in programming.

Programming the same data to two or more TMI 323Ds simultaneously can be accomplished by cor necting the respective pins together.

#### Program Verify Mode

In this mode the VPP power supply is 25V.

But assuming that PD/PGM = VII and  $\overline{CS}$  = VII it can be possible to read written data.

For normal read operation, the VPP power supply voltage required is 5V.

#### **Program Inhibit Mode**

Assuming that PD/PGM = VII and  $\overline{CS}$  = VIH under VPP = 25V, it is able to inhibit the programming.

According to the above, programming into two o more TMM323Ds mounted on a board will be pos sible

Programming into a desired chip tied on a commor bus line independently is possible by connecting all respective inputs except PD/PGM together and apply ing a pulse to the PD/PGM input of a desired chip and applying DC voltage at the VII level to the PD/PGN inputs of the other chip.

Note

- 1 Each lead putch is 2.54 mm. All leads are located within 0.25 mm of their true longitudinal position with respect to No. 1 and No. 24 leads

- 2 This value is measured at the end of leads.

- 3. All dimensions are in millimeters.