- High Density 300-mil (7.62 mm) 18-Pin Package

- Fully Static Operation (No Clocks, No Refresh, No Timing Strobe)

- 4 Performance Ranges:

|                         | ACCESS READ | OR WRI |

|-------------------------|-------------|--------|

|                         | TIME        | CYCLE  |

|                         | (MAX)       | (MIN)  |

| TMS4044-12, TMS40L44-12 | 120 ns      | 120 ns |

| TMS4044-20, TMS40L44-20 | 200 ns      | 200 ns |

| TMS4044-25, TMS40L44-25 | 250 ns      | 250 ns |

| TMS4044-45, TMS40L44-45 | 450 ns      | 450 ns |

- 400-mV Guaranteed DC Noise Immunity with Standard TTL Loads – No Pull-Up Resistors Required

- Common I/O Capability

- 3-State Outputs and Chip Select Control for OR-Tie Capability

- Fan-Out to 2 Series 74, 1 Series 74S, or 8 Series 74LS TTL Loads

- Low Power Dissipation

|          | MAX         | MAX       |

|----------|-------------|-----------|

|          | (OPERATING) | (STANDBY) |

| TMS4044  | 303 mW      | 84 mW     |

| TMS40144 | 220 mW      | 60 mW     |

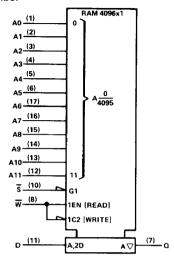

| A0 [           | ſ٦ | U <sub>18</sub> | □vcc |

|----------------|----|-----------------|------|

| A1 [           | 2  | 17              | A6   |

| A2 [           | 3  | 16              | _ A7 |

| A3 [           | 4  | 15              | 8A   |

| A4 🗌           | 5  | 14              | A9   |

| A5 [           | 6  | 13              | A10  |

| a [            | 7  | 12              | A11  |

| $\overline{w}$ | 8  | 11              | ] D  |

| vss [          | 9  | 10              | ] s  |

| PIN NO   | MENCLATURE   |

|----------|--------------|

| A0 - A11 | Addresses    |

| D        | Data In      |

| Q        | Data Out     |

| Š        | Chip Select  |

| Vcc      | +5-V Supply  |

| VSS      | Ground       |

| ₩        | Write Enable |

#### description

This series of static random-access memories is organized as 4096 words of 1 bit. Static design results in reduced overhead costs by elimination of refresh-clocking circuitry and by simplification of timing requirements. Because this series is fully static, chip select may be tied low to further simplify system timing. Output data is always available during a read cycle.

All inputs and outputs are fully compatible with Series 74, 74S or 74LS TTL. No pull-up resistors are required. This 4K Static RAM series is manufactured using Tl's reliable N-channel silicon-gate technology to optimize the cost/performance relationship. All versions are characterized to retain data at  $V_{CC} = 2.4 \text{ V}$  to reduce power dissipation.

The TMS4044/40L44 series is offered in the 18-pin dual-in-line plastic (NL suffix) packages designed for insertion in mounting-hole rows on 300-mil (7.62 mm) centers. The series is guaranteed for operation from 0°C to 70°C.

Static RAM and Memory Support Devices

#### addresses (A0-A11)

The twelve address inputs select one of the 4096 storage locations in the RAM. The address inputs must be stable for the duration of a write cycle. The address inputs can be driven directly from standard Series 54/74 TTL with no external pull-up resistors.

#### chip select (S)

The chip-select terminal, which can be driven directly from standard TTL circuits, affects the data-in and data-out terminals. When chip select is at a logic low level, both terminals are enabled. When chip select is high, data-in is inhibited and data-out is in the floating or high-impedance state.

#### write enable (W)

The read or write mode is selected through the write enable terminal. A logic high selects the read mode; a logic low selects the write mode.  $\overline{W}$  must be high when changing addresses to prevent erroneously writing data into a memory location. The  $\overline{W}$  input can be driven directly from standard TTL circuits.

#### data-in (D)

Data can be written into a selected device when the write enable input is low. The data-in terminal can be driven directly from standard TTL circuits.

#### data-out (Q)

The three-state output buffer provides direct TTL compatibility with a fan-out of two Series 74 TTL gates, one Series 74S TTL gate, or eight Series 74LS TTL gates. The output is in the high-impedance state when chip select  $(\overline{S})$  is high or whenever a write operation is being performed, facilitating device operation in common I/O systems. Data-out is the same polarity as data-in.

#### standby operation

The standby mode, which will retain data while reducing power consumption, is attained by reducing the  $V_{CC}$  supply from 5 volts to 2.4 volts. When reducing supply voltage during the standby mode,  $\overline{S}$  and  $\overline{W}$  must be high to retain data. The  $V_{CC}$  transition rate should not exceed 26 mV/ms. During standby operation, data can not be read or written into the memory. When resuming normal operation, five cycle times must be allowed after normal supplies are returned for the memory to resume steady state operation conditions.

#### logic symbol†

#### **FUNCTION TABLE**

|     |     | 7 0110 11011 17 | IDLL            |

|-----|-----|-----------------|-----------------|

| INP | UTS | OUTPUT          |                 |

| Ī   | W   | a               | MODE            |

| Н   | X   | HI-Z            | DEVICE DISABLED |

| L   | L   | HI-Z            | WRITE           |

| L   | Н   | DATA OUT        | READ            |

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with IEEE Std 91/ANSI Y32.14 and recent decisions by IEEE and IEC. See explanation on page 10-1.

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted) †

| Supply voltage, V <sub>CC</sub> (see Note 1) | 7 V |

|----------------------------------------------|-----|

| Input voltage (any input) (see Note 1)       | 7 V |

| Continuous power dissipation                 | W   |

| Operating free-air temperature range         | °C  |

| Storage temperature range                    | °C  |

NOTE 1: Voltage values are with respect to the ground terminal.

#### recommended operating conditions

|                                                      | PARAMETER        |           | MIN        | NOM MAX | UNIT        |

|------------------------------------------------------|------------------|-----------|------------|---------|-------------|

|                                                      | TMS4044-12       | Operating | 4.5        | 5 5.5   |             |

| Supply voltage, VCC                                  | TMS40L44-12      | Standby   | 2.4        | 5.5     |             |

|                                                      | TMS4044-20       | Operating | 4.5        | 5.5     |             |

|                                                      | TMS40L44-20      | Standby   | 2.4 5.     |         | ٦           |

|                                                      | TMS4044-25       | 0         | 4.5 5.5    |         | -<br>-<br>- |

|                                                      | TMS40L44-25      | Operating |            |         |             |

|                                                      | TMS40L44-45      | Standby   | 2.4        | 5.5     |             |

|                                                      | TMS4044-45       | Operating | 4.5        | 5.5     |             |

| Supply voltage, VSS                                  |                  |           |            | 0       | V           |

| High-level input voltage, VIH                        |                  |           | 2          | 5.5     | V           |

| ow-level input voltage, V <sub>IL</sub> (see Note 2) |                  |           | <b>– 1</b> | 0.8     | ٧           |

| Operating free-air temperature                       | , T <sub>A</sub> |           | 0          | 70      | °C          |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

<sup>&</sup>lt;sup>†</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## electrical characteristics over recommended operating free-air temperature ranges (unless otherwise noted)

|                 | PARAMETER                           | TEST                               | CONDITIONS                  |                         | MIN          | TYP | MAX   | UNIT     |

|-----------------|-------------------------------------|------------------------------------|-----------------------------|-------------------------|--------------|-----|-------|----------|

| Voн             | High-level output voltage           | i <sub>OH</sub> = -1.0 mA          | V <sub>CC</sub> = 4.5 V     |                         | 2.4          |     | IIIAA | V        |

| $v_{OL}$        | Low-level output voltage            | I <sub>OL</sub> = 3.2 mA           | VCC = 4.5 V                 |                         |              |     | 0.4   | l 🔻      |

| l <sub>l</sub>  | Input current                       | V <sub>I</sub> = 0 V to 5.5 V      |                             |                         | <del> </del> |     | 10    |          |

| loz             | Off-state output current            | Sat 2 V or<br>Wat 0.8 V            | V <sub>O</sub> = 0 V to 5.1 | 5 V                     |              |     | ± 10  | μA<br>μA |

|                 |                                     |                                    | TMS40L44                    | V <sub>CC</sub> =MAX    |              | 25  | 40    |          |

|                 |                                     |                                    | 1101540144                  | V <sub>CC</sub> = 2.4 V |              | 15  | 25    |          |

| <sup>I</sup> CC | Supply current from V <sub>CC</sub> | IO=0 mA                            | TMS4044-12                  | V <sub>CC</sub> =MAX    |              | 50  | 55    |          |

| 100             | apply content from ACC              | T <sub>A</sub> = 0 °C (worst case) | TMS4044-20<br>TMS4044-25    | V <sub>CC</sub> =2.4 V  |              | 25  | 35    | mΑ       |

|                 |                                     |                                    | TMS4044-45                  | V <sub>CC</sub> ≃MAX    |              | 50  | 55    | I<br>I   |

| Ci              | Input capacitance                   | V <sub>I</sub> = 0 V,<br>f = 1 MHz |                             |                         |              |     | 8     | pF       |

| Co              | Output capacitance                  | V <sub>O</sub> = 0 V,<br>f = 1 MHz |                             |                         |              | •   | 8     | рF       |

$<sup>^{\</sup>dagger}All$  typical values are at  $V_{CC}\!=\!5$  V,  $T_{A}\!=\!25\,^{o}C.$

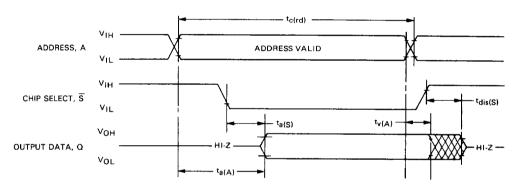

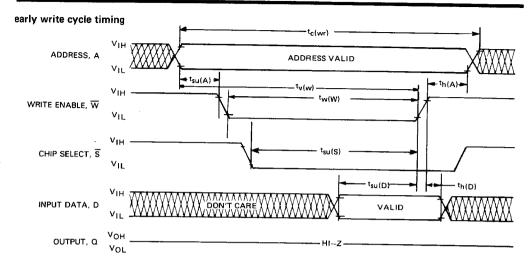

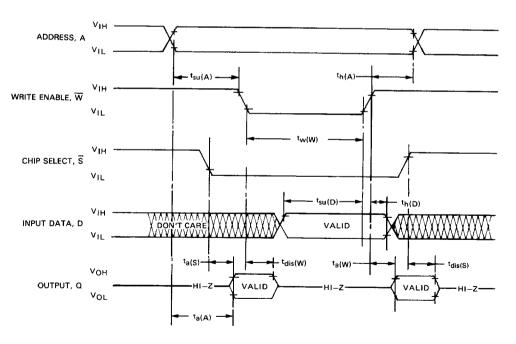

# timing requirements over recommended supply voltage range, $T_A = 0$ °C to 70 °C, 1 Series 74 TTL load, $C_L = 100 \ pF$

|                    | PARAMETER                     | 1     | 044-12<br>)L44-12 | 1   | 044-20<br> L44-20 |     | 044-25<br>L44-25 |     | )44-45<br>L44-45 | UNIT |

|--------------------|-------------------------------|-------|-------------------|-----|-------------------|-----|------------------|-----|------------------|------|

|                    |                               | MIN   | MAX               | MIN | MAX               | MIN | MAX              | MIN | MAX              |      |

| <sup>t</sup> c(rd) | Read cycle time               | 120   |                   | 200 |                   | 250 |                  | 450 |                  | ns   |

| t <sub>c(wr)</sub> | Write cycle time              | 120   |                   | 200 |                   | 250 |                  | 450 |                  | ns   |

| tv(W)              | Address valid to end of write | 110   |                   | 180 |                   | 230 |                  | 230 |                  | ns   |

| tw(W)              | Write pulse width             | 60    |                   | 60  | -                 | 75  |                  | 200 | _                | ns   |

| t <sub>su(A)</sub> | Address set up time           | 0     |                   | -   |                   | 0   |                  | 0   |                  | ns   |

| t <sub>su(S)</sub> | Chip select set up time       | 60    |                   | 60  |                   | 75  |                  | 200 |                  |      |

| t <sub>su(D)</sub> | Data set up time              | 50    |                   | 60  |                   | 75  |                  | 200 |                  | ns   |

| th(D)              | Data hold time                | 0     |                   | 0   |                   | 0   |                  | 200 |                  | ns   |

| th(A)              | Address hold time             | - 1 0 |                   | 0   |                   | 0   |                  | 0   |                  | ns   |

### switching characteristics over recommended voltage range, $T_A = 0$ °C to 70 °C, 1 Series 74 TTL load, $C_L = 100$ pF

| PARAMETER            |                                            |     |     |     |     |     |     | TMS4044-45   |     | UNIT |

|----------------------|--------------------------------------------|-----|-----|-----|-----|-----|-----|--------------|-----|------|

|                      |                                            | MIN | MAX | MIN | MAX | MIN | MAX | MiN          | MAX |      |

| ta(A)                | Access time from address                   |     | 120 | ]   | 200 |     | 250 |              | 450 | ns   |

| ta(S)                | Access time from chip select low           |     | 70  |     | 70  |     | 100 |              | 100 | ns   |

| ta(W)                | Access time from write enable high         |     | 70  | i   | 70  |     | 100 | 1            | 100 | ns   |

| t <sub>v(A)</sub>    | Output data valid after address change     | 20  |     | 20  |     | 20  |     | 20           |     | ns   |

| t <sub>dis</sub> (S) | Output disable time after chip select high |     | 50  |     | 60  |     | 60  |              | 80  | ns   |

| t <sub>dis</sub> (W) | Output disable time after write enable low |     | 50  |     | 60  | ·   | 60  | <del> </del> | 80  | ns   |

#### read cycle timing (see Note 3)

34

All timing reference points are 0.8 V and 2.0 V on inputs and 0.6 V and 2.2 V on outputs (90% points). Input rise and fall times = 10 ns. NOTE 3. Write enable is high for a read cycle.

8

#### read-write cycle timing

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.