# SYNERTEK 1981-1982 DATA CATALOG

# **Table of Contents**

# SYNERTEK 1981-1982 DATA CATALOG

Random Access Memories

Read Only Memories **Z**

Microprocessors

Logic Capabilities 4

SYSTEMS

L OGIC PABIL ITIES

Systems

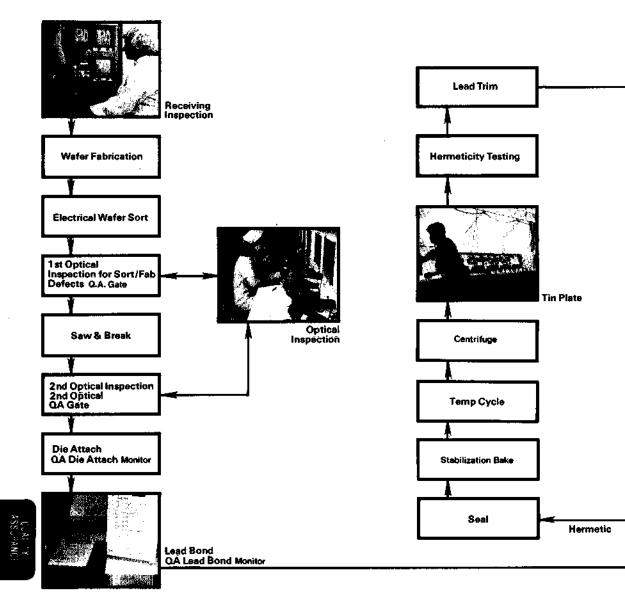

Quality Assurance

P.O. BOX 552 - MS/34 • SANTA CLARA, CA 95052 TEL.(408) 988-5600 • TWX: 910-338-0(35

General Information

RAMs

ROMs

Index

# Contents

#### CHAPTER 1 Random Access Memory

| RAM Selector Guide                | 1-2  |

|-----------------------------------|------|

| SY2101, 256 x 4-Bit Static RAM    | 1-3  |

| SY2111, 256 x 4-Bit Static RAM    | 1-7  |

| SY2112, 256 x 4-Bit Static RAM    | 1-11 |

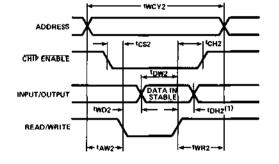

| SY2114, 1024 x 4-Bit Static RAM   | 1-17 |

| SY2114LV, 1024 x 4-Bit Static RAM | 1-21 |

| SY2128, 2048 x 8-Bit Static RAM   | 1-25 |

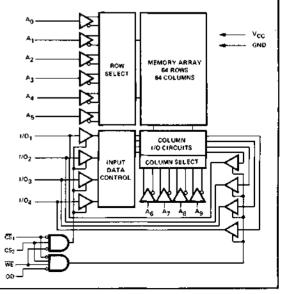

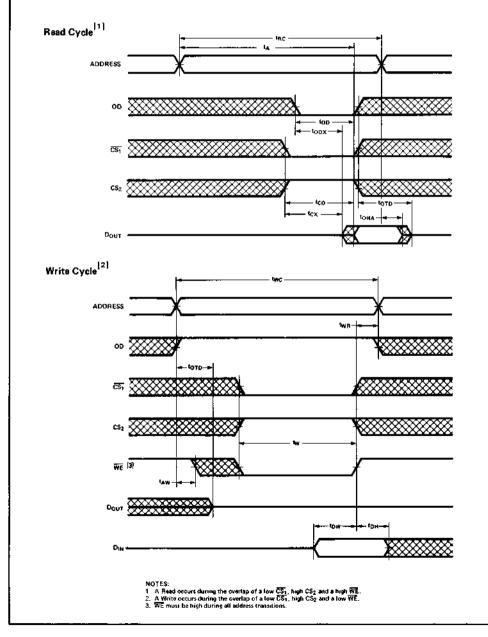

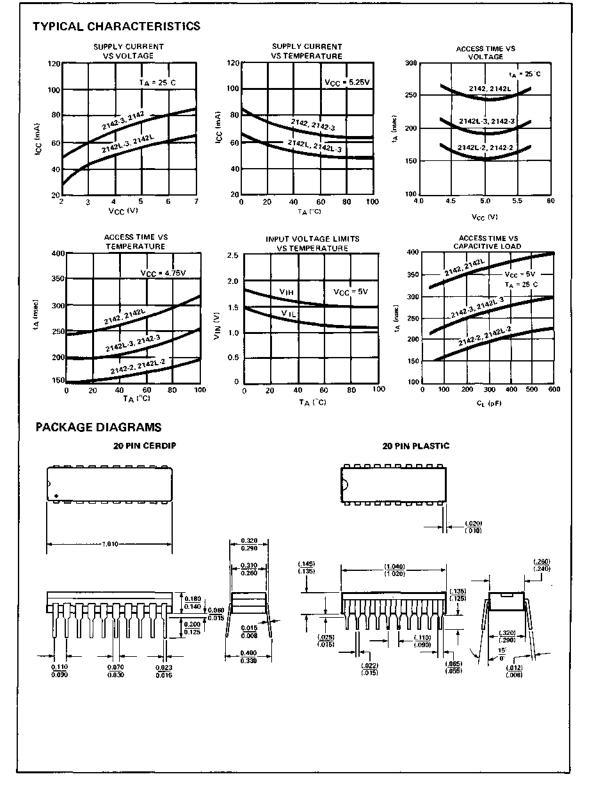

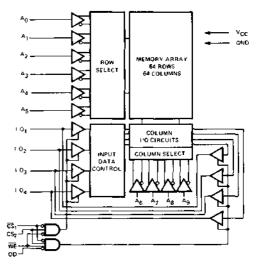

| SY2142, 1024 x 4-Bit Static RAM   | 1-26 |

| SY2142LV, 1024 x 4-Bit Static RAM | 1-30 |

| SY2147, 4096 x 1-Bit Static RAM   | 1-34 |

| SY2147H, 4096 x 1-Bit Static RAM  |      |

| SYM2147, 4096 x 1-Bit Static RAM  | 1-39 |

| SY2148H, 1024 x 4-Bit Static RAM  | 1-40 |

| SYM2148. 1024 x 4-Bit Static RAM  | 1-44 |

| SY2149H, 1024 x 4-Bit Static RAM  |      |

| SYM2149H, 1024 x 4-Bit Static RAM |      |

|                                   |      |

### CHAPTER 2

# **Read Only Memory**

| ROM Selector Guide              |     |

|---------------------------------|-----|

| SY2316A/B, 2048 x 8-Bit ROM     |     |

| SY2316B-2, 2048 x 8-Bit ROM     | 2-7 |

| SY2316B-3, 2048 x 8-Bit ROM 2   | -11 |

| SY2332/3, 4096 x 8-Bit ROM 2    | -   |

| SY2332/3-3, 4096 x 8-Bit ROM 2- |     |

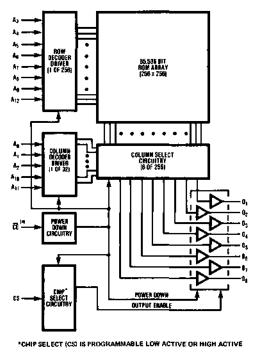

| SY2364/A, 8192 x 8-Bit ROM      |     |

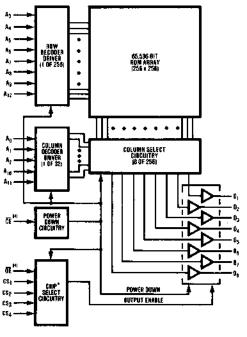

| SY2365/A, 8192 x 8-Bit ROM 2    |     |

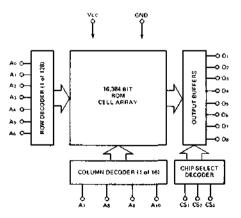

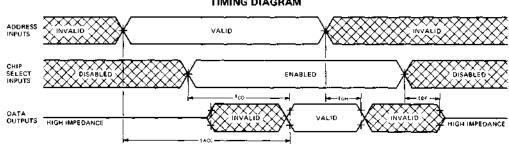

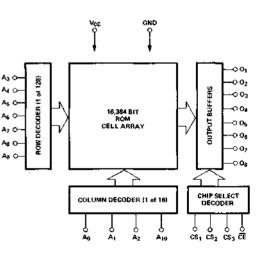

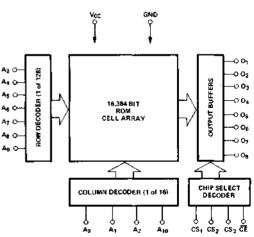

| SY23128, 16,384 x 8-Bit ROM 2-  |     |

| SY3308, 1024 x 8-Bit ROM 2-     |     |

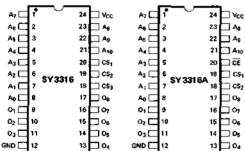

| SY3316/A, 2048 x 8-Bit ROM 2-   |     |

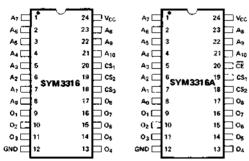

| SYM3316/A, 2048 x 8-Bit ROM 2-  | -40 |

### CHAPTER 3

#### Microprocessors Microcomputers

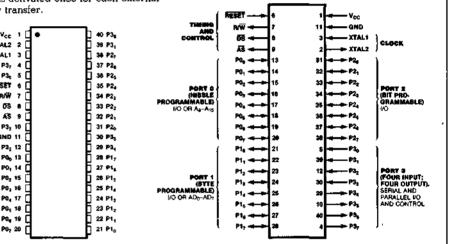

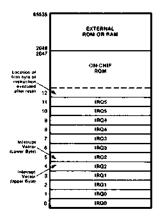

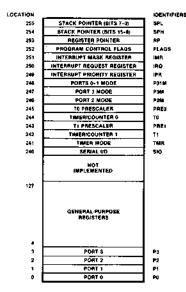

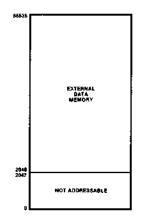

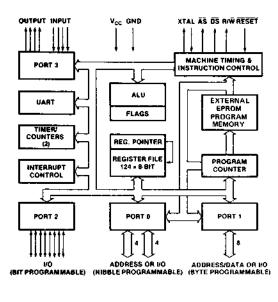

| Z8, Single Chip Microcomputer                          |

|--------------------------------------------------------|

| Microprocessors and Peripherals                        |

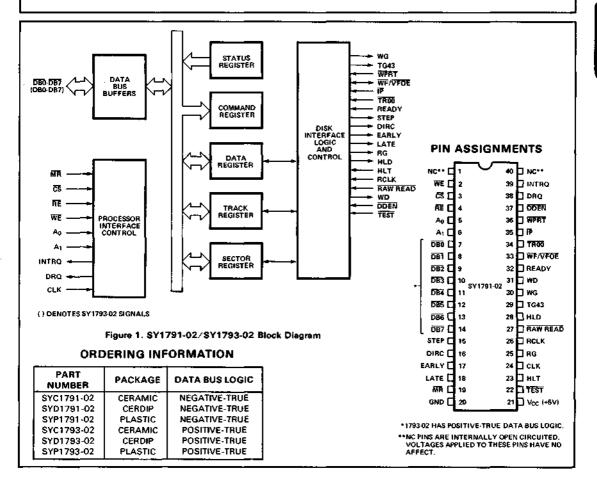

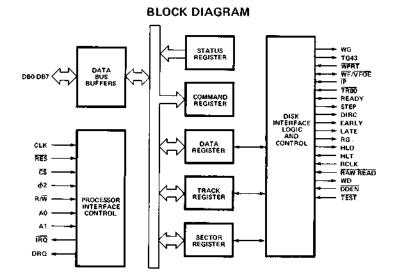

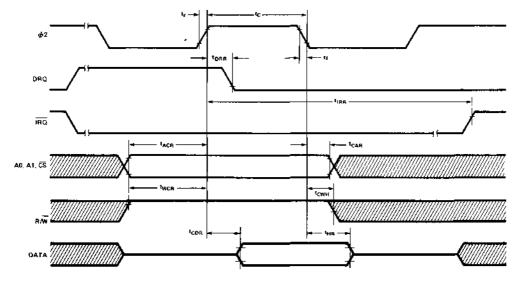

| SY1791-02/SY1793-02, Floppy Disk Controller 3-23       |

| SY2661, Enhanced Programmable Communications Interface |

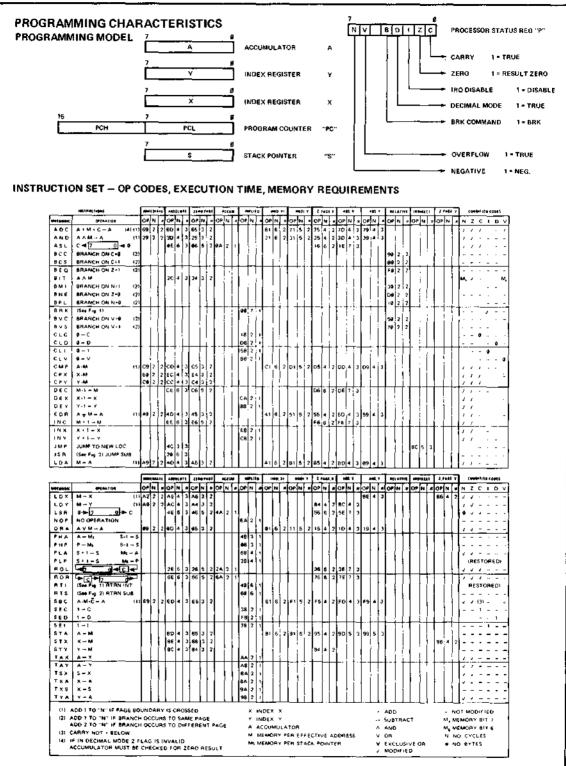

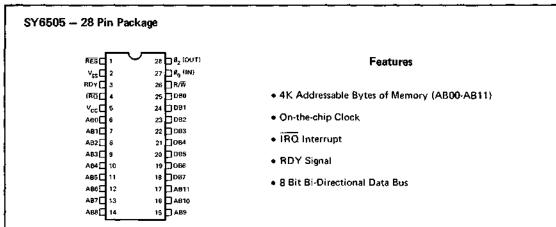

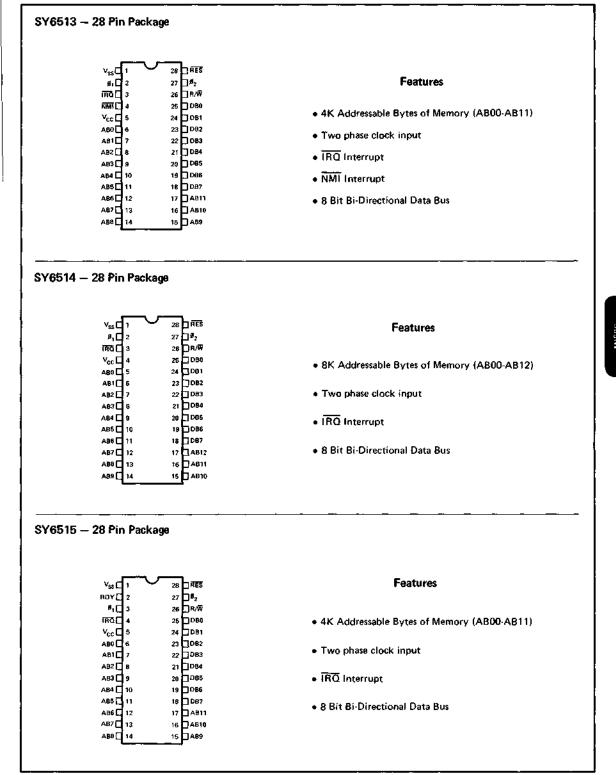

| SY6500, 8-Bit Microprocessor Family 3-53               |

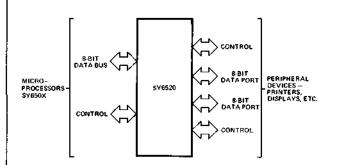

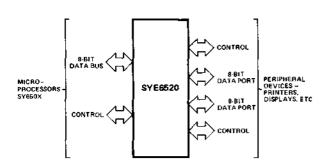

| SY6520, Peripheral Interface Adapter 3-67              |

| SY6521/SY6821, Peripheral Interface Adapter 3-81       |

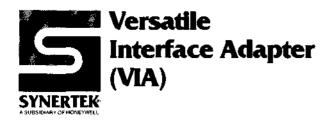

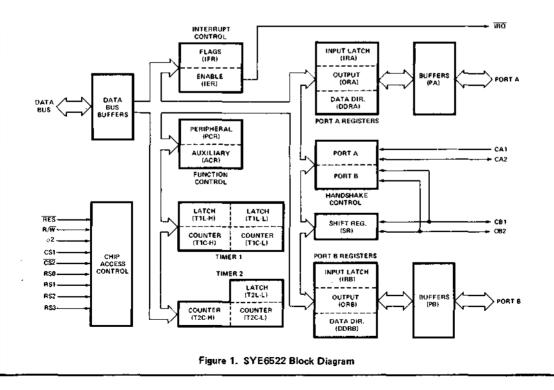

| SY6522, Versatile Interface Adapter 3-95               |

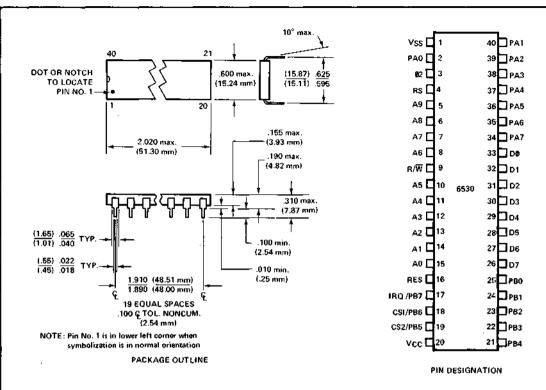

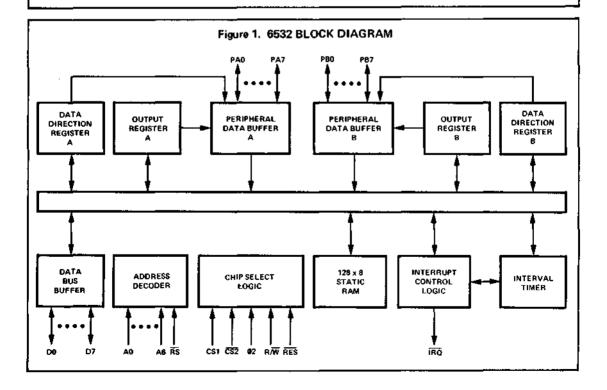

| SY6530, Memory, I/O, Timer Array 3-117                 |

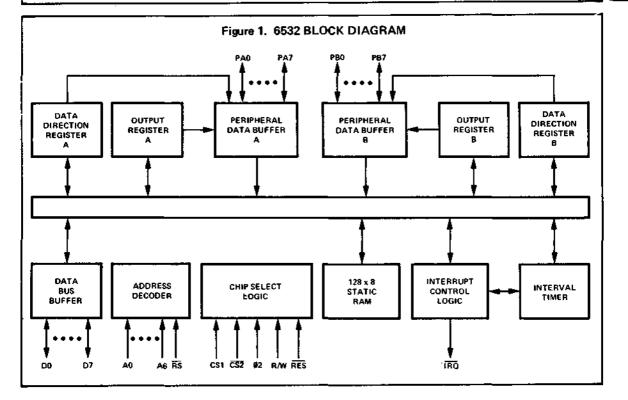

| SY6532, RAM, I/O, Timer Array 3-129                    |

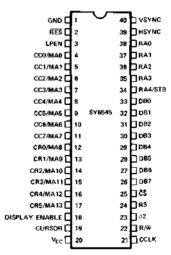

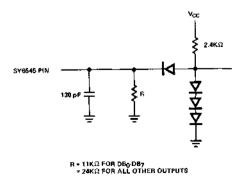

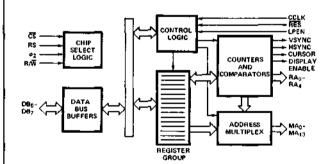

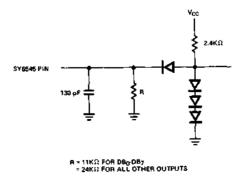

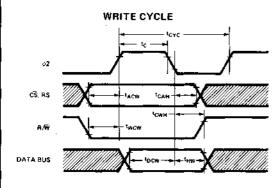

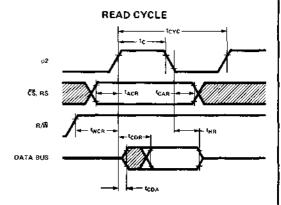

| SY6545, CRT Controller                                 |

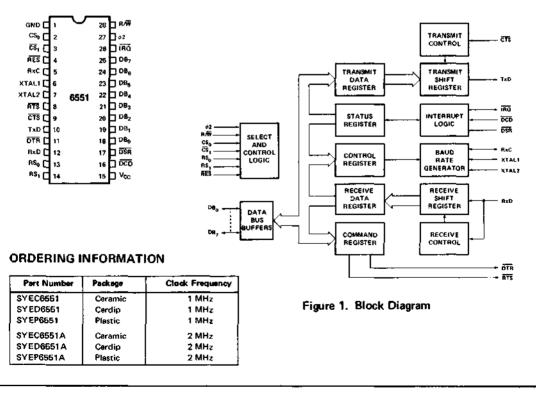

| SY6551. Asynchronous Communication Interface Adapter   |

| SY6591, Floppy Disk Controller                         |

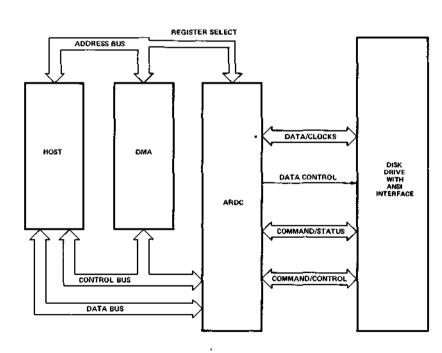

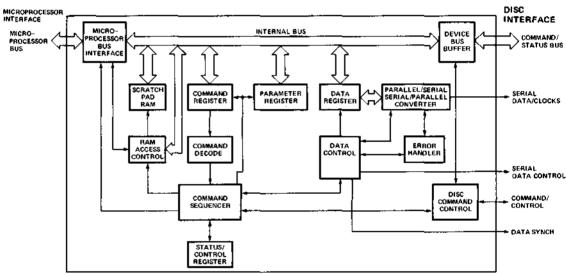

| SY6691/SY6692, ANSI Rigid Disk Controller 3-183        |

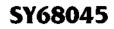

| SY68045, CRT Controller                                |

Page

# **Contents (Contd.)**

| CHAPTER 4<br>Logic Capabilities                                           | <b>Page</b><br>4-1 |

|---------------------------------------------------------------------------|--------------------|

| CHAPTER 5<br>Systems                                                      |                    |

| CP110, Super Jolt CPU Board                                               | £ 0                |

| AS200. Universal Card                                                     |                    |

| EPS-1, SYM-1 Diagnostic Program                                           |                    |

| SYM-1, Single Board Computer                                              |                    |

| SYM-1, Single Board Computer SYM-1/68, SYM-1/69, Single Board Computers   |                    |

| MOD-68; MOD-69, Adapter Boards for SYM-1                                  |                    |

| PEX-1, Port Expansion and Connector Kit                                   |                    |

| SRM-1/SRM-3, Static RAM Memory Kit                                        |                    |

| SM100. OEM Version of SYM-1                                               |                    |

| BAS-1. Full Function BASIC                                                |                    |

| RAE-1. Resident Assembler/Editor                                          |                    |

| KTM-2, Keyboard Terminal Module                                           |                    |

| KTM-3, Keyboard Terminal Module                                           |                    |

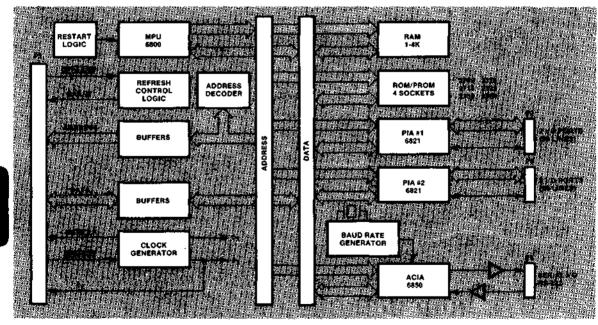

| MBC010. CPU Board                                                         |                    |

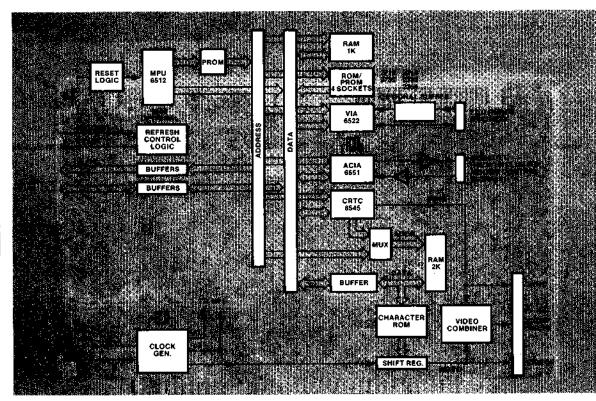

| MBC020, CPU/Video Board                                                   |                    |

| MBC01A2/MBC01A2-1, Single Board Computer Motorola Micromodule Replacement |                    |

| MBC008/016. Static RAM Modules                                            |                    |

| MBC016D, MBC032D, MBC048D, MBC064D, Dynamic RAM Boards                    |                    |

| MBC081, EPROM Programmer                                                  |                    |

| MBC091, Prototyping Board                                                 |                    |

| MQC092/93, Extender Boards                                                |                    |

| MBC210, Floppy Disk Controller                                            |                    |

| MBC510. Combo I/O Board                                                   |                    |

| MDT2000, Micro Development System for Z8 and SY6500 Microprocessors       | 5-17               |

| CHAPTER 6                                                                 |                    |

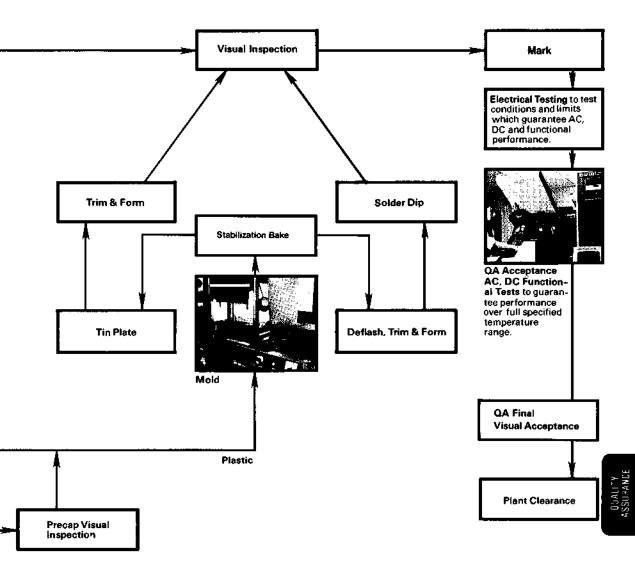

| Quality Assurance                                                         | 6-1                |

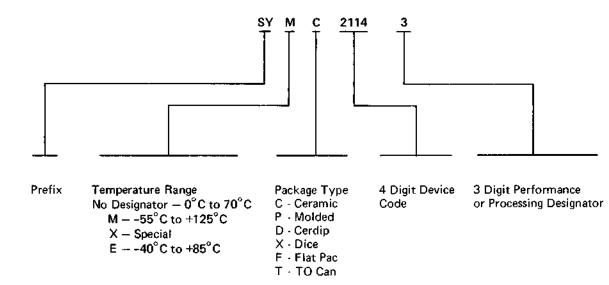

| CHAPTER 7<br>General Information                                          | <b>.</b> .         |

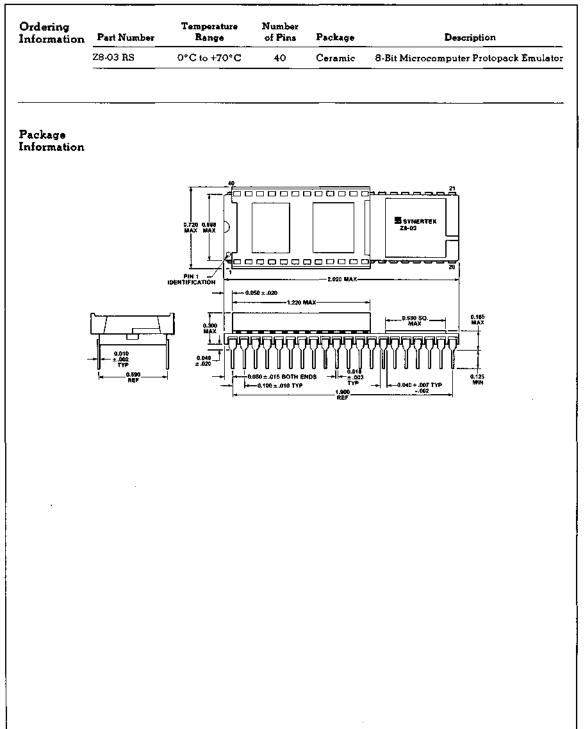

| Ordering Information                                                      |                    |

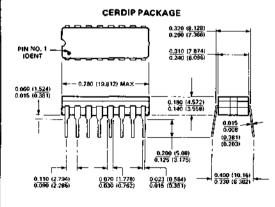

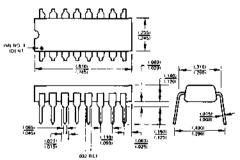

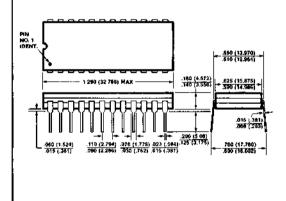

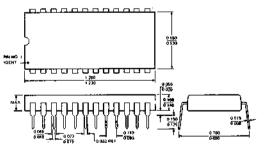

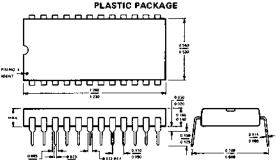

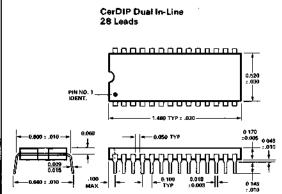

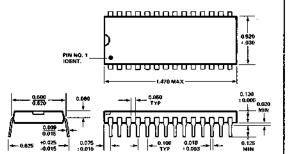

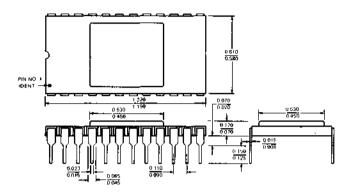

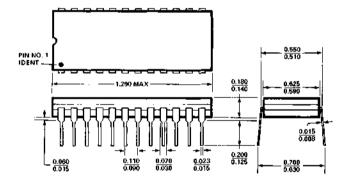

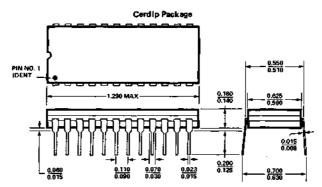

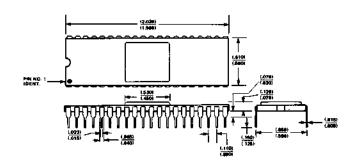

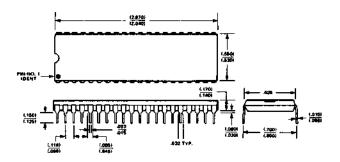

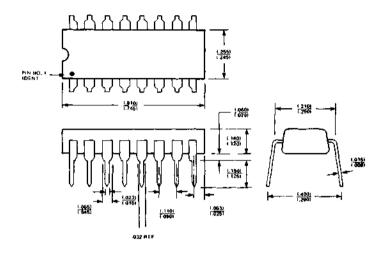

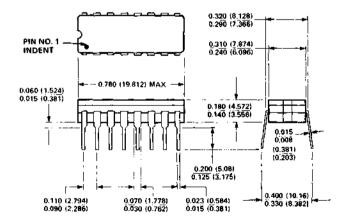

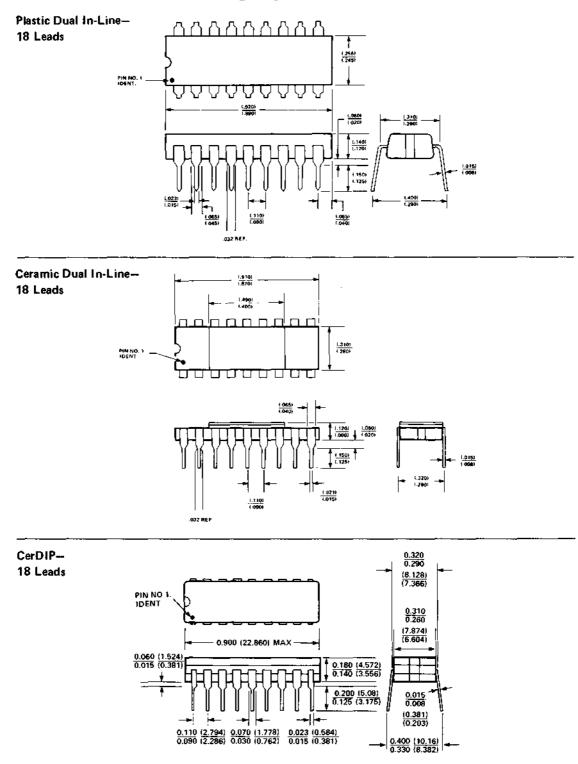

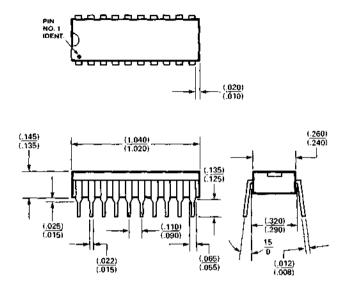

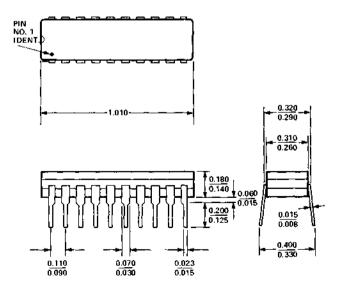

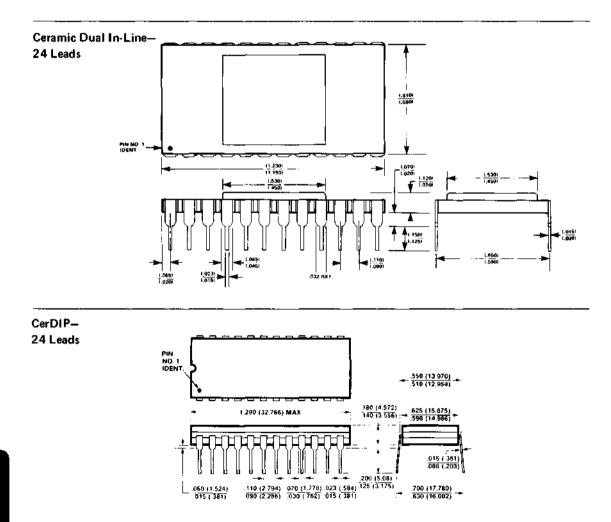

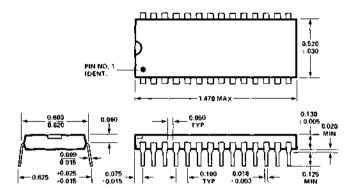

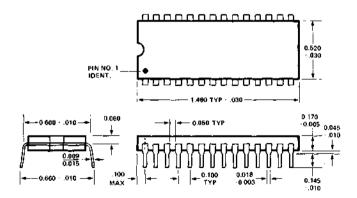

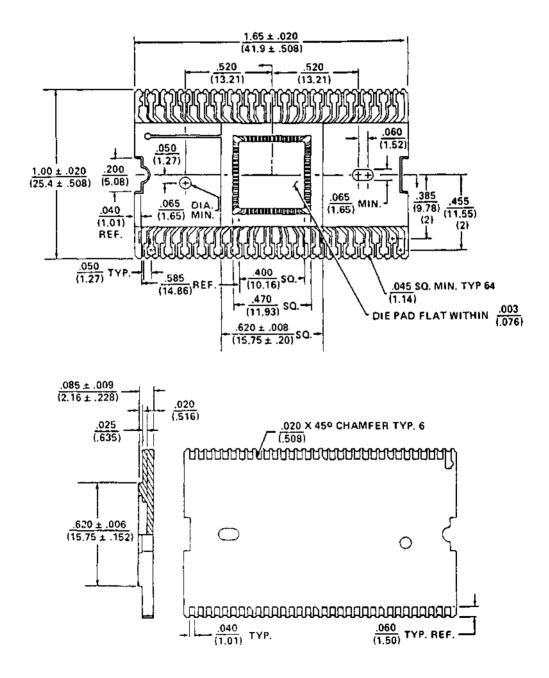

| Packaging Information                                                     | /-3                |

# **Numerical Index**

Page

|                         | Page                                                                                    |

|-------------------------|-----------------------------------------------------------------------------------------|

| Z8**                    | Single-Chip Microcomputer3-3                                                            |

| SY1791-02/<br>SY1793-02 | Floppy Disk Controller (FDC)                                                            |

| SY2101-1                | 256x4 Bit Static MOS RAM (500 nsec) 1-3                                                 |

| SY2101A                 | 256x4 Bit Static MOS RAM (350 nsec) 1-3                                                 |

| SY2101A-2               | 256x4 Bit Static MOS RAM (250 nsec) 1-3                                                 |

| SY2101A-4               | 256x4 Bit Static MOS RAM (450 nsec) 1-3                                                 |

| SY2111-1                | 256x4 Bit Static MOS RAM (500 nsec) 1-7                                                 |

| SY2111A                 | 256x4 Bit Static MOS RAM (350 nsec) 1-7                                                 |

| SY2111A-2               | 256x4 Bit Static MOS RAM (250 nsec) 1-7                                                 |

| SY2111A-4<br>SY2112-1   | 256x4 Bit Static MOS RAM (450 nsec), 1-7<br>256x4 Bit Static MOS RAM (500 nsec), 1-11   |

| SY2112A                 | 256x4 Bit Static MOS RAM (350 nsec) 1-11                                                |

| SY2112A-2               | 256x4 Bit Static MOS RAM (250 nsec) 1-11                                                |

| SY2112A-4               | 256x4 Bit Static MOS RAM (450 nsec) 1-11                                                |

| SY2114                  | 1024x4 Bit Static MOS RAM (450 nsec), 1-17                                              |

| SY2114-1                | 1024x4 Bit Static MOS RAM (150 nsec) 1-17                                               |

| SY2114-2                | 1024x4 Bit Static MOS RAM (200 nsec) 1-17                                               |

| SY2114-3                | 1024x4 Bit Static MOS RAM (300 nsec) 1-17                                               |

| SY2114L                 | 1024x4 Bit Static MOS RAM<br>Low Power (450 nsec)                                       |

| SY2114L-1               | 1024x4 Bit Static MOS RAM                                                               |

| SY2114L-2               | Low Power (150 nsec) 1-17<br>1024x4 Bit Static MOS RAM                                  |

|                         | Low Power (200 nsec) 1-17                                                               |

| \$Y2114L-3              | 1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)                                       |

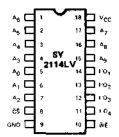

| SY2114LV                | 1024x4 Bit Static MOS RAM<br>Power Down (450 nsec)                                      |

| SY2114LV-2              | 1024x4 Bit Static MOS RAM<br>Power Down (200 nsec)                                      |

| SY2114LV-3              | 1024x4 Bit Static MOS RAM<br>Power Down (300 nsec) 1-21                                 |

| SY2128                  | 2048x8 Bit Static MOS RAM (120 nsec) 1-25                                               |

| SY2142                  | 1024x4 Bit Static MOS RAM (450 nsec) 1-26                                               |

| SY2142-2                | 1024x4 Bit Static MOS RAM (200 nsec) 1-26                                               |

| SY2142-3                | 1024x4 Bit Static MOS RAM (300 nsec) 1-26                                               |

| SY2142L                 | 1024x4 Bit Static MOS RAM (450 nsec) 1-26                                               |

| SY2142L-2<br>SY2142L-3  | 1024x4 Bit Static MOS RAM (200 nsec) 1-26<br>1024x4 Bit Static MOS RAM                  |

| 3121426-3               | Low Power (300 nsec)                                                                    |

| SY2142LV                | 1024x4 Bit Static MOS RAM (450 nsec) 1-30                                               |

| SY2142LV-2              | 1024x4 Bit Static MOS RAM (200 nsec) 1-30                                               |

| SY2142LV-3              | 1024x4 Bit Static MOS RAM (300 nsec) 1-30                                               |

| SY2147                  | 4096x1 Bit Static MOS RAM (70 nsec) 1-34                                                |

| SY2147-3                | 4096x1 Bit Static MOS RAM (55 nsec) 1-34                                                |

| SY2147-6<br>SY2147L     | 4096x1 Bit Static MOS RAM (85 nsec) 1-34<br>4096x1 Bit Static MOS RAM (70 nsec) 1-34    |

| SY2147E                 | 4096x1 Bit Static MOS RAM (70 nsec) 1-34<br>4096x1 Bit Static MOS RAM (35-70 nsec) 1-38 |

| SY2148H                 | 1024x4 Bit Static MOS RAM (70 nsec) 1-40                                                |

| SY2148H-2               | 1024x4 Bit Static MOS RAM (45 nsec) 1-40                                                |

| SY2148H-3               | 1024x4 Bit Static MOS RAM (55 nsec) 1-40                                                |

| SY2148HL                | 1024x4 Bit Static MOS RAM<br>Low Power (70 nsec)                                        |

| SY2148HL-3              | 1024x4 Bit Static MOS RAM<br>Low Power (70 nsec)                                        |

| SY2149H                 | 1024x4 Bit Static MOS RAM (70 nsec) 1-45                                                |

| SY2149H-2               | 1024x4 Bit Static MOS RAM (45 nsec) 1-45                                                |

| SY2149H-3               | 1024x4 Bit Static MOS RAM (55 nsec) 1-45                                                |

| SY2149HL                | 1024 x4 Bit Static MOS RAM<br>Low Power (70 nsec)                                       |

| SY2149HL-3              | 1024x4 Bit Static MOS RAM                                                               |

| CV001CA                 | Low Power (55 nsec)                                                                     |

| SY2316A<br>SY2316B      | 2048x8 Bit Static MOS ROM (550 nsec) 2-3<br>2048x8 Bit Static MOS ROM (450 nsec) 2-3    |

| SY2316B-2               | 2048x8 Bit Static MOS ROM (450 risec) 2-3<br>2048x8 Bit Static MOS ROM (200 risec) 2-7  |

|                         |                                                                                         |

|                               | raye                                                                         |

|-------------------------------|------------------------------------------------------------------------------|

| SY2316B-3 20                  | 48x8 Bit Static MOS ROM (300 nsec) 2-11                                      |

| SY2332 40                     | 96x8 Bit Static MOS ROM (450 nsec) 2-15                                      |

| SY2332-3 40                   | 96x8 Bit Static MOS ROM (300 nsec) 2-19                                      |

| SY2333 40                     | 96x8 Bit Static MOS ROM (450 nsec) 2-15                                      |

| SY2333-3 40                   | 96x8 Bit Static MOS ROM (300 nsec) 2-19                                      |

| SY2364 81                     | 92x8 Bit Static MOS ROM (450 nsec) 2-23                                      |

| SY2364-2 81                   | 92x8 Bit Static MOS ROM (200 nsec) 2-23                                      |

| SY2364-3 81                   | 92x8 Bit Static MOS ROM (300 nsec) 2-23                                      |

| SY2364A 81                    | 92x8 Bit Static MOS ROM (450 nsec) 2-23                                      |

| SY2364A-2 81                  | 92x8 Bit Static MOS ROM (200 nsec) 2-23                                      |

| SY2364A-3 81                  | 92x8 Bit Static MOS ROM (300 nsec) 2-23                                      |

| SY2365 81                     | 92x8 Bit Static MOS ROM (450 nseci 2-27                                      |

| SY2365-2 81                   | 92x8 Bit Static MOS ROM (200 nsec) 2-27                                      |

| SY2365-3 81                   | 92x8 Bit Static MOS ROM (300 nsec) 2-27                                      |

| SY2365A 81                    | 92x8 Bit Static MOS ROM (450 nsec) 2-27                                      |

| SY2365A-2 81                  | 92x8 Bit Static MOS ROM (200 nsec) 2-27                                      |

| SY2365A-3 81                  | 92x8 Bit Static MOS ROM (300 nsec) 2-27                                      |

| SY23128 16                    | 384x8 Bit Static MOS ROM (200 nsec), 2-31                                    |

|                               | hanced Programmable Communications                                           |

|                               | Interface                                                                    |

| SY3308 10                     | 24x8 Bit Static MOS ROM (70 nsec) 2-32                                       |

|                               | 48x8 Bit Static MOS ROM (80 nsec) 2-36                                       |

|                               | 48x8 Bit Static MOS ROM (80 nsec) 2-36                                       |

| SY6500                        | 8-Bit Microprocessor Family 3-53                                             |

| SYE6500/6500A                 | 8-Bit Microprocessor Family                                                  |

|                               | (Extended Temperature) 3-65                                                  |

| SY6520/6520A                  | •                                                                            |

| SY6820/68B20                  | Peripheral Interface Adapter (PIA) 3-67                                      |

| SYE6520/6820                  | Peripheral Interface Adapter                                                 |

| SYE6520A/68B20                | (Extended Temperature) 3-79                                                  |

| SY6521/6821                   |                                                                              |

| SY6521A/68B21                 | Peripheral Interface Adapter (PIA)                                           |

| SYE6521/6821                  | Peripheral Interface Adapter                                                 |

| SYE6521A/68B21                | (Extended Temperature)                                                       |

| SY6522/6522A<br>SYE6522/6522A | Versatile Interface Adapter                                                  |

| 31E0022/0022A                 | Extended Temperature:                                                        |

| SY6530                        | Memory, I/O, Timer Array 3-117                                               |

| SY6532                        | RAM, I/O, Timer Array 3-129                                                  |

| SYE6532                       | RAM, I/O, Timer Array                                                        |

| SYE6532A                      | (Extended Temperature)                                                       |

| SY6545                        | CAT Controller 3-139                                                         |

| SY6545-1                      | CRT Controller 3-155                                                         |

| SY6551                        | Asynchronous Communication Interface                                         |

| OVEACCA INCOM                 | Adapter 3-169                                                                |

| SYE6551/6551A                 | Asynchronous Communication Interface<br>Adapter (Extended Temperature) 3-177 |

| SY6591/6591A                  | Floppy Disk Controller (FDC) 3-177                                           |

| SY6691/6692                   | ANSI Rigid Disk Controller (ARDC <sup>**</sup> ) 3-183                       |

| SY68045                       | CRT Controller (CRTC)                                                        |

|                               |                                                                              |

#### Military Grade Products: TA = -55° C to +125° C

| SYM2147    | 4096x1 Bit Static MOS RAM (70 nsec)  | 1-39   |

|------------|--------------------------------------|--------|

| SYM2147-6  | 4096x1 Bit Static MOS RAM (85 nsec)  | . 1-39 |

| SYM2148    | 1024x4 Bit Static MOS RAM (70 nsec)  | 1-44   |

| SYM2148-6  | 1024x4 Bit Static MOS RAM (85 nsec)  | 1-44   |

| SYM2149H   | 1024x4 Bit Static MOS RAM (70 nsec)  | . 1-49 |

| SYM2149H-3 | 1024x4 Bit Static MOS RAM (55 nsec)  | . 1-49 |

| SYM3316    | 2048x8 Bit Static MOS ROM (100 nsec) | . 2-40 |

| SYM3316A   | 2048x8 Bit Static MOS ROM (100 nsec) | 2-40   |

## Numerical Index (Contd.)

#### .

#### Systems: Page CP110 Super Jolt CPU Board 5-2 AS200 Universal Card ..... 5-2 EPS-1 SYM-1 Diagnostic Program ..... 5-2 SYM-1 Single Board Computer ..... 5-3 SYM-1/68: SYM-1/69 Single Board Computers 5-3 MOD-68: MOD-69 Adapter Boards for SYM-1 5-4 PEX-1 Port Expansion and Connector Kit ..... 5-4 SRM-1/SRM-3 Static RAM Memory Kit ..... 5-4 OEM Version of SYM-1 SM100 5-5 BAS-1 Full Function BASIC 5-5 Resident Assembler/Editor RAE-1 5-5 KTM-2 Keyboard Terminal Module 5-6 KTM-3 Keyboard Terminal Module 5-7 MBC010 CPU Board ..... 5-9 MBC020 CPU/Video Board ..... 5-9 MBC01A2/ Single Board Computer, Motorola Micromodule Replacement ..... 5-11 MBC01A2-1 MBC008/016 Static RAM Modules ..... 5-13 MBC016D Oynamic RAM boards ..... 5-14 MBC032D MBC048D MBC064D MBC081 EPROM Programmer ..... 5-15 Prototyping Board ..... 5-15 **MBC091** MBC092/93 Extender Boards ..... 5-15 MBC210 Floppy Disk Controller ..... 5-16 MBC510 Combo I/O Board ..... 5-16 MDT2000 Micro Development System for Z8 and SY6500 Microprocessors ..... 5-17

The information contained in this document has been carefully checked and is believed to be reliable; however, Synertek shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, the information contained in this document. Synertek makes no guarantee or warranty concerning the accuracy of such information, and this document does not in any way extend Synertek's warranty on any product beyond that set forth in Synertek's standard terms and conditions of sale. Synertek does not guarantee that the use of any information contained herein will not infringe upon the patent or other rights of third parties, and no patent or other license is implied hereby. Synertek reserves the right to make changes in the product without notification which would render the information contained in this document obsolete or inaccurate. Please contact Synertek for the latest Information concerning this product.

#### Commercial: $T_A = 0^\circ C$ to $+70^\circ C$

RA Mis

## **RAM Selector Guide**

|                        |              |             | Access Time  | Maximum Cu | Maximum Current (mA) |                         |          |  |  |

|------------------------|--------------|-------------|--------------|------------|----------------------|-------------------------|----------|--|--|

| Part No.               | Organization | No. of Pins | (ns)<br>Max. | Operating  | Standby              | Power Supply<br>(Volts) | Page     |  |  |

| SY2101-1               | 256 x 4      | 22          | 500          | 70         | _                    | +5                      | 1-3      |  |  |

| SY2101A                | 256 x 4      | 22          | 350          | 55         |                      | +5                      | 1-3      |  |  |

| SY2101A-2              | 256 x 4      | 22          | 250          | 55         | _                    | +5                      | 1-3      |  |  |

| SY2101A-4              | 256 x 4      | 22          | 450          | 55         | _                    | +5                      | 1-3      |  |  |

| SY2111-1               | 256 x 4      | 18          | 500          | 70         | _                    | +5                      | 1-7      |  |  |

| SY2111A                | 256 × 4      | 18          | 350          | 55         | _                    | +5                      | 1-7      |  |  |

| SY2111A-2              | 256 x 4      | 18          | 250          | 55         | _                    | +5                      | 1-7      |  |  |

| SY2111A-4              | 256 x 4      | 18          | 450          | 55         | _                    | +5                      | 1-7      |  |  |

| SY2112-1               | 256 x 4      | 16          | 500          | 70         | _                    | +5                      | 1-11     |  |  |

| SY2112A                | 256 x 4      | 16          | 350          | 55         |                      | +5                      | 1-11     |  |  |

| SY2112A-2              | 256 x 4      | 16          | 250          | 55         | _                    | +5                      | 1-11     |  |  |

| SY2112A-2<br>SY2112A-4 | 256 x 4      | 16          | 450          | 55         | _                    | +5                      | 1-11     |  |  |

|                        |              |             |              |            |                      |                         |          |  |  |

| SY2114                 | 1024 × 4     | 18          | 450          | 100        |                      | +5                      | 1-17     |  |  |

| SY2114-1               | [ 1024 × 4   | 18          | 150          | 100        | —                    | +5                      | 1-17     |  |  |

| SY2114-2               | 1024 x 4     | 18          | 200          | 100        | -                    | +5                      | 1-17     |  |  |

| SY2114-3               | 1024 x 4     | 18          | 300          | 100        | -                    | +5                      | 1-17     |  |  |

| SY2114L                | 1024 x 4     | 18          | 450          | 70         | -                    | +5                      | 1-17     |  |  |

| SY2114L-1              | 1024 × 4     | 18          | 150          | 70         | —                    | +5                      | 1-17     |  |  |

| SY2114L-2              | 1024 x 4     | 18          | 200          | 70         | —                    | +5                      | 1-17     |  |  |

| SY2114L-3              | 1024 x 4     | 18          | 300          | 70         | -                    | +5                      | 1-17     |  |  |

| SY2114LV               | 1024 x 4     | 18          | 450          | 70         | _                    | +511                    | 1-21     |  |  |

| SY2114LV-2             | 1024 x 4     | 18          | 200          | 70         |                      | +5:1                    | 1-21     |  |  |

| SY2114LV-3             | 1024 x 4     | 18          | 300          | 70         | _                    | +5'1                    | 1-21     |  |  |

| SY2142                 | 1024 x 4     | 20          | 450          | 100        | - 1                  | +5                      | 1-26     |  |  |

| SY2142-2               | 1024 × 4     | 20          | 200          | 100        | _                    | +5                      | 1-26     |  |  |

| SY2142-3               | 1024 × 4     | 20          | 300          | 100        |                      | +5                      | 1-26     |  |  |

| SY2142L                | 1024 x 4     | 20          | 450          | 70         | -                    | +5                      | 1-26     |  |  |

| SY2142L-2              | 1024 x 4     | 20          | 200          | 70         | _                    | +5                      | 1-26     |  |  |

| SY2142L-3              | 1024 x 4     | 20          | 300          | 70         | _                    | +5                      | 1-26     |  |  |

| SY2142LV               | 1024 x 4     | 20          | 450          | 70         | _                    | +511                    | 1-30     |  |  |

| SY2142LV-2             | 1024 x 4     | 20          | 200          | 70         | _                    | +511                    | 1-30     |  |  |

| SY2142LV-3             | 1024 x 4     | 20          | 300          | 70         | _                    | +5:1                    | 1-30     |  |  |

| SY2148H                | 1024 x 4     | 18          | 70           | 150        | 30                   | +5                      | 1-40     |  |  |

| SY2148H-2              | 1024 x 4     | 18          | 45           | 150        | 30                   | +5                      | 1-40     |  |  |

| SY2148H-3              | 1024 x 4     | 18          | 55           | 150        | 30                   | +5                      | 1-40     |  |  |

| SY2148HL               | 1024 x 4     | 18          | 70           | 125        | 20                   | +5                      | 1-40     |  |  |

| SY2148HL-3             | 1024 x 4     | 18          | 55           | 125        | 20                   | +5                      | 1-40     |  |  |

| SY2149H                | 1024 x 4     | 18          | 70           | 150        |                      | +5                      | 1-45     |  |  |

| SY2149H-2              | 1024 x 4     | 18          | 45           | 150        | l _                  | +5                      | 1-45     |  |  |

| SY2149H-3              | 1024 x 4     | 18          | 55           | 150        | l _                  | +5                      | 1-45     |  |  |

| SY2149HL               | 1024 x 4     | 18          | 70           | 125        | l _                  | +5                      | 1-45     |  |  |

| SY2149HL-3             | 1024 x 4     | 18          | 55           | 125        |                      | +5                      | 1-45     |  |  |

|                        |              |             |              |            | ····                 |                         | <u> </u> |  |  |

| SY2147                 | 4096 x 1     | 18          | 70           | 160        | 20                   | +5                      | 1-34     |  |  |

| SY2147-3               | 4096 × 1     | 18          | 55           | 180        | 30                   | +5                      | 1-34     |  |  |

| SY2147-6               | 4096 x 1     | 18          | 85           | 160        | 20                   | +5                      | 1-34     |  |  |

| SY2147L                | 4096 x 1     | 18          | 70           | 140        | 10                   | +5                      | 1-34     |  |  |

| SY2147H <sup>121</sup> | 4096 x 1     | 18          | 35-70        | 180        | 30                   | +5                      | 1-38     |  |  |

| SY2128 2               | 2048 × 8     | 24          | 120-200      | 100        | 30                   | +5                      | 1-25     |  |  |

#### Military: $T_A = -55^{\circ}C$ to $\pm 125^{\circ}C$

| SYM2148 <sup>2</sup>   | 1024 x 4 | 18 | 70 | 150 | 30 | +5 | 1-44 |

|------------------------|----------|----|----|-----|----|----|------|

| SYM2148-6 <sup>2</sup> | 1024 x 4 | 18 | 85 | 150 | 30 | +5 | 1-44 |

| SYM2149H 2             | 1024 × 4 | 18 | 70 | 150 | -  | +5 | 1-49 |

| SYM2149H-3 2           | 1024 × 4 | 18 | 55 | 150 |    | +5 | 1-49 |

| SYM2147 <sup>2</sup>   | 4096 x 1 | 18 | 70 | 180 | 30 | +5 | 1-39 |

| SYM2147-6 <sup>2</sup> | 4096 x 1 | 18 | 85 | 180 | 30 | +5 | 1-39 |

1. +2.5V Data Retention

2 To Be Announced.

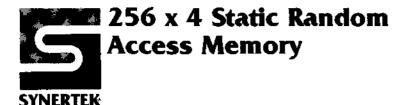

# SY2101

# MEMORY PRODUCTS

- 256x4 Organization to Meet Needs For Small System Memories

- Access Time 250/350/450/500/ns

- Single +5V Supply Voltage

- Directly TTL Compatible All Inputs and Outputs

- Static MOS No Clocks or Refreshing Required

- Simple Memory Expansion Two Chip Enable Inputs

- Inputs Protected All Inputs Have Protection Against Static Charge

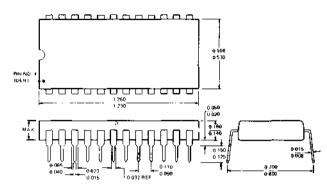

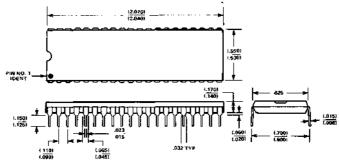

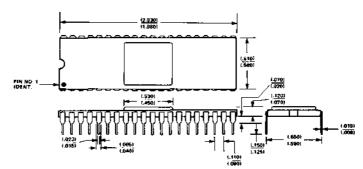

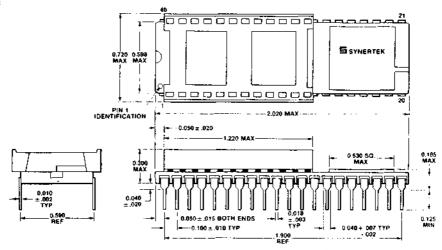

- Low Cost Packaging 22 Pin Plastic Dual-In-Line Configuration

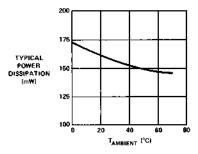

- Low Power Typically 150 mW

- Three-State Output OR-Tie Capability

- Output Disable Provided For Ease of Use in Common Data Bus Systems

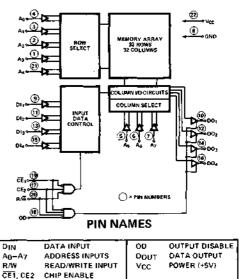

The SY2101 is a 256 word by 4 bit static random access memory element using N-channel MOS devices integrated on a monolithic array. It uses fully DC stable (static) circuitry and therefore requires no clocks or refreshing to operate. The data is read out nondestructively and has the same polarity as the input data.

The SY21D1 is designed for memory applications where high performance, low cost, large bit storage, and simple interfacing are important design objectives.

It is directly TTL compatible in all respects: inputs, outputs, and a single +5V supply. Two Chip Enables allow easy selection of an individual package when outputs are OR-tied. An output disable is provided

#### PIN CONFIGURATION

| A3 🗖 1                         | 22D VCC        |

|--------------------------------|----------------|

| A2 C 2                         | 21 44          |

| A1 3                           | 20 R/W         |

| A0 🗖 4                         | 19 🗖 🖬         |

| A5 🗖 5                         | 18 <b>⊡</b> 00 |

| A6 🗖 6                         | 17 🗖 CE2       |

| A7 [] 7                        | 16 000         |

| GND 🗖 8                        | 15 014         |

| DI 1 🗖 9                       | 14 🗖 1003      |

| DØ1 🗖 10                       | 13 013         |

| <sup>042</sup> □ <sup>11</sup> | 12 002         |

#### ORDERING INFORMATION

| Order<br>Number | Package<br>Type | Access<br>Time | Temperature<br>Range |

|-----------------|-----------------|----------------|----------------------|

| SYP2101-1       | Plastic DIP     | 500 ns         | 0°C to 70°C          |

| SYC2101-1       | Ceramic DIP     | 500 ns         | 0°C to 70°C          |

| SYP2101A-2      | Plastic DIP     | 250 ns         | 0°C to 70°C          |

| SYC2101A-2      | Ceramic DIP     | 250 ns         | 0°C to 70°C          |

| SYP2101A        | Plastic DIP     | 350 ns         | 0°C to 70°C          |

| SYC2101A        | Ceramic DIP     | 350 ns         | 0°C to 70°C          |

| SYP2101A-4      | Plastic DIP     | 450 ns         | 0°C to 70°C          |

| SYC2101A-4      | Ceramic DIP     | 450 ns         | 0°C to 70°C          |

so that data inputs and outputs can be tied for common I/O systems. Output disable is then used to eliminate any bi-directional logic.

The SY2101 is fabricated with N-channel ion implanted silicon gate technology. This technology allows the design and production of high-performance, easy-to-use MOS circuits and provides a higher functional density on a monolithic chip than either conventional MOS technology or N-channel silicon gate technology.

Synertek's ion implanted silicon gate technology also provides excellent protection against contamination. This permits the use of low cost plastic packaging.

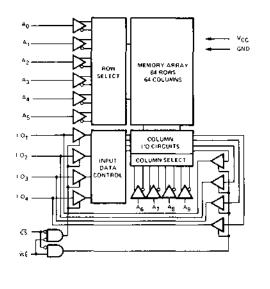

#### **BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS

| Ambient Temperature Under Bias | -10°C to +80°C             |

|--------------------------------|----------------------------|

| Storage Temperature            | -65°C to +150°C            |

| Voltage On Any Pin With        |                            |

| Respect to Ground              | -0.5V to +7V               |

| Power Dissipation              | <ul> <li>1 Watt</li> </ul> |

#### D.C. AND OPERATING CHARACTERISTICS

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified.

|        |                        | 2101-1 |         | 2101A-2<br>2101A, 2101A-4 |      |         |      |      |                                                                        |

|--------|------------------------|--------|---------|---------------------------|------|---------|------|------|------------------------------------------------------------------------|

| Symbol | Parameter              | Min.   | Түр.(1) | Max.                      | Min. | Typ.(1) | Max. | Unit | Test Conditions                                                        |

| ١u     | Input Current          |        |         | 10                        |      |         | 10   | μA   | V <sub>IN</sub> = 0 to 5.25V                                           |

| LOH    | I/O Leakage Current(2) | 1      |         | 15                        |      |         | 10   | μA   | CE = 2.2V, VOUT = 4.0V                                                 |

| LOL    | I/O Leakage Current(2) |        |         | -50                       |      |         | -10  | μA   | CE = 2.2V, VOUT = 0.45V                                                |

| ICC1   | Power Supply Current   |        | 30      | 60                        |      | 30      | 50   | mA   | V <sub>IN</sub> = 5.25V, I <sub>O</sub> = 0mA<br>T <sub>A</sub> = 25°C |

| ICC2   | Power Supply Current   |        |         | 70                        |      |         | 55   | mA   | V <sub>IN</sub> = 5.25V, I <sub>O</sub> = 0mA<br>∓ <sub>A</sub> = 0°C  |

| VIL    | Input Low Voltage      | -0.5   |         | +0.65                     | -0.5 |         | +0.8 | v    |                                                                        |

| ViH    | Input High Voltage     | 2.2    |         | Vcc                       | 2.0  |         | Vcc  | Ìν   |                                                                        |

| VoL    | Output Low Voltage     | i      |         | +0.45                     |      |         | +0.4 | v    | 1 <sub>OL</sub> = 3.2mA<br>{I <sub>OL</sub> = 2.0mA 2101-1}            |

| ∨он    | Output High Voltage    | 2,2    |         |                           | 2.4  |         |      | v    | I <sub>OH</sub> = −150µA                                               |

COMMENT:

NOTE: 1. Typical Values are for  $T_A = 25^{\circ}C$  and nominal supply voltage. 2. Input and Output tied together.

Stresses above those listed under "Absolute Maximum Rating" may cause per-manent demage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAPACITANCE TA = 25°C, f = 1MHz

| Symbol | Test                                        | Τγρ. | Max. | Unit |

|--------|---------------------------------------------|------|------|------|

| CIN    | Input Capacitance (All Input Pins) VIN = 0V | 4    | 8    | ρF   |

| COUT   | Output Capacitance VOUT = 0V                | 8    | 12   | рF   |

#### A.C. CHARACTERISTICS - SY2101-1

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified.

| Symbol             | Parameter                                        | Min. | Max. | Unit |

|--------------------|--------------------------------------------------|------|------|------|

| READ CYCLE         |                                                  |      |      |      |

| <sup>‡</sup> RCY   | Read Cycle                                       | 500  |      | ns   |

| tĄ                 | Access Time                                      | {    | 500  | ns   |

| *CO                | Chip Enable To Output                            |      | 350  | ns   |

| tOD                | Output Disable To Output                         |      | 300  | ns   |

| tDF <sup>[1]</sup> | Data Output to High Z State                      | 0    | 150  | ns   |

| tон                | Previous Data Read Valid after change of Address | 0    |      | ns   |

| RITE CYCLE         |                                                  |      |      |      |

| tWCY               | Write Cycle                                      | 500  |      | ns   |

| taw                | Write Delay                                      | 100  |      | ns   |

| *CW                | Chip Enable To Write                             | 400  |      | ns   |

| tDW                | Data Setup                                       | 280  |      | ns   |

| <sup>t</sup> DH    | Data Hold                                        | 100  | 1    | ns   |

| tWP                | Write Pulse                                      | 300  | 1    | ns   |

| tWR                | Write Recovery                                   | 50   |      | ns   |

#### A.C. CHARACTERISTICS - SY2101A-2

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified.

| Symbol                                                                                                                                                                                                                | Parameter                                                                                                                                                                                                                                                                                                                                                                                           | Min.                                             | Max.              | Unit                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|----------------------------------------------------------|

| READ CYCLE                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  |                   |                                                          |

| <sup>t</sup> RCY                                                                                                                                                                                                      | Read Cycle                                                                                                                                                                                                                                                                                                                                                                                          | 250                                              |                   | ns                                                       |

| tĄ                                                                                                                                                                                                                    | Access Time                                                                                                                                                                                                                                                                                                                                                                                         |                                                  | 250               | ns                                                       |

| tCO                                                                                                                                                                                                                   | Chip Enable To Output                                                                                                                                                                                                                                                                                                                                                                               |                                                  | 180               | ns                                                       |

| tOD                                                                                                                                                                                                                   | Output Disable To Output                                                                                                                                                                                                                                                                                                                                                                            |                                                  | 130               | ns                                                       |

| tDF <sup>(1)</sup>                                                                                                                                                                                                    | Data Output to High Z State                                                                                                                                                                                                                                                                                                                                                                         | 0                                                | 180               | ns                                                       |

| tOH                                                                                                                                                                                                                   | Previous Data Read Valid after change of Address                                                                                                                                                                                                                                                                                                                                                    | 40                                               |                   | ПS                                                       |

| WRITE CYCLE                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  |                   |                                                          |

| tWCY                                                                                                                                                                                                                  | Write Cycle                                                                                                                                                                                                                                                                                                                                                                                         | 250                                              |                   | ПS                                                       |

| tAW                                                                                                                                                                                                                   | Write Delay                                                                                                                                                                                                                                                                                                                                                                                         | 20                                               |                   | ns                                                       |

| *CW                                                                                                                                                                                                                   | Chip Enable To Write                                                                                                                                                                                                                                                                                                                                                                                | 150                                              |                   | ns                                                       |

| 1DW                                                                                                                                                                                                                   | Data Setup                                                                                                                                                                                                                                                                                                                                                                                          | 150                                              |                   | nş                                                       |

| tDH                                                                                                                                                                                                                   | Data Hold                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                |                   | ns                                                       |

| twp                                                                                                                                                                                                                   | Write Pulse                                                                                                                                                                                                                                                                                                                                                                                         | 150                                              |                   | ns                                                       |

| <b>WR</b>                                                                                                                                                                                                             | Write Recovery                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                |                   | រាទ                                                      |

| *DS                                                                                                                                                                                                                   | Output Disable Setup                                                                                                                                                                                                                                                                                                                                                                                | 20                                               |                   | ns                                                       |

|                                                                                                                                                                                                                       | CTERISTICS — SY2101A                                                                                                                                                                                                                                                                                                                                                                                |                                                  |                   |                                                          |

|                                                                                                                                                                                                                       | CTERISTICS – SY2101A<br><sup>2</sup> C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.<br>Parameter                                                                                                                                                                                                                                                                                           | Min.                                             | Max.              | Uni                                                      |

| T <sub>A</sub> = 0°C to 70 <sup>6</sup>                                                                                                                                                                               | C, $V_{CC} = 5V \pm 5\%$ unless otherwise specified.                                                                                                                                                                                                                                                                                                                                                | Min.                                             | Max.              | Uni                                                      |

| T <sub>A</sub> = 0°C to 70°<br>Symbol                                                                                                                                                                                 | C, $V_{CC} = 5V \pm 5\%$ unless otherwise specified.                                                                                                                                                                                                                                                                                                                                                | Min.<br>350                                      | Max.              | Unin                                                     |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE                                                                                                                                                                   | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified. Parameter                                                                                                                                                                                                                                                                                                                                   |                                                  | Max.<br>350       |                                                          |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br><sup>†</sup> RCY                                                                                                                                               | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified. Parameter Read Cycle                                                                                                                                                                                                                                                                                                                        |                                                  | <b></b>           | ກຮ                                                       |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>TRCY<br>TA                                                                                                                                                     | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified. Parameter Read Cycle Access Time                                                                                                                                                                                                                                                                                                            |                                                  | 350               | ns                                                       |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br><sup>T</sup> RCY<br>TA<br><sup>1</sup> CO                                                                                                                      | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.<br>Parameter<br>Read Cycle<br>Access Time<br>Chip Enable To Output                                                                                                                                                                                                                                                                          |                                                  | 350<br>240        | ភាន<br>កាន<br>កាន                                        |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>tRCY<br>tA<br>tCO<br>tOD                                                                                                                                       | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.<br>Parameter<br>Read Cycle<br>Access Time<br>Chip Enable To Output<br>Output Disable To Output                                                                                                                                                                                                                                              | 350                                              | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns                                     |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>tRCY<br>tA<br>tCO<br>tOD<br>tDF <sup>[1]</sup>                                                                                                                 | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.<br>Parameter<br>Read Cycle<br>Access Time<br>Chip Enable To Output<br>Output Disable To Output<br>Data Output to High Z State                                                                                                                                                                                                               | 350                                              | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns                                     |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>TRCY<br>tA<br>tCO<br>tOD<br>tDF <sup>[1]</sup><br>tOH                                                                                                          | C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.<br>Parameter<br>Read Cycle<br>Access Time<br>Chip Enable To Output<br>Output Disable To Output<br>Data Output to High Z State                                                                                                                                                                                                               | 350                                              | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns                                     |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>tRCY<br>tA<br>tCO<br>tOD<br>tDF <sup>[1]</sup><br>tOH<br>WRITE CYCLE                                                                                           | °C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.         Parameter         Read Cycle         Access Time         Chip Enable To Output         Output Disable To Output         Data Output to High Z State         Previous Data Read Valid after change of Address                                                                                                                       | 350<br>0<br>40                                   | 350<br>240<br>180 | กร<br>กร<br>กร<br>กร<br>กร<br>กร                         |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>tRCY<br>tA<br>tCO<br>tOD<br>tDF[1]<br>tOH<br>WRITE CYCLE<br>tWCY                                                                                               | °C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.         Parameter         Read Cycle         Access Time         Chip Enable To Output         Output Disable To Output         Data Output to High Z State         Previous Data Read Valid after change of Address         Write Cycle                                                                                                   | 350<br>0<br>40<br>350                            | 350<br>240<br>180 | 75<br>75<br>75<br>75<br>75<br>75                         |

| TA         = 0°C to 70'           Symbol           READ CYCLE           tRCY           tA           tCO           top           top[1]           tOH           WRITE CYCLE           tWCY           tAW               | <sup>2</sup> C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.         Parameter         Read Cycle         Access Time         Chip Enable To Output         Output Disable To Output         Data Output to High Z State         Previous Data Read Valid after change of Address         Write Cycle         Write Delay                                                                   | 350<br>0<br>40<br>350<br>20                      | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns                   |

| TA         = 0°C to 70'           Symbol           READ CYCLE           tRCY           tA           tCO           tDF[1]           tOH           WRITE CYCLE           tWCY           tAW           tCW               | <sup>2</sup> C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.         Parameter         Read Cycle         Access Time         Chip Enable To Output         Output Disable To Output         Data Output to High Z State         Previous Data Read Valid after change of Address         Write Cycle         Write Delay         Chip Enable To Write                                      | 350<br>0<br>40<br>350<br>20<br>200               | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns             |

| T <sub>A</sub> = 0°C to 70'<br>Symbol<br>READ CYCLE<br>tRCY<br>tA<br>tCO<br>tOD<br>tDF[1]<br>tOH<br>WRITE CYCLE<br>tWCY<br>tAW<br>tCW<br>tDW                                                                          | <sup>2</sup> C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.         Parameter         Read Cycle         Access Time         Chip Enable To Output         Output Disable To Output         Data Output to High Z State         Previous Data Read Valid after change of Address         Write Cycle         Write Delay         Chip Enable To Write         Data Setup                   | 350<br>0<br>40<br>350<br>20<br>200<br>200<br>200 | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns       |

| TA         - 0°C to 70'           Symbol           READ CYCLE           tRCY           tA           tCO           tDF[1]           tOH           WRITE CYCLE           tWCY           tAW           tCW           tDH | <sup>2</sup> C, V <sub>CC</sub> = 5V ±5% unless otherwise specified.         Parameter         Read Cycle         Access Time         Chip Enable To Output         Output Disable To Output         Data Output to High Z State         Previous Data Read Valid after change of Address         Write Cycle         Write Delay         Chip Enable To Write         Data Setup         Data Hold | 350<br>0<br>40<br>350<br>20<br>200<br>200<br>0   | 350<br>240<br>180 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

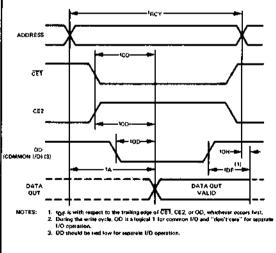

NOTE: 1 tDF is with respect to the trailing edge of  $\overline{CE1}$ , CE2, or OD, whichever occurs first.

Output Disable Setup

tDS

20

ns

| ×٨۲ | 2 |  |

|-----|---|--|

| ×   |   |  |

|     | ĥ |  |

|     |   |  |

Ê

| A.C. | CHAR/ | ACTERISTICS - | SY2101A-4 |

|------|-------|---------------|-----------|

|      | -     |               |           |

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified.

| Symbol                         | Parameter                                        | Min. | Max. | Unit |

|--------------------------------|--------------------------------------------------|------|------|------|

| READ CYCLE                     |                                                  | •    |      |      |

| <sup>t</sup> RCY               | Read Cycle                                       | 450  |      | ns   |

| tĄ                             | Access Time                                      |      | 450  | . ns |

| tCO                            | Chip Enable To Output                            |      | 310  | ns   |

| top                            | Output Disable To Output                         |      | 250  | ns   |

| <sup>t</sup> DF <sup>[1]</sup> | Data Output to High Z State                      | 0    | 200  | ns   |

| tОН                            | Previous Data Read Valid after change of Address | 40   |      | ns   |

| RITE CYCLE                     |                                                  |      |      |      |

| twcy                           | Write Cycle                                      | 450  |      | ns   |

| taw                            | Write Delay                                      | 20   |      | ns   |

| tcw                            | Chip Enable To Write                             | 250  |      | ns   |

| *DW                            | Data Setup                                       | 250  |      | ns   |

| tDH                            | Data Hold                                        | 0    |      | ns   |

| tWP                            | Write Pulse                                      | 250  |      | ns   |

| twr                            | Write Recovery                                   | 0    |      | ns   |

| tos                            | Output Disable Setup                             | 20   |      | ns   |

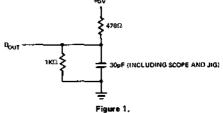

| Input Pulse Levels:                 |                         |                         |

|-------------------------------------|-------------------------|-------------------------|

| Input Pulse Rise & Fall Times:      | 10ns                    |                         |

| Timing Measurement Reference Level: | Inputs: 1.5V            |                         |

|                                     | Outputs: 0.8V & 2.0V    |                         |

| Output Load:                        | 1 TTL Gate & CL = 100pF | 1 TTL Gate & CL = 100pF |

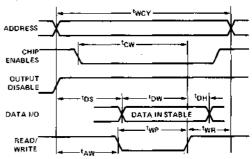

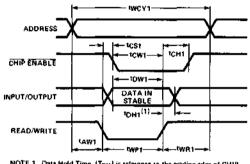

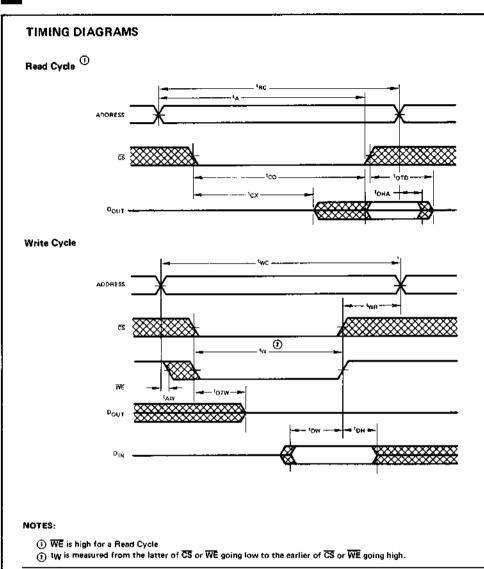

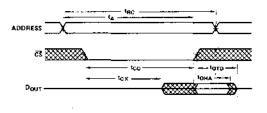

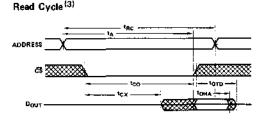

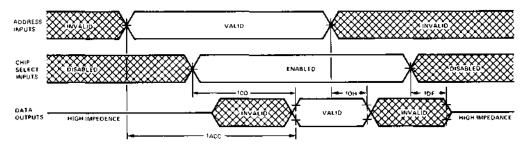

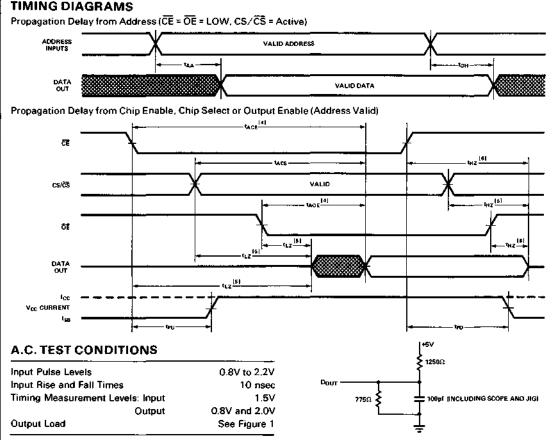

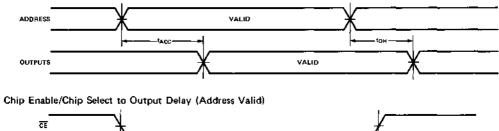

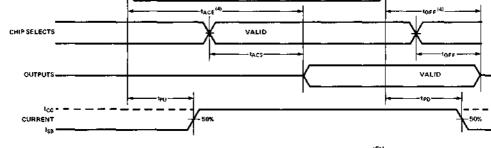

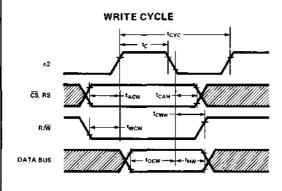

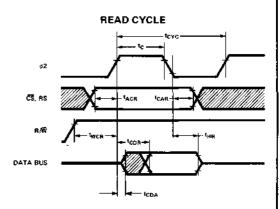

#### TIMING DIAGRAMS

READ CYCLE

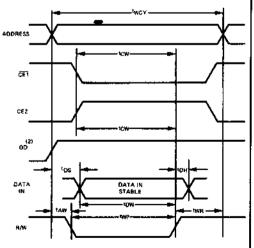

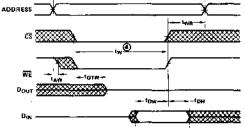

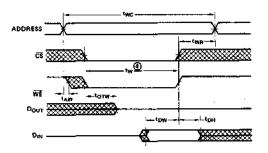

#### WRITE CYCLE

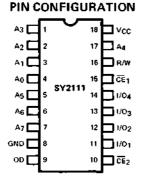

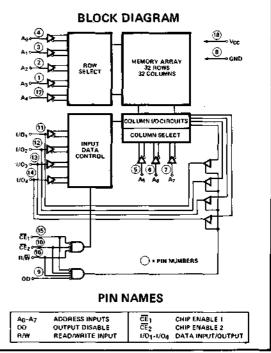

- Organization 256 Words By 4 Bits

- Common Data Input And Output

- Single +5V Supply Voltage

- Directly TTL Compatible All Inputs and Outputs

- Static MOS No Clocks or Refreshing Required

- Access Time 250/350/450/500ns

- Simple Memory Expansion 2 Chip Enable Inputs

The SY2111 is a 256 word by 4 bit static random access memory element using N-channel MOS devices integrated on a monolithic array. It uses fully DC stable (static) circuitry and therefore requires no clocks or refreshing to operate. The data is read out nondestructively and has the same polarity as the input data. Common input/output pins are provided.

The SY2111 is designed for memory applications in small systems where high performance, low cost, large bit storage, and simple interfacing are important design objectives.

It is directly TTL compatible in all respects: inputs,

#### ORDERING INFORMATION

| Order<br>Number | Package<br>Type | Access<br>Time | Temperature<br>Range |

|-----------------|-----------------|----------------|----------------------|

| SYP2111-1       | Plastic DIP     | 500 ns         | 0°C to 70°C          |

| SYD2111-1       | Cerdip          | 500 ns         | 0°C to 70°C          |

| SYP2111A-2      | Plastic DIP     | 250 ns         | 0°C to 70°C          |

| SYD2111A-2      | Cerdip          | 250 ns         | 0°C to 70°C          |

| SYP2111A        | Plastic DIP     | 350 ns         | 0°C to 70°C          |

| SYD2111A        | Cerdip          | 350 ns         | 0°C to 70°C          |

| SYP2111A-4      | Plastic DIP     | 450 ns         | 0°C to 70°C          |

| SYD2111A-4      | Cerdip          | 450 ns         | 0°C to 70°C          |

- Fully Decoded On-Chip Address Decode

- Inputs Protected All Inputs have Protection Against Static Charge

- Low Cost Packaging 18 Pin Plastic Dual-In-Line Configuration

- Low Power Typically 150mW

- Three State Output OR Tie Capability

outputs, and a single +5V supply. Separate Chip Enable leads allow easy selection of an individual package when outputs are OR-tied.

The SY2111 is fabricated with N-channelion-implanted silicon gate technology, which allows the design and production of high performance, easy-to-use MOS circuits and provides a higher functional density on a monolithic chip than either conventional MOS technology or N-channel silicon gate technology.

Synertek's silicon gate technology also provides excellent protection against contamination. This permits the use of low cost plastic packaging.

#### ABSOLUTE MAXIMUM RATINGS

| Ambient Temperature Under Bias | -10°C to +80°C  |

|--------------------------------|-----------------|

| Storage Temperature            | -65°C to +150°C |

| Voltage on Any Pin             |                 |

| With Respect to Ground         | -0.5V to +7V    |

| Power Dissipation              | 1 Watt          |

#### COMMENT

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. AND OPERATING CHARACTERISTICS

|                 |                      | 2111-1           |         |       | 2111A<br>_2111A-2, 2111A-4 |         |      |      |                                                                         |

|-----------------|----------------------|------------------|---------|-------|----------------------------|---------|------|------|-------------------------------------------------------------------------|

|                 |                      |                  |         |       |                            |         |      |      |                                                                         |

| Symbol          | Parameter            | Min.             | Typ.(1) | Max.  | Min.                       | Тур.(1) | Max. | Unit | Test Conditions                                                         |

| <sup>۱</sup> ۱۱ | Input Load Current   |                  |         | 10    |                            |         | 10   | μA   | V <sub>1N</sub> = 0 to 5.25V                                            |

| LOH             | I/O Leakage Current  |                  | 1       | 15    |                            |         | 10   | μA   | CE = 2.2V, VI/O = 4.0V                                                  |

| LOL             | I/O Leakage Current  |                  |         | -50   |                            |         | -10  | μA   | CE = 2.2V, VI/O = 0.45                                                  |

| ICC1            | Power Supply Current |                  | 30      | 60    |                            | 30      | 50   | mΑ   | V <sub>IN</sub> = 5.25V<br>II/O = 0mA, T <sub>A</sub> = 25°C            |

| ICC2            | Power Supply Current |                  |         | 70    |                            |         | 55   | mА   | V <sub>IN</sub> = 5.25V<br>I <sub>I/O</sub> = 0mA, T <sub>A</sub> = 0°C |

| VIL             | Input Low Voltage    | -0,5             |         | +0.65 | -0.5                       |         | +0.8 | v    |                                                                         |

| Viн             | Input High Voltage   | 2.2              |         | Vcc   | 2.0                        |         | Vcc  | v    |                                                                         |

| VOL             | Output Low Voltage   |                  |         | 0.45  |                            |         | 0.4  | v    | IOL = 3.2mA<br>(IOL = 2.0mA - 2111-1)                                   |

| ∨он             | Output High Voltage  | 2,2 <sup>.</sup> |         |       | 2.4                        |         |      | v    | l <sub>OH</sub> = -150μA                                                |

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$ , unless otherwise specified.

NOTES: 1. Typical values are for  $T_{\rm A}$  = 25°C and nominal supply voltage.

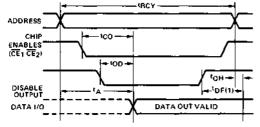

### A.C. CHARACTERISTICS - SY2111-1

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 5\%$ , unless otherwise specified.

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parameter                                        | Min, | Max. | Unit |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|------|------|--|

| READ CYCLE       tRCY     Read Cycle     500       tA     Access Time     500       tQO     Chip Enable To Output     350       tQD     Output Disable To Output     300       tDF[1]     Data Output To High Z State     0     150       tOH     Previous Data Read Valid After Change Of Address     0     150       WRITE CYCLE     500     500       tAW     Write Cycle     500       tAW     Write Delay     100       tCW     Chip Enable To Write     400       tDW     Data Setup     280       tDH     Data Hold     100 |                                                  |      |      |      |  |

| TRCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Read Cycle                                       | 500  |      | ns   |  |

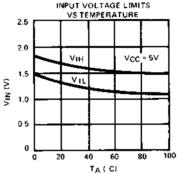

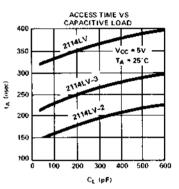

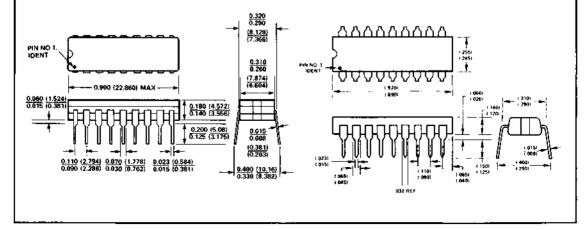

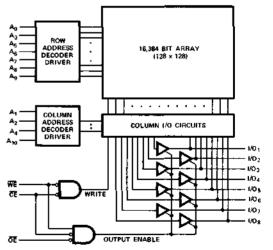

| tA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Access Time                                      |      | 500  | ns   |  |