## SIGNETICS 8X300 REFERENCE MANUAL

## SIGNETICS 8X300 REFERENCE MANUAL

## PREFACE

he 8X300 Reference Manual was compiled from various sources to assist designers in the use and evaluation of the 8X300 Microcontroller. Included are basic descriptions of the microcontroller, support circuits, development aids and applications.

Additional assistance in the use of the 8X300 can be obtained from personnel in Signetics Field Sales Offices and the documents listed below:

- 8X300 Programming Course

- Signetics Bipolar/MOS Microprocessor Data Manual

- Signetics Bipolar & MOS Memory Data Manual

- The Microcontroller Cross Assembler Program (MCCAP) User's Guide

- Designing a Floppy Disc Controller an Applications Manual

- Microprocessor Evaluation Guide

Copies of this manual and those referenced above are available from Signetics Field Sales Offices.

## TABLE OF CONTENTS

| Preface                                                           | 3   |

|-------------------------------------------------------------------|-----|

| Product Description                                               | 7   |

| One-chip Bipolar Microcontroller Approaches Bit-Slice Performance | 9   |

| 8X300 Microcontroller Data Sheet                                  | 15  |

| Support Products                                                  | 31  |

| Designer's Evaluation Kit for Fixed Instruction Bipolar           |     |

| Microprocessor                                                    | 33  |

| 8X300 Programming Course                                          | 35  |

| SMS Microcontroller Simulator SMS3000                             |     |

| SMS Microcontroller MS3300                                        |     |

|                                                                   |     |

| Application Memos                                                 | 43  |

| 8X300 Input/Output Design AH3                                     |     |

| 8X300 Applications AH4                                            |     |

| Signetics 8X300 CRT Controller                                    | 62  |

| 8X300 Cross Assembly Program (MCCAP) SPI                          |     |

| 8X300 Program Library B3                                          |     |

| TAD16 Procedure                                                   |     |

| MUL8X8 Procedure                                                  |     |

| M16X16 Procedure                                                  |     |

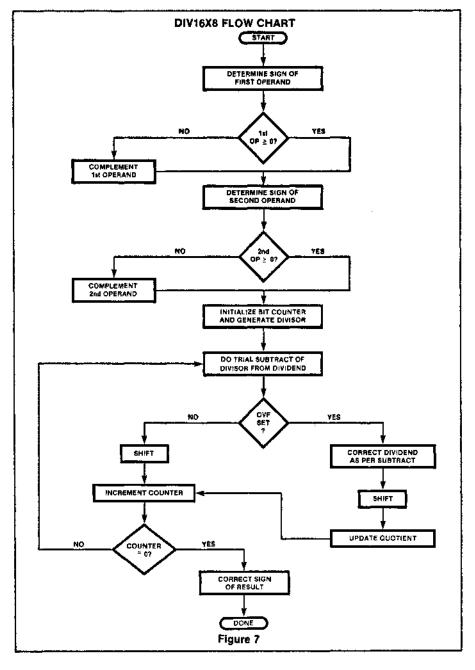

| DIV16X8 Procedure                                                 |     |

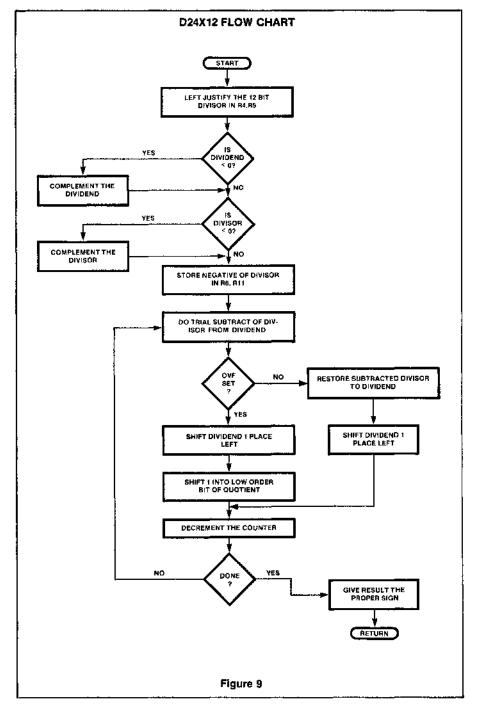

| D24X12 Procedure                                                  |     |

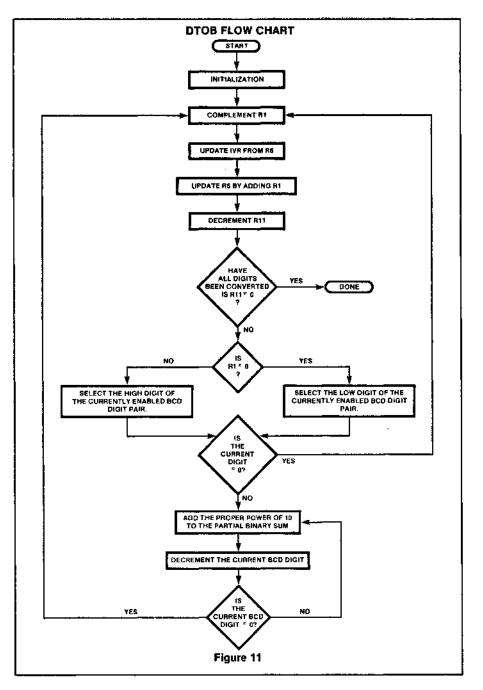

| DTOB Procedure                                                    |     |

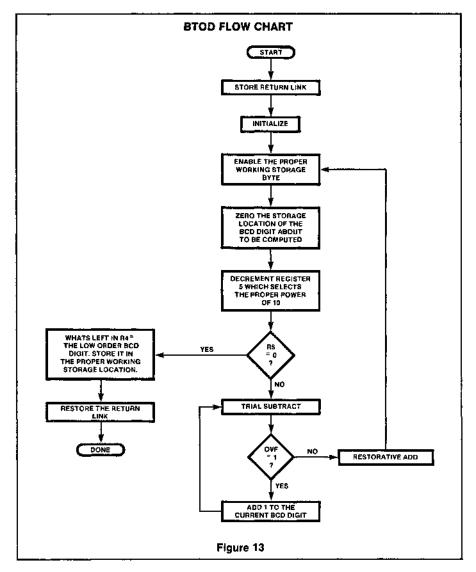

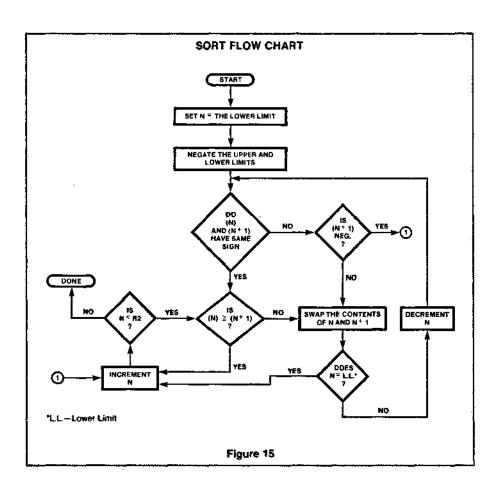

| BTOD Procedure SORT Procedure                                     |     |

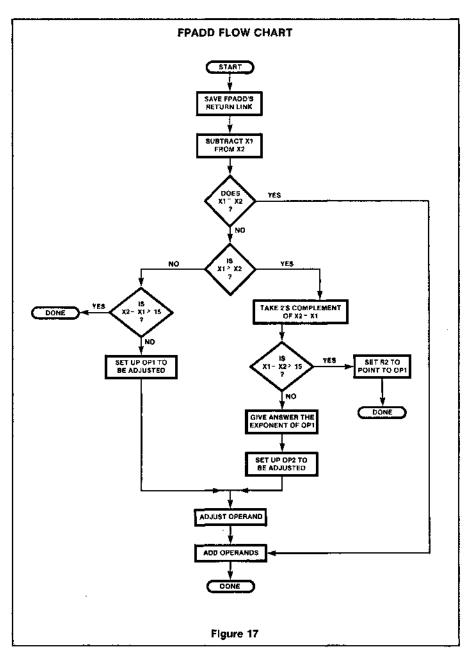

| FPADD Procedure                                                   |     |

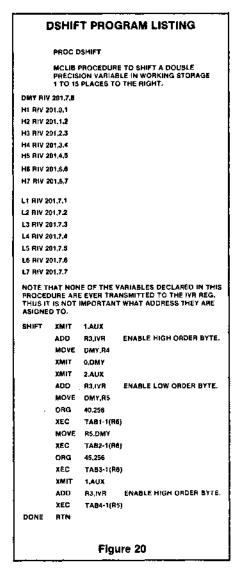

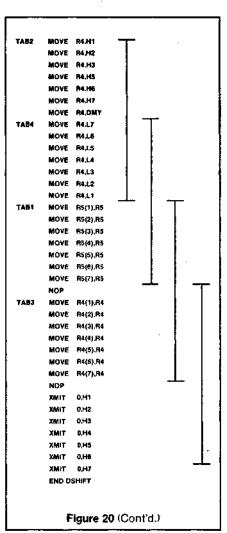

| DSHIFT Procedure                                                  |     |

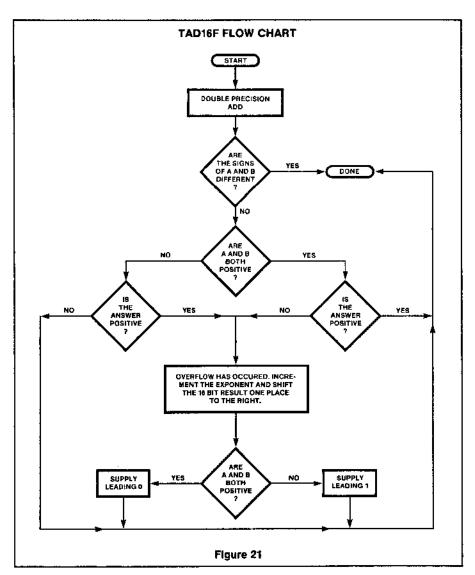

| TAD16F Procedure                                                  |     |

| Data Sheets                                                       | 109 |

| 8T31                                                              |     |

| 8T32/8T33/8T35/8T36                                               |     |

| 8739                                                              |     |

| 8T58                                                              |     |

| Bipolar Memory Selection Guide                                    |     |

| 82S16/82S116—82S17/82S117                                         |     |

|                                                                   |     |

| Appendix                                                          | 141 |

| 8X300 Designer's Evaluation Kit Instruction Manual 8X300KT100SK   | 143 |

| Sales Offices                                                     | 151 |

## PRODUCT DESCRIPTION

#### ONE-CHIPEBIPOLAR MICROCONTROLLER APPROACHES BITESLICE PERFORMANCE

# 8X300 combines best of both worlds with 250-nanosecond cycle time and powerful instruction set

by John Nemec, Signetics Corp., Sunnyvate, Calif.

☐ While refinements in the metal-oxide-semiconductor process have improved the performance of 8-bit MOS microprocessors, the need for really high speed still drives designers to the bipolar bit-slice machines. Advances in bipolar Schottky technology, however, now allow the design of a single-chip microprocessor with the computational ability and the performance advantages that approach those found in bit-slice designs.

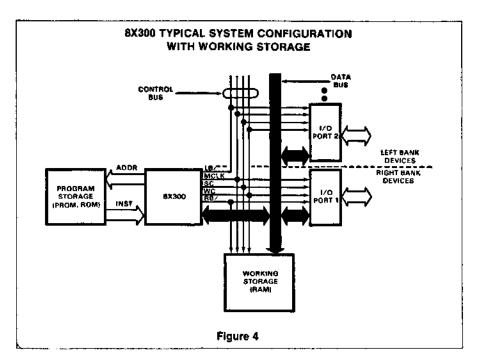

The 8X300 microprocessor from Signetics Corp. is the first such device. Not only does it have a cycle time of 250 nanoseconds, but it also has an improved architecture that makes it extremely efficient; hence its throughput is vastly superior to those of MOS devices. The interfacing bus structure, for example, is partitioned into two banks, and in a single instruction cycle the processor can accept data from a port on one bank, operate on it, and deposit the result in a port on the other bank. Since instruction fetching is concurrent with data operations, and both are executed in one 250-ns instruction cycle, the 8X300 is as fast as bipolar bit-slice systems on a microcycle basis.

Moreover, the 8X300 is easier to program than bitslice devices. The powerful instructions have simple mnemonic representations of the functions they perform, such as ADD for the addition function, and these mnemonics can be directly translated into their octal representation. With these conveniences, several hundred lines of program code can readily be written by hand. Consequently, for tasks of less than 500 instructions, no assembler is needed—only a simple conversion is required to generate the actual program-memory content.

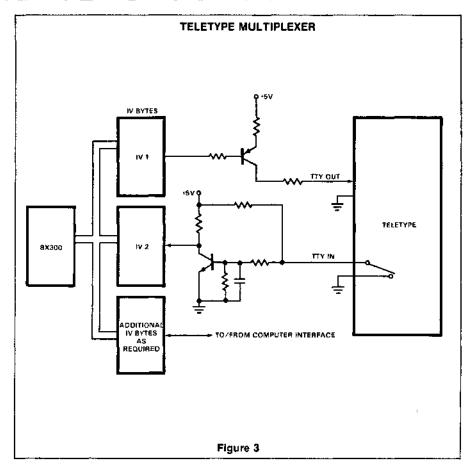

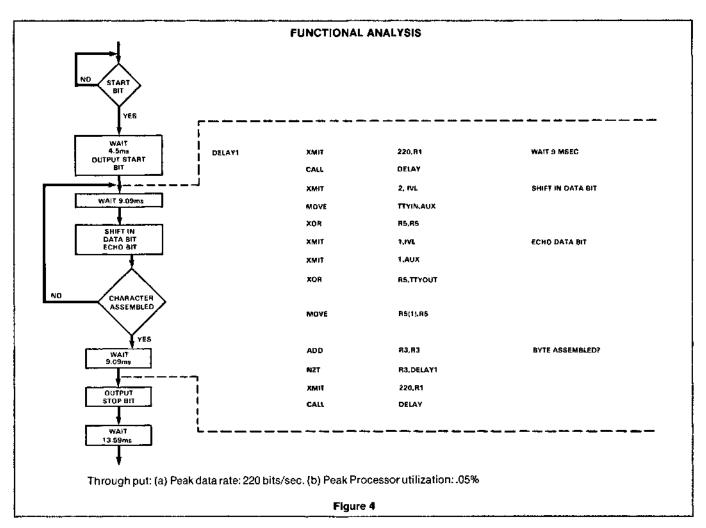

Its ease of programming and flexible interfacing structure make the 8X300 a natural as a subsystem and peripheral-device controller—one requiring little additional hardware for such applications. And the speed of the 8X300 allows it to handle control functions that MOS processors cannot, such as direct-memory-access interfacing, for example.

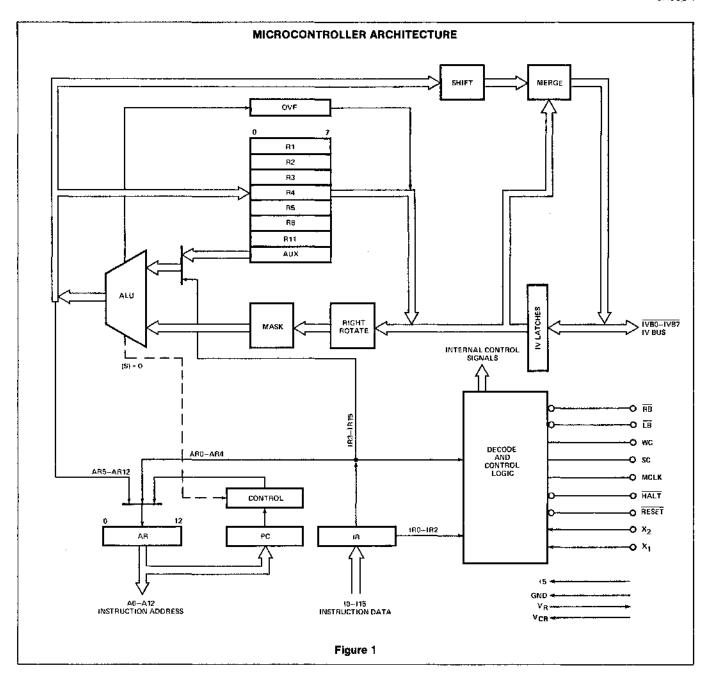

#### Novel architecture

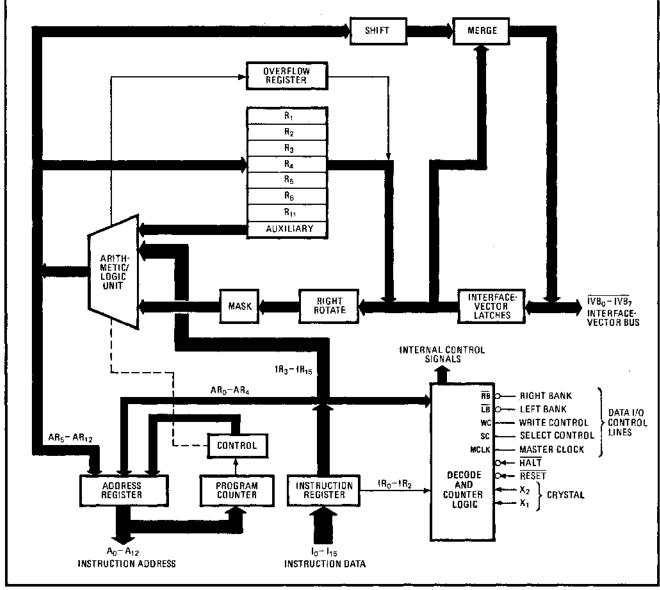

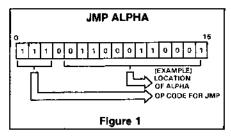

The architecture of the 8X300 processor is shown in Fig. 1. The chip includes full instruction-decoding logic that interprets the particular class of instructions, such as input/output or arithmetic and logic, and performs the indicated operation. The decoding and control logic supplies all internal signals for the processor, as well as signals on the control lines for directing the data input and output.

The processor also contains its own program counter, which is automatically incremented upon execution of the instruction. The counter may also be left unchanged or loaded with a new value. Control of the current

\*NOTE

This article originally appeared in ELECTRONICS Magazine September 1, 1977. It is reprinted here through the courtesy of and with permission of ELECTRONICS Magazine.

1. **High-performance microcontroller.** The Signetics 8X300 processor, a bipolar Schottky device with a 250-ns cycle time, is capable of processing at throughputs rivaling those of bit-slice machines. Fetching of its 16-bit instructions is concurrent with data operations; and with a bus partitioned into right and left banks, the 8X300 can, in a single instruction cycle, accept data, operate on it, and deposit the result.

address is provided by the address register and may be derived completely or partially from the program counter, from the instruction data lines (AR<sub>0</sub> through AR<sub>4</sub>), or from the output of the arithmetic/logic unit (lines AR<sub>5</sub> through AR<sub>12</sub>). Because of this flexible instructionaddress scheme, the order of execution may be altered by instructions or under conditions determined from selected data.

#### The read/write registers

The processor manipulates 8-bit data bytes. Internal data is stored in eight 8-bit read/write registers—R<sub>1</sub> through R<sub>6</sub>, R<sub>11</sub>, and an auxiliary register. The auxiliary register holds one of the operands used in two-operand instructions, such as ADD or AND, and a single-bit overflow register stores the carry-over bit from additional operations.

Further, the addition of the rotate, mask, shift, and

merge functions to the ALU extends the 8X300's operating capability and enhances its efficiency.

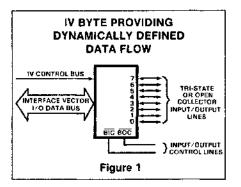

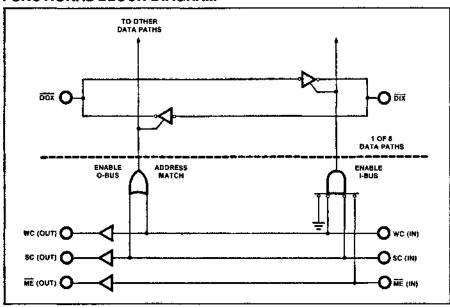

Interfacing with external circuitry is through an 8-bit bus called the interface-vector bus and consisting of lines IV<sub>0</sub> through IV<sub>2</sub>. The bus carries both address and data information, and the accompanying data-1/0 control lines tell the external circuitry which of the two types of information is on the bus. These lines include write- and select-control, right- and left-bank-signal, and master-clock lines.

Since the interface-vector bus carries addresses as well as data, 1/0 ports on the external circuits must be enabled before data transfer can take place. This is usually accomplished by placing an address on the bus under program control and then activating the select-control line, which indicates that a valid address is on the bus. When presented with an address, each of the possible 512 1/0 ports either enables itself upon

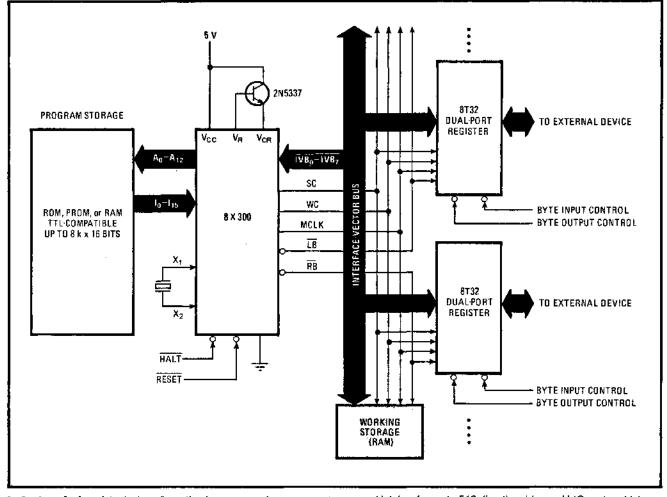

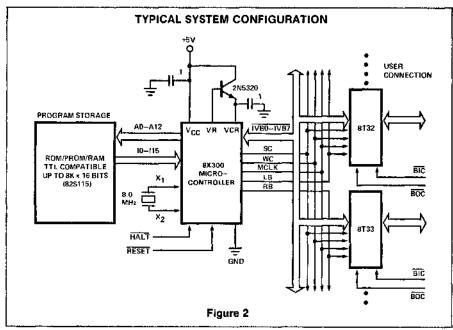

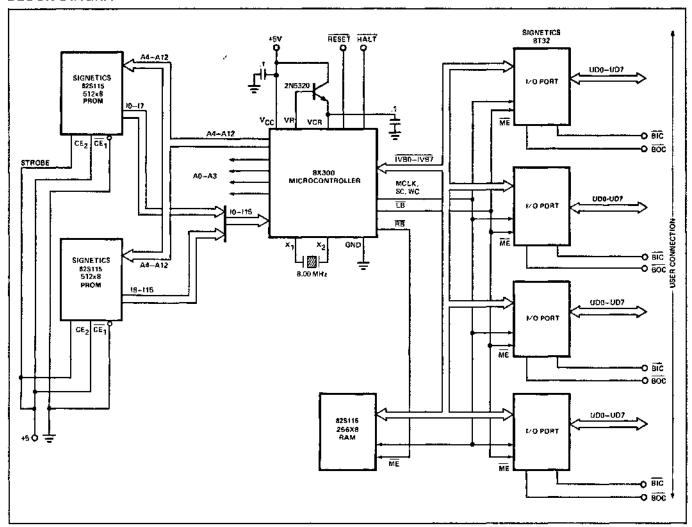

2. System design. A typical configuration has memory for program storage and latches for up to 512 directly addressed I/O ports, which are divided among left and right banks. All addresses and data are carried by the interface-vector bus and directed by control lines.

identifying the address as its own or disables itself if the addresses do not match.

The processor can directly address all of the I/O ports without the need for a decoder. The bus, and the interface-vector bytes on it, are bidirectional.

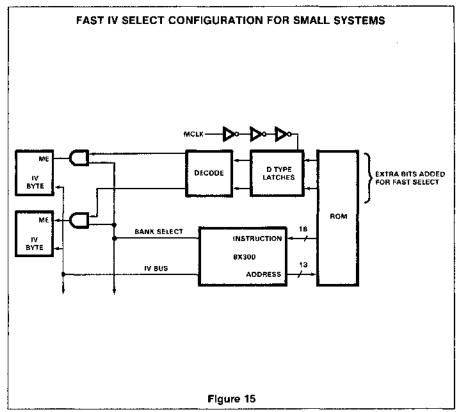

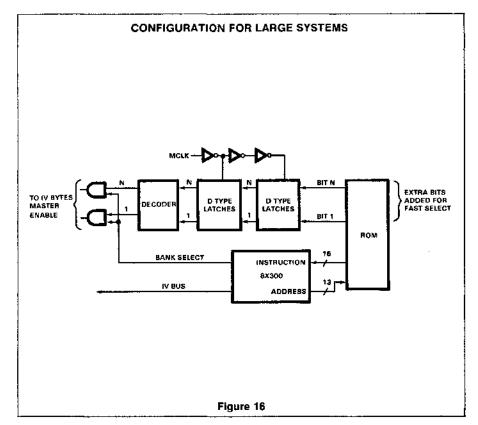

Within the processor, the interface-vector bytes are addressed in a unique fashion. Each byte has an 8-bit field-programmable address. When a given address is selected, the byte is automatically designated, and the 8X300 can then communicate with the 1/0 device. Moreover, once enabled, the addresses remain so until the processor changes them. This direct-addressing feature is especially convenient if a few ports are to be accessed frequently. However, if the time required for this operation is an imposition on the user, instruction memory can be extended so that the selection of ports is automatic upon instruction fetch.

In extending the memory, an extra field is appended to each instruction through an additional bus applied to each 1/0 port. The address field may be as wide as required to serve all system 1/0 ports and, if necessary, to serve memory. The address field contains two addresses, since the interface-vector bus is partitioned into right and left banks.

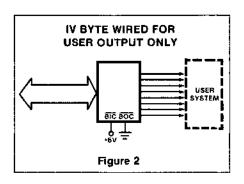

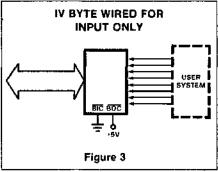

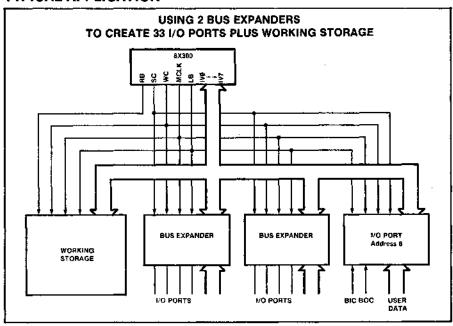

Partitioning of the interface-vector bus into two banks allows the 8X300 to select ports dynamically. The

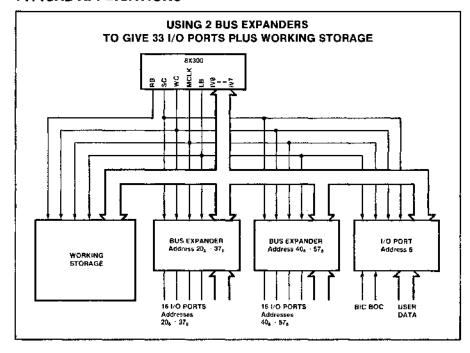

processor uses the left-bank (LB) and right-bank (RB) data-control lines as master enables for the 1/O ports, as shown in the typical interconnect scheme of Fig. 2. Any two 1/O ports can be active at the same time provided they are on opposite banks, and the ports recognize address, data, and controls only when enabled by the bank signal to which each is connected. Bank partitioning can thus be considered a ninth address bit that is alterable by the processor within an instruction, and it is this additional bit that permits direct addressing of 512, or 29, 1/O ports.

In a general data operation between two 1/0 ports, first an address is presented to one bank that enables an 1/0 port and disables all others on the bank. Next, another address is presented to the opposite bank, effecting a similar selection there. Then the operation between the two takes place.

#### Instruction cycle

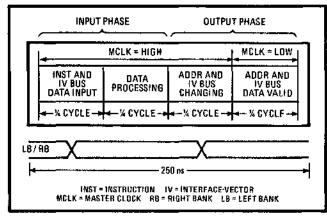

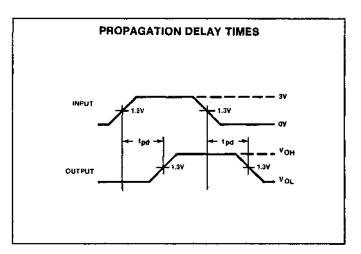

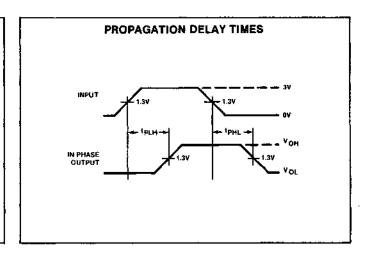

Each 8X300 operation is executed in one instruction cycle, which is subdivided into four quarter cycles as shown in Fig. 3. The instruction address for an operation is presented at the output of the processor during the third quarter of the previous instruction cycle. If the system memory is fast enough, the instruction returns to the processor during the first quarter of the cycle in

**3.** Instruction cycle. Two I/O ports may be dynamically selected in a single cycle if they are on opposite banks. Complementary LB and RB control signals change state during first and third quarter-cycles to accept data from one port and deposit it in the other.

which it is to be executed. The decoded instruction then directs the operation of the processor throughout the cycle.

In terms of processing data, the instruction cycle may be viewed as having two halves, an input and an output phase. During the first half of the instruction cycle, data is brought into the processor and stored in an interface-vector latch. Storage is completed during the first quarter cycle, and in the next quarter cycle the data is processed through the ALU. In the second half cycle, the data is presented to the bus and finally clocked into the designated 1/0 port.

Bank selection during the input and output phases is independent. Thus data may be received from the right bank, processed, and then deposited in the left bank or vice versa, or may even be sent to and from the same bank. Bank selection during instruction cycles is specified by the instruction.

Much of the strength of the 8X300 architecture lies in the powerful instruction set that controls the processor. The instruction words, each 16 bits in length, are made up of several fields that include the operational code, the source and destination fields, and the length field.

#### Instruction fields

The contents of each field can be represented by a set of octal digits, to simplify the task of coding. These digits have a direct relation to the specific operations that the data undergoes in its travel along the 8X300's internal data paths. The op code for addition, for example, is 01. In an operation between two 1/0 ports, the first of the source field's two digits specifies the bank and the second prescribes the number of bits to be rotated to the right. Similarly, the first digit of the destination field again specifies a bank, while the second digit prescribes the number of bits to be shifted. The length field specifies the number of bits to be accepted for operation in the ALU.

The capabilities of the 8X300 are such that it can, with few additional devices, perform all the functions required of an intelligent terminal. Whereas a typical system of this kind is constructed from many small- or medium-scale-integrated circuits for the control portion

of the terminal—cathode-ray-tube display, dot-matrix graphics, keyboard data entry, and host or mass-storage interface—and a microprocessor for the intelligence portion—data manipulation and number crunching—the 8X300 performs most of both the control and intelligence functions. The result is a system with fewer parts and far more capabilities for the money.

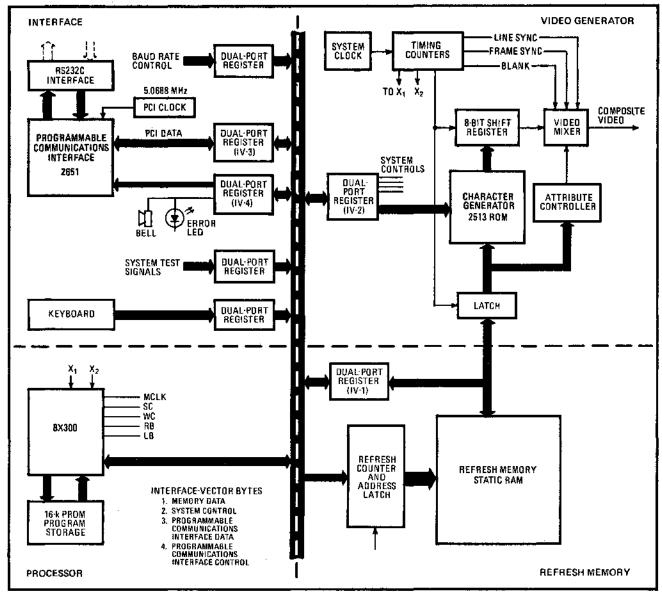

#### Intelligent terminal

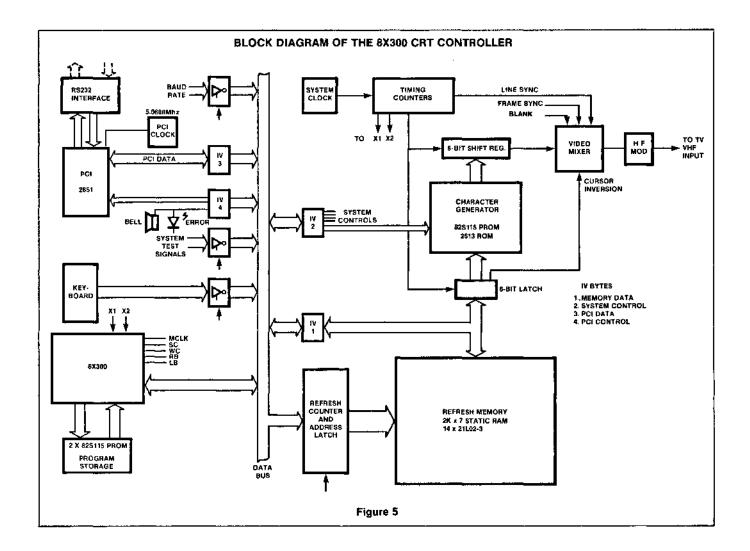

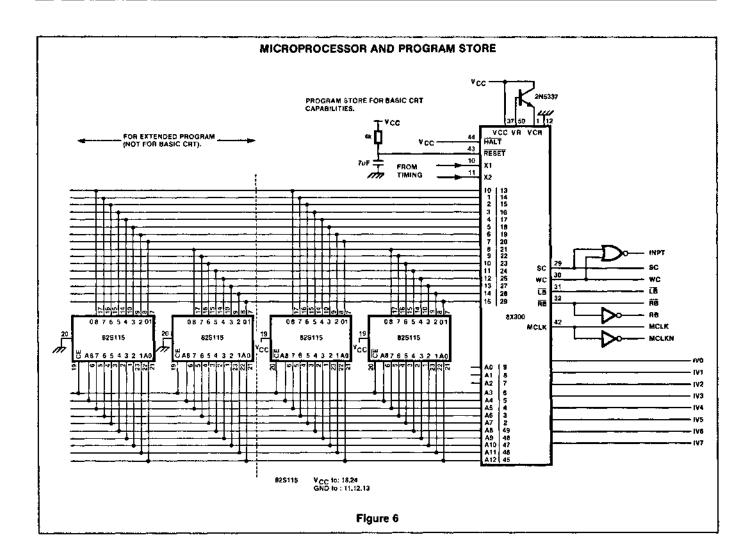

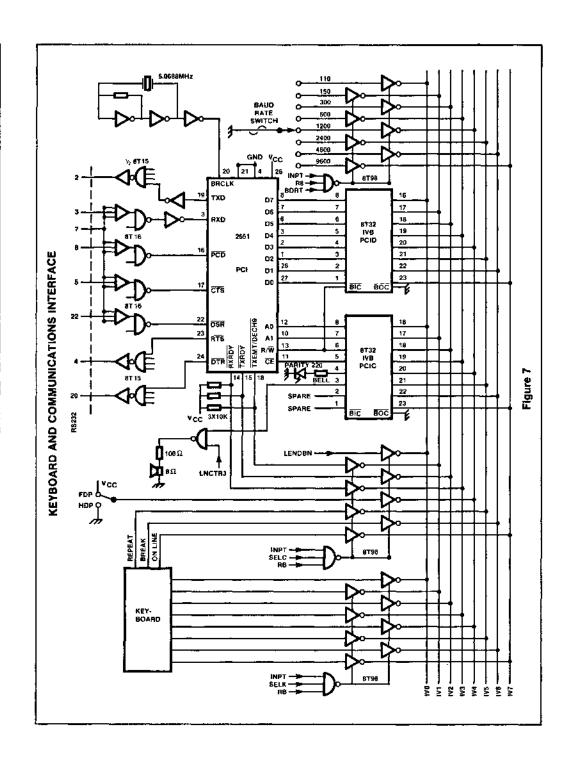

The 8X300-based intelligent terminal depicted in Fig. 4 consists of four major sections. First is the interface section, which implements the standard RS-232C interface with the host or main-data storage. The Signetics 2651 programmable communications interface performs the serial-parallel data interconversion for byte processing by the 8X300 and for display-refresh memory. The interface section includes a keyboard that is scanned by the processor for operator inputs.

The second major section comprises the video circuitry that generates all pixel, character, and line timing, as well as the composite video signal. This circuitry also supplies signals to the refresh-memory address counter for proper timing of character codes and attributes—blinking, reverse video, and so on. Synchronization, blanking, video, and attribute signals are then summed in the video mixer to produce the signal for driving standard monitors.

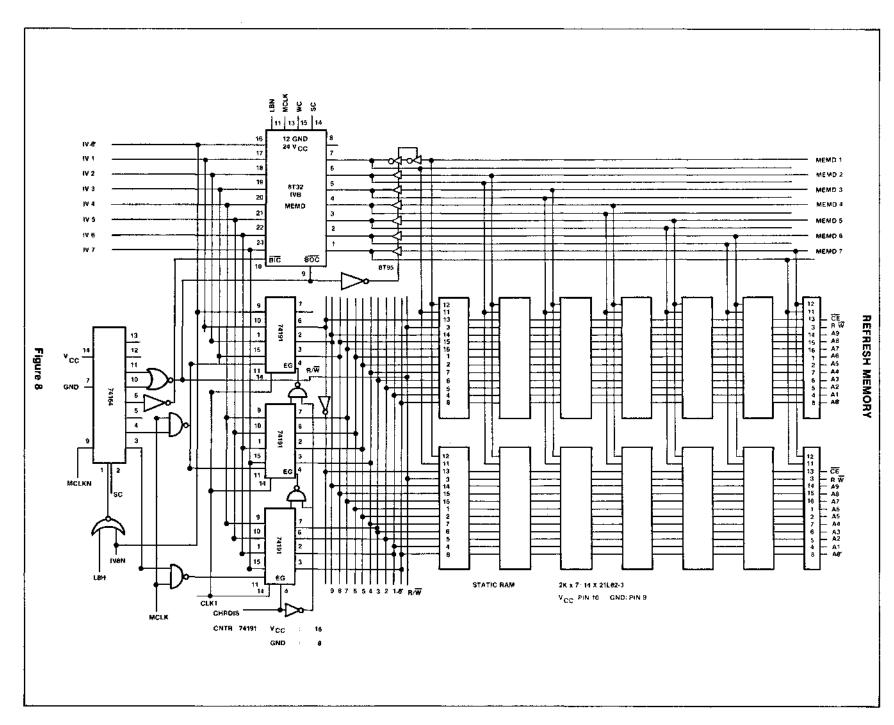

The third section, the refresh memory, stores the characters to be displayed on the screen. Its characters are addressed under control of the video-generator circuitry. The circuitry also provides for timing and control to facilitate interleaved access to the memory by the 8X300 processor. Interleaving permits the processor to examine or modify the refresh memory without disturbing the on-screen display or the video-refresh process.

#### The processor's role

The final section is the processor, the terminal's intelligence center. It performs both the executive control—managing the other three sections—and the data-processing function required by the terminal.

Since the 8X300 controls the refresh memory and video-generator sections and thus provides the timing for each frame, all frame-related features, such as scrolling and command-scanning, can be easily implemented. But most important, the processor also performs all the data manipulations—the intelligence within the terminal. The processor may accept input data from the host or the keyboard and can then present the data in proper format by means of the CRT display. Information may be entered or modified by the user and then returned to the host after the essential data items have been extracted from the refresh-memory file. This process, tailored to the user's needs, may be accomplished fully by the 8X300 microprocessor in firmware.

The basic control program, including keyboard scan, RS-232C interface service, edit, scroll, cursor, and so forth, requires only 502 words of program storage. Thus the entire terminal can be coded with two 4,096-bit programmable read-only memories. The balance of parts for the entire terminal hardware include the 2651

**4. Intelligent terminal.** The 8X300 builds an intelligent terminal that, with a total of about only 40 devices, is low in cost while high in capabilities. Included in the terminal are RS-232C interfacing, keyboard scanning, character generation with attributes, and fully interleaved refresh memory. The processor manages the other three sections and adds intelligence in data handling and number crunching.

programmable interface chip, the random-access memory for display refresh, a field-programmable logic array, and several low-power Schottky components, in addition to the 8X300. The use of about only 40 medium- and large-scale-integrated parts to construct the complete system contrasts with the over 110 small-and medium-scale-integrated components needed at present to build dumb terminals.

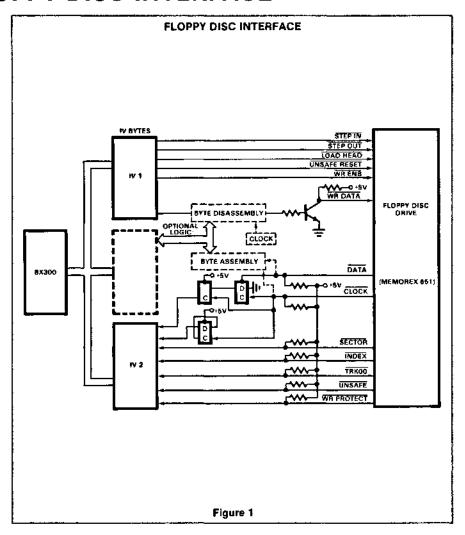

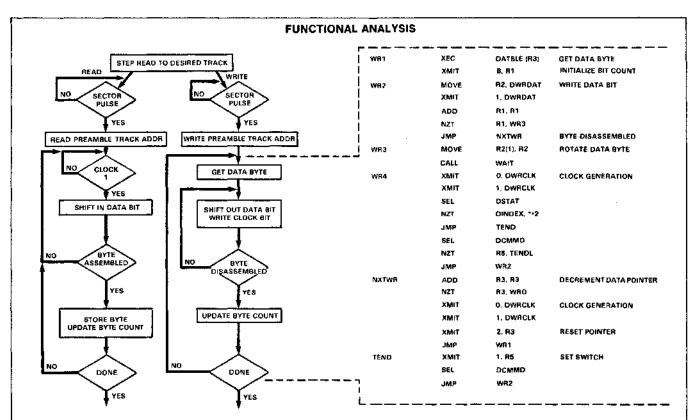

#### Floppy controller

The 8X300 can be used in a very practical floppy-disk controller circuit that has few parts and offers highly reliable control and data transfer and complete interfacing with the host processor. The processor's high speed enables it to handle any density—single, dual, and quad formats. With only minor firmware changes, a single hardware configuration can accommodate all popular disk drives and a variety of host processors.

What is more, it can do so within a single operating system—all that is needed is to switch from one set of firmware to another.

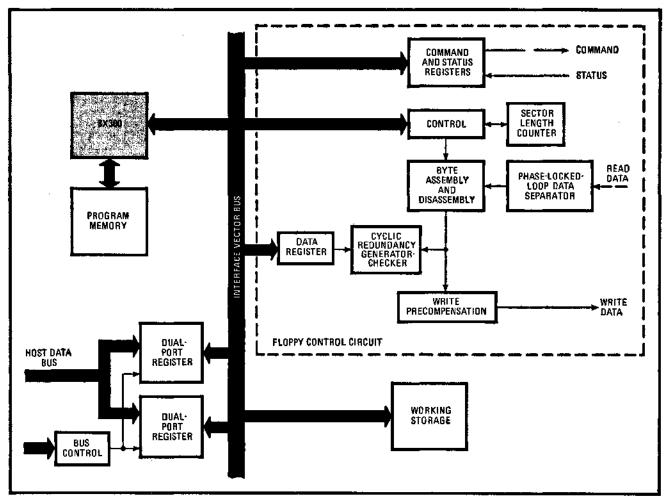

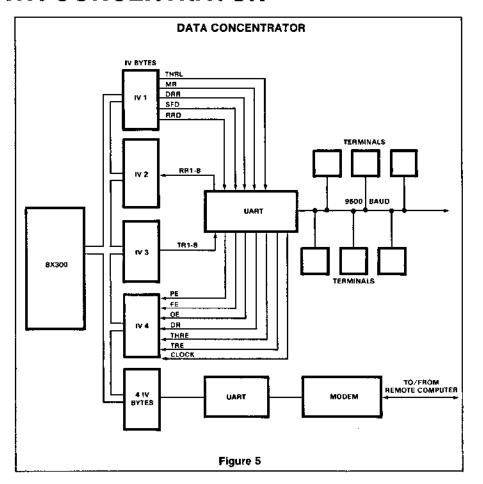

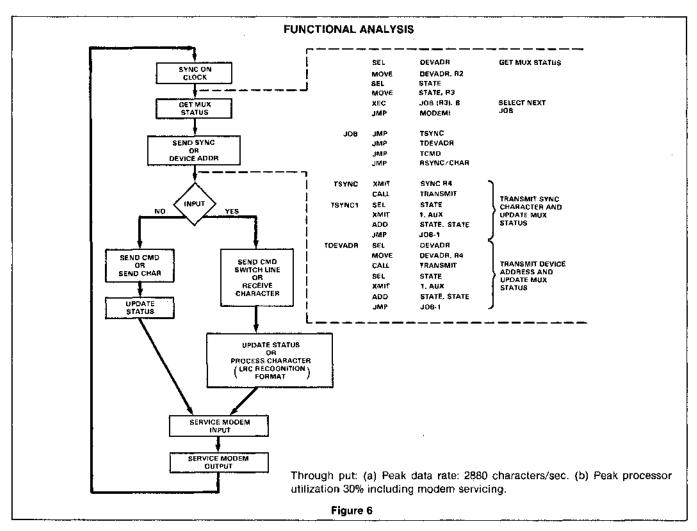

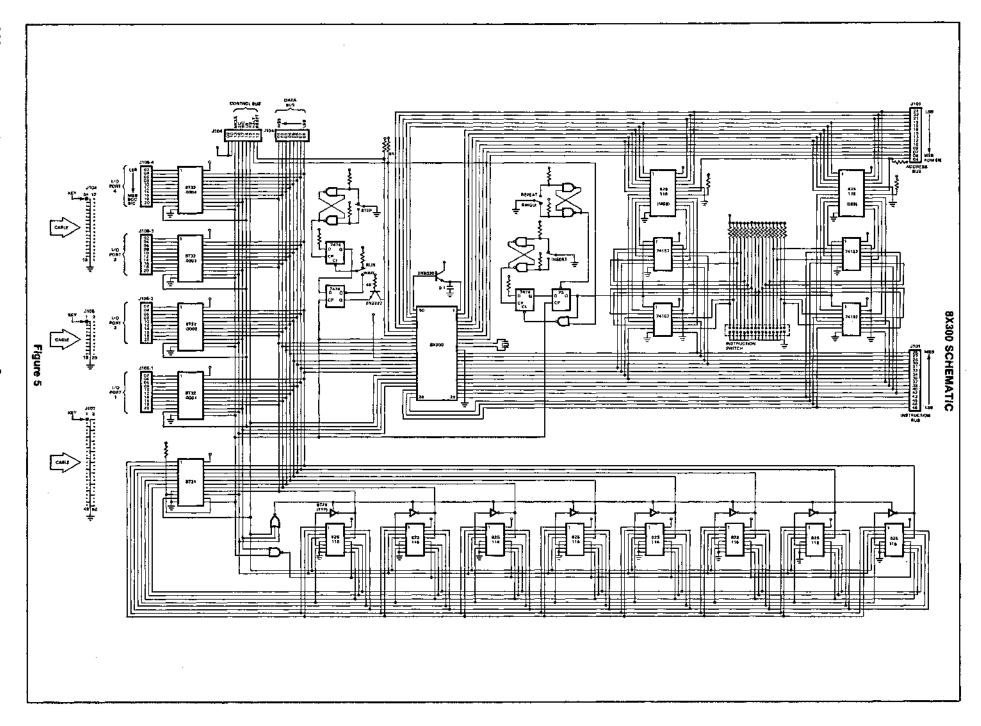

The floppy-disk controller, shown in Fig. 5, has basically two major functional parts, plus minor support functions. The two major sections are the processor and the control circuit.

The 8X300 communicates with the surrounding circuits through the interface-vector bus and controls the disk drives through command and status registers. Operating efficiency is high because selected control and status bits share the same bidirectional 1/0 register, allowing both polling (status monitoring) and command to take place in as short a time as 250 ns. The processor's high speed allows simultaneous control of several disk drives for operations such as overlap seeks, where one drive is accessing while another reads or writes data. The 8X300's limits are reached only during tight-loop data

5. Floppy-disk controller. High performance of the 8X300 allows it to effectively control a floppy-disk drive. The processor not only handles track and sector addressing but actually oversees data transfer. It also provides interfacing with the working store or directly with the host.

transfers that have to be extremely fast, but since these periods are very short, they present no significant system delays.

The 8X300 builds reliability into the disk operations by overseeing the actual data transfer, in addition to positioning the read/write head. The intelligence of the processor can be used to reread data after it has been written or even to mask out bad tracks that fail to read correctly after, say, 10 rewrites.

#### Efficient operation

Registers within the 8X300 monitor the track and sector addresses, making seeks and sector accesses highly efficient. In setting up the data transfers, the 8X300 monitors both interleaved data on the disk and the system clock for address-mark detection; it then examines and moves data a byte at a time once the controller circuit has been synchronized with the byte boundaries. Under control of the processor, disk data may be transferred to working storage (which can interface directly with the processor bus) for subsequent transfer to the host or, if it can be accommodated, transferred immediately to the host.

Very little external logic is needed for direct-memoryaccess interfacing between the 8X300 and the host. Transfer of data, commands, and status takes place through eight bidirectional 1/0 ports that are compatible with transistor-transistor logic and are supplemented with additional logic for direct connection to the host. The protocol is established in processor microprogramming, which may be conveniently altered for a variety of host types. Total program size for disk control and interfacing the 8X300 with the host processor is less than 800 instructions.

The other major section, the control circuit, has the hardware, which does a better job of recovering data from the disk than microprocessor software could. Functions include phase-locked-loop data separation, cyclic redundancy generating and checking, data-byte assembly and disassembly, and precompensation for widening the write pulses applied to the disk. These circuit functions, under control of the 8X300, can easily be instructed to operate for either single or dual recording densities, and the system can be expanded to handle most types of quad-density encoding.

Counting the control circuit as two LSI devices, the entire floppy-disk controller can be built from about 12 components. The system is complete in that it not only controls the access of disk data, but also provides the interface between any host and any off-the-shelf floppy-disk drive, and monitors and checks data transfer for ultimate reliability.

MICROCONTROLLER 8X300

8X300-I

#### DESCRIPTION

The Signetics 8X300 Microcontroller is a monolithic, high-speed microprocessor implemented with bipolar Schottky technology. As the central processing unit, CPU, it allows 16-bit instructions to be fetched, decoded and executed in 250ns. A 250ns instruction cycle requires maximum memory access of 65ns, and maximum I/O device access of 35ns.

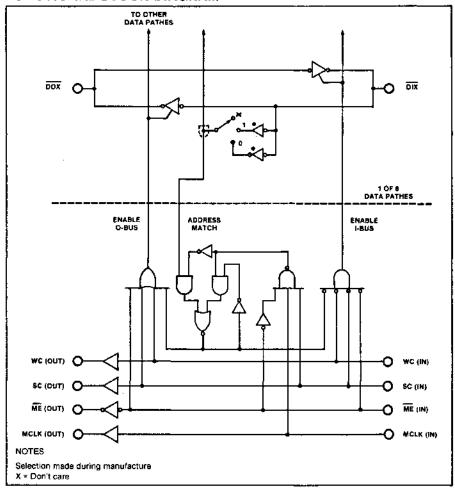

Microcontroller instructions operate on 8-bit, parallel data. Logic is distributed along the data path within the Microcontroller. Input data can be rotated and masked before being subject to an arithmetic or logical operation; and output data can be shifted and merged with the input data, before being output to external logic. This allows 1-to 8-bit I/O and data memory fields to be accessed and processed in a single instruction cycle.

#### **PROGRAM STORAGE INTERFACE**

Program Storage is typically connected to the A0-A12 (A12 is least significant bit) and I0-I15 signal lines. An address output on A0-A12 identifies one 16-bit instruction word in program storage. The instruction word is subsequently input on I0-I15 and defines the Microcontroller operations which are to follow.

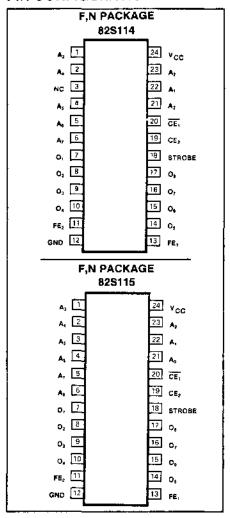

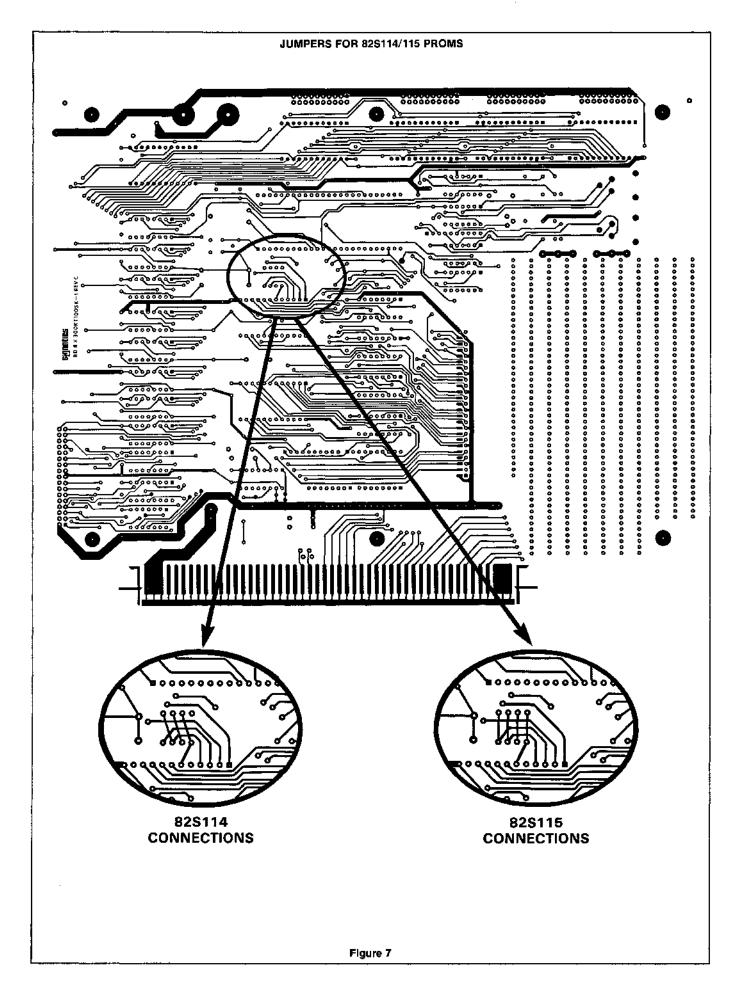

The Signetics 82S115 PROM, or any TTL compatible memory, may be used for program storage.

#### I/O DEVICES INTERFACE

An 8-bit I/O bus, called the Interface Vector (IV) data bus, is used by the Microcontroller to communicate with 2 fields of I/O devices. The complementary LB and RB signals identify which field of the I/O devices is selected.

Both I/O data and I/O address information can be output on the IV bus. The SC and WC signals are typically used to distinguish between I/O data and I/O address information as follows:

#### SC WC

- 1 0 I/O address is being output on IV bus

- 0 1 I/O data is being output on IV bus

- 0 0 I/O data is expected on the IV, bus, as input to the Microcontroller

- 1 1 Not generated by the Microcontrol-

The Signetics 82SXXX series RAM, and the 8T32/33 may be attached to the IV bus.

#### **FEATURES**

- 185ns instruction decode and execute delay (with Signetics 8T32/33 I/O port)

- Eight 8-bit working registers

- Single instruction access to 1-bit, 2-bit, 3bit or 8-bit field on I/O bus

- Separate instruction address, instruction, and I/O data buses

- On-chip oscillator

- Bipolar Schottky technology

- . TTL inputs and outputs

- . Tri-state output on I/O data bus

- +5 volt operation from 0° to 70°C

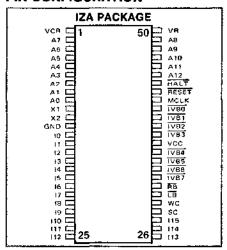

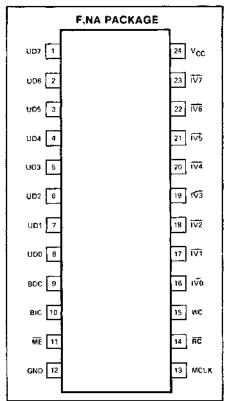

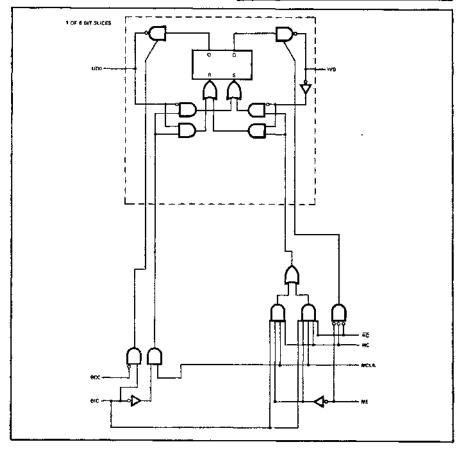

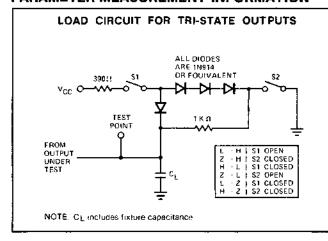

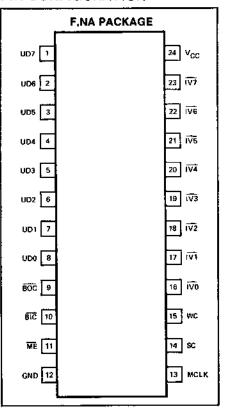

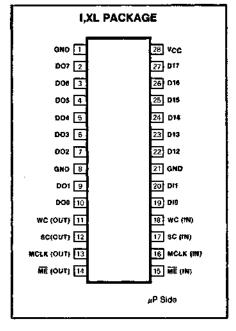

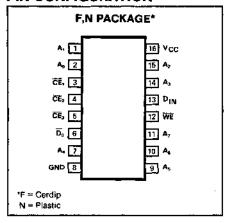

#### PIN CONFIGURATION

#### PIN DESIGNATION

| PIN             | SYMBOL            | NAME AND FUNCTION                                                                                                                                     | TYPE                      |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 2-9, 45-49      | A0-A12:           | Instruction address lines. A high level equals "1." These outputs directly address up to 8192 words of program storage. A12 is least significant bit. | Active high               |

| 13-28           | IO-115:           | Instruction lines. A high level equals "1." Receives instructions from Program Storage. I <sub>15</sub> is least significant bit.                     | Active high               |

| 33-36,<br>38-41 | IVBO-IVB7         | Interface Vector (IV) Bus. A low level equals "1." Bidirectional tri-state lines to communicate with I/O devices. IVB7 is least significant bit.      | Three-state<br>Active low |

| 42              | MCLK:             | Master Clock. Output to clock I/O devices, and/or provide synchronization for external logic                                                          | Active high               |

| 30              | WC:               | Write Command. High level output indicates data is being output on the IV Bus.                                                                        | Active high               |

| 29              | SC:               | Select Command. High level output indicates that an address is being output on the IV Bus.                                                            | Active high               |

| 31              | LB:               | Left Bank. Low level output to enable one of<br>two sets of I/O devices (LB is the comple-<br>ment of RB).                                            | Active low                |

| 32              | ŘB:               | Right Bank. Low level output to enable one of two sets of I/O devices (RB is the complement of LB).                                                   | Active low                |

| 44              | HALT:             | Low level is input to stop the Microcontroller.                                                                                                       | Active low                |

| 43              | RESET:            | Low level is input to initialize the Microcontroller.                                                                                                 | Active low                |

| 10-11           | X1, X2:           | Inputs for an external frequency determining crystal. May also be interfaced to logic or test equipment.                                              |                           |

| 50              | VR                | Reference voltage to pass transistor.                                                                                                                 |                           |

| 1               | VCR               | Regulated output voltage from pass transistor.                                                                                                        |                           |

| 37              | V <sub>CC</sub> : | 5V power connection.                                                                                                                                  |                           |

| 12              | GND:              | Ground.                                                                                                                                               |                           |

8X300-F

- R1 General working register

R2 General working register

R3 General working register

R4 General working register

R5 General working register

R5 General working register

R6 General working register

R7 Summary).

- R6 General working register

R11 General working register

- AUX General working register. Contains second term for arithmetic or logical operations.

- OVF The least-significant bit of this register is used to reflect overflow status resulting from the most recent ADD operation (see Instruction Set Summary).

- Instruction Register (IR)

- Holds the 16-bit instruction word currently being executed.

#### Program Counter (PC)

Normally contains the address of the current instruction and is incremented to obtain the next instruction address.

#### Address Register (AR)

A 13-bit register containing the address of the current instruction.

Table 1 INTERNAL REGISTERS

#### **INSTRUCTION CYCLE**

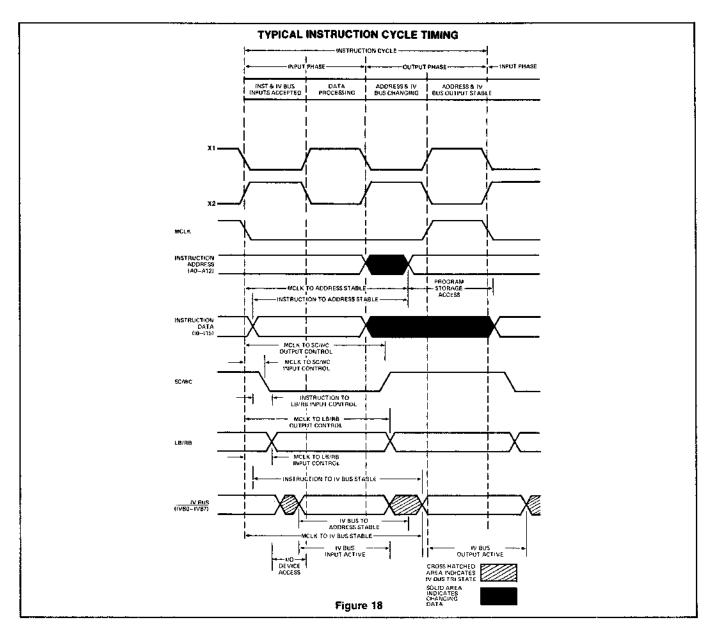

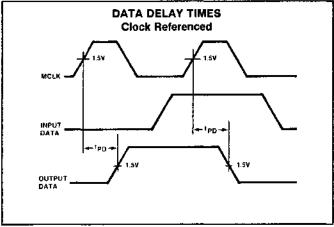

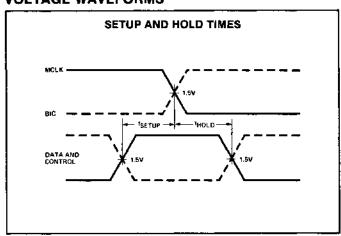

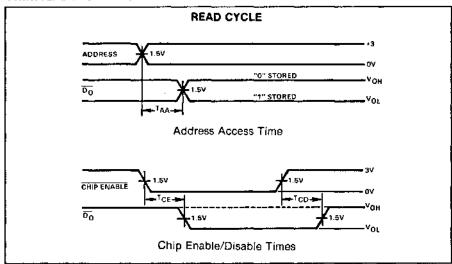

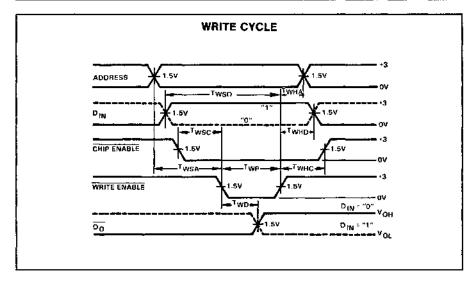

Each Microcontroller operation is executed in 1 instruction cycle, which may be as short as 250ns. The Microcontroller generates MCLK to synchronize external logic to the instruction cycle. Instruction cycles are subdivided into quarter cycles. MCLK is an output during the last quarter cycle.

During the third quarter cycle of an instruction, an address is output on A0-A12, identifying the location in program storage of the next instruction word. This instruction word defines the next instruction, which must be input on I0-I15 during the first quarter cycle of the next instruction cycle (see Table 2).

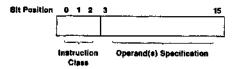

#### Instruction Set Summary

The 16-bit instruction word input on 10-115 is decoded by the instruction decode logic to implement events that are to occur during the remainder of the instruction cycle. Generally the 16-bit instruction word is decoded as follows:

A detailed usage of the 13 "operand(s) specification" bits is given in following sections.

Three operation code bits allow for 8 instruction classes. The 8 instruction classes are summarized in Table 3. Each entry is referred to as an "instruction class" because the unique architecture of the Interpreter allows a number of powerful variations to be specified by the 13 operand (s) specification bits. A complete description of instruction formats and some instruction examples are provided in the Microprocessor Applications manual.

#### **Data Processing**

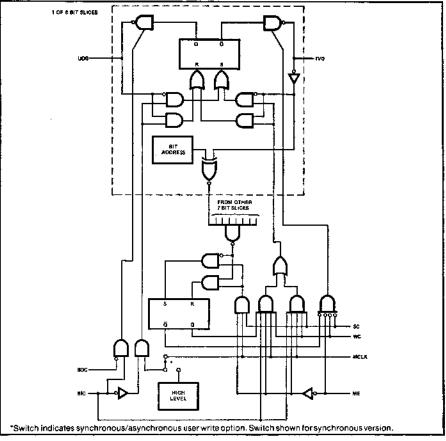

The Microcontroller architecture includes eight 8-bit working registers, an arithmetic logic unit (ALU), an overflow register, and the 8-bit IV Bus. Internal 8-bit data paths connect the registers and IV Bus to the ALU inputs, and the ALU output to the registers and IV Bus. Data processing logic is distributed along these internal 8-bit data paths. Rotate and mask logic precedes the ALU on the data entry path. Shift and merge logic follows the ALU on the data output path. All 4 sets of logic can operate on 8 data bits in a single instruction cycle (See Figure 1).

When less than 8 bits of data are specified for output to the IV bus by the ALU, the data field (shifted if necessary) is inserted into the prior contents of the IV bus latches. The

| INSTRUCTION<br>AND IV<br>BUS DATA<br>INPUT | DATA        | ADDRESS<br>AND IV<br>BUS CHANGING | ADDRESS AND<br>IV BUS DATA<br>VALID<br>MCLK=HIGH |

|--------------------------------------------|-------------|-----------------------------------|--------------------------------------------------|

| • ¼ cycle →                                | ← ¼ cycle → | ← ¼ cycle →                       | ← ¼ cycle →                                      |

Table 2 INSTRUCTION CYCLE

IV bus latches contain data input at the start of an instruction. This data in the IV bus latches will be specified in the instruction as a) IV bus source data or b) data from an automatic read when the IV bus is specified as a destination. Therefore, IV bus bit positions outside an inserted bit field are unmodified.

#### Data Addressing

Sources and destinations of data are specified using a 5-bit octal number. The source and/or destination of data to be operated upon is specified in a single instruction word.

Referring to Figure 1, the Auxiliary register (address 00) is the implied source of the second argument for ADD, AND or XOR operations.

IVL and IVR are write-only registers used only as a destination. They have addresses and are treated as registers, but in reality they do not exist. When IVL is specified as a destination or the D field = 20-27<sub>8</sub>, then LB= 'tow', RB= 'high' are generated; when IVR is specified as a destination or the D field = 30-37<sub>8</sub>, then RB= low, LB= 'high' are generated.

When IVL or IVR is specified as the destination in an instruction, SC is also activated and data is placed on the IV bus, If IVL or IVR is specified as a source of data, the source data is all zeroes.

### INSTRUCTION SEQUENCE CONTROL

The Address Register and Program Counter are used to generate addresses for accessing an instruction. The Address Register is used to form the instruction address, and in all but 3 instructions (XEC, NZT, and JMP) the address is copied into the Program Counter. The instruction address is formed in 1 of 3 ways:

- For all instructions but the JMP, XEC, and a satisfied NZT, the Program Counter is incremented by 1 and placed in the Address Register.

- For the JMP instruction, the full 13-bit address field from the JMP instruction is placed into the Address Register and copied into the Program Counter.

- For the XEC and NZT instructions, the high order 5- or 8-bits of the Program Counter are combined with 8- or 5lower-order bits of ALU output (XEC or NZT) and placed in the Address Register. For the NZT instruction, it is also copied into the Program Counter.

MICROCONTROLLER 8X300

8X300-I

#### **INSTRUCTION SET**

The 8X300 Microcontroller has a repertoire of 8 instruction classes which allow the user to test input status lines, set or reset output control lines, and perform high speed input/output data transfers. All instructions are 16 bits in length and each is tetched, decoded and executed in 250ns.

Data is respresented as an 8-bit byte; bit positions are numbered from left to right, with the least significant bit in position 7.

Within the 8X300, all operations are performed on 8-bit bytes. Arithmetic operations use 8-bit, unsigned 2's complement arithmetic.

#### **INSTRUCTION FORMATS**

The general 8X300 instruction format is:

| 0 | 1        | 2       | 3 | 4 | 5 | 6 | 7 | 8 | 9  | 10  | 11  | 12  | 13 | 14 | 15 |

|---|----------|---------|---|---|---|---|---|---|----|-----|-----|-----|----|----|----|

| 0 | Op<br>Od | )<br>le |   |   | • |   |   | 0 | pe | ran | d(s | \$} |    |    |    |

All instructions are specified by a 3-bit Operation (Op Code) field. The operand may consist of the following fields: Source

(S) field, Destination (D) field, Rotate/ Length (R/L) field, Immediate (I) field, or (Program Storage) Address (A) field.

The instructions are divided into 5 format types, based on the Op Code and the Operand(s), as shown in Figure 3.

|                                          | INSTRUCTION FORMATS                                               |  |  |  |  |  |  |

|------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| by a 3-bit                               | DPERATIONS<br>(REGISTER TO REGISTER)<br>MOVE AND<br>ADD XOR       |  |  |  |  |  |  |

| ds: Source                               | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                             |  |  |  |  |  |  |

|                                          | OP S R                                                            |  |  |  |  |  |  |

| s<br>                                    | Type \$                                                           |  |  |  |  |  |  |

| both are                                 | (REGISTER TO I/O, I/O TO REGISTER, I/O TO I/O)  MOVE ADD  AND XOR |  |  |  |  |  |  |

| nen R/L                                  | 0 1 2 3 4 5 5 7 8 9 10 11 12 13 14 15                             |  |  |  |  |  |  |

| ght rotate                               | OP S (LENGTH) D                                                   |  |  |  |  |  |  |

| er specifi-                              | Type II                                                           |  |  |  |  |  |  |

|                                          | <u>OPERATIONS</u>                                                 |  |  |  |  |  |  |

|                                          | XEC XMIT*<br>NZT                                                  |  |  |  |  |  |  |

| address                                  | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                             |  |  |  |  |  |  |

| mited to                                 | OP S                                                              |  |  |  |  |  |  |

| mited to                                 | Type III                                                          |  |  |  |  |  |  |

|                                          | <u>OPERATIONS</u>                                                 |  |  |  |  |  |  |

| address<br>imited to                     | XEC XMIT <sup>4</sup><br>NZT                                      |  |  |  |  |  |  |

| <ol> <li>Other-<br/>imited to</li> </ol> | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 16                             |  |  |  |  |  |  |

| 7.                                       | OP \$ (LENGTH)                                                    |  |  |  |  |  |  |

|                                          | Type IV                                                           |  |  |  |  |  |  |

| eration is<br>by reduc-                  | OPERATIONS                                                        |  |  |  |  |  |  |

| of PC to                                 | JMP                                                               |  |  |  |  |  |  |

| nultiple of<br>Dor 256 life              | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                             |  |  |  |  |  |  |

| and add-                                 | OP A                                                              |  |  |  |  |  |  |

| t.                                       | Type V                                                            |  |  |  |  |  |  |

| the range                                | 'NOTE                                                             |  |  |  |  |  |  |

|                                          | # XMIT, S actually represents the destination                     |  |  |  |  |  |  |

|                                          | Figure 3                                                          |  |  |  |  |  |  |

|                                          |                                                                   |  |  |  |  |  |  |

| OPERATION | FORMAT | RESULT                                                                                                                                                                                                                                                                                    | NOTES                                                                                                                                                       |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVE      | 1,11   | Content of data field specified by {S, R/L} replaces data in field specified by {D, R/L.}                                                                                                                                                                                                 |                                                                                                                                                             |

| ADD       | 1,#1   | Sum of AUX and data specified by $S, R/L$ replaces data in field specified by $D, R/L$ .                                                                                                                                                                                                  | If S and D both are registers, then R/L                                                                                                                     |

| AND       | ŧ,Ħ    | Logical AND of AUX and data specified by {S, R/L} replaces data in field specified by {D, R/L.}                                                                                                                                                                                           | specifies a right rotate<br>of the register specifi-<br>ed by S.                                                                                            |

| XOR       | 1,11   | Logical exclusive OR of AUX and data specified by $\{S,R/L\}$ replaces data in field specified by $\{D,R/L.\}$                                                                                                                                                                            |                                                                                                                                                             |

| хміт      | VI,III | The literal value I replaces the data in the field specified by $\{S,L.\}$                                                                                                                                                                                                                | If S is an I/O address then I is timited to range 00-37. Otherwise I is limited to range 000-377.                                                           |

| NZT       | H1,1V  | If the data in the field specified by<br>{S, L} equals zero, perform the<br>next instruction in sequence. If the<br>data specified by {S,L} is not equal<br>to zero, execute the instruction at<br>address determined by using the lit-<br>eral I as an offset to the Program<br>Counter. | If S is an I/O address then I is limited to range 00-37. Otherwise I is limited to range 000-377.                                                           |

| XEC       | fir,iV | Perform the instruction at address determined by applying the sum of the literal I and the data specified by {S, L} as an offset to the Program Counter. If that instruction does not transfer control, the program sequence will continue from the XEC instruction location.             | The offset operation is performed by reducing the value of PC to the nearest multiple of 32 (if I = 000-377) or 256 (if I = 000-377) and adding the offset. |

| JMP       | ٧      | The address value A replaces contents of the Program Counter.                                                                                                                                                                                                                             | A limited to the range 0-177778.                                                                                                                            |

Table 3 8X300 INSTRUCTION SUMMARY

#### **INSTRUCTION FIELDS**

#### Op Code Field (3-Bit Field)

The Op Code field is used to specify 1 of 8 8X300 instructions as shown in Table 4.

| OP CODE<br>OCTAL<br>VALUE | IN   | STRUCTION      |

|---------------------------|------|----------------|

| 0                         | MOVE | S,R/L,D        |

| ] 1                       | ADD  | S,R/L,D        |

| 2                         | AND  | S,R/L,D        |

| 3                         | XOR  | S,R/L,D        |

| 4                         | XEC  | I,R/L,S or I,S |

| 5                         | NZT  | I,R/L,S or I,S |

| 6                         | хміт | I,R/L,D or I,D |

| 7                         | JMP  | A              |

Table 4 OP CODE FIELD OCTAL ASSIGNMENTS

#### \$.D Fields (5-Blt Fields)

The S and D fields specify the source and destination of data for the operation defined by the Op Code field. The Auxiliary Register is an implied second source for the instructions ADD, AND and XOR, each of which require two source fields. That is, instructions of the form.

#### ADD X, Y

imply a third operand, say Z, located in the Auxiliary Register so that the operation which takes place is actually X + Z, with the result stored in Y.

The Sand/or D fields may specify a register, or a 1 to 8-bit I/O field. S and D field value assignments in octal are shown in Table 5.

$0_8$ - $17_8$  is used to specify 1 of 7 working registers (R1-R6, R11), the Auxiliary Register, the Overflow Register, or IVL and IVR write-only registers.

| VALUE |                                       | VALUE |                                                                           |

|-------|---------------------------------------|-------|---------------------------------------------------------------------------|

| 00    | AUX-Auxiliary Register                | 10    | OVF-Overflow register-Used only                                           |

| 01    | R1                                    |       | as a source                                                               |

| 02    | R2                                    | 11    | R11                                                                       |

| 03    | R3                                    | 12    | Unassigned                                                                |

| 04    | R4                                    | 13    | Unassigned                                                                |

| 05    | R5                                    | 14    | Unassigned                                                                |

| 06    | R6                                    | 15    | Unassigned                                                                |

| 07    | IVL Register-Left Bank I/O address    | 16    | Unassigned                                                                |

|       | register. Used only as a destination. | 17    | IVR Register-Right Bank I/O address register. Used only as a destination. |

#### a. Register Specification

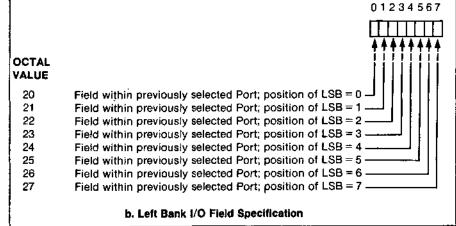

20g-27g is used to specify the least significant bit of a variable length field within the I/O Port previously selected by the IVL register. The length of the field is determined by R/L.

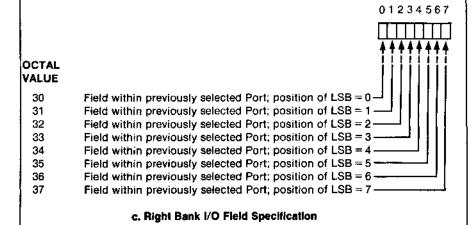

30a-37a is used to specify the least significant bit of a variable length field within the I/O Port previously selected by the IVR Register. The length of the field is determined by R/L.

Table 5 S AND D FIELD OCTAL ASSIGNMENTS

Migrocontroller

8X300-1

#### R/L Field (3-Bit Field)

The R/L field performs one of two functions, specifying either a field length (L) or a right rotation (R). The function it specifies for a given instruction depends upon the contents of the S and D fields:

- A. When both S and D specify registers, the R/L field is used to specify a right rotation of the data specified by the S field. (Rotation occurs on the bus and not in the source register.) The register source data is right rotated within one instruction cycle time independent of the number of bit positions specified in the R/L field.

- B. When either or both the S and D fields specify a variable length I/O data field, the R/L field is used to specify the length of that data field.

- C. R/L field assignments are shown in Table 6.

| R/L FIELD<br>OCTAL<br>VALUE | SPECIFICATION         |  |  |  |  |

|-----------------------------|-----------------------|--|--|--|--|

| 0                           | Field Length = 8 Bits |  |  |  |  |

| 1 1                         | Field Length = 1 Bit  |  |  |  |  |

| 2                           | Field Length = 2 Bits |  |  |  |  |

| 3                           | Field Length = 3 Bits |  |  |  |  |

| 4                           | Field Length = 4 Bits |  |  |  |  |

| 5                           | Field Length = 5 Bits |  |  |  |  |

| 6                           | Field Length = 6 Bits |  |  |  |  |

| 7                           | Field Length = 7 Bits |  |  |  |  |

Table 6 R/L FIELD OCTAL ASSIGNMENTS

#### I Field (5/8-Blt Fleld)

The I field is used to load a literal value (contained in the instruction) into a register, or a variable I/O data field, or to modify the low order bits of the Program Counter.

The length of the I field is based on the S field in XEC, NZT, and XMIT instructions, as follows:

- A. When S specifies a register, the literal I is an 8bit field (Type III format).

- B. When S specifies variable I/O data field, the literal I is a 5-bit field (Type tV format).

#### A Field (13-Bit Field)

The A field is a 13-bit Program Storage address field. This allows the 8X300 to directly address 8192 instructions.

#### REGISTER OPERATIONS

When a register is specified as the source and a variable I/O data field is specified as the destination, the low order bits of the results of the instructions MOVE, ADD, XOR are merged with the original destination data.

When an I/O data field of 1 to 8 bits is specified as the source, and a register as the destination, the 8-bit result of the operations MOVE, ADD, AND, XOR is stored in the register. The operations ADD, AND, XOR actually use the I/O data field (1 to 8 bits) with leading zeros to obtain 8-bit source data for use with the 8-bit AUX data during the operation.

IVL and IVR are write-only pseudo registers, and therefore can be specified as destination fields only. Operations involving IVL and IVR as sources are not possible. For example, it is not possible to increment IVR or IVL in a single instruction, and the contents of IVL or IVR cannot be transferred to a working register, or I/O Port.

The OVF (Overflow) Register can only be used as a source field; it is set or reset *only* by the ADD instruction.

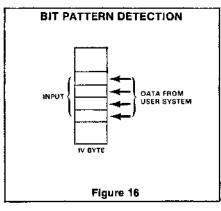

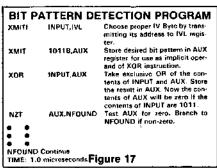

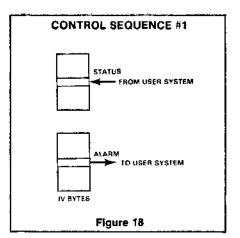

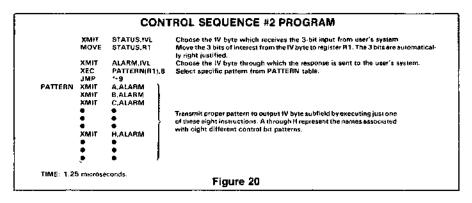

### ADDRESSING DATA ON THE INTERFACE VECTOR

I/O data fields are implemented via general purpose 8-bit I/O registers called Interface Vector (IV) Bytes. The IV registers serve to select IV bytes. In order for an instruction to access (read or write) an I/O data field, the address must be output to the IVL or IVR registers.

Thus, two instructions are required to operate on an Interface Vector byte.

XMIT ADDRESS, IVL MOVE LB, RB

Each of the two IV registers (IVL and IVR) may be set to select an IV byte, therefore two I/O ports may be active at one time—one on the Right Bank (IVR) and one on the Left Bank (IVL). Data may be input and output in one instruction following the selection of IV bytes:

XMIT ADDRESS1, IVL XMIT ADDRESS2, IVR ADD LB. RB

Once the IV byte is selected (addressed) it will remain selected until another address is output to the same IV register. Since an IV register (IVL, IVR) can be used only as a destination field of an instruction, any instruction sending data to IVL or IVR can be used to select an IV byte.

From the user's standpoint, however, all IV byte outputs can be read by an external device regardless of whether they are selected or not.

The address range of IVL and IVR is 0-255<sub>10</sub>.

#### INSTRUCTION DESCRIPTIONS

The following instruction descriptions employ MCCAP (the 8X300 Cross Assembly Program) programming notation. This notation varies somewhat from the instruction descriptions provided in Tables 3 through 5. Thus, for example, explicit L field definition, as shown in Table 3 and Table 4 is not required by MCCAP instructions; MCCAP can create appropriate variable field addresses from information contained in Data Declaration statements which may be provided by the programmed at the beginning of his program.

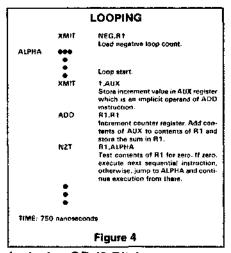

The 8X300 instruction set is described below with examples shown in Figures 4 through 11.

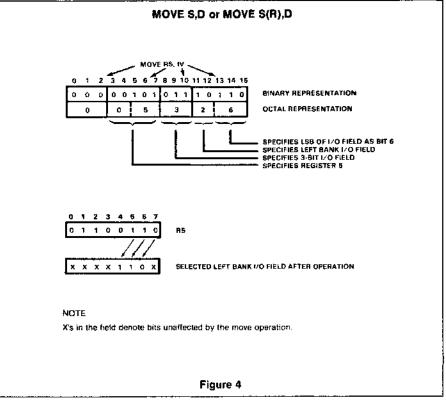

MOVE S,D or MOVE S(R),D

Format: Type I, Type II Operation: (S)→(D)

Description

Move data. The contents of S are transferred to D; the contents of S are unaffected. If both S and D are registers, R/L specifies a right rotate of the source data before the move. Otherwise, R/L specifies the length of the source and/or destination I/O data field. If the MOVE is between Left Bank and Right Bank I/O field, an 8-bit field must always be moved.

#### Example

Store the least significant 3 bits of register 5 (R5) in bits 4, 5 and 6 of the I/O Port previously addressed by the IVL register. See Figure 4.

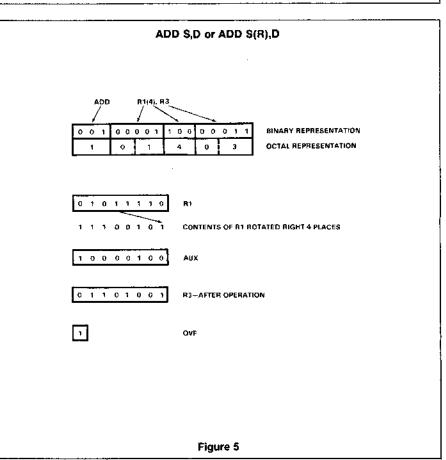

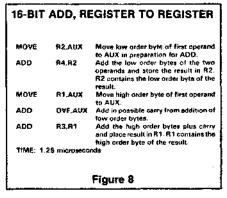

### ADD S,D or ADD S(R),D

Format: Type I, Type II

Operation: (S) + (AUX)—→D

Carry—→OVF

#### Description

Unsigned 2's complement 8-bit addition. The contents of S are added to the contents of the Auxiliary Register. The result is stored in D; OVF is set to the value of the carry. If both S and D are registers, R/L specifies a right rotate of the source (S) data before the operation. Otherwise, R/L specifies the length of the source and/or destination I/O data fields. S and AUX are unaffected unless specified as the destination.

#### Example

Add the contents of R1 rotated 4 places to AUX and store the result in R3. See Figure 5.

8X300

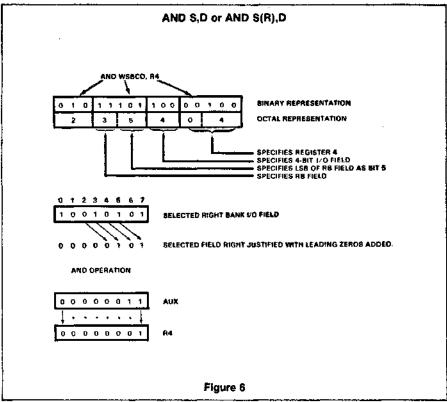

### AND S,D or AND S(R),D

Format: Type I, Type II

Operation: (S) ∧ (AUX)→D

Description

Logical AND. The AND of the source field and the Auxiliary Register is stored into the destination. If both S and D are registers, R/L specifies a right rotate of the source (S) data before the AND operation. Otherwise R/L specifies the length of the source and/or destination I/O data fields. S and AUX are unaffected unless specified as a destination.

#### Example

Store the AND of the selected right bank I/O field and AUX in R4. The right bank data field is called WSBCD and is 4 bits long and located in bits 2, 3, 4 and 5. See Figure 6.

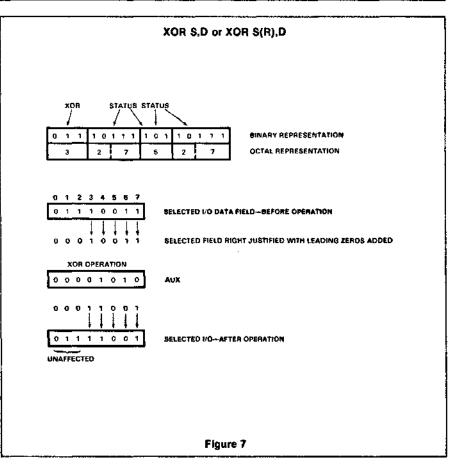

### XOR S,D or XOR S(R),D

Format: Type I, Type II

Operation: (S) ⊕ (AUX) → D

Description

Exclusive-OR. The Exclusive-OR of the source field and the Auxiliary Register is stored in the destination. If both S and D are registers, R/L specifies a right rotate of the source (S) data before the XOR operation. Otherwise R/L specifies the length of the source and/or destination I/O data fields. S and AUX are unaffected unless specified as a destination.

#### Example

Replace the selected f/O data field with the XOR of the field and AUX. The I/O data field is called STATUS and is 5 bits in length and located in bits 3, 4, 5, 6 and 7 of left bank. See Figure 7.

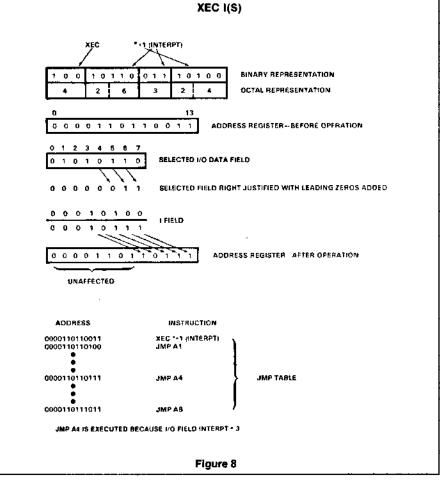

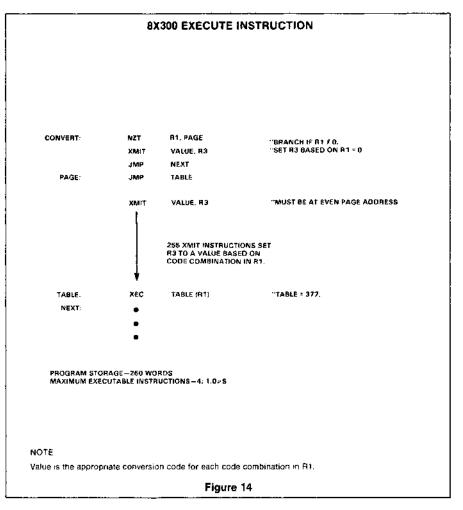

#### XEC I(S)

#### Format: Type III, Type IV

#### Operation

Execute instruction at the address specified by the Address Register with lower 5 or 8 bits replaced by (S) + I.

#### Description

Execute the instruction at the address determined by replacing the low order bits of the Address Register (AR) with the low order bits of the sum of the literal I and the contents of the source field. If S is a register, the low order 8 bits of AR are replaced; if S is an I/O data field, the low order 5 bits of AR are replaced, resulting in an execute range of 256 and 32 respectively. The Program Counter is not affected unless the instruction executed is a JMP or NZT (whose branch is taken).

#### Example

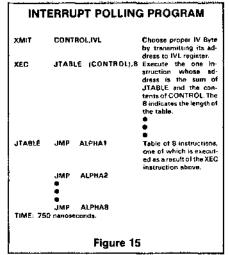

Execute one of n JMPs in a table of JMP instructions determined by the value of the selected I/O data field on the left bank. The table follows immediately after the XEC instruction and the I/O field is called INTERPT and is a 3-bit field located in bits 4,5 and 6. See Figure 8.

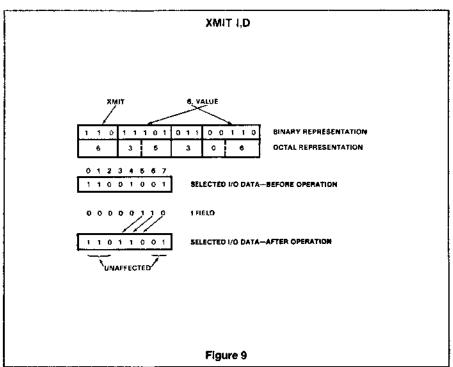

#### XMIT I,D

Format: Type III, Type IV

Operation: I+ (D)

#### Description

Transmit literal. The literal field lis stored in D. If D is a register, an 8-bit field is transferred; if D is an I/O data field, up to a 5-bit field is transferred.

#### Example

Store the bit pattern 110 in the selected I/O data field on the right bank. The field name is VALUE and is located in bits 3, 4 and 5. See Figure 9.

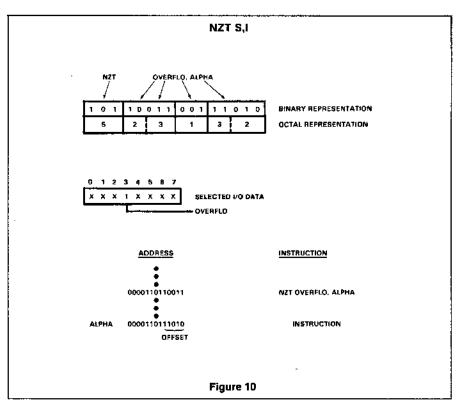

#### NZT S,I

#### Format: Type III, Type IV

#### Operation:

Non-Zero Transfer. If  $(S) \neq 0$ , PC offset by I  $\rightarrow$  PC; otherwise PC + 1  $\rightarrow$  PC.

#### Description

If the data specified by the S field is non-zero, replace the low order bits of the Program Counter with I. Otherwise, processing continues with the next instruction in sequence. If S is a register, the low order 8 bits of the PC are replaced; if S is an I/O data field, the low order 5 bits of the PC are replaced, resulting in an NZT range of 256 and 32 respectively.

#### Example

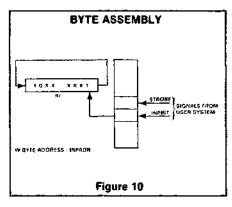

Jump to Program Address ALPHA if the selected left bank I/O field is non-zero. The field name is OVERFLO and it is a 1-bit field located in bit 3. See Figure 10.

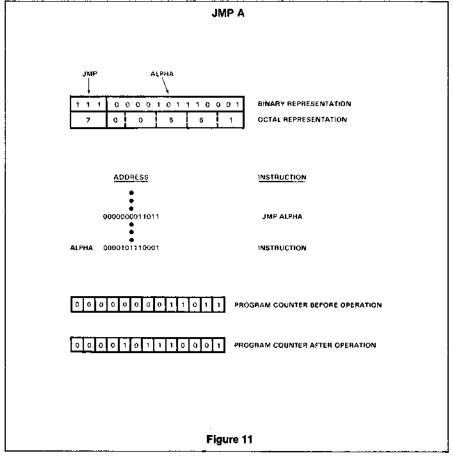

#### JMP A

Format: Type V

Operation: A - PC

#### Description

The literal value A is placed in the Program Counter and Address Register, and processing continues at location A. A has a range of 0-177778 (0-8191).

#### Example

Jump to location ALPHA (0000101110001). See Figure 11.

MICROCONTROLLER 8X300

8X300-I

### SYSTEM DESIGN USING THE 8X300 MICROCONTROLLER

Designing hardware around the 8X300 Interpreter reduces to selecting a program storage devicer (ROM, PROM, etc.), selecting I/O devices (IV byte, multiplexers, RAM, etc.), selecting clock mode (system driven or crystal controlled) and interfacing the Microcontroller to these components.

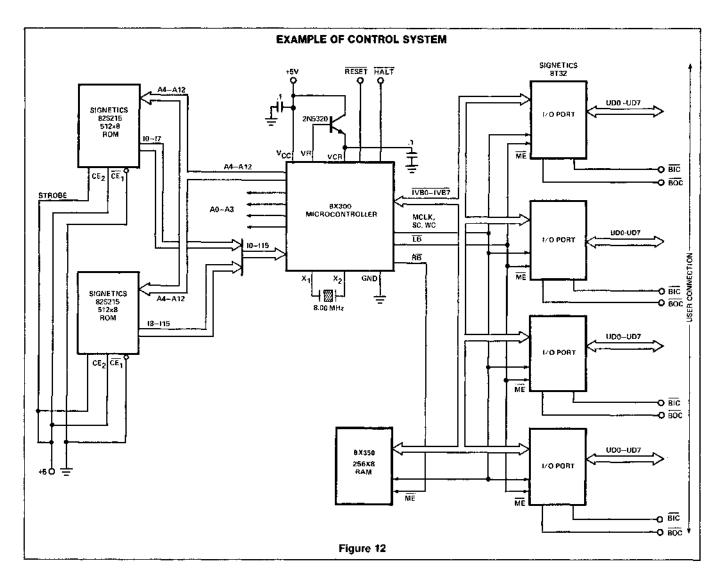

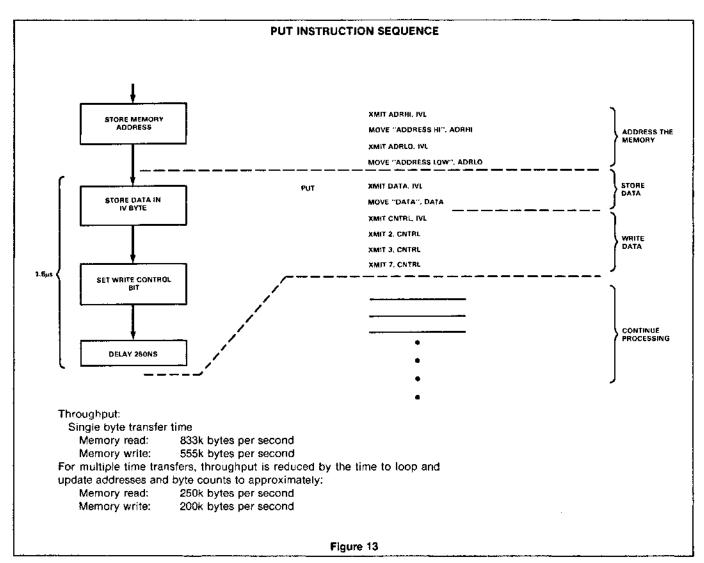

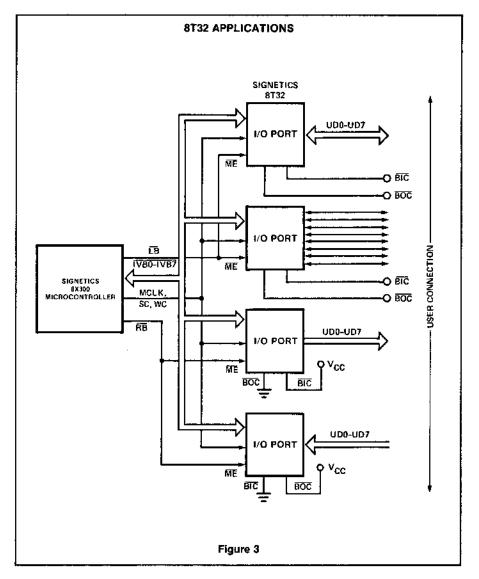

A specific example of a control system using the 8X300 Microcontroller is shown in Figure 12. Only 8 components—four 8T32 I/O Ports, one 8X350 RAM, two 82S215 ROMs, and an 8X300 are required to build this system which contains 512 words of program storage, 32 TTL I/O connection points, 256 bytes of working storage, and operates at a 250ns instruction cycle time.

#### Halt, Reset Signals

#### HALT:

A low level at the HALT input stops internal operation of the Microcontroller at the start of the next instruction after HALT is applied (quarter cycle after MCLK). Since HALT is sampled at the start of each instruction cycle it is possible to prevent a cycle by applying HALT early in that cycle. HALT does not inhibit MCLK or affect any internal registers. Normal operation begins with the next complete cycle after the HALT input goes high.

#### RESET:

A low level at the RESET input sets the program counter and address register to zero. While RESET is low MCLK is inhibited. If RESET is applied during the last 2 quarter cycles, the MCLK during that cycle may be shortened. RESET should be applied for 1 full instruction cycle time to assure proper operation. When RESET input goes high an MCLK occurs prior to the resumption of normal processing. RESET does not affect the other internal registers.

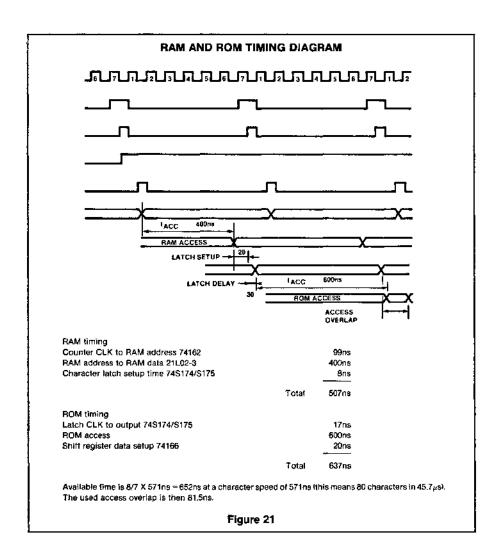

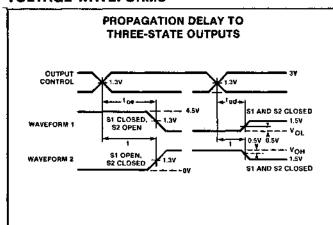

#### SYSTEM TIMING

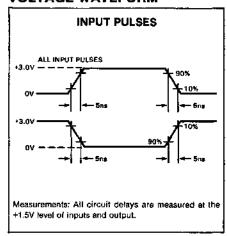

In systems with fast instruction cycle times, most Microcontroller delays are strictly determined by internal gate propagation delays.

8X300-F

Since some events are constrained to occur in certain quarter cycles, as system cycle times become slower, the delays will appear to increase due to gating with internal clocks. In the table of AC Electrical Characteristics, 2 columns are used: 1 to denote times which occur due to internal clock intervention and 1 to denote minimum delays for fast cycle times.

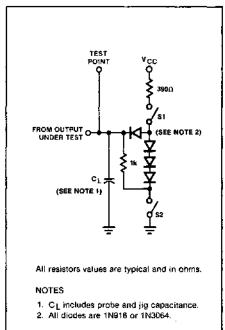

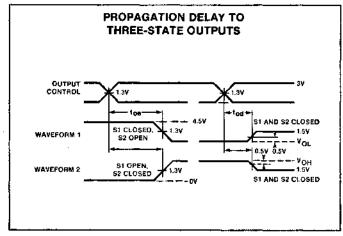

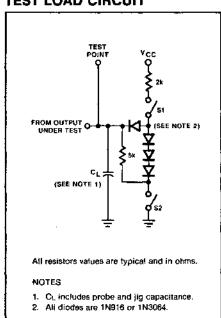

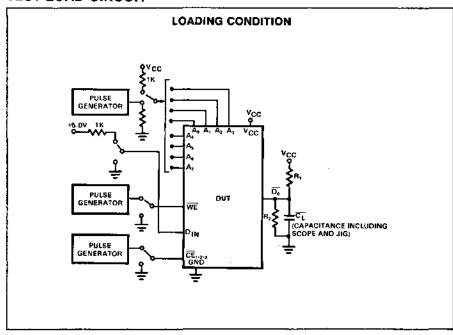

When using Signetics 8T32 I/O Ports, selection of instruction cycle time involves calculating the maximum program storage access time. Assuming the instruction is available when MCLK falls, the I/O control lines are stable 35ns later. Signetics 8T32's require another 35ns to disable a previously selected port and enable the desired port (assumes a change in bank signals). A 10ns margin has been added to the 8T32 enable for this evaluation to reflect the fact that most systems will have more capacitive loading than the 50pF test condition in the 8T32 specification and to allow for line delays.

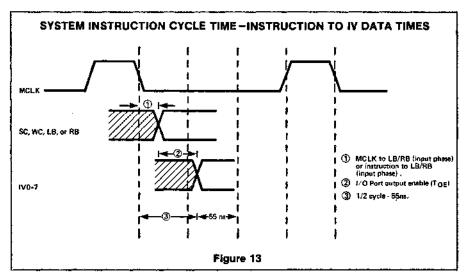

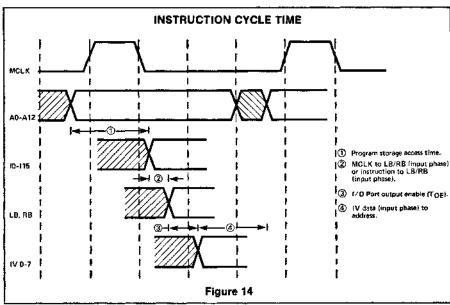

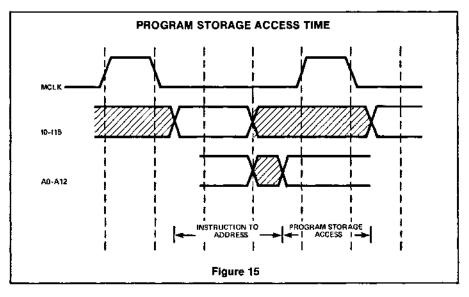

The system instruction cycle time for normal systems such as shown in Figure 12 is determined by Microcontroller propagation delays, program storage access time, and port output enable times. Instruction cycle time is normally constrained by one or more of the following conditions:

- Instruction to LB/RB (input phase) + I/O Port output enable: To∈ ≤½ cycle - 55ns (Figure 13).

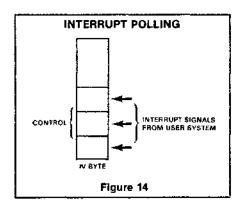

- Program storage access time + instruction to LB/RB (input phase) + I/O Port output enable and IV data (input phase) to address ≤ instruction cycle time (Figure 14).

- Program storage access time + instruction to address ≤ instruction cycle time (Figure 15).

The first constraint can be used to determine the minimum cycle time. Using the inequality 35ns + 35ns  $\leq \frac{1}{2}$  cycle - 55ns implies  $\frac{1}{2}$  cycle  $\geq$  125ns or an instruction time of 250ns.

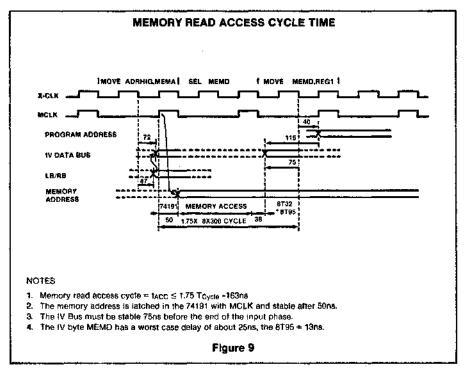

Program storage access time for a 250ns instruction cycle can be calculated from the second constraint. Noting that the specification for IV data (input phase) to address is 115ns: Program storage access time + 35ns + 35ns + 115ns ≤ 250ns implies program storage access time ≤ 65ns.

The third constraint can be used to verify the maximum program storage access time. Noting that the specification for instruction to address is 185ns: Program storage access time + 185ns ≤ 250ns confirms that program storage access time 65ns is satisfactory.

#### System Clock

The Microontroller has an integrated oscillator which generates all necessary clock signals. The oscillator is designed to connect directly to a series resonant quartz crystal via pins X1 and X2. The crystal resonant frequency, f, is related to the desired cycle time, T, by the relationship f = 2/T. For a 250ns system, f = 8.00MHz.

| Туре:                             | Fundamental mode,<br>series resonant |

|-----------------------------------|--------------------------------------|

| Impedance at<br>Fundamental:      | 35 ohms maximum                      |

| Impedance at harmonics and spurs: | 50 ohms minimum                      |

Table 7 CRYSTAL CHARACTERISTICS

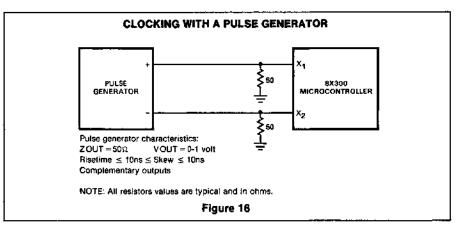

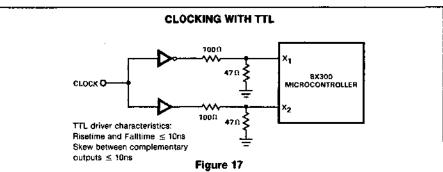

In lower speed applications where the cycle time need not be precisely controlled, a capacitor may be connected between X1 and X2 to drive the oscillator. Approximate capacitor values are given in Table 8. If cycle time is to be varied, X1 and X2 should be driven from complementary outputs of a pulse generator. Figure 16 shows a typical configuration. For systems where the Interpreter is to be driven from a master clock the X1 and X2 lines may be interfaced to TTL logic as shown in Figure 17.

| Cx,pF | CYCLE TIME     |

|-------|----------------|

| 100   | 300ns          |

| 200   | 500ns          |

| 500   | 1.1 <i>µ</i> s |

| 1000  | 2.0µs          |

Table 8 CLOCK CAPACITOR VALVES

#### AC ELECTRICAL CHARACTERISTICS V<sub>CC</sub> = 5V ± 5% and 0°C ≤ T<sub>A</sub> < 70°C

| DELAY DESCRIPTION                               | PROPAGATION<br>DELAY TIME | CYCLE TIMÉ<br>LIMIT |

|-------------------------------------------------|---------------------------|---------------------|

| X1 falling edge to MCLK (driven from external   |                           |                     |

| pulse generator)                                | 75ns                      |                     |

| MCLK to SC/WC failing edge (input phase)        | 25ns                      |                     |

| MCLK to SC/WC rising edge (output phase)        |                           | 1/2 cycle + 25ns    |

| MCLK to LB/RB (input phase)                     | 35ns                      |                     |

| Instruction to LB/RB output (input phase)       | 35ns                      | į                   |

| MCLK to LB/RB (output phase)                    |                           | ½ cycle + 35ns      |

| MCLK to IV data (output phase)                  | 185ns                     | ½ cycle + 60ns      |

| IV data (input phase) to IV data (output phase) | 115ns                     | ļ                   |

| Instruction to Address                          | 185ns                     | 1/2 cycle + 40ns    |

| MCLK to Address                                 | 185ns                     | 1/2 cycle + 40ns    |

| IV data (input phase) to Address                | 115ns                     |                     |

| MCLK to IV data (input phase)                   |                           | ½ cycle - 55πs      |

| " MCLK to Halt falling edge to prevent          |                           |                     |

| current cycle                                   |                           | 1/4 cycle – 40ns    |

| Reset rising edge to first MCLK                 |                           | 0 to 1 cycle        |

#### NOTE

- Reference to MCLK is to the falling edge when loaded with 300pF.

- 2. Loading on Address lines is 150pF.

1-00EX8

MICROCONTROLLER 8X300

8X300-I

## DC ELECTRICAL CHARACTERISTICS Limits apply for V<sub>CC</sub> = $5V \pm 5\%$ and $0^{\circ}C < T_A < 70^{\circ}C$ unless specified otherwise.

| PARAMETER         |                                                 | TEST CONDITIONS                                                                                                                | LIMITS  |                       |               |                    |

|-------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|---------------|--------------------|

|                   |                                                 |                                                                                                                                | Min     | Тур                   | Max           | UNIT               |

| v <sub>IH</sub>   | High level input voltage<br>X1,X2<br>All others |                                                                                                                                | .6<br>2 |                       |               | V<br>V             |

| V <sub>IL</sub>   | Low level input voltage<br>X1,X2<br>All others  |                                                                                                                                |         |                       | .4<br>.8      | V                  |

| VіС               | Input clamp voltage<br>(Note 1)                 | V <sub>CC</sub> = 4.75V<br>I <sub>I</sub> = +10mA                                                                              |         |                       | -1.5          | ٧                  |

| l <sub>I</sub> BH | High level input current<br>X1,X2<br>All others | V <sub>CC</sub> = 5.25V<br>V <sub>IH</sub> = .6V<br>V <sub>CC</sub> = 5.25V                                                    |         | 2700<br><1            | 50            | . μ <b>Α</b><br>μΑ |

| 111               | Low level input current<br>X1.X2<br>IVBO-7      | V <sub>IH</sub> = 4.5V<br>V <sub>CC</sub> = 5.25V<br>V <sub>IL</sub> = .4V<br>V <sub>CC</sub> = 5.25V<br>V <sub>IL</sub> = .4V |         | -2500<br>-140<br>-880 | -200<br>-1600 | μΑ<br>μΑ<br>Αυ     |

|                   | HALT, RESET                                     | V CC = 5.25V<br>V IL = .4V<br>V CC = 5.25V<br>V IL = .4V                                                                       |         | -230                  | -400          | μΑ                 |

| VOL               | Low level output voltage<br>A0-A12              |                                                                                                                                |         | .35                   | .55           | ٧                  |

|                   | All others                                      | V <sub>CC</sub> = 4.75V<br>I <sub>OL</sub> = 4.25mA<br>V <sub>CC</sub> = 4.75V<br>I <sub>OL</sub> ≈ 16mA                       |         | .35                   | .55           | ٧                  |

| v <sub>ОН</sub>   | High level output voltage                       | V <sub>CC</sub> = 4.75V<br>1 <sub>OH</sub> = 3mA                                                                               | 2.4     |                       | :             | V                  |

| los               | Short circuit output current (Note 2)           | V <sub>CC</sub> = 5.25V                                                                                                        | -30     |                       | -140          | mA                 |

| v <sub>cc</sub>   | Supply voltage                                  |                                                                                                                                | 4.75    | 5                     | 5.25          | ٧                  |

| l <sub>CC</sub>   | Supply current                                  | V <sub>CC</sub> = 5.25V                                                                                                        |         |                       | 1.60          | mΑ                 |

| REG               | Regulator control                               | V <sub>CC</sub> = 5.0V                                                                                                         | -14     |                       | -21           | mA                 |

| CR                | Regulator current (Note 3)                      |                                                                                                                                |         |                       | 290           | mA                 |

| VCR               | Regulator voltage (Note 3)                      |                                                                                                                                | 2.2     |                       | 3.2           | V                  |

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                             | RATING | UNIT |

|-------------------------------------------------------|--------|------|

| V CC Supply voltage<br>X1,X2 Crystal input<br>voltage | 7<br>2 | >>   |

| Others Logic input voltage                            | 5.5    | ٧    |

#### NOTES

29

<sup>1.</sup> Crystal inputs X1 and X2 do not have clamp diodes.

<sup>2.</sup> Only one output may be grounded at a time.

<sup>3.</sup>  $V_{CC} = 5.25V$ , HALT = RESET = ADDRESS = IVX = 0.0V, all other pins open.

## SUPPORT PRODUCTS

#### DESCRIPTION

The Signetics 8X300 Fixed Instruction Bipolar Microprocessor provides new levels of high performance to microprocessor applications not previously possible with MOS technology.

In the majority of cases, the choice of a bipolar microprocessor slice, as opposed to an MOS device, is based on speed. The 8X300 processor, combined with high-speed memory and I/O devices, is capable of executing all instruction in 250ns.

The 8X300 is optimized for control and data movement applications. It has a 13-bit address bus for selecting instructions from program storage and a separate input bus for entering a 16-bit instruction words. Data handling and I/O device addressing are accomplished via the 8-bit Interface Vector (IV) bus. The IV bus is supported by four additional control lines and a clock.

The unique features of the 8X300 IV bus and instruction set permit 8-bit parallel data to be rotated or masked before undergoing arithmetic or logical operations. Then, the data may be shifted and merged into any set of from 1 to 8 contiguous bits at the destination. The entire process of input, shifting, processing and output is done in 1 instruction cycle time. The 250ns cycle time makes the 8X300 ideally suited for high-speed applications.

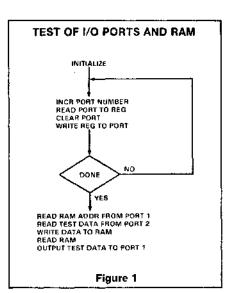

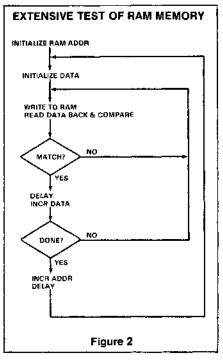

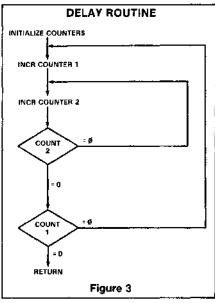

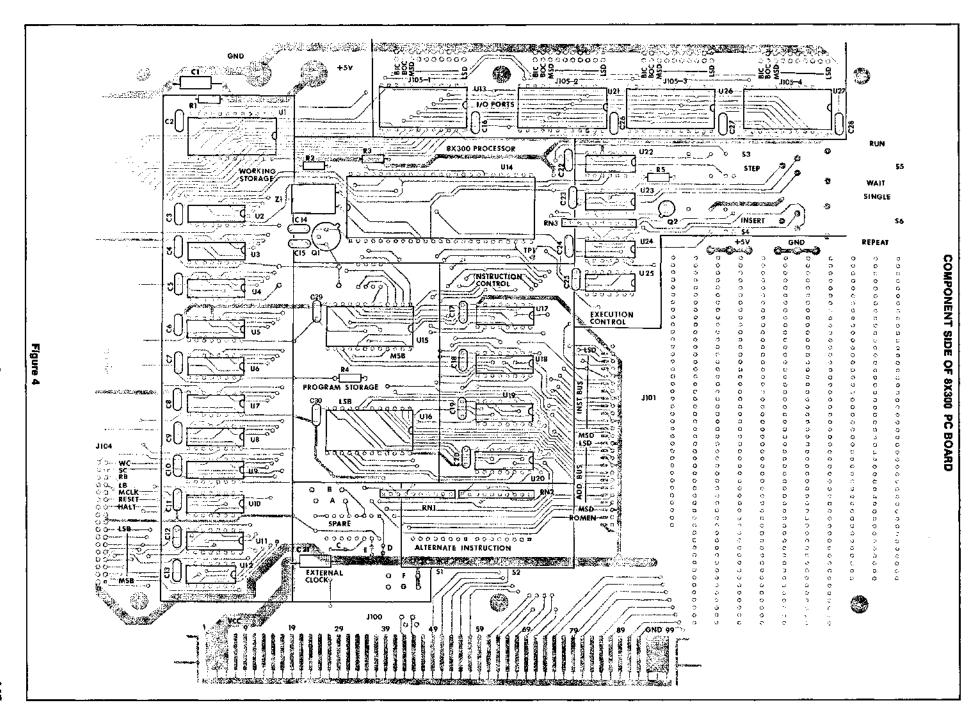

The evaluation board contains all the elements which a designer needs to judge the suitability of the 8X300 for his systems applications. Included with the 8X300 are 4 I/O ports for external device interface, 256 bytes of temporary (working) data storage, and 512 words of program storage, all properly connected to the 8X300 to allow immediate exercising of the board. For this purpose, the PROMs are preprogramed with the I/O control, RAM control, and RAM integrity diagnostic programs. With the remaining PROM space, the designer may enter his own benchmark, test, or development routines.

The board design allows complete flexibility in access to the address, instruction, and IV busses as well as all controls and signals of the 8X300. The IV bus, I/O port user connection, clock signals control lines, address bus and instruction bus are wired to output pins, the board edge connector and flat cable connectors.

The board layout permits variations and/or expansions of the basic design. In addition to the access to all signals for transfer off the board, a wire wrap area is provided so that the designer may add to the board circuitry as he desires. The addition may include memory, additional interfaces, or

special circuits which meet specific user requirements.

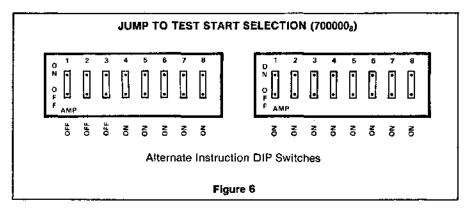

Controls are also provided for diagnostic and instructional purposes by allowing various operating modes. In the WAIT mode, the program may be single stepped for ease of checkout. The one-shot instruction jamming allows control of the program start location, changes of program flow, changing or examining the internal registers, or testing of simple sequences. The repeated instruction jamming provides a means of repetitive execution of an instruction so that the I/O bus and the control lines may be examined without software changes. In both of these jam cases, the jammed instruction is selected by boardmounted switches.

#### **FEATURES**

- 250ns CPU with Crystal

- 4 I/O Ports (32 Lines)

- 256 Bytes Data Storage

- 512 Words Program Storage

- Run/Wait Control

- Single Step

- Instruction Jamming

One Shot Instruction Jam

Repeated Jam

- All Buses to Output Pins

- Firmware Diagnostics

- Wire-Wrap Area

- Edge Connector

- Flat Cable Connectors

- Wire Wrap Posts for Bus Lines

#### **CONTENTS**

1 ea- 8X300

8 ea - 82S116 (256 x 1 RAM)

2 ea- 82S115 (512 x 8 PROM)

4 ea— 8T32 Addressable Bidirectional I/O Port

1 ea--- 8T31 (Bidirectional I/O Port)

2 ea - 8T26A (Quad Bus Transceiver)

4 ea— 74157 (Quad 2-Input Data Selec-

2 ea - 7474 (Dual D Flip Flop)

2 ea- 7400 (Quad Nand Gate)

1 ea- 7427 (3-Input NOR Gate)

1 ea— P.C. Board Misc. Parts

1 ea-- Introductory Manual, assembly instructions, code listings and schematics

#### **AVAILABILITY**

Immediate delivery from Signetics Rep. or Distributors.

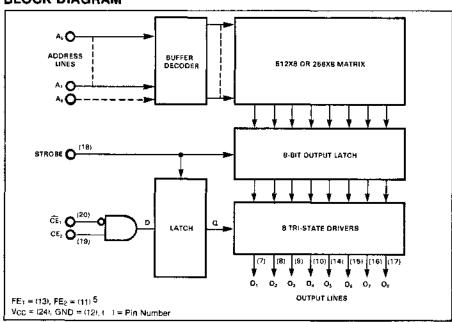

#### **BLOCK DIAGRAM**

#### **Auxiliary Circuits**

The 8X300 can be used with any bipolar (or TTL-compatible) ICs. It can directly address 8192 program instruction locations and up to 512 I/O ports. The memory paging feature may be employed for larger working storage. Typical auxiliary circuits include:

| Program<br>I/O | Storage<br>8T32/33 | 82S115 (512x8 PROM)<br>(8-Bit Synchronous<br>Bidirectional I/O<br>Port) |

|----------------|--------------------|-------------------------------------------------------------------------|

|                | 8T35/36            | (8-Bit Asynchronous<br>Bidirectional i/O<br>Port)                       |

|                | 8T31               | (8-Bit Bidirectional<br>I/O Port)                                       |

|                | 8T39               | (Quad Bus Extender)                                                     |

Working Storage 82S116 RAM

#### DESCRIPTION

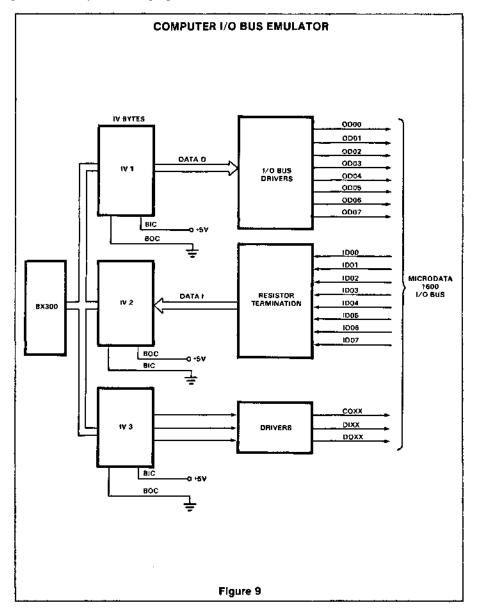

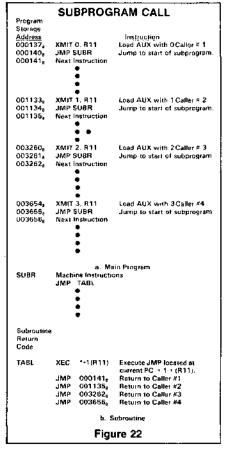

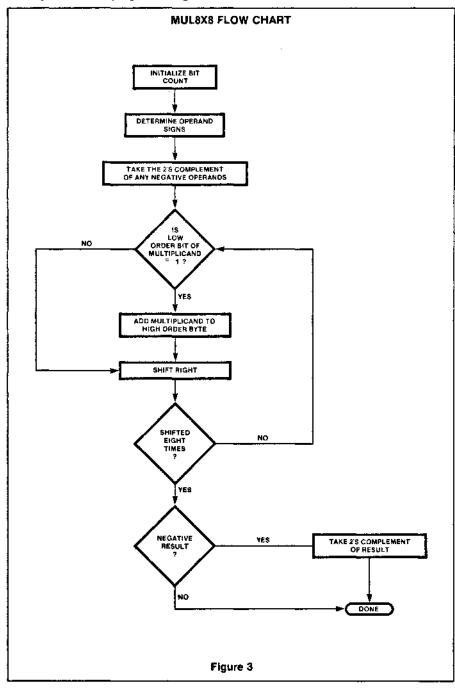

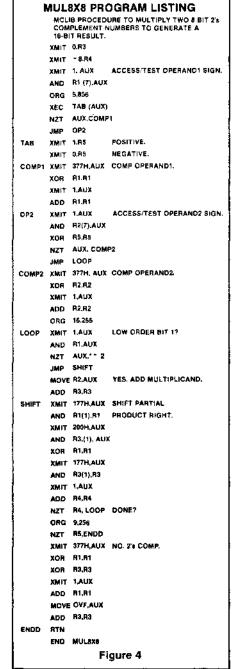

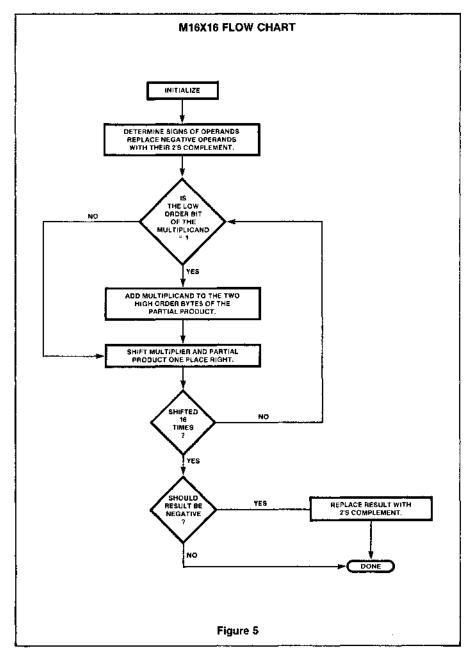

The 8X300 Programming Course is an audio/visual course designed to assist system logic designers with little or no previous microprocessor programming experience to confidently and effectively design and generate software for his own application.