# SIGNETICS 8X300 PROGRAMMING MANUAL

# SIGNETICS 8X300 PROGRAMMING MANUAL

Material used in this document was prepared by A.H.J. Schatorjé of N.V. Philips, Eindhoven, The Netherlands.

SIGNETICS reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and Signetics makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

<sup>®</sup>Copyrighted by Signetics Corporation May 1978.

# PREFACE

Signetics 8X300 Programming Manual is designed to provide all the information necessary to prepare code for the 8X300 Microcontroller. Details for every variation within each class of instruction are shown diagrammatically, in binary and in assembly language. Sample programs and a description of the Microcontroller Cross Assembly Program (MCCAP) are included.

Additional information relevant to the application of the 8X300 can be found in the following documents:

8X300 Programming Course

8X300 Reference Manual

Signetics Microcontroller Cross Assembly Program

These and other Signetics product documents are available through the offices listed in the back of this manual.

# TABLE OF CONTENTS

| The 8X300 System                               | 6  |

|------------------------------------------------|----|

| The 8X300 Instruction Set                      | 14 |

| MCCAP Microcomputer Cross Assembler Program    | 15 |

| MOVE Instructions                              | 16 |

| ADD Instructions                               | 28 |

| AND Instructions                               | 40 |

| XOR (eXclusive OR) Instructions                | 50 |

| XEC (eXECute) Instructions                     | 67 |

| NZT (Non Zero Test) Instructions               |    |

| XMIT (transMIT) Instructions                   | 75 |

| JMP (JuMP) Instructions                        | 79 |

| Microcontroller Cross Assembly Program (MCCAP) | 90 |

| Programming Examples                           |    |

| Sales offices                                  |    |

|                                                |    |

# THE 8X300 SYSTEM

#### THE 8X300 SYSTEM

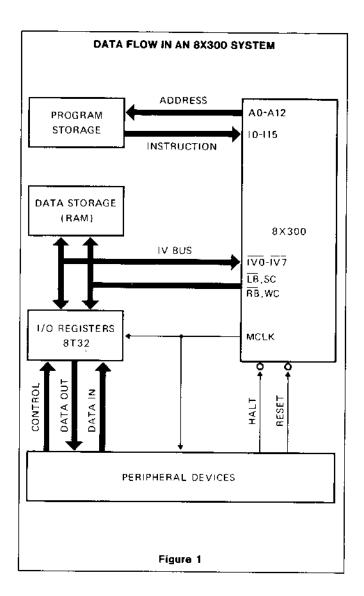

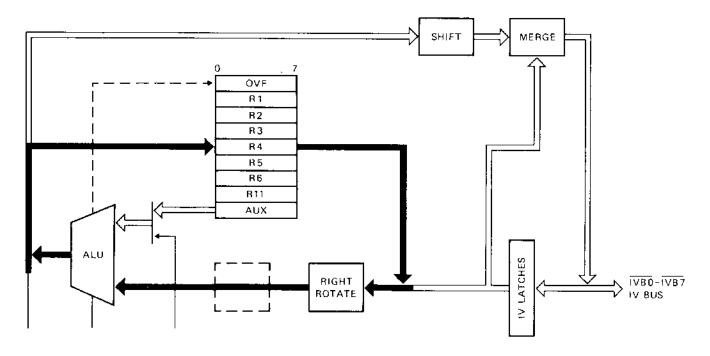

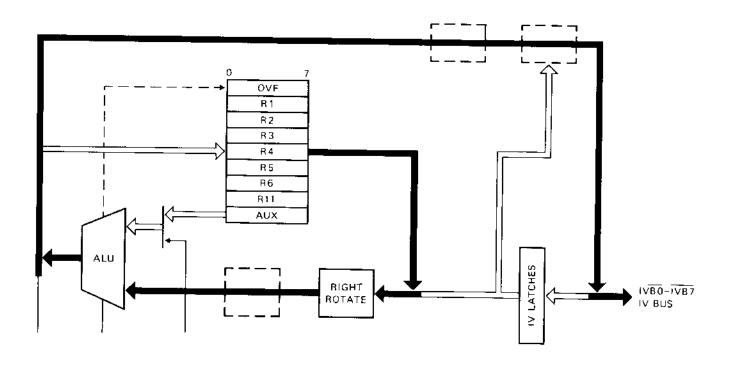

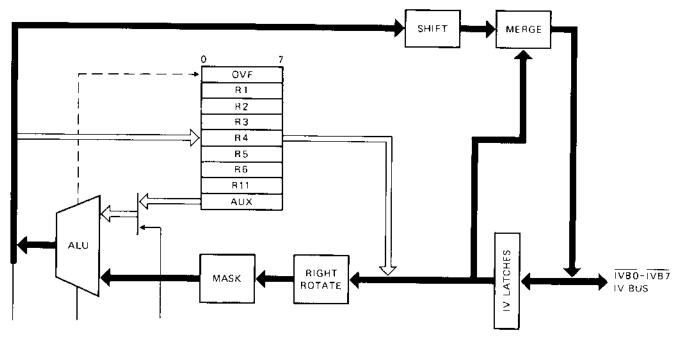

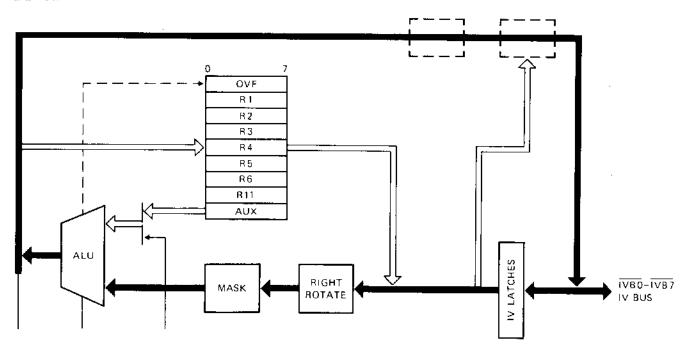

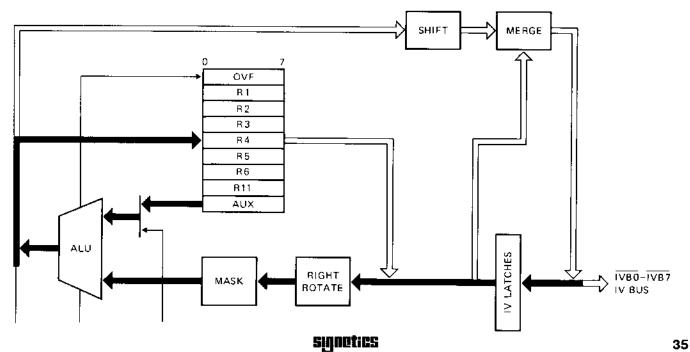

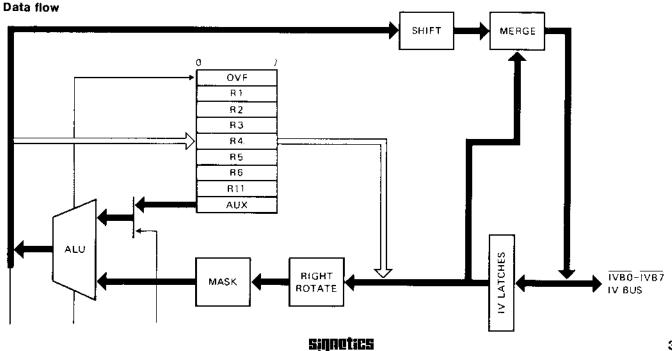

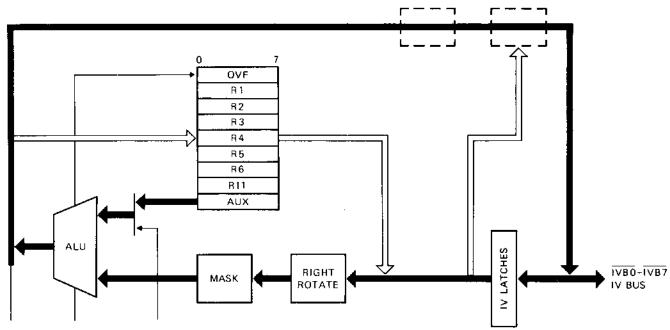

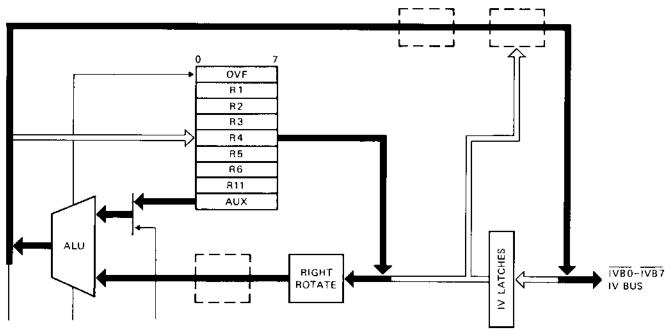

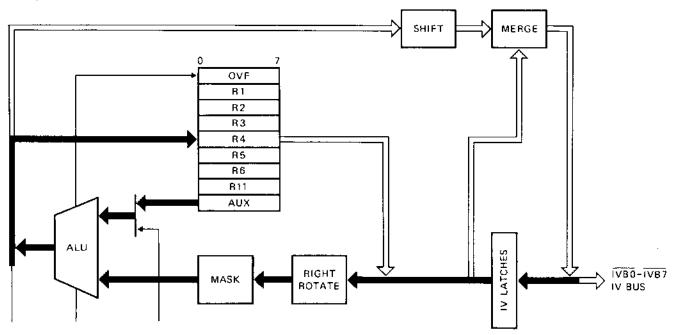

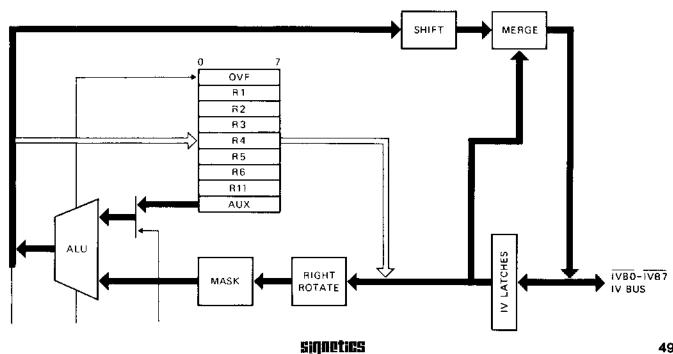

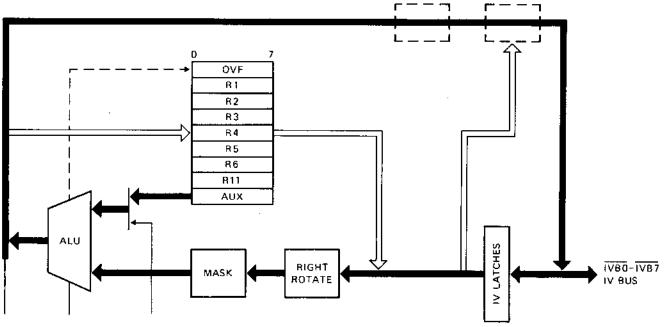

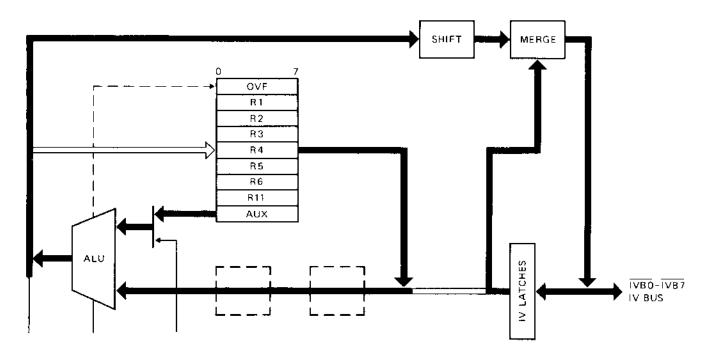

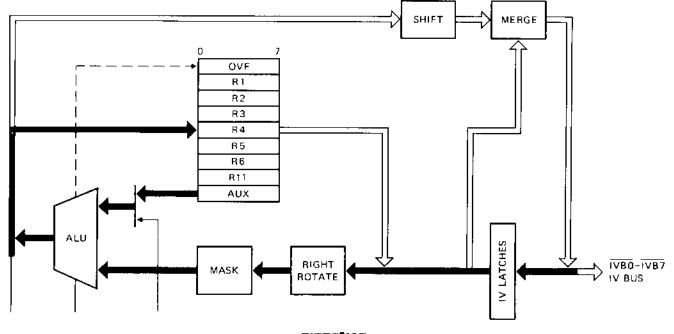

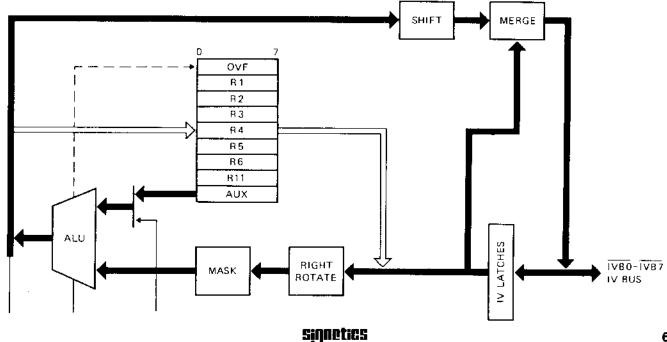

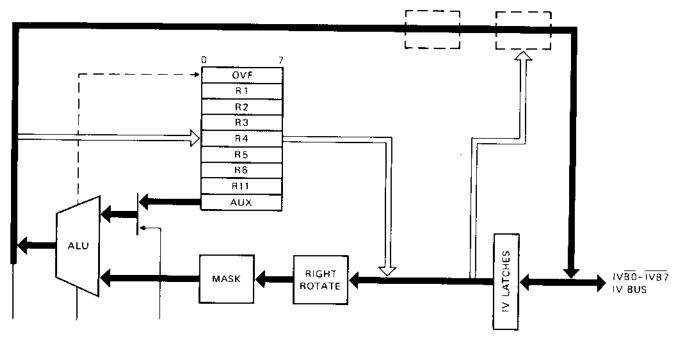

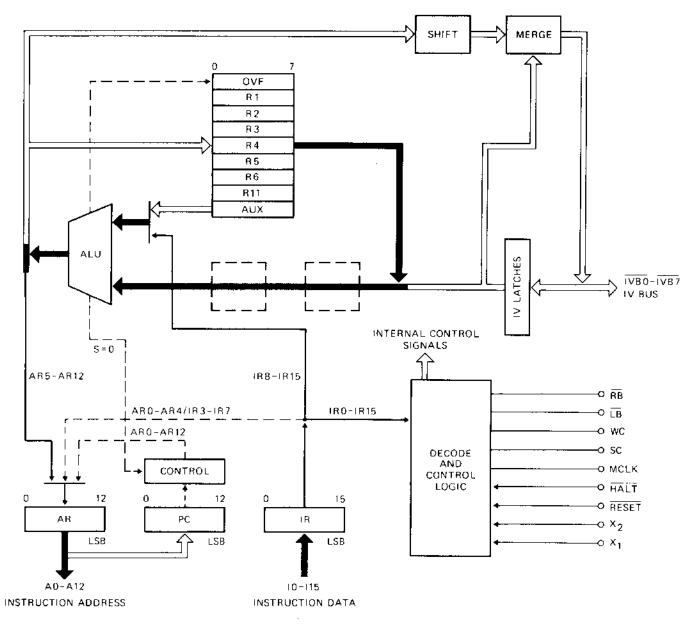

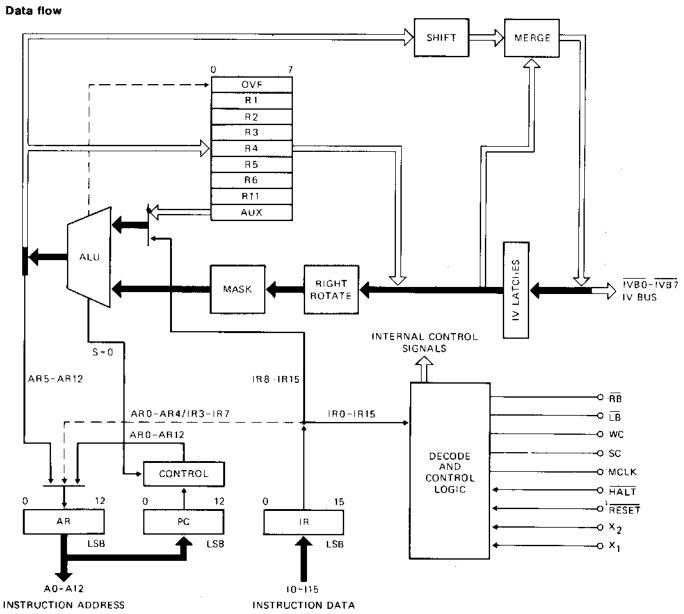

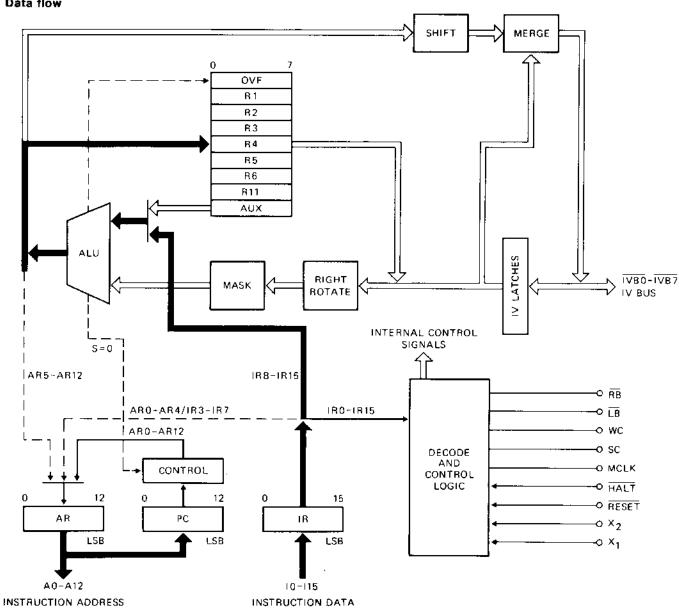

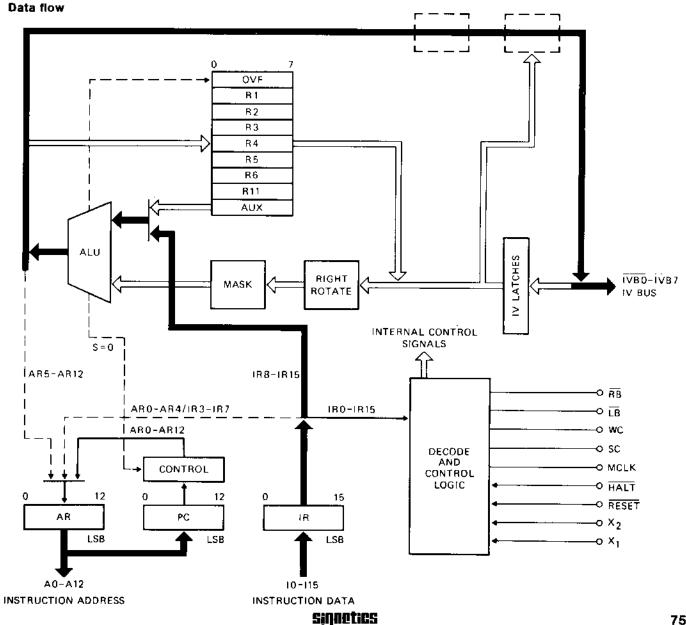

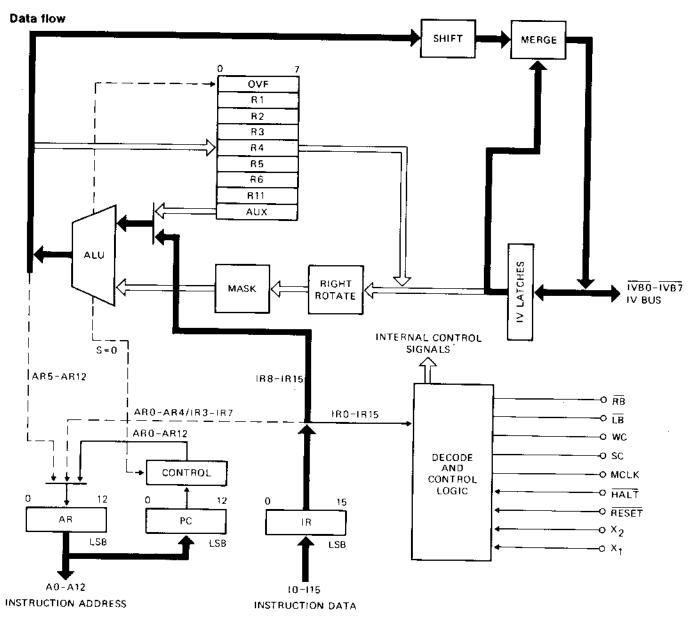

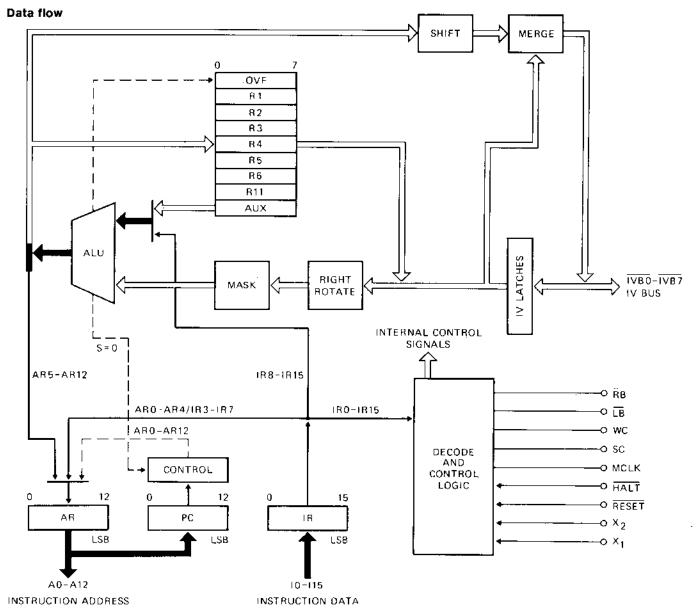

The independent instruction and data input/output (I/O) system of the 8X300 is shown in Fig. 1. The 13-bit address bus, capable of addressing 8192 instructions, and the 16-bit instruction bus allow the 8X300 to access the next instruction while simultaneously performing data I/O with the Interface Vector (IV) bus. As can be seen from the diagram, all data to or from external devices or registers passes via the IV bus.

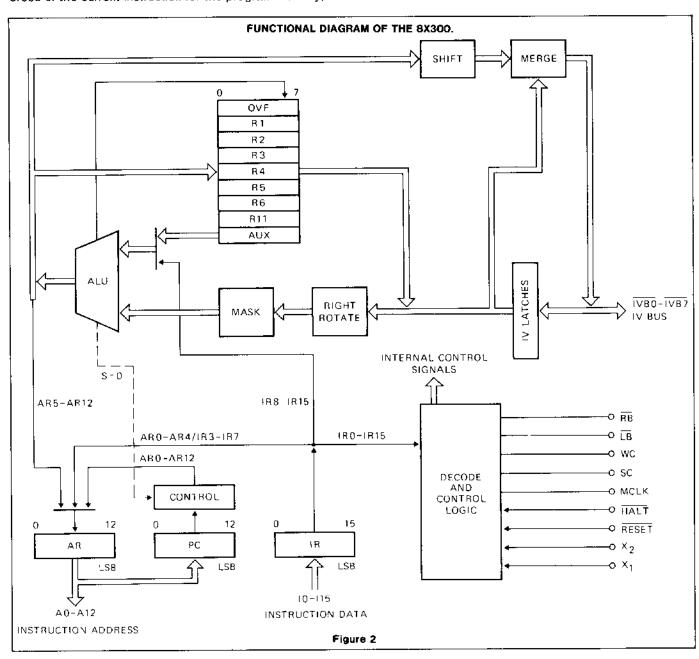

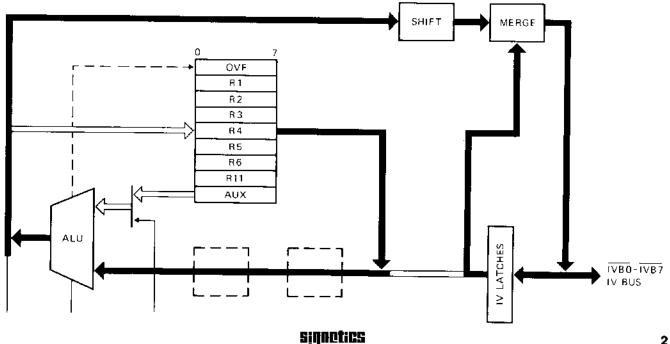

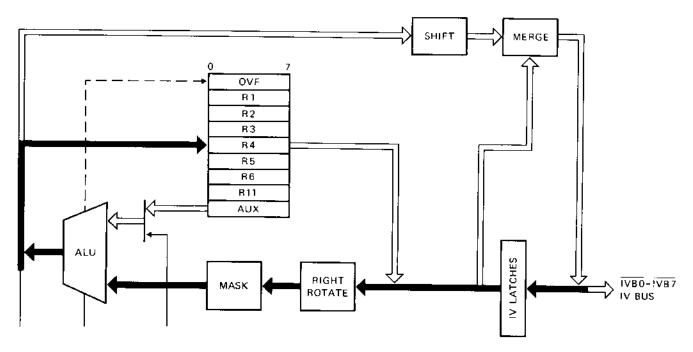

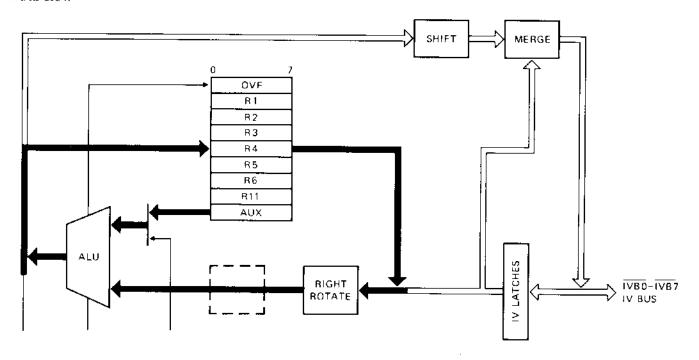

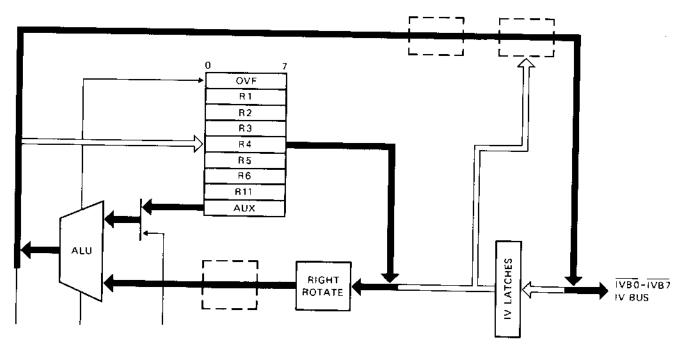

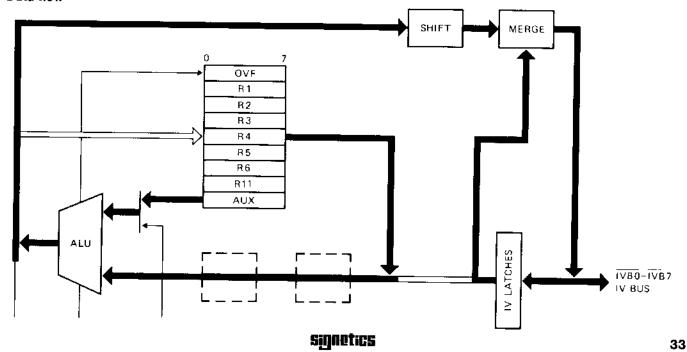

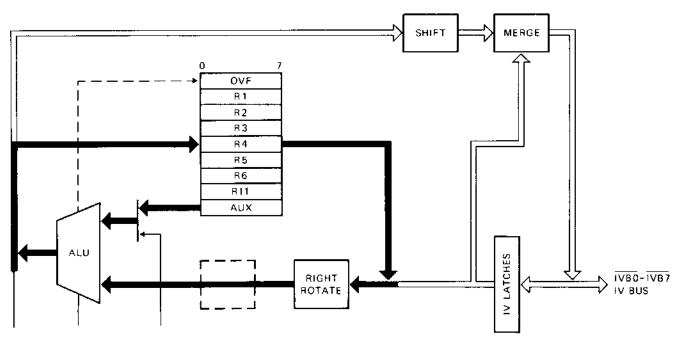

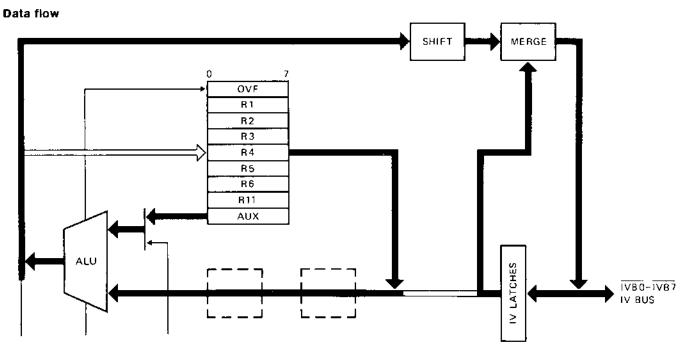

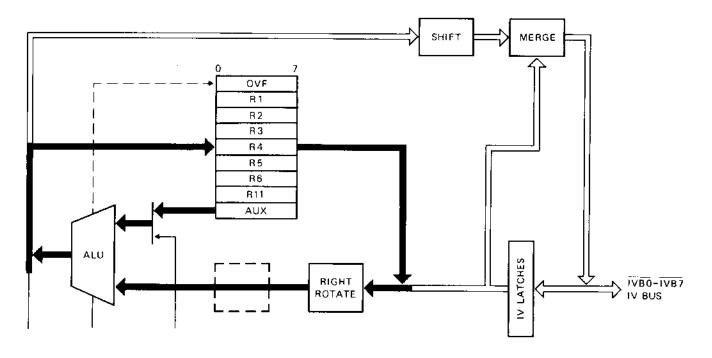

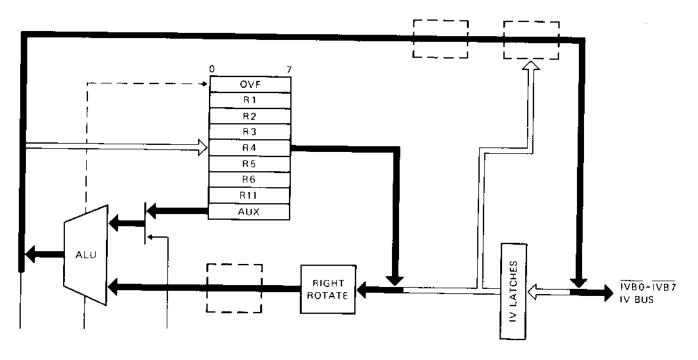

Figure 2 shows the functional diagram of the 8X300, with the data paths between the elements of the microprocessor and the connections to the address, instruction and IV busses. Although the program instruction addressing is essentially independent of the data flow, links exists to allow address modification or the transmission of data from the program to an output device.

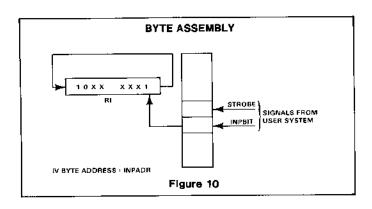

#### Interface Vector Bus

All data input to or output from the 8X300 goes via the IV bus. This IV bus serves both as an address and data bus and is accompanied by control signals to determine its function. Being an 8-bit bus, it has the capability to address up to 256 I/O registers (IV bytes). The input/output facilities are further expanded by selection of Left Bank (LB) or Right Bank (RB) address, giving a total of 512 addressable IV bytes.

When the 8X300 is required to accept data from or send data to a particular IV byte, it must first enable the IV byte. An IV byte is enabled when its address is presented on the IV bus and the bus control signals indicate that the data is an address on the required bank. The IV byte will remain enabled until another IV byte on the same bank is enabled, at which time it becomes disabled.

Because the Left and Right Banks are independent, one IV byte on each Bank can be active (enabled) simultaneously. Data input from, or output to the IV bus implied data I/O to the active byte on the Bank specified by the Instruction causing the I/O action.

The most significant bit of all data is bit 0.

#### Internal Data Registers

The 8X300 contains an auxiliary (AUX) register and seven work registers to facilitate data manipulation. A separate overflow register is used to provide overflow indication after an ADD instruction. Figure 2 shows these in the schematic diagram of the 8X300.

The AUX register is used as the implied operand in ADD, AND and XOR instructions: however it can also be used as a normal work register for other instructions.

The overflow register can only be used as a source of data. Its seven most significant bits are always zero, while a one in the least significant bit position indicates that overflow occurred during the last ADD instruction. The overflow register contents can only be changed by the result of an ADD instruction.

Table 1 gives details of the data registers of the 8X300 and the corresponding instruction operand values.

#### **Internal Program Registers**

There are three registers concerned with instruction execution in the 8X300:

Address Register (AR) — output register holding the address of the current instruction for the program memory;

**Program Counter (PC)** — holding the address of the current or next instruction to allow modification by the control circuity;

Instruction Register (IR) — Holding the 16-bit instruction word currently being executed.

These registers cannot be addressed as the operand of an instruction although the content of the program counter and address register can be changed as the result of special instructions. The program counter and address register are incremented by one during each instruction cycle to provide the address of the next instruction to be executed. However, a jump instruction can cause this action to be overruled and a new address substituted.

Table 1. INTERNAL DATA REGISTERS OF THE 8X300.

| NAME | OCTAL ADDRESS | DESCRIPTION                                                                                                                                                                 |

|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUX  | 00            | Work register, containing the implied operand for ADD, AND and XOR instructions.                                                                                            |

| R1   | 01            | )                                                                                                                                                                           |

| R2   | 02            |                                                                                                                                                                             |

| R3   | 03            |                                                                                                                                                                             |

| R4   | 04            | General purpose registers.                                                                                                                                                  |

| R5   | 05            | ,,,,,,,, .                                                                                                                                                                  |

| R6   | 06            |                                                                                                                                                                             |

| R11  | 11            |                                                                                                                                                                             |

| OVF  | 10            | Read-only register whose least significant bit indicates overflow status of the last ADD instruction: LSB = 1, overflow occurred. The remaining seven bits are always zero. |

#### The Address Bus

The 8X300 has a separate 13-bit instruction address bus with the capability to address up to 8192 program words.

#### The Instruction Bus

This is a 16-bit bus which delivers the contents of the selected instruction memory address to the instruction register of the 8X300.

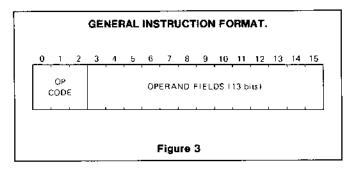

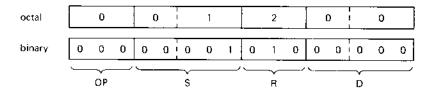

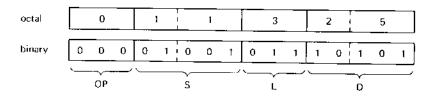

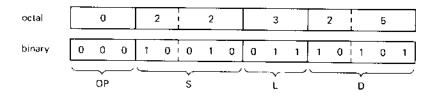

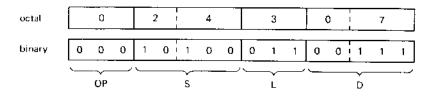

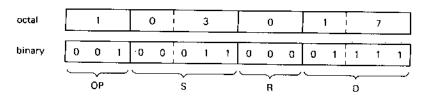

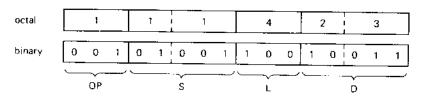

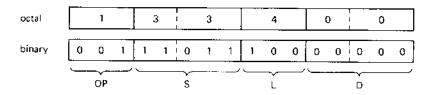

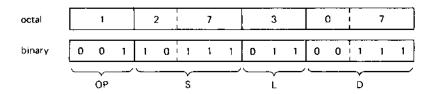

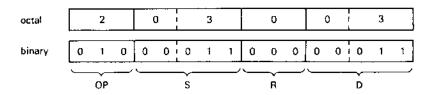

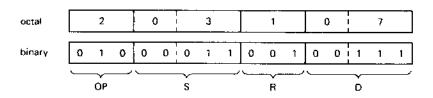

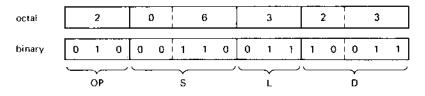

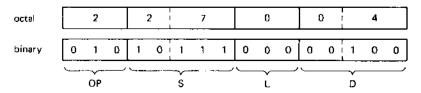

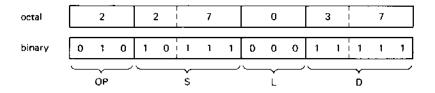

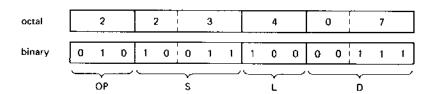

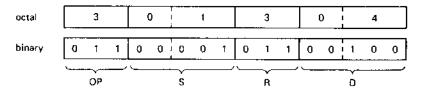

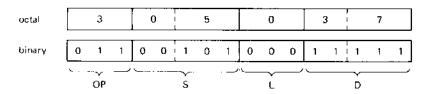

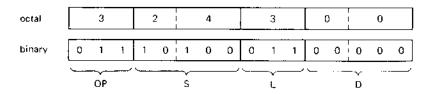

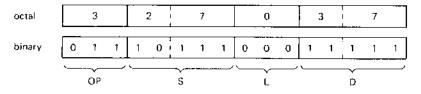

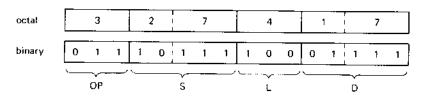

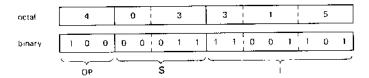

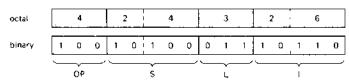

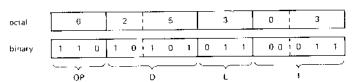

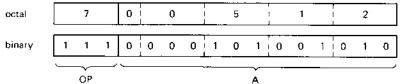

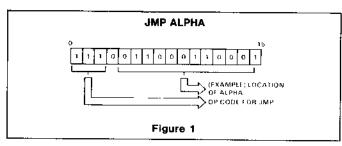

#### Instruction Formats and Operand Fields

An 8X300 instruction consists of a three bit operation code (OP) followed by a thirteen bit operand field. The operation code determines the class of the instruction to be performed, while the operand field provides details of the data to be processed. Figure 3 shows the general instruction format for the 8X300.

Table 2 shows the various instruction formats and the instructions that use those.

Table 2 INSTRUCTION FORMATS.

| Forma | at        |        |                | Instruct                  | ions                                                                                     |

|-------|-----------|--------|----------------|---------------------------|------------------------------------------------------------------------------------------|

| 012   | 3 4 5 6 7 | 8 9 10 | 11 12 13 14 15 |                           |                                                                                          |

| OP    | S         | R      | D              | MOVE<br>ADD<br>AND<br>XOR | register to register register to IV bus address                                          |

| OP    | S         | L      | D              | MOVE<br>ADD<br>AND<br>XOR | register to IV bus<br>IV bus to register<br>IV bus to IV bus<br>IV bus to IV bus address |

| OP    | S         |        |                | XEC<br>NZT                | register<br>register                                                                     |

| OP    | S         | L      | I              | XEC<br>NZT                | IV bus<br>IV bus                                                                         |

| OP    | D         | ı      |                | XMIT                      | register<br>IV bus address                                                               |

| OP    | D         | L      | I              | XMIT                      | IV bus                                                                                   |

| OP    |           | \      |                | JMP                       |                                                                                          |

#### S — Source

This field defines the location of the data byte to be processed. It is a 5-bit field divided into two sub-fields:  $S_0$  (3 bits) and  $S_1$  (2 bits). This allows the address of the source data byte to be specified as two octal digits (maximum is 37). The source can be either a register, in which case both sub-fields are used for the address (see Table 1), or the IV bus. When the source is the IV bus,  $S_1$  specifies the bank (2 = Left bank, 3 = right bank) and  $S_0$  specifies the LSB of the data to be processed:  $S_0 = n$  means that the source data byte will be right rotated until bit n is the least significant bit. Thus  $S_0 = 7$  requires no right rotation.

#### D — Destination

This 5-bit field specifies the destination of the processed data: it can be a register, the IV bus or an IV bus address. Sub-fields D<sub>0</sub> and D<sub>1</sub> allow the destination to be addressed as two octal digits in the same manner as the source field.

When the destination is a register, both sub-fields are used for the address (see Table 1).

When the data is to be used as an IV bus address, the octal values 07 (left bank address) or 17 (right bank address) must be programmed.

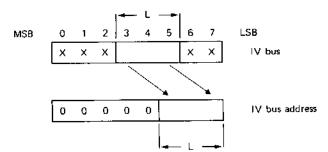

When the destination is the IV bus (to the currently enabled IV byte),  $D_1$  specifies the bank (2 = left bank, 3 = right bank) and  $D_0$  specifies the position in the IV byte with which the least significant bit of the processed data field should be aligned.

#### L — Length

This 3-bit field defines the number of bits in the source and/or destination field.

When the destination is the IV bus, the L field specifies the length of the destination field whose least significant bit is specified by  $D_{\Omega}$ .

When the source is the IV bus, the L field specifies the length of the source field whose least significant bit is specified by  $S_0$ . If the destination is also the IV bus then the L field applies to both source and destination.

Note: a value of L = 0 specifies an 8-bit data field.

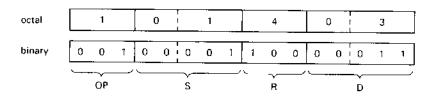

#### R --- Rotate

For instructions where the source is a register and the destination is either a register or an IV bus address, the 3-bit rotate field is used in place of the length field. A value n means that the source data field is right rotated n-places before being processed.

#### I — Integer

The integer field is either 5 bits or 8 bits long, depending on the instruction. It is used to provide a constant in the range 0 to 378 (5 bits) or 0 to 3778 (8 bits).

#### A — Address

The 13-bit address field is used with the jump instruction to define the absolute address to be set into the address register and program counter, i.e. the address of the next instruction to be executed.

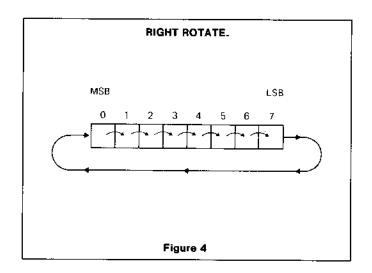

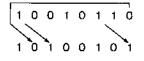

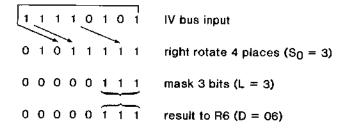

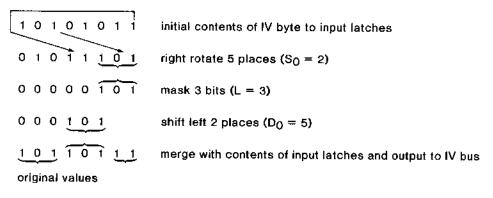

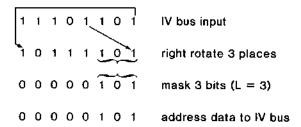

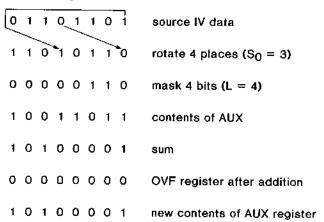

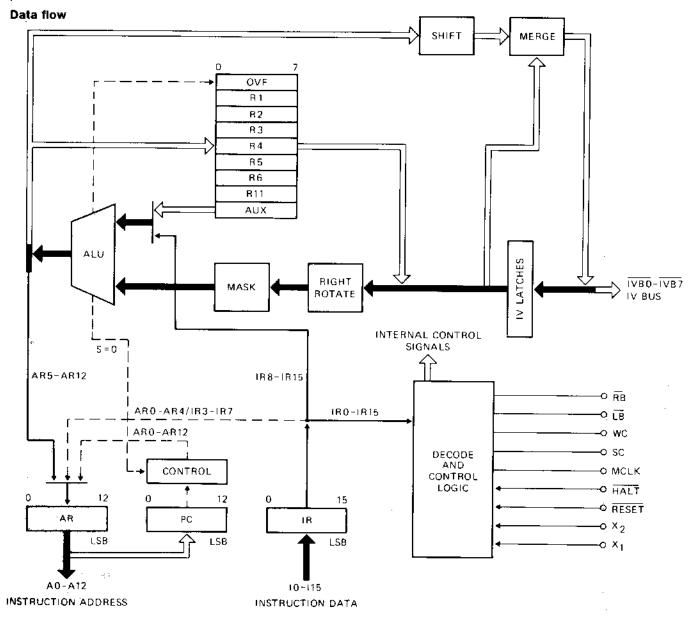

#### Right Rotate and Mask Functions

The combination of right rotate and mask functions allows selection of one or more bits from a source data field. For instructions where both the source and destination are registers, only the rotate function is available, the data being a fixed length of 8 bits.

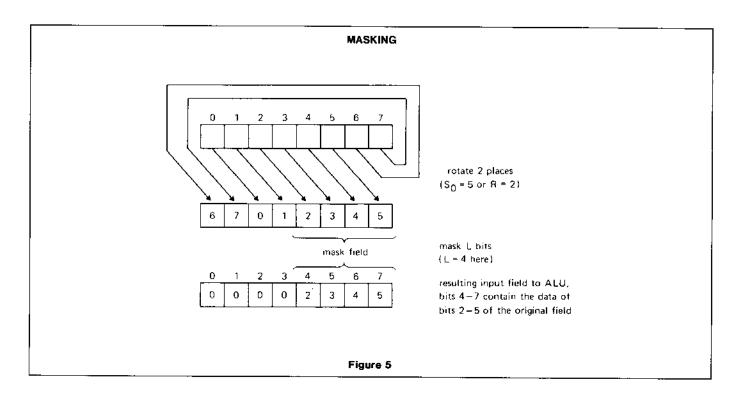

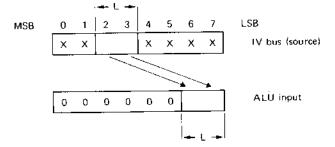

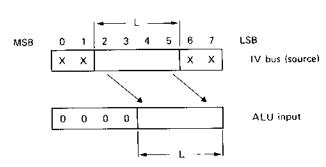

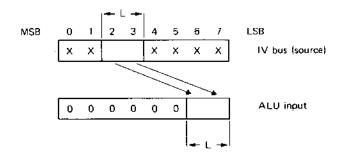

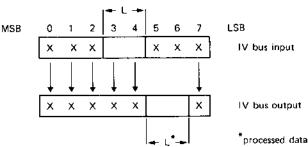

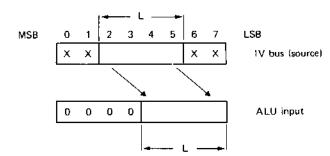

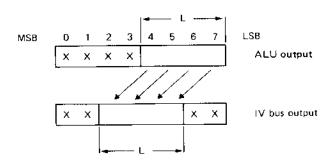

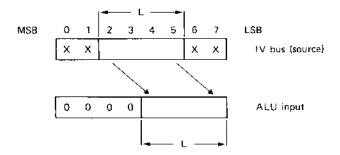

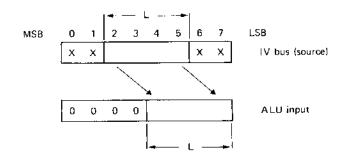

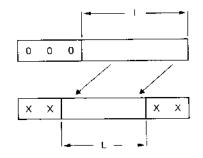

The right rotate function provides an end-around-shift of one to seven places of the 8-bit source field, see Fig. 4. In this manner, the least significant bit of the bit string required can be positioned in the least significant position of the data byte, ready for further processing, see Fig. 5.

The number of places that the data is to be rotated is specified by the R field, when present, and by the S<sub>0</sub> field when the source is the IV bus.

The R field specifies the number of places the data is to be rotated; the  $S_0$  field specifies the bit of the source data field which will be rotated to bit position seven before masking.

The mask function allows selection of the least significant L bits of the rotated IV bus source data for subsequent processing. The value L is specified by the L-field of the instruction. After masking, the L least significant bits are output to the Arithmetic and Logic Unit (ALU), with the remaining bits of the byte set to zero.

#### Arithmetic and Logic Unit (ALU)

As its name implies, the ALU performs all the arithmetic and logic functions. For this purpose it has a direct input from the AUX register for the implied operand in ADD, AND and XOR instructions. The output of the ALU may go directly to the address or data registers, or, via the shift and merge circuits, to the IV bus.

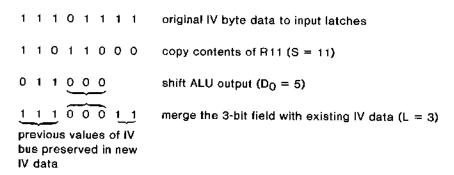

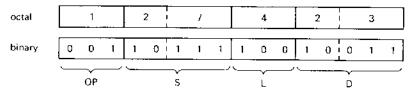

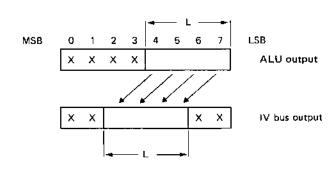

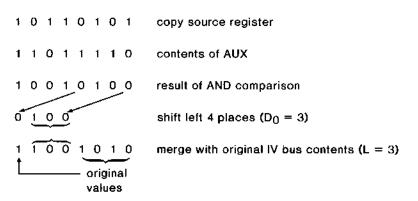

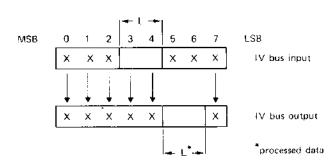

#### Shift and Merge Functions

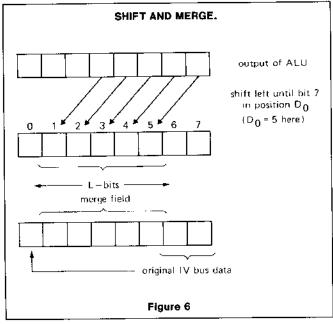

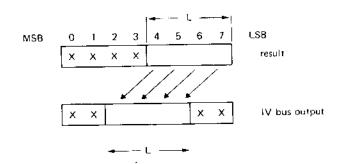

The shift and merge functions allow alteration of the state of a bit string within the IV bus data byte. The action of the rotate and mask functions ensures that the required processed data is in the least significant bits of the ALU output; the left shift function then aligns the data in the required bit positions prior to merging, see Fig. 6.

Because the process is not an end-around-shift, data shifted from position 0, the MSB, is lost. The number of positions to be shifted is determined by the value  $D_0$ : the data is left shifted until the LSB has reached the bit position specified by  $D_0$ .

The merge function allows the user to update part of the existing IV bus data without affecting the remaining parts of the data byte. The length of the bit string to be merged with the existing data is specified by the L-field, the LSB of the bit string being specified by  $D_0$  (after shifting).

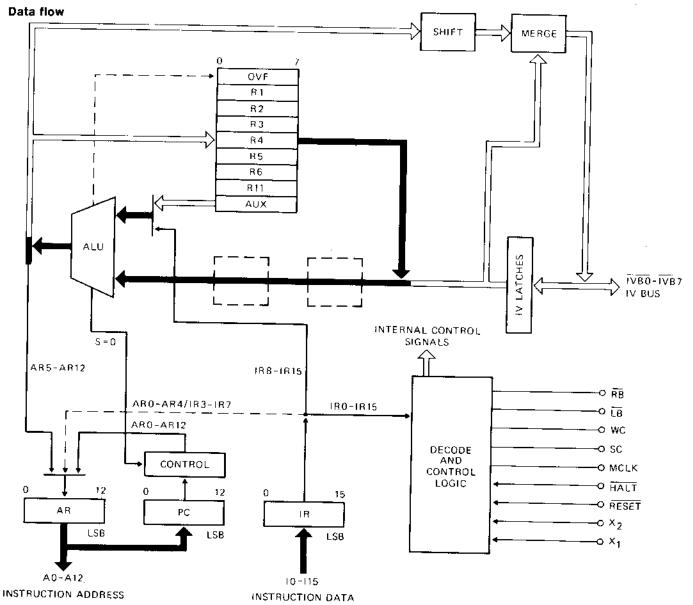

#### **Timing and Instruction Cycle**

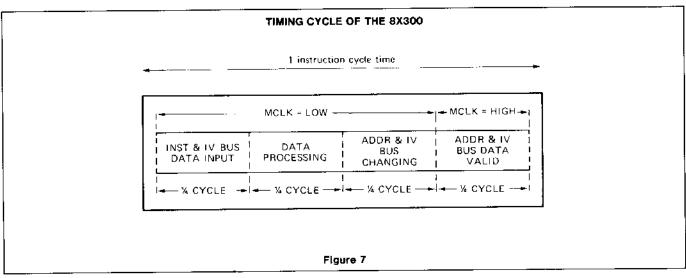

Each processor operation is executed in one instruction cycle which is internally divided into quarter cycles. During the first quarter cycle the instruction word is accepted by the instruction register and the data input latches are enabled to accept the data on the IV bus. As processing takes place during the second and third quarter cycles, the input data must be stable by the end of the first quarter cycle. The address for the next instruction becomes available during the third quarter cycle enabling access of the program memory during the third and fourth quarter cycles for the ensuing instruction. If data is to be output to the IV bus, output drivers are activiated during the third quarter cycle to present stable output data during the fourth data cycle. Thus, the IV bus works in the input mode during the first two quarter cycles and in the output mode during the last two quarter cycles. Figure 7 shows the breakdown of the instruction cycle time.

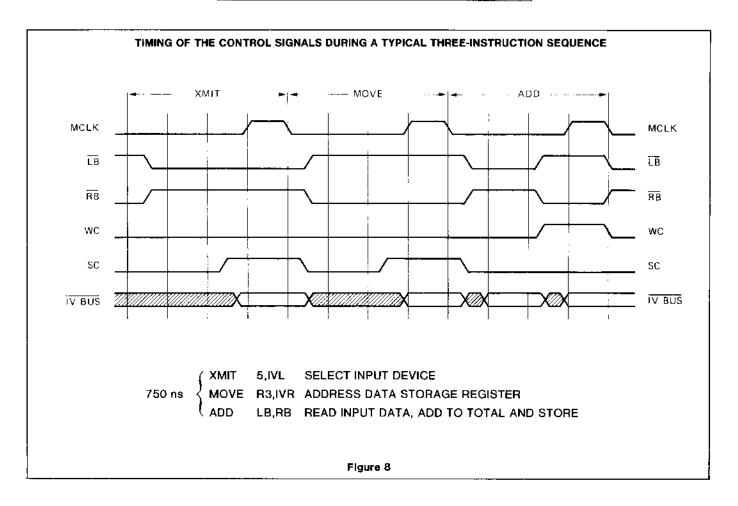

During the instruction cycle, the control and decoding logic of the 8X300 selects and activates the required timing and bus control signals in order to execute the current instruction. These signals are shown in Table 3. Figure 8 shows the timing of the control signals during a sequence of three instructions to add the data from an I/O device on the left bank to a running total in storage in a register at the right bank.

Table 3. I/O TIMING AND CONTROL SIGNALS

| SIGNAL | FUNCTION                                                                               |

|--------|----------------------------------------------------------------------------------------|

| MCLK   | Master clock: used to clock I/O devices or provide synchronization for external logic. |

| WC     | Write Command: HIGH when data is being output to the IV bus.                           |

| SC     | Select Command: HIGH level indicates that the data output on the IV bus is an address. |

| LB     | Left Bank: LOW level enables I/O registers on the left bank.                           |

| RB     | Right Bank: LOW level enables I/O registers on the right bank.                         |

# THE 8X300 INSTRUCTION SET

#### THE 8X300 INSTRUCTION SET

The 8X300 instruction set is comprised of eight classes of instruction, each identified by a different OP code value. Variations in the operand specification provide a subset of instructions within the instruction class to give a total of thirty-two instructions. The eight classes of instruction are:

- MOVE: 0 Data from the source register or IV bus is moved to the destination register or IV bus. The data may be rotated any number of places and/or masked to any length during the MOVE operation. The source data field remains unchanged after the operation.

- ADD: 1 Data from the source register or IV bus is added to the contents of the AUX register in ALU and the result is placed in the destination register or IV bus. The data may be rotated and/or masked during the operation. The source data field and the AUX register remain unchanged unless one is also the destination.

- AND: 2 Data from the source register or IV bus is ANDed with the contents of the AUX register and the

result is placed in the destination register or IV

bus. The data may be rotated and/or masked

during the operation. The source data field and

AUX register remain unchanged unless one of

those is also the destination.

- XOR: 3 Data from the source register or IV bus undergoes an EXCLUSIVE OR comparison with the contents of the AUX register. The result is placed in the destination register or IV bus. Data may be rotated and/or masked during the operation. The source data field and AUX register remain unchanged unless one of those is also the destination.

- XEC: 4 Causes execution of the instruction at the address formed by replacing the least significant bits of the last address with the sum of the I field and the data in the source register or IV byte. After execution of the instruction at the specified address, instruction execution continues at the address following the XEC instruction, unless the executed instruction caused a jump.

- NZT: 5 The least significant bits of the instruction address are replaced by the I field data if the register or IV bus specified by the source field has non-zero contents. The tested data field remains unchanged.

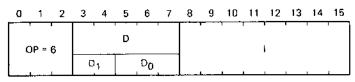

- XMIT: 6 The data in the I field is placed in the register or IV bus specified as the destination.

- JMP: 7 The address of the next instruction to be executed is changed to that specified by the 13bit A field of the instruction.

#### MCCAP — MicroComputer Cross Assembler Program for the 8X300

A cross assembler program is available to translate programs written in mnemonic source code. This is far more convenient and includes the advantages of explanatory text within the source program and error detection during the assembly process. The relevant assembler statement is shown in each example of the 8X300 instructions to provide correlation between the cross assembler statements and the 8X300 instruction code. A complete description of MCCAP and listings of typical programs are given at the end of this manual.

The cross assembler is written in FORTRAN and can be used on most computer systems capable of accepting this source language.

MOVE, Register, Register

#### **Format**

Operation

| ) |

|---|

|   |

| 0      | 1      | 2 | 3 | 4 | 5              | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13             | 14 | 15 |

|--------|--------|---|---|---|----------------|---|---|---|---|----|----|----|----------------|----|----|

| c      | )P = ( | 0 |   |   | s              |   |   |   | R | į  |    |    | D              |    |    |

| OF = 0 |        | S | 1 |   | s <sub>0</sub> |   |   |   |   | D  | 1  |    | D <sub>0</sub> |    |    |

#### Description

The contents of the register specified by S are right rotated as specified by R and placed in the destination register specified by D. The contents of the source register remain unchanged. The original contents of the destination register are lost.

S specifies the source register.

R specifies the number of places that the source data is to be rotated.

D specifies the destination register.

The order of operation is:

copy the contents of the source register;

right rotate the copied data R places;

move the rotated data to the destination register.

#### Permitted operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 00/01/02/03/04/05/06/11

#### Example

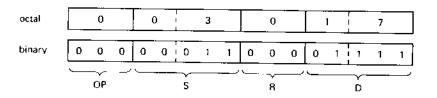

MOVE, Register, Register

Move the contents of R1, right rotated 2 places, to the AUX register.

#### Instruction word

Assembler notation

MOVE R1 (2), AUX

#### Instruction operation

Copy source register R1 (S = 01)

Rotate 2 places (R = 2)

1 0 1 0 0 1 0 1

Move result into AUX (D = 00)

#### Result

The original contents of the AUX register are replaced by the rotated data of  $R_1$ . The contents of  $R_1$  are not changed.

MOVE, Register, IV bus address

#### **Format**

Operation

| 0 | 1      | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---|--------|---|---|---|---|----------------|---|---|---|----|----|----|----|----|----|

|   | )P = 1 | n |   |   | s |                |   |   | R |    |    |    | D  |    |    |

|   |        |   | S | 1 |   | s <sub>0</sub> |   |   |   |    |    | 1  |    | Do |    |

Enable IV byte with address (S)

#### Description

Enable the IV byte, at the bank specified by D, whose address is given by the right rotated contents of the register specified by S.

S specifies the source register.

R specifies the number of places that the source data is to be rotated.

D specifies the destination bank of the IV bus for the address data:

D = 07 specifies the left bank;

D = 17 specifies the right bank.

The order of operation is:

rotate the copied contents of register S by R places;

output the result to the IV bus as an address.

The contents of the source register remain unchanged after the instruction.

#### Operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 07/17

## Example

MOVE, Register, IV bus address

Select the working storage register at the right bank whose address is given by the contents of R3.

#### Instruction word

Assembler notation

MOVE R3 (0), IVR

#### Instruction operation

#### Result

The previously enabled IV byte on the right bank is disabled and the byte with address 004 on the right bank is enabled.

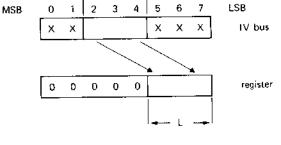

#### **Data Flow**

MOVE, Register, IV bus

#### **Format**

Operation

(S) → D

| 0 | 1         | 2 | 3   | 4 | 5 | 6              | 7 | 8        | 9     | 10 | 11 | 12 | 13 | 14 | 15 |

|---|-----------|---|-----|---|---|----------------|---|----------|-------|----|----|----|----|----|----|

|   | )<br>DP = | n |     |   | s |                |   |          | <br>_ | •  |    | 1  | D  |    | '  |

| ` |           |   | F - | 1 | ļ | S <sub>0</sub> |   | <u> </u> | ı     | ا  | £  | 1  |    | DO |    |

#### Description

Move the least significant L bits of the register specified by S to the variable length field of the IV bus.

- S specifies the source register.

- specifies the length (number of bits) of the masked data field that is to be merged with the existing IV byte data. (L = 0 selects an 8-bit field.)

- D<sub>1</sub> specifies the bank of the IV bus which is the destination:

- $D_1 = 2$  selects the left bank;

- $D_1 = 3$  selects the right bank.

- D<sub>O</sub> specifies the bit position in the IV byte with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit D<sub>O</sub> of the IV bus.

The order of operation is:

read the contents of the selected IV byte into the IV latches;

copy the contents of the source register;

shift the copied data field as specified by Do;

merge the least significant L bits with the data in the IV latches;

output the modified data field to the IV byte.

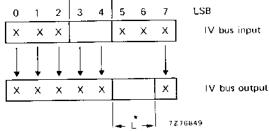

0 1 2 3 4 5 6 7 LS8

X X X X X Source register

X X X X X IV bus

Note that the original data in the IV byte outside the merged L-bit field remains unaltered. The contents of the source register remain unchanged.

#### Operand values

S: 00/01/02/03/04/05/06/10/11

L: 1/2/3/4/5/6/7/0

Do: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3

Note that L = 0 selects an 8-bit field.

MSB

#### Example

MOVE, Register, IV bus

Move the contents of the least significant 3 bits of register 11 to the selected IV byte at the left bank, with bit 5 as the least significant position of the IV byte.

#### Instruction word

Assembler notation

MOVE R11, 3, LIV5

#### Instruction operation

#### Result

Content of bits 5, 6 and 7 of R11 inserted in bits 3, 4 and 5 of the IV byte. Bits 0, 1, 2, 6 and 7 of the IV byte unchanged.

MOVE, IV bus, Register

#### **Format**

Operation

(IV byte) → D

| 0 | 1      | 2      | 3 | 4 | 5  | 6              | 7 | 8 | 9 | 10 | 11_ | 12 | 13 | 14 | 15 |

|---|--------|--------|---|---|----|----------------|---|---|---|----|-----|----|----|----|----|

|   | )P = ( | י<br>נ | , |   | \$ |                |   |   | L |    |     | 1  | D  |    |    |

|   | OP = 0 |        |   | 1 |    | s <sub>0</sub> | _ |   |   |    | С   | 1  |    | Do |    |

#### Description

Move the L-bit field of the IV bus data to the least significant L bits of the register specified by D.

S1 specifies the bank of the IV bus which is the data source.

S<sub>1</sub> = 2 selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the input data field after rotation.

specifies the length (number of bits) of the masked field.

Note that L = 0 selects an 8-bit field.

D specifies the address of the destination register.

The order of operation is:

read data on IV bus specified by S1 to input latches;

right rotate the input data field as given by So;

mask off the least significant L bits of the rotated field;

move the masked field to the least significant L bits of the destination register, with zeros in the unmasked positions.

#### Operand values

So: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0

D: 00/01/02/03/04/05/06/11

#### Example

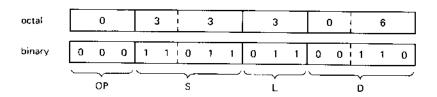

MOVE, IV bus, Register

Move bits 1, 2 and 3 of the enabled IV byte at the right bank to register 6.

#### Instruction word

Assembler notation

MOVE RIV3, 3, R6

#### Instruction operation

#### Result

Bits 1, 2 and 3 of the IV byte at the right bank are inserted into the least significant 3 bits of R6. The other bits of R6 are set to zero. The source IV byte is not altered.

MOVE, IV bus, IV bus

**Format**

Operation

(S) → D

| 0 | 1      | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14             | 15 |

|---|--------|---|---|---|---|----------------|---|---|---|----|----|----|----|----------------|----|

|   | )P =   | n |   |   | S | ,              | • |   |   |    |    | r  | D  | •              | .  |

|   | )r = 1 |   | S | 1 |   | S <sub>0</sub> |   | Ì | _ |    |    | 1  |    | D <sub>0</sub> |    |

#### Description

Move the variable length field, specified by  $S_0$  and L, from the bank specified by  $S_1$  to the field and bank specified by D.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

specifies the length (number of bits) of the masked field that is to be processed and merged with the existing IV bus data.

Note that L = 0 selects an 8-bit field.

${\bf D_1}$  specifies the bank of the IV bus which is the destination:

$D_1 = 2$  selects the left bank;

$D_1 = 3$  selects the right bank.

D<sub>0</sub> specifies the bit position in the data from the input latches with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit D<sub>0</sub> of the input latches.

The order of operation is:

read the data from the source IV byte into the input latches;

copy the input data and right rotate as specified by So;

mask off the least significant L bits;

shift left as specified by Do;

merge the L-bit field with the data from the input latches;

output 8 bits of data to IV bus.

6 **LSB** MSB n 1 2 Х IV bus input Х Х Х х IV bus output Х Х Х х

Note that during the merge phase, the original values of the source field bits outside the masked field are preserved.

#### Operand values

S<sub>0</sub>: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0 D<sub>0</sub>: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3

#### **Example**

MOVE, IV bus, IV bus

Move bits 0, 1 and 2 of the IV byte at the Left Bank to bits 3, 4 and 5 of the same IV byte.

#### Instruction word

Assembler notation

MOVE LIV2, 3, LIV5

#### Instruction operation

#### Result

Bits 3, 4 and 5 contain the same values as bits 0, 1 and 2. All other bits unchanged.

MOVE, IV bus, IV bus address

#### **Format**

Operation

|   | 0      | 1      | 2 | 3 | 4 | 5 | 6   | 7 | 8 | 9                                            | 10 | 11 | 12 | 13       | 14 | 15 |

|---|--------|--------|---|---|---|---|-----|---|---|----------------------------------------------|----|----|----|----------|----|----|

|   | C      | )P = 1 | 0 |   |   | s |     |   |   | L                                            |    |    |    | D        |    |    |

| ! | OP # Q |        |   | S | 1 |   | \$0 | ı |   | <u>.                                    </u> |    | Ξ  | 1  | <u> </u> | Do |    |

Enable the IV byte at the bank specified by D, whose address is given by the bus data specified by S.

#### Description

Copy the data from the IV bus as specified by  $S_1$ , right rotate the data field until bit  $S_0$  is in the least significant position, mask the least significant L bits and output the result to the bank of the IV bus specified by D, as an IV byte address. Bits of the output field outside the mask are set to zero.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

L specifies the length (number of bits) of the masked field.

D specifies the destination bank of the IV bus for the address data:

D = D7 specifies left bank address (IVL);

D = 17 specifies right bank address (IVR).

The order of operation is:

copy the input data on the IV bus;

right rotate the input data as given by So;

mask the least significant L bits;

output result with zeros in positions outside mask.

#### Operand values

So: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0

D: 07/17.

Note that L = 0 specifies 8-bit field.

#### Example

MOVE, IV bus, IV bus address

Enable the IV byte at the left bank whose address is the value of bits 2, 3 and 4 of the presently enabled IV byte at the left bank.

#### Instruction word

Assembler notation

MOVE LIV4, 3, IVL

#### Instruction operation

#### Result

The IV byte, at the address given by bits 2, 3 and 4 of the previously enabled byte, is enabled. As both bytes are on the same bank, the source byte is disabled when the new address is output on the bus.

ADD, Register, Register

#### **Format**

Operation

(S) plus (AUX) → D

| 0 | 1         | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10 | 11_ | 12 | 13 | 14             | 15 |

|---|-----------|---|---|---|---|----------------|---|---|---|----|-----|----|----|----------------|----|

| , | )<br>)P = | 1 |   | l | s |                |   |   | R | T  |     |    | D  |                | '  |

|   |           |   | S | 1 |   | s <sub>o</sub> |   |   |   |    | D   | 1  |    | D <sub>0</sub> | ]  |

#### Description

Add the right rotated contents of register S to the contents of the AUX register and place the result in register D. If overflow occurs during the addition, bit 7 of the OVF register is set to 1, otherwise it is set to 0.

S specifies the source register.

R specifies the number of places that the source data is to be rotated.

D specifies the destination register.

The order of operation is:

copy the contents of the source register;

right rotate the copied data;

add the right rotated data to the contents of the AUX register;

move the result to the destination register;

set the overflow indication as appropriate.

The contents of the source and AUX registers remain unchanged after the instruction unless one of these is also specified as the destination.

#### Operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 00/01/02/03/04/05/06/11

#### Example

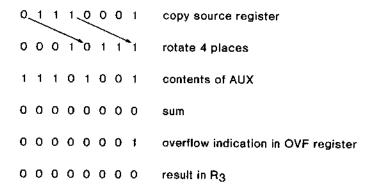

ADD, Register, Register

Add the contents of R1, right rotated 4 places, to the contents of the AUX register and store the result in R3.

#### Instruction word

Assembler notation

ADD R1 (4), R3

#### Instruction operation

#### ADD, Register, IV bus address

Operation

#### Format

Enable the IV byte with address (S) plus (AUX).

|  | 0      | 1 | 2 | 3                             | 4 | 5  | 6 | 7 | 8 | 9 | 10  | 11 | 12 | 13 | 14 | 15 |  |

|--|--------|---|---|-------------------------------|---|----|---|---|---|---|-----|----|----|----|----|----|--|

|  | OP = 1 |   |   |                               |   | \$ | , |   | R |   |     | D  |    |    |    |    |  |

|  |        |   |   | s <sub>1</sub> s <sub>0</sub> |   |    |   |   |   |   | . ! | C  | 1  |    | 00 |    |  |

#### Description

Enable the IV byte whose address is given by the sum of the right rotated contents of the source register and the contents of the AUX register at the bank specified by D.

- S specifies the source register.

- R specifies the number of places that the source data is to be rotated.

- D specifies the destination bank of the IV bus for the address data:

- D = 07 specifies left bank address (IVL);

- D = 17 specifies right bank address (IVR).

The order of operation is:

rotate the copied contents of register (S) by R places;

add the rotated data field to the contents of AUX;

set the overflow indication as appropriate;

output the sum to the IV bus as an address.

The contents of the source register remain unchanged after the instruction.

#### Operand values

8: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 07/17

#### Example

ADD, Register, IV bus address

Enable the IV byte at the right bank whose address is the sum of the contents of R3 and AUX.

#### Instruction word

Assembler notation

ADD R3 (0), IVR

#### Instruction operation

0 0 0 1 0 1 1 0 copy source data

0 0 0 1 0 1 1 0 no rotation (R = 0)

0 0 0 0 1 1 0 1 sum

0 0 0 0 1 1 0 1 result to IV bus as an address at the right bank (D = 17)

#### Result

The IV byte on the right bank, whose address is the sum of the contents of R3 and the AUX register, is enabled.

ADD, Register, IV bus

Operation

#### **Format**

(S) plus (AUX) → D

| 0      | 1 | 2 | 3 | 4 | 5 | 6  | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14             | 15 |  |

|--------|---|---|---|---|---|----|---|---|---|----|----|----|----|----------------|----|--|

| OP = 1 |   |   |   |   | S |    |   |   | L |    | D  |    |    |                |    |  |

|        |   |   | 5 | 1 |   | So |   |   |   | J  | C  | 1  |    | D <sub>O</sub> |    |  |

#### Description

Add the contents of the source register to the contents of the AUX register and move the least significant L bits of the result to the IV bus as given by D.

- S specifies the source register.

- L specifies the length (number of bits) of the masked field that is to be merged with the existing IV byte data. Note that L = 0 selects an 8-bit field.

$D_1$

specifies the bank of the IV bus which is the destination:

$D_1 = 2$  selects the left bank;

$D_1 = 3$  selects the right bank.

Do

specifies the bit position in the IV byte with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit  $D_0$  of the IV bus.

The order of operation is:

the contents of the destination IV byte are read into the input latches;

the contents of the source register are copied and added to the contents of the AUX register;

the result is left shifted as specified by D;

the overflow indication is set as appropriate;

the shifted data field is merged with the original contents of the IV byte and output to the IV bus.

Note that the bits of the output data field outside the L-bit masked field retain their original values. The contents of the source register remain unchanged after the instruction.

#### Operand value

S: 00/01/02/03/04/05/06/10/11

L: 1/2/3/4/5/6/7/0

Do: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3

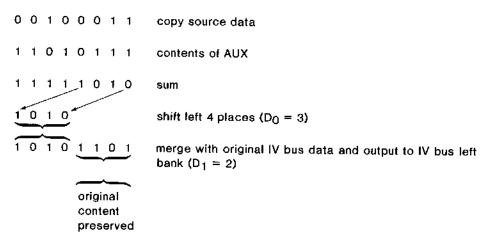

#### Example

ADD, IV bus, Register

Add the contents of R11 to the contents of the AUX register and output the least significant 4 bits of the sum to bits 0, 1, 2 and 3 of the IV byte at the Left Bank.

#### Instruction word

**Assembler notation**

ADD R11, 4, LIV3

#### Instruction operation

#### Result

Bits 0, 1, 2 and 3 of the IV byte at the left bank are set to the values of the least significant 4 bits of the sum of (R11) and (AUX). The overflow indicator is set to zero.

ADD, IV bus, IV bus

#### **Format**

Operation

(S) plus (AUX) → D

| 0   | 1      | 2 | 3  | 4 | 5        | 6   | 7 | 8 | 9 | 10 | 11_ | 12 | 13 | 14 | 15 |

|-----|--------|---|----|---|----------|-----|---|---|---|----|-----|----|----|----|----|

| · " |        |   |    |   | <u> </u> |     | 1 |   | - |    |     | '  | Ð  | •  | '  |

| C   | OP = 1 |   |    |   |          |     |   |   | L |    |     |    |    |    |    |

| 1 . |        |   | \$ | 1 |          | \$0 |   |   |   |    |     | 1  |    | 00 | 1  |

#### Description

Add the L-bit field of the IV bus source data to the contents of the AUX register and move the least significant L bits of the result to the IV bus field specified by D<sub>0</sub>.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

specifies the length (number of bits) of the masked field that is to be processed and merged with the existing IV bus data.

Note that L = 0 selects an 8-bit field.

D<sub>1</sub> specifies the bank of the IV bus which is the destination:

$D_1 = 2$  selects the left bank;

$D_1 = 3$  selects the right bank.

D<sub>O</sub> specifies the bit position in the IV byte with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit D<sub>O</sub> of the IV bus.

The order of operation is:

read the data from the IV bus into the input latches;

right rotate the copied input data as given by So;

mask off L bits;

add the L-bit field to the contents of the AUX register;

left-shirt the sum as given by  $D_0$ ;

merge the least significant L bits of the shifted field with the contents of the input latches;

\* processed data

output the merged 8-bit field to the bank of the IV bus given by D<sub>1</sub>.

Note that during the merge phase, the original values of the source field outside the masked field are preserved. The original contents of the destinction field are lost.

#### Operand values

So: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0 Do: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3

MSB

#### Example

ADD, IV bus, Register

Add bits 0, 1, 2 and 3 of the IV byte at the right bank to the contents of the AUX register and store the result in the AUX register.

#### Instruction word

Assembler notation

ADD RIV3, 4, AUX

#### Instruction operation

#### Result

The 4 most significant bits of the IV byte are added to the AUX register contents. The overflow indicator is set to zero.

#### ADD, Register, IV bus

Operation

Format

(S) plus (AUX) → D

| 0 1 2  | 3   | 4                             | 5 | 6 | 7 | 8 | 9 | 10 | 11                            | 12 | 13 | 14 | 15 |  |

|--------|-----|-------------------------------|---|---|---|---|---|----|-------------------------------|----|----|----|----|--|

|        | Ţ ' | ,                             | s | r | r |   |   | 1  |                               |    | D  |    |    |  |

| OP = 1 | \$  | s <sub>1</sub> s <sub>0</sub> |   |   |   |   |   |    | D <sub>1</sub> D <sub>0</sub> |    |    |    |    |  |

#### Description

Add the L-bit field of the IV bus source data to the contents of the AUX register and place the result in the destination register. Set the overflow indicator as appropriate.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

S<sub>1</sub> = 2 selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

- specifies the length (number of bits) of the masked field.

Note that L = 0 selects an 8-bit field.

- D specifies the address of the destination register.

The order of operation is:

read the source IV byte data into the input latches;

right rotate the input data as given by So;

mask the rotated data field as specified by L;

add the masked data to the contents of the AUX register;

set the overflow indicator as appropriate;

move the result of the addition to the destination register.

#### Operand values

S<sub>0</sub>: 2/3

S<sub>1</sub>: 0/1/2/3/4/5/6/7

L: 1/2/3/4/5/6/7/0

D: 00/01/02/03/04/05/06/11

Note that L = 0 selects an 8-bit field.

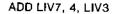

### Example

ADD, IV bus, IV bus

Add the contents of bits 4 to 7 of the IV byte at the left bank to the contents of the AUX register and move the least significant 4 bits of the sum to the most significant 4 bits of the IV byte at the left bank.

#### Instruction word

Assembler notation

#### Instruction word

### Result

The 4 most significant bits of the IV byte are changed to the values given by the sum of the 4 least significant bits and the contents of the AUX register. The overflow indicator is set to 0.

ADD, IV bus, IV bus address

#### **Format**

Operation

(S) plus (AUX)-→D

| 0 | 1     | 2 | 3     | 4 | 5  | 6  | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14             | 15 |

|---|-------|---|-------|---|----|----|---|---|---|----|----|----|----|----------------|----|

|   | )P -  |   |       |   | \$ | Τ' |   |   | 1 |    |    |    | D  | ,              |    |

|   | , F · |   | <br>S | 1 |    | So |   |   |   |    | 0  | 1  |    | D <sub>0</sub> |    |

#### Description

Enable the IV byte, at the bank specified by D<sub>1</sub>, whose address is given by the sum of the L-bit field of the source data and the contents of the AUX register.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

L specifies the length (number of bits) of the masked field Note that L = 0 selects an 8-bit field.

D specifies the destination bank of the IV bus for the address data:

D = 07 specifies left bank address (IVL);

D = 17 specifies right bank address (IVR).

The order of operation is:

read the data from the current IV byte into the input latches;

right rotate the copied input data as given by So;

mask off the least significant L bits;

add the masked field to the contents of the AUX register;

set the overflow indicator as appropriate;

output the data as in IV bus address at the bank specified by D.

#### Operand values

So: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0

D: 07/17

# Example

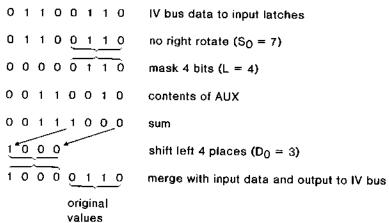

ADD, IV bus, IV bus address

Enable the IV byte at the left bank whose address is the sum of the contents of the AUX register and bits 5, 6 and 7 of the presently enabled IV byte at the left bank.

#### Instruction word

Assembler notation

ADD LIV7, 3, IVL

### Instruction operation

### Result

Original address at left bank disabled and new address, given by sum above, enabled.

AND, Register, Register

### **Format**

Operation

(S)  $\Lambda$  (AUX)  $\rightarrow$  D

| 0 | 1     | 2        | 3 | 4 | 5  | 6  | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14             | 15 |

|---|-------|----------|---|---|----|----|---|---|---|----|----|----|----|----------------|----|

| 0 | P = 2 | <u>.</u> |   |   | \$ |    |   |   | R | •  |    |    | D  |                |    |

| L | 4     |          | S | 1 |    | so |   |   |   |    | ۵  | 1  |    | D <sub>0</sub> |    |

#### Description

ADD the right rotated contents of register S with the contents of the AUX register and place the result in register D.

S specifies the source register.

R specifies the number of places that the source data is to be rotated.

D specifies the destination register.

The order of operation is:

copy the contents of the source register;

right rotate the copied data;

AND the right rotated data with the contents of the AUX register;

move the result to the destination register.

The contents of the source and AUX registers remains unchanged after the instruction unless one of these is also the destination register.

### Operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 00/01/02/03/04/05/06/11

# Example

AND, Register, Register

AND the contents of R3 to the contents of the AUX register and store the result in R3.

### Instruction word

Assembler notation

AND R3 (0), R3

### Instruction operation

0 0 0 0 1 1 1 1 initial contents of R3 (no rotation, R = 0)

0 0 0 0 0 0 1 1 contents of AUX

0 0 0 0 0 0 1 1 result of AND function

0 0 0 0 0 0 1 1 new contents of R3

#### Result

R3 new contains the result of ANDing its original contents with those of the AUX register.

AND, Register, IV bus address

#### **Format**

Operation

Enable IV byte with address (S) A (AUX).

### **Description**

Enable the IV byte, at the bank specified by D, whose address is given by the AND operation on the right rotated contents of the source register and the contents of the AUX register.

S specifies the source register.

R specifies the number of places that the source data is to be rotated.

D specified the destination bank of the IV bus for the address data:

D = 07 specifies the left bank;

D = 17 specifies the right bank.

The order of operation is:

rotate the copied contents of register S by R places;

AND the rotated data field with the contents of AUX;

output the result to the IV bus as an address.

The contents of the source register remain unchanged after the instruction.

#### Operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 07 / 17

# Example

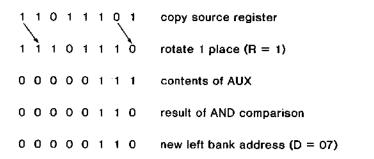

AND, Register, IV bus address

Select the IV byte at the left bank, whose address is contained in bits 4, 5 and 6 of register R3. It is assumed that the AUX register already contains the required mask.

#### Instruction word

Assembler notation

AND R3 (1), IVL

### Instruction operation

### Result

The IV byte on the left bank with address 006 is enabled.

AND, Register, IV bus

#### **Format**

Operation

(S) A (AUX)→D

| 0 1 2  | 3 4            | 5 | 6              | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|--------|----------------|---|----------------|---|---|---|----|----|----|----|----|----|

| OP = 2 | ,              | S | · <del>T</del> |   |   | L |    |    |    | D  |    |    |

|        | s <sub>1</sub> |   | s <sub>o</sub> |   |   |   |    | D  | 1  |    | DO |    |

#### Description

Perform an AND operation on the source register contents and those of the AUX register and move the least significant L bits of the result to the destination field of the IV bus.

- S specifies the source register.

- specifies the length (number of bits) of the masked field that is to be merged with the existing IV byte data.

Note that L = 0 selects an 8-bit field.

- D<sub>1</sub> specifies the bank of the IV bus which is the destination:

- $D_1 = 2$  selects the left bank;

- $D_1 = 3$  selects the right bank.

- $D_0$  specifies the bit position in the IV byte with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit  $D_0$  of the IV bus.

The order of operation is:

- the contents of the destination IV byte are read into the input latches;

- the contents of the source register are copied and ANDed with the contents of the AUX register.

- the result is left-shifted as specified by D:

- the shifted data field is merged with the original contents of the IV byte and output to the IV byte.

Note that the bits of the output data field outside the L-bit processed field retain their original values. The contents of the source register remain unchanged after the instruction.

#### Operand values

\$: 00/01/02/03/04/05/06/10/11

L: 1/2/3/4/5/6/7/0

D<sub>0</sub>: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3

# Example

AND, Register, IV bus

Perform an AND operation on the contents of R6 and the AUX register and move the least significant 3 bits of the result to bits 1, 2 and 3 of the IV byte at the left bank.

### Instruction word

Assembler notation

AND R6, 3, LIV3

### Instruction operation

### Result

The 3-bit result of the AND operation is moved to bits 1, 2 and 3 of the IV byte at the left bank

AND, IV bus, Register

#### **Format**

Operation

(S) A (AUX)→D

| 0 | 1     | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---|-------|---|---|---|---|----------------|---|---|---|----|----|----|----|----|----|

|   | P = 2 | 2 | , |   | S |                |   |   | L |    |    |    | D  |    |    |

|   |       |   | S | 1 |   | s <sub>o</sub> |   |   |   |    | D  | 1  |    | DO |    |

#### Description

Perform an AND operation on the L-bit field of the IV bus source data and the contents of the AUX register.

S<sub>1</sub> specificies the bank of the IV bus which is the data source;

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

specifies the length (number of bits) of the masked field.

Note that L = 0 selects an 8-bit field.

D specifies the address of the destination register.

The order of operation is:

read the contents of the IV byte into the input latches;

right rotate the input data as given by So;

mask the rotated data field as specified by L;

AND the masked data to the contents of the AUX register;

move the result to the destination register.

#### Operand values

So 2/3

S<sub>1</sub> 0/1/2/3/4/5/6/7

L: 1/2/3/4/5/6/7/0

D: 00/01/02/03/04/05/06/11.

Note that L = 0 selects an 8-bit field.

# Example

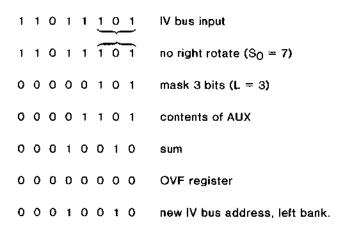

AND, IV bus, Register

Perform an AND operation on the contents of the IV byte at the left bank and the contents of the AUX register and store the result in R4.

Instruction word

Assembler notation

AND LIV7, 8, R4

### Instruction operation

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | IV bus input              |

|---|---|---|---|---|---|---|---|---------------------------|

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | no rotation ( $S_0 = 7$ ) |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | no mask (L = 8 bits)      |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | contents of AUX           |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | result of AND             |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | new contents of R4        |

#### Result

R4 contains the result of the AND operation on the contents of the left bank of the IV bus and the AUX register.

AND, IV bus, IV bus

Operation

#### Format

(S) A (AUX) → D

| 0 | 1      | 2 | 3 | 4 | 5  | 6              | 7 | 8 | 9 | 10 | 11 | 12      | 13 | 14 | 15 |

|---|--------|---|---|---|----|----------------|---|---|---|----|----|---------|----|----|----|

|   | )P = : | 2 |   |   | ·s |                |   |   | L | •  |    | · · · · | D  |    |    |

|   |        |   | S | 1 |    | s <sub>0</sub> |   |   | ı | 1  | ۵  | 1       |    | Do |    |

### Description

Perform an AND operation on the L-bit field of the IV bus source data and the contents of the AUX register, and move the least significant L bits of the result to the destination field of the IV bus.

- S<sub>1</sub> specifies the bank of the IV bus which is the data source:

- $S_1 = 2$  selects the left bank;

- $S_1 = 3$  selects the right bank.

- So specifies the bit which will be the least significant bit of the rotated input data field.

- specifies the length (number of bits) of the masked field that is to be processed and merged with the existing IV bus source data.

Note that L = 0 selects an 8-bit field.

- D<sub>1</sub> specifies the bank of the IV bus which is the destination:

- $D_1 = 2$  selects the left bank;

- $D_1 = 3$  selects the right bank.

- D<sub>O</sub> specifies the bit position in the data from the input latches with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit D<sub>O</sub> of the input latches.

The order of operation is:

- read the data from the IV bus into the input latches;

- right rotate the copied input data as given by So;

- mask off the least significant L bits;

- perform the AND operation on the contents of the AUX register;

- left-shift the result as given by Do;

- merge the least significant L bits of the shifted field with the contents of the input latches;

- output the merged 8-bit field to the bank of the IV bus given by D<sub>1</sub>.

Note that during the merge phase the original values of the bits outside the masked field are preserved. The original data in the destination IV byte is lost.

#### Operand values

S<sub>0</sub>: 0/1/2/3/4/5/6/7

S1: 2/3

L: 1/2/3/4/5/6/7/0 D<sub>0</sub>: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3.

Example AND, IV bus, IV bus

Mask the most significant 4 bits of the IV bus data at the left bank and move the result to the IV byte at the right bank. (It is assumed that the AUX register has already been loaded with the required contents for this.)

Assembler notation

#### Instruction word

AND LIV7, 0, RIV7

# Instruction operation

10110110 IV bus data to input latches

10110110 no rotate or mask ( $S_0 = 7$ , L = 0)

1 1 1 1 0 0 0 0 contents of AUX

10110000 result of AND

10110000 no shift ( $D_0 = 7$ )

10110000 new IV bus data

### Result

The most significant 4 bits of the input data are moved to the IV byte at the right bank.

AND, IV bus, IV bus address

Operation

#### **Format**

(S)  $\Lambda$  (AUX)  $\rightarrow$  D

| 0 1 2  | 3 4            | 5        | 6     | 7 | 8 | 9        | 10 | 11 | 12 | 13 | 14 | 15 |

|--------|----------------|----------|-------|---|---|----------|----|----|----|----|----|----|

| OP = 2 | -              | <b>S</b> |       |   |   | ,        | •  |    | •  | D  |    |    |

| !      | S <sub>1</sub> |          | $s_0$ | L |   | <b>.</b> |    | 0  | 1  |    | DO |    |

#### Description

Enable the IV byte at the bank specified by D, whose address is the result of the AND operation on the L-bit field of the IV bus and the contents of the AUX register.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

specifies the length (number of bits) of the masked field.

Note that L = 0 selects an 8-bit field.

D specifies the destination bank of the IV bus for the address data:

D = 07 specifies left bank address (IVL);

D = 17 specifies tight bank address (IVR).

The order of operation is:

read the data from the current IV byte into the input latches;

right rotate the copied input data as given by So;

mask off the least significant L bits;

perform the AND operation on the contents of the AND registers;

output the data as an address at the bank specified by D.

### Operand values

S<sub>0</sub>: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0

D: 07/17

## Example

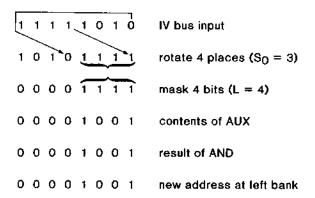

AND, IV bus, IV bus address

Enable the IV byte at the left bank whose address is the result of the AND operation on the contents of the AUX register and bits 0 to 3 of the currently enabled IV byte at the left bank.

### Assembler notation

AND LIV3, 4, IVL

### Instruction operation

Instruction word

### Result

The previously enabled byte at the left bank is disabled and the byte at address 11 (octal) is enabled.

### XOR, Register, Register

### Operation

### Format

(S) ⊕ (AUX) → D

| 0 1 | 2   | 3 | 4 | 5 | 6_             | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14             | 15 |

|-----|-----|---|---|---|----------------|---|---|---|----|----|----|----|----------------|----|

| OP  | = 3 | · |   | S | ,              |   |   | R | •  |    |    | D  |                |    |

| L.  | ,   | S | 1 |   | s <sub>0</sub> | 1 |   |   |    | 0  | 1  |    | D <sub>0</sub> |    |

### Description

Perform an exclusive OR operation on the right rotated contents of the source register and the contents of the AUX register.

S specifies the source register

R specifies the number of places that the source data is to be rotated.

D specifies the destination register.

The order of operation is:

copy the contents of the source register;

right rotate the copied data;

XOR the right rotated data with the contents of the AUX register;

move the result to the destination register.

The contents of the source and AUX registers remains unchanged after the instruction unless one of these is also specified as the destination register.

### Operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 00/01/02/03/04/05/06/11

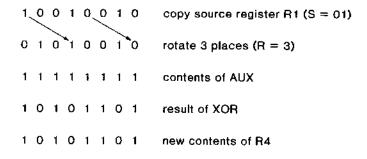

### Example

XOR, Register, Register

Perform an exclusive OR operation on the contents of R1, rotated 3 places, and the contents of the AUX register. Store the result in R4.

#### Assembler notation

XOR R1 (3), R4

# Instruction word

### Instruction operation

### Result

Register R4 holds the result of the XOR operation on the rotated contents of R1 and the contents of AUX.

XOR, Register, IV bus address

Operation

#### **Format**

Enable the IV byte with address (S) @ (AUX).

| 0 1    | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|--------|---|---|---|---|----------------|---|---|---|----|----|----|----|----|----|

| OP = : | 3 |   |   | s | ₹ I            |   |   | R | ,  | à. |    | D  |    |    |

|        |   | S | 1 |   | s <sub>0</sub> |   |   |   | ı  | C  | 1  |    | ٥٥ |    |

### Description

Enable the IV byte, at the bank specified by D, whose address is the result of the XOR operation on the right rotated contents of the source register and the contents of the AUX register.

S specifies the source register.

R specifies the number of places that the source data is to be rotated.

D specifies the destination bank of the IV bus for the address data:

D = 07 specifies left bank address (IVL);

D = 17 specifies right bank address (IVR).

The order of operation is:

rotate the copied contents of register S by R places;

XOR the rotated data field to the contents of AUX;

output the result to the IV bus as an address.

The contents of the source register remain unchanged after the instruction.

#### Operand values

S: 00/01/02/03/04/05/06/10/11

R: 0/1/2/3/4/5/6/7

D: 07/17

## Example

XOR, Register, IV bus address

Enable the IV byte at the right bank whose address is the result of the XOR operation on the contents of R3 and the AUX register.

### Instruction word

Assembler notation

XOR R3 (0), IVR

### Instruction operation

### Result

The previously enabled IV byte at the right bank is disabled and the IV byte at address 332 (octal) is enabled. The source and AUX registers remain unchanged.

XOR, Register, IV bus

Operation

(S) ⊕ (AUX) →D

### Format

| 0 1 2  | 3 4            | 5_ | 6 7            | 8 | 9                                      | 10 | 11 | 12 | 13 | 14 | 15 |

|--------|----------------|----|----------------|---|----------------------------------------|----|----|----|----|----|----|

| OP = 3 | •              | s  | 1              |   | L                                      |    |    |    | D  | 1  |    |

| 1      | S <sub>1</sub> | ,  | s <sub>o</sub> |   | ــــــــــــــــــــــــــــــــــــــ |    | ۵  | 1  |    | DO |    |

### Description

Perform an exclusive OR operation on the contents of the source register and the contents of the AUX register. Move the least significant L bits of the result to the L-bit field of the IV bus.

- S specifies the source register.

- specifies the length (number of bits) of the masked field that is to be merged with the existing IV byte data.

Note that L = 0 selects an 8-bit field.

- D<sub>1</sub> specifies the bank of the IV bus which is the destination:

$D_1 = 2$  selects the left bank;

$D_1 = 3$  selects the right bank.

Do specifies the bit position in the IV byte with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit Do of the IV bus.

The order of operation is:

read the data of the destination IV byte into the input latches;

copy the contents of the source register and perform an XOR operation on the contents of the AUX register;

left-shift the result as specified by Do;

merge the least significant L-bits of the shifted field with the data in the input latches;

output the merged data to the IV bus.

Note that the bits of the output data field outside the L-bit masked field retain their original values. The contents of the source register remain unchanged after the instruction.

#### Operand values

S: 00/01/02/03/04/05/06/10/11

L: 1/2/3/4/5/6/7/0

DO: 0/1/2/3/4/5/6/7

D<sub>1</sub>: 2/3

Note: L = 0 selects an 8-bit field.

# Example

XOR, Register, IV bus

Store the one's complement of the contents of R5 in the IV byte at the right bank. (It is assumed that the AUX register already contains all ones.)

#### Instruction word

Assembler notation

XOR R5, 0, RIV7

### Instruction operation

0 1 1 0 0 1 1 1 copy source register

1 1 1 1 1 1 1 1 contents of AUX

1 0 0 1 1 0 0 0 result of XOR

1 0 0 1 1 0 0 0 no shift ( $D_0 = 7$ )

1 0 0 1 1 0 0 0 data to IV bus

### Result

The one's complement of the source register is output to the right bank of the IV bus.

XOR, IV bus, Register

#### **Format**

Operation

| 0 | 1         | 2 | 3 | 4 | 5 | 6              | 7  | 8 | 9                                            | 10 | $11 \times 12$ | 13  | 14             | 15_ |

|---|-----------|---|---|---|---|----------------|----|---|----------------------------------------------|----|----------------|-----|----------------|-----|

|   | '<br>OP = | 3 |   |   | S |                |    |   | L.                                           |    |                | ָ ח |                |     |

|   |           |   | S | 1 |   | s <sub>0</sub> | 1, |   | <u>.                                    </u> |    | D <sub>1</sub> |     | D <sub>0</sub> |     |

# Description

Perform an exclusive OR operation on the L-bit field of the IV bus source data and the contents of the AUX register. Move the 8-bit result to the register specified by D.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  selects the left bank;

$S_1 = 3$  selects the right bank.

So specifies the bit which will be the least significant bit of the rotated input data field.

L specifies the length (number of bits) of the masked field.

Note that L = 0 selects an 8-bit field.

D specifies the address of the destination register.

The order of operation is:

read the IV bus data into the input latches;

right rotate the input field as specified by So;

mask the rotated data field as specified by L;

XOR the masked data with the contents of the AUX register;

move the 8-bit result to the destination register.

#### Operand values

\$0: 2/3

S<sub>1</sub>: 0/1/2/3/4/5/6/7

L: 1/2/3/4/5/6/7/0

D: 00/01/02/03/04/05/06/11

Note that L = 0 selects an 8-bit field.

# Example

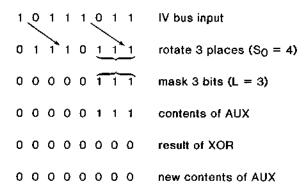

XOR, IV bus, Register

Perform an exclusive OR operation on the contents of bits 2, 3 and 4 of the IV byte at the left bank and the contents of the AUX register. Store the result in the AUX register.

### Instruction word

Assembler notation

XOR LIV4, 3, AUX

### Instruction operation

### Result

The contents of the AUX register are changed to the result of the XOR operation. The source IV byte remains unchanged.

XOR, IV bus, IV bus

#### **Format**

Operation

(S) ⊕ (AUX) → D

| 0 | 1      | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14             | 15 |

|---|--------|---|---|---|---|----------------|---|---|---|----|----|----|----|----------------|----|

|   | )P = : | , | ' |   | s |                | 1 |   |   | •  |    |    | D  |                |    |

| ` | )r     |   | S | 1 |   | s <sub>0</sub> |   |   |   |    | С  | 1  |    | D <sub>0</sub> |    |

#### Description

Perform an exclusive OR operation on the L-bit field of the IV bus source data and the 8-bit contents of the AUX register and move the least significant L bits of the result to the destination field of the IV bus, given by D.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  specifies the left bank;

$S_1 = 3$  specifies the right bank.

So specifies the bit which will be the least significant bit of the input data field after rotation.

specifies the length (number of bits) of the masked field that is to be processed and merged with the existing IV bus source data.

Note that L = 0 selects an 8-bit field.

D<sub>1</sub> specifies the bank of the IV bus which is the destination:

$D_1 = 2$  specifies the left bank;

$D_1 = 3$  specifies the right bank.

D<sub>0</sub> specifies the bit position in the data from the input latches with which the least significant bit of the processed data field should be aligned. This means that the processed data field is left-shifted so that bit 7 is aligned with bit D<sub>0</sub> of the input latches.

The order of operation is:

read the IV bus data into the input latches;

right rotate the input data field until bit So becomes the LSB;

mask the least significant L bits;

XOR the masked field with the contents of the AUX register;

left-shift the result until bit 7 is aligned with bit Do;

merge the least L bits with the original IV bus data from the input latches;

output the merged 8-bit field to the IV bus.

Note that during the merge phase, the original values of the bits outside the masked field are preserved. The original data in the destination IV byte is lost.

# Permitted operand values

So: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0 D<sub>0</sub>: 0/1/2/3/4/5/6/7

D<sub>1: 2/3</sub>

Note that L = 0 selects an 8-bit field.

### Example

XOR, IV bus, IV bus

Perform exclusive OR operation on the contents of the AUX register and the contents of the IV byte at the left bank and output the result to the IV byte at the right bank.

### Instruction word

Assembler notation

**XOR, LIV7, 0, RIV7**

### Instruction operation

```

1 0 1 1 1 0 1 1 IV bus input

1 0 1 1 1 0 1 1 no rotate (S_0 = 7)

1 0 1 1 1 0 1 1 no mask (L = 0)

0 0 1 0 0 1 0 1 contents of AUX

1 0 0 1 1 1 1 0 result of XOR

1 0 0 1 1 1 1 0 no shift (D_0 = 7)

1 0 0 1 1 1 1 0 new IV bus data

```

#### Result

The IV byte at the right bank contains the results of the exclusive OR operation on the contents of the AUX register and the IV byte at the left bank.

XOR, IV bus, IV bus address

#### **Format**

Operation

(S) ⊕ (AUX) → D

| 0 | 1      | 2 | 3 | 4 | 5 | 6              | 7 | 8 | 9 | 10       | 11 | 12 | 13 | 14 | 15 |

|---|--------|---|---|---|---|----------------|---|---|---|----------|----|----|----|----|----|

|   | )P = : | 3 |   |   | S |                |   |   | L |          |    |    | D  |    |    |

|   |        |   | ş | 1 |   | s <sub>0</sub> |   |   |   | <b>L</b> | C  | 1  |    | ٥٥ |    |

#### Description

Enable the IV byte, at the bank specified by D, whose address is the result of the XOR operation on the L-bit field of the IV bus and the contents of the AUX register.

S<sub>1</sub> specifies the bank of the IV bus which is the data source:

$S_1 = 2$  specifies the left bank;

$S_1 = 3$  specifies the right bank.

So specifies the bit which will be the least significant bit of the input data field after rotation.

specifies the length (number of bits) of the mask field.

Note that L = 0 selects an 8-bit field.

D specifies the destination bank of the IV bus for the address data:

D = 07 specifies left bank address (IVL);

D = 17 specifies right bank address (IVR).

The order of operation is:

read the IV bus data into the input latches;

right rotate the input data field until bit So becomes the LSB;

mask the least significant L bits;

XOR the masked field with the contents of the AUX register;

move the resulting 8-bit field to the IV bus as an address at the bank specified by D.

### Permitted operand values

So: 0/1/2/3/4/5/6/7

S<sub>1</sub>: 2/3

L: 1/2/3/4/5/6/7/0

D: 07/17

Note that L = 0 selects an 8-bit field.

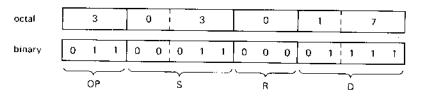

XOR, IV bus, IV bus address

### Example

Enable the IV byte at the right bank whose address is the result of the XOR operation on the contents of the AUX register and the least significant 4 bits of the IV byte at the left bank.

### Instruction word

Assembler notation

XOR LIV7, 4, IVR

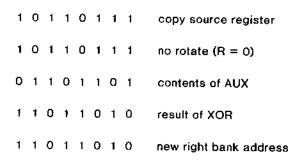

### Instruction operation

00001000

1 0 1 1 0 1 1 0 IV bus input

1 0 1 1 0 1 1 0 no rotate (S<sub>0</sub> = 7)

0 0 0 0 0 1 1 0 mask 4 bits (L = 4)

0 0 0 0 1 1 1 0 contents of AUX

0 0 0 0 1 0 0 0 result of XOR

#### Result

The previously enabled byte at the right bank is disabled and the byte at address 10 (octal) at the right bank is enabled.

new IV bus right bank address

XEC, Register

#### **Format**

| 0  | 1 2 | 3        | 4      | 5        | 6   | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|----|-----|----------|--------|----------|-----|---|---|---|----|----|----|----|----|----|

| [  |     | T        |        |          | 1   | , |   |   | 1  |    | _  | T  | r  | '  |

| _n | = 4 |          |        | S        |     |   |   |   |    |    | 1  |    |    | ļ  |

| 0  | - 4 | <b>—</b> |        | Γ        | S - |   | 1 |   |    |    |    |    |    | 1  |

| L  |     |          | ']<br> | <u> </u> | 20  |   | L |   |    |    |    |    |    | ш  |

#### Operation

Execute the instruction at the current page address offset by I + (S). Return to the instruction following the XEC instruction unless an unconditional jump or a satisfied conditional jump is encountered.

### Description

Execute the instruction at the address formed by replacing the 8 least significant bits of the contents of the address register with the 8-bit sum of I and the contents of the register specified by S.

S specifies the source register.

I is the 8-bit integer value for address modification.

The order of operation is:

copy the data from the source register;

form the 8-bit sum of the I field value and the source register contents;

modify the address register with the 8-bit sum.

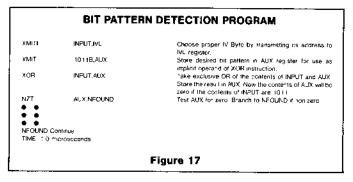

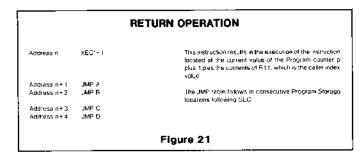

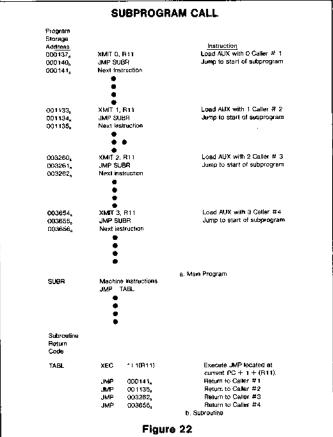

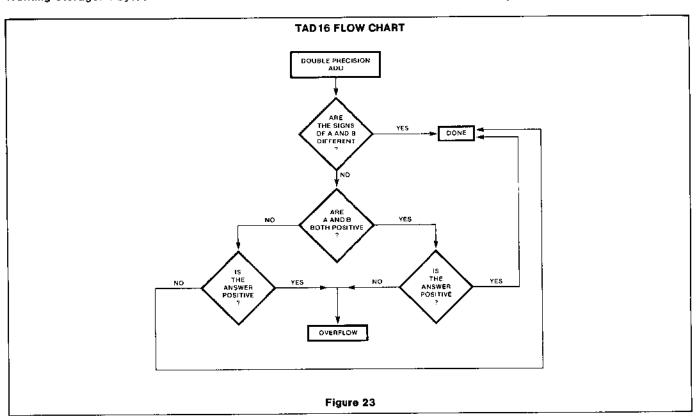

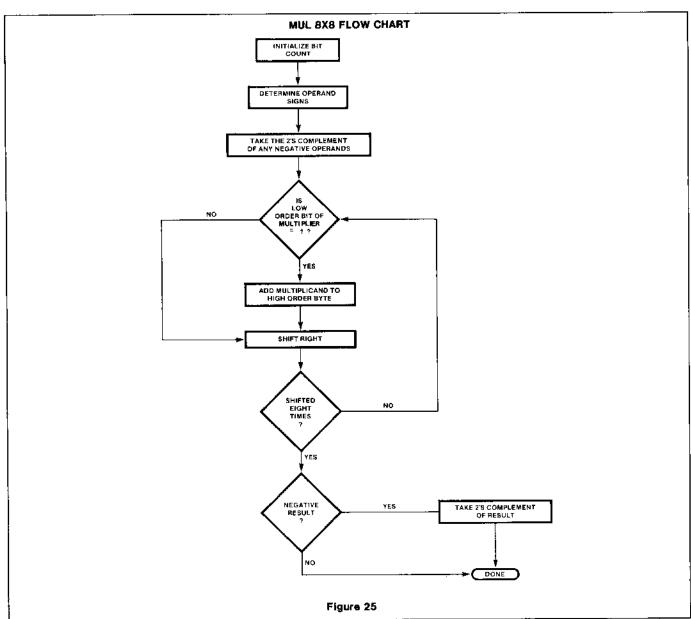

Only the least significant 8-bits of the address register can be changed by this instruction, so that a range of 256 addresses is available. This range of 256 addresses is termed the address page, determined by the five most significant bits of the address register. When the sum of (S)  $\pm 1$  is greater than 255 (377 octal) only the least significant 8 bits are used; the overflow register is not changed.