8K X 8 EEPROM

#### **FEATURES**

- Access Times of 150, 200, 250 and 350ns

- Single 5V±10% Power Supply

- Simple Byte and Page Write

- Low Power CMOS:

- 40 mA Active Current

- 100 µA Standby Current

- **■** Fast Write Cycle Times

- Software Data Protection

- CMOS & TTL Compatible Inputs and Outputs

- Endurance:

- 100,000 Write Cycles

- Data Retention: 10 Years

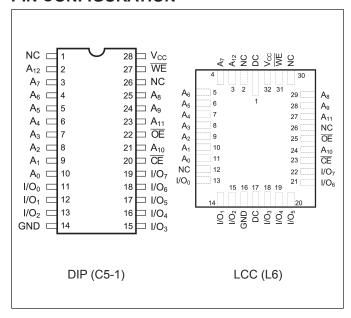

- Available in the following packages:

- 28-Pin 600 mil Ceramic DIP

- 32-Pin Ceramic LCC (450x550 mils)

#### DESCRIPTION

The PYA28C64B is a 5 Volt 8Kx8 EEPROM. The device supports 64-byte page write operation. The PYA28C64B features DATA and Toggle Bit Polling to indicate early completion of a Write Cycle. The device also includes

user-optional software data protection. Data Retention is 10 Years. The device is available in a 28-Pin 600 mil wide Ceramic DIP and 32-Pin LCC.

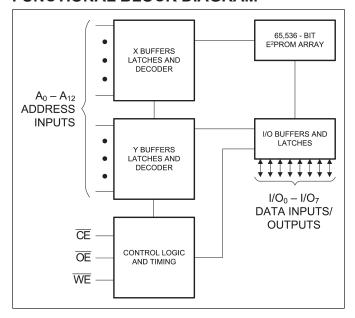

#### **FUNCTIONAL BLOCK DIAGRAM**

#### PIN CONFIGURATION

#### **OPERATION**

#### **READ**

Read operations are initiated by both  $\overline{OE}$  and  $\overline{CE}$  LOW. The read operation is terminated by either  $\overline{CE}$  or  $\overline{OE}$  returning HIGH. This two line control architecture eliminates bus contention in a system environment. The data bus will be in a high impedance state when either  $\overline{OE}$  or  $\overline{CE}$  is HIGH.

#### **BYTE WRITE**

Write operations are initiated when both  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  are LOW and  $\overline{\text{OE}}$  is HIGH. The PYA28C64B supports both a  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  controlled write cycle. That is, the address is latched by the falling edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs last. Similarly, the data is latched internally by the rising edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs first. A byte write operation, once initiated, will automatically continue to completion.

#### **PAGE WRITE**

The page write feature of the PYA28C64B allows 1 to 64 bytes of data to be consecutively written to the PYA28C256 during a single internal programming cycle. The host can fetch data from another device within the system during a page write operation (change the source address), but the page address (A $_{\rm 6}$  through A $_{\rm 12}$ ) for each subsequent valid write cycle to the part during this operation must be the same as the initial page address. The bytes within the page to be written are specified with the A $_{\rm 0}$  through A $_{\rm 5}$  inputs.

The page write mode can be initiated during any write operation. Following the initial byte write cycle, the host can write an additional 1 to 63 bytes in the same manner as the first byte was written. Each successive byte load cycle, started by the  $\overline{\text{WE}}$  HIGH to LOW transition, must begin within 150µs of the falling edge of the preceding  $\overline{\text{WE}}$ . If a subsequent  $\overline{\text{WE}}$  HIGH to LOW transition is not detected within 150µs, the internal automatic programming cycle will commence. There is no page write window limitation. Effectively, the page write window is

infinitely wide, so long as the host continues to access the device within the byte load cycle time of 150µs.

#### **DATA POLLING**

The PYA28C64B features DATA Polling as a method to indicate to the host system that the byte write or page write cycle has completed. DATA Polling allows a simple bit test operation to determine the status of the PYA28C64B, eliminating additional interrupts or external hardware. During the internal programming cycle, any attempt to read the last byte written will produce the complement of that data on I/O<sub>7</sub> (i.e., write data=0xxx xxxx, read data=1xxx xxxx). Once the programming cycle is complete, I/O<sub>7</sub> will reflect true data. Note: If the PYA28C64B is in the protected state and an illegal write operation is attempted, DATA Polling will not operate.

#### **TOGGLE BIT**

The PYA28C64B also provides another method for determining when the internal write cycle is complete. During the internal programming cycle,  $I/O_6$  will toggle from HIGH to LOW and LOW to HIGH on subsequent attempts to read the device. When the internal cycle is complete the toggling will cease and the device will be accessible for additional read or write operations.

#### MAXIMUM RATINGS(1)

| Sym               | Parameter                                                | Value         | Unit |

|-------------------|----------------------------------------------------------|---------------|------|

| V <sub>cc</sub>   | Power Supply Pin with Respect to GND                     | -0.3 to +6.25 | ٧    |

| V <sub>TERM</sub> | Terminal Voltage with<br>Respect to GND (up to<br>6.25V) | -0.5 to +6.25 | V    |

| T <sub>A</sub>    | Operating Temperature                                    | -55 to +125   | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias                                   | -55 to +125   | °C   |

| T <sub>STG</sub>  | Storage Temperature                                      | -65 to +150   | °C   |

| P <sub>T</sub>    | Power Dissipation                                        | 1.0           | W    |

| I <sub>OUT</sub>  | DC Output Current                                        | 50            | mA   |

#### RECOMMENDED OPERATING CONDITIONS

| Grade <sup>(2)</sup> | Ambient Temp    | GND | V <sub>cc</sub> |

|----------------------|-----------------|-----|-----------------|

| Military             | -55°C to +125°C | 0V  | 5.0V ± 10%      |

#### CAPACITANCES<sup>(4)</sup>

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, f = 1.0MHz)$

| Sym              | Parameter          | Conditions            | Тур | Unit |

|------------------|--------------------|-----------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 0V  | 10  | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 10  | pF   |

#### DC ELECTRICAL CHARACTERISTICS

(Over Recommended Operating Temperature & Supply Voltage)(2)

| 0                | Dayanastay                                       | To at O and this was                                                                                                   | PYA2                  |                       |      |

|------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| Sym              | Parameter                                        | Test Conditions                                                                                                        | Min                   | Max                   | Unit |

| V <sub>IH</sub>  | Input High Voltage                               |                                                                                                                        | 2.0                   | V <sub>cc</sub> + 0.3 | V    |

| V <sub>IL</sub>  | Input Low Voltage                                |                                                                                                                        | -0.5(3)               | 0.8                   | V    |

| V <sub>HC</sub>  | CMOS Input High Voltage                          |                                                                                                                        | V <sub>cc</sub> - 0.2 | V <sub>cc</sub> + 0.5 | V    |

| V <sub>LC</sub>  | CMOS Input Low Voltage                           |                                                                                                                        | -0.5(3)               | 0.2                   | V    |

| V <sub>oL</sub>  | Output Low Voltage (TTL Load)                    | I <sub>OL</sub> = +2.1 mA, V <sub>CC</sub> = Min                                                                       |                       | 0.4                   | V    |

| V <sub>OH</sub>  | Output High Voltage (TTL Load)                   | $I_{OH}$ = -0.4 mA, $V_{CC}$ = Min                                                                                     | 2.4                   |                       | V    |

| I <sub>LI</sub>  | Input Leakage Current                            | $V_{CC} = Max$ $V_{IN} = GND \text{ to } V_{CC}$                                                                       | -10                   | +10                   | μA   |

| I <sub>LO</sub>  | Output Leakage Current                           | $V_{CC} = Max, \overline{CE} = V_{IH},$ $V_{OUT} = GND \text{ to } V_{CC}$                                             | -10                   | +10                   | μA   |

| I <sub>SB</sub>  | Standby Power Supply Current (TTL Input Levels)  | $\overline{CE} \ge V_{IH}, \ \overline{OE} = V_{IL},$ $V_{CC} = Max,$ $f = Max, Outputs Open$                          | _                     | 2                     | mA   |

| I <sub>SB1</sub> | Standby Power Supply Current (CMOS Input Levels) | $\overline{CE} \ge V_{HC}$ ,<br>$V_{CC} = Max$ ,<br>f = 0, Outputs Open,<br>$V_{IN} \le V_{LC}$ or $V_{IN} \ge V_{HC}$ | _                     | 100                   | μA   |

| I <sub>cc</sub>  | Supply Current                                   | $\overline{CE} = \overline{OE} = V_{IL},$ $\overline{WE} = V_{IH},$ All I/O's = Open, Inputs = $V_{CC} = 5.5V$         | _                     | 40                    | mA   |

#### Notes:

- Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.

- 2. Extended temperature operation guaranteed with 400 linear feet per minute of air flow.

- Transient inputs with V<sub>IL</sub> and I<sub>IL</sub> not more negative than -3.0V and -100mA, respectively, are permissible for pulse widths up to 20ns.

- 4. This parameter is sampled and not 100% tested.

#### **POWER-UP TIMING**

| Symbol                                       | Symbol Parameter           |     | Unit |

|----------------------------------------------|----------------------------|-----|------|

| t <sub>PUR</sub>                             | Power-up to Read operation | 100 | μs   |

| t <sub>PUW</sub> Power-up to Write operation |                            | 5   | ms   |

#### AC ELECTRICAL CHARACTERISTICS—READ CYCLE

$(V_{CC} = 5V \pm 10\%, All Temperature Ranges)^{(2)}$

| C                 | Bowerston                           | -150 -2 |     | -200 |     | 50  | -3  | -350 |     |      |

|-------------------|-------------------------------------|---------|-----|------|-----|-----|-----|------|-----|------|

| Sym               | Parameter                           | Min     | Max | Min  | Max | Min | Max | Min  | Max | Unit |

| t <sub>AVAV</sub> | Read Cycle Time                     | 150     |     | 200  |     | 250 |     | 350  |     | ns   |

| t <sub>AVQV</sub> | Address Access Time                 |         | 150 |      | 200 |     | 250 |      | 350 | ns   |

| t <sub>ELQV</sub> | Chip Enable Access Time             |         | 150 |      | 200 |     | 250 |      | 350 | ns   |

| t <sub>olqv</sub> | Output Enable Access Time           |         | 70  |      | 80  |     | 100 |      | 100 | ns   |

| t <sub>ELQX</sub> | Chip Enable to Output in Low Z      | 0       |     | 0    |     | 0   |     | 0    |     | ns   |

| t <sub>EHQZ</sub> | Chip Disable to to Output in High Z |         | 50  |      | 55  |     | 60  |      | 70  | ns   |

| t <sub>olqx</sub> | Output Enable to Output in Low Z    | 0       |     | 0    |     | 0   |     | 0    |     | ns   |

| t <sub>ohqz</sub> | Output Disable to Output in High Z  |         | 50  |      | 55  |     | 60  |      | 70  | ns   |

| t <sub>AVQX</sub> | Output Hold from Address Change     | 0       |     | 0    |     | 0   |     | 0    |     | ns   |

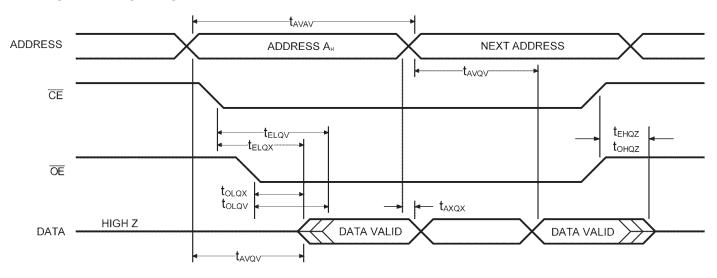

#### TIMING WAVEFORM OF READ CYCLE

# AC CHARACTERISTICS—WRITE CYCLE ( $V_{CC}$ = 5V $\pm$ 10%, All Temperature Ranges)<sup>(2)</sup>

| Cumbal                                                          | Darameter            | 150 / 200 | / 250 / 350 | I I a it |

|-----------------------------------------------------------------|----------------------|-----------|-------------|----------|

| Symbol                                                          | Parameter            | Min       | Max         | Unit     |

| t <sub>WHWL1</sub><br>t <sub>EHEL1</sub>                        | Write Cycle Time     |           | 10          | ms       |

| t <sub>AVEL</sub><br>t <sub>AVWL</sub>                          | Address Setup Time   | 0         |             | ns       |

| $\mathbf{t}_{_{\mathrm{ELAX}}}$ $\mathbf{t}_{_{\mathrm{WLAX}}}$ | Address Hold Time    | 50        |             | ns       |

| t <sub>wlel</sub><br>t <sub>elwl</sub>                          | Write Setup Time     | 0         |             | ns       |

| t <sub>wheh</sub>                                               | Write Hold Time      | 0         |             | ns       |

| t <sub>ohel</sub><br>t <sub>ohwl</sub>                          | OE Setup Time        | 10        |             | ns       |

| t <sub>whoL</sub>                                               | OE Hold Time         | 10        |             | ns       |

| t <sub>eleh</sub><br>t <sub>wlwh</sub>                          | WE Pulse Width       | 100       |             | ns       |

| t <sub>DVEH</sub><br>t <sub>DVWH</sub>                          | Data Setup Time      | 50        |             | ns       |

| t <sub>EHDX</sub><br>t <sub>WHDX</sub>                          | Data Hold Time       | 0         |             | ns       |

| t <sub>EHEL2</sub><br>t <sub>WHWL2</sub>                        | Byte Load Cycle Time | 0.2       | 150         | μs       |

| t <sub>ELWL</sub>                                               | CE Setup Time        | 1         |             | μs       |

| t <sub>ovhwL</sub>                                              | Output Setup Time    | 1         |             | μs       |

| t <sub>EHWH</sub>                                               | CE Hold Time         | 1         |             | μs       |

| t <sub>whoh</sub>                                               | OE Hold Time         | 1         |             | μs       |

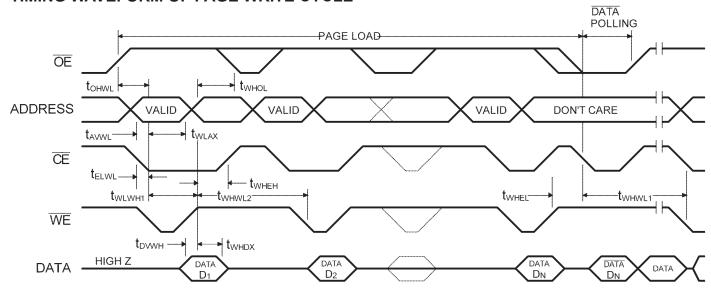

#### TIMING WAVEFORM OF PAGE WRITE CYCLE

#### **NOTES:**

- For each successive write within the page write operation, A<sub>6</sub>-A<sub>12</sub> should be the same. Otherwise, writes to an unknown address could occur.

- Between successive byte writes within a page write operation,  $\overline{OE}$  can be strobed LOW. For example, this can be done with  $\overline{CE}$  and  $\overline{WE}$  HIGH to fetch data from another memory device within the system for the next write. Alternatively, this can be done with  $\overline{WE}$  HIGH and  $\overline{CE}$  LOW, effectively performing a polling operation.

- The timings shown above are unique to page write operations. Individual byte load operations within the page write must conform to either the  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  controlled write cycle timing.

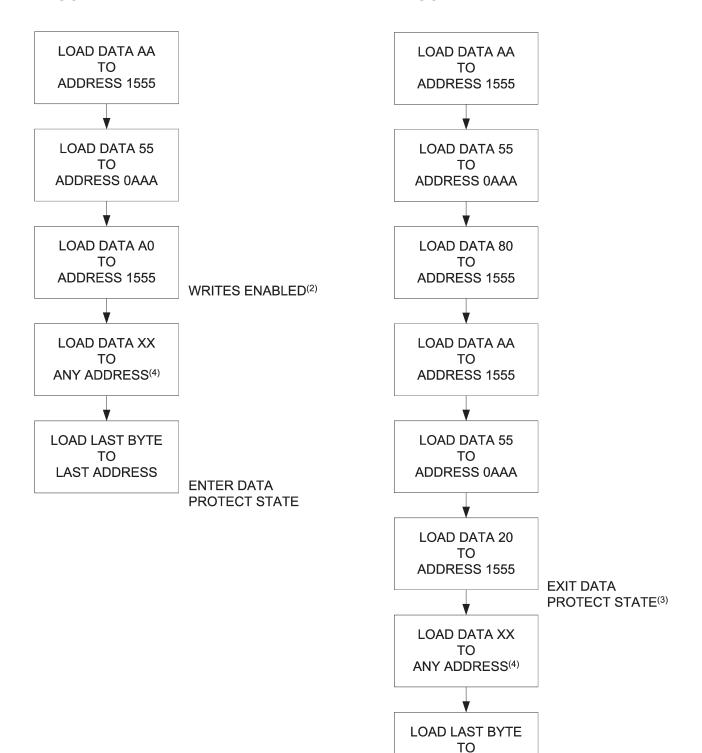

## SOFTWARE DATA PROTECTION ENABLE ALGORITHM<sup>(1)</sup>

## SOFTWARE DATA PROTECTION DISABLE ALGORITHM(1)

(SDP Set) (SDP Reset)

LAST ADDRESS

#### Notes:

- 1. Data Format: I/O<sub>7</sub> I/O<sub>0</sub> (Hex) Address Format: A<sub>12</sub> - A<sub>0</sub> (Hex)

- 2. Write Protect state will be activated at end of write even if no other data is loaded.

- 3. Write Protect state will be deactivated at end of write period even if no other data is loaded.

- 4. 1 to 64 bytes of data are loaded.

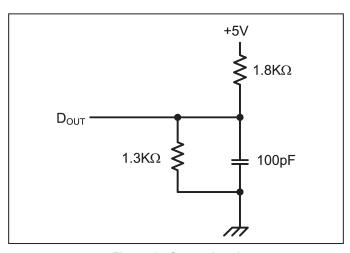

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise and Fall Times     | 10ns         |

| Input Timing Reference Level  | 1.5V         |

| Output Timing Reference Level | 1.5V         |

| Output Load                   | See Figure 1 |

#### **TRUTH TABLE**

| Mode           | CE | ŌĒ | WE | I/O              |

|----------------|----|----|----|------------------|

| Read           | L  | L  | Н  | D <sub>out</sub> |

| Write          | L  | Н  | L  | D <sub>IN</sub>  |

| Write Inhibit  | Х  | L  | Х  | _                |

| Write Inhibit  | Х  | Х  | Н  | _                |

| Standby        | Н  | Х  | Х  | High Z           |

| Output Disable | Х  | Н  | Х  | High Z           |

Figure 1. Output Load

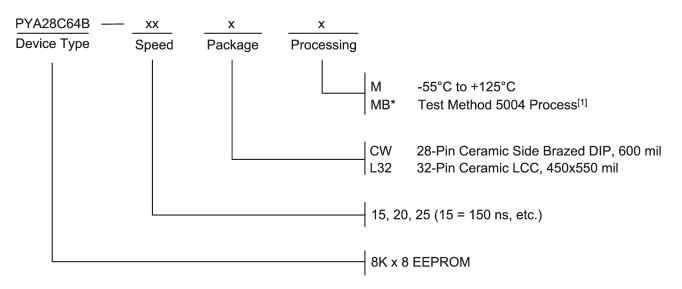

#### ORDERING INFORMATION

[1] Parts are not MIL-STD-883 compliant. Parts are processed per Test Method 5004

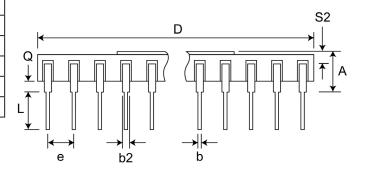

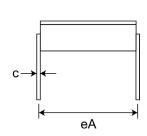

| ~      |        |         |  |  |

|--------|--------|---------|--|--|

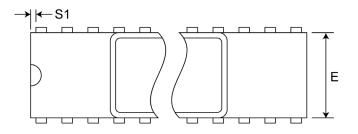

| Pkg #  | C5-1   |         |  |  |

| # Pins | 28 (60 | 00 mil) |  |  |

| Symbol | Min    | Max     |  |  |

| Α      | -      | 0.232   |  |  |

| b      | 0.014  | 0.026   |  |  |

| b2     | 0.045  | 0.065   |  |  |

| С      | 0.008  | 0.018   |  |  |

| D      | -      | 1.490   |  |  |

| Е      | 0.500  | 0.610   |  |  |

| eA     | 0.600  | BSC     |  |  |

| е      | 0.100  | BSC     |  |  |

| L      | 0.125  | 0.200   |  |  |

| Q      | 0.015  | 0.060   |  |  |

| S1     | 0.005  | -       |  |  |

| S2     | 0.005  | _       |  |  |

#### SIDE BRAZED DUAL IN-LINE PACKAGE (600 mils)

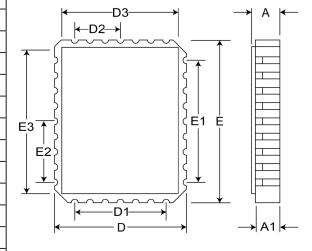

# # Pins 32 Symbol Min Max A 0.060 0.075

L6

| Α  | 0.060     | 0.075 |  |

|----|-----------|-------|--|

| A1 | 0.050     | 0.065 |  |

| B1 | 0.022     | 0.028 |  |

| D  | 0.442     | 0.458 |  |

| D1 | 0.300     | BSC   |  |

| D2 | 0.150     | BSC   |  |

| D3 | -         | 0.458 |  |

| Е  | 0.540     | 0.560 |  |

| E1 | 0.400 BSC |       |  |

| E2 | 0.200     | BSC   |  |

| E3 | -         | 0.558 |  |

| е  | 0.050 BSC |       |  |

| h  | 0.040 REF |       |  |

|    | 0.020 RFF |       |  |

Pkg#

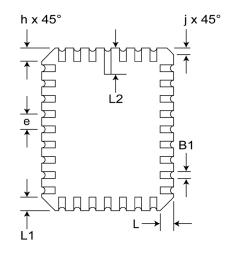

## RECTANGULAR LEADLESS CHIP CARRIER

7

9

0.045

0.045

0.075

L1

L2

ND

NE

0.055

0.055

0.095

#### **REVISIONS**

| DOCUMENT NUMBER | EEPROM111                 |

|-----------------|---------------------------|

| DOCUMENT TITLE  | PYA28C64B - 8K x 8 EEPROM |

| REV | ISSUE DATE | ORIGINATOR | DESCRIPTION OF CHANGE                                           |

|-----|------------|------------|-----------------------------------------------------------------|

| OR  | Jun 2013   | JDB        | New Data Sheet                                                  |

| 01  | Oct 2014   | JDB        | Replaced MIL-STD-883 Class B process flow with Test Method 5004 |

| 02  | Apr 2015   | JDB        | Corrected Block Diagram                                         |