## MOS EPROMS

# MM4203/MM5203 2048-Bit (256 $\times$ 8 or 512 $\times$ 4) **UV Erasable PROM**

### General Description

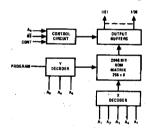

The MM4203/MM5203 is a 2048-bit static readonly memory which is electrically programmable and uses silicon gate technology to achieve bipolar compatibility. The device is a non-volatile memory organized as a 256-8-bit words or 512-4-bit words. Programming of the memory contents is accomplished by storing a charge in a cell location by programming that location with a 50 volt pulse. Separate output supply lead is provided to reduce internal power dissipation in the output stage (VLL).

#### **Features**

- Field programmable

- Bipolar compatibility

+5V. -12V operation

High speed operation

1µs max access time

- Pin compatible with MM5213, MM5231 mask programmable ROMs

- Static operation no clocks required

- Common data busing (TRI-STATE® output)

- "Q" quartz lid version erasable with short wave ultra-violet light (i.e. 253.7 n.m.)

- Chip select output control

- 256 x 8 or 512 x 4 organization

#### **Applications**

- Code conversion

- Random logic synthesis

- Table look-up

- Character generator

- Micro-programming

## **Block and Connection Diagrams**

Order Number MM4203Q or MM5203Q See NS Package J24CQ

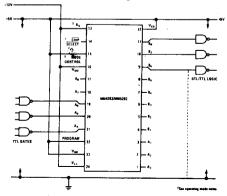

# **Typical Applications**

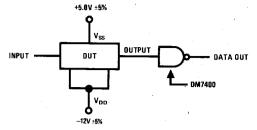

256 x 8 PROM Showing TTL Interface

#### Operating Modes

256 x 8 ROM connection (shown) Mode Control - HIGH (VSS) Ag - LOW

512 x 4 ROM connections

Mode Control — LOW (GND or VDD)

Ag — Logic HIGH enables the odd (B1, B3, B3) outputs

— Logic LOW enables the even (B2, B4, B8) outputs

The outputs are enabled when a logic LOW is applied to the Chip Select line.

Programming is accomplished in 256 x 8 mode only

### **Absolute Maximum Ratings**

**Operating Conditions** Operating Temperature Range MM4203

All Input or Output Voltages with Respect to VBB Except During Programming Power Dissipation

Storage Temperature Range

Lead Temperature (Soldering, 10 sec)

-65°C to 125°C 300°C -55°C to 85°C 0°C to 70°C

Electrical Characteristics TA within operating temperature range,  $V_{SS}$  = +5V ±5%,  $V_{DD}$  =  $V_{LL}$  = -12V, ±5%,  $V_{BB}$  = PROGRAM =  $V_{SS}$  unless otherwise noted.

| YMBOL PARAMETER |                             | CONDITIONS                                                                                                                            | MIN                   | TYP        | MAX                   | UNITS    |

|-----------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|-----------------------|----------|

| T.              | Input Current               | V <sub>IN</sub> = 0V                                                                                                                  |                       |            | 1                     | μΑ       |

| Lo              | Output Leakage              | $V_{OUT} = 0V \overline{CS} = V_{SS} - 2.0$                                                                                           |                       |            | 1                     | μΑ       |

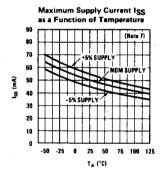

| Iss             | Power Supply Current        | $T_A = 25^{\circ} C \overline{CS} = V_{SS} - 2.0$                                                                                     |                       | 35 .       | 55                    | mA       |

| VIL             | Input LOW Voltage           |                                                                                                                                       | V <sub>SS</sub> - 10  |            | V <sub>SS</sub> - 4.0 | ٧        |

| V <sub>IH</sub> | Input HIGH Voltage          |                                                                                                                                       | V <sub>SS</sub> - 2.0 |            | V <sub>SS</sub> + .3  | V        |

| V <sub>OL</sub> | Output LOW Voltage          | 1.6 mA sink -12.6V < V <sub>LL</sub> < -3V                                                                                            |                       |            | .40                   | V        |

| I <sub>CF</sub> | Output Clamp Current        | $V_{LL} = -3.0V \ V_{OUT} = -1.0V \ (Note 8) \ T_A = 0^{\circ}C$<br>$V_{LL} = -12.6V \ V_{OUT} = -1.0V \ (Note 8) \ T_A = 0^{\circ}C$ |                       | 3.5<br>8.0 | 6.0<br>15.0           | mA<br>mA |

| V <sub>OH</sub> | Output HIGH Voltage         | 0.8 mA source                                                                                                                         | 2.4                   |            |                       | ٧        |

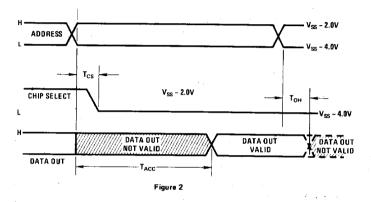

| Тон             | Data Hold Time              | (Min Access Time) Figures 1 & 2                                                                                                       |                       |            | 100                   | ns       |

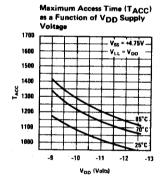

| TACC"           | Access Time                 | T <sub>A</sub> = 25°C Figures 1 & 2 (Note 6)                                                                                          |                       | .700       | 1                     | μs       |

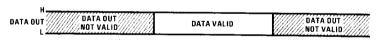

| Tco             | Chip Select Time            | Figures 1 & 3                                                                                                                         |                       | •          | 500                   | ns       |

| Top             | Chip Deselect Time          | Figures 1 & 3                                                                                                                         |                       |            | 500                   | ns       |

| t <sub>cs</sub> | Allowable Chip Select Delay | Figures 1 & 2 Allowable delay in selecting chip after change of address without affecting access time.                                |                       |            | 100                   | ns       |

| Cı№             | Input Capacitance           | V <sub>IN</sub> = V <sub>SS</sub>                                                                                                     |                       | 8.         | 15                    | pF       |

| Cout            | Output Capacitance          | $\begin{cases} V_{1N} = V_{SS} \\ \frac{V_{OUT}}{CS} = V_{SS} - 2.0 \end{cases}$ f = 1.0 MHz (Note 2)                                 |                       | 8          | 15                    | pF       |

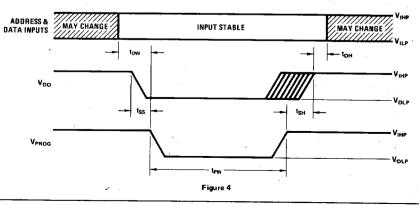

#### Programming Characteristics (see Figure 4)

$T_A = 25^{\circ}C$ ,  $V_{SS} = 0V$ ,  $V_{BB} = +12V \pm 10\%$ ,  $\overline{CS} = 0V$  unless otherwise noted

| YMBOL           | PARAMETER                                                            | CONDITIONS                                    | MIN        | TYP | MAX      | UNITS  |

|-----------------|----------------------------------------------------------------------|-----------------------------------------------|------------|-----|----------|--------|

| I <sub>LD</sub> | Address and Data Input Load Current                                  | V <sub>IN</sub> = -50V                        |            | 0   | 10       | mA     |

| I <sub>LP</sub> | Program Load Current                                                 | V <sub>IN</sub> ≃ -50V                        |            | 0   | 10       | mA     |

| ILB             | V <sub>BB</sub> Supply Load Current                                  |                                               |            | 0   | 10       | mA     |

| LDD             | Peak IDD Supply Load Current (Note 3)                                | V <sub>DD</sub> = V <sub>program</sub> = -50V |            | 650 |          | mA     |

| VIHP            | Input High Voltage                                                   |                                               | -2         |     | +.3      | V      |

| VILP            | Address and Data Input Low Voltage                                   |                                               | -50        |     | -40      | V      |

|                 | Pulsed Input Low Voltage: $V_{DD}$ , and Program, $V_{DLP}$ $V_{LL}$ | (Note 5)                                      | -50<br>-50 |     | -48<br>0 | v<br>v |

| 1               | V <sub>DD</sub> Pulse Duty Cycle                                     |                                               |            |     | 2        | %      |

| t <sub>PW</sub> | Program Pulse Width (Note 4)                                         | V <sub>DD</sub> = V <sub>program</sub> = -50V |            |     | 20       | ms     |

| t <sub>DW</sub> | Data and Address Set Up Time                                         |                                               |            | 1   |          | μs     |

| t <sub>DH</sub> | Data and Address Hold Time,                                          |                                               |            | 0   |          | μs     |

| t <sub>SS</sub> | Pulsed V <sub>DD</sub> Supply Overlap,                               | ٠.                                            |            | 1 . | 100      | μs     |

| t <sub>SH</sub> | Pulsed V <sub>DD</sub> Supply Overlap,                               |                                               |            | −.1 | 3        | ms     |

|                 | V <sub>DD</sub> , Program, Address, and Input Rise and Fall Times    |                                               |            |     | • 1      | μs     |

Note 1: During programming, data is always applied in the  $256 \times 8$  mode, regardless of the logic state of Ag and MODE CONTROL.

Note 2: Capacitances are not tested on a production basis but are periodically sampled.

Note 3: 1DDP flows only during program period tpwp. Average power supply current LDD is typically 15 mA at 2% duty cycle. Note 3: Maximum duty cycle of tppg should not be greater than 2% of cycle time so that power dissipation is minimized. The program cycle should be repeated until the data reads true, then over-program three times that number of cycles (symbolized as X+3X programming.

Note 5: VLL is not needed during programming but may be tied to VDD for convenience.

Note 6:  $T_{ACC} = 1000$  ns + 25(N-1) where N is the number of chips wired-OR together. Note 7: Measured under continuous operation.

Note 8: ICF flows out the VLL pin, it does not flow out the VDD pin.

## **Access Time Diagrams**

Figure 1

Figure 3

## **Program Waveforms**

#### Operation of the MM4203/MM5203 in Program Mode

Initially, all 2048 bits of the MM4203/MM5203 are in the HIGH state. Information is introduced by selectively programming LOWS in the proper bit locations. (Note 1)

Word address selection is done by the same decoding circuitry used in the Read mode. The eight output terminals are used as data inputs to determine the information pattern in the eight bits of each word. A LOW data input level (-50V) will leave a HIGH and a HIGH data input level will allow programming of a LOW. All eight bits of one word are programmed simultaneously by setting the desired bit information patterns on the data input terminals. The duty cycle of the V<sub>DD</sub> pulse (amplitude and width as specified on page 4) should be limited to 2%. The address should be applied for at least 1 µs before application of the Program pulse. In programming mode, data inputs

1-8 are pins 4-11 respectively regardless of the logic state of  $A_9$  and mode control. Chip select should be disabled (HIGH).

Positive logic is used during the read mode for addresses and data out. Address 0 corresponds to all address inputs at  $V_{IL}$  and address  $255_{10}$  corresponds to all address inputs at  $V_{IH}$ . A "1" or a P at a data output corresponds to  $V_{OH}$ . A "0" or an N at a data output corresponds to  $V_{OL}$ . Positive logic is also used during the programming mode for addresses. Address 0 corresponds to all address inputs at  $V_{ILP}$  and address  $255_{10}$  corresponds to all address inputs at  $V_{IHP}$ .

Negative logic is used during the programming mode for data in. A "1" or a P at a data input corresponds to  $V_{1LP}$ . A "0" or an N at a data input corresponds to  $V_{1HP}$ .

|         | DATA AND ADDRESS LINES |                       |                  |                 |                 |                 |                      |             |  |

|---------|------------------------|-----------------------|------------------|-----------------|-----------------|-----------------|----------------------|-------------|--|

| MODE    | HIGH                   | LOW                   | .V <sub>SS</sub> | V <sub>BB</sub> | V <sub>DB</sub> | PROGRAM         | cs                   | VLL         |  |

| Read    | V <sub>SS</sub> - 2.0  | V <sub>SS</sub> - 4.0 | +5               | Vss             | -12             | V <sub>SS</sub> | V <sub>SS</sub> - 4V | ~3V to -12V |  |

| Program | V <sub>SS</sub> -2.0   | V <sub>SS</sub> - 40  | GND              | +12             | -48<br>(Pulse)  | -48<br>(Pulse)  | GND                  | GND to -50V |  |

#### **Erasing Procedure**

The MM4203Q/MM5203Q may be erased by exposure to short-wave ultraviolet light—253.7 nm. There exists no absolute rule for erasing time or distance from source. The erasing equipment output capability should be calibrated. Establish a worst-case time required with the equipment. Then over-erase by a factor of 2, i.e., if the device appears erased after 8 minutes, continue exposure for an additional 16 minutes for a total of 24

minutes. Examples of UV sources include the Model UVS-54 and Model S-2 manufactured by Ultra-Violet Products, Inc. (5114 Walnut Grove Avenue, San Gabriel, California). The lamps should be used without short-wave filters. The MM4203/MM5203 should be placed about one nich away from the lamp for about 20–30 minutes.

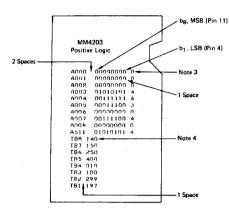

### **Preferred Tape Format**

The custom patterns may be sent in on a Telex or submitted as a paper tape in a 7 bit ASCII code

from model 33 teletype or TWX. The paper tape should be as the following example:

\*Data Field: Must have only P's or N's typed between B and F. No nulls or rubouts. Must have exactly eight P and N characters between B and F. Any characters sected B and F may be typed between the F stop character and the B start character. If an error is made in preparing a tape the entire word including the B and F start and stop characters must be rubbed out. Data for exactly 256 words must be entered, beginning with word 0.

# Alternate Format [Punched Tape (Note 1) or Cards]

Note 1: The code is a 7-bit ASCII code on 8 punch tape. The tape should begin and end with 25 or more "RUBOUT" punches. Note 2: The ROM input address is expressed in decimal form and is preceded by the letter A.

Note 3: The total number of "1" bits in the output word.

Note 4: The total number of "1" bits in each output column or bit

## **Typical Performance Characteristics**