### Description

The  $\mu$ PD28C04 is a 4,096-bit electrically erasable and programmable read-only memory (EEPROM) organized as 512 x 8 bits and fabricated with an advanced CMOS process for high performance and low power consumption.

The device operates from a single + 5-volt power supply and provides a  $\overline{\text{DATA}}$  polling function to indicate the precise end of write cycles. Additional features include chip erase, auto erase and programming cycles. The  $\mu\text{PD28C04}$  is available in standard 24-pin plastic DIP or miniflat packaging.

#### **Features**

- □ Fast access times of 200 and 250 ns maximum

- □ Single + 5-volt power supply

- □ Chip erase feature

- □ Auto erase and programming at 10 ms maximum

- □ DATA polling verification

- Low power dissipation

- 50 mA max (active)

- 100 uA max (standby)

- □ Endurance: 100,000 erase/write cycles per byte

- TTL-compatible inputs and outputs

- □ Three-state outputs

- Advanced CMOS technology

- 24-pin plastic DIP or miniflat packaging

### Ordering Information

| Part Number  | Access Time (max) | Package                 |  |  |

|--------------|-------------------|-------------------------|--|--|

| μPD28C04C-20 | 200 ns            | 24-pin plastic DIP      |  |  |

| C-25         | 250 ns            | •                       |  |  |

| μPD28C04G-20 | 200 ns            | 24-pin plastic miniflat |  |  |

| G-25         | 250 ns            | •                       |  |  |

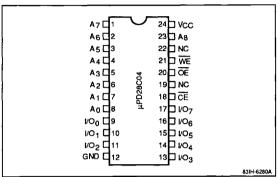

### Pin Configuration

#### 24-Pin Plastic DIP or Miniflat

278

#### Pin Identification

| Symbol                          | Function             |  |  |  |  |  |

|---------------------------------|----------------------|--|--|--|--|--|

| A <sub>0</sub> - A <sub>8</sub> | Address inputs       |  |  |  |  |  |

| 1/00 - 1/07                     | Data inputs/outputs  |  |  |  |  |  |

| CE                              | Chip enable          |  |  |  |  |  |

| ŌĒ                              | Output enable        |  |  |  |  |  |

| WE                              | Write enable         |  |  |  |  |  |

| GND                             | Ground               |  |  |  |  |  |

| v <sub>cc</sub>                 | +5-volt power supply |  |  |  |  |  |

| NC                              | No connection        |  |  |  |  |  |

## **Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>         | - 0.6 to + 7.0 V |

|-----------------------------------------|------------------|

| Input voltage, V <sub>I1</sub>          | - 0.6 to + 7.0 V |

| Input voltage, V <sub>I3</sub> (OE)     | -0.6 to +16.5 V  |

| Output voltage, V <sub>O</sub>          | - 0.6 to + 7.0 V |

| Operating temperature, T <sub>OPT</sub> | - 10 to +85°C    |

| Storage temperature, T <sub>STG</sub>   | - 65 to + 125°C  |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

## **Recommended Operating Conditions**

| Parameter           | Symbol          | Min   | Тур | Max                   | Unit |

|---------------------|-----------------|-------|-----|-----------------------|------|

| Supply voltage      | Vcc             | 4.5   | 5.0 | 5.5                   | ٧    |

| Input voltage, high | V <sub>IH</sub> | 2.0   |     | V <sub>CC</sub> + 0.3 | ٧    |

| Input voltage, low  | V <sub>IL</sub> | - 0.3 |     | 0.8                   | ٧    |

| Ambient temperature | TA              | 0     |     | 70                    | °C   |

## Capacitance

$T_A = 25$ °C; f = 1 MHz;  $V_{IN}$  and  $V_{OUT} = 0$  V

| Parameter          | Symbol         | Min | Тур | Max | Unit |

|--------------------|----------------|-----|-----|-----|------|

| Input capacitance  | C <sub>I</sub> |     | 7   | 12  | рF   |

| Output capacitance | Со             |     | _   | 10  | рF   |

## **Truth Table**

|                           | -               |                  |                 |                  |         |

|---------------------------|-----------------|------------------|-----------------|------------------|---------|

| Function                  | CE              | ŌĒ               | WE              | 1/0              | Icc     |

| Read                      | V <sub>IL</sub> | V <sub>IL</sub>  | V <sub>IH</sub> | D <sub>OUT</sub> | Active  |

| Standby and write inhibit | V <sub>IH</sub> | Х                | Х               | High-Z           | Standby |

| Write                     | VIL             | V <sub>IH</sub>  | V <sub>IL</sub> | D <sub>IN</sub>  | Active  |

| Chip erase                | V <sub>IL</sub> | V <sub>IHH</sub> | V <sub>IL</sub> | DIN = VIH        | Active  |

| Write inhibit             | Х               | V <sub>IL</sub>  | Х               |                  | _       |

|                           | X               | х                | V <sub>IH</sub> | -                |         |

#### Notes:

- (1) X can be either  $V_{IL}$  or  $V_{IH}$ .

- (2)  $V_{IHH} = +15 \pm 0.5 V$ .

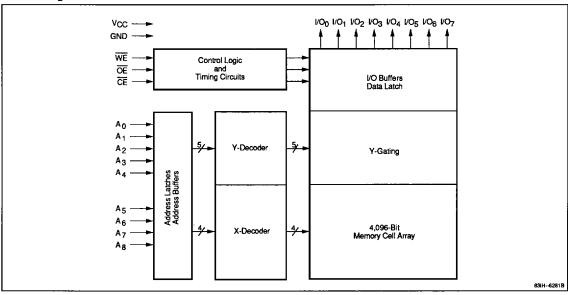

# **Block Diagram**

## **DC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%$

| Parameter                         | Symbol            | Min                   | Тур | Max  | Unit | Test Conditions                                                 |

|-----------------------------------|-------------------|-----------------------|-----|------|------|-----------------------------------------------------------------|

| Output voltage, high              | V <sub>OH1</sub>  | 2.4                   |     |      | ٧    | $I_{OH} = -400 \mu A$                                           |

|                                   | V <sub>OH2</sub>  | V <sub>CC</sub> - 0.7 |     |      | ٧    | I <sub>OH</sub> = -100 μA                                       |

| Output voltage, low               | V <sub>OL</sub>   |                       |     | 0.45 | ٧    | I <sub>OL</sub> = 2.1 mA                                        |

| Output leakage current            | lo                |                       |     | 10   | μΑ   | V <sub>OUT</sub> = 0 to V <sub>CC</sub>                         |

| Input leakage current             | l <sub>LI</sub>   |                       |     | 10   | μΑ   | V <sub>IN</sub> = 0 to V <sub>CC</sub>                          |

| V <sub>CC</sub> current (active)  | I <sub>CCA1</sub> |                       |     | 20   | mA   | CE = VIL; VIN = VIH                                             |

|                                   | ICCA2             |                       |     | 50   | mA   | f = 5 MHz; I <sub>OUT</sub> = 0 mA                              |

| V <sub>CC</sub> current (standby) | lccs1             | _                     |     | 1    | mA   | CE = VIH                                                        |

|                                   | lccs2             |                       |     | 100  | μΑ   | CE = V <sub>CC</sub> ; V <sub>IN</sub> = 0 V to V <sub>CC</sub> |

# **AC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%$

| Parameter                               |                  | μPD28 | C04-20 | μPD28 | μPD28C04-25 |      | . "                                                                                 |

|-----------------------------------------|------------------|-------|--------|-------|-------------|------|-------------------------------------------------------------------------------------|

|                                         | Symbol           | Min   | Max    | Min   | Max         | Unit | Test Conditions                                                                     |

| Read Operation                          |                  |       |        |       |             | -    |                                                                                     |

| Address to output delay                 | tacc             |       | 200    |       | 250         | ns   | CE = OE = VIL; WE = VIH                                                             |

| CE to output delay                      | tcE              |       | 200    |       | 250         | ns   | OE = VIL; WE = VIH                                                                  |

| CE high to output float                 | t <sub>DFC</sub> | 0     | 60     | 0     | 80          | ns   | OE = V <sub>IL</sub> ; WE = V <sub>IH</sub>                                         |

| OE high to output float                 | t <sub>DFO</sub> | 0     | 60     | 0     | 80          | ns   | CE = VIL; WE = VIH                                                                  |

| OĒ to output delay                      | toE              | 10    | 75     | 10    | 100         | ns   | CE = VIL; WE = VIH                                                                  |

| Output hold time from<br>address change | toha             | 0     |        | 0     |             | ns   | $\overline{CE} = \overline{OE} = V_{IL};$ $\overline{WE} = V_{IH} \text{ (Note 2)}$ |

| Output hold time from rising edge of CE | tонс             | 0     |        | 0     |             | ns   | $\overline{OE} = V_{IL}; \overline{WE} = V_{IH} \text{ (Note 2)}$                   |

| Output hold time from rising edge of OE | tоно             | 0     |        | 0     |             | ns   | CE = V <sub>IL</sub> ; WE = V <sub>IH</sub>                                         |

| WE hold time from rising edge of OE     | twho             | 10    |        | 10    |             | ns   | ŌĒ = V <sub>IH</sub>                                                                |

| WE setup time to CE                     | twsc             | 10    |        | 10    |             | ns   | CE = VIH                                                                            |

| WE setup time to OE                     | twso             | 10    |        | 10    |             | ns   | OE = V <sub>IH</sub>                                                                |

| Write Operation                         |                  |       |        |       |             |      |                                                                                     |

| Address hold time                       | t <sub>AH</sub>  | 200   |        | 200   |             | ns   |                                                                                     |

| Address setup time                      | t <sub>AS</sub>  | 10    |        | 10    | -           | ns   |                                                                                     |

| CE high after CE-controlled write cycle | <sup>t</sup> CEH | 9.9   |        | 9.9   |             | ms   |                                                                                     |

| Write hold time                         | t <sub>CH</sub>  | 0     |        | 0     |             | ns   |                                                                                     |

| Write setup time                        | tcs              | 0     |        | 0     |             | ns   |                                                                                     |

# AC Characteristics (cont)

| Parameter                               | Symbol            | μPD28C               | 04-20 | μPD280               | μPD28C04-25 |      |                 |

|-----------------------------------------|-------------------|----------------------|-------|----------------------|-------------|------|-----------------|

|                                         |                   | Min                  | Max   | Min                  | Max         | Unit | Test Conditions |

| Write Operation (cont)                  |                   |                      |       |                      |             |      |                 |

| CE pulse width                          | tcw               | 150                  |       | 150                  |             | ns   |                 |

| Data hold time                          | t <sub>DH</sub>   | 20                   |       | 20                   |             | ns   |                 |

| Data setup time                         | t <sub>DS</sub>   | 100                  |       | 100                  |             | ns   | <u> </u>        |

| Data valid time                         | t <sub>DV</sub>   |                      | 300   |                      | 300         | ns   |                 |

| OE high hold time                       | toeH              | 10                   |       | 10                   |             | ns   |                 |

| OE high setup time                      | toes              | 10                   |       | 10                   |             | ns   |                 |

| Write cycle time                        | twc               | 10                   |       | 10                   |             | ms   |                 |

| WE high after WE-controlled write cycle | t <sub>WEH</sub>  | 9.9                  |       | 9.9                  |             | ms   | -               |

| WE pulse width                          | t <sub>WP</sub>   | 150                  |       | 150                  |             | ns   |                 |

| WE high hold time                       | t <sub>WPH</sub>  | 50                   |       | 50                   |             | ns   |                 |

| Chip Erase Operation                    |                   | •                    |       |                      |             |      |                 |

| CE hold time                            | tECH              | 5                    |       | 5                    |             | με   | -               |

| CE setup time                           | t <sub>ECS</sub>  | 500                  |       | 500                  |             | ns   |                 |

| Data hold time                          | t <sub>EDH</sub>  | 100                  |       | 100                  |             | ns   |                 |

| Data setup time                         | t <sub>EDS</sub>  | 500                  |       | 500                  |             | ns   |                 |

| OE hold time                            | tEOEH             | t <sub>ECH</sub> + 3 |       | t <sub>ECH</sub> + 3 |             | μs   |                 |

| OE setup time                           | t <sub>EOES</sub> | 500                  |       | 500                  |             | ns   |                 |

| WE pulse width                          | tEWP              | 10                   |       | 10                   |             | ms   |                 |

#### Notes:

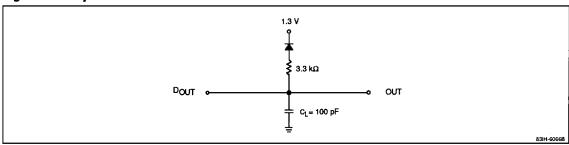

- See figure 1 for the output load. Input rise and fall time ≤ 20 ns; input pulse levels = 0.45 and 2.4 V; timing measurement reference levels = 0.8 and 2.0 V for both inputs and outputs.

- (2) Output hold time is specified from address, OE or CE, whichever goes invalid first.

Figure 1. Output Load

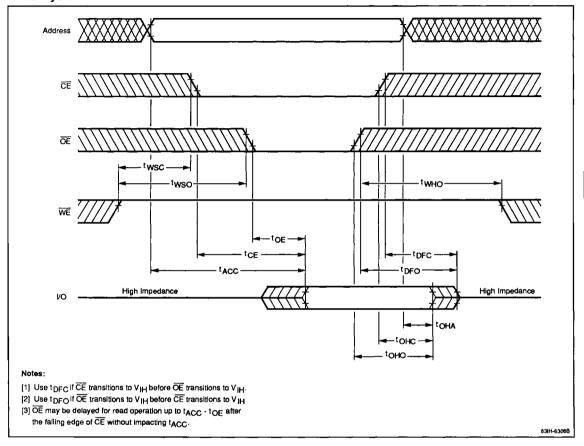

# **Timing Waveforms**

# Read Cycle

# Timing Waveforms (cont)

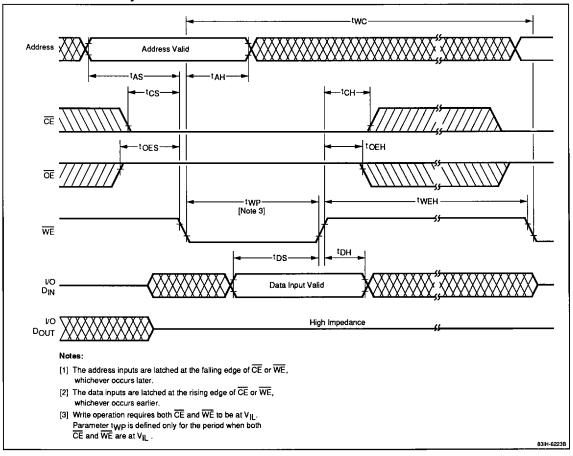

# WE-Controlled Write Cycle

# Timing Waveforms (cont)

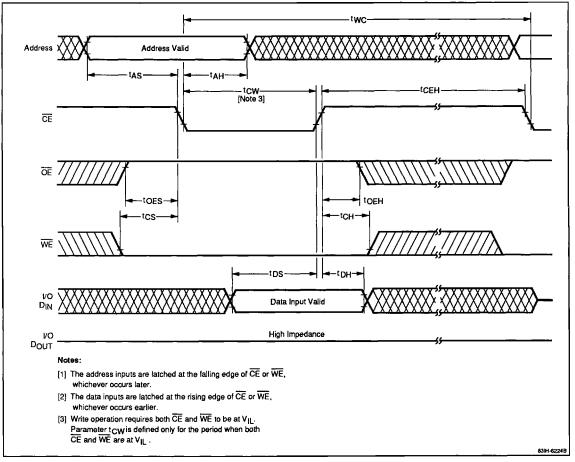

# CE-Controlled Write Cycle

# Timing Waveforms (cont)

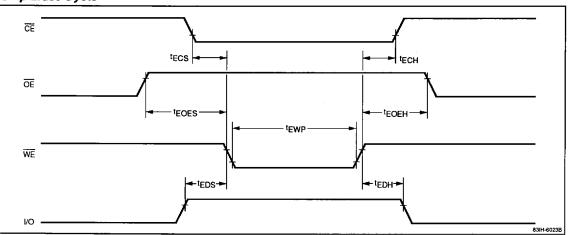

# Chip Erase Cycle

#### Read Cycle

Both  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  must be at  $V_{IL}$  in order to read stored data. While the device is executing read cycles, bringing either of these inputs to  $V_{IH}$  will place the outputs in a state of high impedance. This two-line output control allows bus contention to be eliminated in the system application.

## Byte Write Cycle

Low levels on  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  and a high level on  $\overline{\text{OE}}$  place the  $\mu\text{PD28C04}$  in write operation. The write address inputs are latched by the falling edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs later. The data inputs are latched by the rising edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs earlier. Once byte write cycles begin executing, internal circuits assume all timing control and the byte being addressed is automatically erased and then programmed. The operation is completed within a write cycle time ( $t_{\text{WC}}$ ) of 10 ms.

## Chip Erase Cycle

All bytes of the  $\mu PD28C04$  can be erased simultaneously by making  $\overline{CE}$  and  $\overline{WE}$  fall to  $V_{IL}$  after  $\overline{OE}$  has been increased to  $V_{IHH}$  (15±0.5 V). The address inputs are "don't care," but the data inputs must all be driven to  $V_{IH}$  before the chip erase cycle begins.

## **DATA** Polling Feature

This feature supports system software by indicating the precise end of byte write cycles.  $\overline{\text{DATA}}$  polling can be used to reduce the total programming time of the  $\mu\text{PD28C04}$  to a minimum value, which varies with the system environment.

While internal automatic write cycles are in progress, any attempt to read data at the last externally supplied address location will result in inverted data on pin I/O<sub>7</sub> (for example, if write data = 1xxx xxxx, then read data = 0xxx xxxx). Once the write cycle is complete, a read cycle will result in true data being output on I/O<sub>7</sub>.

## Write Protection Features

The  $\mu$ PD28C04 provides three features to prevent invalid write cycles:

27a

- Noise immunity, where write operation is inhibited when the WE pulse width is 20 ns or less.

- Supply voltage-level detection, where write operation is inhibited when V<sub>CC</sub> is 2.5 volts or less.

- Write protection logic, where write operation is inhibited if OE is held low or OE or WE is held high during power-on or -off of the V<sub>CC</sub> supply voltage.