# 16,384 (2K X 8) BIT UV ERASABLE PROM

### **DESCRIPTION**

The  $\mu$ PD2716 is a 16,384 bit (2048 x 8 bit) Ultraviolet Erasable and Electrically Programmable Read-Only Memory (EPROM). It operates from a single +5 volt supply, making it ideal for microprocessor applications. It offers a standby mode with an attendant 75% savings in power consumption, and is compatible with the  $\mu$ PD2316E as a ROM. This allows for economical change-over to a masked ROM for production quantities, where desired.

The  $\mu$ PD2716 features fast, simple one pulse programming controlled by TTL level signals. Total programming time for all 16,384 bits is only 100 seconds.

### **FEATURES**

- Ultraviolet Erasable and Electrically Programmable

- Access Time 390 ns Max

- Single Location Programming

- Programmable with Single Pulse

- Low Power Dissipation Standby Mode

- Input/Output TTL Compatible for Reading and Programming

- Pin Compatible to μPD2316E, μPD446 and μPD4016.

- Single +5V Power Supply

- 24 Pin Ceramic DIP

- Three-State Outputs

### PIN CONFIGURATION

|                  |    |      |    | 1                       |

|------------------|----|------|----|-------------------------|

| A7 🗖             | 1  |      | 24 | VCC (+5V)               |

| <b>^6</b> □      | 2  |      | 23 | <b>□</b> ^8             |

| A5 □             | 3  |      | 22 | <b>□</b> A <sub>9</sub> |

| A4 🗖             | 4  |      | 21 | □ V <sub>PP</sub>       |

| A3 🗆             | 5  |      | 20 | D OE                    |

| A2 🗖             | 6  | μPD  | 19 | A10                     |

| A1 🗆             | 7. | 2716 | 18 | ☐ CE/PGM                |

| A <sub>0</sub> □ | 8  |      | 17 | <b>□</b> 07             |

| ∞⊏               | 9  |      | 16 | <b>□</b> 06             |

| 01 □             | 10 |      | 15 | <b>□</b> 0 <sub>5</sub> |

| 02 □             | 11 |      | 14 | <b>□</b> 04             |

| (0V) GND 🗆       | 12 |      | 13 | <b>Þ</b> ∘₃             |

|                  |    |      |    |                         |

#### ..........

|                                 | PIN NAMES           |

|---------------------------------|---------------------|

| A <sub>0</sub> -A <sub>10</sub> | Addresses           |

| OE                              | Output Enable       |

| 00-07                           | Data Outputs        |

| CE/PGM                          | Chip Enable/Program |

TABLE 1. MODE SELECTION

| PINS<br>MODE    | Œ/PGM             | ŌĒ         | Vpp | Vcc | OUTPUTS |

|-----------------|-------------------|------------|-----|-----|---------|

| Read            | VIL               | VIL        | +5  | +5  | POUT    |

| Standby         | VIH               | Don't Care | +5  | +5  | High Z  |

| Program         | Pulsed VIL to VIH | ViH        | +25 | +5  | DIN     |

| Program Verify  | VIL               | VIL        | +25 | +5  | DOUT    |

| Program Inhibit | VIL               | VIH        | +25 | +5  | High Z  |

$V_{IH}$  and  $V_{IL}$  are TTL high level ("1") and TTL low level ("0") respectively.

## **μPD2716**

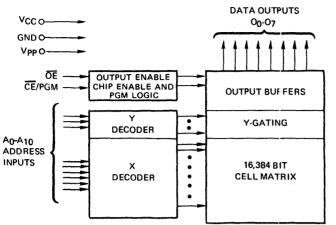

**BLOCK DIAGRAM**

Output Voltage....-0.3 to +6 Volts Supply Voltage V<sub>cc</sub>....-0.3 to +6 Volts

$T_a = 25^{\circ}C$

\*COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

T<sub>2</sub> = 25°C: f = 1 MHz

|                    |        |     | LIMITS |     |      | TEST       |

|--------------------|--------|-----|--------|-----|------|------------|

| PARAMETER          | SYMBOL | MIN | TYP    | MAX | UNIT | CONDITIONS |

| Input Capacitance  | CIN    |     | 4      | 6   | pF   | VIN = 0V   |

| Output Capacitance | COUT   |     | 8      | 12  | рF   | VOUT = 0V  |

## READ MODE AND STANDBY MODE

$T_8 = 0^{\circ}C \sim 70^{\circ}C$ ;  $V_{CC}$  ① = +5V ± 5%;  $V_{PP}$  ① ② =  $V_{CC}$  ± 0.6V ③

|                             |                  |      | LIMITS | 3                  |        |                                    |

|-----------------------------|------------------|------|--------|--------------------|--------|------------------------------------|

| PARAMETER                   | SYMBOL           | MIN. | TYP.   | MAX.               | UNIT   | TEST CONDITIONS                    |

| Output High Voltage         | VOH              | 2.4  |        |                    | \<br>\ | 1 <sub>OH</sub> = -400 μA          |

| Output Low Voltage          | VOL              |      |        | 0.45               | ٧      | IOL = 2.1 mA                       |

| Input High Voltage          | VIN              | 2.0  |        | V <sub>cc</sub> +1 | V      |                                    |

| Input Low Voltage           | VIL              | -0.1 |        | 0.8                | V      |                                    |

| Output Leakage Current      | 1LO              |      |        | 10                 | μΑ     | V <sub>OUT</sub> = 5.25V           |

| Input Leakage Current       | 11L              |      |        | 10                 | μΑ     | V <sub>IN</sub> = 5.25V            |

| V <sub>PP</sub> Current     | l <sub>PP1</sub> |      |        | 5                  | mA     | V <sub>PP</sub> = 5.85V            |

| V <sub>CC</sub> Current (2) | 1cc1             |      | 10     | 25                 | mA     | CE/PGM = VIH OE - VIL Standby Mode |

| V <sub>CC</sub> Current ②   | I <sub>CC2</sub> |      | 57     | 100                | mA     | CE/PGM = VIL OE - VIL Read Mode    |

Notes: 1 VCC must be applied simultaneously or before Vpp and removed after Vpp.

- 2 Vpp may be connected directly to VCC (+5V) at read mode and standby mode. The supply current would then be the sum of Ipp1 and ICC (ICC1 or ICC2).

- 3 The tolerance of 0.6V allows the use of a driver circuit for switching the Vpp supply pin from +25V to +5V.

### CAPACITANCE

### DC CHARACTERISTICS

## PROGRAM, PROGRAM VERIFY AND PROGRAM INHIBIT MODE

# DC CHARACTERISTICS (CONT.)

$T_a = 25^{\circ} C \pm 5^{\circ} C$ ;  $V_{CC}$  ① = +5V ± 5%;  $V_{PP}$  ① ④ = +25V ± 1V

|                         | Į.               | LIMITS |      |                    |      |                                             |

|-------------------------|------------------|--------|------|--------------------|------|---------------------------------------------|

| PARAMETER               | SYMBOL           | MIN.   | TYP. | MAX.               | UNIT | TEST CONDITIONS                             |

| nput High Voltage       | ViH              | 2.0    |      | V <sub>cc</sub> +1 | ٧    |                                             |

| Input Low Voltage       | VIL              | -0.1   |      | 0,8                | V    |                                             |

| Input Leakage Current   | 1 <sub>IL</sub>  |        |      | 10                 | μА   | V <sub>IN</sub> = 5.25V/0,45V               |

| V <sub>PP</sub> Current | l <sub>PP1</sub> |        |      | 5                  | mA   | Program Verify CE/PGM = VIL Program Inhibit |

|                         | Ipp2             |        |      | 30                 | mA   | CE/PGM = VIH Program Mode                   |

| CC Current              | ¹cc              |        |      | 100                | mA   |                                             |

### AC CHARACTERISTICS

### READ MODE AND STANDBY MODE

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C; V_{CC} = +5V \pm 5\%; V_{PP} = 0^{\circ} = V_{CC} \pm 0.6V$

|                                       |                 |     | LIMIT | S   |      | TEST              |

|---------------------------------------|-----------------|-----|-------|-----|------|-------------------|

| PARAMETER                             | SYMBOL          | MIN | TYP   | MAX | UNIT | CONDITIONS        |

| Address to Output Delay               | †ACC            |     |       | ⑤   | ns   | CE/PGM = OE = VIL |

| CE/PGM to Output Delay                | <sup>t</sup> CE |     |       | ⑤   | ns   | OE = VIL          |

| Output Enable<br>to Output Delay      | . toE           |     |       | 120 | ns   | CE/PGM = VIL      |

| Output Enable High<br>to Output Float | <sup>t</sup> DF | 0   |       | 100 | ns   | CE/PGM = VIL      |

| Address to Output Hold                | .toH            | 0   |       |     | ns   | CE/PGM = OE = VIL |

**Test Conditions**

Output Load: 1 TTL gate and CL = 100 pF

Input Rise and Fall Times: 20 ns Input Pulse Levels: 0.8 to 2.2V Timing Measurement Reference Level:

Inputs: 1.0V and 2.0V Outputs: 0.8V and 2.0V

### PROGRAM, PROGRAM VERIFY AND PROGRAM INHIBIT MODE

$T_a = 25^{\circ} \text{ C} \pm 5^{\circ} \text{ C}; V_{CC} = +5 \text{ V} \pm 5 \text{ W}; V_{PP} = +25 \text{ V} \pm 1 \text{ V}$

|                                     |                 |     | LIMIT | s   |       | TEST         |

|-------------------------------------|-----------------|-----|-------|-----|-------|--------------|

| PARAMETER                           | SYMBOL          | MIN | TYP   | MAX | UNITS | CONDITIONS   |

| Address Setup Time                  | tAS             | 2   |       |     | μs    |              |

| OE Setup Time                       | tOES            | 2   |       |     | μs    |              |

| Data Setup Time                     | tDS             | 2   |       |     | μs    |              |

| Address Hold Time                   | tAH             | 2   |       |     | μs    |              |

| OE Hold Time                        | ₹0EH            | 2   |       |     | μs    |              |

| Data Hold Time                      | tDH             | 2   |       |     | μs    |              |

| Output Enable to Output Float Delay | <sup>t</sup> DF | 0   |       | 120 | ns    | CE/PGM = VIL |

| Output Enable to Output Delay       | <sup>t</sup> OE |     |       | 120 | ns    | CE/PGM = VIL |

| Program Pulse Width                 | tpW             | 45  | 50    | 55  | ms    |              |

| Program Pulse Rise Time             | <b>tPRT</b>     | 5   |       |     | ns    |              |

| Program Pulse Fall Time             | <b>tPFT</b>     | 5   |       |     | ns    |              |

Test Conditions:

Input Pulse Levels . . . . . . . . 0.8V to 2.2V Output Timing Reference Level. . . 0.8V and 2V Input Timing Reference Level. . . . . 1V and 2V

- Notes: 1 VCC must be applied simultaneously or before Vpp and removed after Vpp.

- ② Vpp may be connected directly to V<sub>CC</sub> (+5V) at read mode and standby mode. The supply current would then be the sum of lpp1 and l<sub>CC</sub> (l<sub>CC1</sub> or l<sub>CC2</sub>).

- The tolerance of 0.6V allows the use of a driver circuit for switching the Vpp supply pin from +25V to +5V.

- Q During programming, program inhibit, and program verify, a maximum of +26V should be applied to the Vpp pin. Overshoot voltages to be generated by the Vpp power supply should be limited to less than +26V.

- ⑤ μPD2716 450 ns μPD2716-2 390 ns

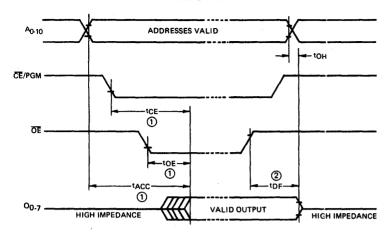

### READ MODE

## **TIMING WAVEFORMS**

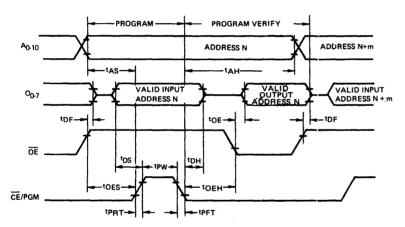

### PROGRAM MODE

Notes: ①  $\overline{\text{OE}}$  may be delayed up to tACC-tOE after the falling edge of  $\overline{\text{CE}}/\text{PGM}$  for read mode without impact on tACC

2) tDF is specified from OE or CE/PGM, whichever occurs first.

FUNCTIONAL The μPD2716 operates from a single +5V power supply and, accordingly, is ideal DESCRIPTION for use with +5V microprocessors such as μPD8085 and μPD8048/8748.

> Programming of the uPD2716 is achieved with a single 50 ms TTL pulse. Total programming time for all 16,384 bits is only 100 sec. Due to the simplicity of the programming requirements, devices on boards and in systems may be programmed easily and without any special programmer.

> The uPD2716 features a standby mode which reduces the power dissipation from a maximum active power dissipation of 525 mW to a maximum standby power dissipation of 132 mW. This results in a 75% savings with no increase in access time.

Erasure of the µPD2716 programmed data can be attained when exposed to light with wavelengths shorter than approximately 4,000 Angstroms (A). It should be noted that constant exposure to direct sunlight or room level fluorescent lighting could erase the  $\mu$ PD2716. Consequently, if the  $\mu$ PD2716 is to be exposed to these types of lighting conditions for long periods of time, the µPD2716 window should be masked to prevent unintentional erasure.

The recommended erasure procedure for the µPD2716 is exposure to ultraviolet light with wavelengths of 2,537 Angstroms (A). The integrated dose (i.e., UV intensity x exposure time) for erasure should be not less than 15 W-sec/cm<sup>2</sup>. The erasure time is approximately 15 to 20 minutes using an ultraviolet lamp of 12,000 μW/cm<sup>2</sup> power rating.

During erasure, the µPD2716 should be placed within 1 inch of the lamp tubes. If the lamps have filters on the tubes, the filters should be removed before erasure.

**OPERATION**

The five operation modes of the µPD2716 are listed in Table 1. The power supplies required are a +5V V<sub>CC</sub> and a V<sub>PP</sub>. The V<sub>PP</sub> power supply should be at +25V during programming, program verification and program inhibit, and it should be at +5V during read and standby. CE/PGM, OE and Vpp select the operation mode as shown in Table 1.

READ MODE When CE/PGM and OE are at low (0) level with Vpp at +5V, the READ MODE is set and the data is available at the outputs after toe from the falling edge of OE and tACC after setting the address.

STANDBY MODE The µPD2716 is placed in the standby mode with the application of a high (1) level TTL signal to the CE/PGM and a Vpp of +5V. In this mode, the outputs are in a high impedance state, independent of the OE input. The active power dissipation is reduced by 75% from 525 mW to 132 mW.

PROGRAMMING MODE Programming of the µPD2716 is commenced by erasing all data and consequently having all bits in the high (1) level state. Data is then entered by programming a low (0) level TTL signal into the chosen bit location.

The  $\mu$ PD2716 is placed in the programming mode by applying a high (1) level TTL signal to the OE with Vpp at +25V. The data to be programmed is applied to the output pins 8 bits in parallel at TTL levels.

Any location can be programmed at any time, either individually, sequentially or at random.

When multiple  $\mu$ PD2716s are connected in parallel, except for  $\overline{CE}$ /PGM, individual μPD2716s can be programmed by applying a high (1) level TTL pulse to the CE/PGM input of the desired µPD2716 to be programmed.

Programming of multiple µPD2716s in parallel with the same data is easily accomplished. All the alike inputs are tied together and are programmed by applying a high (1) level TTL pulse to the CE/PGM inputs.

# μPD2716

Programming of multiple µPD2716s in parallel with different data is rendered more easily by the program inhibit mode. Except for CE/PGM, all alike inputs (including OE) INHIBIT MODE of the parallel µPD2716s may be common. Programming is accomplished by applying a TTL level program pulse to the µPD2716 CE/PGM input with Vpp at +25V. A low level applied to the CE/PGM of the other µPD2716 will inhibit it from being programmed.

**PROGRAMMING**

A verify should be performed on the programmed bits to determine that the data was correctly programmed on all bits of the µPD2716. The program verify can be performed with Vpp at +25V and CE/PGM and OE at low (O) levels.

PROGRAM VERIFY MODE

The data outputs of two or more µPD2716s may be wire-ored together to the same data bus. In order to prevent bus contention problems between devices, all but the selected  $\mu PD2716s$  should be deselected by raising the  $\overline{OE}$  input to a TTL high.

OUTPUT DESELECTION

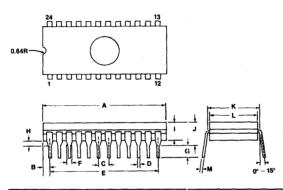

PACKAGE OUTLINE μPD2716D (CERDIP)

| ltem | Millimeters | inches        |

|------|-------------|---------------|

| A    | 33.5 MAX.   | 1,32 MAX.     |

| В    | 2.78        | 1,1           |

| С    | 2.54        | 0.1           |

| D    | 0.46 + 0.10 | 0.018 - 0.004 |

| E    | 27.94       | 1.10          |

| F    | 1.3         | 0.05          |

| G    | 2.54 MIN.   | 0.1 MIN.      |

| Н    | 0.5 MIN.    | 0.020         |

| 1    | 5.0 MAX.    | 0.20          |

| J    | 5.5 MAX.    | 0.216         |

| К    | 15.24       | 0.60          |

| L    | 14.66       | 0.58          |

| М    | 0.25 · 0.05 | 0.010 · 0.002 |

### Window Label

An amber-colored window label is provided unattached for the convenience of the user. The window label filters ultra-violet light frequencies, thus preventing accidental erasure or long-term degradation caused by ambient light or sunlight.