# 2816A 16K (2K x 8) ELECTRICALLY ERASABLE PROM

- 5 Voit Only Operation

- Fast Read Access Time:

- -2816A-2, 200ns Max

- -2816A. 250ns Max

- ---2816A-3, 350ns Max

- -2816A-4, 450ns Max

- Byte Erase/Write with TTL Level WE Signal

- 9ms Byte Erase/Write Time

- 9ms Chip Erase Time

- HMOS\*-E Flotox Cell Design

- Minimum Endurance of 10,000 Erase/Write Cycles per Byte

- Unlimited Number of Read Cycles

- Conforms to JEDEC Universal Site

- Erase/Write Specifications Guaranteed 0–70°C

- Write Protect Circuit to Preserve Data on Power Up and Power Down

The Intel 2816A is a 16,384-bit electrically erasable programmable read-only memory (E<sup>2</sup>PROM). The 2816A can be easily erased and reprogrammed on a byte basis with a TTL-low level signal on WE. The 2816A operates from a single 5 Volt supply. External programming voltage and write pulse shaping are not required because they are generated by on-chip circuitry.

The Intel 2816A is compatible with the Intel 2816 E<sup>2</sup>PROM. Dual voltage detection logic allows the 2816A to use an existing, externally supplied high voltage programming pulse required with the 2816 to write to the Intel 2816A. No hardware changes are required when substituting a 2816A in an existing 2816 socket. System upgrades to 5 volt only operation can be implemented, however, by removing the 21V and write shaping circuitry. The 2816A, like the 2816, has fast read access speeds allowing zero wait state read cycles with high performance microprocessors such as the IAPX286.

The electrical erase/write capability of the 2816A makes it ideal for a wide variety of applications requiring in-system, non-volatile erase and write. Any byte can be erased in 9ms without affecting the data in any other byte. Alternatively, the entire memory can be erased in 9ms allowing the total time to rewrite all 2k bytes to be cut by 50%. The 2816A is part of the Intel E<sup>2</sup>PROM family that provides a significant increase in flexibility allowing new applications (remote firmware update of program code, dynamic parameter storage) never before possible.

The 2816 E<sup>2</sup>PROM possesses Intel's 2-line control architecture to eliminate bus contention in a system environment. A power down mode is also featured; in standby mode, power consumption is reduced by over 50% without increasing access time. The standby mode is achieved by applying a TTL-high signal to the  $\overline{\text{CE}}$  input.

\*HMOS is a patented process of Intel Corporation

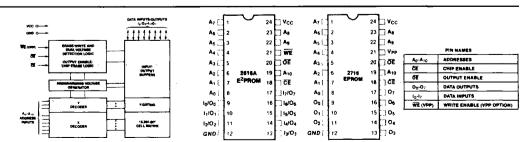

Figure 1. 2816A Functional Block Diagram

Figure 2. Pin Configuration

#### **DEVICE OPERATION**

The 2816A has six modes of operation, listed in Table 1. All operational modes are designed to provide maximum microprocessor compatibility and system consistency.

Table 1. Mode Selection

| PIN          | CE<br>(18)      | <b>OE</b> (20)       | WE<br>(21)    | INPUTS/<br>OUTPUTS               |  |

|--------------|-----------------|----------------------|---------------|----------------------------------|--|

| Read         | VIL             | VIL                  | VIH           | Dout                             |  |

| Standby      | ViH             | Don't<br>Care        | Don't<br>Care | High Z                           |  |

| Byte Erase   | VIL             | VIH                  | VIL           | DIN=VIH                          |  |

| Byte Write   | VIL.            | ViH                  | VIL           | DIN                              |  |

| Chip Erase   | VIL             | + 10V<br>to<br>+ 15V | VIL           | D <sub>IN</sub> =V <sub>IH</sub> |  |

| No Operation | VIL             | ViH                  | ViH           | High Z                           |  |

| E/W Inhibit  | V <sub>lH</sub> | VIH                  | VIL           | High Z                           |  |

All control inputs are TTL-compatible with the exception of chip erase.

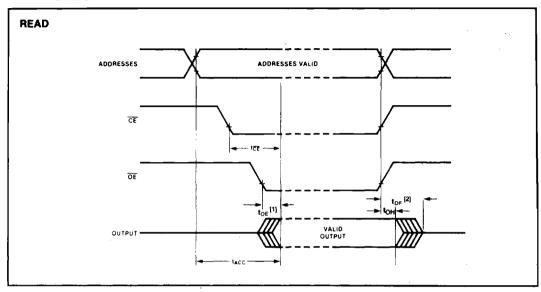

#### **READ MODE**

Optimal system efficiency depends to a great extent on a tightly coupled microprocessor/memory interface. The E<sup>2</sup>PROM device should respond rapidly with data to allow the highest possible CPU performance. The 2816A satisfies this high performance requirement because of read access times typically less than 250ns. Program execution directly out of electrically erasable memory has never before been possible; the 2816A opens this new, powerful applications segment.

The 2816A uses Intel's proven 2-line control architecture for read operation. The 2-line control function removes bus contention from the system environment and allows low power dissipation (by deselecting unused devices).

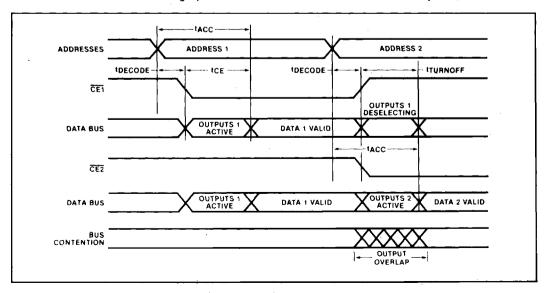

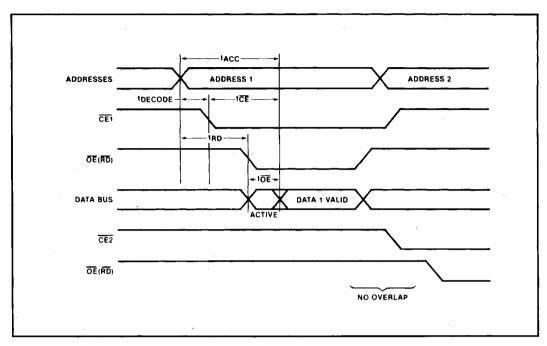

Figure 3 shows the timing disadvantages of a single-line control architecture. 2-line control, shown in Figure 4, has been developed by Intel to solve this bus contention and the associated system reliability problems. Both  $\overline{CE}$  and  $\overline{OE}$  must be at logic low levels to obtain information from the device. Chip enable ( $\overline{CE}$ ) is the power control pin and should be used for device selection. The output enable ( $\overline{OE}$ ) pinserves to gate internal data to the output pins. Assuming that the address inputs are stable, address access time ( $t_{ACC}$ ) is equal to the delay from  $\overline{CE}$  to output ( $t_{CE}$ ). Data is available at the outputs after a time delay of  $t_{OE}$ , assuming that  $\overline{CE}$  has been low and addresses have been stable for at least  $t_{ACC}$ – $t_{OE}$ .

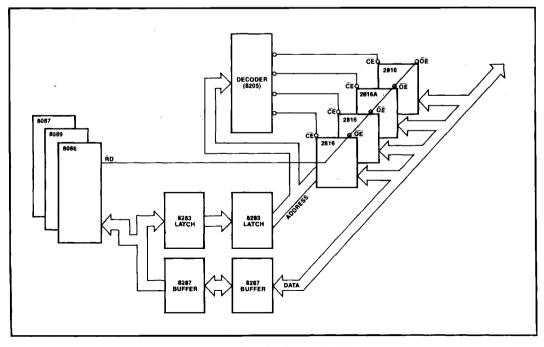

Figure 5 shows a typical system interconnection. Here the 2816A contains program information that the 8086 requires for system function.  $\overline{CE}$  (pin 18) is decoded from addresses as the primary device selection function.  $\overline{OE}$  (pin 20) should be made a common connection to all devices in system, and connected

Figure 3. Single-Line Control and Bus Contention

Figure 4. Two-Line Control Architecture

Figure 5. iAPX 86/2816A Read Architecture

to the RD line from the system control bus. This assures that all deselected memory devices are in their low power standby mode and that the output pins are only active when data is desired from a particular memory device.

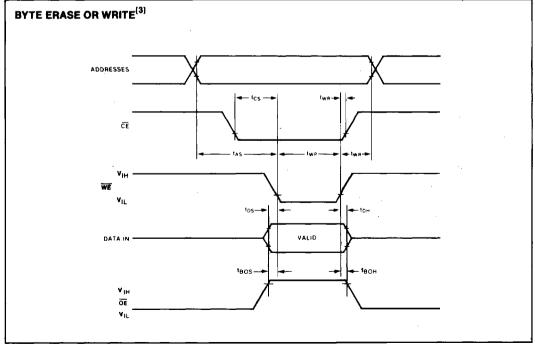

#### WRITE MODE

The 2816A is erased and reprogrammed electrically as opposed to EPROMs which require ultraviolet light for erasure. The device offers dynamic flexibility because both byte (single location) and chip erase are possible.

A close examination of the broad application spectrum for the E<sup>2</sup> device reveals an inherent need for single location erase capability. Program store applications can be classified in several ways. Figure 6 lists various storage modes and the required erase function. In greater than 80% of all cases, a byte erase feature is necessary.

| APPLICATION TYPE              | IDEAL<br>ERASE MODE |

|-------------------------------|---------------------|

| STRICT PROGRAM STORE          | CHIP                |

| RELOCATABLE PROGRAM STRUCTURE | BYTE                |

| PROGRAM STORE EXTENSION       | BYTE                |

| PROGRAM EXECUTION CONSTANTS   | BYTE                |

| PROGRAM DEPENDENT DATA STORE  | BYTE                |

| DATA STORE APPLICATIONS       | BYTE                |

Figure 6. Microprocessor Storage Types

To write a particular location, that byte must be erased prior to a data write. Erasing is accomplished by placing the byte address at the address input pins, applying logic 1 (TTL-high) to all eight data input pins, and lowering  $\overline{\text{CE}}$ ,  $\overline{\text{WE}}$  to  $V_{1L}$ . The  $\overline{\text{OE}}$  pin must be held at  $V_{1H}$  during byte erase and write operations. The  $\overline{\text{WE}}$  pulse width must be a minimum of 9ms, and a maximum of 15ms. Once the location has been erased, the same operation is repeated for a data write. The data input pins in this case reflect the byte that is to be stored. The data to be programmed, address and control signals must be presented to the 2816A throughout the required programming time.

Because the device is designed to be written in system, all data sheet specifications (including write and erase operations) hold over the full operating temperature range (0-70°C).

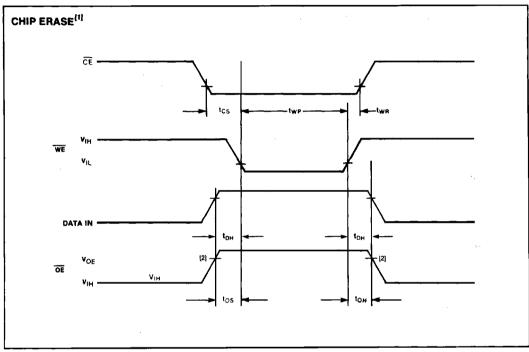

#### **CHIP ERASE MODE**

Should one wish to erase the entire 2816A array at once, the device offers a chip erase function. When

the chip erase function is performed, all 2K bytes are returned to a logic 1 (FF) state.

The 2816A's chip erase function is engaged when the output enable (OE) pin is raised above 9 volts. When OE is greater that 9 volts and CE and WE are in the normal write mode, the entire array is erased. This chip erase function takes approximately 10ms. The data input pins must be held to a TTL-high level during this time.

#### STANDBY MODE

The 2816A has a standby mode which reduces active power dissipation by 50% from 100ma to 50ma. The 2816A is placed in standby mode by applying a TTL-high signal to the  $\overline{\text{CE}}$  input. When in the standby mode, the outputs are in a high impedance state, independent of the  $\overline{\text{OE}}$  and  $\overline{\text{WE}}$  input.

The standby mode for the 2816A is a superset of the standby mode for the 2816. The standby mode for the 2816A includes the E/W inhibit mode of the 2816.

#### NO OPERATION MODE

This mode is frequently entered while in a read or write cycle. In the READ cycle,  $\overline{CE}$  may go low before  $\overline{OE}$  goes low because  $t_{CE}$  ( $\overline{CE}$  to Output Delay) is longer than  $t_{\overline{OE}}$  ( $\overline{OE}$  to Output Delay). While  $\overline{CE}$  is low with  $\overline{OE}$  and  $\overline{WE}$  at TTL-high, no READ, ERASE, or WRITE operation will occur. The read operation would begin in the READ cycle when  $\overline{OE}$  input also falls to TTL-low.

The No Operation mode differs from Standby Mode in that active power is drawn by the 2816A in this mode.

#### WRITE TIME CHARACTERISTICS

The 2816A write time specification is 9ms (min.) and 15ms (max.). If the write pulse width applied to the WE input is 9ms, the programmed byte is guaranteed to be correctly and reliably programmed to any location in the 2816A.

The maximum pulse width to the WE input of 15ms limits the duration of the pulse width. Exceeding this specification may overstress the E<sup>2</sup>PROM cells and affect long term device reliability. Any write pulse width between 9ms and 15ms will also guarantee byte programming and chip erase over the full temperature range.

Programmed data will be retained by the Intel 2816A for over 10 years.

Although the number of read cycles is unlimited, a characteristic of all E<sup>2</sup>PROMs is that the total number of erase/write cycles is not unlimited. The 2816A has been designed and manufactured to meet applications requiring up to 1 x 10<sup>4</sup> erase/write cycles per byte. The erase/write cycling characteristic is completely byte independent. Adjacent bytes are not affected during erase/write cycling.

# On-Chip Write Protection on V<sub>CC</sub> Power Up and Power Down

An erase/write of a byte in the 2816A is accomplished with input signals  $\overline{CE}$ ,  $\overline{WE} = V_{1L}$ . During system (Vcc) power up and power down, this condition may be present as Vcc ramps up to or down from its steady state value of 5 volts. To prevent the possibility of an inadvertent byte write during this power transition period, an on-chip sensing circuit disables the internal programming circuit if Vcc falls below 4 volts ( $V_{LKO}$ ).

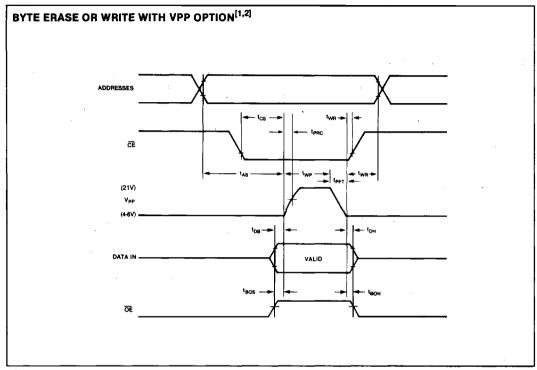

### **VPP OPTION**

Although the Intel® 2816A requires only 5 volts for programming, it was designed to be totally upward compatible with the Intel 2816. No hardware changes are required when substituting a 2816A into a 2816 socket. Shaping of the Vpp programming pulse is also not required with the 2816A. Table 2 lists the Vpp Option Modes.

**Table 2. VPP Option Modes**

| PIN        | CE<br>(18) | ŌĒ<br>(20)         | VPP<br>(21) | INPUTS/<br>OUTPUTS               |

|------------|------------|--------------------|-------------|----------------------------------|

| Byte Erase | VĮL        | VIH                | 20-22V      | D <sub>IN</sub> =V <sub>IH</sub> |

| Byte Write | VIL 1      | VIH                | 20-22V      | DIN                              |

| Chip Erase | VIL        | +10V<br>to<br>+15V | 20-22V      | D <sub>IN</sub> =V <sub>IH</sub> |

#### **APPLICATIONS**

2816A

The 2816A E<sup>2</sup>PROM is a new and powerful addition to the Intel non-volatile family. Like other Intel E<sup>2</sup>PROMs, it offers a high degree of flexibility through in-circuit alterability while retaining the non-volatile characteristics of ROM.

Because of these device parameters, the device is ideal in many applications. Some of the potential uses are listed below:

- Calibration constants storage (continuous calibration)

- 2. Software alterable central stores (dynamic reconfiguration)

- 3. Remote communication programming

- 4. PC and NC Industrial Applications

- CRT Terminal configuration and custom graphic and font sets

- Military replacement for core memory and fuselink PROMs

- 7. Point of sale terminals

- 8. Remote alterable look-up tables

- 9. Printer communications, controllers

- 10. Remote data or error logging

- 11. Replacing CMOS RAM and battery backup

- 12. Remote firmware update of program code

#### **AVAILABLE LITERATURE**

To give the system designer an opportunity to more thoroughly understand the device attributes and uses, a library of E<sup>2</sup>PROM information is available in the Memory Component Handbook. Some of the E<sup>2</sup>PROM application information included is listed below.

AR 119 — 16-K EE-PROM Relies On Tunneling for Byte-Erasable Program Storage

AP 100 — Reliability Aspects of a Floating Gate E<sup>2</sup>PROM

#### **ABSOLUTE MAXIMUM RATINGS\***

Temperature Under Bias ..... – 10°C to +80°C

Storage Temperature ..... – 65°C to + 100°C

All Input or Output Voltages with

Respect to Ground ..... + 6V to – 0.3V

Maximum Duration of Erase/Write Cycle ... 20ms

VOE with Respect to Ground .... + 17V to – 0.1V

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. AND A.C. OPERATING CONDITIONS DURING READ AND WRITE

| Temperature Range            | 0°C-70°C |

|------------------------------|----------|

| V <sub>CC</sub> Power Supply | 5V ± 5%  |

#### D.C. CHARACTERISTICS

|                       |                                                      |       | Limits  |                    |       |                           |  |

|-----------------------|------------------------------------------------------|-------|---------|--------------------|-------|---------------------------|--|

| Symbol                | Parameter                                            | Min.  | Тур.[1] | Max.               | Units | Test Conditions           |  |

| լը                    | Input Leakage Current                                |       |         | 10                 | μΑ    | $V_{IN} = 5.25V^{(2)}$    |  |

| ILO                   | Output Leakage Current                               |       |         | 10                 | μΑ    | V <sub>OUT</sub> = 5.25V  |  |

| ICCA                  | V <sub>CC</sub> Current (Active)                     |       | 50      | 100                | mA    | OE = CE = VIL             |  |

| Iccs                  | V <sub>CC</sub> Current (Standby)                    |       | 25      | 50                 | mA    | CE = V <sub>IH</sub>      |  |

| Iccw                  | V <sub>CC</sub> Current (Byte Erase/Write)           |       |         | 130                | mA    | WE = CE = V <sub>IL</sub> |  |

| V <sub>IL(D.C.)</sub> | Input Low Voltage (D.C.)                             | - 0.1 |         | 0.8                | ٧     |                           |  |

| V <sub>IL(A.C.)</sub> | Input Low Voltage (A.C.)                             | - 0.4 |         |                    | V     | Time = 10 ns              |  |

| VIH                   | Input High Voltage                                   | 2.0   |         | V <sub>CC</sub> +1 | ٧     |                           |  |

| VOL                   | Output Low Voltage                                   |       |         | 0.45               | ٧     | I <sub>OL</sub> = 2.1mA   |  |

| VoH                   | Output High Voltage                                  | 2.4   |         |                    | V     | $I_{OH} = -400\mu A$      |  |

| VOE                   | OE Voltage for Chip Erase                            | 10    |         | 15                 | V     | I <sub>OE</sub> = 10μA    |  |

| V <sub>LKO</sub>      | V <sub>CC</sub> Lockout Level for Data<br>Protection | 4.0   |         | 4.4                | ٧     |                           |  |

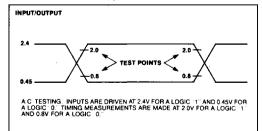

#### A.C. TEST CONDITIONS

| Output Load             | 1TTL gate and $C_L = 100pF$ |

|-------------------------|-----------------------------|

| Input Rise and Fall Tim | es (10% to 90%) 20ns        |

| Input Pulse Levels      | 0.45V to 2.4V               |

| Input Timing Reference  | Level 0.8V and 2.0V         |

| Output Timing Referen   | ce Level 0.8V and 2.0V      |

<sup>1.</sup> This parameter is only sampled and not 100% tested.

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

<sup>2.</sup> I<sub>LI(Max)</sub> is less than 10µa when V<sub>IN</sub> is less than 5.25V.

CAPACITANCE [1] TA = 25°C, f = 1 MHz

| Symbol    | Parameter Ty                |   | Max. | Units | Test Conditions       |  |

|-----------|-----------------------------|---|------|-------|-----------------------|--|

| CIN       | Input Capacitance           | 5 | 10   | pF    | VIN = OV              |  |

| Cout      | Output Capacitance          |   | 10   | pF    | V <sub>OUT</sub> = 0V |  |

| Cvcc      | V <sub>CC</sub> Capacitance |   | 500  | pF    | OE = CE = VIH         |  |

| CWE (VPP) | WE Input Capacitance        |   | 50   | pF    | ŌĒ = Œ = VIH          |  |

#### A.C. CHARACTERISTICS

#### READ

| Symbol              | Parameter                                                              | 281  | 6A-2 Li | mits | 21   | 16A Lie | nite | 281  | 2816A-3 Limits |      | 281  | 6A-4 LI | mits | Units | Test         |

|---------------------|------------------------------------------------------------------------|------|---------|------|------|---------|------|------|----------------|------|------|---------|------|-------|--------------|

|                     | Parameter                                                              | Min. | Typ.[1] | Mex. | Min. | Typ.[1] | Max. | Min. | Typ.[1]        | Max. | Min. | Typ.[1] | Max. | OTHER | Conditions   |

| <sup>t</sup> ACC    | Address to Output<br>Delay                                             |      | 150     | 200  |      | 200     | 250  |      | 300            | 350  |      | 400     | 450  | ns    | ČE = ČE = VI |

| tCE                 | CE to Output Delay                                                     |      | 150     | 200  |      | 200     | 250  |      | 300            | 350  |      | 400     | 450  | ns    | OE = VIL     |

| <sup>1</sup> OE     | OE to Output Delay                                                     | 10   | •       | 75   | 10   | I       | 100  | 10   |                | 120  | 10   |         | 150  | ns    | ČĒ = VIL     |

| t <sub>DF</sub> [2] | OE High to Output<br>Float                                             | 0    |         | 80   | 0    |         | 80   | 0    |                | 100  | 0    |         | 130  | ns    | ČĒ = VIL     |

| tон                 | Output Hold from<br>Addresses, ČE or ÕE<br>Whichever Occurred<br>First |      |         |      |      |         |      |      |                |      | 0    |         |      | na    | CE = OE = V  |

### WRITE

| Symbol              |                                        |      | Limit   | • -  |       |                       |

|---------------------|----------------------------------------|------|---------|------|-------|-----------------------|

|                     | Parameter                              | Min. | Тур.[1] | Max. | Units | Test Conditions       |

| tas                 | Address to Write Set-Up Time           | 150  |         |      | ns    | -                     |

| tcs                 | CE to Write Set-Up Time                | 150  |         |      | ns    | *                     |

| tDS[3]              | Data to Write Set-Up Time              | 0    |         |      | ns    |                       |

| tDH[3]              | Data Hold Time                         | 100  |         |      | ns    |                       |

| twp <sup>[4]</sup>  | Write Pulse Width for 2816A            | 9    |         | 15   | ms    | · ·                   |

| twn                 | Write Recovery Time                    | 100  |         |      | ns    |                       |

| tos                 | Chip Erase Set-Up Time                 | 0    |         |      | ns    | V <sub>OE</sub> = 10V |

| tон                 | Chip Erase Hold Time                   | 0    |         |      | ns    | V <sub>OE</sub> = 10V |

| tBOS                | Byte Erase/Write Set-Up Time           | 0    |         |      | ns    |                       |

| tвон                | Byte Erase/Write Hold Time             | 0    |         |      | ns    |                       |

| twwR <sup>[5]</sup> | Cycle Delay Time Following Write Cycle | 40   |         |      | μs    |                       |

<sup>1.</sup> This parameter is only sampled and not 100% tested.

2. top is measured from the point when CE or OE returns high (whichever occurs first) to the time when the outputs are no longer driven. This parameter is not 100% tested.

3. The data is set up and hold times for chip erase are identical to those specified for byte erase.

4. Adherence to type specification is important to device reliability.

5. Adherence to tywen is important for device reliability.

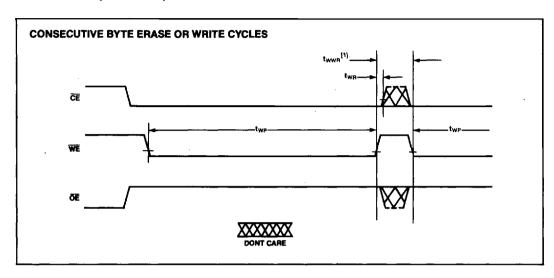

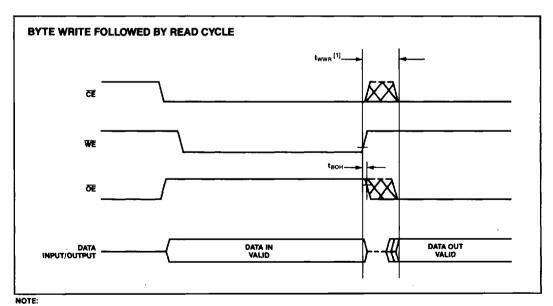

### **WAVEFORMS**

#### NOTES:

- 1. OE may be delayed up to 150 ns after falling edge of OE without impact on to the form the point when CE or OE returns high (whichever occurs first) to the time when the outputs are no longer driven. This parameter is not 100% tested.

3. Prior to a data write, an erase operation must be performed. For a byte erase, data in = V<sub>IH</sub>.

# **WAVEFORMS (Continued)**

1. In the chip erase mode D<sub>IN</sub> = V<sub>IH</sub>.

2. Timing reference for OE during Chip Erase is 90% of V<sub>OE</sub>.

# **WAVEFORMS (Continued)**

1. Adherence to twwR is important for device reliability.

## VPP OPTION SPECIFICATIONS[1]

#### **ABSOLUTE MAXIMUM RATINGS**

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. CHARACTERISTICS

|        |                                |      | Limits  | )    |       |                                                    |

|--------|--------------------------------|------|---------|------|-------|----------------------------------------------------|

| Symbol | Parameter                      | Min. | Тур.[2] | Max. | Units | Test Conditions                                    |

| IPP(R) | Vpp Current (Read)             |      |         | 10   | μa    | ČE = V <sub>IL</sub> , V <sub>PP</sub> = 4<br>to 6 |

| Vpp    | Read Voltage                   | 4    |         | 6    | V     |                                                    |

| IPP(W) | Vpp Current (Byte Erase/Write) |      |         | 10   | μа    | ČE = VIL                                           |

| VPP    | Write/Erase Voltage            | 20   | 21      | 22   | V     |                                                    |

| IPP(C) | Vpp Current (Chip Erase)       |      |         | 10   | μа    |                                                    |

# CAPACITANCE<sup>[2]</sup> T<sub>A</sub> = 25°C, f = 1 MHz

| Symbol | Parameter                   | Тур. | Max. | Units | Test Conditions |

|--------|-----------------------------|------|------|-------|-----------------|

| Сурр   | V <sub>PP</sub> Capacitance |      | 50   | pf    | OE = CE = VIH   |

#### A.C. CHARACTERISTICS

|        | Parameter                 |      | Limit               | s    |       | Test Conditions |

|--------|---------------------------|------|---------------------|------|-------|-----------------|

| Symbol |                           | Min. | Typ. <sup>[2]</sup> | Max. | Units |                 |

| tPRC   | Vpp RC Time Constant      |      |                     | 750  | μs    |                 |

| tPFT   | V <sub>PP</sub> Fall Time |      |                     | 100  | μς    |                 |

#### NOTES:

2. This parameter is only sampled and not 100% tested.

Only specifications unique to V<sub>PP</sub> option operation are shown. All other specifications under 5 volt only operation apply to V<sub>PP</sub> option operation as well, except where noted.

### NOTES:

- 1. Only specifications unique to V<sub>PP</sub> option operation are shown. All other specifications under 5 volt only operation apply to V<sub>PP</sub> option operation as well, except where noted

- as well, except where noted.

2. Prior to a data write, an erase operation must be performed. For a byte erase, data in = V<sub>|H</sub>.