## memory design handbook

#### INTRODUCTION

The Intel Memory Design Handbook contains information on the use of Intel's memory components and support circuits in system application. It is intended to aid the system designer to gain a thorough understanding of the operation and characteristics of Intel memory components in a system environment.

The Handbook contains six major sections:

- 1. An overview, which discusses the evolution of various members of the semiconductor memory family.

- Random Access Memories, which discusses the Intel 16K, 4K family of dynamic RAMs, and both high speed and low power Static 1K RAMs.

- 3. Read Only Memories, which discusses the Intel bipolar and MOS families of fusible link and Erasable Programmable Read Only Memories, including the newest 5V 16K device, the Intel® 2716.

- 4. Serial Memories, which discusses the operation of Charge Coupled Devices (CCD's) and the information necessary to design several systems with them.

- Support Circuits, which discusses the use of the various refresh controllers and drivers that are available as companion devices to the Intel storage devices.

- 6. Appendix, which contains reprints of several previously published articles that are pertinent to the devices discussed elsewhere in the handbook.

The Intel Data Catalog is intended to be a companion to the handbook, as it contains detailed specifications of all of Intel's storage devices. You may request a copy of the Data Catalog from the nearest Intel Sales Office or distributor listed on the inside back cover.

Bob Greene Application Engineering

#### ON THE COVER:

The cover represents the entire process of designing a semiconductor memory.

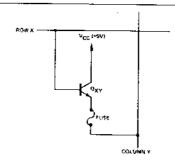

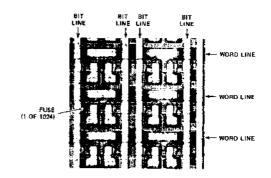

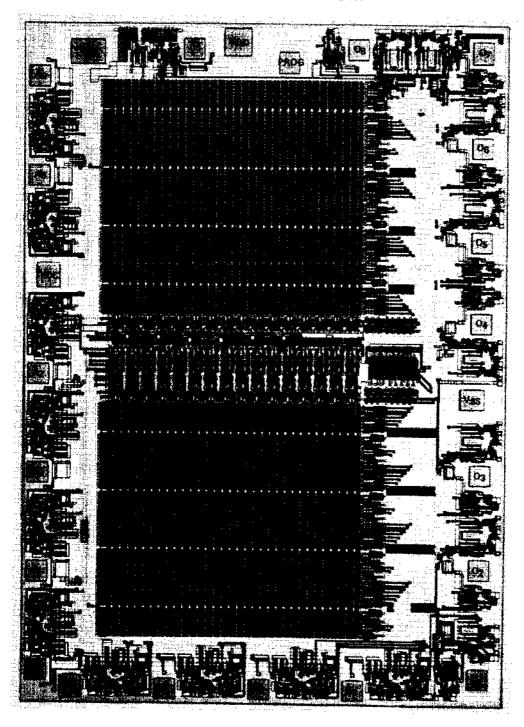

1. During the process of manufacture, each semiconductor memory is "laid out" in a manner similar to that used in printed circuit boards, with a different mask used for each step to control etching, metal deposition, etc. This rendering illustrates a reduced segment of a mask used in manufacturing an Intel dynamic RAM.

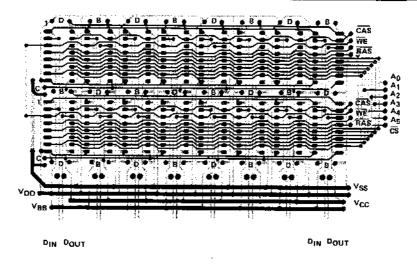

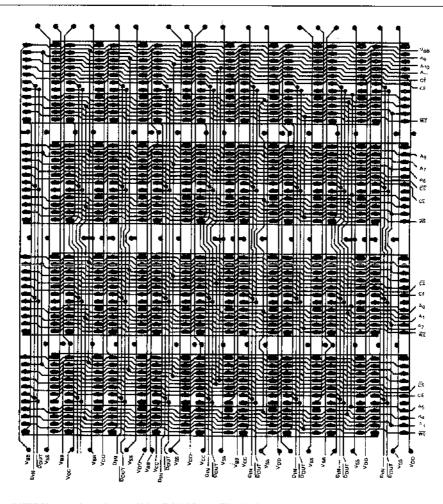

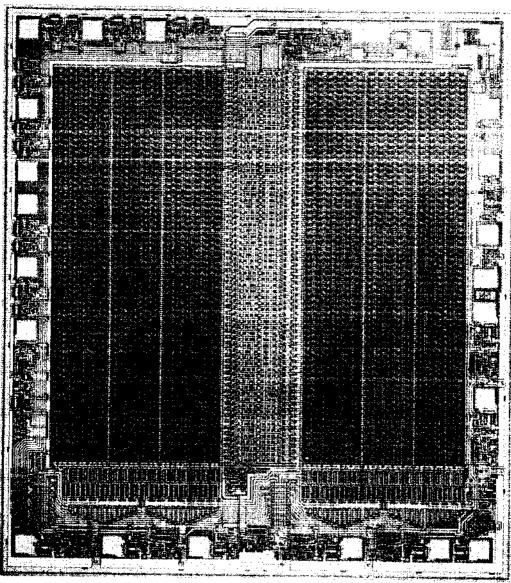

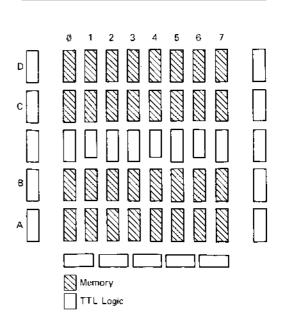

- 2. In order to interconnect the storage and control devices to make an operational memory system, a printed circuit board must be designed. This photo represents the composite (component side and solder side) layout used by designers to check the electrical integrity of the circuit connections. Detailed memory storage card layouts are presented in several sections of this handbook.

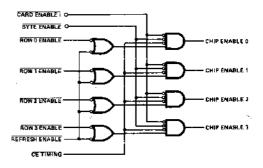

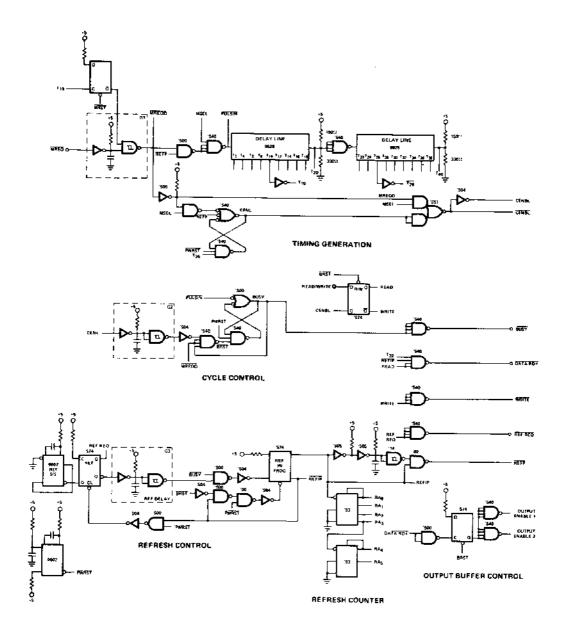

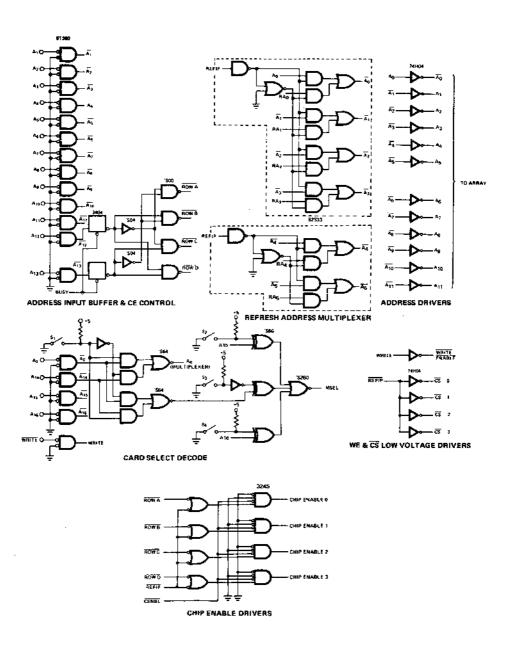

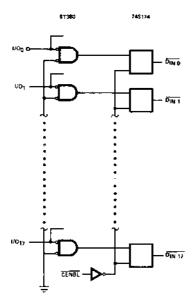

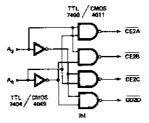

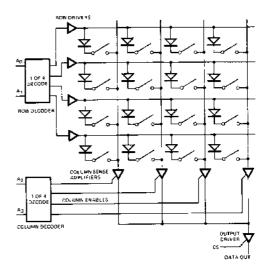

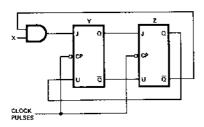

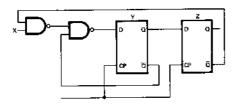

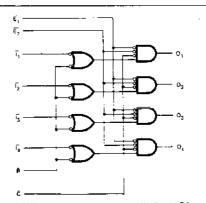

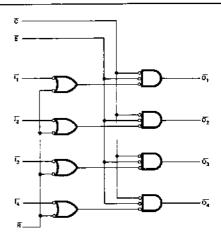

- 3. No system is complete without a logic diagram of the control portion. The correct implementation of control logic is absolutely necessary to proper operation of any storage system. NOR gates, NAND gates, as well as other TTL logic elements are the building blocks used in designing the control and interface portions of a storage system.

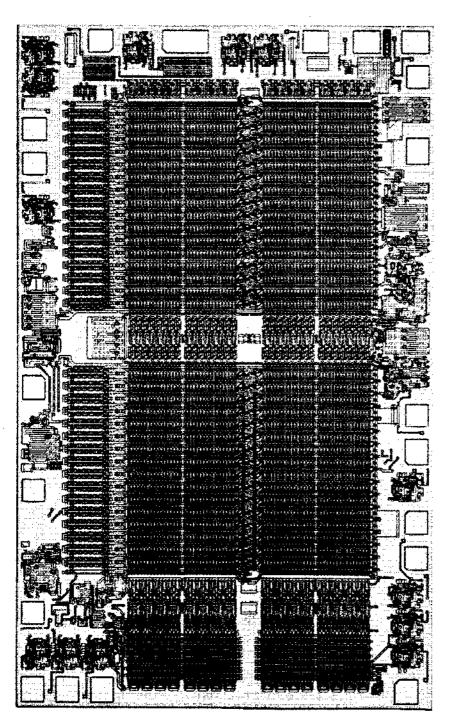

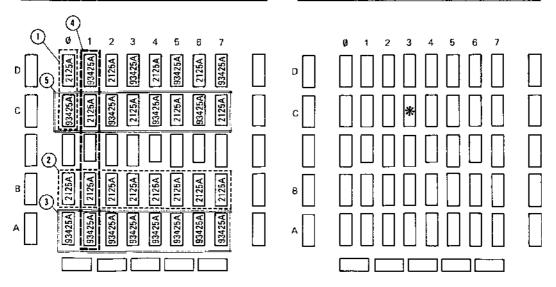

- 4. The finished storage card will resemble this photo of the Intel in-1611 Basic Storage Module, designed and manufactured by the Memory Systems Division of Intel. The in-1611 uses the Intel® 2116 as the basic storage element. The card is available in either 64Kx18 bit or 128Kx9 bit configurations, and can be used in systems requiring up to 384Kx72 bit storage systems utilizing the Intel in-Unichassis.

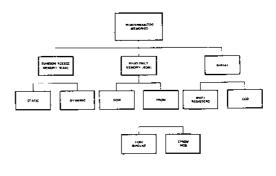

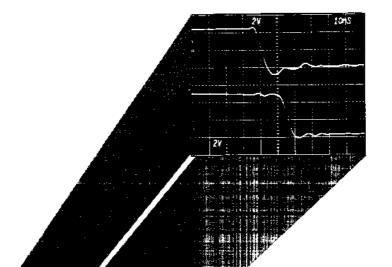

- 5. The proof of any storage system is in its performance. Using a high speed oscilloscope, this photograph was taken of an access cycle on an Intel® 2115, a high speed 1K static RAM. The address is shown as the top trace, and the bottom trace is the Data Out signal. This particular device shows an access time of approximately 15 nanoseconds at room temperature.

### intطأ

#### memory design handbook

Intel Corporation 3065 Bowers Ave., Santa Clara, CA 95051 Tel: 408/246-7501, TWX: 910-338-0026, Telex: 34-6372

| CO | ntents Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | OVERVIEW 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2. | RANDOM ACCESS MEMORIES (RAM)         2116 16K Dynamic RAM       2-i         2104A 4K Dynamic RAM       3-i         2107B 4K Dynamic RAM       4-i         5101 1K CMOS Static RAM       5-i         Static 1K MOS RAMs       6-i         Product Selection Guide       PSG-1                                                                                                                                                                                                                                                         |

| 3. | READ ONLY MEMORIES (ROMs)         Designing with INTEL® PROMs and ROMs       .7-i         3601/3621 & 3301A Bipolar 1K PROMs & ROMs       .7-6         3602/3622 & 3302/3322 Bipolar 2K PROMs & ROMs       .7-7         3604/3624 & 3304A/3324A Bipolar 4K PROMs & ROMs       .7-8         1602A/1702A & 1302 MOS 2K PROMs & ROMs       .7-12         Application of the INTEL® 2708 8K Erasable PROM       .8-i         Application of the INTEL® 2716 5V 16K Erasable PROM       .9-i         Product Selection Guide       .PSG-2 |

| 4. | SERIAL MEMORIES           2416 16K CCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

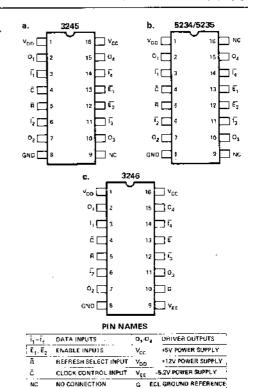

| 5, | SUPPORT CIRCUITS         Introduction       .11-1         Refresh Support Circuits       .11-1         3222 System Operation       .11-5         3232/3234 Operation       .11-8         Driver Circuits For Memory Arrays       .11-10         Other MOS Level Drivers       .11-15         3246 Operation       .11-15         5234 and 5235 Operation       .11-17         Systems Considerations       .11-20         Product Selection Guide       .PSG-4                                                                       |

| 6. | APPENDIX  2115A/93415A Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7. | MISCELLANEOUS INTEL® Military Product Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

OVERVIEW

RANDOM ACCESS MEMORIES

3. READ ONLY MEMORIES

4. SERIAL MEMORIES

> 5. SUPPORT CIRCUITS

6. APPENDIX

# VERVIEW

### Overview

| Overview | <br> | 1-1 |

|----------|------|-----|

|          |      |     |

#### OVERVIEW

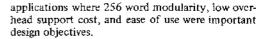

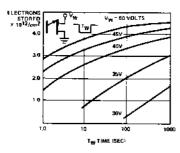

Developments in the semiconductor industry during the last six years have resulted in a major shift in the type of storage technology used in digital systems. Semiconductor memories used today are lower in cost, higher in density, faster in access and cycle time, higher in reliability and more modular in incremental size than the comparable core memory modules that are available. The advantages of semiconductor memories have been so widely accepted that semiconductor memory shipments will exceed core memory shipments in 1975. The curves shown in Figure 1 show this change in the memory market place and the increasing importance of semiconductor memory.

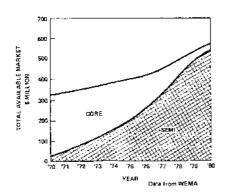

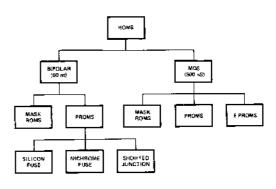

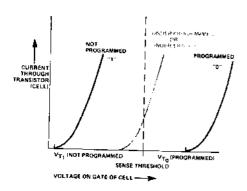

#### SEMICONDUCTOR MEMORIES

Semiconductor memories are divided into three broad categories as shown in Figure 2. With two exceptions, each of these three generic categories can be implemented with either of the two major semiconductor technologies: MOS or bipolar. These exceptions are the CCDs (Charge Coupled Devices) and EPROMs (Erasable Programmable Read-Only Memories) which are uniquely implemented with MOS technology.

#### Random Access Memories

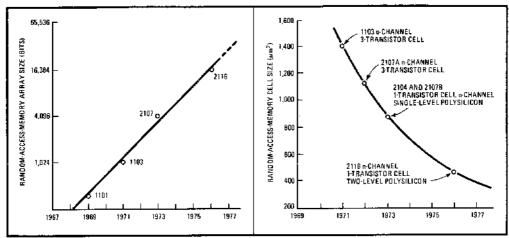

No other area of semiconductor memory has grown as rapidly and as large as that of random access memories. Leading the way in the explosive growth of RAMs are the MOS devices. One of the reasons for the wide acceptance of such devices has been the increasing bit density of MOS devices. The density has been quadrupling on the average of every two years as shown by the graph in Figure 3.

in 1969, Intel introduced the 1101, a 256 x1 bit static MOS random access memory (RAM). This device was designed primarily for small buffer storage

In 1971, Intel introduced the 1103, a 1K x 1 bit dynamic MOS RAM. The 1103 offered a 4:1 density improvement along with a 4:1 speed improvement over the 1101. The 1103 was the first semiconductor memory element to be speed and cost competitive with core memory systems, which explains the fact that the 1103 is the largest volume semiconductor memory device ever produced.

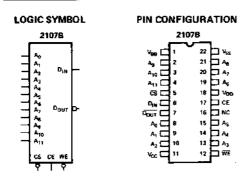

In 1973, Intel introduced the first 4K dynamic NMOS memory, the 2107. This product was subsequently improved and is known as the 2107B, which has become the industry standard for 4K RAMs in 22 pin packages. In addition, Intel now offers the 2104A, which has reduced the package size for a 4K RAM to a standard 16 pin package. The 2104A, in integrating many of the support circuits internal to the device, has produced an improvement in ease of use. P-channel 1K RAMs, with their MOS level inputs, required high voltage TTL-MOS drivers on all input pins. Their low level signal output required the use of external sense amplifiers. These overhead devices have been integrated onto the 4K 2104A chip such that all input and outputs are fully TTL compatible. The trend has been and continues to be toward denser, faster, and easier to use semiconductor memory devices.

In 1977 Intel introduced the 2116, a 16-pin 16K dynamic RAM with latched outputs, thus continuing the evolution shown in Figure 3. This RAM is also TTL compatible on all inputs and outputs, and can be plugged directly into 2104A sockets, providing a 4:1 increase in density.

While dramatic improvements have been made in MOS dynamic memories (such as the 1103 and

Figure 1. Total Available Memory Market.

Figure 2. Semiconductor Memory Family Tree.

Figure 3. Dynamic RAM Evolution.

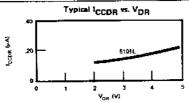

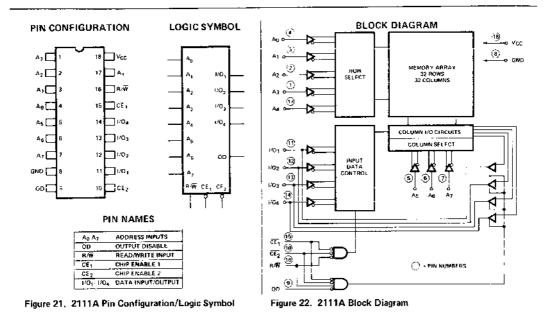

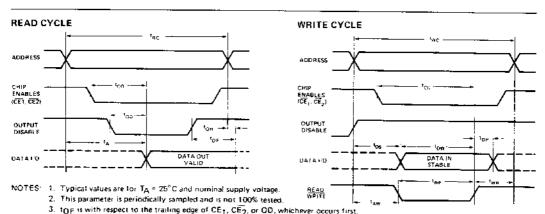

2107A, 2107B, 2104A), equal improvements have been made in high density static, TTL compatible memories. This family of devices, such as the 2102A, 2101A, 2111A, 2112A, 2114, 2115A, 2147, and the CMOS 5101 has greatly increased the ease of use of memories in systems which do not require a large amount of memory. These static RAMs (like the dynamic RAMs) are continuing to expand to include faster devices.

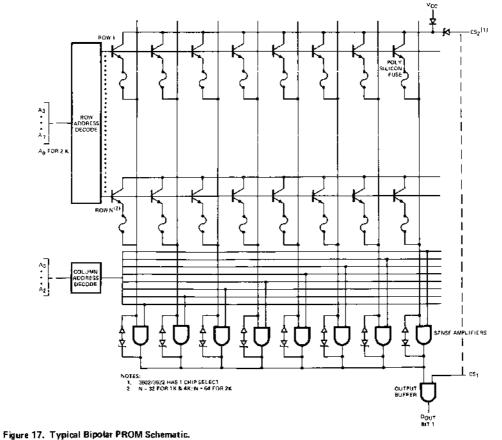

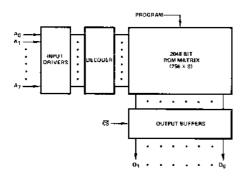

#### Read Only Memories

The Read Only Memory, like the random access memory, has gone through evolutionary changes in a short period of time. Innovations in bipolar and MOS technology have resulted in programmable and eraseable programmable ROMs, called PROMs and EPROMs respectively. These two types of devices have greatly increased the usefulness and acceptability of Read Only Memories in system applications.

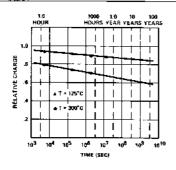

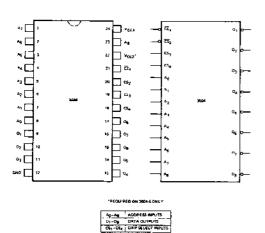

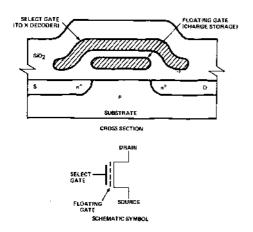

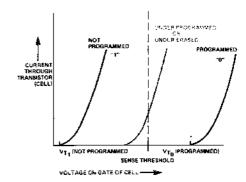

One of the most unique devices in the ROM family is the eraseable PROM (EPROM) such as the Intel® 1702A, 2708, and 2716. These devices, which have bit densities of 2K, 8K, and 16K respectively, offer the system designer maximum flexibility in changing program instructions etc. in the development of their systems.

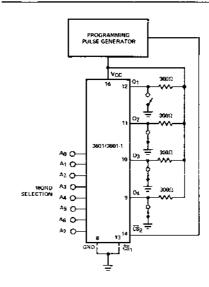

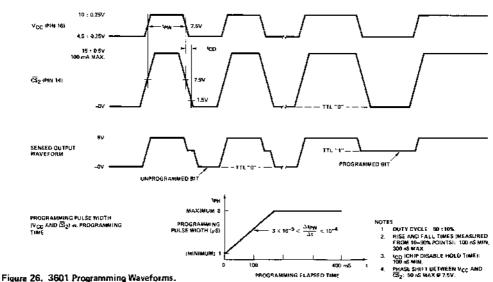

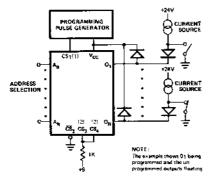

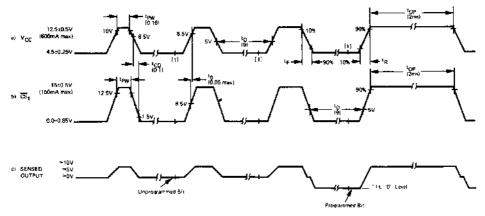

Other user programmable device types (not erasable) are the Intel® 3601, 3602 and 3604 family of bipolar PROMs. These devices offer the system designer very fast access times along with the ability to change programs "in-house" by merely replacing an old PROM with a newly programmed PROM.

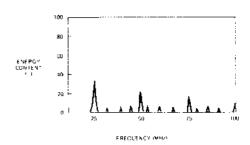

Since their introduction in 1971, MOS EPROMs have undergone evolution similar to dynamic RAMs, only at a somewhat slower rate. Figure 4 indicates that their density doubles approximately every two years.

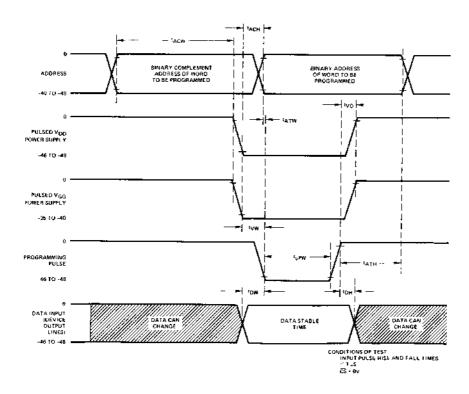

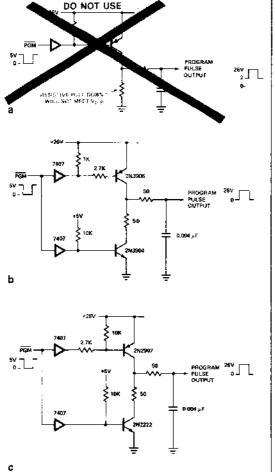

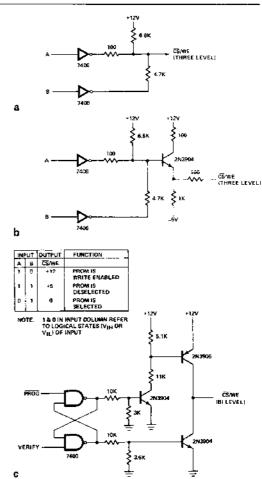

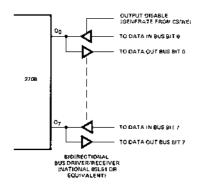

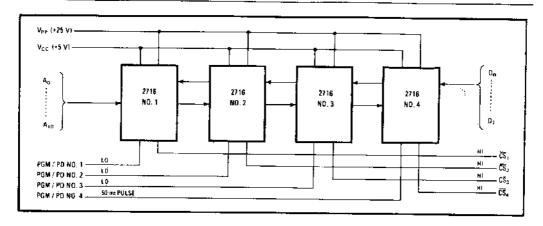

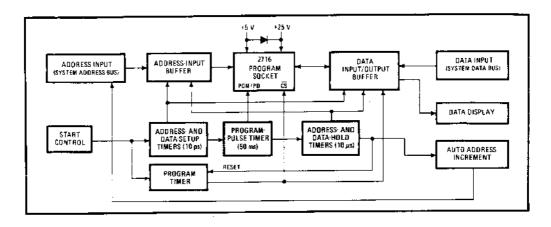

To maintain compatibility with the new generation of microprocessors which have a 5V technology, in 1977 Intel introduced the 2716, a 2K by 8 bit UV eraseable PROM, which requires only a single power supply for normal operation. In addition, pro-

Figure 4. MOS EPROM Evolution

gramming was simplified and now resembles a bipolar PROM type of programming; after raising programming supply to +26 volts, addresses can be programmed in random order; with all signals being TTL compatible, including the address data and program pulse-inputs. Erasure requirements remain the same as the 2708-15w sec/cm<sup>2</sup>.

In addition to the 2716, true mask ROM replacement is now available in the form of the Intel 2316E. When the programmable Chip Select inputs are selected in accordance with the suggested pinout in the Intel 1977 Data Catalog, the 2316E can plug directly into the 2716 socket, with no need to relayout the board. In addition, a system designed for use with the 2316E can be "customized" for OEM special systems by programming them with the custom data pattern and inserting them in the 2316E sockets, either at time of manufacture or in the field.

All of the Intel PROM family of devices has a counter-part in ROM (non alterable or mask programmable) form. These devices are generally used in systems which are in mass production.

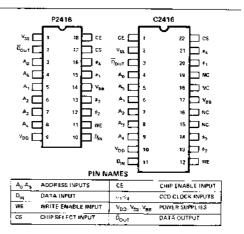

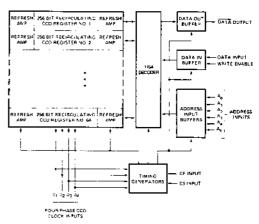

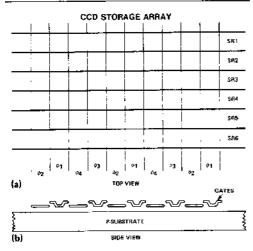

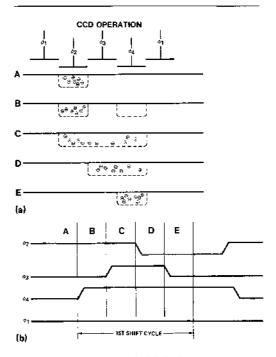

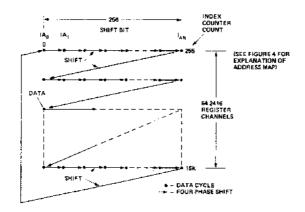

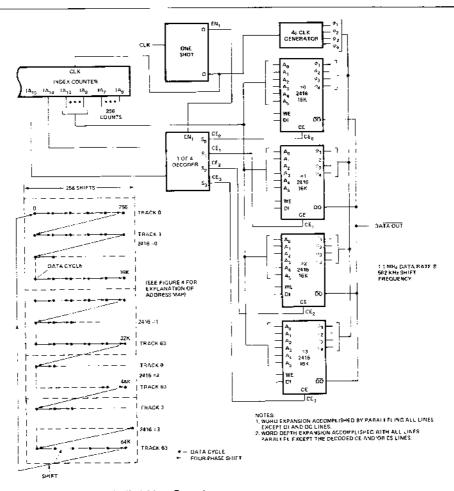

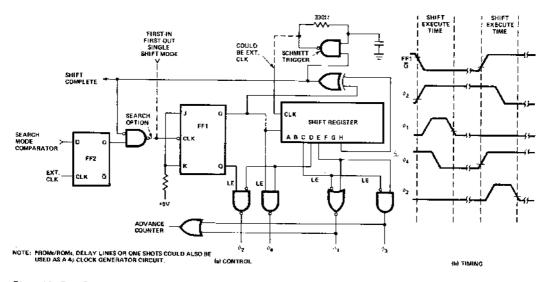

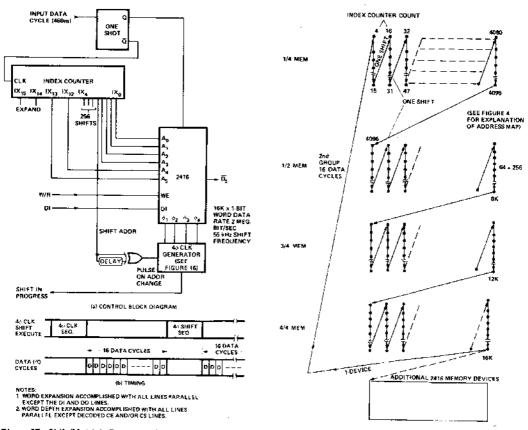

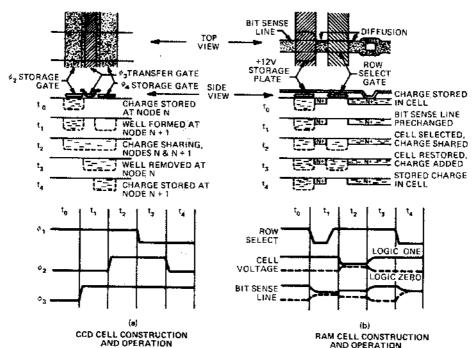

#### Serial Memories

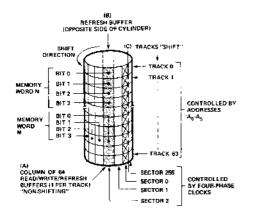

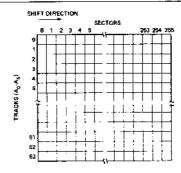

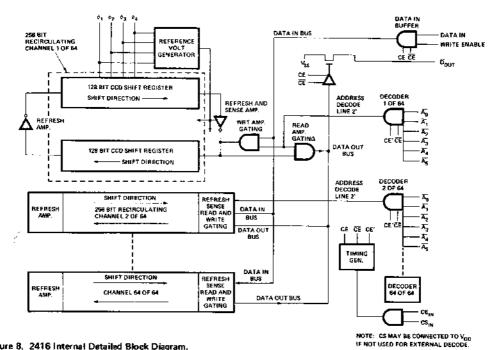

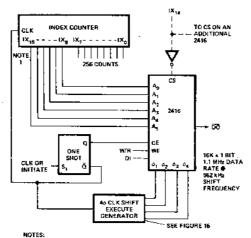

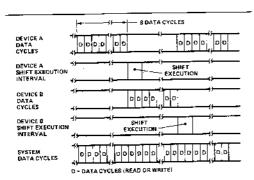

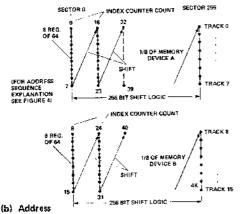

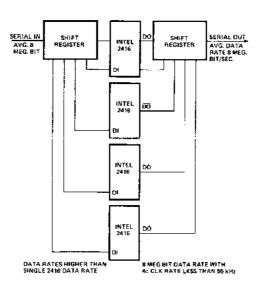

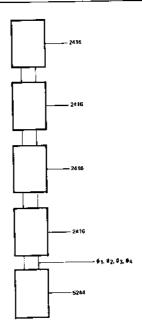

One of the most exciting new memory products to be recently introduced is the Intel<sup>®</sup> 2416, a 16K charge coupled device (CCD). The high density and low cost of this device makes it very attractive for use in "drum" replacement type systems as well as terminal and minicomputer applications.

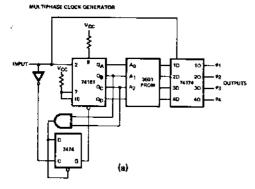

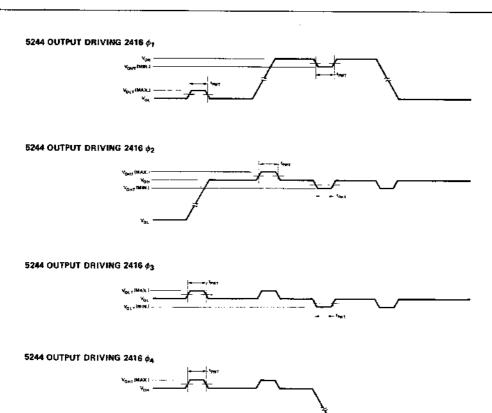

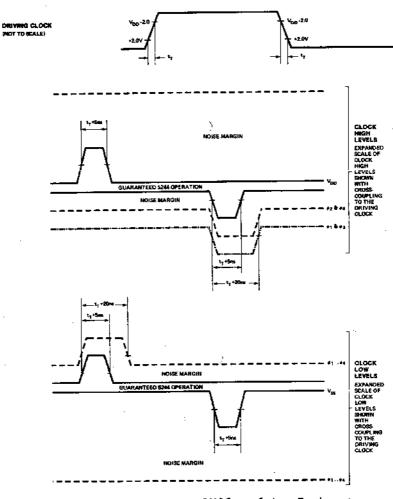

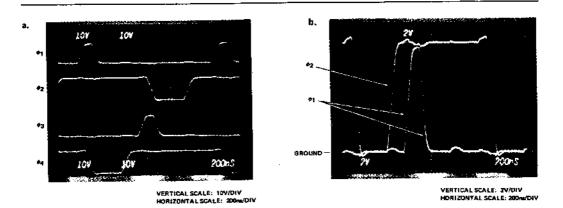

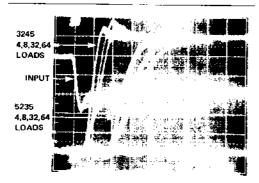

To facilitate the use of the 2416, Intel now offers the 5244, a clock driver that minimizes the problems of manipulating the 4 clock inputs by 1) providing TTL inputs and 2) providing output rise time control and 3) providing "cross coupling" control to minimize intercoupling between phases. One 5244 will drive 4 2416's or provide storage and transfer clock control for a total of 64K bits.

This handbook contains a detailed explanation of the use of the 2416 in a system environment. The significance of the unique organization of the 2416 is also fully explored so that the designer may take maximum advantage of its characteristics.

## **Random Access Memories**

| 2116 <i></i>            |  |  | , |   |   |  |     | , |  |  |  |  |    |     | 2. |

|-------------------------|--|--|---|---|---|--|-----|---|--|--|--|--|----|-----|----|

| 2104A                   |  |  |   |   |   |  |     |   |  |  |  |  |    |     | 3. |

| 21078 4K Dynamic RAM    |  |  |   |   | , |  |     |   |  |  |  |  |    |     | 4. |

| 5101 1K CMOS Static RAM |  |  |   | , |   |  | . , |   |  |  |  |  |    |     | 5. |

| Static 1K MOS RAMs      |  |  |   |   |   |  |     |   |  |  |  |  |    | . 1 | 6. |

| Product Selection Guida |  |  |   |   |   |  |     |   |  |  |  |  | P: | 30  | ٠. |

#### Contents

## Application of the Intel® 2116 16K RAM

Jim Coe Application Engineering

| INTRODUCTION2-1                         |

|-----------------------------------------|

| DEVICE INTERNAL OPERATION 2-1           |

| Data Sensing                            |

| Data Storage                            |

| Address Latches                         |

| Data Latches                            |

| Refresh Modes                           |

| APPLICATIONS INFORMATION 2-4            |

| Implementing Refresh                    |

| Address Multiplexing/Refresh Timing 2-5 |

| Power Distribution/Decoupling2-8        |

|                                         |

#### INTRODUCTION

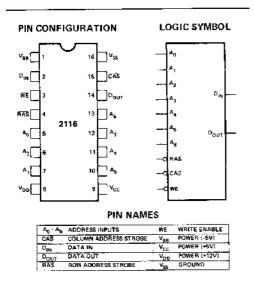

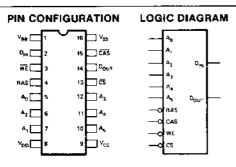

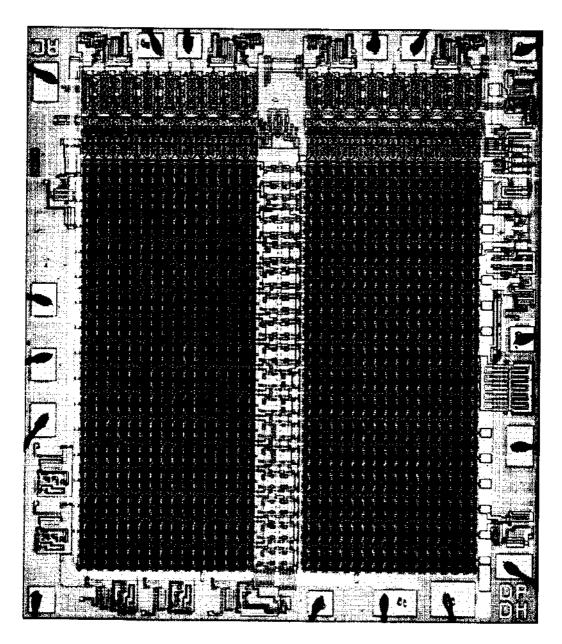

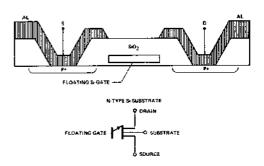

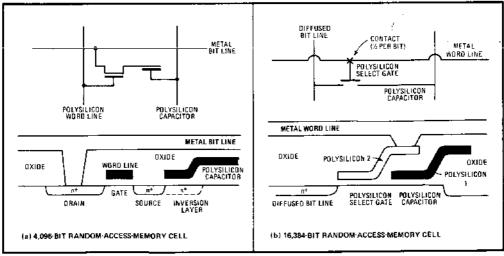

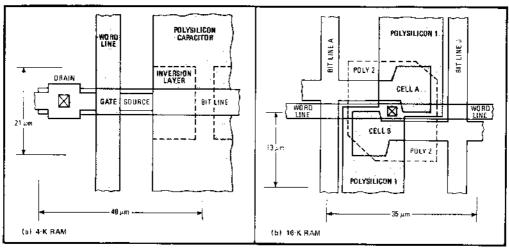

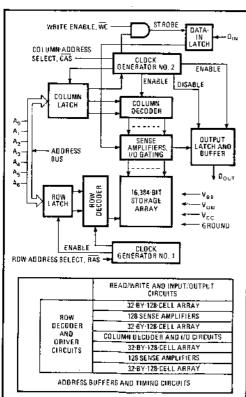

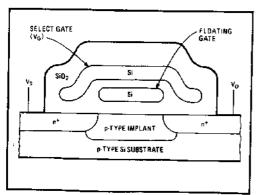

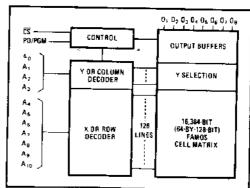

The Intel® 2116 is a 16,384 word by 1 bit dynamic random access memory. The 2116 is fabricated using Intel's proven two-layer polysilicon, n-channel silicon gate MOS technology. The device is packaged in a standard 16-pin DIP. The pin configuration and logic symbol are shown in Figure 1.

Figure 1, 2116 Pin Assignments

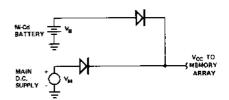

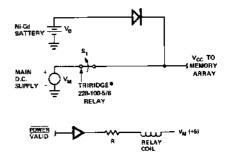

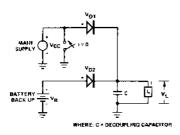

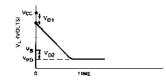

The 2116 operates with three power supplies relative to ground: VDD (+12V), VBB (-5V), and VCC (+5V). The VCC supply is connected only to the output buffer of the 2116 and may be turned off during power down (battery back-up) operation.

The 2116 is designed to be compatible with the industry standard 16-pin 4K RAM, the Intel® 2104A. This compatibility allows a single system design for both the 4K and 16K devices providing for memory expansion without additional engineering.

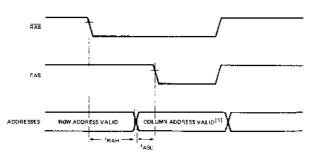

The use of the 16-pin package is made possible by multiplexing the 14 address bits (required to address 1 of 16,384 bits) into the 2116 on 7 address input pins. The two 7-bit address words are latched into the 2116 by the two TTL clocks, Row Address Strobe (RAS) and Column Address Strobe (CAS). Non-critical clock timing requirements allow use of the multiplexing technique while maintaining high performance.

Data is stored in the 2116 in single transistor, dynamic storage cells. The storage cells require refreshing for data retention. Refreshing is accomplished by performing a memory cycle at each of the 128 row addresses every 2 milliseconds.

The purpose of this Application Brief is to describe the basic internal operation of the 2116 and to outline the areas in design which allow a 2104A/2116 compatible memory system.

#### Device Internal Operation

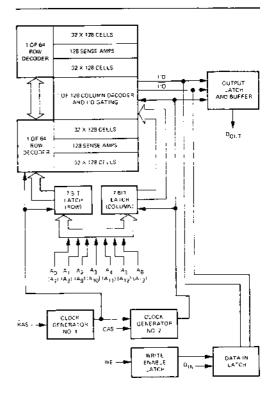

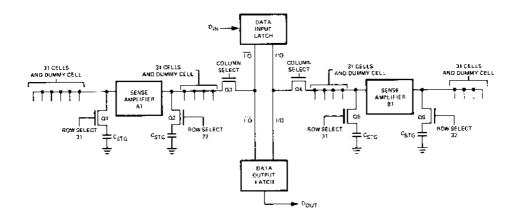

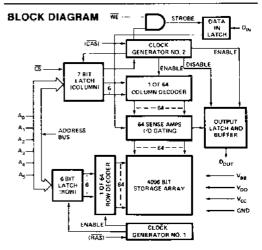

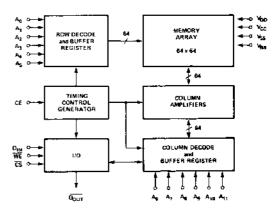

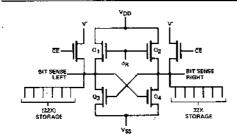

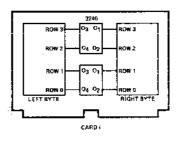

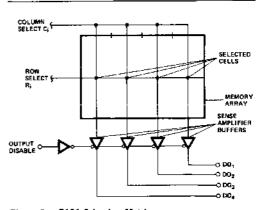

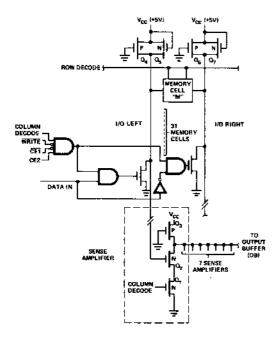

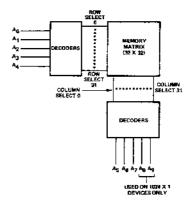

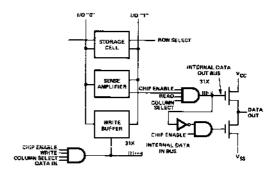

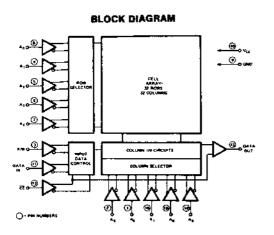

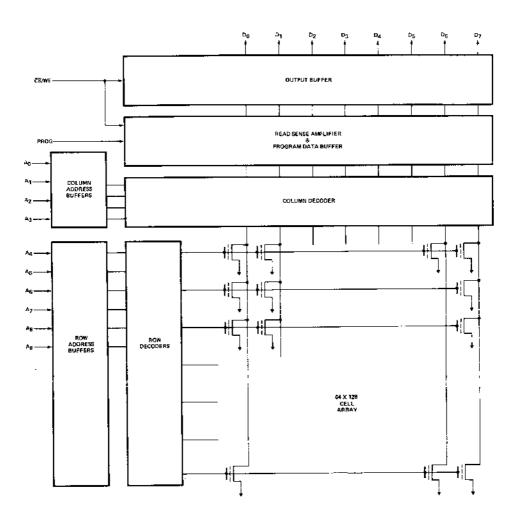

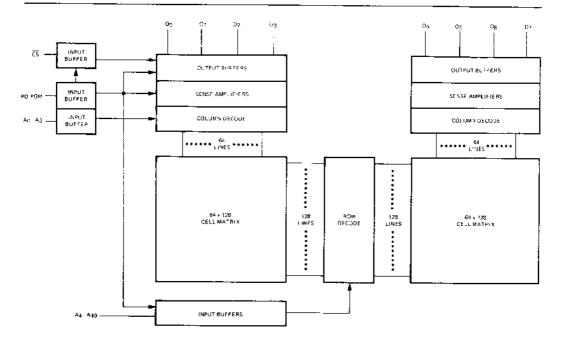

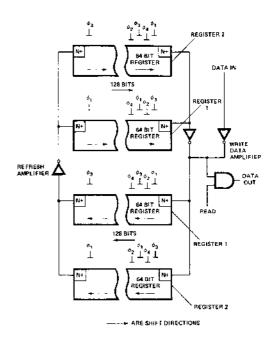

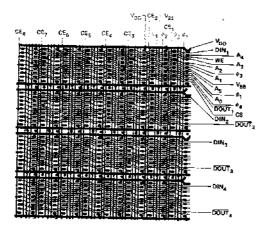

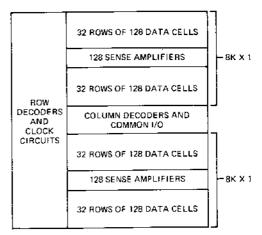

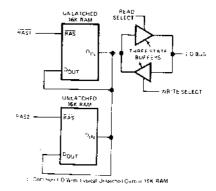

Operation of the 2116 is most easily understood with the aid of the block diagram shown in Figure 2. As is shown in this figure, the 2116 is arranged as two 8192-bit storage arrays sharing a common set of column address decoders and a common I/O bus. Each array is arranged in a 64 row by 128 column matrix of storage cells with 128 sense amplifiers per array. Row address bit  $A_6$  is decoded and selects one of the two arrays to be active during any given memory cycle. Thus, only one set of 128 sense amplifiers is active during a cycle maintaining low operating power.

Figure 2. 2116 Block Diagram

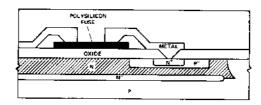

The storage cells are implemented with a single transistor and a "storage" capacitor and are called single transistor cells. A cell is accessed by the coincidence of a row select (defined by address bits A<sub>0</sub> - A<sub>6</sub>) and a column select (defined by address bits A<sub>7</sub> - A<sub>13</sub>). On chip timing and control

generators provide the internal timing signals for decoding, data sensing, read/write strobing and I/O data gating. The timing circuits in the 2116 are activated by the negative going edges of the two TTL clocks, RAS and CAS.

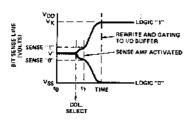

#### Data Sensing

Data is stored in the 2116 storage cells as one of two discrete voltage levels on the cell capacitor; a high is ~VDD (+12V) and a low is ~VSS (ground). These levels must be sensed by the data sense amplifiers and propagated to the Data Output (DOUT) in order to fulfill the function of a RAM device. Sensing of the stored levels is destructive and automatic restoration (rewriting) of the sensed data must also occur.

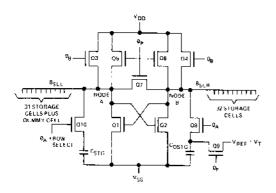

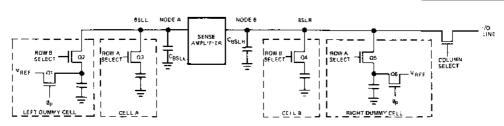

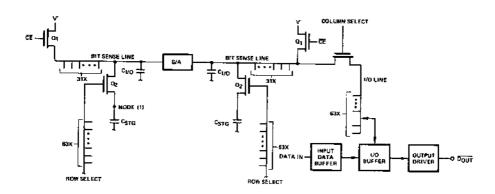

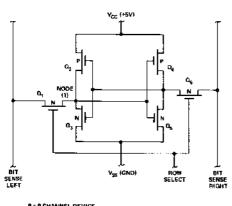

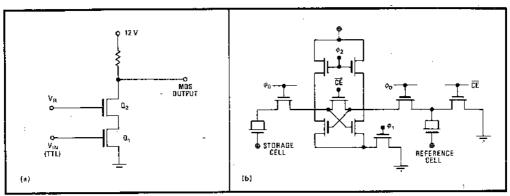

The 2116 data sensing scheme is known as the Dummy Cell Reference technique. The reference level that the sense amplifier compares the stored level to is a level stored in a special, non-accessable storage cell. The level stored in this reference or "dummy" cell is less than the minimum allowable stored high level and greater than the maximum allowable stored low. Examination of the simplified sense amplifier schematic of Figure 3 will clarify the sensing operation.

Figure 3. Simplified 2116 Data Sensing Schematic

During the RAS clock off time (high),  $\emptyset$ p turns on devices Q5 and Q6 connecting nodes A and B to VDD and precharging the nodes to  $VX(\sim VDD-VT)$  where VT is the MOS device threshold voltage). Device Q7 is also turned on by  $\emptyset$ p and connects nodes A and B together assuring that they reach the same precharge level.  $\emptyset$ p also turns on device Q9 precharging the dummy storage cell capacitor (CDSTG) to VREF.

When RAS goes active (low),  $\emptyset$ p turns off isolating nodes A and B and the dummy cell capacitor. When the row address bits have been decoded and the row select is valid,  $\emptyset$ A turns on Q8 and Q10, the dummy cell and storage cell transistors respectively.

This connects the cell capacitors to the bit sense lines (Bit Sense Line Left [BSLL] and Bit Sense Line Right [BSLR]). If the voltage stored in CSTG is greater than the voltage stored in CDSTG (VREF), node A will be higher than node B. This voltage inequality will cause the sense amplifier (a crosscoupled latch made up of devices Q1 and Q2) to switch when load devices Q3 and Q4 are turned on by \( \theta\_B \). The latch will switch node B to VSS and node A to ~VDD due to the regenerative action of the latch,  $\emptyset B$  is delayed from  $\emptyset A$  sufficiently to allow the voltages on nodes A and B to stabilize prior to enabling the sense amplifier. If the voltage stored in CSTG had been less than that stored in CDSTG, the latch would have sensed a low and switched such that node A would be at  $V_{SS}$  and node B would be at  $\sim V_{DD}$ .

After the stored level has been sensed against the reference level, the sense amplifier will have forced BSLL to a level corresponding to the level originally stored in the storage cell capacitor (VDD if VCSTG > VREF or VSS if VCSTG < VREF). Since the storage cell transistor (Q10) is still turned on, the storage cell capacitor will be charged to the BSLL level. This effectively restores the sensed data into the cell capacitor but at full levels, not leakage or noise degraded levels. This is also what occurs when a storage cell is refreshed, the data integrity is restored through the sensing function.

Note that the stored level only has to be greater than or less than VREF, not full VDD or VSS levels. This is important because leakage currents from the storage cell capacitor degrades a stored high level toward VREF while system ground noise degrades a stored low level toward VREF. Leakage degraded high levels are the most serious design problem and VREF is generally set closer to VSS than to VDD to counteract the leakage effects. Leakage of stored high levels is also the reason dynamic storage RAMs must be periodically refreshed.

#### Data Storage

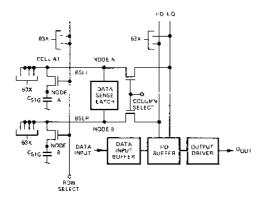

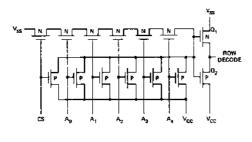

The block diagram in Figure 2 shows that the two 8192-bit arrays in the 2116 share a common I/O bus and common column decoders. The simplified schematic of Figure 4 shows one set of corresponding columns from the two arrays with their sense amplifiers and I/O gating. As shown, the I/O bus consists of two parallel, opposite polarity data lines which connect the column(s) to the Data In and Data Out latches. Referring to the previous discussion of the operation of the sense amplifiers and storage cells, a "stored level" or data map may be developed for the 2116.

Figure 4. I/O Line and Data Column Schematic

Column select device (Q3) connects sense amplifier A1 and its related storage cells to the  $\overline{I/O}$  line. Data stored in the cells on A1's BSLR will be inverted with respect to the data level at the Data Input (DIN). Data in the cells on BSLL will be the same polarity as DIN since the I/O bus data is inverted through the sense amplifier. Conversely, sense amplifier B1 and its related cells are connected to the I/O line by device Q4 and data on it's BSLL will be DIN while data on it's BSLR will be DIN. These data inversions are internal to the 2116 and are invisible to the user since DOUT will be the same polarity as DIN. The data map for the 2116 is therefore, as shown in Figure 5. This figure also indicates the address map for the 2116.

#### Address Latches

The 7-bit row and column address words are latched into internal latches by RAS and CAS respectively. These latches capture the TTL level address information on the shared address input pins and convert the TTL levels to the MOS levels (12V) required internally by the 2116.

#### Data Latches

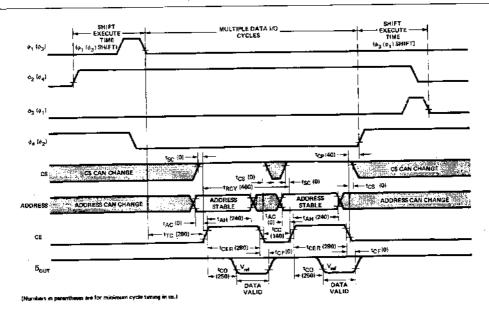

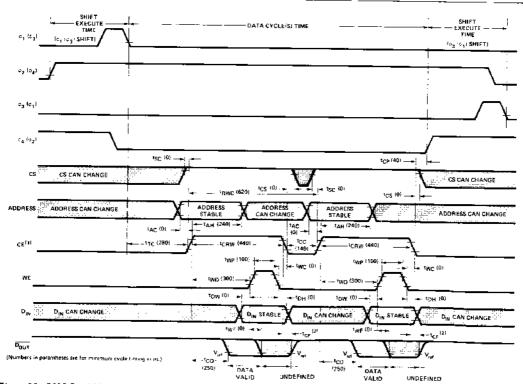

Both the Data Input (DIN) and Data Output (DOUT) information is latched by the 2116. The input data is latched by the logical AND function of RAS, CAS, and WE. When a data cycle is being performed (RAS low), DIN will be latched by the falling edge of the last of the two control signals (CAS or WE) to go low. In a "fast" write cycle,i.e., WE low before CAS goes low, the CAS edge will operate the latch. In a "late" write (CAS low before WE goes low) or read-modify-write cycle, DIN is latched by the falling edge of WE.

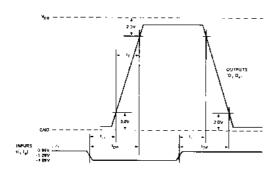

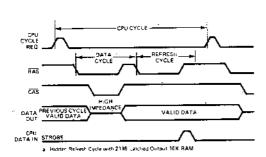

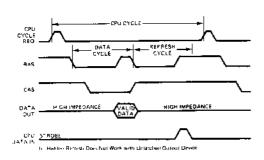

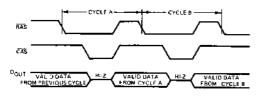

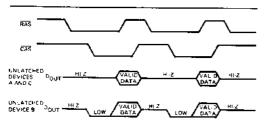

Figure 5, 2116 Address and Data Map

The Data Output (DOUT) latch and buffer is controlled by CAS. The leading (falling) edge of CAS in any cycle causes DOUT to assume an open-circuit (HI-Z) state. At access time (tRAC or tCAC), DOUT will assume a data state (high or low) dependent upon the type of data cyle performed or will remain in the HI-Z state if the cycle was a CAS-only deselect cycle. The DOUT state is latched and remains valid until the next cycle during which a CAS occurs. Table I summarizes the states the data output assumes for each type of 2116 cycle.

#### Refresh Modes

The data stored in the 2116 single transistor storage cells may be refreshed in any of three modes. The cells must be refreshed every 2msec.

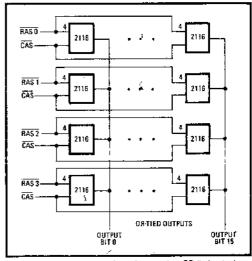

Read Cycle Refresh: A read cycle at each of the 128 row addresses (A<sub>0</sub> - A<sub>6</sub>) of the 2116 will refresh all the storage cells. This refresh mode is useful only when the memory system consists of a single row of devices (16K words X n-bits) and OR-tying of outputs is not necessary. Each device will access data during the refresh cycle and OR-tying of device outputs would result in conflict between devices for the output data bus. Write cycles also fulfill the refresh requirement but the selected cell (determined by the column address) on the row being refreshed will have new data written into it while the remaining 127 cells on the row are simply refreshed.

Table 1. Data Output Content

| Type of Cycle                                                      | Data Latch Content (DOUT)                                                         |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Read Cycle                                                         | Data from Addressed Memory<br>Cell                                                |

| Write Cyale                                                        | Input Data (DIN)                                                                  |

| RAS-Only Cycle                                                     | Data from previous Cycle or<br>HI-Z if Device was Deselected<br>in previous Cycle |

| CAS-Only Cycle                                                     | HI-Z (CAS-Only Deselects Device and Turns Output Buffer Off)                      |

| R-M-W Cycle                                                        | Data Read from Addressed<br>Memory Cell During Read<br>Portion of Cycle           |

| Page Mode Entry<br>Cycle                                           | Data from Addressed Memory<br>Cell                                                |

| Page Mode Read<br>Cycle                                            | Data from Addressed Memory<br>Cell                                                |

| Page Mode Write<br>Cycle (or Page<br>Mode Write and<br>Exit Cycle) | Input Data (DţŊ)                                                                  |

$\overline{RAS}$ -Only Refresh: A cycle with only the  $\overline{RAS}$  clock active, performed at each of the 128 row addresses will refresh the 2116 storage cells. This mode is useful when the memory system consists of multiple rows of devices. The data outputs of the RAMs may be OR-tied when  $\overline{RAS}$ -only refresh cyclcs are performed since the DOUT line of each 2116 will remain unchanged during the refresh cycle.

CAS-Before-RAS-Refresh: The 2116 storage cells may be refreshed with only 64 cycles each 2msec if the CAS-before-RAS mode is used. In this mode, initiated by CAS being valid (low) when RAS goes low, both 8KX1 halves (see Figure 2) of the 2116 are turned on and one row in both halves is refreshed during each cycle. Since there are 64 rows of cells in each half, only 64 cycles are required to refresh all the cells. This refresh mode is also useful in systems with multiple rows of devices since receipt of a CAS before the RAS turns off all device outputs, thereby preventing OR-tied data conflicts.

#### APPLICATIONS INFORMATION

The Intel® 2116 is functionally compatible with the industry standard Intel® 2104A 16-pin 4K RAM. It is pin compatible with the 2104A with the exception of the seventh address bit (A6) input pin. The 4K RAM uses that pin as the Chip Select (CS) input pin. The CS signal on the 4K RAMs was essentially treated as a seventh column address bit and, therefore, there is considerable similarity between the 16K and 4K 16-pin RAMs.

The following applications information will concentrate on designing compatible 4K/16K memory systems rather than on just using the 2116. Additional basic applications information on the use of 16-pin, multiplexed address RAMs is contained in the next section of this Handbook.

#### Implementing Refresh

The 2116 may be refreshed in any of three modes. Read cycles and RAS-only cycles refresh the row of storage cells (1 of 128 rows) addressed by A0 through A6 and, therefore, require 128 cycles each 2msec to refresh the stored data. The third 2116 refresh mode, CAS-before-RAS, refreshes two rows of storage cells during each cycle and, therefore, only requires 64 cycles each 2 msec to refresh the stored data.

The 2104A is compatible with all three 2116 refresh modes. A very simple compatible refresh system would perform 128 RAS-only refresh cycles each 2 msec on both the 2104A and 2116. The 2104A would of course be refreshed twice as often as necessary but this is not a problem. The advantage would be that no logic or timing change would be necessary to differentiate between the 4K and 16K RAMs for refreshing.

Read cycles could also be used with 128 cycles each 2 msec but the 2104A  $\overline{CS}$  input would need to be driven high (deselected) during each cycle to prevent data bus conflicts between OR-tied 2104A data outputs during refresh. This requires a logic control funtion of  $\overline{CS}$  during refresh (and read cycles also dissipate more power than  $\overline{RAS}$ -only cycles) so most systems will use  $\overline{RAS}$ -only refresh.

Each of the first two refresh modes require 128 refresh cycles each 2 msec. Assuming a system cycle time of 500 nsec, 3.2% of the available memory time is required for refreshing. In many systems, this loss of memory availability is of no consequence. In the high throughput memory system environments found in many large and mid-sized computer systems, however, any loss of memory availibility is undesireable.

For these systems, the 64 cycle refresh mode is advantageous since it requires only 1.6% of the available memory line, a 50% savings over 128 cycle refresh. It is also compatible with the 4K RAM systems presently in use since the the 4K RAMs require only 64 refresh cycles each 2 msec.

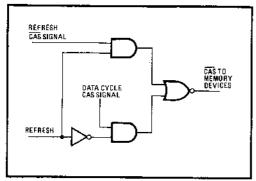

The 2116 automatically goes into its 64-cycle refresh mode when CAS is low (active) at the time RAS goes low (active). When this CAS-before-RAS condition is satisfied, the 2116 ignores address bit A6 and refreshes one row in each half of the device, thus refreshing all 128 rows of storage cells in only 64 cycles. Address bits A0 through A5 determine which rows are refreshed. The 2104A will also accept the CAS-before-RAS cycle and will simply perform a READ cycle on the row addressed by address bits A0 through A5, thereby refreshing the row of storage cells. The 2104A CS input should be driven high (unselected) during this refresh mode to prevent conflicts between OR-tied data outputs just as with normal read cycle refreshing.

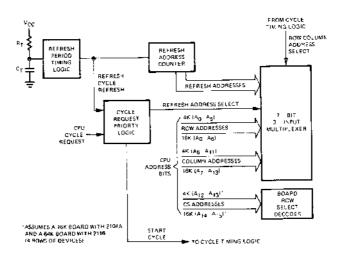

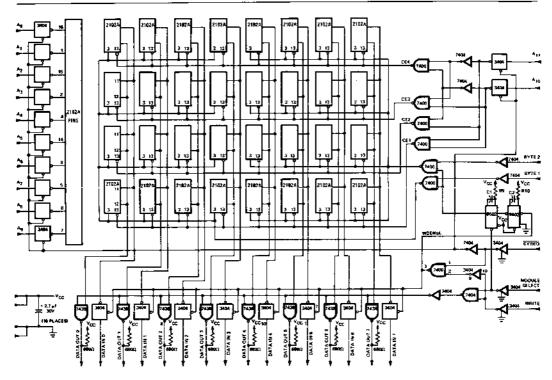

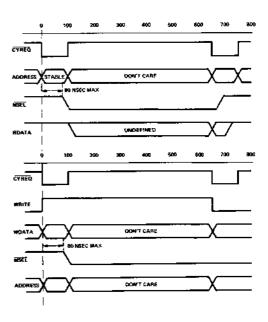

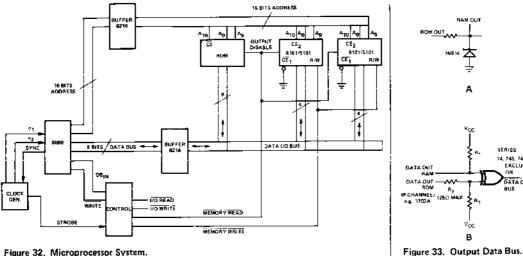

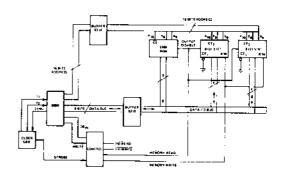

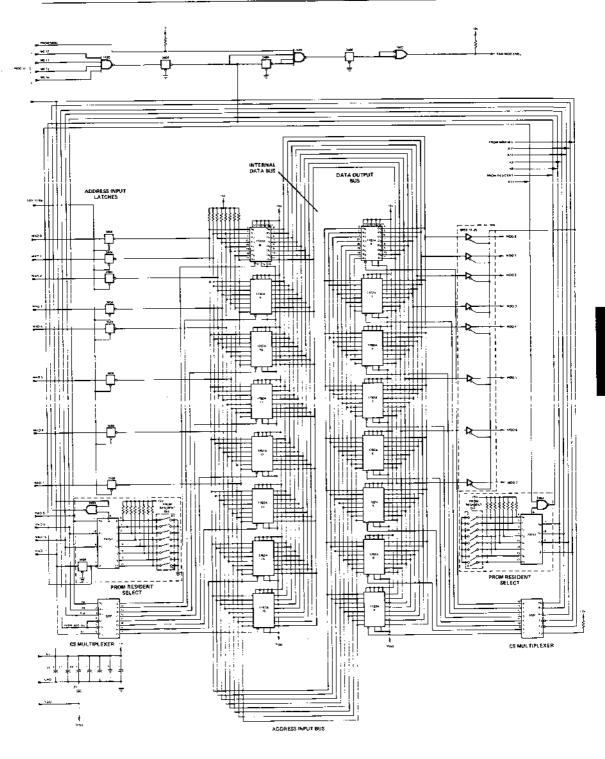

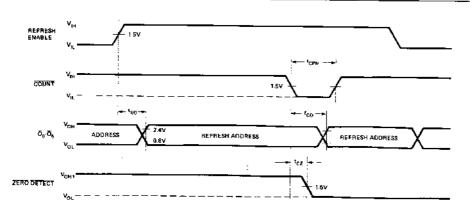

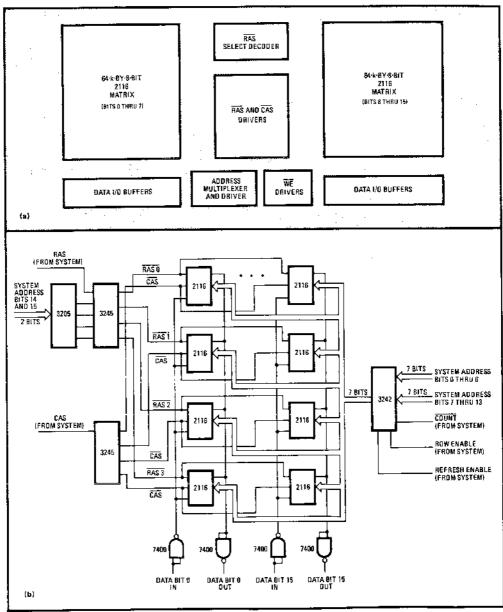

#### Address Multiplexing/Refresh Timing

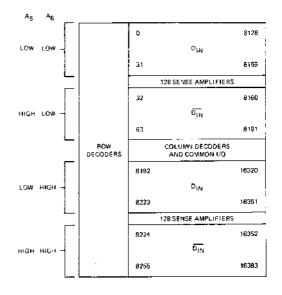

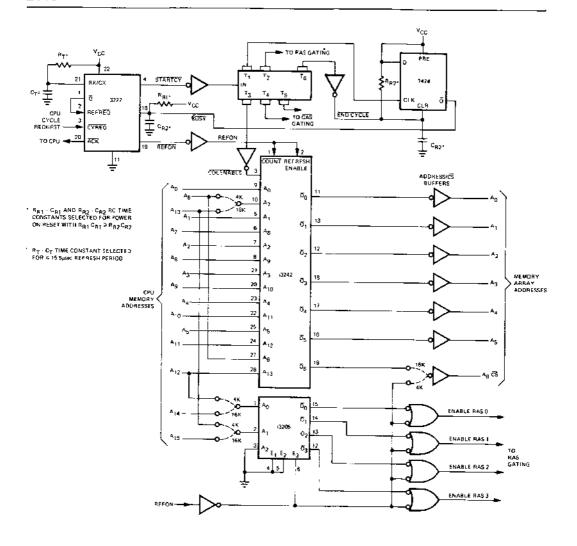

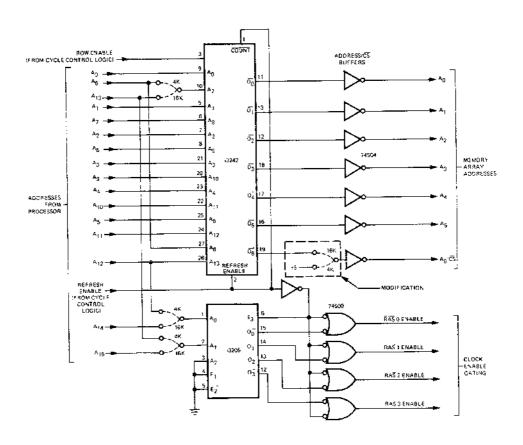

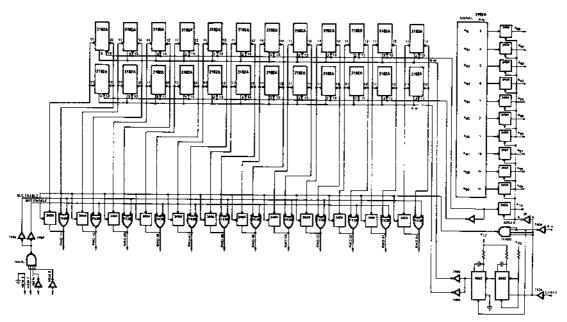

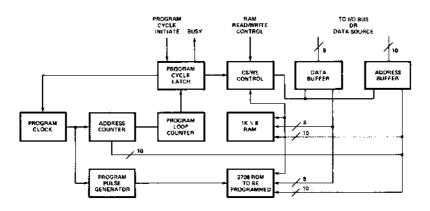

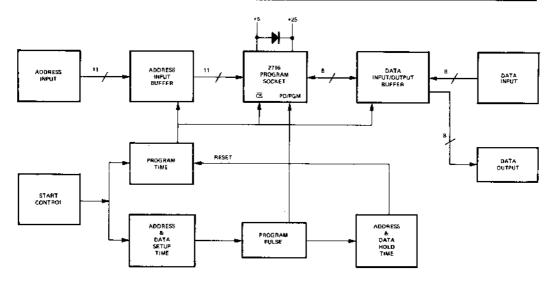

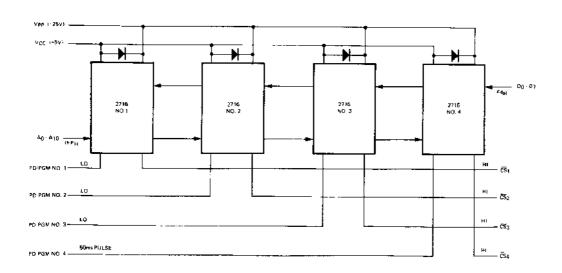

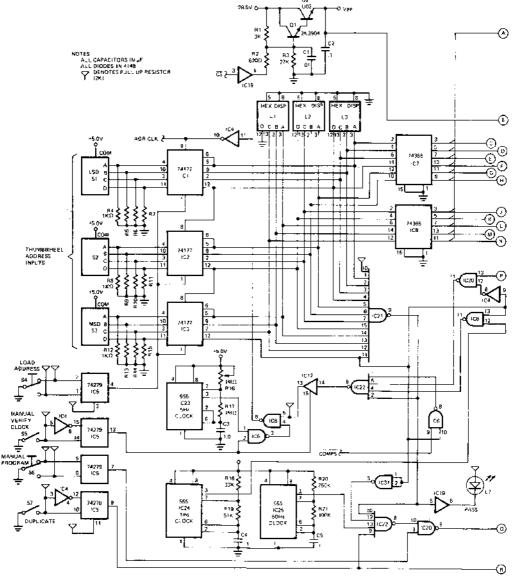

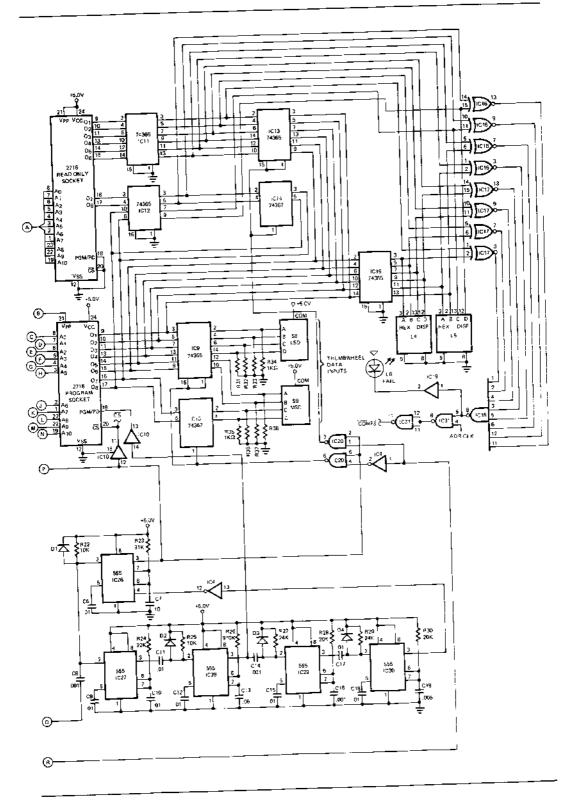

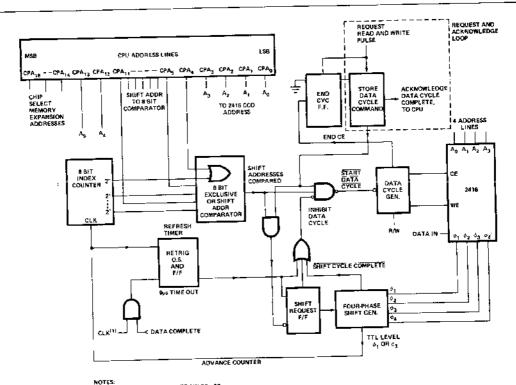

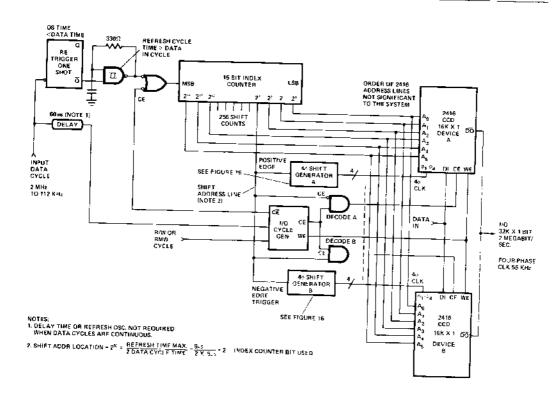

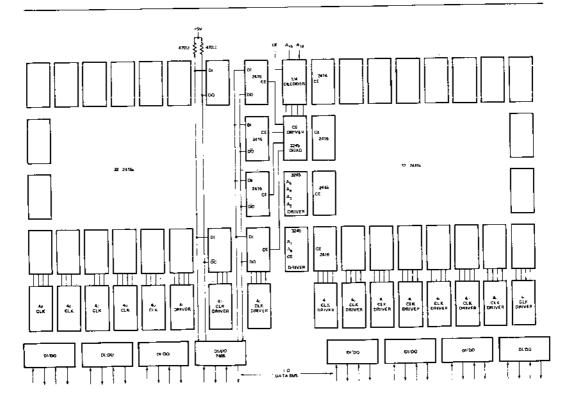

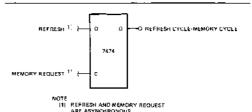

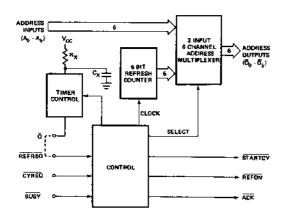

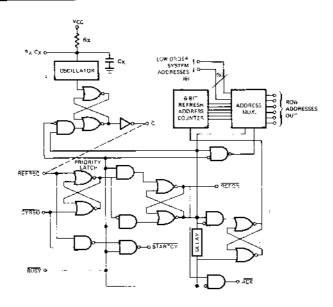

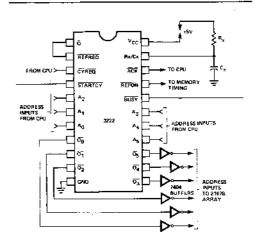

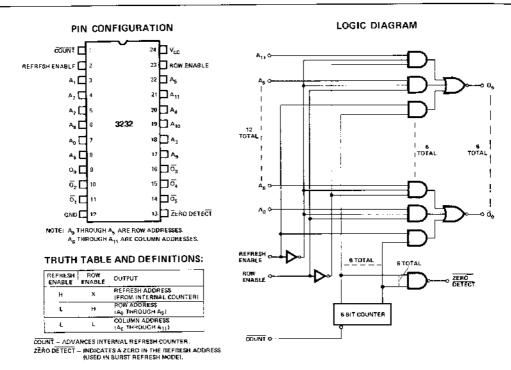

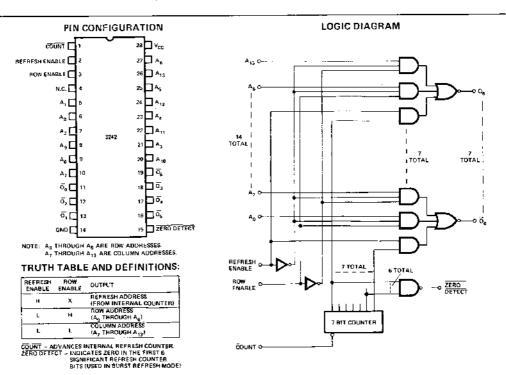

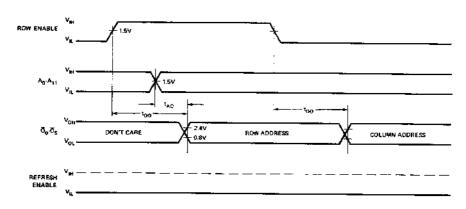

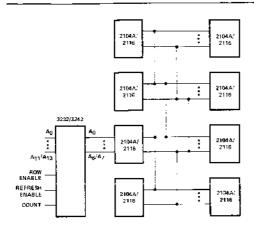

After the refreshing mode has been selected, the address multiplexer and refresh address counter/timer must be configured to support the selected operational mode. The simplest compatible mode (128-cycle RAS-only refresh) will again be developed first. Figure 6 shows the detailed block diagram of the logic required to perform the multiplexing/refresh function for the 2104A/2116 compatible system. An implementation of the required logic using the Intel® 3222 and Intel® 3242 Schottky TTL memory support devices is shown in Figure 7.

The 2104A requires 12 address bits multiplexed into 6 address input pins plus a Chip Select (CS) input. The 2116 requires 14 address bits multiplexed into 7 address input pins and no CS signal. Rather than requiring jumpers or strapping at each address multiplexer input pin, the address assignments shown in Figure 1 are "scrambled" to minimize the strapping requirements as much as possible. This address scrambling effects only the column addresses to the 2116. It results in the column address to the memory devices progressing in the order 0, 2, 4, 6,  $\dots$ , 124, 126, 1, 3, 5, 7,  $\dots$  125, 127 as the column address bits (A9 through A13) from the processor progress in the order 0, 1, 2, 3, 4, ..., 125, 126, 127. This does not effect refreshing since only the column address bits are scrambled. No system effects will result from this technique but it is necessary to be aware of the addressing characteristics while troubleshooting the system.

Figure 6. Detailed Block Diagram of Address and Refresh Logic

Figure 7. 4K/16K Memory System Control

The circuit of Figure 7 assumes a memory board configuration of four rows of memory devices (16K words X n-bits with the 2104A or 64K words X n-bits with the 2116). It also assumes that row selection will be via RAS gating for both the 2104A and 2116 and that the RAS-only refresh mode will be used with both devices. The address decoding for row selection and RAS gating is performed by the 3205. Only address inputs AQ and A1 of the 3205 are used and the E3 enable input pin is used to inhibit the address decoding during refresh cycles.

Processor address bits A<sub>12</sub> and A<sub>13</sub> are decoded by the 3205 when the 2104A is used (14 system address bits total) and address bits A<sub>14</sub> and A<sub>15</sub> are decoded for row selection with the 2116 (16 system address bits total). This requires strapping of the proper system address bits into the 3205 as indicated in Figure 7.

A 74S00 quad Nand gate is used in an inverting OR gate configuration to provide either 1-of-4 RAS enables during data cycles or 4-of-4 RAS enables during refresh cycles to refresh all rows at once.

The 3242 includes the refresh address counter and the counter is incremented following each refresh cycle by the high-to-low transition of the REFRESH ENABLE signal at the 3242 COUNT input.

An optimization of the configuration of Figure 7 would be to select between 64-cycle refresh for the

2104 A and 128-cycle refresh for the 2116. This would optimize the memory availability for each device type while using RAS-only refresh cycles. Figure 8 shows the modifications required on the circuit of Figure 7 to implement the refresh switching.

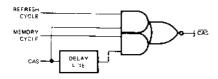

If 64-cycle refresh is desired for both the 4K and 16K RAMs, clock control logic is necessary to switch CAS low prior to RAS during refresh cycles.

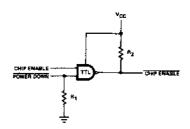

The  $\overline{\text{CS}}$  pin of the 2104A must also be driven high during refresh cycles to prevent data output bus conflicts. One possible logic configuration to perform the switching function is shown in figure 9.

#### Power Distribution/Decoupling

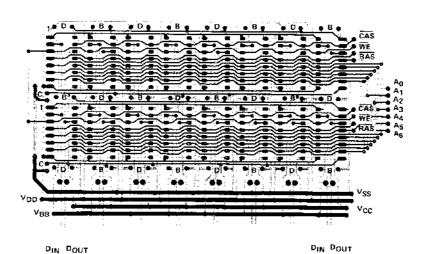

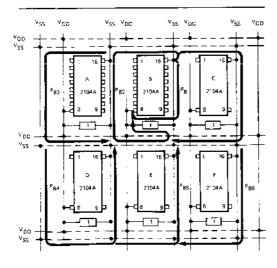

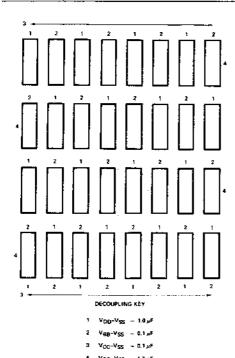

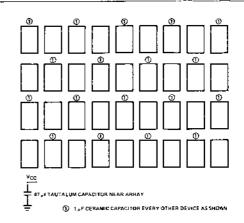

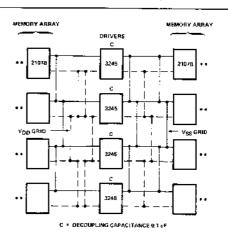

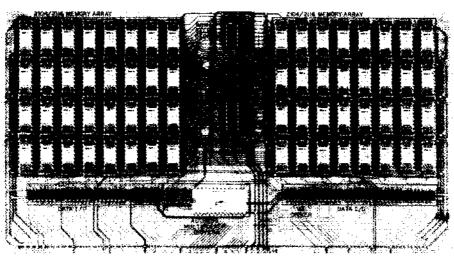

The recommended printed circuit board layout for the memory device array is shown in Figure 10. Notice that each power supply distribution system

Figure 8. Refresh Timing Switching

Figure 9. Multiplexed CAS for 64 Cycle Refresh

in this double-sided layout is gridded both horizontally and vertically at each device location. This technique provides a low inductance, high quality distribution system which performs as well as multilayered layout techniques.

When the layout of Figure 2 and the following recommended decoupling capacitance values are used, power supply noise levels within the memory device matrix will be within the required operational limits for the 2104A and 2116.

Recommended decoupling for the 2104A is as Follows:

VDD: A 0.1μF ceramic capacitor between VDD and VSS at every other device location.

A 10μF tantalum or equivalent bulk capacitor adjacent to the array for each 16 devices in the array.

VBB: A 0.1µF ceramic capacitor between VBB and VSS at every other device location (preferably afternate devices to the VDD decoupling).

A  $10\mu F$  tantalum or equivalent bulk capacitor adjacent to the array for each 32 devices in the array.

VCC: A 0.01µF ceramic capacitor between VCC and VSS for each 8 devices in the array.

Recommended decoupling for the 2116 is the same as for the 2104A with the following exceptions:

VDD: Use  $0.33\mu F$  ceramic capacitors rather than  $0.1\mu F$ .

Use a  $20\mu F$  tantalum rather than a  $10\mu F$ .

A common configuration would be to use  $0.33\mu F$  ceramics for VDD decoupling with both the 2104A and 2116. Also use a  $10\mu F$  tantalum on VDD for each 8 devices in the array. The VBB and VCC decoupling would use the recommended values for the 2104A. This configuration would yield acceptable results with both the 4K and 16K devices and would most likely be more economical than using two different configurations.

DECOUPLING CAPACITORS

D = 0.33 µFtb V<sub>DD</sub> TO V<sub>SS</sub>

B = 0.1 µF V<sub>BB</sub> TO V<sub>SS</sub>

C = 0.01 µF VCC TO VSS

Figure 10. Recommended two-Sided Board Layout for 2116

## Application of the Intel®2104A 4k RAM

Jim Coe Application Engineering

#### Contents

| INTRODUCTION                                   |

|------------------------------------------------|

| DEVICE CIRCUIT OPERATION3-1                    |

| Data Accessing                                 |

| Clock Input Buffers                            |

| Address Buffer/Latch                           |

| Data Sensing                                   |

| Data Sense Amplifier                           |

| Output Data Latch/Driver                       |

| APPLICATIONS INFORMATION 3-6                   |

| Addressing                                     |

| Read Cycle                                     |

| Write Cycle                                    |

| Refresh                                        |

| Page Mode Operation                            |

| Power Dissipation/Operating3-7                 |

| Standby Power-Refresh Only                     |

| Data Output Operation                          |

| POWER DISTRIBUTION/DECOUPLING3-8               |

| General                                        |

| Printed Circuit Board Trace Characteristics3-9 |

| Decoupling Capacitor Characteristics3-9        |

| Power Distribution System Characteristics 3-10 |

| Recommended Decoupling Values 3-12             |

| IBB Characteristics                            |

|                                                |

#### INTRODUCTION

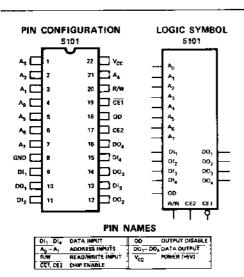

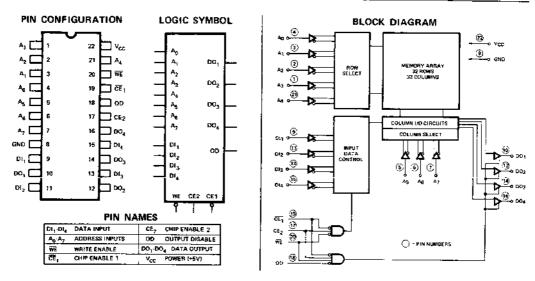

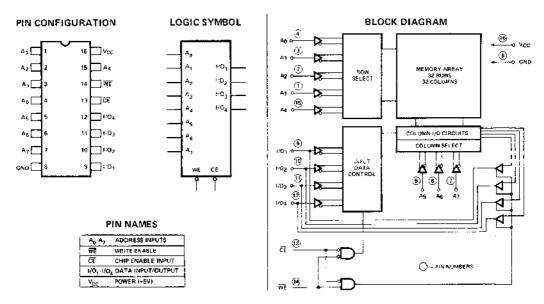

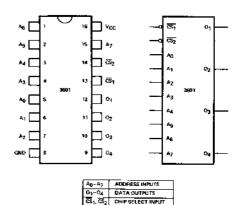

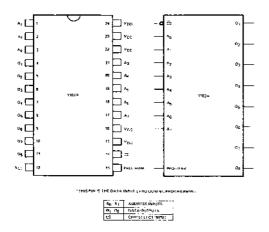

The Intel® 2104A is a 4096 word by 1 bit dynamic random access memory. The 2104A is fabricated using Intel's proven n-channel silicon gate MOS technology. The device is packaged in a standard 16-pin DIP. The pin configuration and logic symbol are shown in Figure 1.

#### PIN NAMES

| Ag As           | ADDRESS INPUTS        | WE.             | WRITE ENABLE |

|-----------------|-----------------------|-----------------|--------------|

| CAS             | COLUMN ADDRESS STROBE | v <sub>aa</sub> | POWER I-SV:  |

| Ġ               | CHIP SELECT           | Vcc             | POWER I+5VI  |

| D <sub>PN</sub> | QATA IN               | Voc             | POWER  +12V  |

| DOUT            | DATA OUT              | Vss             | GROUND       |

| RAS             | ROW ADDRESS STROBE    |                 |              |

Figure 1. 2104A Pin Assignments

The combination of Intel's n-channel silicon gate process and circuit design has resulted in a part that is fast, easy to use, and economically produced in large volume. In addition, the combination of process and device design has resulted in a small device using conservative layout rules. The small size offers advantages in both large volume production and increased reliability.

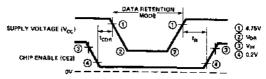

The 2104A operates with three power supplies relative to ground: V<sub>DD</sub> (+12V), V<sub>BB</sub> (-5V), and V<sub>CC</sub> (+5V). The V<sub>CC</sub> (+5V) supply is connected only to the output buffer of the 2104A and may be turned off during power down operations.

The unique design of the 2104A allows it to be packaged in the industry standard 16-pin dual-inline package. The 16-pin package provides the highest system bit densities and is compatible with widely available automated handling equipment.

The use of the 16-pin package is made possible by multiplexing the 12 address bits (required to address 1 of 4096 bits) into the 2104A on 6 address input pins. The two 6-bit address words are latched into the 2104A by the two TTL clocks, Row Address Strobe (RAS) and Column Address Strobe (CAS). Non-critical clock timing requirements allow use of the multiplexing technique while maintaining high performance.

The dynamic storage cell provides high speed along with low power dissipation. The memory cell requires refreshing for data retention. Refreshing is most easily accomplished by performing a read cycle at each of the 64 row addresses every 2 milliseconds

The purpose of this application note is to describe the internal operation of the 2104A and outline those areas in system implementation to which the designer should pay particular attention.

#### DEVICE CIRCUIT OPERATION

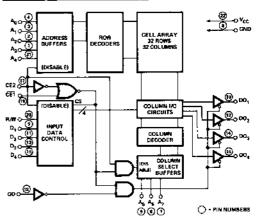

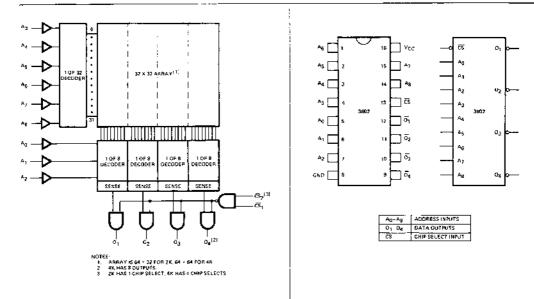

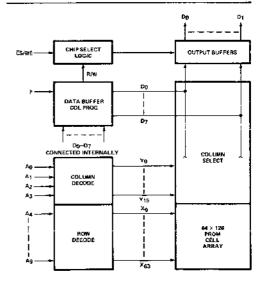

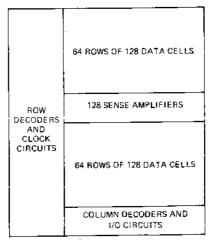

Operation of the 2104A is most easily understood with the aid of the block diagram shown in Figure 2. As is shown in this figure, the memory array is arranged in a 64 row X 64 column matrix of storage cells. The storage cells are implemented with select transistors and "storage" capacitors. The operation of the storage cell will be discussed later. The cell is accessed by the coincidence of a row select (defined by addresses Ao-A5) and a column select (defined by addresses A6-A11) signal at the desired address. On chip timing and control generators provide the internal timing signals for decoding, read/write strobing, data gating and output gating. All of the timing circuits in the 2104A are activated by the negative going edges of the two TTL clocks, RAS and CAS.

Figure 2. 2104A Block Diagram

#### Data Accessing

Prior to discussing the RAS/CAS timing relationships, a discussion of the basic operation of dynamic 4K RAM devices is in order. Access of stored data from a dynamic memory device consists of two discrete retrieval operations. The first of these

operations is the selection of the desired row of storage cells (1 of 64 rows of 64 cells in the 2104A), sensing the data stored in each of the cells with sense amplifiers (64 sense amplifiers in the 2104A), and restoring the sensed data back into the cells since the readout is destructive. When this operation is complete, the sensed data (64 bits) is available at the output of the sense amplifiers. This operation may be completed with only the row address and a clock (RAS with the 2104A) having been supplied to the memory device. This first operation fulfills the refresh requirement on the selected row since data has been restored in the cells on the row.

The second operation consists of connecting the output of one of the sense amplifiers to the device data output via a multiplexer (64 to 1 in the 2104A) and latching the data into the output data latch. In essence, this is accessing data from the sense amplifier outputs rather than from the data cells. This operation requires a column address and a clock (CAS with the 2104A). This second operation is the characteristic which makes page-mode operation possible. Page-mode will be discussed in the Applications Information Section.

The two access operations may occur in parallel as in the 18-pin and 22-pin 4K RAMs or in a time sequential manner in a 16-pin 4K RAM such as the 2104A. With proper design techniques such as used in the 2104A, the sequential mode of operation may be used, saving package pins and with no performance loss as compared to the parallel mode RAMs.

In the parallel mode RAMs (such as the Intel® 2107B) all address information is applied to the RAM at the same time and both access operations occur simultaneously. The cell data access is the slower of the two operations and is the limiting factor in device speed. The selection of the proper sense amplifier output for connection to the device output is completed prior to the time it is necessary.

In the sequential mode 2104A RAM, cell data access is begun first by the latching in of the row address information (6-bits for 1 of 64 row select) by the RAS. The access of data from the sense amplifier outputs is faster and thus may be started later without impacting overall access time [up to 70 nanoseconds (tRCL(max)) later in the 2104A-2]. The 6-bit, 1 of 64 sense amplifier data address (column address) is latched into the 2104A-2 by the CAS. As long as the sense amplifier output data access is started prior to 70 nanoseconds into the memory cycle, the limiting access time is tRAC, the data cell access time plus the propagation time through the sense amplifier data select multiplexer.

This access time is the same as the parallel mode access time would be.

If the column address latching is delayed until later than 70 nanoseconds into the memory cycle, the limiting access time will become the sense amplifier data access time. In this instance, the access time will be tCAC (access time from CAS which includes the sense amplifier output data multiplexer propagation time) plus tRCL actual (the actual RAS to CAS delay time). It is obvious that it is desirable to latch the column address into the 2104A-2 at or prior to the 70 nanosecond point in the memory cycle to preclude lengthening of data access time.

In the 2104A-2, a 45 nanosecond window is provided during which  $\overline{CAS}$  may be switched while maintaining device access time. In other words, the  $\overline{CAS}$  leading edge may occur at any time between 25 and 70 nanoseconds following  $\overline{RAS}$  and the access time will be tRAC. Timing accuracy required between  $\overline{RAS}$  and  $\overline{CAS}$  is thus reduced. The advantages of this timing "window" will be discussed in the Applications Information Section.

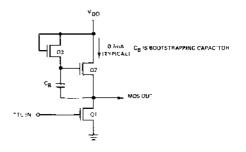

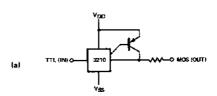

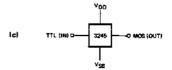

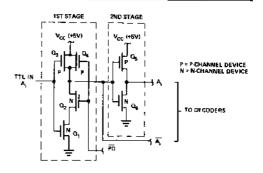

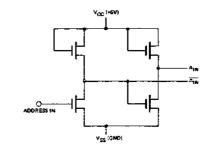

#### Clock Input Buffers

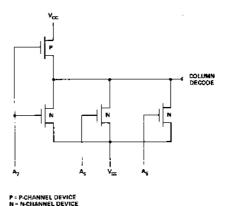

The two device clocks, RAS and CAS, are TTL compatible, active-low signals. The clock input buffers are inverters which convert the TTL levels to the MOS (12 volt) levels required within the 2104A. The major design consideration for these buffers is speed since it is desirable to respond to the clock inputs as quickly as possible to obtain minimum data access. The speed is obtained by implementing the inverters with high gain (large geometry) devices operating at relatively high current levels. The inverter circuit is shown in Figure 3.

Figure 3. Simplified CLOCK Input Buffer

The inverter uses a bootstrapped, 0.7 milliampere (typical) load device. The bootstrapping is used to assure that the load device (Q2) is fully turned-on so that the drain voltage of Q1 reaches VDD. Without the bootstrapping, the drain of Q1 would only reach VDD-VT where VT is the load device threshold voltage. This would slow down the inverter operation and affect the response time to the clock(s).

The current requirement of the input buffer accounts for the difference in standby power levels between the 16-pin TTL clock devices and the 18 or 22-pin MOS clock devices. When the RAS clock is inactive (high), the 2104A RAS buffer is on and the inverter load current (2.0mA maximum) is drawn from The V<sub>DD</sub> supply yielding the 26.4mW maximum standby power specification. MOS clock devices (such as the Intel® 2107B) have inactive low clocks and no buffer is on during standby, yielding standby power specifications under 3mW maximum (leakage currents only). This standby power reduction at the memory device level is offset at the system level by the larger power dissipation levels of MOS level clock driver devices versus TTL level drivers. The 2104A TTL clock inputs are lower in capacitance than the MOS clock inputs (7 picofarads versus 25 picofarads). At a given speed, this means a typical TTL driver can drive 32 2104A clock inputs while a typical MOS clock driver can drive only 10 2107B clock inputs.

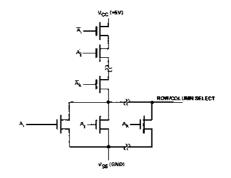

#### Address Buffer/Latch

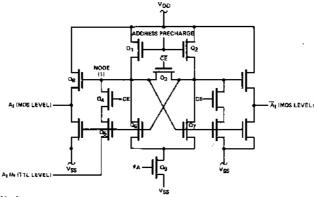

The TTL-level compatible address buffer/latch circuit is shown in Figure 4. This circuit senses the input TTL level, translates it to MOS signal levels, and latches the address information. There are two groups of six input buffer/latches in the 2104A; one for the six row addresses and one for the six column addresses. The operation of each group of latches is the same except for the clock signals which control their function.

The operation of the address buffer/latch is as follows: During the clock ( $\overline{RAS}$  or  $\overline{CAS}$ ) off time (tRP or tCP) both sides of the latch (Nodes A and B) are precharged to VX ( $\approx 10$  volts) by devices Q7 and Q9. Device Q8 is turned on during the precharge period to assure that the two nodes charge to the same potential. Internal signal  $\emptyset$ p controls the precharge devices and is on while the  $\overline{RAS}$  and  $\overline{CAS}$  clocks are off (at  $V_{IH}$ ). When the appropriate system clock ( $\overline{RAS}$  or  $\overline{CAS}$ ) goes low (active),  $\emptyset$ p turns off isolating the two precharged nodes and internal clock phase  $\emptyset$ A turns on connecting the TTL address (AIN) to Node C (the gate of the input buffer device Q2 and capacitor C1). Clock phase  $\emptyset$ A stays on for the address

hold time  $(t_{AH})$  and then turns off isolating Node C from the shared address input pin. The TTL level which was on the address pin during  $t_{AH}$  is still stored on capacitor  $C_1$  allowing the address latch additional time to capture the address. This "sample and hold" technique allows short address hold times to be achieved.

Figure 4. Simplified Address Buffer/Latch Schematic

Internal clock phase  $\emptyset_B$  turns on after a slight delay from phase  $\emptyset_A$  turning on. Phase  $\emptyset_B$  enables the buffer/latch by turning on load devices Q3, Q6, and Q10. The buffer (Q2 and Q3) converts the TTL level address input to MOS levels (VSS and VDD) and drives Node A of the latch. The delay between  $\emptyset_A$  and  $\emptyset_B$  is to allow the voltage at Node C to stabilize prior to enabling the buffer/latch.

A TTL high level at the address input will force Node A to VSS. The cross-coupled latch devices (Q4 and Q5) will then switch driving Node B to VDD. Conversely, a TTL low level at the address input will force Node A to ~VDD and Node B to VSS. Since the buffer/latch is isolated from the address input after tAH, the latched address will remain in the latch even though the TTL level at the address input may change due to the multiplexing of the addresses.

#### **Data Sensing**

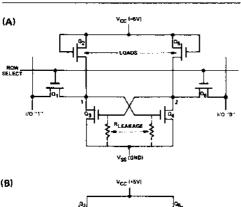

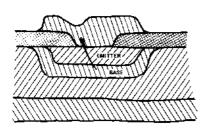

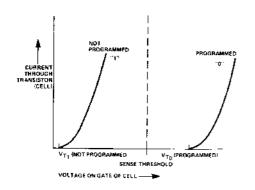

A major contributor to the operating margins of the 2104A is the use of two single-transistor storage cells per bit of storage. The effect of using two cells per bit rather than one is best understood by comparison of the data sensing function when used with one and two cells per bit.

Figure 5 illustrates the commonly used sense amplifier and reference voltage scheme for single cell per bit 4K RAMs. The sense amplifier in Figure 5 senses data stored in a storage cell by comparing the voltage level in the storage cell capacitor to the voltage level in the cell capacitor of a "dummy" storage cell. The dummy cell capacitor contains a voltage which is less than the minimum high level and greater than the maximum low level which may be stored in the storage cell capacitor. The sense amplifier then senses the differential level between the storage and dummy cell capacitor voltages. The level stored in the dummy cell would ideally be equal to one-half the difference between a minimum written high and a maximum written low as this would yield a maximum differential across the sense amplifier during sensing. Unfortunately, leakage currents from the storage capacitors degrade the written high levels toward the written low levels. This normally requires that the designer set the dummy storage cell level lower (closer to a low level than a high level) to compensate for leakage degradation of a stored high level. Although this "lower" reference level tends to compensate for a leakage degraded high level, it also makes it more difficult to sense a ground (VSS) noise degraded low level. Thus, designs with dummy reference cells must necessarily be a compromise in the maximum differential level between the storage and dummy cells and can never have a differential greater than one-half the difference between a high and low level.

The dummy ceil technique is used (rather than simply developing a reference voltage level with a resistive divider) because it contributes to the capacitive balance of the sense amplifier.

The sense amplifer of Figure 5 will operate with maximum margins only when the capacitance seen by Node B is the same as the capacitance seen by Node A, i.e., the capacitances are equal or balanced. The capacitances of the left (BSLL) and right (BSLR) bit sense lines as well as the dummy cell and storage cell capacitances can be made approximately equal by layout constraints. The effect of

the I/O line connection to the right bit sense line is to add capacitance on the right bit sense line which is not offset or balanced by capacitance on the left bit sense line. The placement of the dummy cell on the bit sense line also contributes to capacitance imbalance since its location is not a mirror image of the accessed storage cell. The resistive effects of the bit sense line magnify the effect of this placement disparity during the data sensing process. The ideal situation would be a dummy cell mirroring the placement of the accessed data cell and a balancing capacitance to the I/O connection capacitance

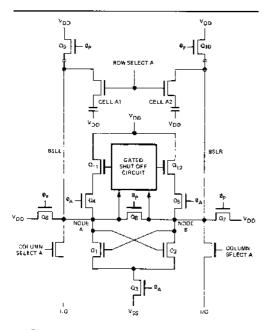

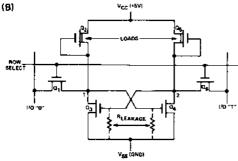

This is essentially the technique used in the Intel® 2104A. Instead of a dummy cell containing a reference level of one-half a minimum high level, the 2104A stores the full opposite data level in a mirror image storage cell physically located near the accessed storage cell as shown in Figure 6. Not only does this mean that the storage cell and "image" cell capacitance and location with respect to the sense amplifier are equal, but the data level is now being sensed against the full opposite level rather than one-half of the minimum high level. Thus, the sense amplifier is seeing the maximum possible differential signal during the sensing operation.

Also, notice in Figure 6, that there is an I/O connection to each bit sense line rather than only to one. The I/O capacitance contribution to the bit sense line capacitance is therefore equal, contributing again to the overall balance of the sense amplifier.

The 2104A sense amplifier sees essentially equal capacitances at nodes A and B and this contributes greatly to the margins of the sensing operation. This balance of the sense amplifier and the sensing of data against a reference of a full opposite level allows the cell capacitors to be a smaller value than with the dummy cell approach (for equal margins) and allows 8192 cells to occupy only slightly more chip area than 4096 cells previously occupied in the Intel® 2104.

Figure 5. Old Dummy Cell Data Sensing Technique

- Each storage location consists of avercells Each cell is furned by single transistor and storage capacitor as shown.

- As row select prior two cells are tyrined on simultaneously to gate the data to the data sense latch.

- Date is stored to a given address fucetion as both a high and a low on each of the two respective data cells.

Figure 6. 2104A !mage Cell Data Sensing Technique

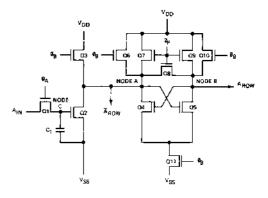

#### Data Sense Amplifier

The data sense amplifier of the 2104A is a cross-coupled static latch as shown in Figure 7. The state

Figure 7. Simplified Data Sense Amplifier Schematic

the latch assumes during sensing of the stored data depends upon the differential voltage between nodes A and B. If the voltage on node A is higher than the voltage on node B, transistor Q2 will turn on switching node B and the gate of transistor Q1 to VSS turning transistor Q1 off. Conversely, if the voltage on node B is higher than the voltage on node A, transistor Q1 will turn on while transistor Q2 will be turned off. Devices Q4 and Q5 act as loads for the switching transistors Q1 and Q2, respectively. Additional transistors (Q6 through Q10) shown in the circuit diagram of Figure 7 serve to precharge nodes A and B to ~VDD in preparation for the next memory cycle. This precharging assures that the sense amplifier and bit sense lines begin each memory cycle in the same known condition or state with no "history" or "memory" of data from previous cycles eliminating data pattern effects on the sensing function. Note that the 2104A has precharge transistors connected to both ends of the bit sense lines to speed up the precharging of the lines and sense amplifier. This increases the timing margin of the clock off time (tRP) and enables the 2104A to run short memory cycles without degradation of the precharge function. The "folded", close proximity bit sense lines shown in Figure 6 and transistor Qs of Figure 7 assure that the precharge level of each pair of bit sense lines and the associated sense amplifier nodes reach the same precharge level contributing to the balance of the sensing function.

Transistor Q3 in Figure 7 turns the sense amplifier on by completing the current path to VSS when the row address bits have been decoded and the desired row of storage cells selected. The gated shutoff circuit controls transistors Q11 and Q12 to reduce the power dissipation of the sense amplifier following the sensing of the stored data. The shutoff circuitry senses the levels on Nodes A and B and turns off the load current to the switching transistor (Q1 or Q2) which is turned on to VSS. This reduces the IDD current drawn by the sense amplifier and contributes to the low power dissipation of the 2104A.

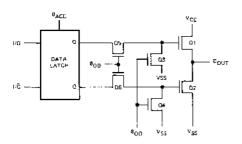

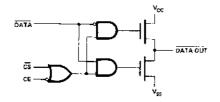

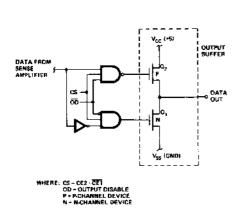

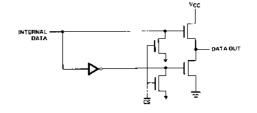

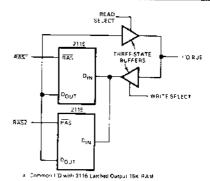

#### Output Data Latch/Driver

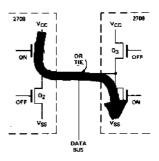

A simplified schematic of the 2104A output data latch/driver is shown in Figure 8. The three operational states for the output driver are:

- 1) "1" output (Q1 on and Q2 off)

- 2) "0" output (Q1 off and Q2 on)

- 3) Open output (Q1 and Q2 off)

Devices Q<sub>1</sub> and Q<sub>2</sub> are large geometry devices which allow the output of the 2104A to source and sink the relatively large current levels associated with TTL interfaces. Devices Q<sub>3</sub> through Q<sub>6</sub> control the output driver stage in conjunction with the data latch.

Figure 8, 2104A Output Data Latch and Buffer

The inputs to the latch are data from the selected cell and a clock phase (\$\Omega\_{ACC}\$) which is related to access time from the cell matrix. At the proper time after the memory cycle starts, \$\phi\_{ACC}\$ will go high, clocking the data from the selected cell into the latch. The Q and  $\overline{Q}$  outputs of the latch then drive the gates of devices Q1 and Q2 controlling the output level. The accessed data will remain in the latch until the next cycle when new data will be clocked into the latch. During a write cycle, the data input to the latch is the data on the I/O lines which is the data to be written into the selected cells. The data latch will, therefore, contain the input data following a write cycle. The first two of the three possible output data states are, therefore, related to the data level stored in the latch.

The third or open-circuited state occurs when devices Q<sub>1</sub> and Q<sub>2</sub> are both off (gates at VSS). Internal signal Ø<sub>OD</sub> turns on devices Q<sub>3</sub> and Q<sub>4</sub> connecting the gates of devices Q<sub>1</sub> and Q<sub>2</sub> respectively to VSS from shortly after the CAS input switches low until data access time. This signal forces the data output to the open-circuited condition following CAS in every memory cycle guarantying that no two OR-tied data outputs in a system will be on at the same time.

The control clock phase  $\emptyset_{OD}$  is a logic function of  $\overline{CAS}$  and  $\overline{CS}$ . Table I lists the various combinations of  $\overline{CAS}$  and  $\overline{CS}$  and the corresponding states of  $\emptyset_{OD}$ .

Devices  $Q_5$  and  $Q_6$  in Figure 8 are simply series switches which isolate the Q and  $\overline{Q}$  outputs of the data latch from output devices  $Q_1$  and  $Q_2$  until the latch data has stabilized.  $Q_5$  and  $Q_6$  are controlled by the inverse of  $\emptyset_{OD}$  so that the latch is isolated from  $Q_1$  and  $Q_2$  when the gates of  $Q_1$  and  $Q_2$  are connected to  $V_{SS}$ .

Table I. Operational States of POD

| RAS  | CAS | <del>CS</del> | <b>Ø</b> OD | COMMENTS                               |

|------|-----|---------------|-------------|----------------------------------------|

| LOW  | LOW | HIGH          | нібн        | Device Deselected by CS (DOUT = HI-Z)  |

| LOW  | LOW | LOW           | LOW         | Device Selected by<br>CS (DOUT = Data) |

| нібн | LOW | Don't<br>Care | HIGH        | Device Deselected by CAS (DOUT=HI-Z)   |

#### APPLICATIONS INFORMATION

#### Addressing

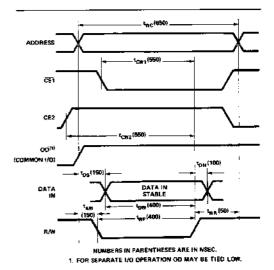

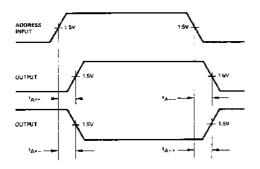

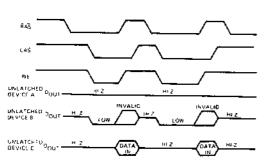

The 2104A RAM combines the advantages of a very high speed RAM with the high packing density of the industry standard 16 pin dual-in-line package. The use of the 16 pin package is made possible by multiplexing the 12 address inputs (required to access 4096 words) on 6 external address pins. Two externally applied negative going clocks, Row Address Select (RAS), and Column Address Select (CAS), are used to strobe the two sets of 6 address bits into the internal address buffer registers. The first clock, RAS, strobes in the six low order address bits (A0-A5) which select one of 64 rows. The second clock, CAS, strobes in the six high order address bits (A6-A11) which select one of 64 columns and Chip Select (CS).

Note that CS and WE do not have to be valid until the second clock, CAS. It is, therefore, possible to start a memory cycle before it is known which device must be selected or what type of cycle is to be performed. This can result in a significant improvement in system access time since the decode time for chip selection does not enter into the calculation for access time.

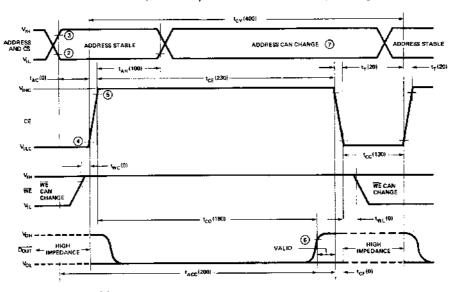

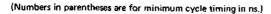

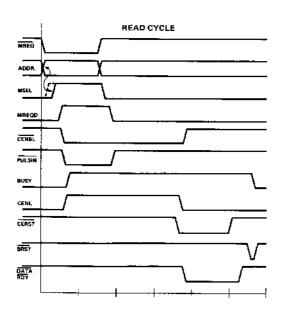

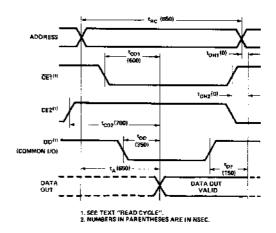

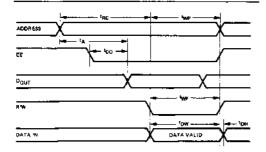

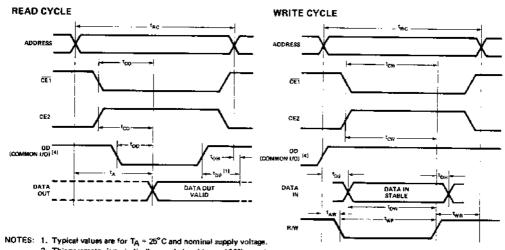

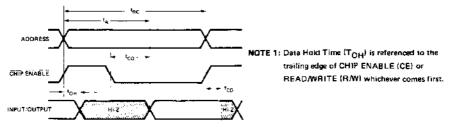

#### Read Cycle

A memory cycle begins with addresses stable and a negative transition of  $\overline{RAS}$ . The data-out pin of the selected device will unconditionally go to a high impedance state immediately following the leading edge of  $\overline{CAS}$  and remain in this state until valid data appears at the output (refer to the Data Output Operation Section). The selected output data is internally latched and will remain valid until a subsequent  $\overline{CAS}$  is given to the device by a Read, Write, Read-Modify-Write or Refresh cycle. Dataout goes to a high impedance state for all non-selected devices ( $\overline{CS}$  high) that receive  $\overline{RAS}$  and  $\overline{CAS}$

Device access time,  $t_{ACC}$ , is the longer of two calculated intervals:

1) tACC = tRAC OR

2)  $t_{ACC} = t_{RCL} + t_{T} + t_{CAC}$

Access time from  $\overline{RAS}$ ,  $t_{RAC}$ , and access time from  $\overline{CAS}$ ,  $t_{CAC}$ , are device parameters. Row to column address strobe lead time,  $t_{RCL}$ , and transition time,  $t_{T}$ , are system dependent timing parameters.

Substituting the device parameters for the 2104A-2 and assuming a TTL level transition time of 5nS yields:

- 3)  $t_{ACC} = t_{RAC} = 200 \text{ns} \text{ for } t_{RCL} + t_T \le 70 \text{ ns}$ OR

- 4)  $t_{ACC} = t_{RCL} + t_T + t_{CAC} = t_{RCL} + t_T + 130 \text{ns}$  for  $t_{RCL} + t_T > 70 \text{ns}$

Note that if  $t_{RCL} + t_T \le t_{RCLmax}$ , device access time is determined by equation 3 and is equal to  $t_{RAC}$ . If  $t_{RCL} + t_T > t_{RCLmax}$ , access time is determined by equation 4. A 45ns interval  $(t_{RCLmax} - t_{RCLmin})$  in which the falling edge of  $\overline{CAS}$  can occur without affecting the access time is provided to allow for system timing skew in the generation of  $\overline{CAS}$ . This "designed in" skew window at the device level allows minimum access times to be achieved in practical system designs.

Note that both the RAS and CAS clocks are TTL compatible and do not require external level shifting to high voltage MOS levels. Internal buffers in the 2104A convert the TTL level signals to MOS levels inside the device. Therefore, the delay associated with external TTL-MOS level converters is not added to the 2104A system access time.

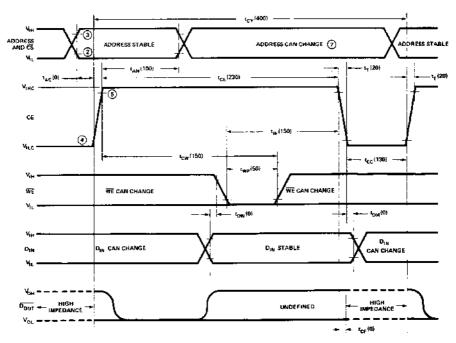

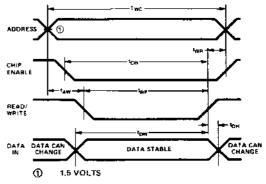

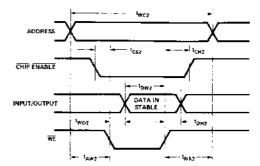

#### Write Cycle

A Write Cycle is performed by bringing Write Enable (WE) low before or during CAS. If Write Enable goes low at or before CAS goes low, the input data must be valid at or before the CAS falling edge. If Write Enable goes low after CAS, Data In must be valid at or before the falling edge of WE. If Write Enable is low before CAS goes low, the data-out buffer will contain the written data at access time. However, if Write Enable goes low while CAS is low, a read operation may also be performed and data-out will go either high or low depending on the state of the accessed cell before the write takes place (refer to the Data Output Operation Section).

#### Refresh

Each of the 64 rows internal to the 2104A must be refreshed every 2 msec to maintain data. Any data cycle (Read, Write, Read-Modify-Write) refreshes the entire selected row (defined by the 6-bit row address). The refresh operation is independent of the state of  $\overline{CS}$ . It is evident, of course, that if a Write or Read-Modify-Write cycle is used to refresh a row, the device should be deselected ( $\overline{CS}$  high) if

it is desired not to change the state of the selected cell. RAS-only cycles may also be used to refresh the 2104A at a savings in power dissipation over data cycles.

#### Page Mode Operation

Page mode operation with the 2104A allows faster successive memory data operations at the 64 column locations in a single address row. Receipt of a RAS and a 6-bit row address byte causes the RAM to access the 64 data cells on the addressed row.

At access time all 64 data bits are available at the sense amplifier outputs as long as  $\overline{RAS}$  is held active. By cycling the  $\overline{CAS}$  clock and addressing the desired data bit with the 6-bit column address byte all 64 data bits may be brought to the data output of the device. Data access and cycle time in this mode, called page mode, is faster than normal data cycles. Page mode is an excellent way to transfer blocks of data to and from memory at high speed, but it is impacted by refreshing.

The refresh requirements of the device limits the number of consecutive page mode cycles that may be performed. The device may remain in the page mode for a period no longer than the time required between refresh cycles. As an example, recall that the distributed refresh mode requires a refresh cycle every 31 microseconds. RAS may then remain low (active) for 31 microseconds maximum before it must be cycled high to precharge and then perform a refresh cycle. System page mode cycle times of 485 nanoseconds or less will enable all 64 data bits in the selected row to be examined or written between refresh cycles, maximizing the usefulness of page mode.

#### Power Dissipation/Operating

The power dissipation of a continuously operating 2104A device is the sum of Vpp x Ipp and Vpp x Ipp and Vpp x Ipp and tpp of 100ns) the typical power dissipation of the 2104A-1 is 289 mW.

#### Standby Power-Refresh Only

The standby power-refresh only is calculated by the following equation:

1)

$$P_{REF} = P_{OP} \left(64 \frac{t_{CYC}}{t_{REF}}\right) + P_{SB}\left[1 - \left(64 \frac{t_{CYC}}{t_{REF}}\right)\right]$$

Where:

PREF = Standby power-refresh only.

**POP** = Power dissipation-continuous operation.

tCYC = Refresh cycle time.

tREF = Refresh period.

PSB = Standby power dissipation.

Table 11. 2104A Family Current Specifications

|                  |                                      | Limits |     | 1 1   | ]                                    |  |

|------------------|--------------------------------------|--------|-----|-------|--------------------------------------|--|

| Symbol           | mbol Parameter Typ                   |        | Max | Units | Comments                             |  |

| <sup>†</sup> DD1 | VDD Standby Current                  | 0.7    | 2.0 | mA    | V <sub>DD</sub> = 13.2 Volts         |  |

| יסס2             | VDD Data Cycle Operating Current     | 24     | 35  | mA    | 2104A-1 t <sub>CYC</sub> = 320 ns    |  |

|                  |                                      | 22     | 32  | mΑ    | 2104A-2 t <sub>CYC</sub> = 320 ns    |  |

|                  |                                      | 20     | 30  | mA    | 2104A-3,-4 t <sub>CYC</sub> = 375 ns |  |

| IDD3             | Von RAS-Only Cycle Operating Current | 12     | 25  | mA    | 2104A-1,-2 t <sub>CYC</sub> = 320 ns |  |

|                  |                                      | 10     | 22  | mA    | 2104A-3,-4 t <sub>CYC</sub> = 375 ns |  |

| IBB1             | VBB Standby Current                  | 5      | 50  | Αц    |                                      |  |

| I <sub>BB2</sub> | VBB Operating Current                | 160    | 400 | μА    | Minimum Cycle Time                   |  |

The standby power dissipation PSB is given by:

2)  $PSB = VDD \times IDD1 + VBB \times IBB1$

The operating power POP is given by:

3)  $POP = VDD \times IDD2 + VBB \times IBB2$

for read and write data cycles or by:

4) Pop = VDD x IDD3 + VBB x IBB2 for RAS-only refresh cycles.

Table II fists the pertinent current values for the 2104A family of devices.

Calculating the standby-refresh only power dissipation for the 2104A-1 using equations 1 through 4 above and the data from Table II yields:

a) For RAS-only Refresh:

$P_{REF} = 330 \text{mW} (0.01) + 26.7 \text{mW} (0.99) = 29.7 \text{mW} \text{maximum}$

b) For Read or Write Cycle Refresh:

$P_{REF} = 462 \text{mW} (0.01) + 26.7 \text{mW} (0.99) = 31.0 \text{mW} \text{ maximum}$

at VDD = 13.2 volts, VBB = -5.5 volts and the specified maximum current levels.

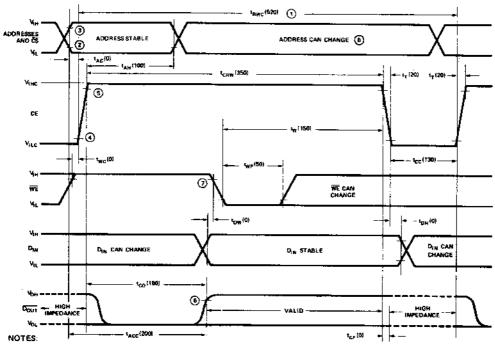

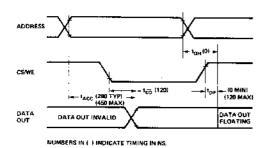

#### Data Output Operation

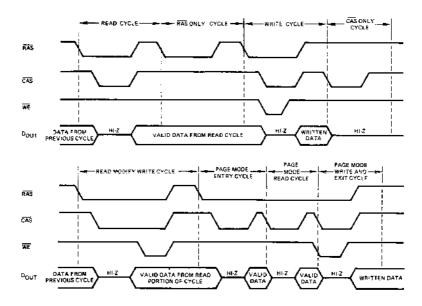

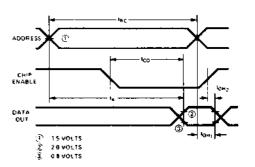

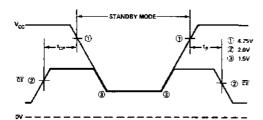

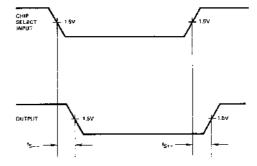

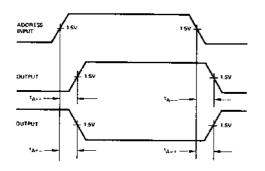

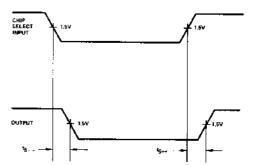

The operation of the output data latch is controlled by the CAS clock. Figure 9 indicates the content of the data latch following access time during various types of 2104A memory cycles. Table III summarizes the information on data content shown in Figure 9.

#### POWER DISTRIBUTION/DECOUPLING

#### General

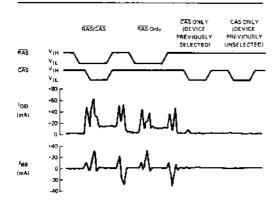

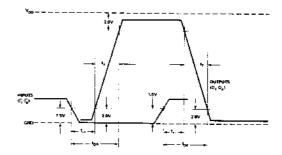

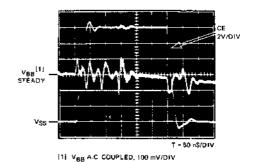

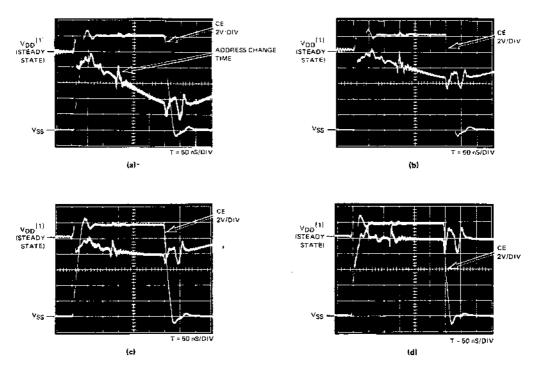

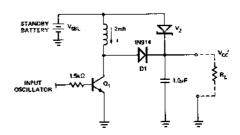

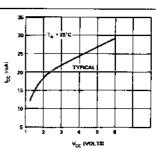

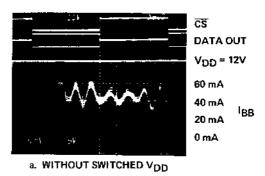

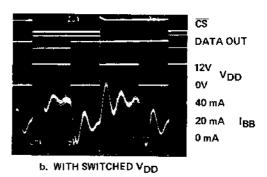

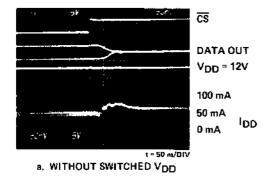

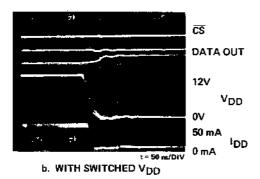

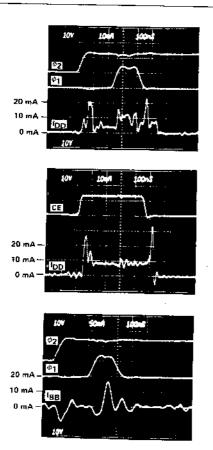

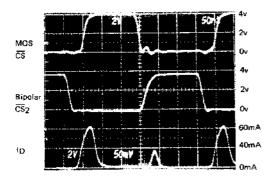

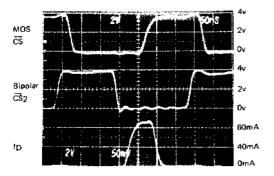

Typical IDD and IBB current waveforms for the 2104A are shown in Figure 10. Examination of these waveforms shows that transient current drawn from the memory circuit board power distri-

Table III. Data Latch Content at End of Cycle

| Type of Cycle                                                      | Data Latch Content (DOUT)                                                         |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Read Cycle                                                         | Data from Addressed Memory<br>Cell                                                |

| Write Cycle                                                        | Input Data (DIN)                                                                  |

| RAS-Only Cycle                                                     | Data from Previous Cycle or<br>HI-Z if Device was Deselected<br>in Previous Cycle |

| CAS-Only Cycle                                                     | HI-Z (CAS-Only Deselects Device and Turns Output Buffer Off)                      |

| R-M-W Cycle                                                        | Data Read from Addressed<br>Memory Cell During Read<br>Portion of Cycle           |

| Page Mode Read<br>and Entry Cycle                                  | Data from Addresssed Memory<br>Cell                                               |

| Page Mode Read<br>Cycle                                            | Data from Addressed Memory<br>Cell                                                |

| Page Mode Write<br>Cycle (or Page<br>Mode Write and<br>Exit Cycle) | Input Data (D;N)                                                                  |

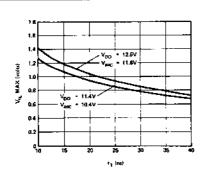

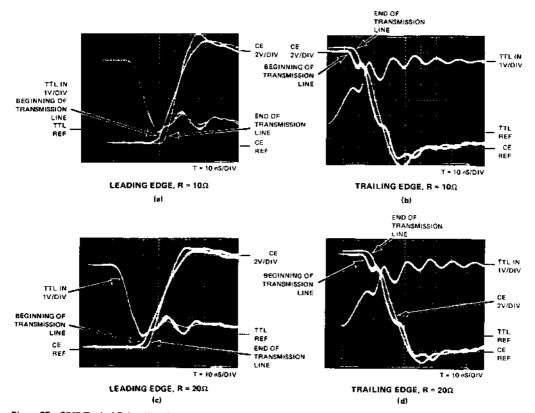

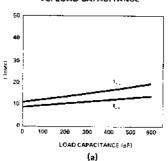

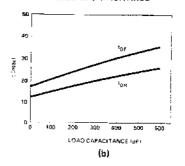

bution system is a function of the two device clocks, RAS and CAS. The peak amplitude of the VDD current transients is approximately 60 milliamperes with rise and fall times in the 5 to 10 nanosecond range and widths of typically 20 nanoseconds. Rise and fall times of this magnitude generate significant harmonic noise components in the 10 MHz and above frequency region. The power distribution/decoupling techniques used to suppress these noise components must be effective at these higher frequencies. The series inductance of the circuit board traces and the decoupling capacitors must be minimized to reduce time constant response effects of the distribution/decoupling system.

Figure 9. Operation of Data Output (DOLLT)

#### Printed Circuit Board Trace Characteristics

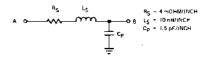

Figure 11 shows the nominal lumped constant equivalent circuit of one-inch of 10 mil wide 2-ounce copper trace on a typical double sided printed circuit board with traces on both surfaces. The effect of the series resistance  $R_{\rm S}$  is very small when compared to the series inductance  $L_{\rm S}$  and can be ignored in practice. The series resistance is also non-reactive and its impedance is not frequency dependent. The following discussions will, therefore, not consider the minimal effects of  $R_{\rm S}$ .

Figure 10. Typical Supply Current Waveforms

#### **Decoupling Capacitor Characteristics**

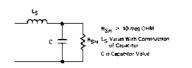

Capacitors used to decouple noise arc not ideal devices and, therefore, exhibit inductive and resistive effects. Figure 12 shows the lumped constant equivalent circuit of a capacitor. The shunt resistance RSH is a very high value (>10 M $\Omega$ ) in capacitors of modern design and has minimal effects on the capacitor function. Therefore, the effect of RSH will not be considered in the analysis of the decoupling capabilities of the capacitor.

The series inductance  $L_S$  in small disc ceramic and monolithic ceramic capacitors consists of lead inductance and is approximately 10nH/inch.

Figure 11. Lumped Constant Trace Equivalent Circuit

Figure 12. Lumped Constant Capacitor Equivalent Circuit

The series inductance in bulk capacitors such as tantalum and aluminum electrolytics is much larger due to the construction of the capacitors. The internal series inductance of the electrolytic units varies widely with capacitance value, physical size, and construction type and is generally much greater than the lead inductance. For this reason, the effectiveness of electrolytic type capacitors as decoupling components for noise frequencies above 10 MHz is minimal. Their use in the power distribution/decoupling network is to provide a bulk power storage element located on the memory array board. This placement eliminates the inductive effects of the system backplane wiring on the power distribution to the memory array board.

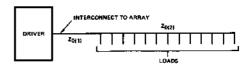

#### Power Distribution System Characteristics

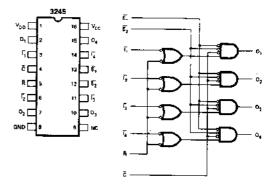

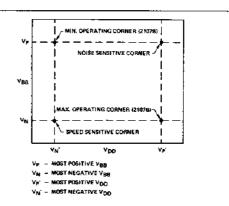

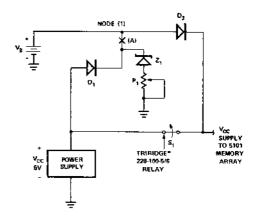

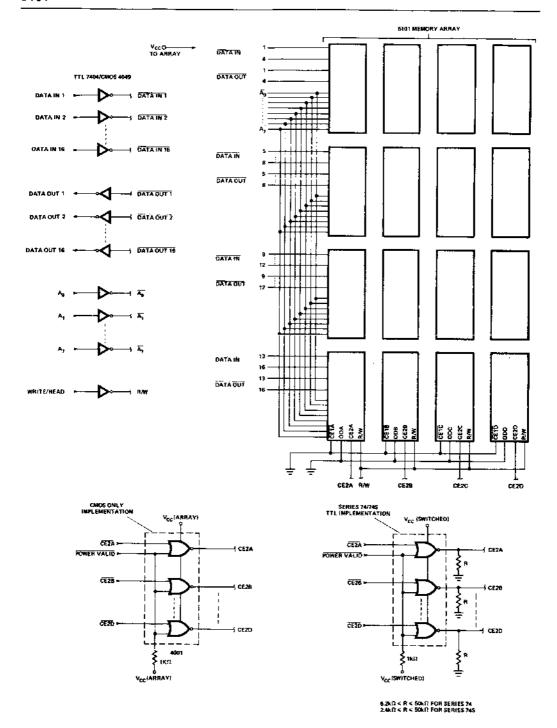

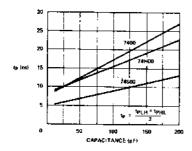

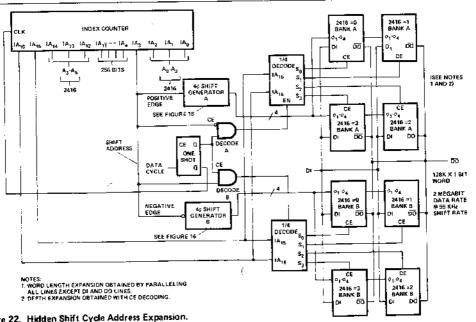

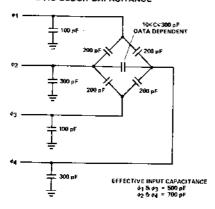

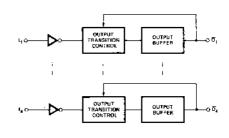

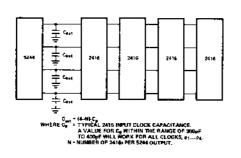

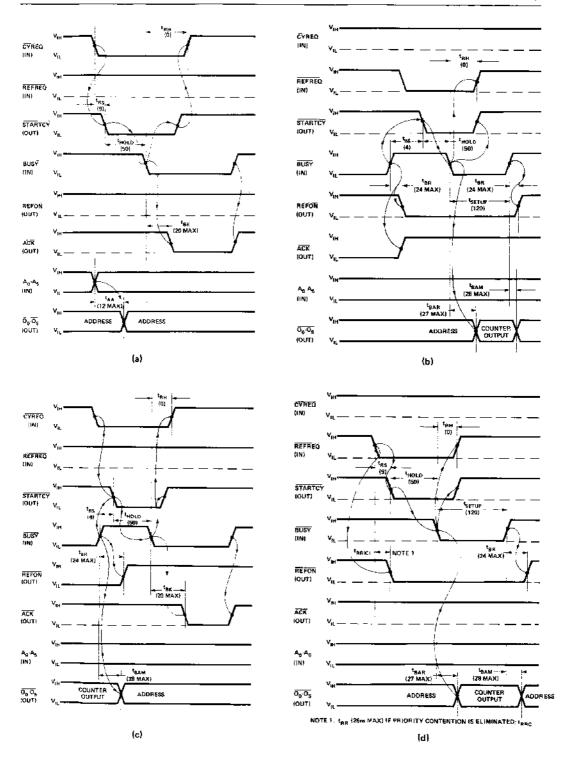

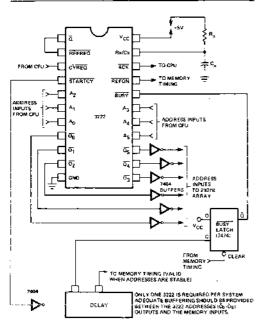

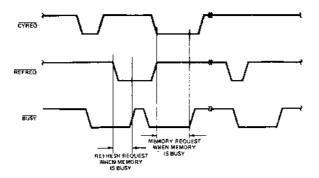

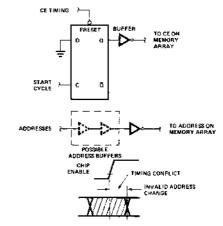

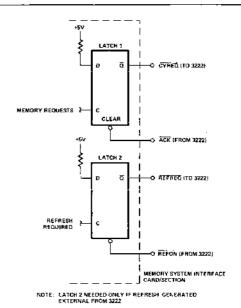

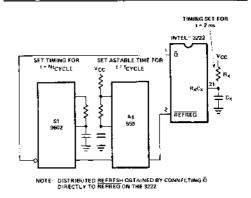

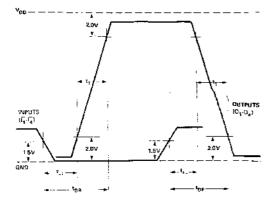

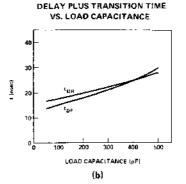

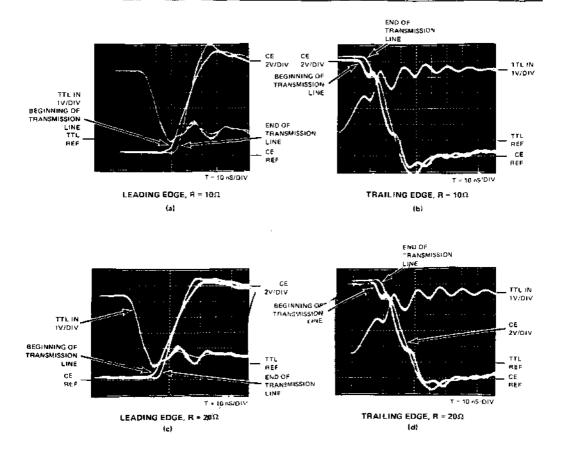

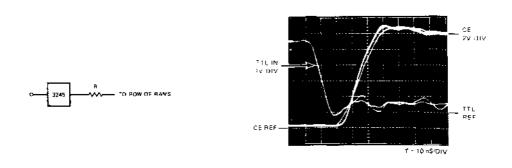

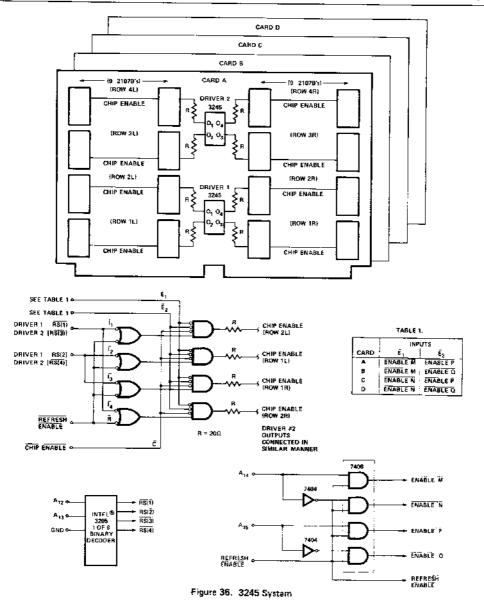

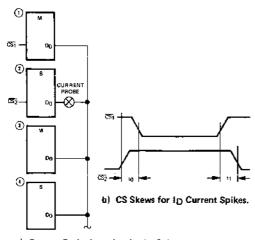

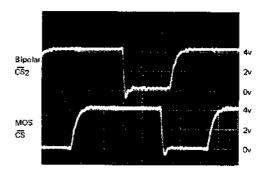

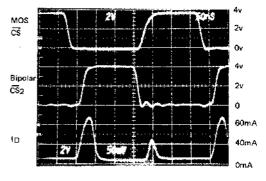

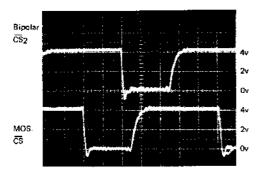

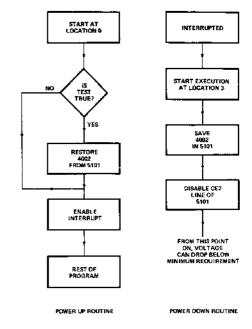

Now that models for the printed circuit board traces and decoupling capacitors have been generated, various power distribution/decoupling schemes can be compared for effectiveness in minimizing power supply noise levels.