MICRO-TERM, INC. ST. LOUIS, MISSOURI Thank you very much for your purchase of an ACT-I. Your unit has been thoroughly tested before shipping and should give you many years of maintenance free service. Before connecting your new ACT-I to your processor, please read the operating manual and be sure that the data rate, logic levels, and options are set for your application.

If your ACT-I or monitor was received in obviously damaged condition please notify the carrier. We have recorded your warranty which extends for 100 days from the date of shipment. If you have ordered a monitor please fill out the appropriate warranty card and read the accompanying instructions.

When unpacking your ACT-I be sure to find 2 phone plugs and a video connector in the packing material.

If MICRO-TERM can be of any further assistance, please do not hesitate to write or phone.

Happy processing!

Sincerely,

Dave Scharon

President

MICRO-TERM, INC.

DS:nw

#### MICRO-TERM MODEL ACT-I

#### OPERATING INSTRUCTIONS 3-76

| 1. | Your unit has been factory set for:                                      |  |  |  |  |  |  |  |  |  |

|----|--------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|    | a) DATA RATE (baud) 110 300 600                                          |  |  |  |  |  |  |  |  |  |

|    | b) RECEIVER MARK high low                                                |  |  |  |  |  |  |  |  |  |

|    | c) TRANSMITTER MARK high low                                             |  |  |  |  |  |  |  |  |  |

|    | d) LOGIC LEVELS RS232C (-12V, +5V) TTL/CURRENT                           |  |  |  |  |  |  |  |  |  |

|    | e) 8TH BIT                                                               |  |  |  |  |  |  |  |  |  |

|    | If any of the above specifications do not match your processor's serial  |  |  |  |  |  |  |  |  |  |

|    | interface, refer to section 4 to accommodate the ACT-I to you processor. |  |  |  |  |  |  |  |  |  |

#### 2. PRELIMINARY CHECK-OUT

- a) Connect the video output of the ACT-I to the low impedance (75ohm) input of a high quality monitor (5Mhz band pass) which will accept a standard composite video signal. We recommend the use of a high bandwidth monitor such as the units offered by MICRO-TERM so that each dot in the 5 x 7 character matrix can be resolved, lending to a sharp, unambiguous character display. Modified television sets will, in general, display characters which appear slightly smeared in the horizontal direction resulting in a display which may be somewhat more tiring to view, particularly over an extended period of time.

- b) If your unit has the same receiver and transmitter polarity (i.e., both mark high or both mark low), then your ACT-I can be self tested by connecting the serial OUT data from the transmitter directly to the serial IN jack of the receiver. This may be accomplished by electrically connecting the center, "tip", conductor of two phone plugs together with a short length of wire and inserting the plugs into the serial OUT and IN jacks at the rear of the cabinet.

- c) Activate the ACT-I to 110 VAC 60Hz and depress the power switch. The switch should illuminate but the monitor screen should remain clear since the ACT-I automatically enters a "clear screen" mode upon power-up. Now depress any key corresponding to a displayable character. The appropriate character should appear on the screen at the lower left hand corner and an underline cursor will appear at the position for the next character. Adjust the monitor brightness and contrast for comfortable viewing.

- d) The display line should fill horizontally to the right as data is entered from the keyboard. When the 64th character has been entered on a line, the cursor will disappear to its home (lower left corner) position and the entire display will move up one line (i.e., scroll). This same operation, cursor home and scroll is initiated by receipt of the RETURN key code. Note that receipt of the RETURN code initiates the functional equivalent of the operations associated with RETURN and LINEFEED and that LINE FEED codes are ignored. Automatic scrolling when a line fills allows the ACT-I to be used with software which may use a greater than 64 character format without data loss or overwrite. The invisible cursor home position protects the CRT from phosphor burn caused by long term, concentrated illumination often associated with the most common cursor position.

- e) Each time the ACT-I scrolls, the top, 'oldest', line of the 16 lines of display will disappear from the top of the screen. The entire screen may be cleared at any time by depressing the 'PAGE' key. The page key operates on the ACT-I display only; no serial code is sent when this key is depressed.

#### 3. PROCESSOR HOOKUP

a) Two connections are required between the ACT-I and processor, modem etc.: serial out and serial in. Both of these connections are made via phone plugs to be inserted in the appropriate socket at the rear of the ACT-I.

For each phone plug, the center, "tip", conductor must be connected to the "hot" or signal line going into or out of the processor. The signal reference (ground) in each case is the shank conductor. Since the serial in and serial out lines are isolated, the ACT-I operates in full duplex; it can receive and transmit simultaneously. If you are using the current loop interface please refer to 4.1b)-e). Once the phone plugs have been properly connected to the processor serial in and serial out lines and the plugs have been inserted in their appropriate sockets at the rear of the ACT-I, all interconnections are complete.

b) Now bring up your operating system, create a simple program to echo characters or otherwise verify that your processor and the ACT-I are communicating properly. At this point you should be able to put away the instruction manual and enjoy the use of your ACT-I.

#### 4. CHANGING THE ACT-I INTERFACE

a) If you should need to change the ACT-I interface from the factory specifications presented in section1, you will need a small soldering iron, some small guage hookup wire, and rosin core solder. <u>Unplug the ACT-I</u>. Remove 6 Phillips screws from the bottom of the cabinet. Carefully separate the cabinet halves by "hinging" the cabinet top at the back. Do not allow excessive strain on the cables at the rear of the cabinet.

# 4.1 LOGIC LEVELS

a) To change the logic levels from RS232C (-12v + 5 volts) to TTL/current loop (o, +5 volts @ 20ma) or vice versa, locate the word 'OUT' next to a solder pad on the printed circuit board in the upper left hand corner. The jumper from the pad must connect to one of the three nearest pads labeled RS232C, LOOP N or (LOOP) P. For TTL levels connect the jumper to LOOP N. For RS232C compatible levels connect the jumper to the pad

labeled RS232C. If this completes your logic level modification, go to section 4.1 f).

b) For 20ma current loop applications the logic level jumper described in the previous paragraph must be connected to the LOOP N solder pad if the ACT-I transmitter is to supply the current in the loop to your processor or to the (LOOP) P pad if your processor supplies the loop current and the ACT-I is to sink it. It is important that this information be positively determined so that the proper connection can be made. An erroneous connection may cause the two current sources to fight each other and although the output of the ACT-I is fully protected, your processor interface may be harmed. It is also important to note that both the serial out and serial in lines have a common ground. If your interface has its own 20ma current source which requires an isolated return it should not be used. And finally the voltage level of the current loop sourced by your processor should not exceed +12 volts or be negative relative to ground. If your current loop source does not meet these requirements, then the ACT-I current source should be used instead.

The following paragraph illustrates the proper connections to a typical processor interface so that the ACT-I will properly source the loop (LOOP N). Note that it may be necessary to change the ACT-I transmitter polarity if a negative voltage source for the current loop was disabled from your processor interface.

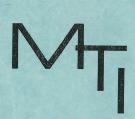

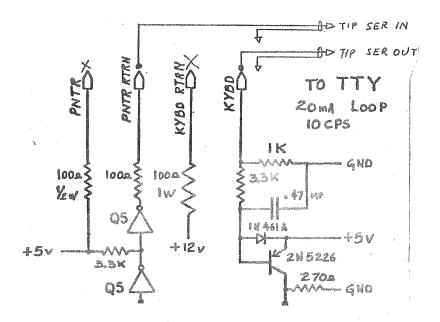

c) Refer to your processor's interface schematic and identify the KEYBOARD and KEYBOARD RETURN lines. Refer to the typical schematic below and note that one of these lines, KYBD RTRN is connected through a resistor to a voltage source.

On your schematic, note which line goes through a resistor to a voltage source. Do not connect this line. Connect the <u>OTHER</u> line to the tip connector of a phone plug. Connect the shaft connector to a convenient ground at your processor interface. Insert the plug into the serial OUT jack at the rear of your ACT-I. Note that the polarity of the data transmitted to your processor has not yet been verified.

- d) Again referring to your processor's interface schematic, find the lines marked PRINTER and PRINTER RETURN. Note that one of these lines goes through a resistor to a voltage source. Do not connect this line. Connect the OTHER line to the tip connector of a phone plug. Connect the shaft connector to a convenient ground at your processor interface. Insert the plug into the serial IN jack at the rear of your ACT-I. This 'loop' should not require polarity verification.

- e) Power up your processor and ACT-I. Have your processor send some known character string out to the ACT-I. The ACT-I should display properly.

Now attempt to prompt your processor from the keyboard of the ACT-I or have your processor echo back the data sent from the ACT-I. If the

expected responses are envoked then the proper polarity is being transmitted from the ACT-I and the current loop connections are complete.

Otherwise the output polarity of the ACT-I must be changed. See 4.2.

f) Upon completion of the logic level modification, carefully reassemble the ACT-I and mark the new specifications in section 1 for future reference. Do not attempt to reassemble the cabinet with the power connected.

#### 4.2 POLARITY

a) Refer to 4. a) before opening the ACT-I cabinet. On the main printed circuit board in the upper center there is a dual operational amplifier in an eight pin package marked CA1558. In the immediate vicinity there are two groups of holes labeled +, 0, -, R to the right and -, +, R, I below. The first group determines the output polarity and the second group determines the input polarity. In each group the + and - holes must be connected to the other two holes. <a href="NEVER">NEVER</a> connect the + hole to the - hole or make any other connections than those indicated in the following table.

|            | Input         | Output        |

|------------|---------------|---------------|

| Mark-low   | - to I + to R | - to 0 + to R |

| Space-high |               |               |

| Mark-high  | - to R + to I | - to R + to 0 |

| Space-low  |               |               |

When the polarity modifications are complete, carefully reassemble the ACT-I and mark the new specifications in section 1 for future reference. Do not attempt to reassemble the cabinet with the ACT-I plugged in.

#### 4.3 DATA RATE SELECTION

Before opening the cabinet refer to 4. a). At the upper left of the main printed circuit board is a semicircle of solder pads and the words "BAUD RATE SELECT". To change the ACT-I baud rate, the jumper which is connected from the pad at the center of the semicircle to one of the labeled pads "110, 300, 600, 1200, 2400, 4800, 9600" must be cut and a jumper should be soldered from the center to the appropriately labeled pad. Carefully reassemble your unit and note the new specification in section 1 for future reference. Be sure that your processor's serial interface is set to operate at the new data rate.

#### 4.4a) UART OPTIONS

Your ACT-I transmits a start bit followed by either 5, 6, 7 or 8 ASCII data bits (depending on the setting of the word select bits), an odd or even parity bit (if parity is enabled) and then either one or two stop bits.

All of these options have default values as follows:

#### DEFAULT UART OPTIONS

# OF DATA BITS 8

8TH BIT LOGICAL 1 (HIGH)

PARITY INHIBITED

# OF STOP BITS 2

# 4.4b) CHANGING THE UART OPTIONS

Should you desire to change any of the default options locate the appropriate directions below. Note that the default values are enabled by narrow "runs" on the printed circuit board. These connections must be broken before adding the necessary jumpers. If these are not cut and a jumper is inserted the +5 volt supply will be shorted to ground and the ACT-I will not function until the run is cut.

1) # OF DATA BITS - To change the number of data bits locate the pads immediately to the left of the UART chip (the only 40 pin IC on the ACT-I

board) which are arranged as per the following sketch:

To change to 7 data bits break the lower connection between N and the pad marked  $^68$  and connect the lower N pad to the pad marked  $^57$ .

To change to 6 data bits break the upper run between N and the  $^78$  pad and connect the upper N pad to the  $^56$  pad.

To change to 5 data bits break both of the default runs between the N pads and the  $^78$  and  $^68$  pads and connect the upper N pad to the  $^56$  pad and the lower N pad to the  $^57$  pad.

2) 8TH BIT - To change the 8th bit from a logical 1 (high level) to a low, cut the run between the B8 pad and the 1 pad and solder a jumper from B8 to 0. These pads are located to the left of the UART chip also.

# 4.5 PARITY

8 other bits. To select this option, locate the solder pad marked "PI", parity inhibit near the upper left corner of the circuit board. The jumper wire must connect this pad to the pad marked "Ī" to enable the parity computation circuitry. Then to select either odd or even parity, the pad labeled "0/E" must be jumpered to either the "0" pad for odd parity or the "E" pad for even parity. Your ACT-I will now transmit an additional parity bit before the stop bit(s) and similarly will expect to receive a parity bit in the serial input data stream which is even or odd as you have selected.

NOTE: When parity is enabled the parity bit is transmitted immediately following the data bits. Hence if you desire to have your ACT-I send and receive one stop bit, seven ASCII data bits, a parity bit and finally, the stop bits, you will have to change the number of data bits from 8 to 7 (see section 4.4b)1.)

#### 4.6 STOP BITS

a) Your ACT-I can transmit and receive 1 or 2 stop bits. This option is selected by connecting the jumper from the pad marked "SB" to either pad marked "1" or "2" immediately to the left. After making any modifications to your ACT-I, carefully reassemble the cabinet while the line cord is disconnected and mark the new specifications in section 1.

#### 5. WARRANTY AND SERVICE

- a) The ACT-I requires no maintenance and should perform faithfully for many years. MICRO-TERM will repair any unit which fails within the original warranty period provided that no modifications have been performed on the circuit, other than the jumper modifications outlined in this manual.

- Beyond the warranty period MICRO-TERM will charge a nominal fee for the repair of any ACT-I. A complete technical manual including schematic, theory of operation and timing diagrams is available to owners of the ACT-I for five dollars. Any further information relating to the operation or interfacing of your ACT-I can be obtained by writing directly to TECHNICAL STAFF, MICRO-TERM INC.

# ACT-I (REV. B) TECHNICAL MANUAL FOR SERIAL #'s 800-949

# TABLE OF CONTENTS

|         |     |                |                                                                                                                                                               | Page                                                                                         |

|---------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| SECTION | I:  | Gene           | eral Overview                                                                                                                                                 | I-1 to I-3                                                                                   |

| SECTION | II: | Оре            | erating Instructions                                                                                                                                          | 11-1                                                                                         |

|         |     | 1) 2) 3) 4)    | Changing the Interface 4.1) Logic Levels 4.2) Polarity 4.3) Data Rate Selection 4.4a) UART Options 4.4b) Changing the UART Options 4.5) Parity 4.6) Stop Bits | II-1<br>II-1<br>II-2<br>II-3<br>II-6<br>II-7<br>II-7<br>II-7<br>II-7<br>II-8<br>II-9<br>II-9 |

| SECTION | III | : I            | nput/Output                                                                                                                                                   | III-1 to III-3                                                                               |

| SECTION | IV: | Mer            | mory                                                                                                                                                          | IV-1                                                                                         |

| SECTION | ۷:  | Memo           | ory Loading                                                                                                                                                   | V-1                                                                                          |

|         |     | 3)             | Character I.D. Displayable Character Processing CR Processing Scroll Operation Page (clear) Operation                                                         | V-1<br>V-1<br>V-4<br>V-7<br>V-8                                                              |

| SECTION | VI: | 0s             | cillators and Control                                                                                                                                         | VI-1                                                                                         |

|         |     | 1)<br>2)<br>3) | 9.828 MHz and Horizontal Oscillator<br>Left Margin Delay and Dot Oscillator Enable<br>Vertical Sync. and Display Enable                                       | VI-1<br>VI-2                                                                                 |

| SECTION | VII | : V            | ideo Display Generation                                                                                                                                       | VII-1 to VII-6                                                                               |

|         |     | ٧              | ideo Combiner and Cursor Generation                                                                                                                           | VII-6                                                                                        |

(continued)

(314) 645-3656

# TABLE OF CONTENTS (cont'd)

|              |                                                                                                                                                                                                                                                                                             | Page                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| SECTION VIII | : Trouble Shooting                                                                                                                                                                                                                                                                          | VIII-1                                                                       |

|              | <ol> <li>Disassembly</li> <li>Equipment</li> <li>Power Supply Test</li> <li>Diagnosis of Main Board Malfunctions         <ul> <li>I/O Test</li> <li>Memory Loading Test</li> <li>Memory Test</li> <li>Display Generation Test</li> </ul> </li> <li>Trouble Symptoms and Remedies</li> </ol> | VIII-1<br>VIII-2<br>VIII-2<br>VIII-3<br>VIII-3<br>VIII-3<br>VIII-3<br>VIII-4 |

| SECTION IX:  | Technical Information                                                                                                                                                                                                                                                                       | IX-1                                                                         |

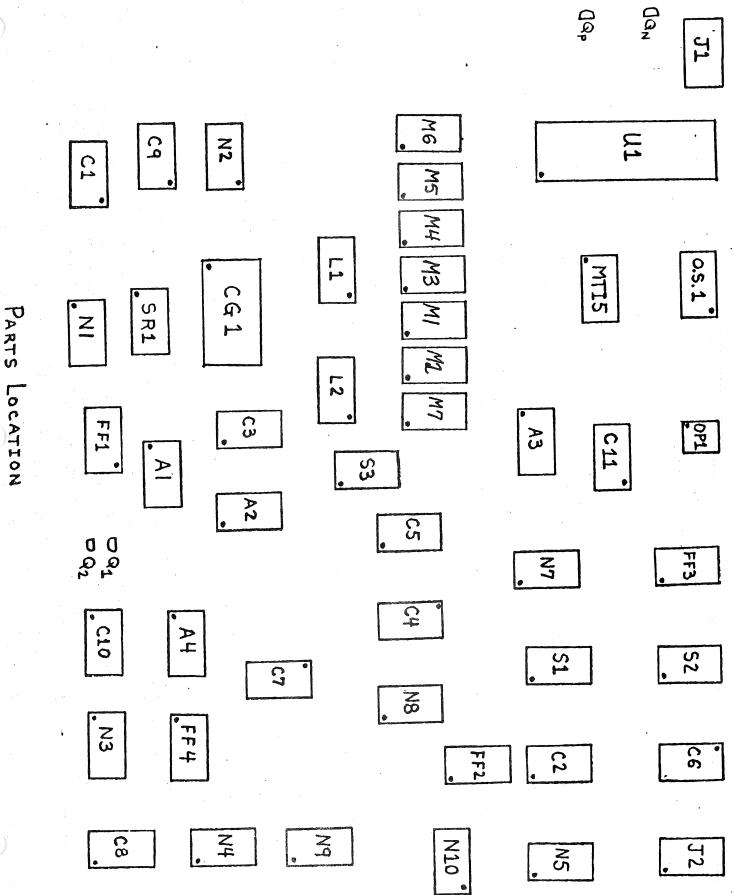

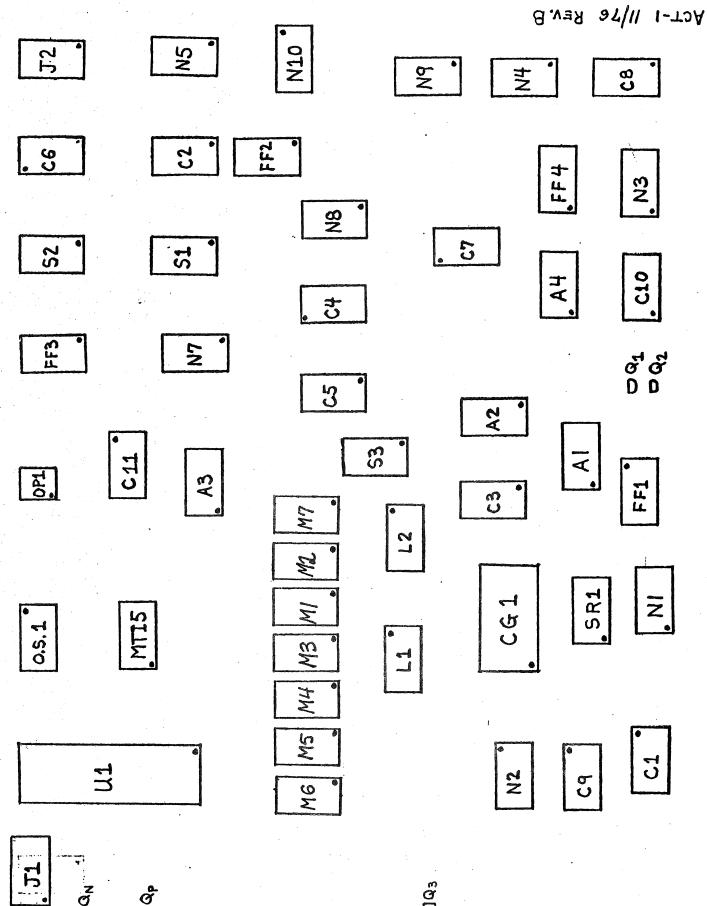

|              | <ol> <li>Table of ASCII Codes</li> <li>Parts Location</li> <li>General Specifications</li> <li>Integrated Circuit Identification and Power Connection</li> <li>Discrete Semiconductors</li> <li>J1 Connector Signals</li> </ol>                                                             | IX-1<br>IX-2<br>IX-3<br>IX-4<br>IX-5<br>IX-5                                 |

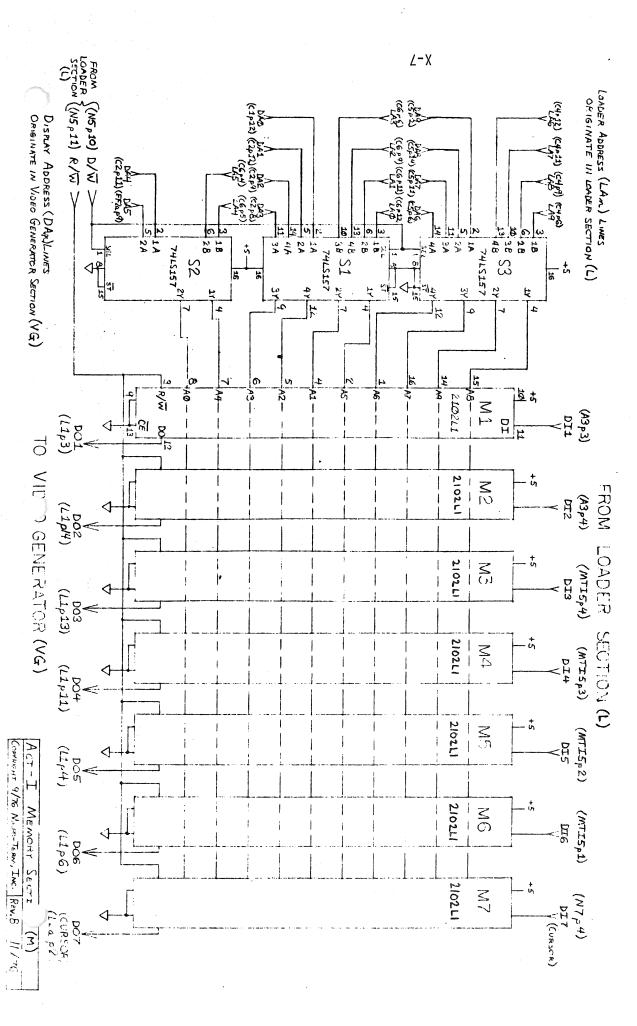

| SECTION X:   | Schematic Diagrams                                                                                                                                                                                                                                                                          | X-1 to X-7                                                                   |

|              | 1) Parts Location 2) Power Supply 3) Memory Loading Section 4) Video Generator 5) Oscillators and Control Section 6) Input/Output Section 7) Memory Section                                                                                                                                 | X-1<br>X-2<br>X-3<br>X-4<br>X-5<br>X-6<br>X-7                                |

# SECTION I: GENERAL OVERVIEW OF THE ACT-I TERMINAL

The ACT-I video terminal is divided into seven major sections:

- 1) Keyboard

- 2) Power Supply

- 3) I/O Section

- 4) Memory

- 5) Memory Loading

- 6) Oscillators and Control

- 7) Video Generator

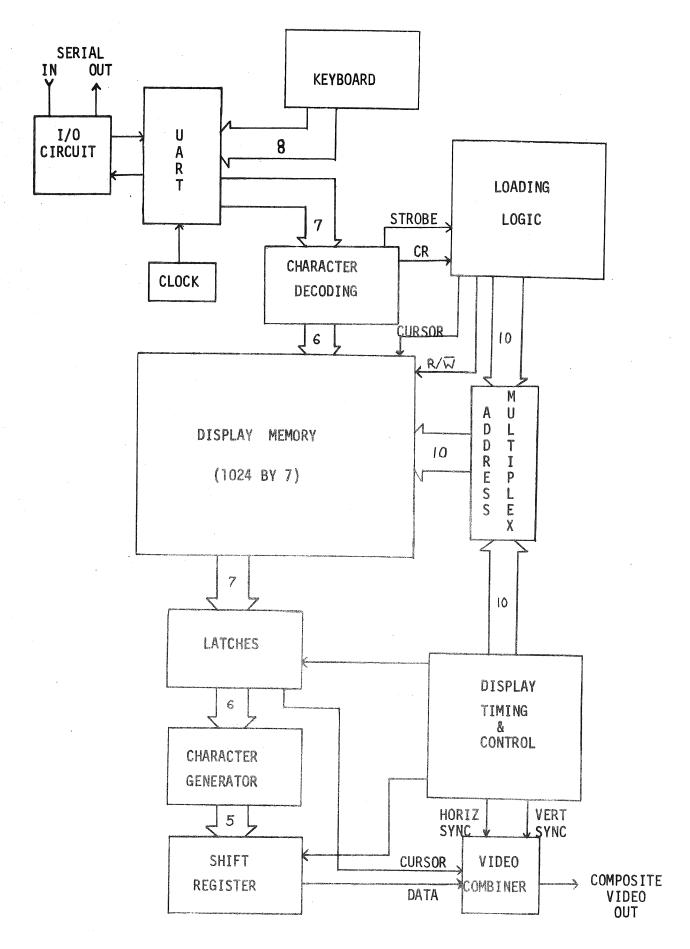

Of these sections, the first two will be described here, while the latter five sections are briefly described here, but have detailed descriptions in sections III, IV, V, VI and VII of this manual. The following summary description of the ACT-I can be better understood by referring to the block diagram in Figure I-1.

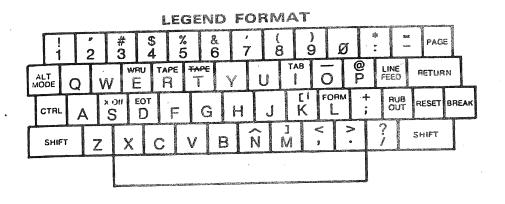

The keyboard is a module (Part #870-4753) made by Cherry Electrical Products Corporation, 3600 Sunset Ave., Waukegan, Illinois 60085. It generates a 7 level ASCII code for the key depressed as illustrated in the following figure, and it also generates a strobe signal to indicate that a key has been depressed. Debouncing is also done in this module. A separate line is used in the ACT-I for the page function. This is sent from the keyboard as a switch closure to ground when the PAGE key is depressed. The reset key is not used by the ACT-I and causes no code to be sent. Depressing the BREAK key forces the ACT-I serial out to the logical 0 (space) state.

FIGURE I-1: ACT-I BLOCK DIAGRAM

#

The keyboard is connected to the ACT-I main circuit board by a ribbon connector (J1), which carries the 7 data bits, the "Key Pressed" signal, the "Page" and "Break" key closures, and +5v and ground. Keyboard information is contained in section IX. J1 also carries serial data and ground between the jacks on the rear of the cabinet and the circuit board.

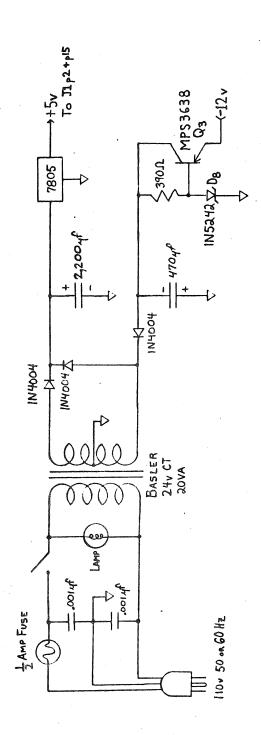

The power supply generates +5v, -12v, and ground from 115vac. The supply is fused with a 1/2 amp fuse, and is switched on by the main power switch located on the top of the case. The transformer is mounted to the bottom of the case, and it provides 24 volts center tapped at 12v with a current rating of 1 amp at 50-60 Hz.

The +5v supply yields about 800MA to drive the ACT-I and the keyboard, while the -12v supply is very lightly loaded, at around 20MA.

The I/O section is responsible for performing all the operations needed to interface RS232C or 20MA current loop serial ACT-I. The serial format used is 8 bit ASCII (with the MSB - Most Significant Bit - jumper selectable by the user) start bit and 2 stop bits. The I/O section receives characters to transmit from the keyboard, and passes received characters to the memory loader section.

The memory loader section of the ACT-I carries out the functions of loading incoming characters into the display memory, translating special characters, and ignoring undisplayable characters, executing carriage return, performing scroll, and executing the screen clear ("Page") operation. It receives characters from

# MICRO-TERM MODEL ACT-I/REV. B

| • | ~ | C1  | PP | ~  |   |       |  |

|---|---|-----|----|----|---|-------|--|

| • | - | , , |    | 11 | м | <br>T |  |

|   |   |     |    |    |   |       |  |

1

# OPERATING INSTRUCTIONS 3-76

| 1. | Your unit has been factory set for:                                        |

|----|----------------------------------------------------------------------------|

|    | a) DATA RATE (baud) 110 300 600                                            |

|    | b) RECEIVER MARK high low                                                  |

|    | c) TRANSMITTER MARK high low                                               |

|    | d) LOGIC LEVELS RS232C (-12V, +5V) TTL/CURRENT                             |

| 5. | e) 8TH BIT high low parity even parity odd                                 |

|    | If any of the above specifications do not match your processor's serial    |

|    | interface, refer to section 4 to accommodate the ACT-I to you processor.   |

|    |                                                                            |

| 2. | PRELIMINARY CHECK-OUT                                                      |

|    | a) Connect the video output of the ACT-I to the low impedance (75ohm) inpu |

|    | of a high quality monitor (5Mhz band pass) which will accept a standard    |

|    |                                                                            |

- ıt composite video signal. We recommend the use of a high bandwidth monitor such as the units offered by MICRO-TERM so that each dot in the 5  $\times$  7 character matrix can be resolved, lending to a sharp, unambiguous character display. Modified television sets will, in general, display characters which appear slightly smeared in the horizontal direction resulting in a display which may be somewhat more tiring to view, particularly over an extended period of time.

- b) If your unit has the same receiver and transmitter polarity (i.e., both mark high or both mark low), then your ACT-I can be self tested by connecting the serial OUT data from the transmitter directly to the serial IN jack of the receiver. This may be accomplished by electrically connecting the center, "tip", conductor of two phone plugs together with a short length of wire and inserting the plugs into the serial OUT and IN jacks at the rear of the cabinet.

- c) Activate the ACT-I to 110 VAC 60Hz and depress the power switch. The switch should illuminate but the monitor screen should remain clear since the ACT-I automatically enters a "clear screen" mode upon power-up. Now depress any key corresponding to a displayable character. The appropriate character should appear on the screen at the lower left hand corner and an underline cursor will appear at the position for the next character. Adjust the monitor brightness and contrast for comfortable viewing.

- d) The display line should fill horizontally to the right as data is entered from the keyboard. When the 64th character has been entered on a line, the cursor will disappear to its home (lower left corner) position and the entire display will move up one line (i.e., scroll). This same operation, cursor home and scroll is initiated by receipt of the RETURN key code. Note that receipt of the RETURN code initiates the functional equivalent of the operations associated with RETURN and LINEFEED and that LINE FEED codes are ignored. Automatic scrolling when a line fills allows the ACT-I to be used with software which may use a greater than 64 character format without data loss or overwrite. The invisible cursor home position protects the CRT from phosphor burn caused by long term, concentrated illumination often associated with the most common cursor position.

- e) Each time the ACT-I scrolls, the top, 'oldest', line of the 16 lines of display will disappear from the top of the screen. The entire screen may be cleared at any time by depressing the 'PAGE' key. The page key operates on the ACT-I display only; no serial code is sent when this key is depressed.

# 3. PROCESSOR HOOKUP

serial out and serial in. Both of these connections are made via phone plugs to be inserted in the appropriate socket at the rear of the ACT-I.

For each phone plug, the center, "tip", conductor must be connected to the "hot" or signal line going into or out of the processor. The signal reference (ground) in each case is the shank conductor. Since the serial in and serial out lines are isolated, the ACT-I operates in full duplex; it can receive and transmit simultaneously. If you are using the current loop interface please refer to 4.1b)-e). Once the phone plugs have been properly connected to the processor serial in and serial out lines and the plugs have been inserted in their appropriate sockets at the rear of the ACT-I, all interconnections are complete.

b) Now bring up your operating system, create a simple program to echo characters or otherwise verify that your processor and the ACT-I are communicating properly. At this point you should be able to put away the instruction manual and enjoy the use of your ACT-I.

# 4. CHANGING THE ACT-I INTERFACE

a) If you should need to change the ACT-I interface from the factory specifications presented in section, you will need a small soldering iron, some small guage hookup wire, and rosin core solder. Unplug the ACT-I. Remove 6 Phillips screws from the bottom of the cabinet. Carefully separate the cabinet halves by "hinging" the cabinet top at the back. Do not allow excessive strain on the cables at the rear of the cabinet.

#### 4.1 LOGIC LEVELS

loop (o, +5 volts @ 20ma) or vice versa, locate the word 'OUT' next to a solder pad on the printed circuit board in the upper left hand corner. The jumper from the pad must connect to one of the three nearest pads labeled RS232C, LOOP N or (LOOP) P. For TTL levels connect the jumper to LOOP N. For RS232C compatible levels connect the jumper to the pad

labeled RS232C. If this completes your logic level modification, go to section 4.1 f).

b) For 20ma current loop applications the logic level jumper described in the previous paragraph must be connected to the LOOP N solder pad if the ACT-I transmitter is to supply the current in the loop to your processor or to the (LOOP) P pad if your processor supplies the loop current and the ACT-I is to sink it. It is important that this information be positively determined so that the proper connection can be made. An erroneous connection may cause the two current sources to fight each other and although the output of the ACT-I is fully protected, your processor interface may be harmed. It is also important to note that both the serial out and serial in lines have a common ground. If your interface has its own 20ma current source which requires an isolated return it should not be used. And finally the voltage level of the current loop sourced by your processor should not exceed +12 volts or be negative relative to ground. If your current loop source does not meet these requirements, then the ACT-I current source should be used instead.

The following paragraph illustrates the proper connections to a typical processor interface so that the ACT-I will properly source the loop (LOOP N). Note that it may be necessary to change the ACT-I transmitter polarity if a negative voltage source for the current loop was disabled from your processor interface.

and KEYBOARD RETURN lines. Refer to the typical schematic below and note that one of these lines, KYBD RTRN is connected through a resistor to a voltage source.

On your schematic, note which line goes through a resistor to a voltage source. Do not connect this line. Connect the OTHER line to the tip connector of a phone plug. Connect the shaft connector to a convenient ground at your processor interface. Insert the plug into the serial OUT jack at the rear of your ACT-I. Note that the polarity of the data transmitted to your processor has not yet been verified.

- d) Again referring to your processor's interface schematic, find the lines marked PRINTER and PRINTER RETURN. Note that one of these lines goes through a resistor to a voltage source. Do not connect this line. Connect the OTHER line to the tip connector of a phone plug. Connect the shaft connector to a convenient ground at your processor interface. Insert the plug into the serial IN jack at the rear of your ACT-I. This 'loop' should not require polarity verification.

- e) Power up your processor and ACT-I. Have your processor send some known character string out to the ACT-I. The ACT-I should display properly.

Now attempt to prompt your processor from the keyboard of the ACT-I or have your processor echo back the data sent from the ACT-I. If the

expected responses are envoked then the proper polarity is being transmitted from the ACT-I and the current loop connections are complete.

Otherwise the output polarity of the ACT-I must be changed. See 4.2.

f) Upon completion of the logic level modification, carefully reassemble the ACT-I and mark the new specifications in section 1 for future reference. Do not attempt to reassemble the cabinet with the power connected.

#### 4.2 POLARITY

Refer to 4. a) before opening the ACT-I cabinet. On the main printed circuit board in the upper center there is a dual operational amplifier in an eight pin package marked CA1558. In the immediate vicinity there are two groups of holes labeled +, 0, -, R to the right and -, +, R, I below. The first group determines the output polarity and the second group determines the input polarity. In each group the + and - holes must be connected to the other two holes. NEVER connect the + hole to the - hole or make any other connections than those indicated in the following table.

|            |       |    | Luput |   |    | Output |     |    |   |      |    |   |

|------------|-------|----|-------|---|----|--------|-----|----|---|------|----|---|

| Mark-low   | teny  | to | I     | + | to | R      | _   | to | 0 | \$   | to | R |

| Space-high |       |    |       |   |    |        |     |    |   |      |    |   |

| Mark-high  | Kined | to | R     | + | to | Ι      | sme | to | R | afe. | to | 0 |

| Space-low  |       |    |       |   |    |        |     |    |   |      |    |   |

When the polarity modifications are complete, carefully reassemble the ACT-I and mark the new specifications in section 1 for future reference. Do not attempt to reassemble the cabinet with the ACT-I plugged in.

#### 4.3 DATA RATE SELECTION

a) Before opening the cabinet refer to 4. a). At the upper left of the main printed circuit board is a semicircle of solder pads and the words "BAUD RATE SELECT". To change the ACT-I baud rate, the jumper which is connected from the pad at the center of the semicircle to one of the labeled pads "110, 300, 600, 1200, 2400, 4800, 9600" must be cut and a jumper should be soldered from the center to the appropriately labeled pad. Carefully reassemble your unit and note the new specification in section 1 for future reference. Be sure that your processor's serial interface is set to operate at the new data rate.

#### 4.4a) UART OPTIONS

Your ACT-I transmits a start bit followed by either 5, 6, 7 or 8 ASCII data bits (depending on the setting of the word select bits), an odd or even parity bit (if parity is enabled) and then either one or two stop bits.

All of these options have default values as follows:

# DEFAULT UART OPTIONS

# OF DATA BITS 8

8TH BIT LOGICAL 1 (HIGH)

PARITY INHIBITED

# OF STOP BITS 2

#### 4.4b) CHANGING THE UART OPTIONS

Should you desire to change any of the default options locate the appropriate directions below. Note that the default values are enabled by narrow "runs" on the printed circuit board. These connections must be broken before adding the necessary jumpers. If these are not cut and a jumper is inserted the +5 volt supply will be shorted to ground and the ACT-I will not function until the run is cut.

1) # OF DATA BITS - To change the number of data bits locate the pads immediately to the left of the UART chip (the only 40 pin IC on the ACT-I

board) which are arranged as per the following sketch:

To change to 7 data bits break the lower connection between N and the pad marked  $^68$  and connect the lower N pad to the pad marked  $^57$ .

To change to 6 data bits break the upper run between N and the  $^78$  pad and connect the upper N pad to the  $^56$  pad.

To change to 5 data bits break both of the default runs between the N pads and the  $^78$  and  $^68$  pads and connect the upper N pad to the  $^56$  pad and the lower N pad to the  $^57$  pad.

2) 8TH BIT - To change the 8th bit from a logical 1 (high level) to a low, cut the run between the B8 pad and the 1 pad and solder a jumper from B8 to 0. These pads are located to the left of the UART chip also.

# 4.5 PARITY

8 other bits. To select this option, locate the solder pad marked "PI", parity inhibit near the upper left corner of the circuit board. The jumper wire must connect this pad to the pad marked "Ī" to enable the parity computation circuitry. Then to select either odd or even parity, the pad labeled "0/E" must be jumpered to either the "0" pad for odd parity or the "E" pad for even parity. Your ACT-I will now transmit an additional parity bit before the stop bit(s) and similarly will expect to receive a parity bit in the serial input data stream which is even or odd as you have selected.

NOTE: When parity is enabled the parity bit is transmitted immediately following the data bits. Hence if you desire to have your ACT-I send and receive one stop bit, seven ASCII data bits, a parity bit and finally, the stop bits, you will have to change the number of data bits from 8 to 7 (see section 4.4b)1.)

#### 4.6 STOP BITS

a) Your ACT-I can transmit and receive 1 or 2 stop bits. This option is selected by connecting the jumper from the pad marked "SB" to either pad marked "1" or "2" immediately to the left. After making any modifications to your ACT-I, carefully reassemble the cabinet while the line cord is disconnected and mark the new specifications in section 1.

#### 5. WARRANTY AND SERVICE

- a) The ACT-I requires no maintenance and should perform faithfully for many years. MICRO-TERM will repair any unit which fails within the original warranty period provided that no modifications have been performed on the circuit, other than the jumper modifications outlined in this manual.

- b) Beyond the warranty period MICRO-TERM will charge a nominal fee for the repair of any ACT-I. A complete technical manual including schematic, theory of operation and timing diagrams is available to owners of the ACT-I for five dollars. Any further information relating to the operation or interfacing of your ACT-I can be obtained by writing directly to TECHNICAL STAFF, MICRO-TERM INC.

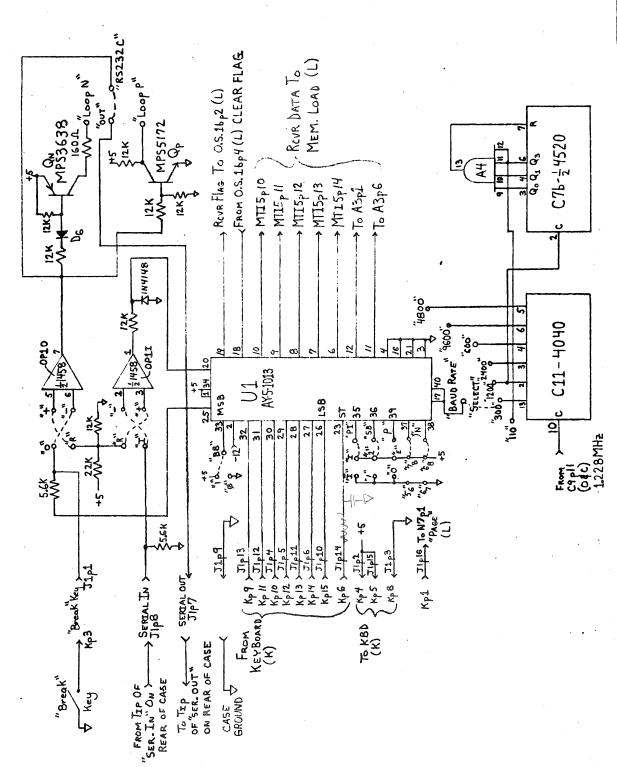

# SECTION III: 1/0:

The I/O circuitry of the ACT-I terminal is responsible for the translation between parallel ASCII format and RS-232C or 20MA current loop serial ASCII format. For your convenience a table of the ASCII codes is included in section IX.

The I/O section is also responsible for the generation of the strobe signal to activate the loading section of the terminal upon receipt of a character on the serial in line. The ACT-I operates in full-duplex mode.

Line driving for the serial out line is accomplished by OP10 (for RS232C). or either the MPS5172 transistor ("Loop P"), or the MPS3638 transistor ("Loop N"). OPII performs the input interfacing. The serial input jack is fed to the "I" pad near OP1 on the board. This pin is jumpered to either the "+" or "-" pads on the board nearby. The "R" pin provides a reference voltage from a 22K/12K voltage divider across the +5v supply, giving a 1.5v reference level. This "R" pin is jumpered to the "+" or "-" pad, whichever is not connected to "I". The default connections are for "I" to be connected to "-", and for "R" to be connected to "+". This is standard for an RS232C interface. The "+" and "-" pads on the board are connected to the + and - inputs of OPII, which functions as a comparator to detect the "Mark" and "Space" states of the input line. OPII's output is connected through a 12K resistor to pin 20 of UART Ul, the serial input pin. This line is also tied to D5, which prevents the line from excursions below ground to the OP amp negative supply voltage, so that pin 20 of Ul sees a TTL signal (the positive supply to OP1 is =5v, so the positive excursion of the signal is about 5v).

The serial output starts at pin 25 of the UART, its serial out pin, and runs to the pad marked "O" on the board. This pad is jumpered to either the "+" or "-" pads near it, depending on the polarity of the output signal needed. Default

is "-". The other polarity pin should be jumpered to the nearby "R" pad, which is the same 1.5v reference signal used by the serial input detector. Default is for "R" to be jumpered to "+". The "+" and "-" pads feed into the + and - inputs of OP10, which produces at its output (pin 7) an RS232C signal with the high state at about +5v, and the low state at about -12v. This signal appears at the pad labeled "RS232C" on the power supply board, and the serial output jack is connected to it as a default. The "Break" key is connected through a 5.6k resistor to the pad marked "0". When the "Break" key is depressed it pulls pad "0" low and forces the output of OP10 to the logical 0 (space) state (+5v).

The RS232C signal drives transistors  $Q_N$  and  $Q_P$  to generate 20ma current loop outputs.  $Q_N$  is capable of sourcing 20ma of current into a load which has its common side at ground potential. D6 insures that OP10's positive output can cutoff  $Q_N$ .  $Q_N$  sources current (mark state) when the RS232C signal is low (mark state), so no polarity inversion at OP10 is needed when the "Loop N" output is selected.  $Q_P$  is capable of sinking current (mark state) to ground when the RS232C signal is high (space state). Hence, when the "Loop P" output is selected, OP10 should have its "+" input jumpered to the "0" pad and its "-" input jumpered to the "R" pad.

The UART (Universal Asynchronous Receiver/Transmitter), U1, performs all parallel/serial and serial/parallel conversions. The UART requires a frequency reference of 16 times the desired baud rate. This is supplied by the UART clock divide down chain -- Cll and C76, which is driven by a 1.228MHz clock from C9 in the oscillator and control circuit. Baud rate selection is made by connecting a jumper from Ulp17,40 to the desired clock rate signal. For instructions on how to change the data rate refer to section II-4.3 of this manual.

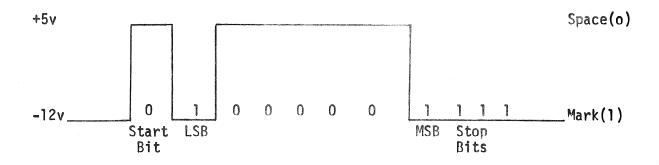

The transmit section of the UART takes the data from the keyboard when "STROBE" occurs at pin 23. This data is latched in from pins 26 through 33, and is converted to serial format and clocked out the serial output pin (pin 25). Pin 33, the MSB

of data, is not supplied from the keyboard, but is set by the "8th Bit" jumper, which connects Ul pin 33 to either +5v or ground. Default is to tie the 8th bit high. If a zero 8th bit is desired, jumper pin 33 to ground. The following figure shows the ACT-I serial out waveform that should appear at the serial out jack for transmitting the letter A (ASCII code = 1000001) in RS232C format.

The receiver section of the UART is responsible for detecting incoming characters on the serial input line to the ACT-I and passing them to the loader section. The UART waits for a start bit on the serial input (pin 20), and when it gets one, it assembles an 8 bit character, and looks for a stop bit. When the stop bit is detected, the UART raises a flag signal at pin 19 to indicate that it has a character ready. This signal triggers the start of the loading sequence as described in the memory loading section.

# SECTION IV: MEMORY

The ACT-I internal refresh memory is organized as 1024 seven-bit words (characters). There are six bits of ASCII data and a cursor bit. The ASCII data is stored in M1 (Least Significant Bit) through M6 (Most Significant Bit). The cursor bit is stored in M7.

When in the display mode, (no characters being loaded) the ten memory address lines (AØ through A9) are driven by the display address lines (DAØ through DA9) by virtue of the multiplex control line  $(D/\overline{W})$  at S1 through S3pl being high to select the display address lines. The data in lines at M1 through M5pl1 and M7pl1 are held low and M6pl1 is held high to force the ASCII space code and a low cursor bit on the input data lines (DI1 through DI7). The data output lines D01 through D07 drive the latches in the video generator circuit (section VII).

When in the load mode M1 through M7p3 (Read/Write-"R/W") and the multiplex control line at S1-S3p1 (Display/Write-"D/W") is pulsed low to allow the load address lines (LAØ through LA9) to address the memory. When loading characters into memory, the data in lines, DII through DI6 (M1-M6p11), have the ASCII data and M7p11 (cursor bit in) is held high.

For a detailed description of memory loading refer to section V of this manual.

# SECTION V: MEMORY LOADING

This section describes:

- 1) Character identification

- 2) Loading of displayable characters to memory

- 3) Carriage Return (CR) processing

- 4) Auto clear and PAGE function

The following components are responsible for performing the above three functions:

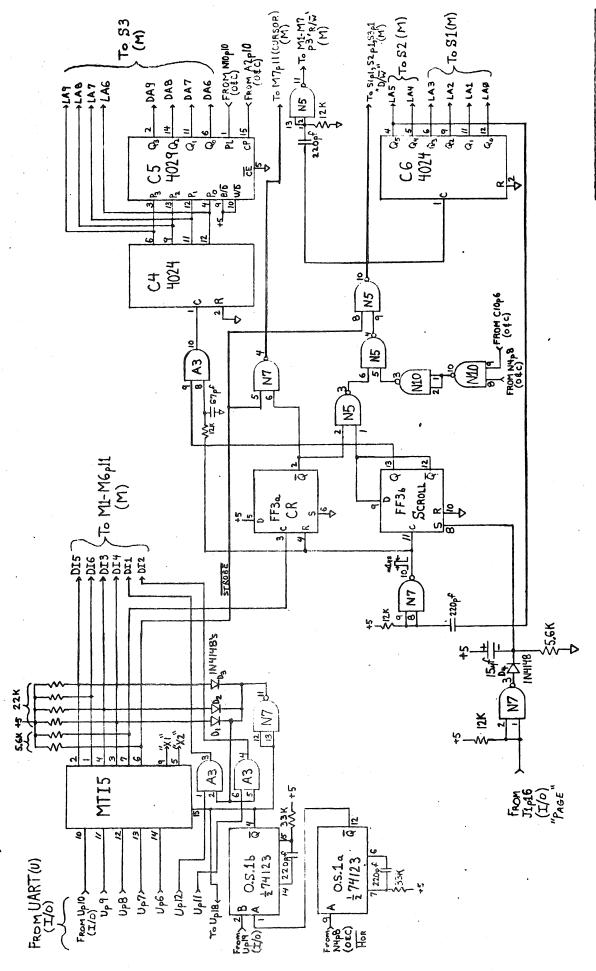

A3, N7, MTI5, FF3, N10, N5, C4, C5, C6, OS1 and M1-M7.

# V-I: CHARACTER IDENTIFICATION

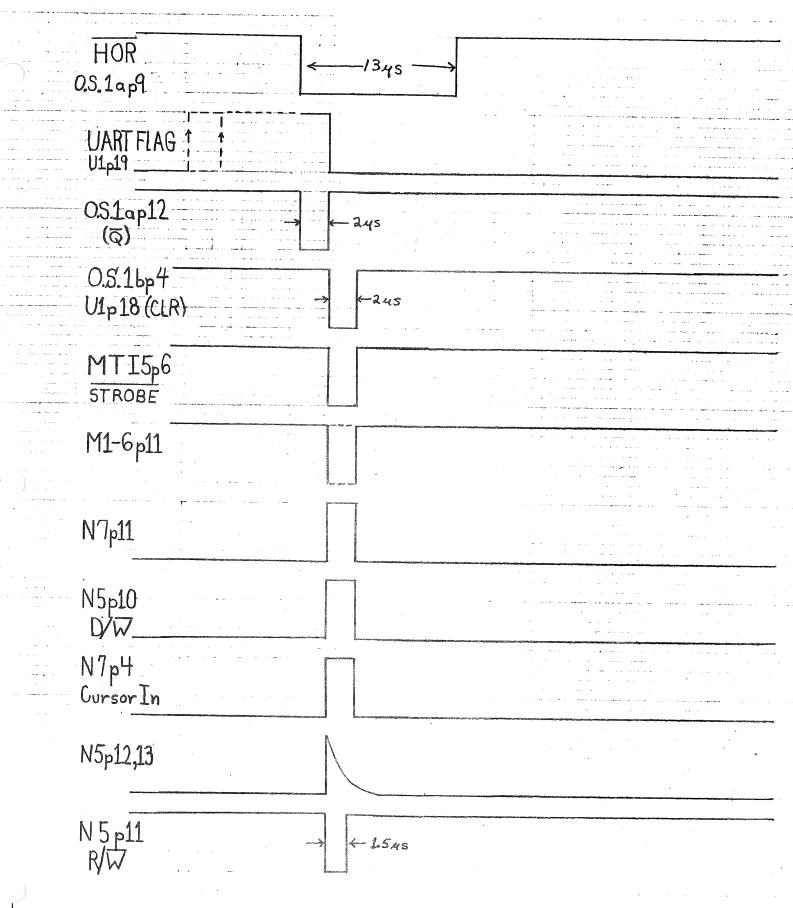

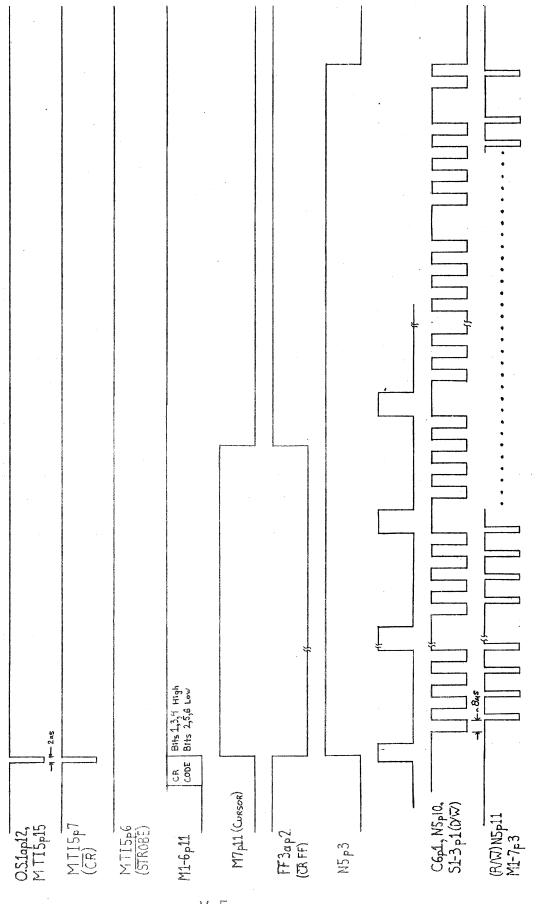

Character processing is initiated when the UART flag (Ulp19) which is applied to OS1bp2 goes high to indicate receiption of a character\*. On the next horizontal retrace pulse  $\overline{\text{HOR}}$  goes low and OS1a is triggered and  $\overline{\mathbb{Q}}$  pin 12 goes low for 2us and is applied to OS1bp1. Since OS1bp2 is high, OS1b fires and OS1bp4 goes low for 2us pulls N7p12, 13 and MTI5p15 low, and resets the UART flag by pulling Ulp18 low. The most significant 5 bits (5 MSB's) of the ASCII character code are tied to pins 10 through 14 of MTI5 and the 2 LSB's (Least Significant Bits) are tied to A3p1 and A3p6. MTI5 decodes the 5 MSB's to detect if the character is a displayable or control character.

# V-2: DISPLAYABLE CHARACTER PROCESSING

If the received character is displayable MTI5 produces a STROBE pulse at pin 6 for the duration of OSlb's pulse (2us). ASCII data for the character is available during the same 2us interval as follows:

BIT #

1(LSB) at A3p3 and M1p11

2 at A3p4 and M2p11

3 at MTI5p4 and M3p11

\*Please refer to Figure V-1.

4 at MTI5p3 and M4p11 5 at MTI5p2 and M5p11 6 at MTI5p1 and M6p11

When a lower case alphabetic character code is received MTI5 and A3 produce the corresponding upper case code. The ASCII code set is given in section IX of this manual.

Since N5p9 is high N5p10 goes high when STROBE falls (MTI5p6). The high level from N5p10 is applied to pin 1 of S1, S2 and S3 (the select line of the multiplexers for the 10 address lines to M1 through M7). This causes the three switches S1, S2 and S3 to allow C4 and C6 to address the memory. C4 holds the 4 bit address of the row that is presently being loaded (LA6 - LA9). C6 has the 6 bit address of the column into which the present character is to be loaded (LAØ - LA5).

The rising edge of N5p10 is capacitively coupled into N5p12, 13. The capacitive coupling causes a 1.5us  $R/\overline{W}$  (read/write) pulse at N5p11 which drives the  $R/\overline{W}$  lines (p3) of M1 through M7. Hence the character is loaded into memory 1.5us after the UART flag and  $\overline{HOR}$  coincide at OS1b.

The rising edge of STROBE (MTI5p6) causes a falling edge at N5p10, C6p1 and S1, S2, and S3p1. This falling edge increments C6 and returns control of the RAM address lines to the display circuitry.

Whenever a displayable character is loaded the CR flip-flop FF3a is clear and hence FF3ap2  $(\overline{0})$  and N7p6 are high causing the  $\overline{\text{STROBE}}$  applied at N7p5 to be inverted and raise M7p11 (cursor bit into memory) and load a l into the cursor bit for the position which is being filled.

When a character is loaded into the 64th column a scroll operation is initiated by virtue of the falling edge of the MSB of C6p4 (due to overflow) being capacitively coupled to N7p8, 9 inverted and applied to the clock line of FF3b (Scroll FF). Since FF3bp12  $(\overline{0})$  is tied to FF3bp9 (D) FF3b toggles. It was previously clear so it now (upon loading of the 64th column) is set and starts

FIG. V-I: Timing Diagram For Character Loading (not 64th Char.)

V**-**3

the scroll operation which is described in section V-4.

# V-3: CR PROCESSING

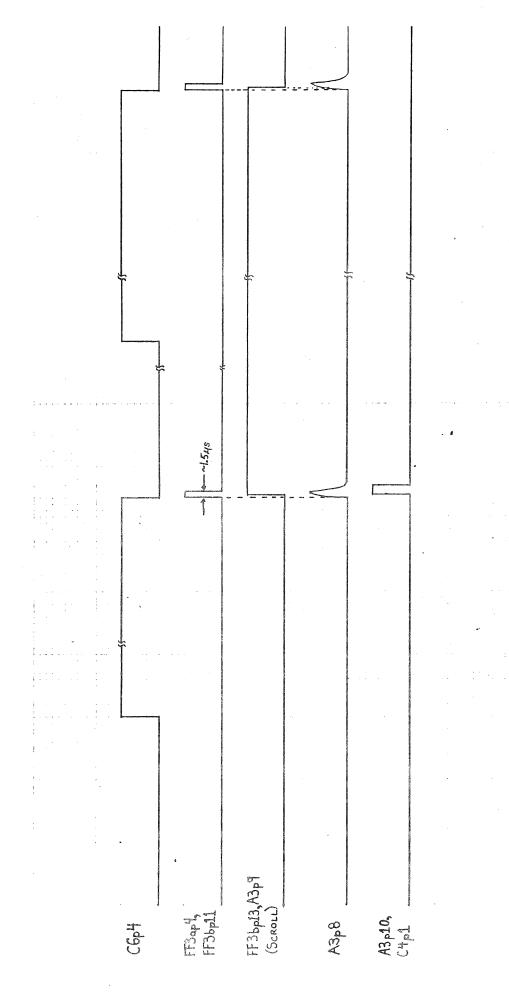

When A CR (Code OD Hex) is received by the UART MTI5 produces a 2usec low pulse at pin 7 ( $\overline{CR}$ ) which is applied to FF3ap3 (clock input of CR FF). Please refer to Fig. V-2. When the  $\overline{CR}$  line rises the CR FF is set (since FF3ap5 (D) is tied high) and FF3ap2 ( $\overline{Q}$ ) falls -- initiating the CR process.

Since MTI5 decodes only the 5 MSB's of the ASCII character code it produces a  $\overline{CR}$  pulse for four ASCII codes; i.e., OC-Form Feed; OC-CR: OE-SO and OF-SI.

To perform the CR function first the present row is filled with spaces and high cursor bits; then the pointer to the top row of the display (C4) has to be incremented modulo 16 and finally the bottom row of the display has to be erased. These last two actions comprise a scroll operation which is described in section V-4.

The low level at FF3ap2 is applied to N7p6 and N5p2 causing N7p4 to rise -setting the cursor bit to memory high and forcing N5p3 and N5p6 high. The high

at N5p6 enables a pulse train out of N5p4 as indicated in Fig. V-2.

Since N5p6 and N5p8 are high the pulse train from N10p3 is inverted twice and applied to C6p1, S1, S2 and S3p1. The rising edge at N5p10 is capacitively coupled to N5p12, 13 to produce a 1.5us negative going  $R/\overline{W}$  pulse at N5p11 and M1-M7p3.

N7p4 is high (cursor data in) and OSlbp4  $(\overline{0})$  is high so N7p13, 12 and MTI5p15 are high and N7pl1 and A3p2, 5 are low resulting in diodes D1-D3 being turned on and memory data lines 1(LSB) through 5 (at N3p3, N3p4, MTI5p4, MTI5p3 and MTI5p2) forced low while memory data lines 6 (MSB) and 7 (Cursor) are held high. This insures that for each pulse in the train a space is written into memory with the cursor bit high to indicate the position has been filled.

FIGURE V-2: TIMING DIAGRAM FOR CR OPERATION (SHEET 1 OF 2)

FIG. Y-2 (CONT.) (SHEET 2 0F2)

V-6

The falling edge of pulses in the train applied to C6p1 causes C6 to increment each time a space is written into memory. When the 64th column is loaded C6 overflows and its MSB (C6p4) falls. The falling edge is capacitively coupled to N7p8, 9 and generates a positive going 1.5us pulse at N7p10, FF3bp11, FF3ap4 and at the 12K resistor which is connected to A3p8.

The rising pulse resets the CR flip-flop (FF3a), toggles FF3b and charges the capacitor tied to A3p8 through a 12K resistor. When the voltage on the capacitor reaches about 2.5 volts A3p10 goes high since A3p9 is high as a result of FF3b being recently toggled into the set state (indicating that a scroll operation is to be executed). A3p10 produces a 500ns positive pulse which is applied to C4p1 (Row counter) and increments C4 modulo 16. A scroll operation is performed next.

# V-4: SCROLL OPERATION

The scroll state (indicated by FF3bpl2 going low) is entered to complete the CR operation. FF3bpl2 (Scroll) is low and applied to N5pl. FF3ap2 ( $\overline{CR}$ ) and N5p2 are now high so N5p3 remains high and the pulse train continues to pass through N5p4.

When the scroll state is entered as the result of C6 overflowing while loading displayable characters (see last paragraph of section V-2), FF3bpl2 ( $\overline{\text{Scroll}}$ ) and N5pl go low, FF3ap2 ( $\overline{\text{CR}}$ ) and N5pl are high so N5p3 goes high and allows N5p4 to produce its pulse train which is used to clear the old top row of the display.

Regardless of how the scroll state is entered, the high level at N5p3 enables a pulse train at N5p4 which is inverted once at N5p10 (since N5p6 is high -- STROBE). These pulses are used to write spaces and <u>low</u> cursor bits into the new bottom row of the display in exactly the same manner as they are used to write spaces and <u>high</u> cursor bits into the memory for filling a row which has

been terminated by a CR. Refer to Section V-3 for the details of how the new bottom row is cleared.

When the memory location corresponding to the last (64th) column in the bottom (16th) row is cleared C6 overflows and the falling edge of C4p4 is capacitively coupled to N7p8, 9 causing a 1.5usec positive going pulse at N7p10, FF3ap4 and FF3bp11. The rising edge of this pulse toggles FF3b into the reset state causing FF3bp12 (Scroll) to rise forcing N5p3 and N5p6 low. The low level at N5p6 prevents any more pulses writing extra spaces into memory and incrementing C6.

The 1.5us positive pulse appearing at N7p10 starts charging the 67pf capacitor tied to A3p8 through a 12K resistor while FF3bp13 (Scroll) is high for about 100nsec after N7p10 rises (due to the propagation delay through FF3b). It takes approximately 500nsec for A3p8 to achieve a logical 1 state (2.5 volts or more) and by then FF3bp13 and A3p9 have fallen so no extraneous count pulses are sent through A3-10 to C4 (Row pointer).

#### V-5: CLEAR (PAGE) OPERATION

The ACT-I screen clear function can be activated in two ways: 1) during the power-on sequence; and 2) by depressing the PAGE key on the ACT-I keyboard.

Automatic screen clear upon power-up is accomplished by coupling the rising +5 volt power supply through a 15uf capacitor to the set input of the scroll flip-flop (FF3b). The set input (FF3bp8) also has a 5.6K resistor tied to ground, and the cathode of D4 whose anode is connected to N7p3. The 5.6K resistor discharges the 15uf capacitor causing the set input to fall after approximately 50 milliseconds.

Depressing the PAGE key pulls N7pl, 2 low and forces N7p3 and FF3bp8 (set) high. Hence the Scroll flip-flop is set for the duration that the PAGE key is depressed.

Holding FF3b in the set state causes the memory loading circuit to scroll repeatedly. Hence, all display memory positions are loaded with the ASCII space code and a low cursor bit. It takes only 40 milliseconds to clear the ACT-I screen.

If the PAGE key is depressed while characters are being received by the UART a clear screen will not always result since the clear and load functions were not designed to operate concurrently.

Programming Hint: In order to clear the ACT-I screen under program control (as opposed to manually depressing the PAGE key), a sequence of 16 carriage returns should be sent from the computer.

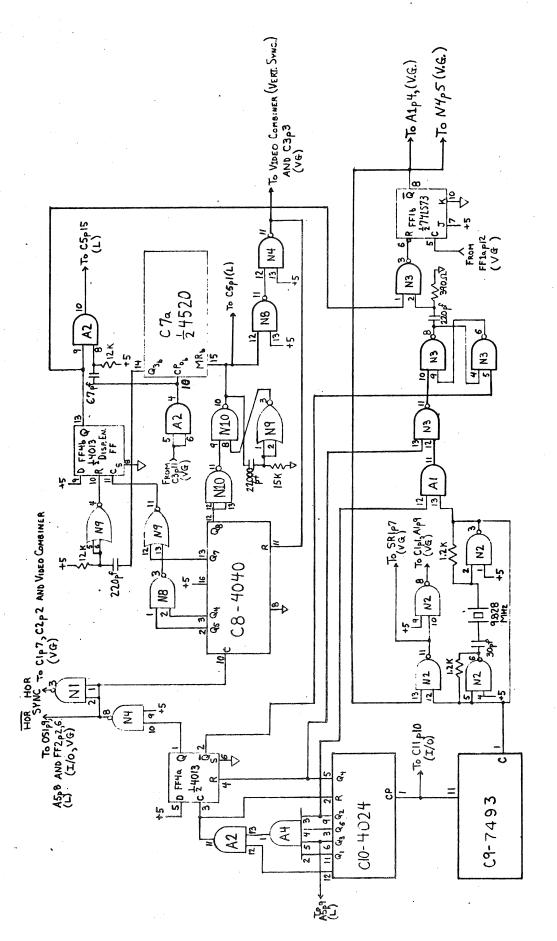

#### SECTION VI: OSCILLATORS AND CONTROL

The oscillators and control section (0 & C) of the ACT-I is responsible for generating all timing clocks and control signals. The following components are used to produce these:

N1, N2, N3, N4, N8, N9, N10, A1, A2, A4, C7a, C8, C9, C10, FF1b, FF4a,b.

### VI-1: 9.828MHz AND HORIZONTAL OSCILLATORS

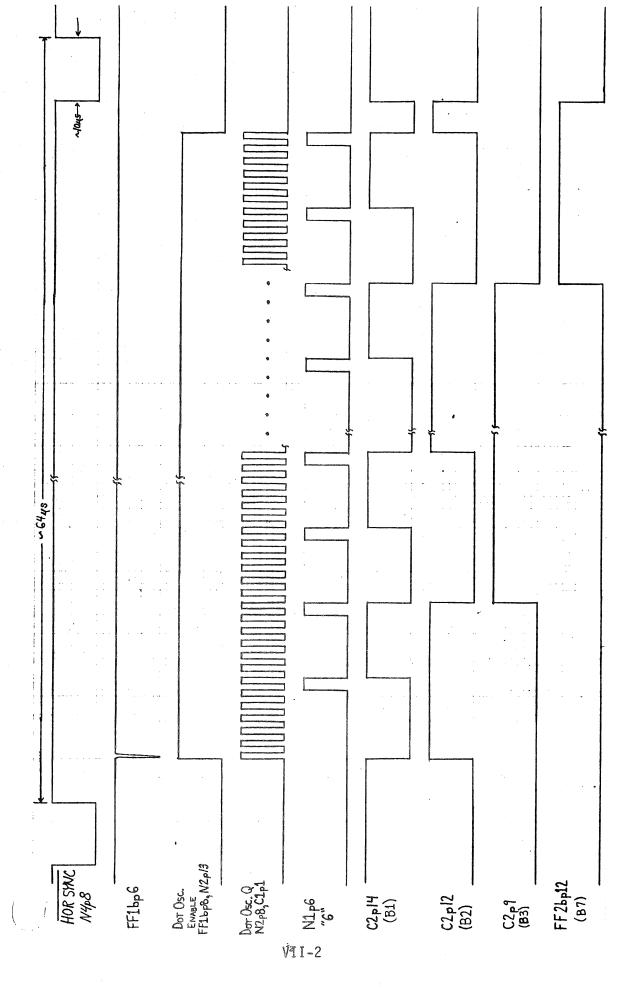

All timing signals in the ACT-I are derived from a master, crystal-controlled, 9.828 Megahertz, oscillator. The output of this oscillator at N2p3 drives a divide-by-eight counter, C9, and also feeds N2p12 and Alp13. When N2p13 is high due to FFlb (Dot oscillator enable) being in the reset state, the 9.828MHz square wave is gated through N2p11 to produce shift pulses for SR1. The inverted 9.828 MHz signal (N2p8) is applied to Clp1 and Alp9 in the video generator (VG) circuit.

The 1.2285 MHz output of C9 drives the UART count down chain in the input/output section (I/O) and also provides the count in pulses for C10 which is a divide-by-79 counter. The divide-by-79 is accomplished by "anding" the  $\Omega_0$  (1-C10p12),  $\Omega_1$  (2-C10p11),  $\Omega_2$  (4-C10p9),  $\Omega_3$  (8-C10p6) and  $\Omega_6$  (64-C10p3) to generate the reset input to C10 at A2p11. This output is high for the duration of the reset propagation delay of C10 (about 100ns). The short positive pulse at A2p11 sets FF4a (Horizontal sync) by clocking it with the D input tied high. This short pulse occurs every 64.3 microseconds (15.550KHz). When C10 reaches a count of 16 (13us after being reset)  $\Omega_4$  (C10p5) goes high and resets the horizontal sync flip-flop (FF4a). Hence the duration of the buffered Hor. sync and Hor. sync at N4p8 and N1p3 respectively is 13us.

#### VI-2: LEFT MARGIN DELAY AND DOT OSCILLATOR ENABLE

$\Omega_4$  of C10 (p5) is also applied to N3p13 to digitally control the left margin position. When  $\Omega_4$  and  $\Omega_2$  of C10 both are high (20 counts after the

reset of C10 and 4 counts after the end of the horizontal sync pulse) N3pll falls and forces N3p8 high. The rising edge at N3p8 is coupled through a 220pf capacitor to N3p2. If the vertical position of the beam is in the display area (horizontal scan lines 48 through 208), the Display Enable flip-flop (FF4b) will be set and N3pl will be high so the positive pulse at N3p2 is inverted and causes FF1b to reset. When FF1b resets its  $\overline{Q}$  output (pin 8) rises and allows the 9.828MHz dot oscillator to drive the shift register SR1 and the dot counter (C1). The output of the dot oscillator enable flip-flop (FF1bp8) is gated with the cursor data to the video combiner to prevent the cursor from being displayed outside of the display area.

$\Omega_3$  of C10 is used to increment C6 during the carriage return and scroll operations as explained section V.

#### VI-3: VERTICAL SYNC. AND DISPLAY ENABLE

The buffered horizontal sync pulses at N4p8 provide the increment signal to C8 which is a nine bit binary counter (C8 is a modulo 256 counter). C8 is held in the zero state for the duration of the vertical sync pulse which appears at N4p11. When C8 reaches a count of 48 scan lines both the  $O_4$  (16-C8p3) and  $O_5$  (32-C8p2) are high and N8p3 falls. Since  $O_7$  of C8 (128-C8p13) is low,N9p11 rises and causes FF4b (Display Enable FF) to set. FF4bp13 (O), N3p1, A2p9 and A2p10 rise accordingly. A2p10 is tied to the count-in line of C5. FF4b remains set until C7a reaches a count of 16 when the sixteenth row of characters finishes being displayed.

C7a is incremented each time the divide-by-ten displayable scan line counter (C3) resets. At the same instants positive going pulses are produced at A2-10 to increment C5.

When C8 reaches a count of 256 scan lines (Q8 (256-C8pl2) and N1Opl2, 13 go high; N1Opl1 and N1Op9 fall, forcing N1Opl0 high. The 22Opf capacitor tied

between N10p10 and N9p1, 2 forces N9p1, 2 high and N9p3 and N10p8 low. The duration of the vertial sync pulse at N10p10, N8p12 and N4p11 is determined by the resistor-capacitor time constant of the components tied to N9p1, 2. A .022uf capacitor and a 15K resistor yields a 220us duration. The duration of the vertical sync pulse is critical since it determines the vertical sync rate by holding C8 in a reset state. In order to get a 60Hz vertical sync rate C8 must act as a divide-by-259 counter. This is achieved by setting the duration of the vertical sync pulse equal to  $3.5 \times 64 \text{us} = 220 \text{us}$ . With this duration the vertical sync pulse falls mid-way between the 259th and 260th horizontal sync pulses. The vertical sync pulse is buffered at N4p11.

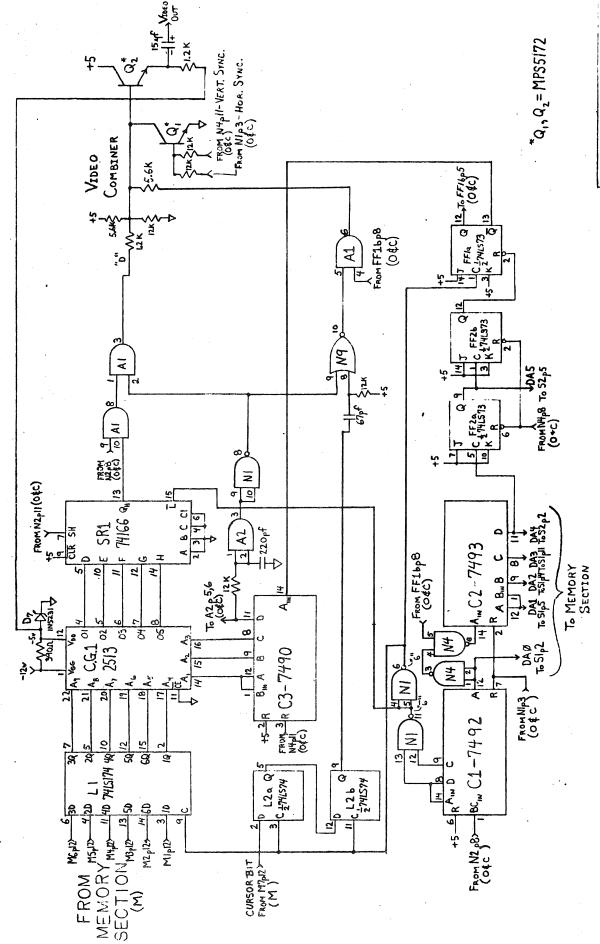

## SECTION VII: VIDEO DISPLAY GENERATION

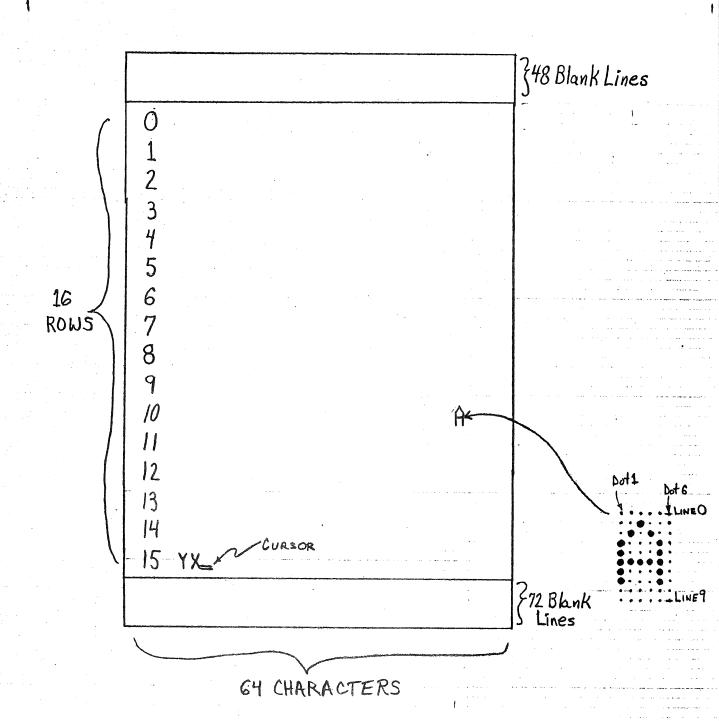

The most complex circuit in the ACT-I is the display generation circuit. It is responsible for fetching characters from memory and generating the character and cursor data for the composite video output signal.

The description of this complicated circuit will start with the vertical retrace pulse and proceed as the beam travels from the top to the bottom of the video frame. The following components are used to generate the display: N1, N9, A1, A2, C1-C3, FF1, FF2, L1, L2, CG1, SR1, O1 and O2.

In order to enhance your understanding of the display circuitry's operation refer to Figures VII-1, VII-2 and VII-3.

At the top of the screen the vertical sync pulse has just completed and cleared C7a (# of character rows displayed), C3 (Modulo 10 scan line counter to address the character generator chip) C8 (# of horizontal scan lines), and jammed the contents of C4 (pointer to bottom row of characters in memory) into C5 (character row address).

Forty-eight horizontal scan lines later C5pl5 rises causing C5 to increment modulo 16. Hence the count in C5 changes from the address of the last row of characters (which was loaded into it by the vertical sync pulse at C5pl) to the address of the first row of characters to be displayed. The Disp. En. FF is set in coincidence with the end of the horizontal sync pulse since C8 counts on the rising edge of Hor sync.

The trailing edge of the Hor sync is or-ed with Clp12 (LSB of character column counter) to produce the count in signal for C2 (which holds the second, third, fourth and fifth bits of the 6 bit character column address). Hence at the start of the first displayable scan line (line 48) and at all other scan lines from 48 to 208, the character column counter is initiated to a value of 2. The six column address lines can be located as follows:

FIGURE WILT: TIMING FOR ONE HORIZONTAL SCAN

FIGURE VIII-2: TIMING DIAGRAM FOR ONE FRAME

VII-3

FIGURE VII-3: Display Format

| Bit #   | Location |

|---------|----------|

| 1 (LSB) | C1p12    |

| 2       | C2p12    |

| 3       | C2p9     |

| 4       | C2p8     |

| 5       | C2p11    |

| 6 (MSB) | FF2ap9   |

This column address is fed to the memory section through S1-S3 and in combination with the row address count held in C5 provides the memory with the address of the third character to be displayed during the present scan line. Latch L1 contains the ASCII code for the second character to be displayed and the shift register (SR1) holds the dot pattern of the present character scan line (pointed to by C3) of the first character to be displayed. Latch L2a holds the cursor bit for the second character to be displayed and L2b holds the cursor bit for the character presently being displayed.

The pulse train emanating from the dot oscillator drives C1 (dot counter and LSB of character column address), SR1 (shift register holding the dot patterns for the present character), and A1p12 (which gates the shift register data out to the video combiner circuit).

On the rising edge of the dot oscillator pulses (N2p8) C1 increments. The serial output of SRlp13 is anded with the dot oscillator pulses (N2p8) at Alp10. This output (Alp8) is anded with the delayed and inverted C3p11 (MSB of the character generator scan line address-counter). Thus when the beam traverses character scan lines eight and nine the serial data out of SR1 is blocked at Alp1 to avoid displaying erroneous dots during these two blank lines.

When C1 reaches a count of six Nlp12 and 13 go high, Nlp11 (" $\overline{6}$ ") goes low, and Nlp5 ("6") goes high. The  $\overline{6}$  pulses load the dot pattern of the next

character into SR1 by pulsing SR1p15 low during the sixth dot of each character in a scan line. The "6" pulses are applied to FF1ap1 (C) to affect the negation of the dot oscillator enable control signal when the 64th character has been displayed.

The rising edge of the seventh dot pulse causes the three least significant bits of Cl to reset to zero while the MSB increments (toggles). The MSB of Cl is the LSB of the character column counter. As mentioned above Clp12 (LSB col. cnt.) and Hor sync. are or-ed into C2p14 (count in for upper bits of char. col. cnt.). C2 continues to count as the beam scans across the line and "6" pulses are generated.

When the character column count reaches a count of 64 FF2bp12 (Q) goes high, removing the reset signal from FFlap2 and enabling FFla to toggle on the falling edge of the "6" pulses. The  $\overline{Q}$  output FFlap13 is tied to C3p14 (count in line of the character scan line counter) so that C3 is incremented when the beam finishes displaying the 63rd character on the line and the 64th " $\overline{6}$ " pulse will jam scan line data for the next line into SR1 while the ASCII code for the second character in the next line is jammed into L1. The Q output of FFla is tied to FFlbp5 (clock line of the dot oscillator enable FF) and thus causes FFlbp8 (Dot Oscillator Enable) to fall when the beam finishes displaying the 64th character.

Since C3 is a modulo ten counter it increments C7a (Number of rows displayed) and C5 (pointer to present row) every 10 scan lines. When C7a reaches a count of 16 it sends a capacitively coupled rising pulse into the reset pin of FF4b (Display Enable FF) causing FF4p13(Q) to fall until the 48th scan line of the next frame when the entire process repeats.

#### VIDEO COMBINER AND CURSOR GENERATION

Data shifted out of SR1, cursor information and horizontal and vertical sync. pulses are all combined at transistors  $Q_1$  and  $Q_2$  to create a composite

video output signal which is capacitively coupled to the video out jack on the rear of the ACT-I cabinet. The output impedance is 1.2K.

The cursor data is generated by L2a, L2b and N9. When a negative going edge is sent from L2b to N9p8 through the R-C pulse circuit (which determines the width of the cursor), and C3p11 (character scan line counter MSB) is high, a lus positive pulse will appear at N9p10 and be summed into the video out signal causing a double underscore cursor to appear at the position into which the next character is to be loaded. When the cursor is in its home position it will not be displayed in order to avoid CRT burn in this heavily used position.

Positive Horizontal or Vertical sync pulses cause  $Q_{\parallel}$  to pull the video out signal into the blanking level for synchronizing the monitor.

## SECTION VIII: TROUBLE SHOOTING

In order to pinpoint the faulty component in a malfunctioning ACT-I, the unit should be placed in the self test mode by choosing RS232C output and connecting the serial out and serial in together.

Having placed your unit in the self test mode you are ready to determine which of the four major circuits is malfunctioning. These four circuits are:

- 1) Power supply

- 2) Input/Output

- 3) Memory loading

- 4) Display

#### VIII-1: DISASSEMBLY

Performing the following tests requires access to the interior of the ACT-I cabinet. This can be accomplished by executing the following operations:

- 1) Unplug the ACT-I line and from its 110 volt AC source,

- 2) Remove the six "phillips" head screws which are located as indicated in the figure below (note that 4 of these are in rubber feet).

3) Place the ACT-I in its upright position and separate the black bottom piece and the white top piece by lifting the front of the white piece from the black piece while holding the rear of both cabinet pieces in close proximity. The white piece should be lifted to a vertical position and propped as below to insure stability.

#### VIII-2: EQUIPMENT

In order to perform the following tests the following equipment is required:

- 1) 35 MHz oscilloscope with dual trace

- 2) voltmeter

- 3) phillips head screw driver

#### VIII-3: POWER SUPPLY TEST

With the ACT-I turned on measure the +5 volt and the -12 volt power supplies on the main circuit board. The +5 supply can be found at the rightmost pin of the three 7805 regulator pins. The middle pin should be grounded and the left-most pin should have about +17 volts with about one volt of ripple. The 7805 (plus 5 volt) regulator should be securely fastened to the ACT-I chassis in order to heat sink it.

The minus twelve volt supply can be located at the emitter lead (rightmost) of the MPS3638 pass transistor  $(Q_3)$ . Minus 12 can be found on the main circuit baord at pin 2 of the UART chip (Ulp2) and at pin 1 of the 2513 character generator chip (CGlp1).

The +5 volt regulator (7805) has short circuit and thermal protection and will shut off if its output gets shorted or if it gets too hot. A thermal problem will cause the output to cycle on and off as the chip's temperature changes. Proper heat sinking of the regulator to the ACT-I chassis will prevent any thermal problems.

The -12 volt supply is a zener diode-pass transistor type. It has no short circuit or thermal protection. Should its output become shorted the MPS 3638 pass transistor will be permanently damaged. Under normal operating conditions the -12 supply is loaded very lightly and the MSP3638 needs no heat sink.

#### VIII-4: DIAGNOSIS OF MAIN BOARD MALFUNCTIONS

Having determined that the main board is a fault you can determine which of the I/O, memory loading, or display circuits is faulty by performing the following tests.

#### VIII-4.1: I/O TEST

With the unit in the self test mode (described at the beginning of this section) repeatedly strike the letter A and compare actual waveforms with those given in section III of this manual. If the necessary signals check out and in particular if the negative going pulse (STROBE) appears at pin 6 of MTI5 and the UART clock frequency is correct, the I/O circuitry is performing as required.

#### VIII-4.2: MEMORY LOADING TEST

Depress the PAGE key and verify that FF3a (Scroll FF) sets and remains set while the PAGE key is depressed. Also verify that C6 and C4 are counting properly and  $R/\overline{W}$  pulses appear at M1-M7p3 as described in section V. If these waveforms check out the memory loading circuitry is not at fault.

#### VIII-4.3: MEMORY TEST

The most common memory failure is a tendency to make bit errors. For example after clearing the screen an ! may appear in one position on the screen. This is due to an errant memory bit in the least significant position (ASCII code for space =  $20_{16}$ , ! =  $21_{16}$ ). If this problem occurs the appropriate memory (M1-M7) should be replaced. Another symptom is that when loading a given position with a character the character in a different position is altered. The bit which is modified indicates the faulty memory chip.

#### VIII-4.4: DISPLAY GENERATION TEST

If the power supply I/O and display loading circuits pass their tests and an abnormal display (or no display at all) persists the display circuitry is at fault. Refer to section VII and verify that all waveforms are as indicated.

Some symptoms and the associated remedies are listed below:

### VIII-5: TROUBLE SYMPTOMS AND REMEDIES

The following is a list of reported trouble symptoms and the remedies suggested by the Micro-Term technical staff:

#### SYMPTOM

- Vertical jitter or bars rolling vertically

- 2) Rubout code (FF Hex) sent instead of struck character

#### REMEDY

Readjust the duration of the vertical sync pulse(N4pl1) by varying the resistor tied to N9pl,2 so that the vertical sync pulse falls midway between the fourth and fifth horizontal sync pulses.

Strobe from keyboard to UART should be delayed 10 microseconds by tying .luf capacitor from Ulp23 to ground (Ulp21) and placing a 1K resistor in series with the KBD strobe line KBD pin 6.

# SECTION IX: TECHNICAL INFORMATION

IX-1: ASCII CODES

|     |      |             |      | •           |              |             |      |

|-----|------|-------------|------|-------------|--------------|-------------|------|

| HEX | CHAR | HEX<br>CODE | CHAR | HEX<br>CODE | CHAR         | HEX<br>CODE | CHAR |

| 00  | NUL  | 20          | SP   | 40          | @            | 60          | •    |

| 01  | SOH  | 21          | !    | 41          | Α            | 61          | a    |

| 02  | STX  | 22          |      | 42          | В            | 62          | b    |

| 03  | ETX  | 23          | #    | 43          | C            | <b>63</b>   | C    |

| 04  | EOT  | 24          | \$   | 44          | D            | 64          | d .  |

| 05  | ENQ  | 25          | %    | 45          | E            | 65          | е    |

| 06  | ACK  | 26          | &    | 46          | F            | 66          | f    |

| 07  | BEL  | 27          | •    | 47          | G            | 67          | g    |

| 08  | BS   | 28          | (    | 48          | Н            | 68          | h,   |

| 09  | HT   | 29          | ) .  | 49          | 1            | 69          | i    |

| 0A  | LF   | 2A          | *    | 4A          | J            | 6A          | j    |

| 0B  | VT   | 2B          | +    | 4B          | K            | 6B          | k    |

| 0C  | FF   | 2C          | ,    | 4C          | L            | 6C          |      |

| 0D  | CR   | 2D          | _    | 4D          | M            | <b>6</b> D  | m    |

| 0E  | SO   | 2E          |      | 4E          | N            | 6E          | n    |

| OF  | SI   | 2F          | /    | 4F          | 0            | 6F          | 0    |

| 10  | DLE  | 30          | 0    | 50          | Р            | 70          | р    |

| 11  | DC1  | 31          | 1    | 51          | Q            | 71          | q    |

| 12  | DC2  | 32          | 2    | 52          | R            | 72          | r    |

| 13  | DC3  | 33          | 3    | 53          | S            | 73          | S    |

| 14  | DC4  | 34          | 4    | 54          | T            | 74          | t    |

| 15  | NAK  | 35          | 5    | 55          | U            | 75          | u .  |

| 16  | SYN  | 36          | 6    | 56          | V            | 76          | V    |

| 17  | ETB  | 37          | 7    | 57          | W            | 77          | w    |

| 18  | CAN  | 38          | 8    | 58          | ×            | 78          | x    |

| 19  | EM   | 39          | 9    | 59          | Y            | 79          | У    |

| 1A  | SUB  | 3A          | :    | 5A          | Z            | 7 <b>A</b>  | Z    |

| 1B  | ESC  | 3B          | ;    | 5B          | [            | 7B          | {    |

| 1C  | FS   | 3C          | <    | 5C          | \            | 7C          | 1    |

| 1D  | GS   | 3D          | =    | 5D          | ]            | 7D          | }    |

| 1E  | RS   | 3E          | >    | 5E          | ٨            | 7E          | ~    |

| 1F  | VS   | 3F          | ?    | 5F          | $\leftarrow$ | 7F          | DEL  |

|     |      |             |      |             |              |             |      |

ACT-1 11/76 REV. B

#### IX-3: GENERAL SPECIFICATIONS

# <u>Display (Receiver):</u>

Format - 64 characters by 16 lines

Spacing - Horizontal - one dot between characters

Vertical - 3 scan lines between rows of characters

Character set - Uppercase alphabet, numbers and punctuation; 64 total ASCII codes

Refresh rate - 60 Hz (non-interleaved)

Video out - 1.5 vp-p, RS 170

Cursor - Underline, double stroke, extinguished in home position to prevent phosphor burn and prolong CRT life

Data Rate - the display (receiver) can load characters at rates between 110 and 9600 Baud, RS232C or 20 ma current loop

## Transmitter:

Character set - uppercase ASCII - includes all control codes

Data Rate - 110 to 9600 Baud crystal controlled - RS232C or 20 ma current loop

# General:

Power - 110 volts AC, 50-60 Hz, 15 watts

Size -  $7.5 \times 36 \times 28 \text{ cm} (3 \times 14 \times 11 \text{ inches})$

Weight - 5 Kg (8 lbs.)

IX-4: INTEGRATED CIRCUIT IDENTIFICATION AND POWER CONNECTION

| Part         | Type      | +5<br>Pin | Ground<br>Pin | Other Power Pin(s)     |

|--------------|-----------|-----------|---------------|------------------------|

| AT           | 74LS08    | 14        | 7             |                        |

| A2,A3        | 4081      | 14        | 7             |                        |

| <b>A4</b>    | 4082      | 14        | 7             |                        |

| C1           | 7492      | 5         | 10            |                        |

| C2           | 7493      | 5         | 10            |                        |

| C3           | 7490      | 5         | 10            |                        |

| C4,C6,C10    | 4024      | 14        | 7             |                        |

| C5           | 4029      | 16        | 8             |                        |

| <b>C7</b>    | 4520      | 16        | 8             |                        |

| C8,C11       | 4040      | 16        | 8             |                        |

| CG           | 2513      | 24        | 10            | -5v pin 12, -12v pin 1 |

| FF1,FF2      | 74LS73    | 4         | 11            |                        |