Applied Digital Data Systems Inc.

MULTIVISION

MULTIVISION"

THEORY OF OPERATIONS

Pub. #516-34500 September, 1981

This is the first release of the Multivision™ Theory of Operation Manual.

Future revisions will have a list of changed pages in this position, with a margin bar on affected text pages.

Users are urged to use the Comment Sheet at the back of the book to communicate their comments to the ADDS' Technical Publications Department, Systems Division.

Multivision is a registered trademark of Applied Digital Data Systems Inc.

The material contained in this document is furnished for customer reference only, and is subject to change without notice. Applied Digital Data Systems makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. ADDS assumes no responsibility for any errors that may appear in this document and makes no commitment to update nor to keep current the information contained in this document.

The techniques described here are proprietary and should be treated accordingly. No part of this manual may be reproduced in any form or by any means without the prior written consent of ADDS.

©1981 Applied Digital Data Systems Inc. Hauppauge, N.Y.

# TABLE OF CONTENTS

| SECTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE                                                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l - 1                                                                                                                                                           |

|         | Multivision 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-2<br>1-4<br>1-6                                                                                                                                               |

| 2       | CPU PC BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 <b>-</b> 1                                                                                                                                                    |

| 2       | Overview  Processor 8085A-2 Functional Description Interrupt Structure  Direct Memory Access (DMA) Controller 8237-2 Functional Description Software Operations  CMOS Memory 5101L-1 Functional Description Programming CMOS "Shadow" EPROM 2732 Functional Description Diagnostics/Bootstrap and System Load Serial I/O Ports 8251A USART Functional Description Port Assignments Programming the 8251A Mode Instruction Mode Instruction Command Instruction Command Instruction Frogrammable Interval Timer (PIT) 8253-5 Functional Description Programmable Interrupt Controller (PIC) 8259A Real Time Clock (RTC) | 2-1<br>2-3<br>2-3<br>2-4<br>2-5<br>2-10<br>2-10<br>2-12<br>2-13<br>2-13<br>2-15<br>2-19<br>2-22<br>2-22<br>2-22<br>2-30<br>2-34<br>2-34<br>2-34<br>2-34<br>2-34 |

|         | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-39<br>2-39<br>2-42<br>2-42                                                                                                                                    |

|         | System Bussing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-44                                                                                                                                                            |

| S | ECT | ION |  |

|---|-----|-----|--|

|   |     |     |  |

| D | ٨ | $\sim$ | t  |

|---|---|--------|----|

| r | n | v      | Γ. |

| 3 | RAM PC BOARD 3-1                                                                                                                                                                                                                                                                                                                                                                                                        |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Overview       3-1         Refresh and Hold Logic       3-1         RAM Array       3-2         Basic Element       3-2         Organization       3-3         Address Multiplexing and Refresh Address       3-3         Generation       3-3         RAS and CAS Generation       3-4         RAS and CAS Demultiplexing       3-4         Parity Generation and Checking       3-4         Programming RAM       3-4 |

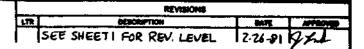

| 4 | MINI DISK/PRINTER INTERFACE PC BOARD 4-1                                                                                                                                                                                                                                                                                                                                                                                |

|   | Functional Description 4-1  Data Request 4-2  Head Load Timing 4-2  Read Gate 4-2  Write Precomp 4-2  Data Separator 4-2  Power Supply and V.C.O. Set Up 4-2  Programming the Mini Disk Controller FD1793 4-2  FD1793 Commands 4-2                                                                                                                                                                                      |

| 5 | PARALLEL PRINTER PORTS 5-                                                                                                                                                                                                                                                                                                                                                                                               |

|   | Printer Interface                                                                                                                                                                                                                                                                                                                                                                                                       |

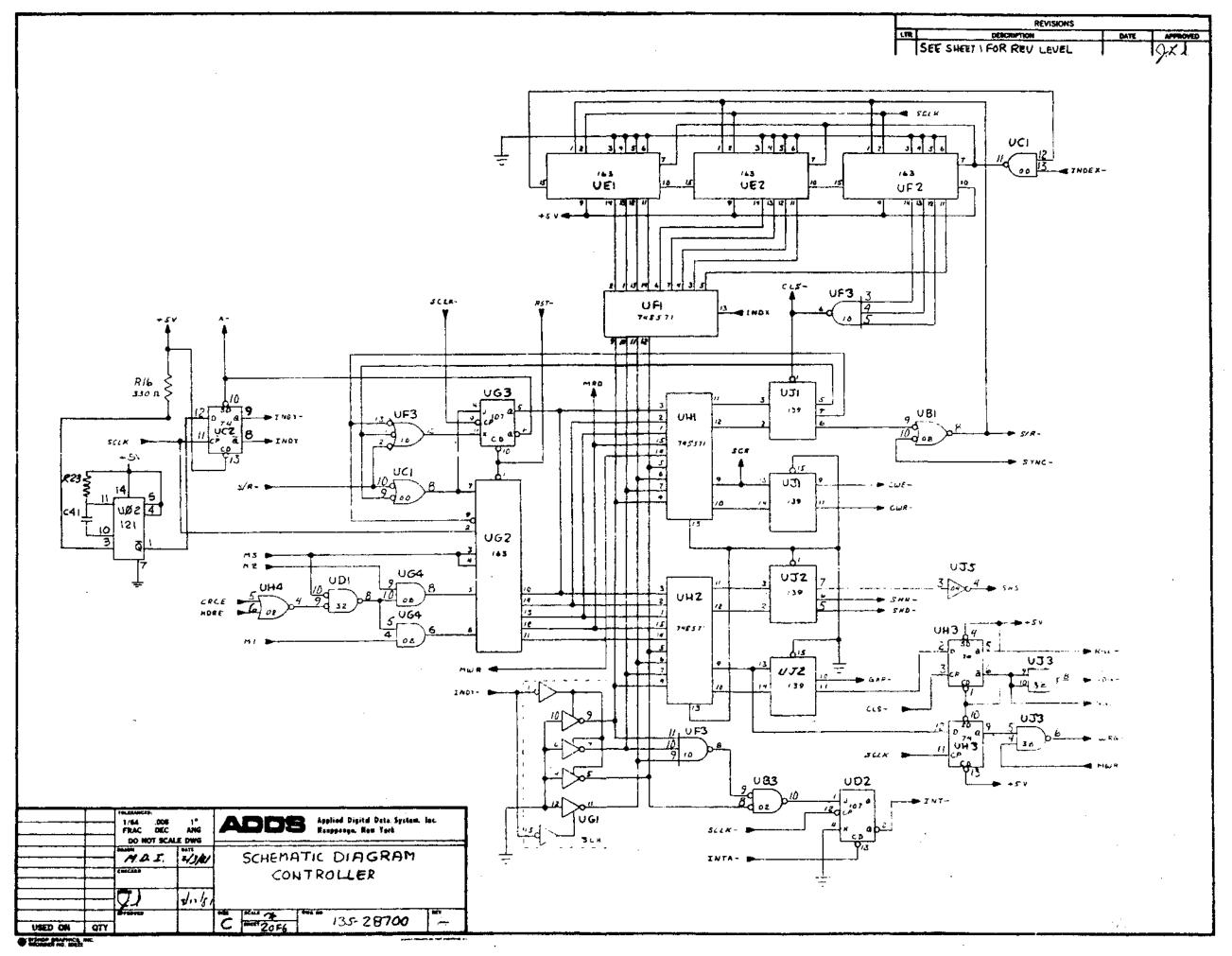

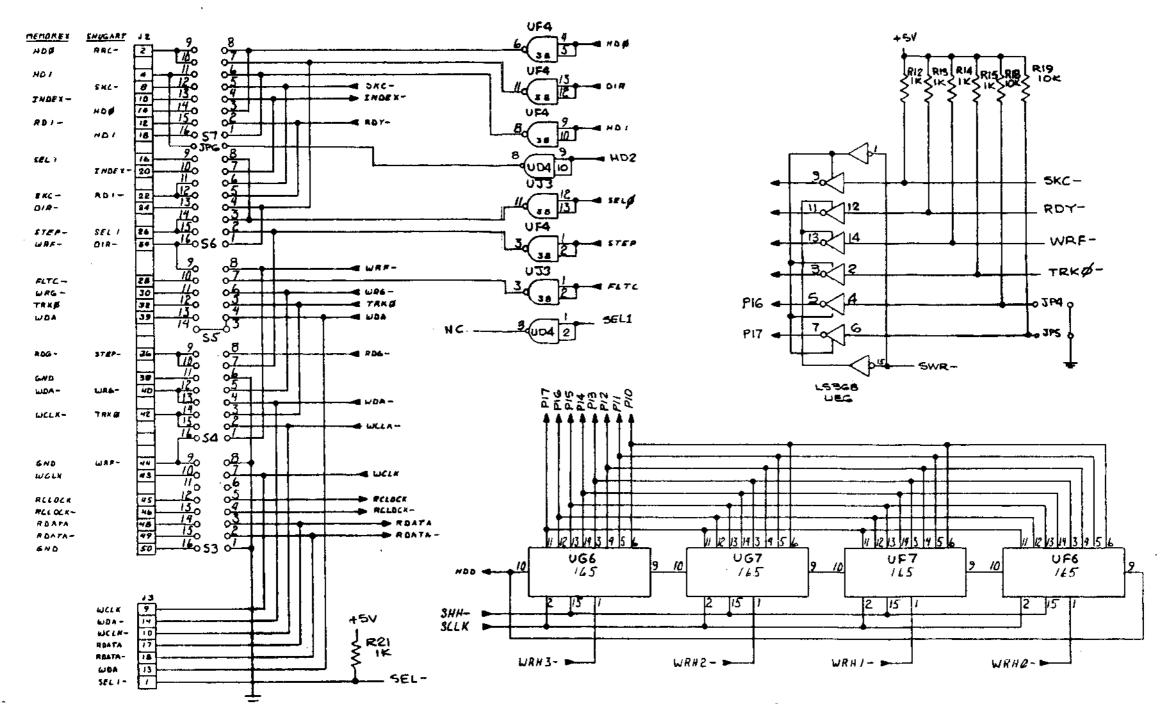

| 6 | HARD DISK CONTROLLER 6-3                                                                                                                                                                                                                                                                                                                                                                                                |

|   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                |

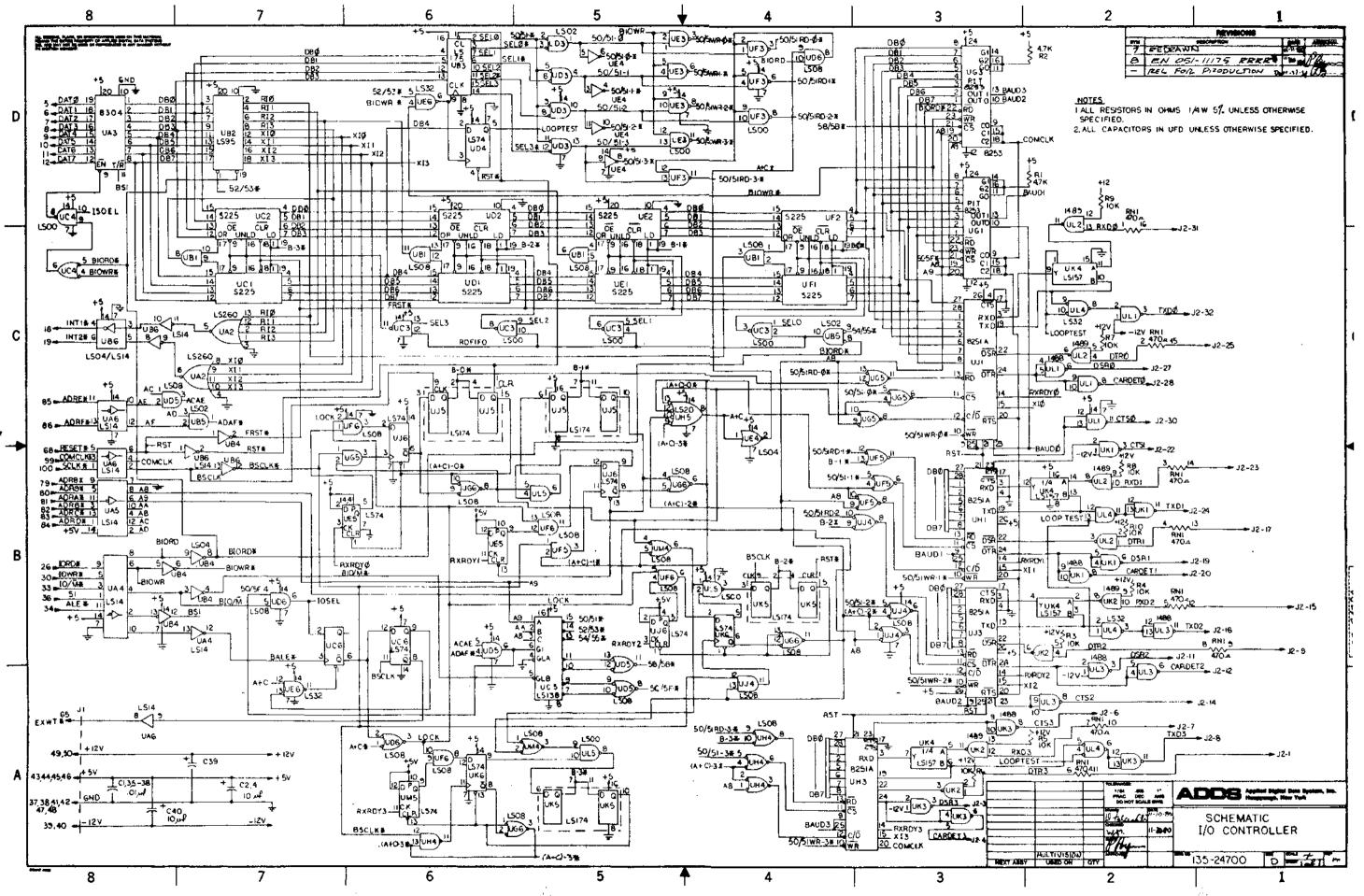

| 7 | I/O CONTROLLER 7-1                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                  |

| SECTION                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PAGE                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 8                                                                                                                                 | MINI DISK DRIVES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8 - 1                                                                                             |

|                                                                                                                                   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-1<br>8-1                                                                                        |

| 9                                                                                                                                 | HARD DISK DRIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9-1                                                                                               |

|                                                                                                                                   | Overview Features Read/Write Electronics Read/Write Heads and Disks Specifications Physical Specifications Reliability Specifications Performance Specifications Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9-1<br>9-1<br>9-1<br>9-2<br>9-3<br>9-3<br>9-4<br>9-4                                              |

| 10                                                                                                                                | POWER SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-1                                                                                              |

|                                                                                                                                   | Multivision 1 Power Supply Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10-1<br>10-2<br>10-4                                                                              |

| 11                                                                                                                                | SCHEMATICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11-1                                                                                              |

|                                                                                                                                   | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   |

| TABLE                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>5.1<br>5.2<br>6.1<br>6.2<br>7.1 | CPU Logic Sections Multivision Port Assignments for DMA CMOS RAM Layout I/O Port Assignments for Multivision 1 I/O Port Assignments for the CPU Pinouts for 100 Pin Bus FD1793 Command Summary Flag Summary for Type I Commands Flag Summary for Type II and III Commands Flag Summary for Type IV Commands Stepping Rates Status Register Summary Status for Type I Commands Status for Type I Commands Status for Type II and III Commands Status for Type II and III Commands One of the Commands Status for Type II and III Commands | 2-1<br>2-6<br>2-16<br>2-2-43<br>2-43<br>4-8<br>4-9<br>4-10<br>4-10<br>4-13<br>5-6<br>6-4<br>5-7-2 |

## LIST OF FIGURES

| FIGURE |                                                   | PAGE  |

|--------|---------------------------------------------------|-------|

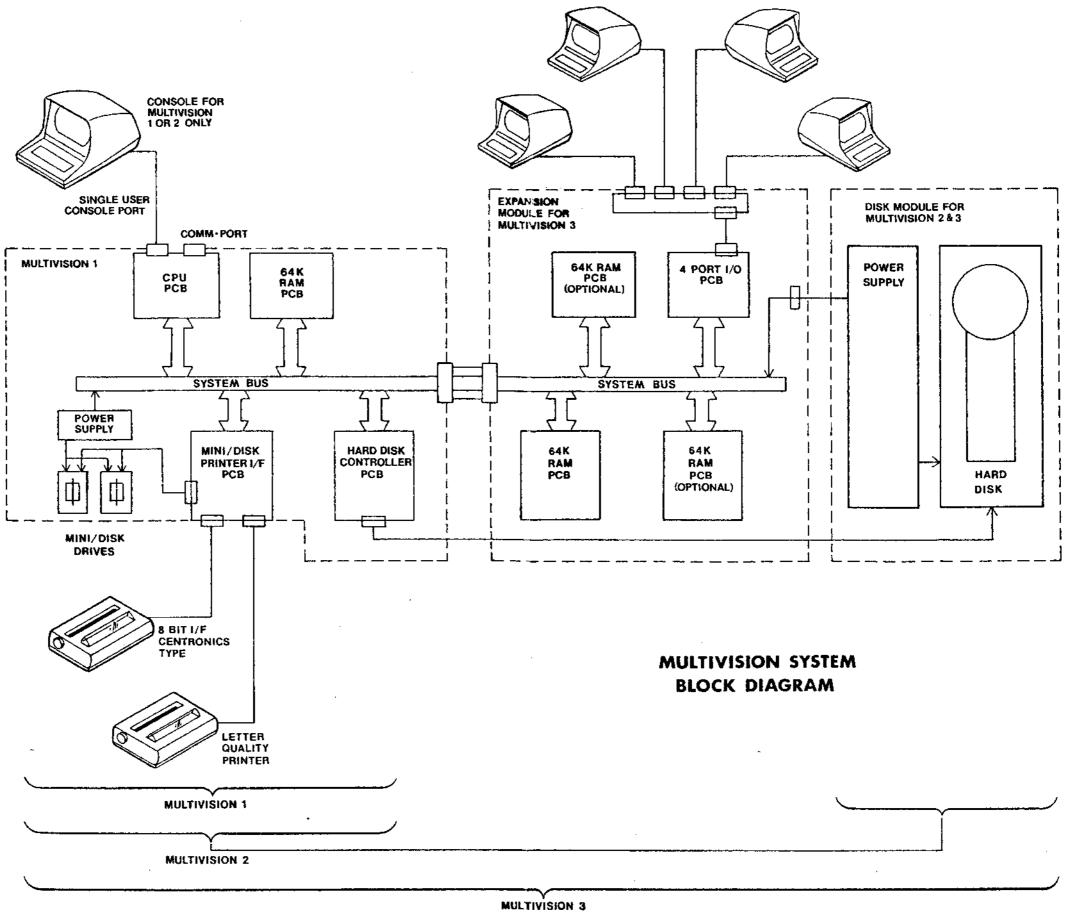

| 1 - 1  | Multivision System Block Diagram                  | 1-9   |

| 2-1    | 8085A-2 Register Set                              | 2-3   |

| 2-2    | Mode Instruction Format - Asynchronous            | 2-24  |

| 2-3    | Asynchronous Mode                                 | 2-25  |

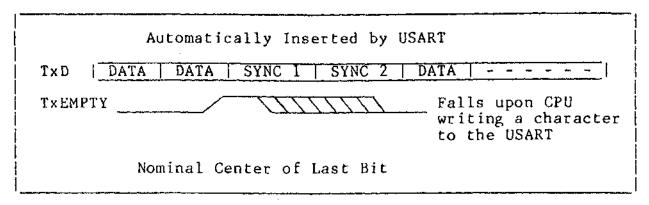

| 2 - 4  | TxEMPTY Pin                                       | 2-26  |

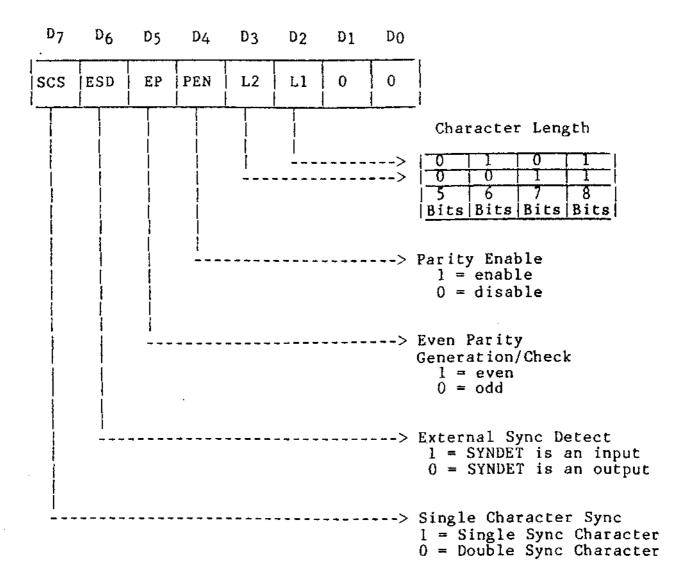

| 2-5    | Mode Instruction Format                           | 2-28  |

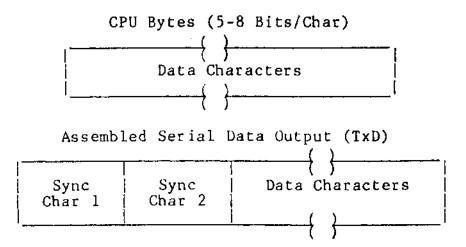

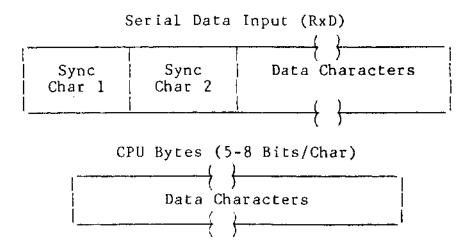

| 2~6    | Data Format - Synchronous Mode                    | 2-29  |

| 2-7    | Typical Data Block                                | 2-30  |

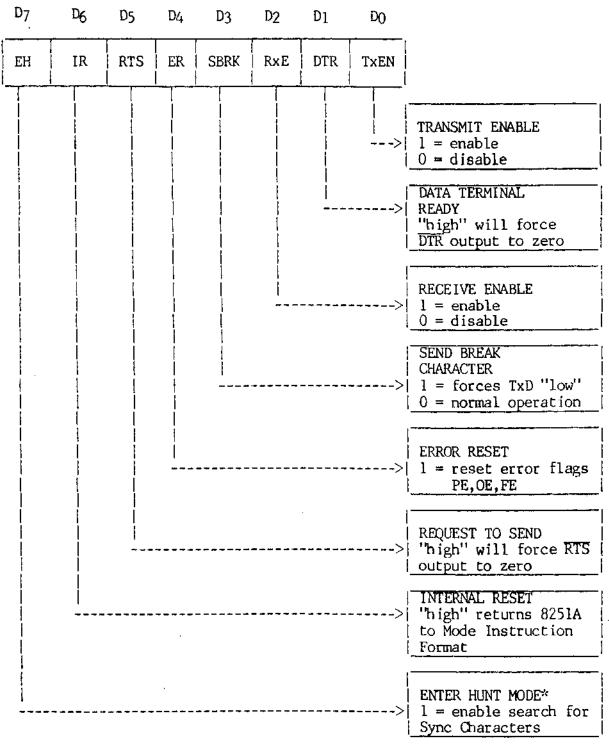

| 2-8    | Command Instruction Format                        | 2-31  |

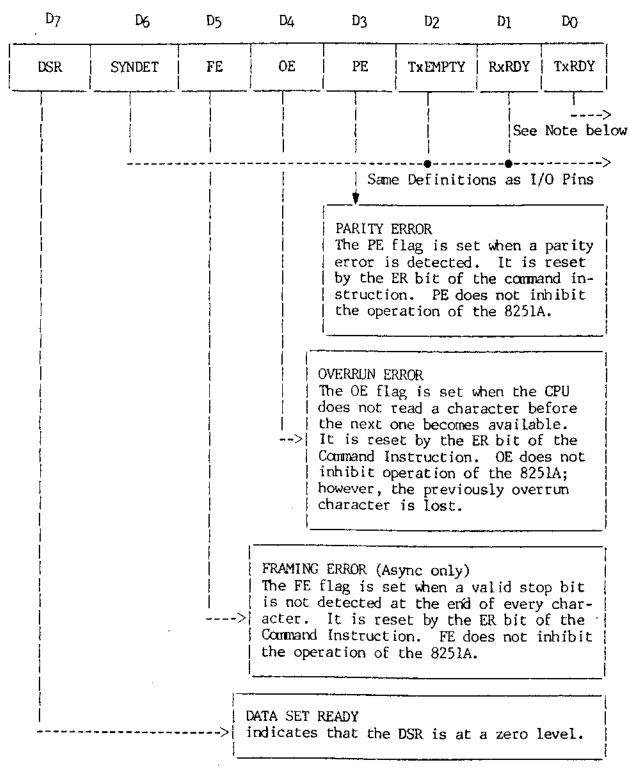

| 2-9    | Status Read Format                                | 2-33  |

| 2-10   | PIC Interrupt Lines                               | 2-36  |

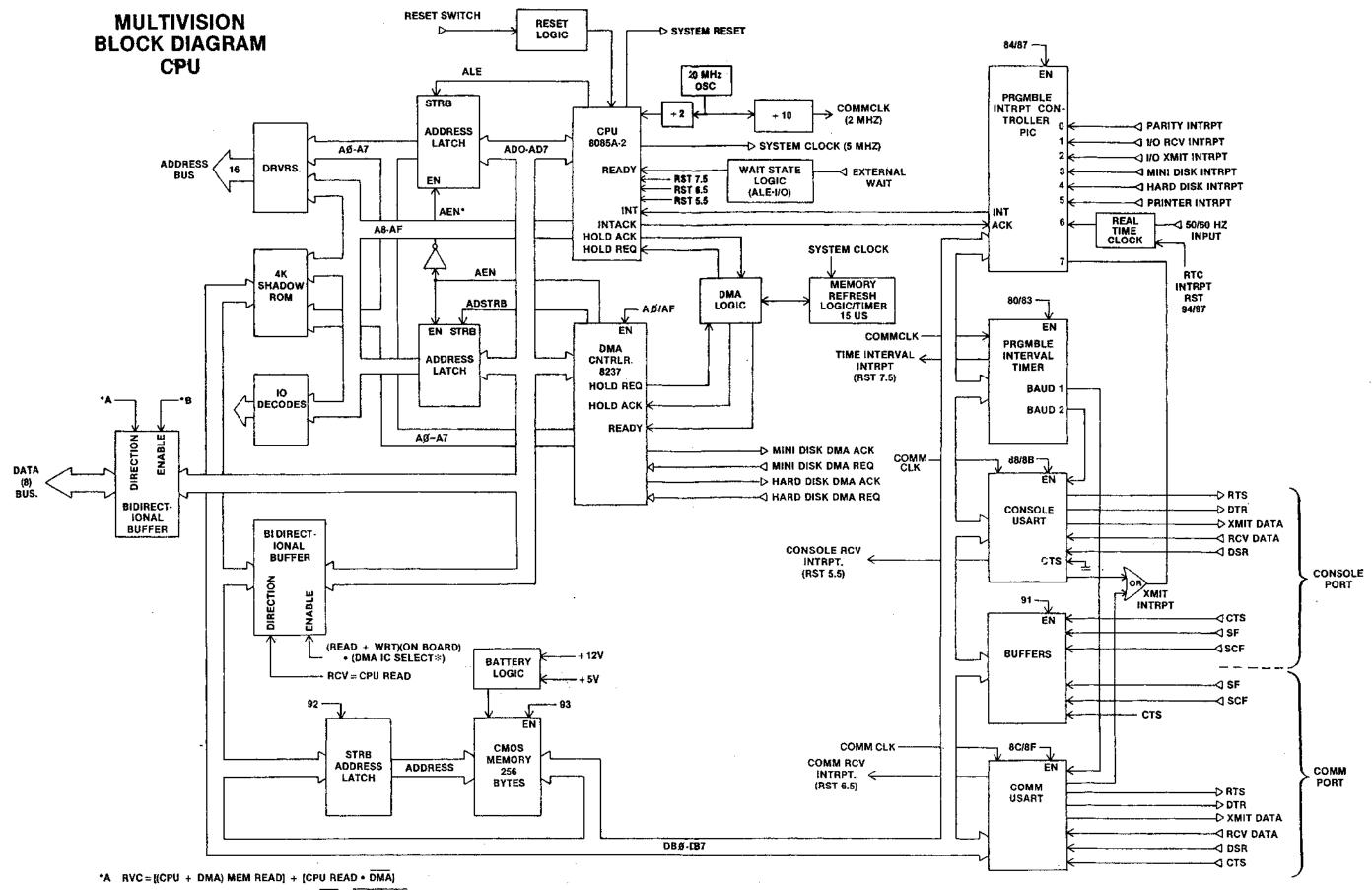

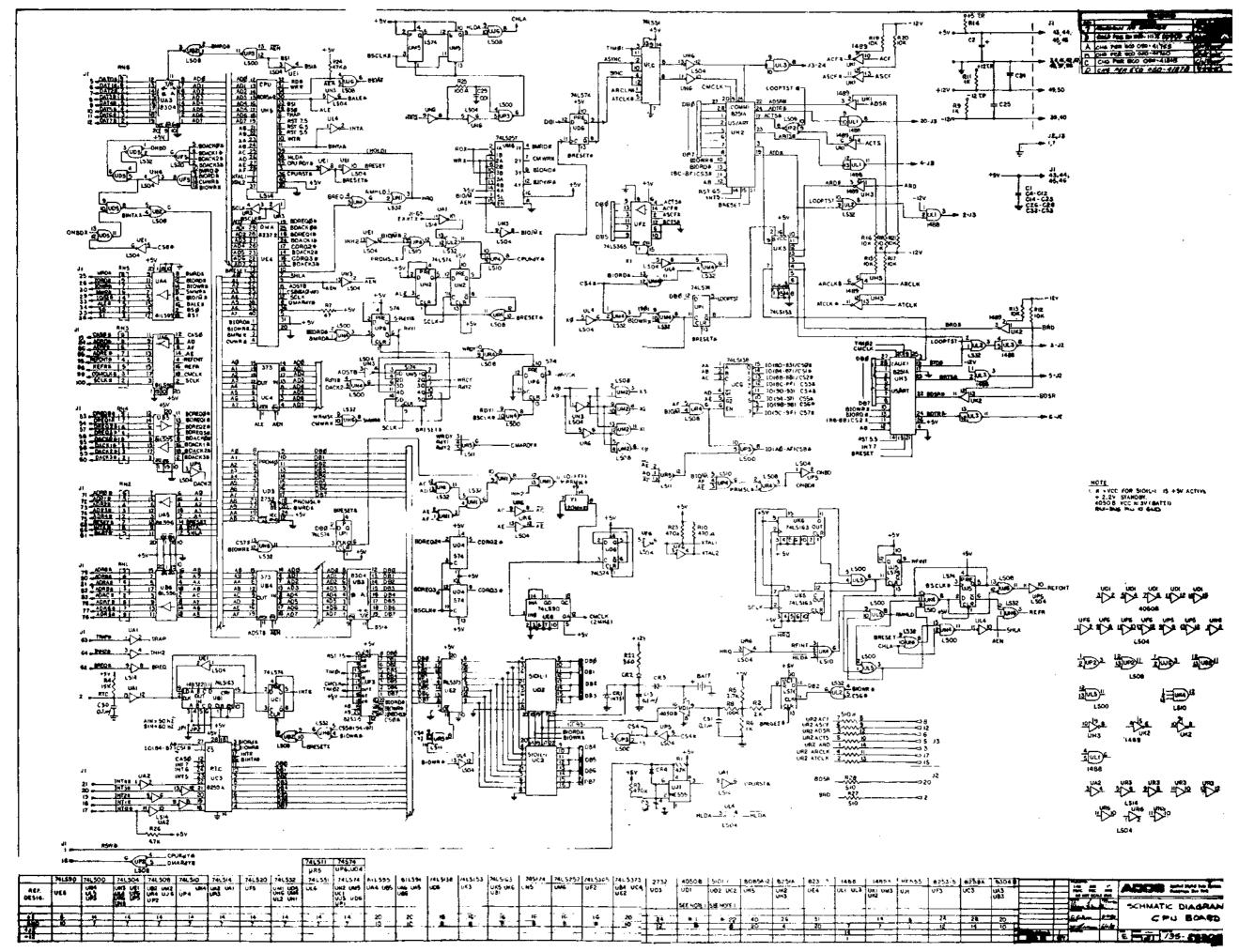

| 2-11   | CPU PC Board Block Diagram                        | 2-49  |

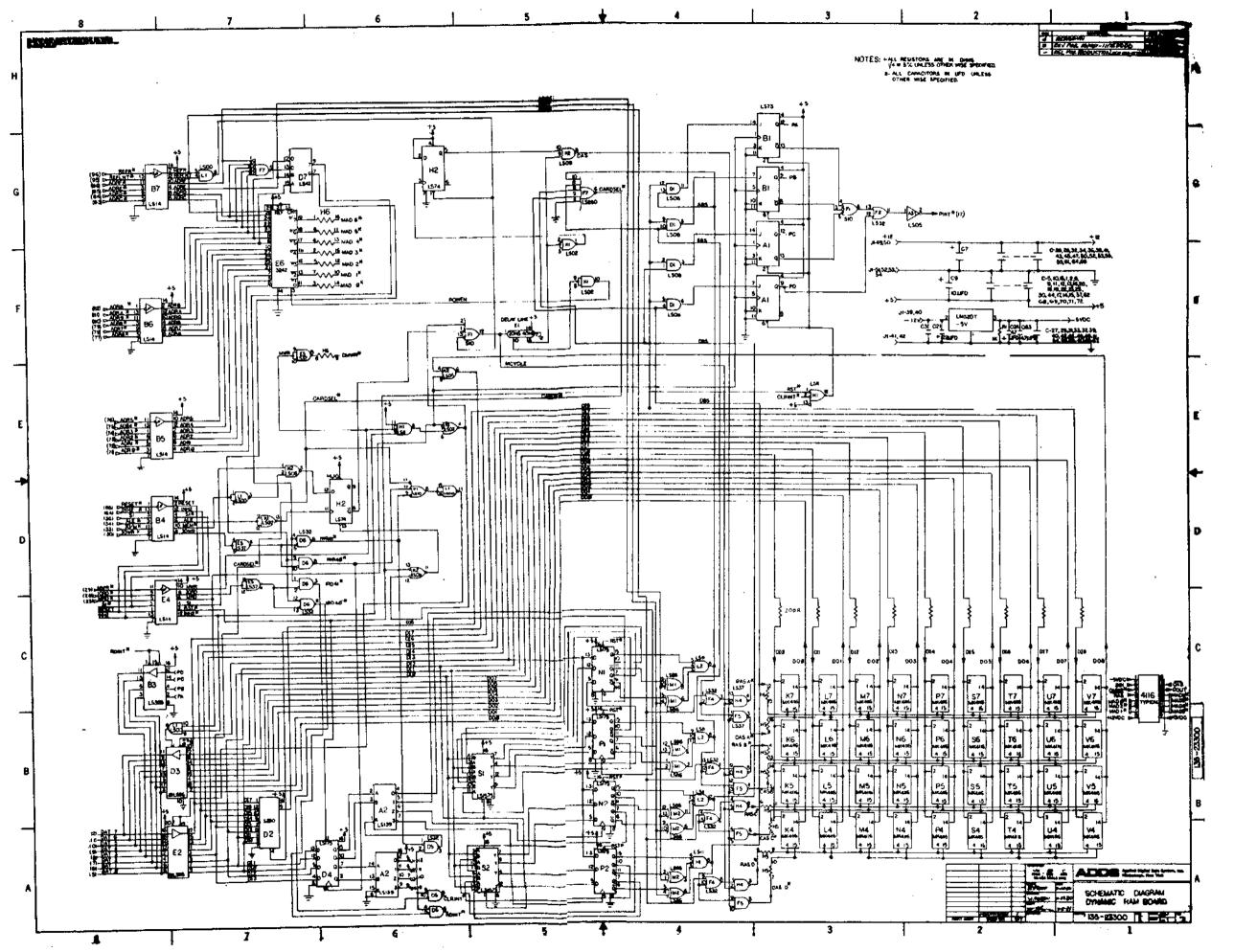

| 3-1    | RAM PC Board Block Diagram                        | 3-7   |

| 4-1    | FD1793 Internal Registers                         | 4-1   |

| 4-2    | Processor Interface 1793 Block Diagram            | 4-2   |

| 4-3    | Diagram of an M.F.M. Recording                    | 4-4   |

| 4 -4   | Multivision Port Assignments                      | 4-8   |

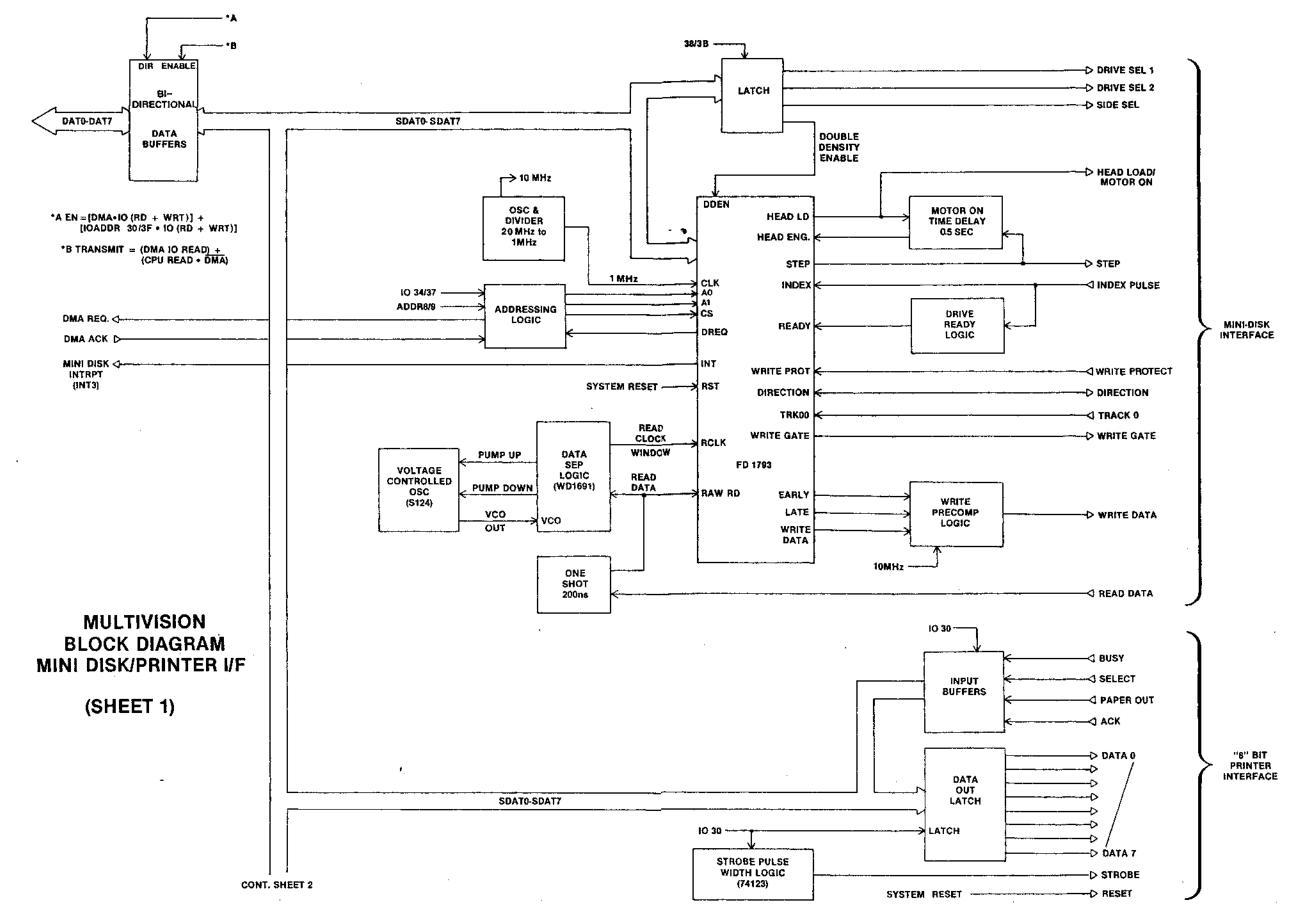

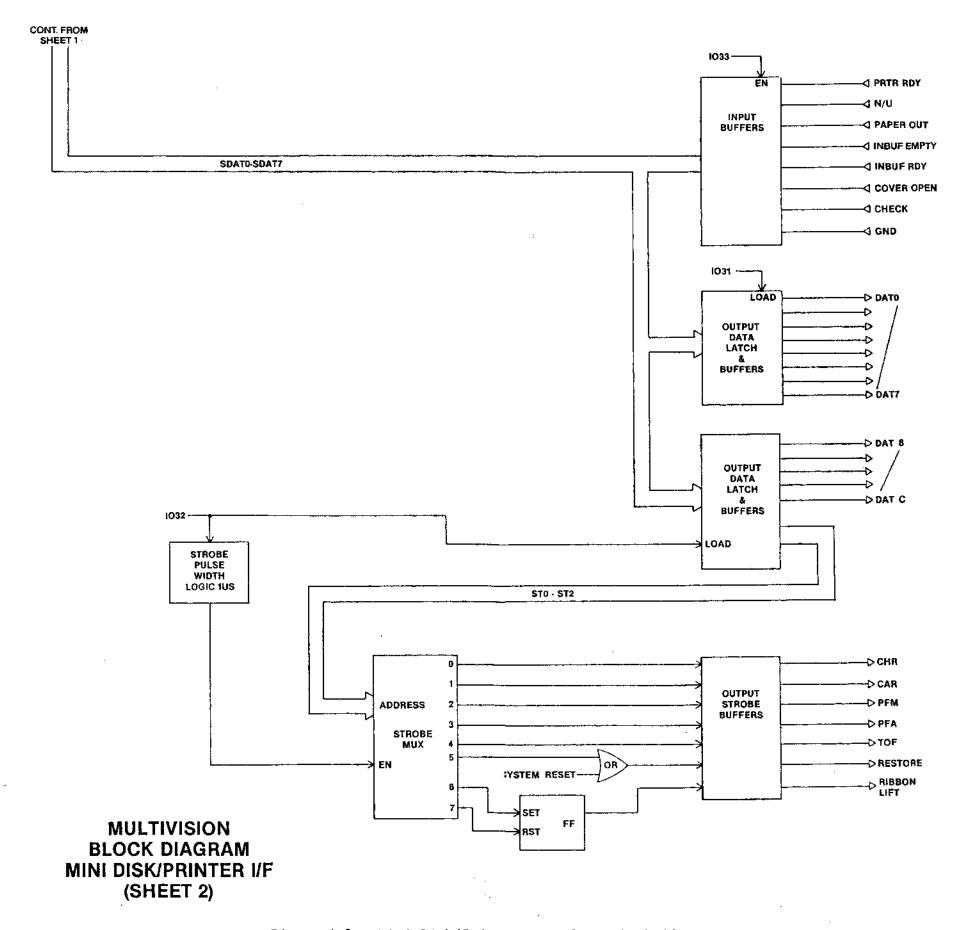

| 4-5    | Mini Disk/Printer Interface Block Diagram         | 4-15  |

| 5 – 1  | Printer I/O Ports                                 | 5-2   |

| 5-2    | Port Assignment for 8-bit Parallel Printer Port   | 5-3   |

| 5-3    | Port Assignments for 13-bit Parallel Printer Port | 5-4   |

| 6-1    | Microcontroller Sector Format                     | 6-2   |

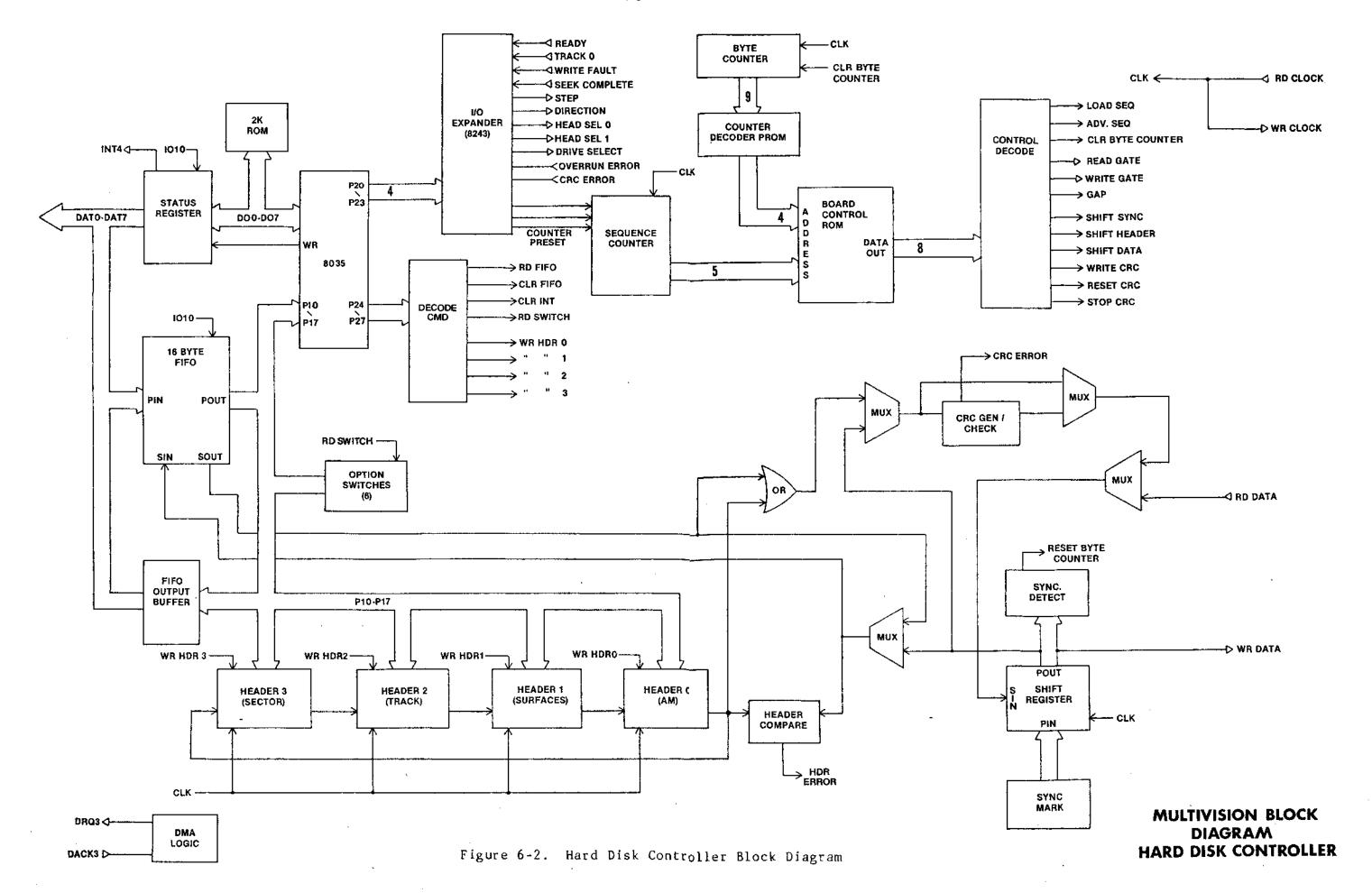

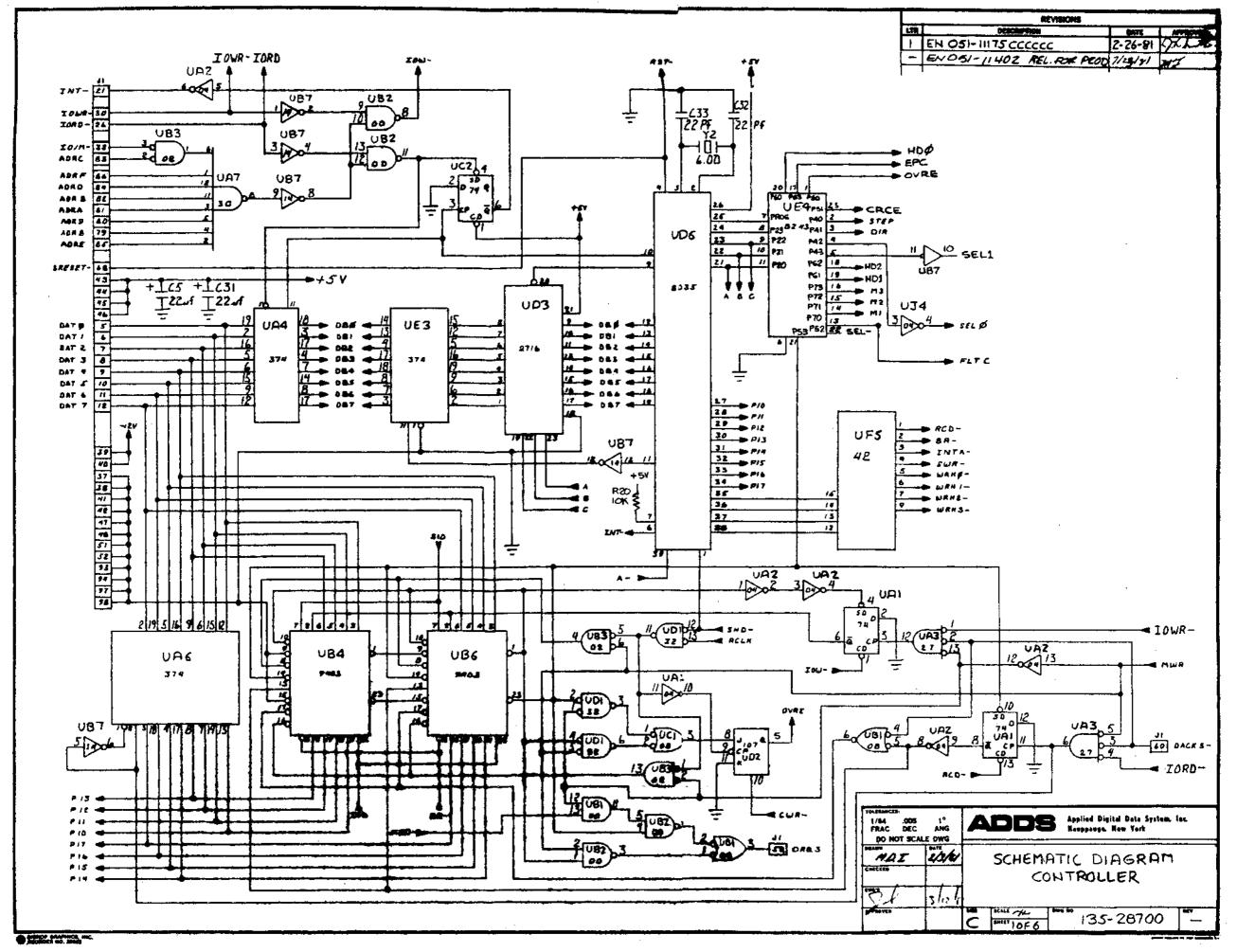

| 6-2    | Hard Disk Controller Block Diagram                | 6-9   |

| 7-1    | XMIT and RCV Interrupt Bits                       | 7 - 2 |

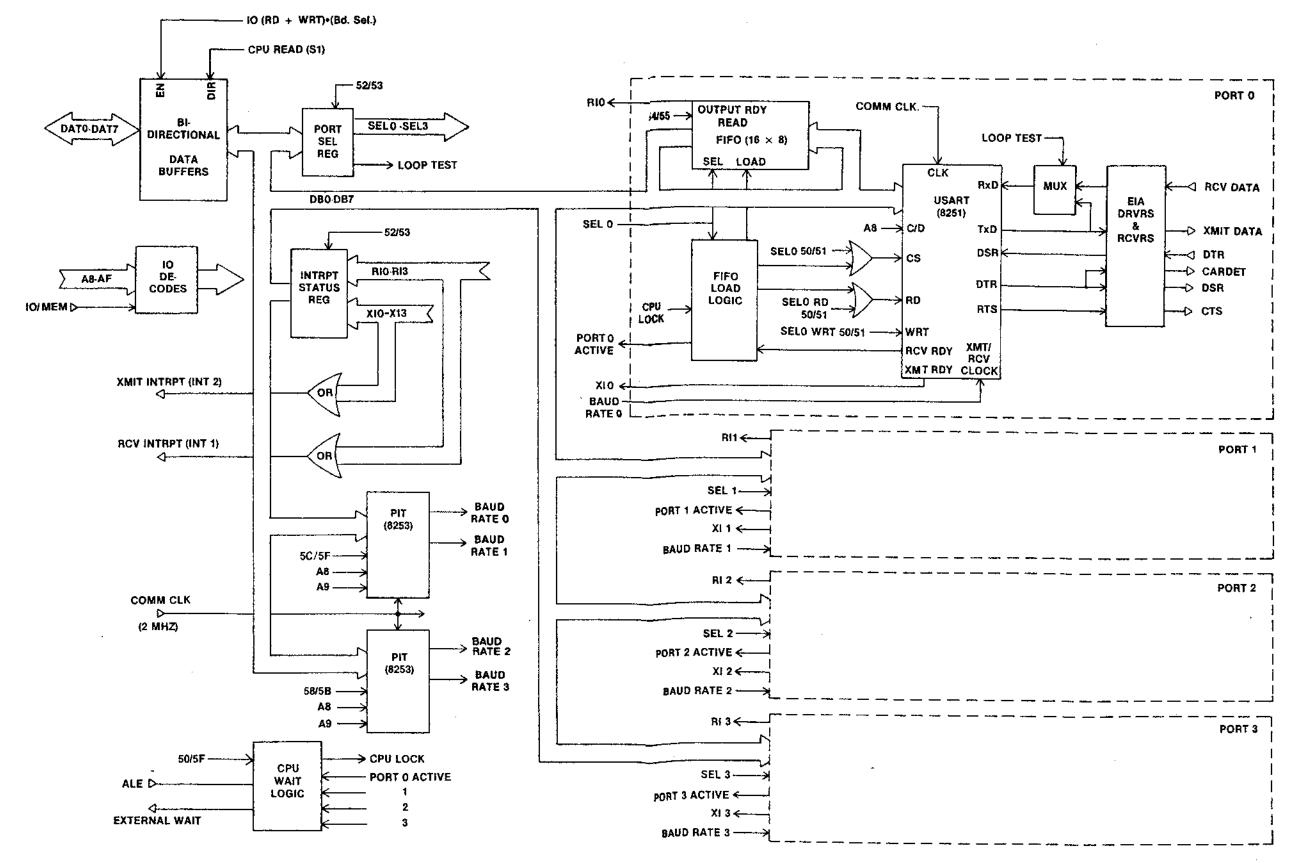

| 7 - 2  | 4 Port I/O Controller Block Diagram               | 7 - 5 |

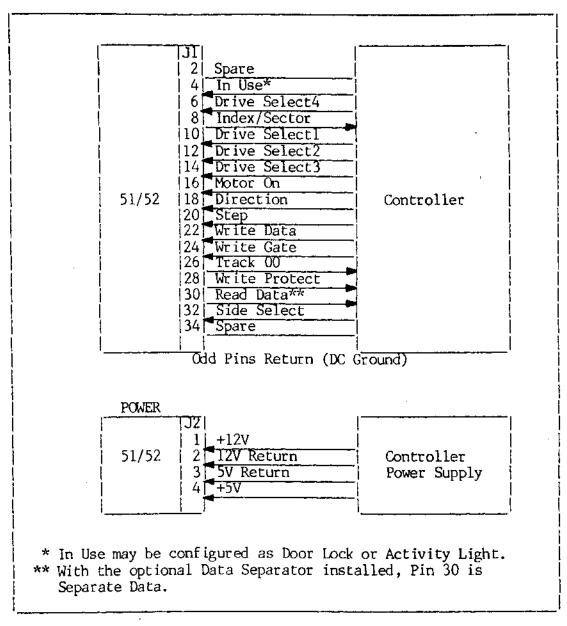

| 8-1    | Specifications for M.P.I. Model 52                |       |

|        | Mini Disk Drives                                  | 8-2   |

| 8-2    | Mini Disk Interface Signals                       | 8-3   |

| 8-3    | M.P.I. Shunt Configuration                        | 8-3   |

| 8-4    | Tandon T100 Shunt Configuration                   | 8-4   |

Multivision is comprised of a family of three desk-top computers referred to as Multivision 1, Multivision 2, and Multivision 3.

Multivision l is a single user mini disk system that can be expanded, by the addition of easily connected modules, to a single user hard disk system, Multivision 2; and a multi-user hard disk system, Multivision 3.

This manual provides the user with a description of the hardware for Multivision 1, 2, and 3 along with the software designed for each device.

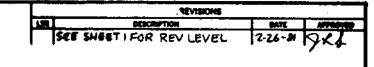

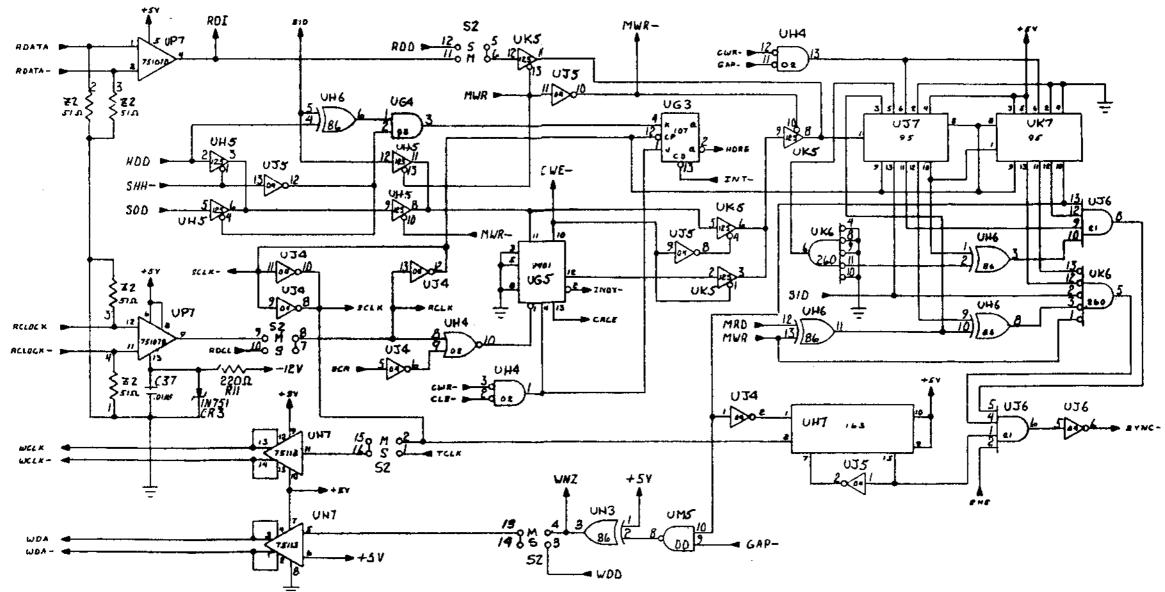

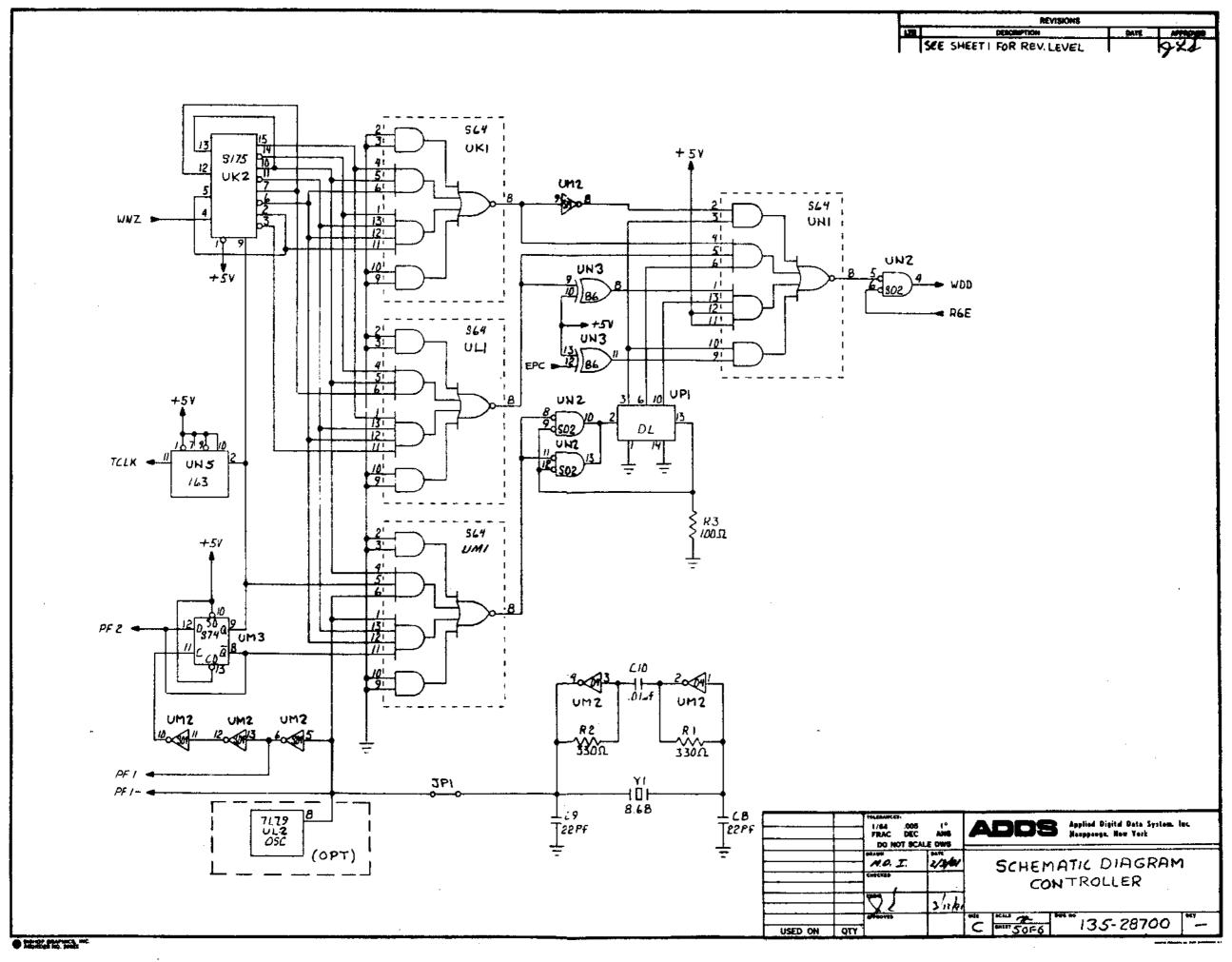

Functional descriptions of the hardware are provided along with block diagrams and schematics for each of the three modules which make up the Multivision family. Schematics are also provided for all major subassemblies, peripherals, and internal connections within the modules.

All PC boards are represented by block diagrams as well. Major logic sections are described along with the major busses and connections. I/O control lines with their corresponding I/O addresses are shown, where applicable.

The software information provided explains how the hardware is directly controlled, without the use of any of ADDS' operating system software. The information is sufficient for the Multivision user to adapt his own operating system, if desired.

#### MULTIVISION 1

Multivision 1 is comprised of six major subassemblies consisting of two mini disks, a power supply, and three PC boards (printed circuit boards), mounted in a card cage assembly.

#### System Bus

Each PC board in a Multivision 1 plugs directly into the system bus. The bus is comprised of 100 common pins including power. Physically, the bus is made from a multi-layer PC board with an integral ground plane. Data and address lines are physically isolated and spare ground lines surround all critical strobes. At the system level, all signals on or off the bus are unit loads. Drivers and receivers on the individual PC boards are highly noise immune components placed within close proximity to the actual PC board connectors. Signal termination is provided on the CPU board.

## CPU PC Board (129-25300)

The CPU contains a 5MHz 8085A-2 microprocessor, a four channel DMA controller (with memory to memory transfer capability at four times the speed of an equivalent programming loop), an interrupt controller with 8 individual interrupt vectors, a three channel timer, 256 bytes of non-volatile memory, a 4K diagnostic and program load "shadow" EPROM, and two serial communication ports.

The first serial port is used for serial asynchronous communication to the console device (up to 9600 baud). The second can be configured for either asynchronous or synchronous communication, (up to 9600 baud), including serial printer applications. Timing for these ports is provided independently by two channels of the three channel timer. The third channel is used for general operating system timing functions. A separate 50/60Hz timing circuit is provided for custom timing applications (i.e., time-of-day).

The non-volatile memory is used primarily to replace mechanical switches in the storing of communication parameters for the serial ports and to store system diagnostic information. Spare portions of this memory are available to the user for other applications such as soft serial numbers.

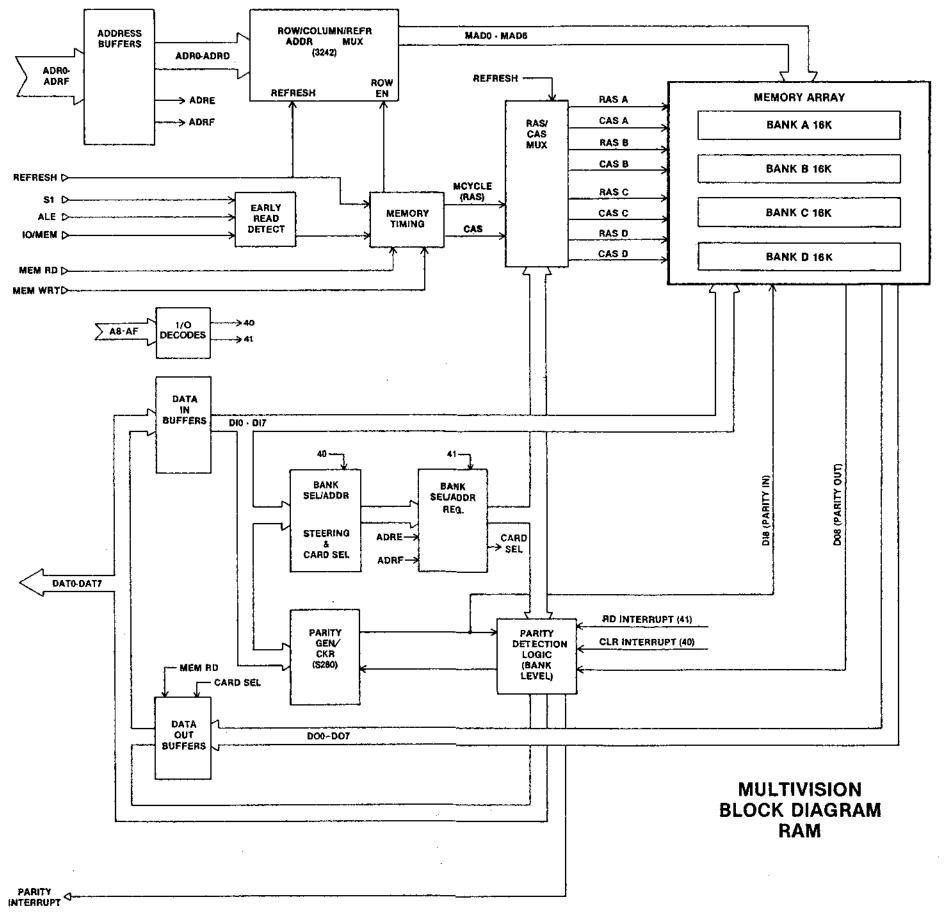

#### 64K RAM PC Board (129-23300)

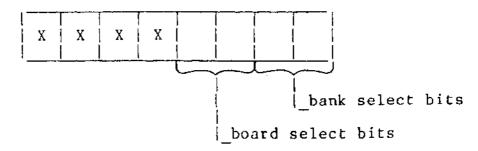

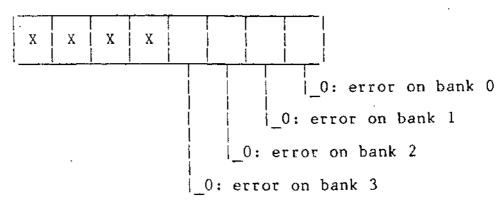

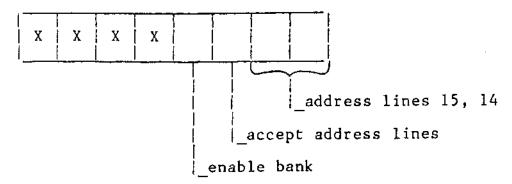

The RAM PC board contains 64K bytes of dynamic memory with parity. The memory is organized into four banks, each of which contain 16K bytes. Parity is detected at the bank level. Each bank may be selected or deselected in any one of the four 16K banks the CPU can address. These addressing features are primarily designed for multi-user and sparing operations.

33

## Mini Disk/Printer Interface PC Board (129-23100)

The PC board contains the two-drive mini disk controller and two independent parallel printer ports. The first port is an 8-bit parallel Centronics-compatible interface and the second is a 13-bit Qume-compatible letter quality interface (some popular printers which use the letter quality interface are QUME, NEC, and DIABLO models).

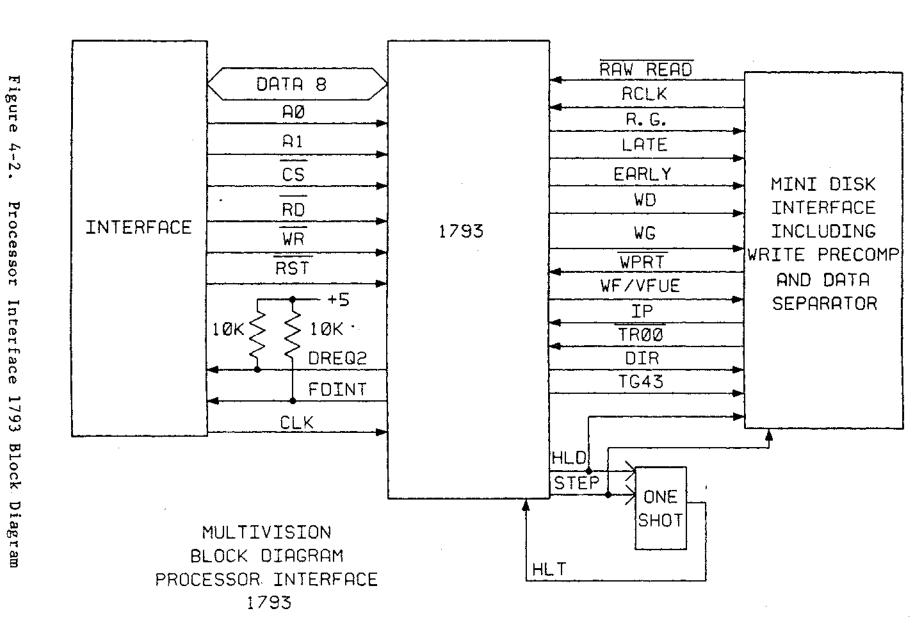

The Mini Disk/Printer Interface is designed around a Western Digital FD1793 disk controller. This circuit, in conjunction with phase lock loop and write precompensation logic, provides the ability to position, format, read, and write both mini disk drives in a double-sided, double-density configuration.

#### Mini Disk Drives

Each drive uses double-sided double-density 5 1/4" disks capable of storing 358K bytes of data for each formatted disk or 716K bytes per system (both disks). Stepping is performed by a band actuator which provides a track-to-track positioning rate of 6mS.

Access is enhanced by treating the top and bottom tracks as cylinders. The disk format is made up of 35 cylinders with 2 tracks per cylinder, 10 sectors per track, and 512 bytes per sector. Under control of MUON (the CP/M compatible operating system designed for Multivision), typical throughput is 25K bytes/second on a track basis and 10K bytes/second averaged over several consecutive cylinders.

Multivision 2 consists of the Multivision l Module plus the Hard Disk Module. The addition of a third drive, the hard disk, provides vastly greater storage capacity and access time, complementing Multivision l's hardware and software features.

#### Hard Disk Module

The Hard Disk Module contains a 10M byte 8" hard disk drive and power supply. The hard disk employs state-of-the-art 8" Winchester technology incorporating such concepts as enclosed head units and lubricated magnetic media surfaces to assure reliability. Unformatted capacity for the disk is 10.67M bytes. The formatted capacity is 8.39M bytes arranged on 256 cylinders each of which contain four tracks with 32 sectors per track and 256 bytes per sector. The instantaneous data transfer rate to system memory is 580K bytes/second. The average rate, on a cylinder basis, is 100K bytes/second which is reduced to 80K bytes/second when averaged over several cylinders. These rates are based on ADDS' MUON Operating System calls.

## Hard Disk Controller PC Board (129-25400 or 129-28700)

The Hard Disk Controller PC board is inserted into the bottom slot of the Multivision 1 backplane. Flat ribbon cables connect the PC board to the actual drive. The controller has a low cost, low parts count, and high reliability design. This is accomplished by a unique dual processor design along with a high system bus bandwidth. The first processor is an 8035 microcomputer which controls all of the slow speed functions of the drive such as head selection, stepping, and interface with the CPU. The second processor is a bipolar ROM-based 32 state sequencer which is driven by the 8035 and provides the required high speed data manipulations. CRC generation, checking, and sector header verification are performed by discrete components. Data is transferred directly to system memory via DMA control from an onboard 16-character FIFO. Since the system bus bandwidth is 1.2M bytes/second and the hard disk's transfer rate is 580K bytes/second, there is ample bandwidth remaining for other concurrent system operations to be performed.

#### Hard Disk Backup

Backup of hard disk files is made possible through the versatility of the mini disks. There are three techniques available:

Transaction backup. Applications must be structured to create transaction files which are used to update hard disk master files and are then saved as a backup library on the mini disks.

- 2. File backup. Entire files are selectively backed up on one or more mini disks, as necessary. Using MUON, an entire mini disk can be filled in 70 seconds.

- 3. Incremental change backup. MUON will copy to mini disk only those records from a given file that have been modified. Since the image on the mini disk is an exact replica of the data on the hard disk, full file dumps are not required. The amount of mini disk storage will always be equivalent to the size of the file. This technique substantially reduces the amount of time required to maintain a backup copy of a hard disk file.

Multivision 3 consists of a Multivision 2 plus the Expansion Module. The Expansion Module is situated between the Multivision 1 Module (top module) and the Hard Disk Module (bottom module). The Expansion Module contains an extension of the system bus which is attached to the Multivision 1 by two connectors. Power is supplied to the expansion bus from the power supply in the Hard Disk Module. The card cage, which is the only subassembly in the Expansion Module, contains slots for four PC boards: a 4 Port I/O PC board, and up to three additional 64K RAM PC boards.

## 4 Port I/O PC Board (129-24700)

The 4 Port I/O PC board contains four fully independent asynchronous serial communication ports. Baud rates are independently selectable (up to 9600 baud). Communication parameters are all software selectable and stored where they are user-modifiable in the CPU PC board's non-volatile memory. The circuitry which controls the ports is designed around the operating system I/O drivers so that maximum system throughput may be obtained in a multi-user environment. For example, access to the four ports is controlled by a steering register located on the PC board; this allows the use of a common software driver. The concurrent operation of the four terminals at 9600 baud is guaranteed by a l6-character FIFO associated with the receive input of each port.

#### Memory Organization

Each 64K RAM PC board in the Expansion Module is identical to the RAM PC board in the Multivision 1 Module. The cards are differentiated by jumper selections.

MUON uses the 64K RAM PC board's bank selection logic to implement multi-user operation. Each user has 48K bytes of real memory, while 16K bytes are always used by the operating system. At task or user switch time, the three banks allocated to the present user are deselected and the next user's three banks are selected. Task switch time is greatly reduced by using real memory to store each user's program instead of the classical disk paging and virtual memory schemes. Because the real memory is stored for each user, a 64K RAM PC board is needed for each user.

Since each user requires only 48K bytes (or three banks) of memory, and only one operating system is needed regardless of the number of users, each time another PCB is installed, another spare memory bank becomes available.

The extra banks may be used if parity errors are detected in other banks. The information regarding the use of a spare bank is stored in the non-volatile memory until the failed PC board is retested. Failed banks are automatically bypassed by the operating system when assigning user memory banks. This is possible due to bank address relocation.

Spare banks may also be used for background tasks. MUON (which is a true multi-tasking operating system) provides features to easily implement these tasks. One such background task, a print queue manager, is provided with the operating system.

Figure 1-1. Multivision System Block Diagram

#### OVERVIEW

The Multivision Central Processing Unit is logically divided into the 12 sections listed in Table 2.1 below and described on the following pages. The CPU Block Diagram, Figure 2-1, shows the major components located on the CPU PC Board. It can be used as a reference to depict interrelationships between the various components.

| Table 2.1. CPU Logic | Sections                                                                                                                                                                                                                      |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Logic Section        | Description                                                                                                                                                                                                                   |  |

| Processor            | 8085A-2 5MHz operating frequency.                                                                                                                                                                                             |  |

| DMA Controller       | An 8237-2 5MHz 4 channel controller.                                                                                                                                                                                          |  |

| CMOS Memory          | The 256 x 8 memory element, used for system parameters, is accessed via I/O ports. Back-up battery power is used to retain these parameters for use by the diagnostic EPROM and operating system.                             |  |

| EPROM                | The 4K x 8 2732 EPROM, used for system power-up diagnostics and coldboot procedure, is disabled after the coldboot operation to free the 4K address space for operation of the system.                                        |  |

| Serial I/O           | Two 8251A USARTs. The first port is used as a console device in a single user system; the second port is used in user-defined serial communications or serial peripheral device operation.                                    |  |

| Timer .              | The 8253-5 Programmable Interval Timer has 3 channels. Channel 0 is used as an interval timer by the operating system for internal timing considerations. Channels 1 and 2 are used as baud rate generators for serial ports. |  |

| Interrupts           | The 8085A has 5 interrupt lines and the 8259A Programmable Interrupt Controller allows direct vectoring for up to 8 additional interrupts.                                                                                    |  |

|               | ntrol Sections (continued)                                                                                                                                                                               |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Section | Description                                                                                                                                                                                              |

| Reset         | Power on reset is a one-shot reset which uses<br>the Reset button on the front panel of Multi-<br>vision l. It provides a .5 second reset pulse<br>to all system peripherals.                            |

| Refresh       | This circuit provides the basic refresh timing for dynamic memory within the system. For detailed information on refresh circuitry, see Section 3, RAM PC Board.                                         |

| RTC           | Real Time Clock circuitry monitors the AC line frequency and provides a 10Hz clock which is used by the interrupt input of the 8259A for real time measurements. RTC is not supported by ADDS' software. |

| Oscillator    | A 20MHz crystal oscillator provides a 10MHz fundamental frequency for the 8085A-2 processor, and provides a 2MHz comm clock used for internal timing in most peripheral devices.                         |

| Decode        | Address I/O decode circuitry, handling all on-<br>board chip select signals, generates an onboard<br>signal for selecting an onboard data bus which<br>allows processor access to onboard devices.       |

:A.

## Functional Description

The 8085A-2 Microprocessor is the heart of the Multivision system. It is a complete 5MHz 8-bit parallel central processor with 16 address lines which can access 64K memory locations and 256 I/O port addresses.

The 8085A-2 has twelve addressable 8-bit registers. Four of them can function only as two 16-bit register pairs. Six others can be used interchangeably as 8-bit registers or as 16-bit register pairs. The 8085A-2 register set is shown in Figure 2-1 below.

| Mnemonic   | Register                                           | Contents                     |

|------------|----------------------------------------------------|------------------------------|

| ACC or A   | Accumulator                                        | 8-bits                       |

| PC         | Program Counter                                    | 16-bit address               |

| BC, DE, HL | General Purpose<br>Registers; data<br>pointer (HL) | 8 bits x 6 or<br>16 bits x 3 |

| SP         | Stack Pointer                                      | l6-bit address               |

| Flags or F | Flag Register                                      | 5 flags (8-bit space)        |

Figure 2-1. 8085A-2 Register Set

The 8085A-2 uses a multiplexed Data Bus. The address is split between the higher 8-bit Address Bus and the lower 8-bit Address/Data Bus. During the first T state (clock cycle) of a machine cycle the low order address is sent out on the Address/Data Bus. These lower 8 bits are latched externally by the Address Latch Enable (ALE) signal. During the rest of the machine cycle the Data Bus is used for memory or I/O data.

The 8085A-2 provides  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $S_0$ ,  $S_1$ , and  $I0/\overline{\text{M}}$  signals for bus control. An Interrupt Acknowledge (INTA) signal is also provided. HOLD, READY, and all interrupts are synchronized with the processor's internal clock. The 8085A-2 also provides Serial Input Data (SID) and Serial Output Data (SOD) lines for simple serial interface.

#### Interrupt Structure

The 8085A-2 has 5 interrupt inputs: TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR.

The interrupts are arranged in a fixed priority that determines which interrupt is to be recognized if more than one is pending. The order is as follows: highest priority -- TRAP, then RST 7.5, RST 6.5, RST 5.5 and, INTR -- the lowest priority. This priority scheme does not take into account the priority of a routine that was started by a higher priority interrupt. RST 5.5 can interrupt an RST 7.5 routine if the interrupts are re-enabled before the end of the RST 7.5 routine.

The three maskable interrupts, RST 5.5, 6.5 and 7.5, initiate the internal execution of RESTART (saving the program counter in the stack and branching to the RESTART address) if the interrupts are enabled and if the interrupt mask is not set. TRAP, the non-maskable interrupt, causes the internal execution of a RESTART vector independent of the state of the interrupt enable or masks.

There are two different types of inputs in the restart interrupts. RST 5.5 and RST 6.5 are high level-sensitive as INTR (and INT on the 8080) and are recognized with the same timing as INTR. RST 7.5 is rising edge-sensitive.

Interrupts 5.5 and 6.5 are connected to the USARTs which control the two serial ports on the CPU PC board. Interrupt 5.5 generates an interrupt whenever the console port USART has a character ready to be input to the CPU. The communications port USART receiver ready is connected to Interrupt 6.5.

Interrupt 7.5 is connected to Counter 0 of the 8253 timer chip. This interrupt is used by MUON to control task scheduling and for the system timer services.

The RST 7.5 requires only a pulse to set an integral flip-flop which generates the internal interrupt request. This flip-flop remains set until the request is serviced. Then it is reset automatically. The RST 7.5 internal flip-flop will be set by a pulse on the RST 7.5 pin even when the RST 7.5 interrupt is masked out. This flip-flop may also be reset by using the SIM instruction or by issuing a RESET IN to the 8085A-2.

The status of the three RST interrupts can only be affected by the SIM instruction and RESET IN.

Interrupt INTR is connected to an 8259A Programmable Interrupt Controller, providing an additional 8 interrupt lines to the 8085A-2.

See the Intel Component Data Catalog for the hardware specifications for this chip, and also the Intel 8080/8085 Assembly Language Programming Manual for information on programming this part.

5.6

## Functional Description

The Multivision CPU makes use of the 8237-2 DMA Controller to reduce the burden placed on the system's software and hardware for data transfers between memory and peripherals such as the mini disk and the hard disk. The device is also capable of performing transfers of data blocks from one memory block to another, reducing the time required for these operations.

DMA (Direct Memory Access) is an operation whereby control of the system bus is taken away from the processor (the 8085) and given to the DMA Controller. Once the Controller is programmed, it remains in an idle state until there is a need for data transfer. The Controller receives an active signal on one of its DREQ (DMA request) lines and, if the device has been programmed to respond to that DREQ, it will issue a HOLD signal to the pro-When the processor receives this hold signal, completes the operational cycle it is currently in, places program and status information on its stack, and goes into an idle state, freeing the bus for DMA operation. When the processor goes into this idle state, it issues a hold acknowledge (HLDA) signal to the DMA device. Upon receiving HLDA, the Controller initiates a data transfer by placing the address information stored in that channel's address register. The Controller then issues the signal DACK (DMA acknowledge) for the channel it is responding to. While DACK is active, the Controller issues the appropriate read/write signals. The DACK signal is used by the requesting device as a device select, allowing the read/write signals to affect the device, completing the data transfer. Upon completion of the transfer, the Controller goes inactive, placing HOLD and DACK in the idle This allows the processor to regain control of the system.

For peripheral to system operations (mini disk, hard disk), the Controller is used in the demand mode of operation, which initiates single byte transfers, until the channel count register reaches completion count. This is done to minimize the time taken from the processor since the mini disk and hard disk interfaces require a relatively large amount of time to make a character available to the Controller.

For memory-to-memory operations, the Controller is used in a block transfer format, as the data is immediately available for the Controller. Memory-to-memory transfers make use of an internal data storage register within the Controller. The Controller first reads the data from the source address, stores the data in this register, then writes the data to the destination address.

Source and destination addresses are stored internally, utilizing channels 0 and 1 of the Controller. For a complete description of the 8237-2, refer to the appropriate Intel documentation.

#### Software Operations

Table 2.2. Multivision Port Assignments for DMA

| Port Number   | Register          |  |

|---------------|-------------------|--|

| ОАОН          | channel 0 address |  |

| 0A1H          | channel O count   |  |

| 0A2H          | channel l address |  |

| 0A3H          | channel 1 count   |  |

| 0A4H          | channel 2 address |  |

| 0A5H          | channel 2 count   |  |

| OA6H          | channel 3 address |  |

| 0A7H          | channel 3 count   |  |

| 0A8H          | status            |  |

| 0A8H          | command           |  |

| 0 <b>A</b> 9H | request           |  |

| OAAH          | mask              |  |

| OABH          | mode              |  |

| 0ACH          | clear flip-flop   |  |

| OADH          | reset             |  |

| OAFH          | mask write        |  |

The following examples illustrate the use of the 8237 for data transfer under MUON.

## 1. Memory-to-Memory DMA Transfer

For memory-to-memory data transfer, channel 0 is programmed as the source and channel 1 as the destination. The 8237 may be programmed as follows:

c. Set source A<--Transfer count -1 (low byte)

count register OUT OA1H

(channel 0) A<--Transfer count -1 (high byte)

OUT OA1H

d. Set destination A<--Destination address (low byte)

address register (channel 1) OUT OA2H

A<--Destination address (high byte)

OUT OA2H

e. Set destination A<--Transfer count -1 (low byte) OUT 0A3H (channel 1) A<--Transfer count -1 (high byte) OUT 0A3H

f. Set mode register MVI A,88H for channel 0 block OUT OABH read and channel 1 MVI A,85H block write (address OUT OABH increment is selected and auto initialize is deselected)

g. Set command register MVI A,41H for memory-to-memory OUT 0A8H transfer

h. Set request register MVI A,04H to begin transfer OUT 0A9H (no instructions will be executed until the transfer is completed)

## 2. Memory <=> Mini Disk DMA Transfer

Channel 2 is used for data transfer between the Mini Disk Controller and memory. The following steps show how to set up the 8237 for demand mode DMA which is initiated by requests from the disk controller for disk data transfer.

| a. | Clear flip-flop                                                                                                               | OUT OACH                                                                                                                  |

|----|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| b. | Set address register for channel 2                                                                                            | A <memory (low="" address="" byte)<br="">OUT OA4H<br/>A<memory (high="" address="" byte)<br="">OUT OA4H</memory></memory> |

| c. | Set count register for channel 2 (the count should be the same as the number of requests that the disk controller will issue) | A <transfer (high="" (low="" -1="" 0a5h="" 0a5h<="" a<transfer="" byte)="" count="" out="" td=""></transfer>              |

| d. | Set mode register for demand mode read or write on channel 2 (auto initialization is disabled, address increment is selected) | MVI A,OAH (memory-to-mini disk) or MVI A,O6H (mini disk-to-memory) OUT OABH                                               |

| е. | Set command register non-memory-to-memory DMA                                                                                 | MVI A,40H<br>OUT OA8H                                                                                                     |

| f. | Set mask register to set channel 2 mask                                                                                       | MVI A,02H<br>OUT OAAH                                                                                                     |

## 3. Memory <=> Hard Disk DMA Transfer

Channel 3 is used for data transfer between the Hard Disk Controller and memory. Below is an example of the programming steps required to set up this channel for a read or write data transfer.

a. Clear flip-flop OUT OACH

b. Set address register A<--Memory address (low byte)

for channel 3 OUT OA6H

A<--Memory address (high byte)

A<--Memory address (high byte)

OUT OA6H

c. Set count register A<--Transfer count -1 for channel 3 (low byte)

OUT 0A7H A<--Transfer count -1

(high byte) OUT OA7H

d. Set mode register for MV1 demand read or write, address increment MV1 selected and auto

MV1 A,OBH (write) or

MV1 A,07H (read)

e. Set command register for non-memory-to-memory DMA

initialize disabled

MV1 A,40H OUT OA8H

f. Set mask register to set channel 3 mask

MV1 A,3 OUT OAAH

## Functional Description

The CMOS memory circuit utilizes two 5101L-1 256 x 4 bit memory chips. These ICs are capable of storing information while in a "power down" state by drawing current from a backup power source. The power source used on the CPU is a 3 volt lithium battery with a design life of five years in the circuit used by the CPU. This battery supplies a 2 volt Vcc for the memory chips while the systemm is powered down, allowing the ICs to retain data. When the system is powered up, the 5 volt system supply provides Vcc for the ICs. The drain on the battery is shut down by the use of a diode which overrides the current flow from the battery to the memory chips.

The CMOS memory is accessed through the use of I/O ports, so the memory elements do not use memory space allocated for system use. I/O port 98H activates CMOS by raising the level of the chip disable (standby mode) pin in the memory chip. It is necessary to activate the circuit prior to any read or write to CMOS. After access is complete, the circuit must be disabled to prevent possible data loss during system power down. Writing an '04' to I/O port 98H activates the circuit, while writing a '00' to port 98H disables the circuit. Accessing port 98H toggles a flip-flop circuit providing a chip enable/disable signal for the memory chip.

In order to read or write data to memory after it has been enabled, you must first load in the memory address you wish to access (00H-FFH) by writing the address into port 92H. This activates an 8-bit latch which holds the address information stable on the memory chip address line. To read or write to this memory location, simply read or write to port 93H, as this port activates the read/write pins of the memory chip. In order to access another memory location in CMOS, it is necessary to again set up the proper address by writing to port 92H, then reading or writing to port 93H to manipulate the data at that location in memory. After all memory accesses are finished, write a '00H' to port 98H to disable the memory circuit.

CMOS memory is used by the "shadow" EPROM during diagnostic self-testing of the system, and by the operating system for initialization of system parameters for proper system operation. Any errors found by the diagnostic programs are stored in a table located in CMOS, and the diagnostic program refers to this table whenever self-testing is active. Any errors flagged in CMOS will be displayed on the console screen and, if required, the operator must take appropriate action to correct these errors. The shadow EPROM also uses CMOS to set up the system parameters of the particular system in use (e.g., memory allocation, terminal configuration, disk configuration, etc.). During loading of the operating system (bootstrap operation), CMOS is accessed so the operating system can check and set system parameters and check memory allocation tables as required.

In order to insure that the data stored in CMOS is correct, the system makes use of a check-sum operation within CMOS. This entails making a count of the number of bits high within the CMOS memory and calculating a check-sum to determine if the bit total has changed. If no change has occured, it is assumed that the data stored in the memory is valid. If the check-sum is incorrect, the shadow EPROM will use a set of default parameters stored within the EPROM for system initialization. It will then store these parameters within CMOS and calculate a new check-sum, placing the check-sum in CMOS memory.

A further step to insure data integrity is the use of a "triple redundancy" scheme, where the data is stored in three identical blocks, each with a checksum. The PROM or operating system reads block one and its checksum is verified. If the checksum is correct, the data is used to update the other two blocks. If the checksum is incorrect, it goes to block two. Block two is then read and, if the checksum is correct, the data stored in this block is used to update blocks one and three, etc. The good "third" will always update the other two blocks.

## Programming CMOS

Information is passed from the Diagnostic/Bootstrap program to the operating system through 256 bytes of non-volatile CMOS RAM. Recorded here are the results of the diagnostic portion of the program, the bank number containing the booted operating system, and certain other system parameters such as console baud rate and parity settings. CMOS is accessed as an I/O peripheral through the following ports:

| PORT |             | USAGE                 |  |  |

|------|-------------|-----------------------|--|--|

| 92H  | Write only: | CMOS Address Register |  |  |

| 93H  | Read/Write: | CMOS Data Register    |  |  |

CMOS must be "turned on" before reading or writing any data. This is done by outputting a '4' to port 98H, then waiting at least 10 milliseconds. CMOS should be "turned off" after all CMOS operations are complete by outputting a '0' to port 98H.

Refer to the topic entitled Diagnostic/Bootstrap and System Load for details on the layout of information in CMOS.

Programming examples for manipulating CMOS are shown below:

To determine the diagnostic for the console port on the CPU, the result is returned in register A:

| GETDIA: |       |                                |

|---------|-------|--------------------------------|

| MVI     | A,05H | :Select the CMOS address       |

| OUT     | 92H   | ,                              |

| IN      | 93H   | :Read the data at that address |

| RET     |       | ,                              |

2. To update the contents of a given address of CMOS while correctly maintaining the checksum byte, the update address is passed in register D, and the new data value is passed in register E. This routine only updates the first CMOS block:

#### WRCMOS: MOV A,D ;Select address to be updated. OUT 92H IN 93H Read current data value there. MOV B , A ;Save current value in B MOV A,E ;and write new value there. TUO 93H VOM A,053H ;Select address of checksum byte. TUO 92H IN 93H ;Read current checksum. SUB В ;Subtract old data value ADD Ε ; and add in new data value. OUT 93H ;Write out new checksum value. RET The end.

## Functional Description

The shadow EPROM 2732 resides on the CPU PC board. It contains a set of diagnostic programs which test all elements within the system. The EPROM has a set of messages stored which provide the operator with error information, system status information, and operator prompts which are used when the system requires outside input. Included in the program set are:

- 1. Memory Diagnostics -- This program places an alternating pattern of "ones" and "zeros" within system memory and then checks the pattern for any changes. If any changes occur, the memory bank being tested is flagged as bad and an error message is displayed on the system console, indicating which bank and memory board are affected. This program will test all memory within the system, up to the 256K used in a multi-user system.

- 2. Serial I/O -- All serial I/O ports within the system are tested utilizing the loop test feature of the serial ports. This program initializes the USARTs, places the channel in loopback, and outputs a character through the port. It then reads the character received by the channel and compares this character to the character sent out. If the characters do not match, the EPROM will issue an error message to the screen indicating which PCB contains the defective serial port. This program tests not only the serial device, but also the associated timer, which supplies the port baud rate, and tests much of the gating logic associated with these ports.

- 3. CMOS -- This program reads CMOS, calculates a check sum and then compares the check sum calculated with the check sum already stored in CMOS. If there is an error, a message is sent to the console device and the CMOS is cleared. New system parameters are then stored in CMOS using a table stored in the EPROM, and a new check sum is then calculated and stored in CMOS.

- 4. Mini Disk -- This program tests the Mini Disk Controller (an-FD1793) by outputting information to the controller device. The program writes to the registers within the 1793, and then reads back from those registers to insure the device can be written to and read from. The program also issues a restore command to the 1793 in order for it to be in a known state for the boot operation which takes place upon completion of diagnostic testing.

- 5. Interrupt Controller -- This program tests the Interrupt Controller by programming the device to respond to an interrupt and then issuing the correct vector address for the 8085. The program places a jump instruction at this address which will return the system to the diagnostic program's control. If the Interrupt Controller does not respond properly, the program issues an error message to the console device and flags the error in CMOS.

- 6. Interval Timer -- This program sets up the interval timer's channel 0 to issue a pulse in a specific amount of time. The output of channel 0 triggers RST 7.5 in the 8085. If the timer does not respond within the correct time, the program issues an error message and flags CMOS. Channels 1 and 2 of the timer are tested during the serial port test.

- 7. DMA Controller -- This program tests the DMA Controller by writing to the internal registers of the device and reading back the data to be sure it is correct. It then programs the DMA Controller for a memory-to-memory transfer operation, placing a known data pattern in the source memory block, and issuing the command to execute the transfer operation. The program then compares the data in the source memory block with the data in the destination memory block to determine whether the data was transferred properly. If the data is not correct, an error message is issued and the error is flagged in CMOS.

- 8. Real Time Clock -- This program determines whether the circuit is issuing a 10Hz signal by programming the Interrupt Controller to respond to the real time clock interrupt (INT 6). If an interrupt does not occur, an error message is generated and the error is flagged in CMOS.

16

## Diagnostics/Bootstrap and System Load

The Multivision Diagnostic/Bootstrap program is contained in the 2732 EPROM. I/O port 9CH controls this EPROM which, when enabled, occupies memory address space 0000H to 0FFFH. Upon power-up or system reset, the EPROM is enabled, control is passed to location 0000H, and program execution begins. Upon successful completion of the diagnostic and bootstrap procedure, the operating system will have been read into a memory bank occupying the address space 0C000H to 0FFFFH, the EPROM is disabled, and control is transferred to address 0C000H.

The EPROM is activated by outputting a "one" to port 9CH; it is deactivated when a "zero" is written to 9CH.

Information is passed from the Diagnostic/Bootstrap program to the operating system through 256 bytes of non-volatile CMOS RAM. Recorded here are the results of the diagnostic portion of the program, the bank number containing the booted operating system, and certain other system parameters such as console band rate and parity settings. Refer to Section 3, RAM PC board, for details accessing the information stored there.

Table 2.3 contains the layout of the information which is passed to CMOS from the Diagnostic/Bootstrap Program.

| Table 2.3.                                                                | CMOS RAM Layou                          | t                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte(s)                                                                   | Bit(s)                                  | Usage                                                                                                                                                                                                                                                                                                                                            |

| 00н                                                                       | 7 (MSB)<br>6<br>5                       | Diagnostic on Memory Bank 0<br>Diagnostic on Memory Bank 1<br>Diagnostic on Memory Bank 2                                                                                                                                                                                                                                                        |

|                                                                           | 6<br>5<br>4<br>3<br>2<br>1<br>0 (LSB)   | Diagnostic on Memory Bank 3 Diagnostic on Memory Bank 4 Diagnostic on Memory Bank 5 Diagnostic on Memory Bank 6 Diagnostic on Memory Bank 7                                                                                                                                                                                                      |

| 01н                                                                       | 7 (MSB)<br>6<br>5<br>4<br>3<br>2        | Diagnostic on Memory Bank 8 Diagnostic on Memory Bank 9 Diagnostic on Memory Bank A Diagnostic on Memory Bank B Diagnostic on Memory Bank C Diagnostic on Memory Bank D                                                                                                                                                                          |

| 02H<br>03H                                                                | 1<br>0 (LSB)                            | Diagnostic on Memory Bank E Diagnostic on Memory Bank F Bank Number Occupied by System Mini Disk Booted from O - Drive A                                                                                                                                                                                                                         |

| 04H<br>05H                                                                |                                         | <pre>l - Drive B Hard Disk Diagnostic CPU Board Port Diagnostic bit 0 - Console fail</pre>                                                                                                                                                                                                                                                       |

| 06H<br>07H<br>08H<br>09H<br>0AH<br>0BH<br>0CH<br>0DH<br>0EH<br>0FH<br>10H |                                         | bit 7 - EIA fail Serial Port 0 Diagnostic Serial Port 1 Diagnostic Serial Port 2 Diagnostic Serial Port 3 Diagnostic Console/Serial Port 0 Baud Rate Console/Serial Port 0 Parity Serial Port 1 Baud Rate Serial Port 1 Parity Serial Port 2 Baud Rate Serial Port 2 Parity Serial Port 3 Baud Rate Serial Port 3 Baud Rate Serial Port 3 Parity |

| 12H<br>13H-52H                                                            | 7 (MSB)<br>6<br>5<br>4<br>3<br>2<br>1,0 | Memory Card O Present/Absent Memory Card I Present/Absent Memory Card 2 Present/Absent Memory Card 3 Present/Absent Serial Port Card Present/Absent Hard Disk Controller Present/AbsentReservedReserved                                                                                                                                          |

<sup>\*</sup>See notes regarding this layout on following page

#### NOTES

- 1. Memory banks 0-3 reside on RAM PC board 0, banks 4-7 on PC board 1, banks 8-B on PC board 2, and banks C-F on PC board 3. Memory card 0 is in the Multivision 1 Module. Cards 1,2 and 3 are present in the Expansion Module.

- 2. Bits 7-2 of byte 12H indicate the presence of a PC board if set, or its absence if reset.

- 3. The memory bank diagnostics in bytes 00H and 01H indicate that a given bank failed the test if it was reset. A set bit indicates either that the bank passed or the bank is not physically present. A memory bank is available for system use if the PC board on which it resides is present in the system, and if it passed the diagnostic test.

- 4. The disk and port diagnostics (bytes 03H to 09H) are reported as a zero value for pass, nonzero for fail.

- 5. In a Multivision 1 or 2, the console port is on the CPU PC board, and its baud rate and parity settings are indicated in bytes OAH and OBH respectively. In a Multivision 3, the console ports are on the 4 Port I/O Interface PC board in the Expansion Module, and the baud rate and parity settings are given in bytes OAH to 11H.

- 6. The correspondence between baud rate settings and baud rates is shown below:

| SETTING    | BAUD RATE    |

|------------|--------------|

| 30H        | 110          |

| 31H<br>32H | 150<br>300   |

| 33H<br>34H | 1200<br>1800 |

| 35H        | 2400         |

| 36H<br>37H | 4800<br>9600 |

| 38H<br>39H | 75<br>600    |