## PRELIMINARY

### Diablo Systems Incorporated A Xerox Company

# HyTerm Communications Terminal Model 1660 Maintenance Manual

400083-01 Rev. B July, 1978

© Copyright 1978 Diablo Systems, Inc. (A Xerox Company) Hayward, California 94545

"Diablo," "HyType," and "Xerox" are registered trademarks of Xerox Corporation. "HyTerm" is a trademark of Diablo Systems, Inc.

#### PREFACE

This manual contains only Theory of Operation (Section 2) and Maintenance (Section 3) information, and schematics and logic drawings (Section 4). Refer to the Product Description manual, no. 400082, for operation instructions, specifications, functional description, interface information and installation instructions.

This is a preliminary edition. Comments and suggestions on this manual and its use are welcome. Please complete the pre-addressed comment card bound in the back of this manual. Your cooperations is appreciated.

Diablo Systems, Inc., reserves the right to make improvements to products without incurring any obligation to incorporate such improvements in units previously sold.

#### WARRANTY

The Diablo HyTerm Communications Terminal Model 1641 is warranted against defects in materials and workmanship for 90 days from the date of shipment. Any questions with respect to the warranty should be directed to your Diablo sales representative. All requests for repairs should be directed to the Diablo repair depot in your area. This will assure you of the fastest possible service.

#### TABLE OF CONTENTS

| SECTIO | N 1 — IN7 | rrodu   | CTIO    | N      |       |        |       |     |   |   |   |   |   |   |   |      |

|--------|-----------|---------|---------|--------|-------|--------|-------|-----|---|---|---|---|---|---|---|------|

| 1.1    | GENERA    | AL DES  | SCRIP'  | rion   | •     |        | •     | •   |   |   |   |   |   |   |   | 1-1  |

| 1.2    | SCOPE     |         |         | •      | •     | •      | •     |     |   |   |   |   |   | • |   | 1-1  |

| 1.3    | RELATE    | ED DOG  | CUME    | NTS    | •     |        | •     | •   |   | • | • |   | • | • |   | 1-1  |

|        |           |         |         |        |       |        |       |     |   |   |   |   |   |   |   |      |

| SECTIO | N 2 — TH  | EORY    | OF O    | PERA   | TION  | 1      |       |     |   |   |   |   |   |   |   |      |

| 2.1    | INTROD    | UCTIC   | ON .    | •      | •     |        | •     |     | • | • | • |   |   |   |   | 2-1  |

| 2.2    | PROCES    | SSOR (1 | HPRO    | 3) BO  | ARD   |        |       |     |   |   |   | • |   |   |   | 2-3  |

|        | 2.2.1     | Gener   | al Ope  | eratio | n     |        | •     |     |   | • |   |   |   |   |   | 2-3  |

|        | 2.2.2     | 8080A   | Micro   | oproc  | essin | g Un   | it (M | PU) |   | • |   |   |   |   | • | 2-5  |

|        | 2.2.3     | Clock   | Gener   | rator  |       | -      |       |     |   |   |   |   |   | • | • | 2-8  |

|        | 2.2.4     | Bus D   | river/S | Syster | n Co  | ntro   | ller  |     |   |   |   |   |   |   |   | 2-9  |

|        | 2.2.5     | Memo    | ry .    |        |       |        |       |     |   |   | • |   |   |   | • | 2-11 |

|        | 2.2.6     | Input/  | Outpu   | t.     |       |        |       |     |   | • | • |   |   |   |   | 2-14 |

|        | 2.2.7     | Misce   | llaneo  | us Cir | cuit  | гу     |       |     |   |   |   |   |   |   |   | 2-20 |

| 2.3    | XMEM (    | EXTRA   | A MEM   | ORY)   | ВО    | ARD    |       |     |   |   |   |   |   |   |   | 2-20 |

|        | 2.3.1     | Applio  | cation  |        |       |        |       |     |   |   |   |   |   |   |   | 2-21 |

|        | 2.3.2     | Basic   | XMEN    | 1 Boai | rđ    |        |       |     |   |   |   |   |   |   |   | 2-21 |

|        | 2.3.3     | XMEN    | M Conf  | ʻigura | tions | · .    |       |     |   |   | • | • |   |   |   | 2-21 |

|        | 2.3.4     | Addre   | essing  |        |       |        |       |     |   |   |   |   |   |   | • | 2-21 |

|        | 2.3.5     | Addit   | ional A | Applic | atio  | ns     |       |     |   |   |   |   |   |   |   | 2-22 |

| 2.4    | MATRIX    | INTE    | RFAC    | E BOA  | ARD   |        | -     | -   |   |   |   |   |   |   |   | 2-22 |

|        | 2.4.1     | I/O Po  | orts 5  | and 6  |       |        |       |     |   |   |   |   |   |   |   | 2-22 |

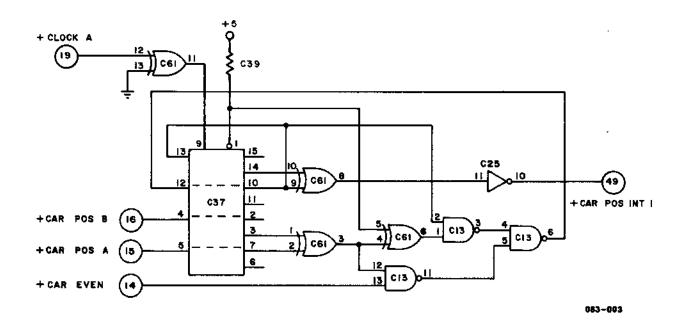

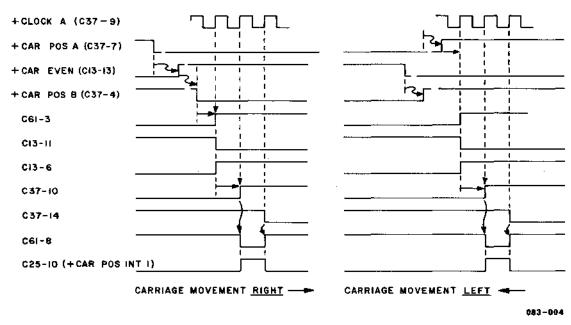

|        | 2.4.2     | Carrie  | age Po  | sition | Dat   | a      |       |     |   |   |   |   |   |   |   | 2-24 |

|        | 2.4.3     | Carrie  | aga Di  | rectic | n Ca  | nm m e | an de |     |   |   |   |   |   |   |   | 2-25 |

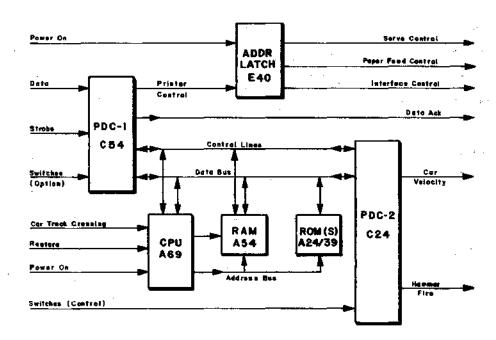

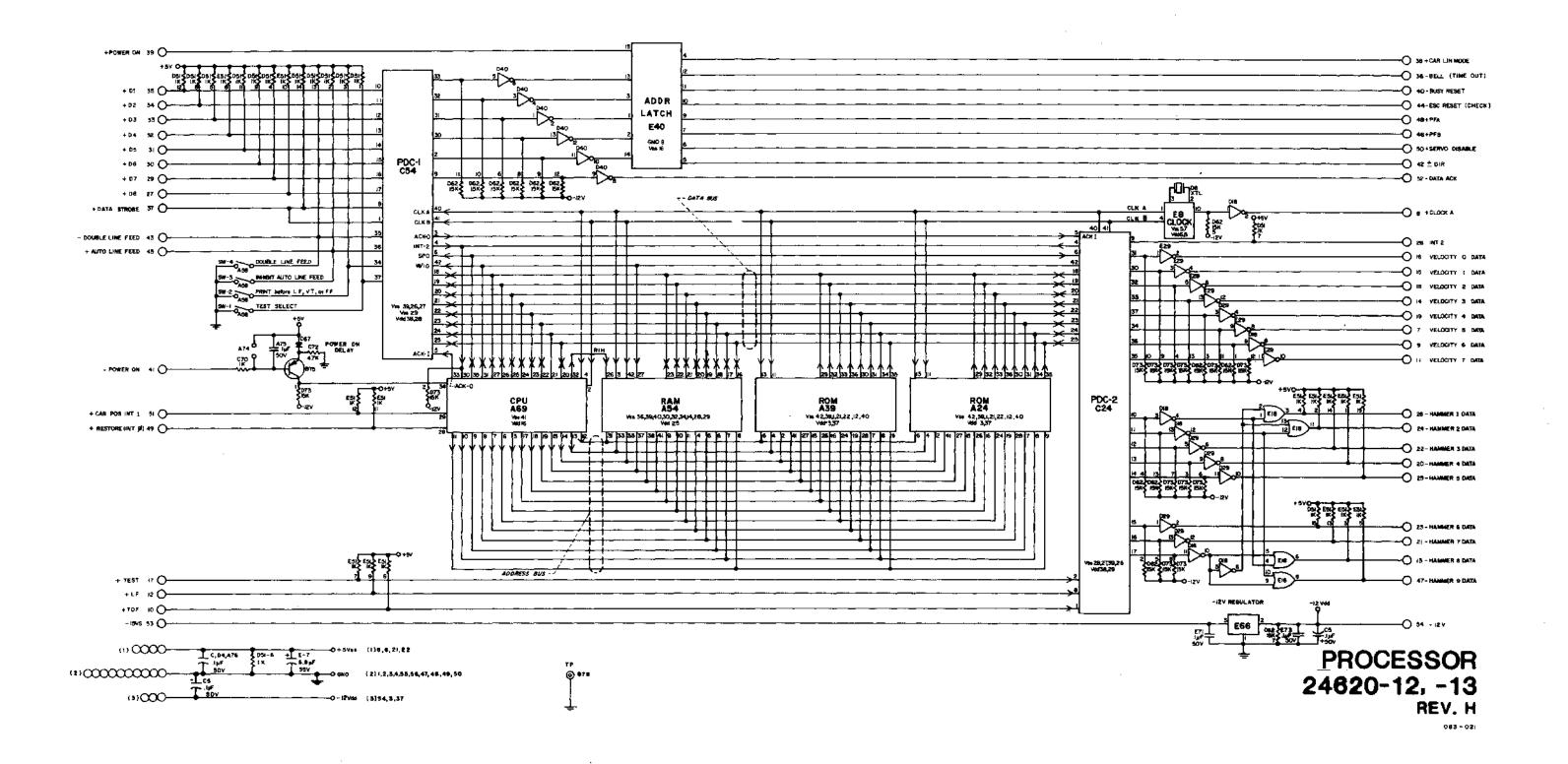

| 2.5    | PROCES   | SSOR (PRINTER) .       | •       | •     | •    | •    | • | • | • | • | • | • | 2-26 |

|--------|----------|------------------------|---------|-------|------|------|---|---|---|---|---|---|------|

|        | 2.5.1    | Chip Task Assignment   |         |       | •    | •    |   |   | • | • |   |   | 2-26 |

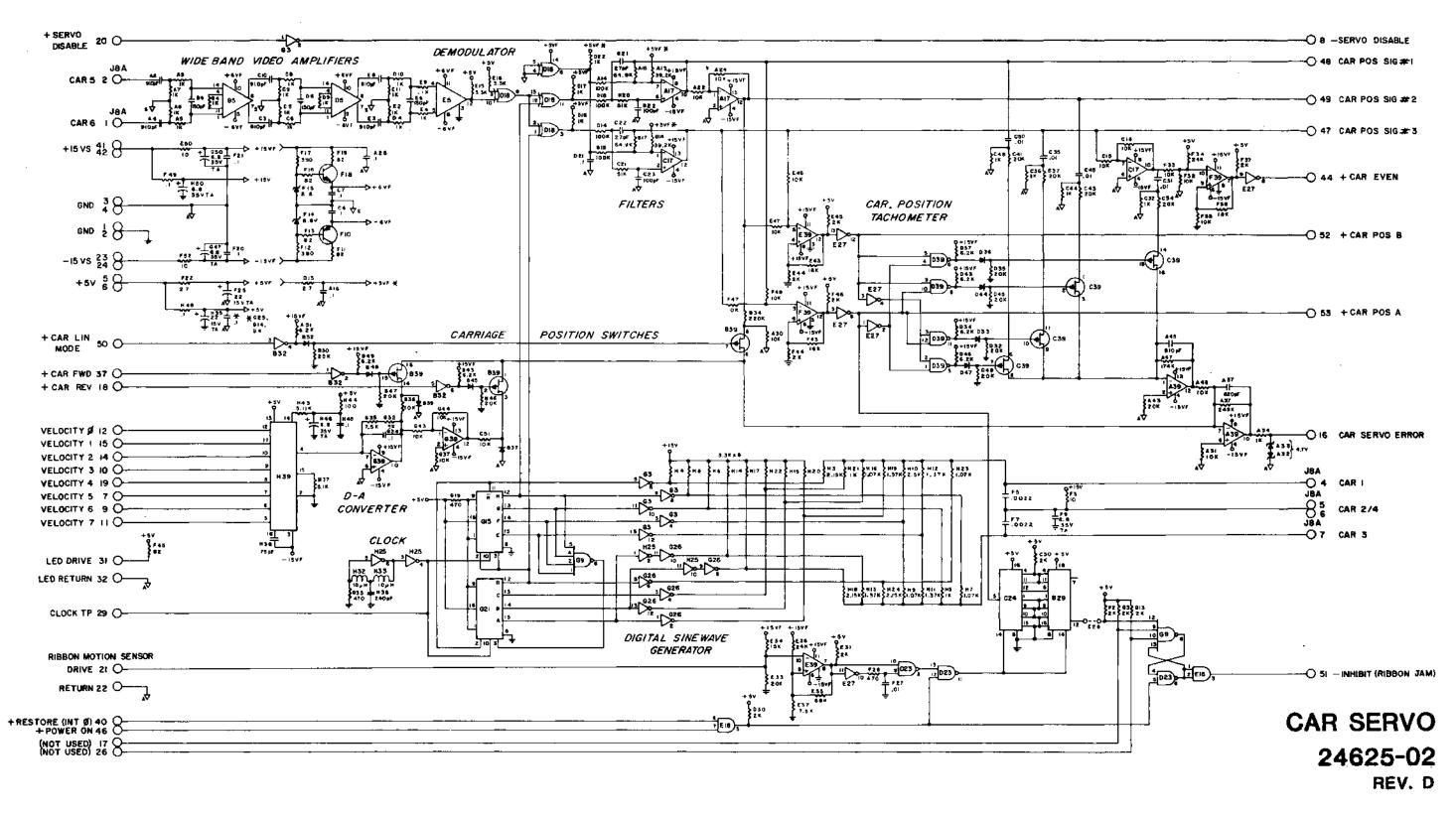

| 2.6    | CARRIA   | GE SERVO BOARD         |         |       |      |      |   |   |   |   |   |   | 2-29 |

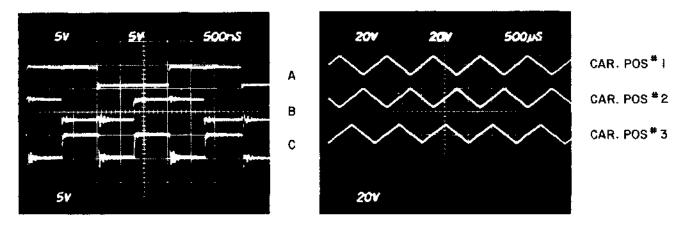

|        | 2.6.1    | Digital Sinewave Gene  | erator  | ,     | •    |      |   |   |   |   |   |   | 2-30 |

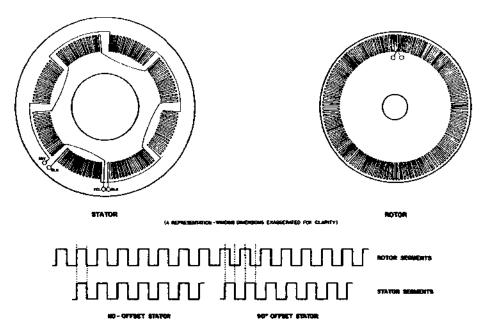

|        | 2.6.2    | Servo Position Transd  | ucer    | •     | •    |      | • |   |   | • |   |   | 2-31 |

|        | 2.6.3    | Servo Feedback Ampl    | ifier   | •     |      |      |   |   |   |   |   |   | 2-31 |

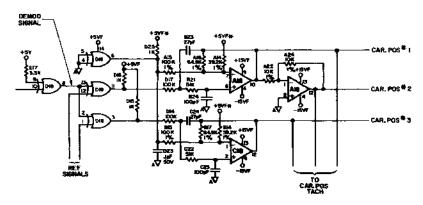

|        | 2.6.4    | Servo Feedback Demo    | dulat   | or/A  | mpli | fier |   |   |   |   |   |   | 2-33 |

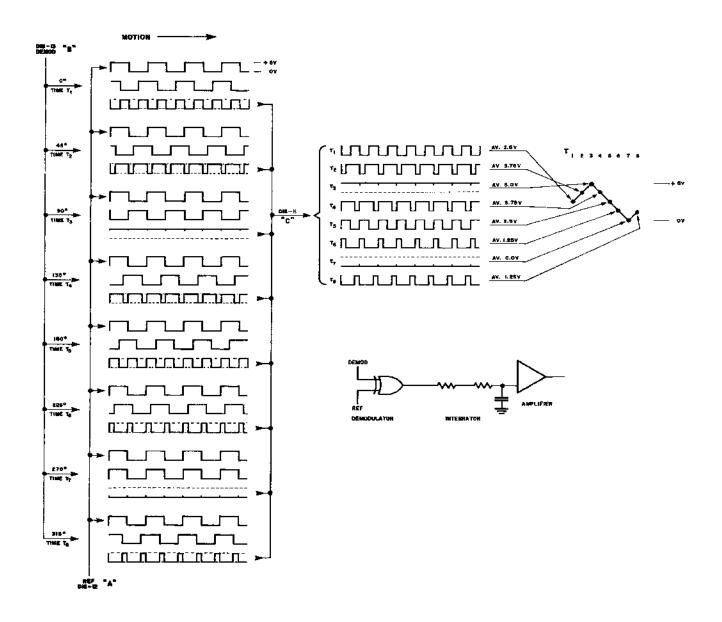

|        | 2.6.5    | Carriage Position Tac  | home    | ter   | •    |      | • |   |   | • |   |   | 2-35 |

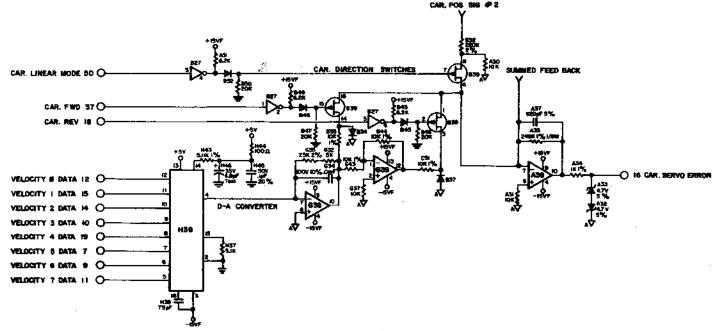

|        | 2.6.6    | Carriage Velocity Con  | nman    | đ     |      |      |   |   |   |   |   |   | 2-37 |

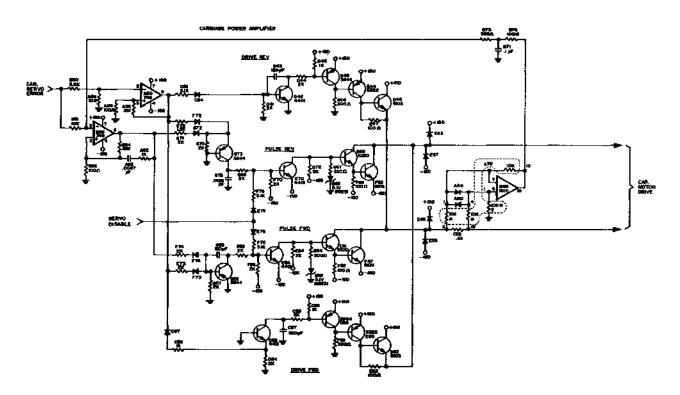

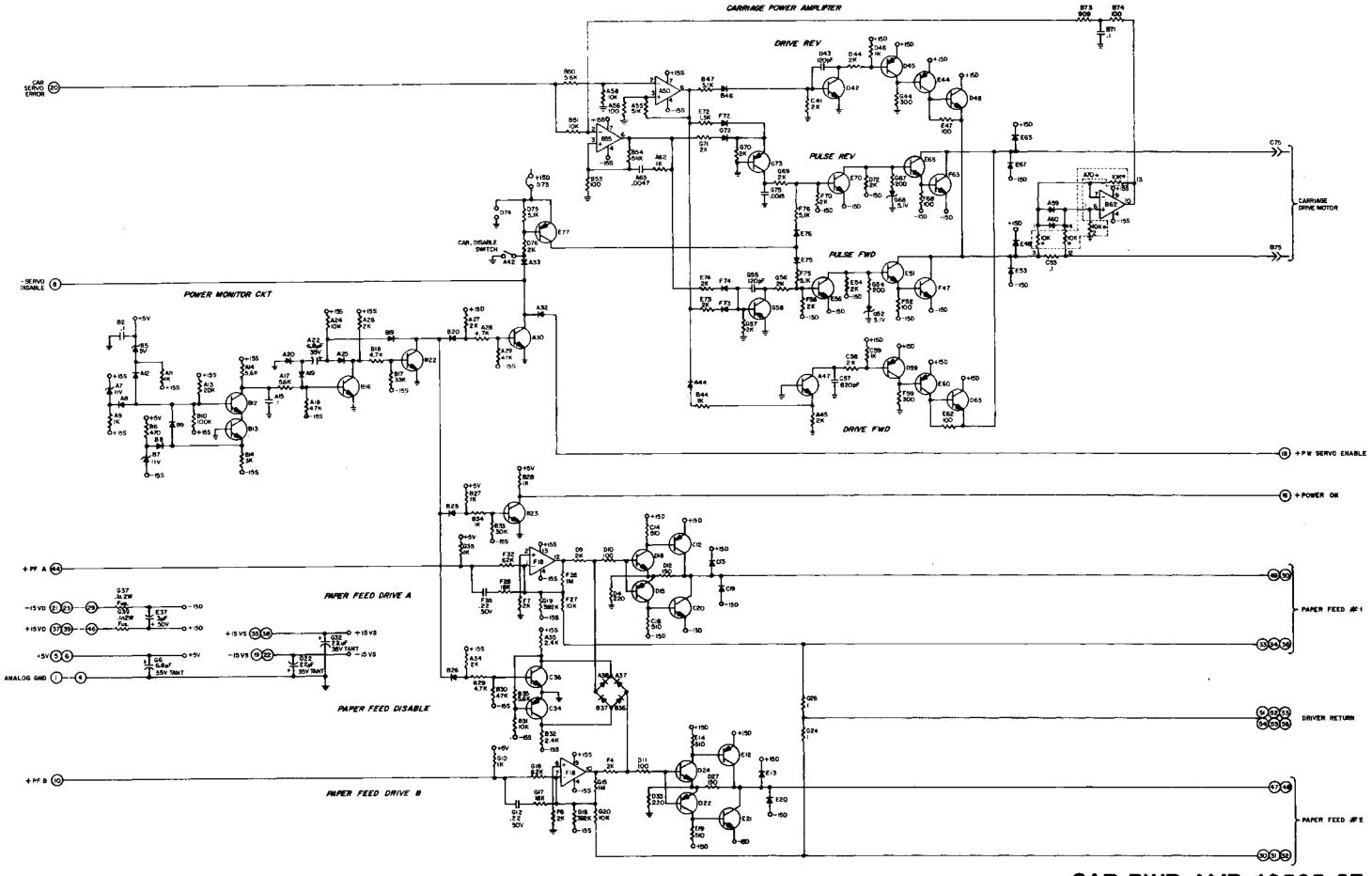

| 2.7 CA | RRIAGE I | POWER AMPLIFIER BO     | DARĐ    | 1     |      |      |   |   |   |   | • |   | 2-41 |

|        | 2.7.1    | Carriage Power Ampli   | ifier ( | Circu | uit  | •    |   |   |   |   | • | • | 2-41 |

|        | 2.7.2    | Power Monitor Circuit  | t.      |       |      |      |   |   | • |   |   |   | 2-43 |

|        | 2.7.3    | Paper Feed Drive Circ  | euit    | •     |      |      |   |   |   |   |   |   | 2-44 |

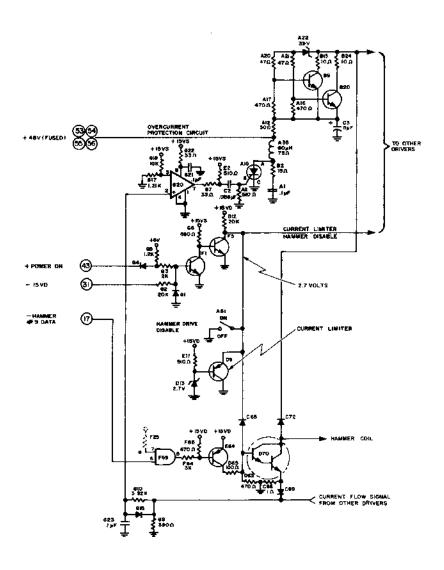

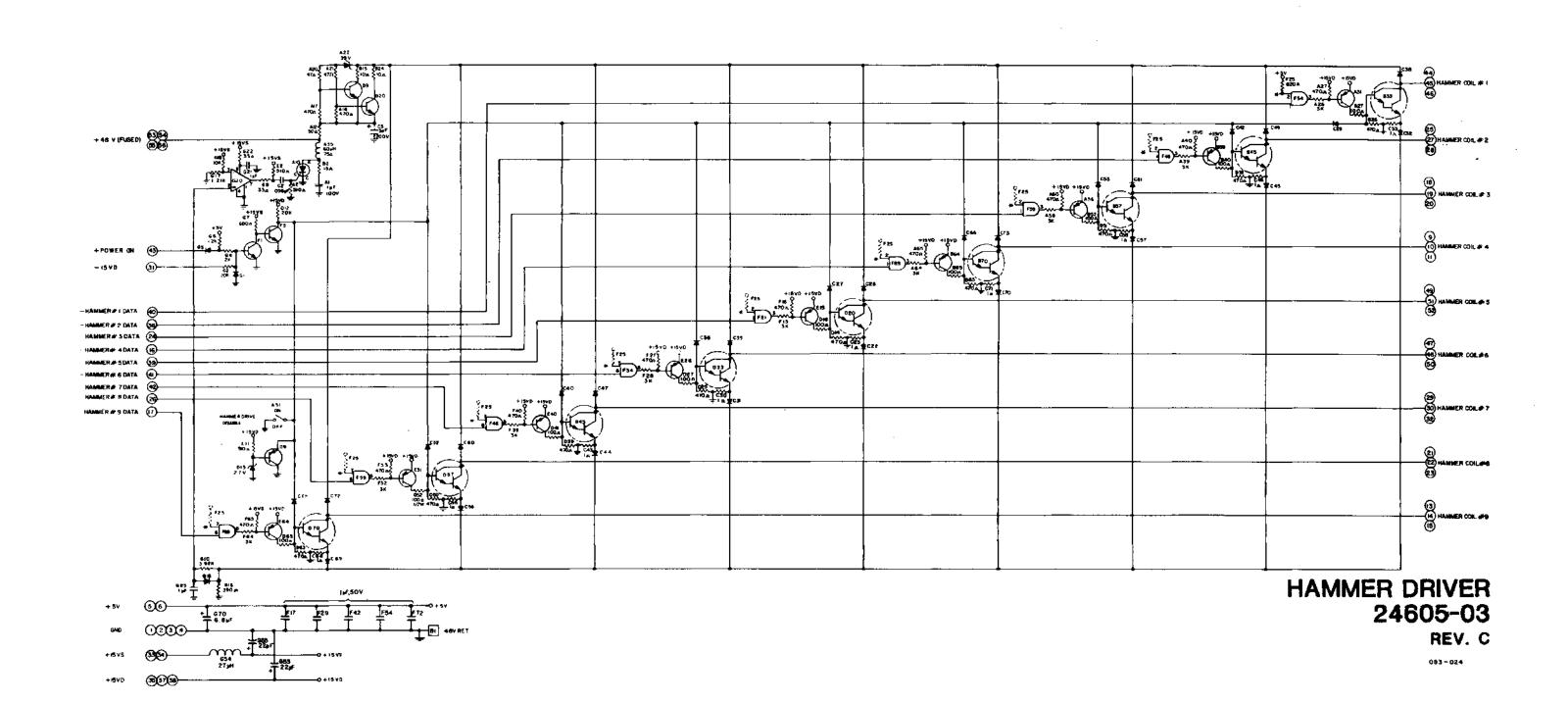

| 2.8    | MATRIX   | HAMMER DRIVER BO       | OARD    | )     |      |      |   | • |   |   |   |   | 2-47 |

|        | 2.8.1    | Hammer Driver Circu    | it      | •     |      |      |   |   |   |   |   |   | 2-47 |

|        | 2.8.2    | Hammer Coil Protecti   | ion Ci  | rcui  | t    |      |   |   | • | • |   |   | 2-47 |

|        | 2.8.3    | Surge Suppression .    | •       | •     |      |      |   |   |   |   |   |   | 2-47 |

|        | 2.8.4    | Current Limiting .     |         | •     |      |      |   | • |   |   | • |   | 2-47 |

|        | 2.8.5    | Power Loss Protection  | ١,      | •     |      |      |   |   | • |   |   |   | 2-47 |

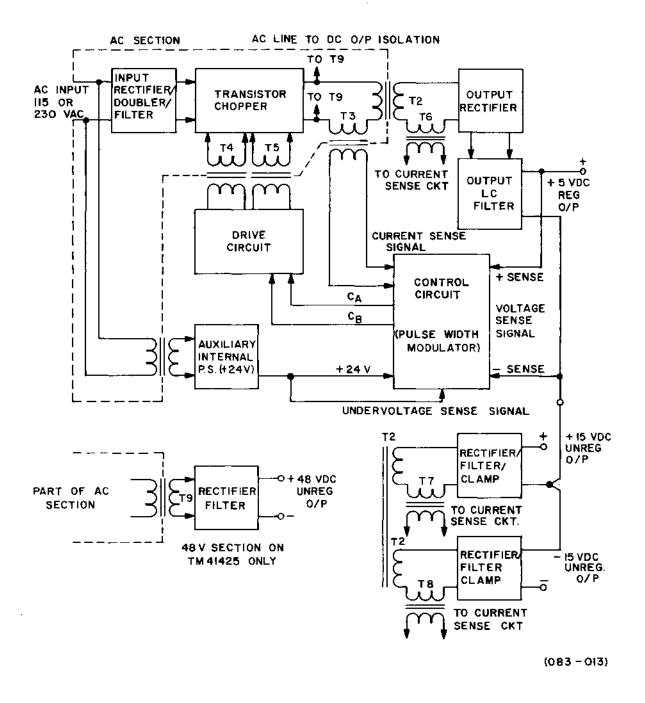

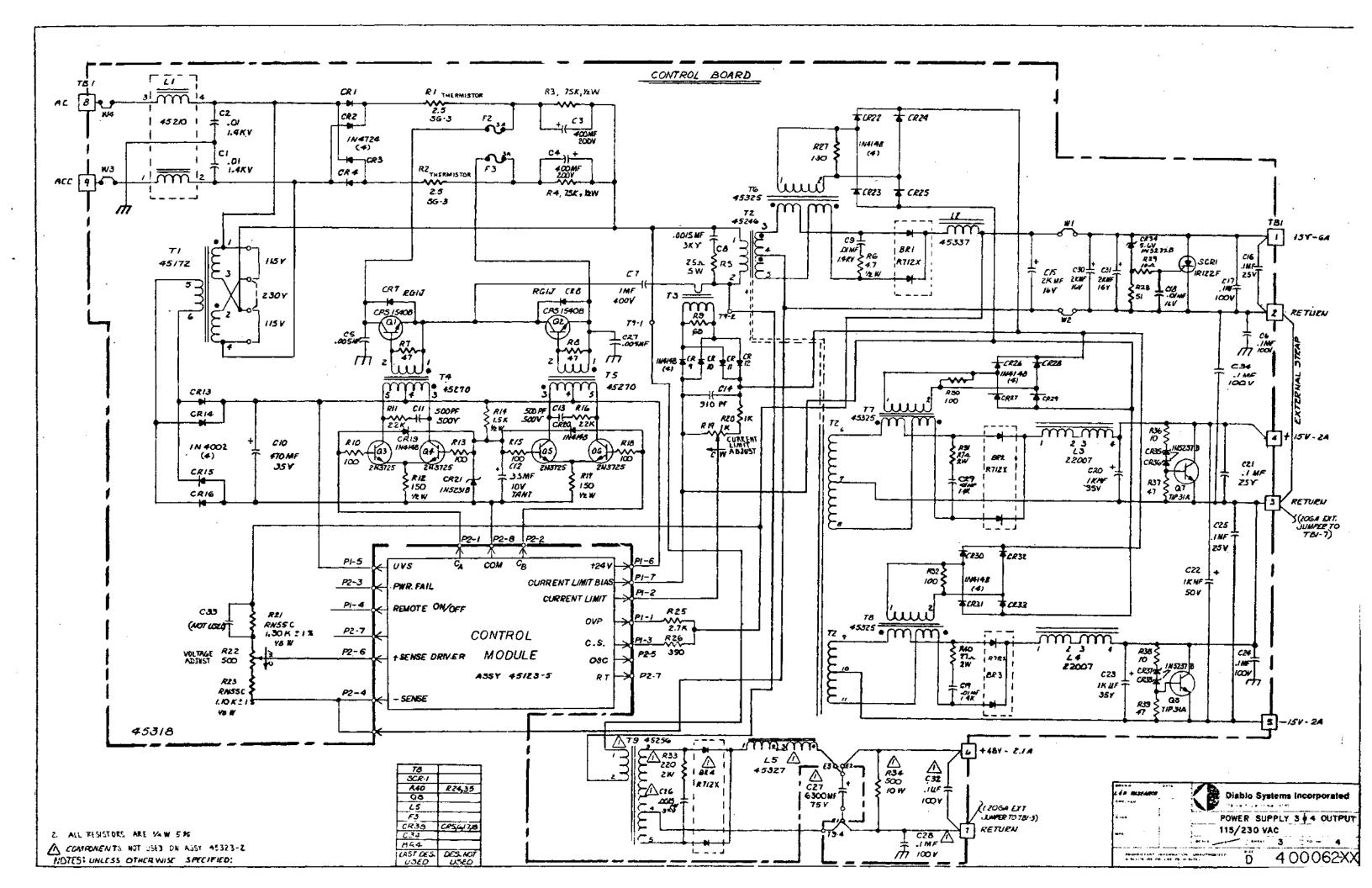

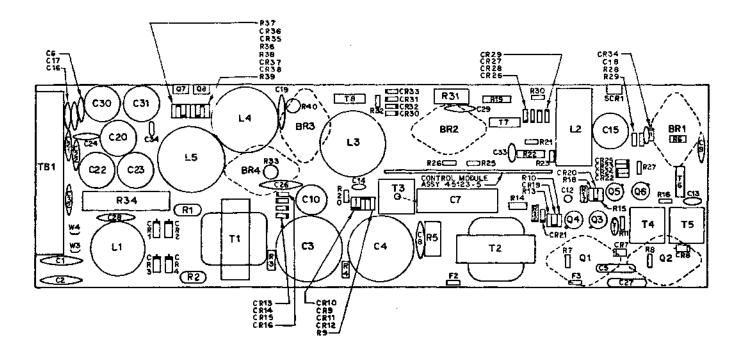

| 2.9    | POWER    | SUPPLY                 | •       | •     |      |      |   |   | • |   |   |   | 2-49 |

|        | 2.9.1    | Detailed Description   | •       | •     |      |      |   |   |   |   |   |   | 2-49 |

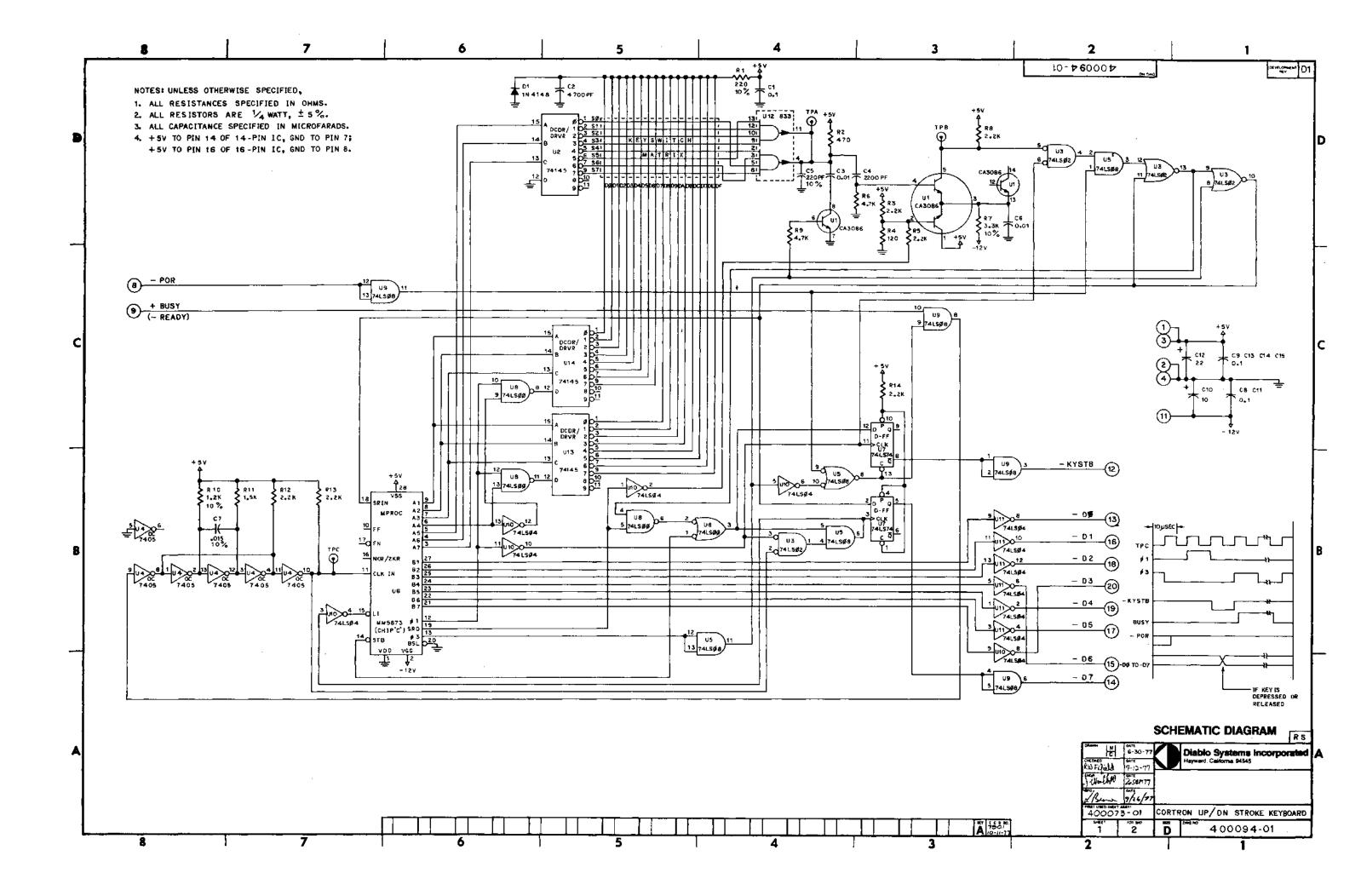

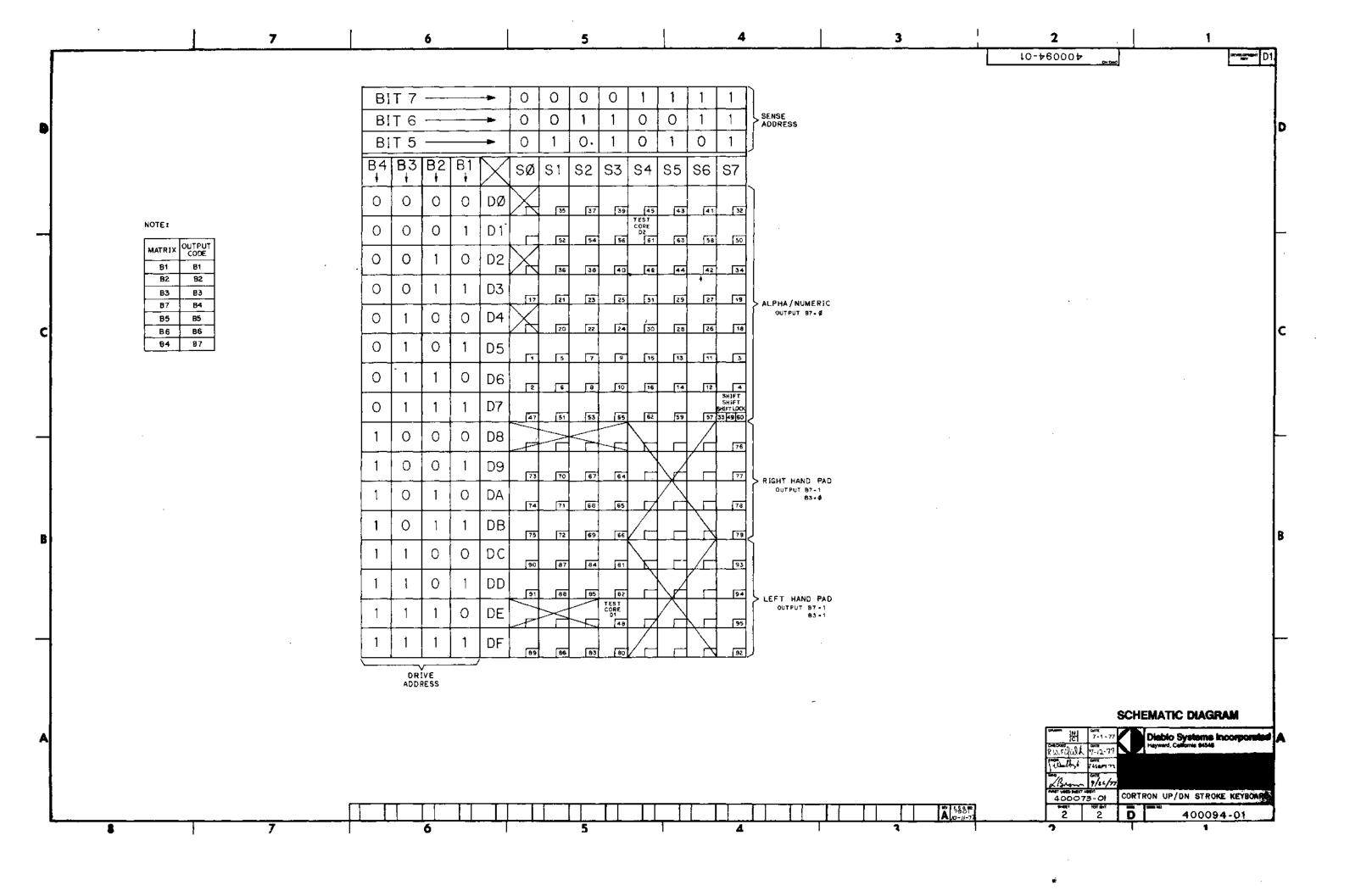

| 2.10   | KEYBOA   | ARD (CORTRON UP/D      | OWN     | STR   | OKE  | )    |   |   |   |   | • |   | 2-55 |

|        | 2.10.1   | Keyswitch Description  | ١.      | •     |      |      | • | • | • |   |   |   | 2-55 |

|        | 2.10.2   | Circuit Description    |         | •     |      |      |   |   |   |   |   |   | 2-55 |

|        | 2.10.3   | External Electronics   |         |       |      |      |   |   |   |   |   |   | 2-56 |

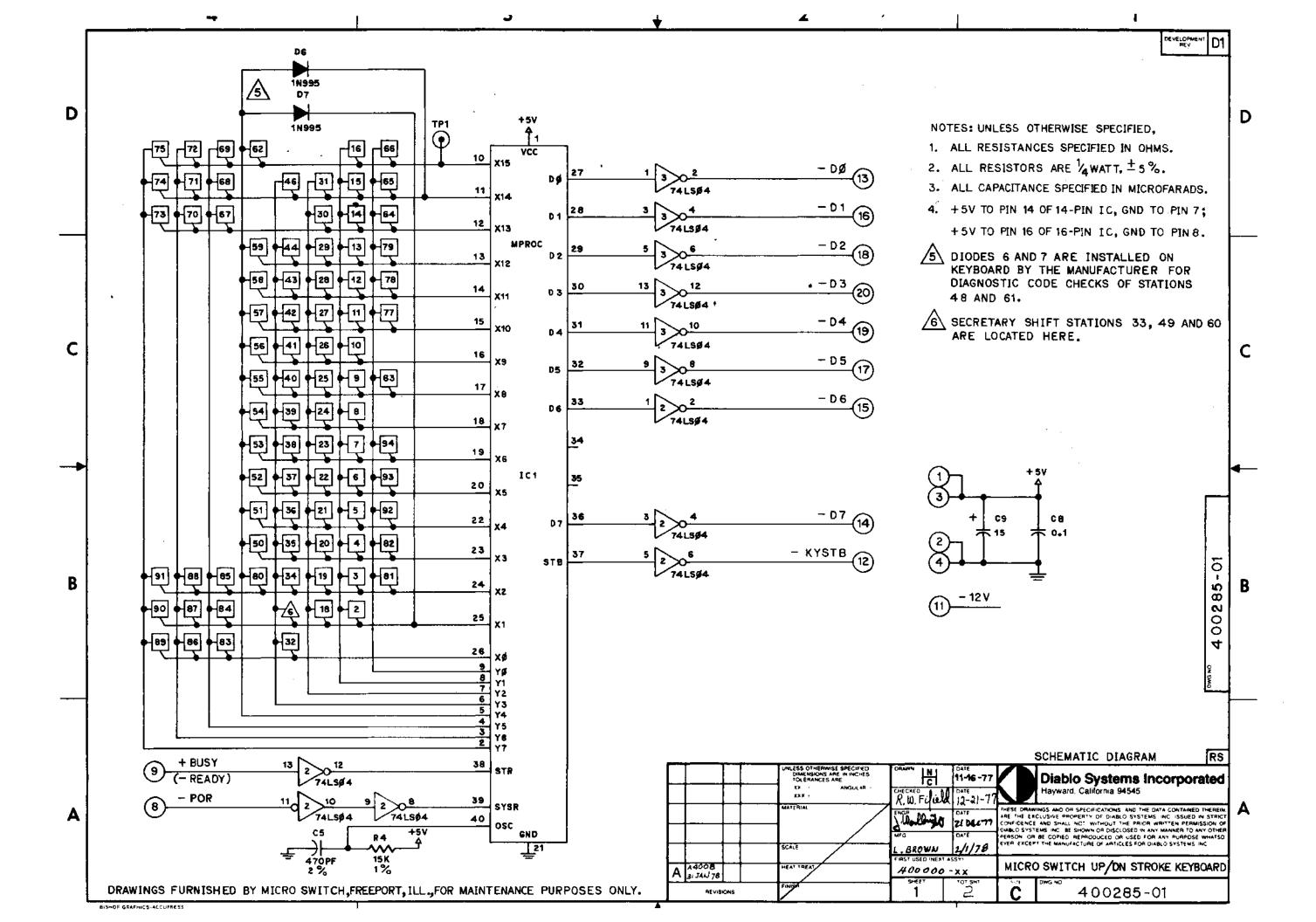

| 2.11   | KEYBO    | ARD (MICROSWITCH U     | JP/DC   | NW    | STR  | OKE  | ) |   | • |   |   |   | 2-58 |

|        | 2.11.1   | General Description    |         | •     | •    |      |   |   |   | • |   |   | 2-58 |

|        | 2.11.2   | Internal Logic Descrip | tion    | _     |      |      |   | _ |   |   | _ |   | 2-58 |

|        | 2.11.3 | External Electron | nics   | •     | •    | •   | • | • | • | • | ٠ | • | • | 2-59 |

|--------|--------|-------------------|--------|-------|------|-----|---|---|---|---|---|---|---|------|

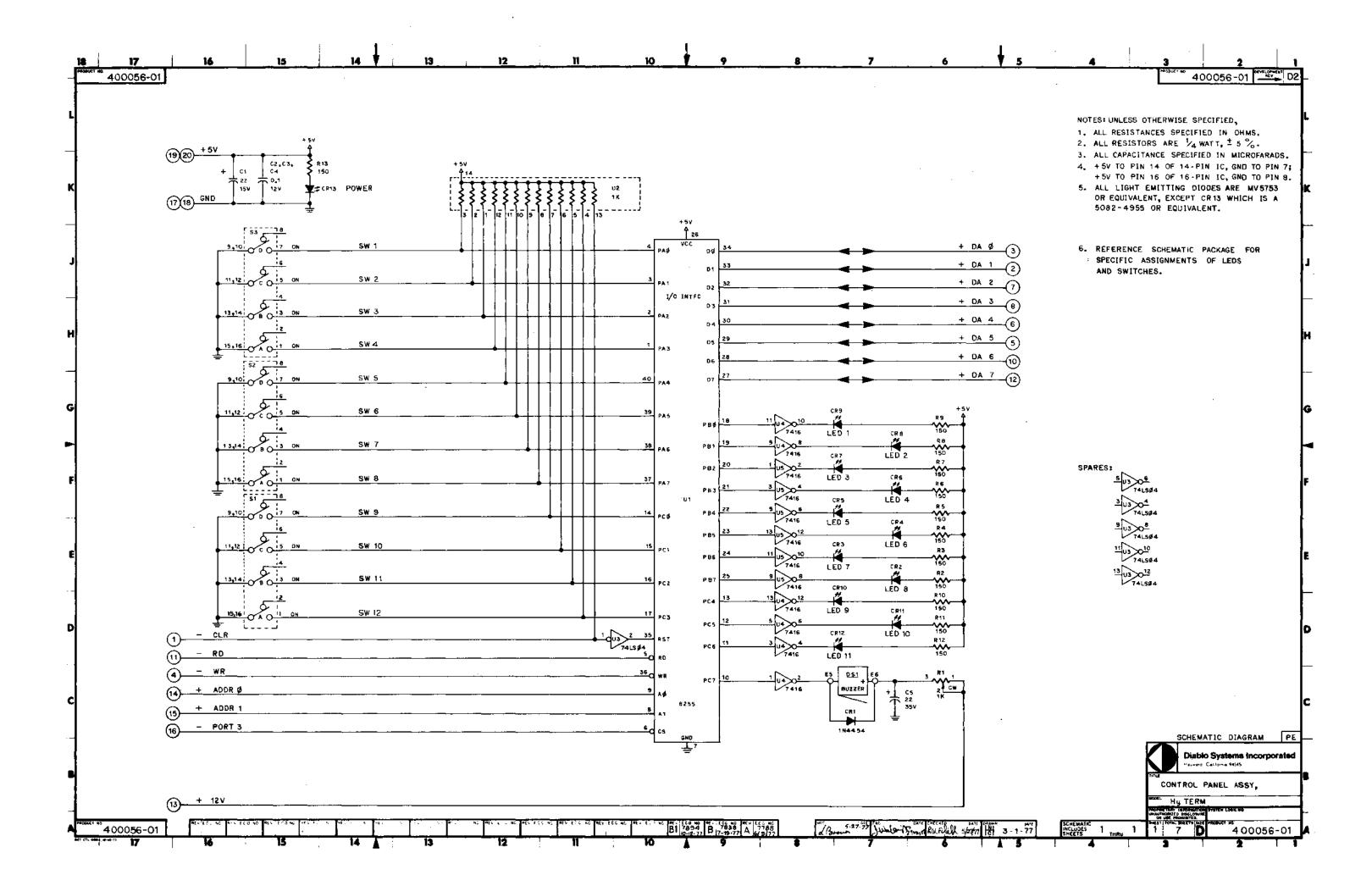

| 2.12   | CONTR  | OL PANEL .        | •      | -     | •    |     |   |   | - | • | • |   | • | 2-61 |

|        | 2.12.1 | Operation Mode    | •      | •     |      |     |   |   |   | • |   |   | • | 2-63 |

|        | 2.12.2 | Switches          |        | •     |      | •   |   | • |   | • | • |   | • | 2-63 |

|        | 2.12.3 | Reading Register  | s.     | •     |      | ,   |   | • |   | • | • |   | • | 2-63 |

|        | 2.12.4 | Indicators and Au | ıdible | Ala   | rm   |     |   |   |   |   | • |   |   | 2-63 |

|        |        |                   |        |       |      |     |   |   |   |   |   |   |   |      |

| SECTIO | N 3 MA | AINTENANCE        |        |       |      |     |   |   |   |   |   |   |   |      |

| 3.1    | INTROI | DUCTION           | •      |       |      |     | • |   | • |   | • | • |   | 3-1  |

|        | 3.1.1  | General Rules     | •      | •     |      | •   |   | • |   |   |   | • |   | 3-1  |

|        | 3.1.2  | Top Cover Remo    | val/R  | tepla | ceme | ent |   |   |   |   | • | • | • | 3-2  |

|        | 3.1.3  | Tools             | •      |       |      | •   |   | • |   |   |   | • |   | 3-3  |

| 3.2    | PREVE  | NTIVE MAINTENA    | NCE    | •     |      |     |   | • |   |   |   |   | • | 3-3  |

|        | 3.2.1  | Supplies          |        | •     |      |     |   | • |   |   |   | • | • | 3-3  |

|        | 3.2.2  | Cleaning and Insp | ectio  | on    |      |     |   | • |   |   |   |   | • | 3-4  |

|        | 3.2.3  | Lubrication .     | •      |       |      |     |   | • |   |   |   |   |   | 3-4  |

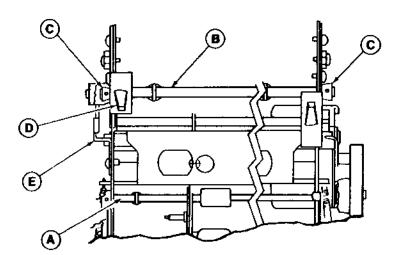

| 3.3    | MODUL  | E REMOVAL AND     | REF    | PLAC  | ЕМЕ  | ENT |   |   |   |   |   |   | • | 3-9  |

|        | 3.3.1  | Printed Circuit B | oard   | s.    |      |     |   |   |   |   |   | • | • | 3-9  |

|        | 3.3.2  | Power Supply.     |        |       |      |     |   |   |   |   |   |   | • | 3-11 |

|        | 3.3.3  | Control Panel     | •      |       |      |     |   | • |   |   | • |   | - | 3-15 |

|        | 3.3.4  | Keyboard .        | •      |       |      |     |   | • |   |   |   | • | • | 3-16 |

|        | 3.3.5  | Printer           |        |       |      |     |   | - |   |   |   | • | • | 3-18 |

|        | 3.3.6  | Print Head .      |        |       |      |     |   | • |   |   |   |   | - | 3-19 |

|        | 3.3.7  | Paper Carrier Sul | basse  | mbly  | , .  |     |   | • |   | • |   | • |   | 3-21 |

|        | 3.3.8  | Paper Feed Moto   | r.     | •     |      |     |   |   | • |   |   | • |   | 3-23 |

|        | 3.3.9  | Carriage Subasse  | mbly   |       |      |     |   |   |   |   |   | • |   | 3-25 |

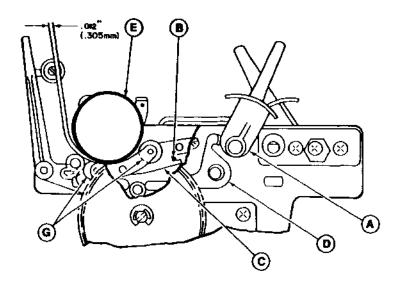

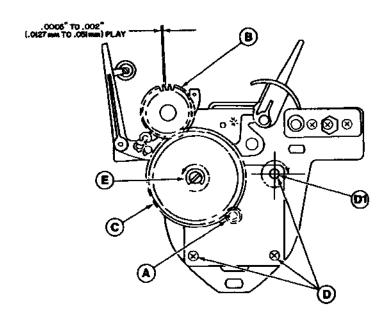

|        | 3.3.10 | Carriage Drive S  | ysten  | n.    |      |     |   |   | • |   |   | • |   | 3-28 |

|        | 3_3_11 | Mother Board.     |        |       |      |     |   |   |   |   |   |   |   | 3-33 |

| 3.4     | ADJUST    | MENTS   | •       |         | •       | •    | •     | •   | •   | • | • | • | • | ٠ | 3-34 |

|---------|-----------|---------|---------|---------|---------|------|-------|-----|-----|---|---|---|---|---|------|

|         | 3.4.1     | Printer | Qualit  | y Test  | ing     | •    | •     |     | •   | • |   | • |   |   | 3-34 |

|         | 3.4.2     | Printer | Adjust  | tments  |         |      | •     |     | •   | • |   | • |   |   | 3-36 |

|         | 3.4.3     | Control | l Panel | Alarm   | i Volun | ne A | djust | men | t.  |   | • |   |   |   | 3-48 |

|         | 3,4,4     | Power   | Supply  | Adjust  | ment    |      |       |     |     | • | • |   |   |   | 3-48 |

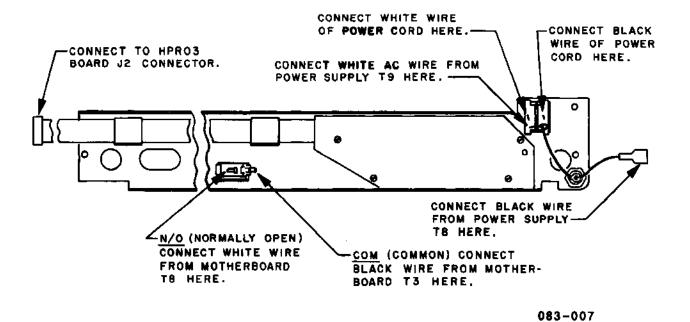

|         | 3.4.5     | Cover-  | Open S  | witch.  | Adjust  | men1 | t .   |     |     |   | • |   |   |   | 3-50 |

|         | 3.4.6     | Paper-0 | Out Sw  | itch A  | djustm  | ent  | •     |     |     | • | • | • | • |   | 3~50 |

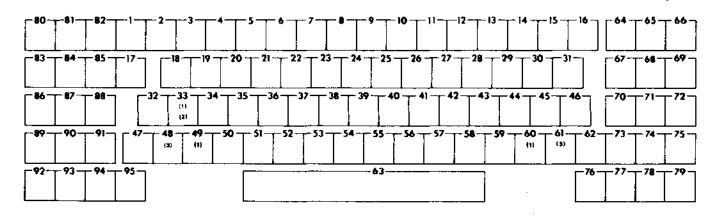

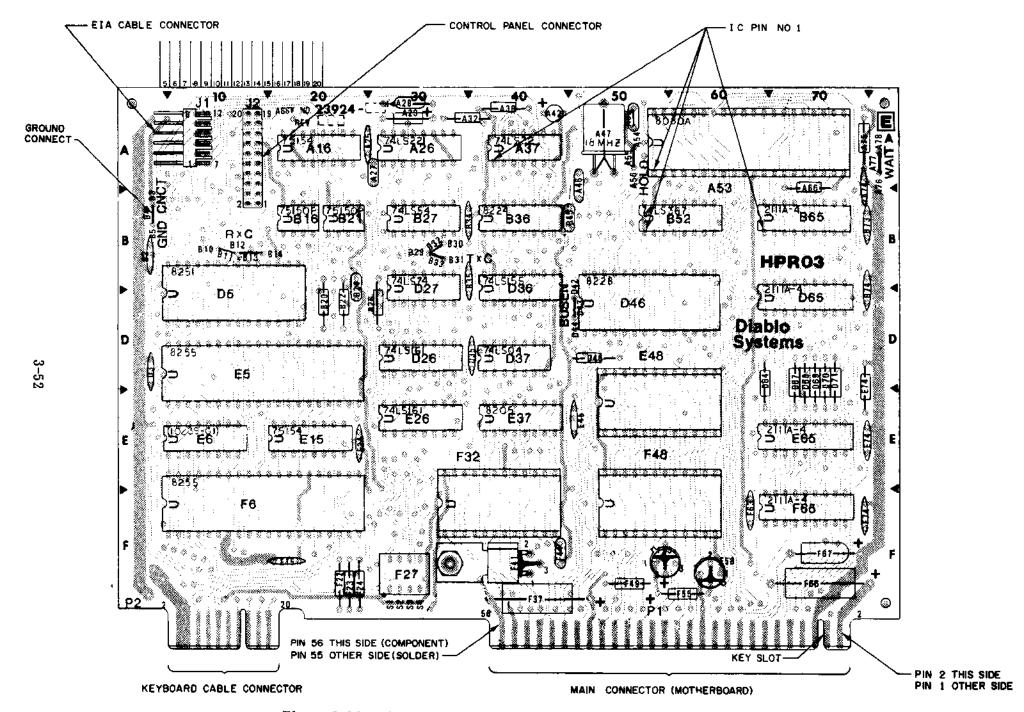

| 3.5     | COMPO     | NENT II | DENTIF  | FICATI  | ON      |      | •     |     |     |   |   |   |   |   | 3-51 |

|         | 3.5.1     | Refere  | nce De  | signato | or Syst | em   | •     |     |     |   | • | • |   | • | 3–51 |

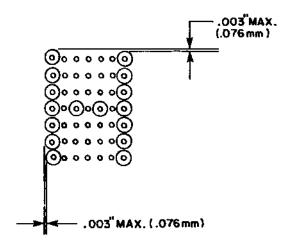

|         | 3.5.2     | Coordin | nate Sy | stem    |         |      | •     |     |     |   |   |   |   |   | 3-51 |

|         | 3.5.3     | Pin Nur | nberin  | g .     | •       | •    | •     | •   |     | • | • | • |   |   | 3-53 |

|         |           |         |         |         |         |      |       |     |     |   |   |   |   |   |      |

| SECTION | N 4 — SCI | нематі  | CS AN   | D REF   | EREN    | CE I | NFO   | RMA | TIO | N |   |   |   |   |      |

| 4.1     | INTROD    | UCTION  | Į.      |         | •       | •    | •     | •   | •   |   |   |   | • | • | 4-1  |

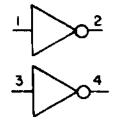

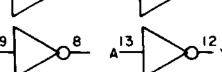

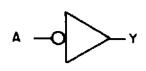

| 4.2     | FUNCTI    | ONAL L  | OGIC    |         | •       |      |       | •   |     |   |   | • |   |   | 4-1  |

| 4.3     | SIGNAL    | NOMEN   | CLAT    | URE.    | •       | •    | •     | •   |     |   |   |   |   |   | 4-2  |

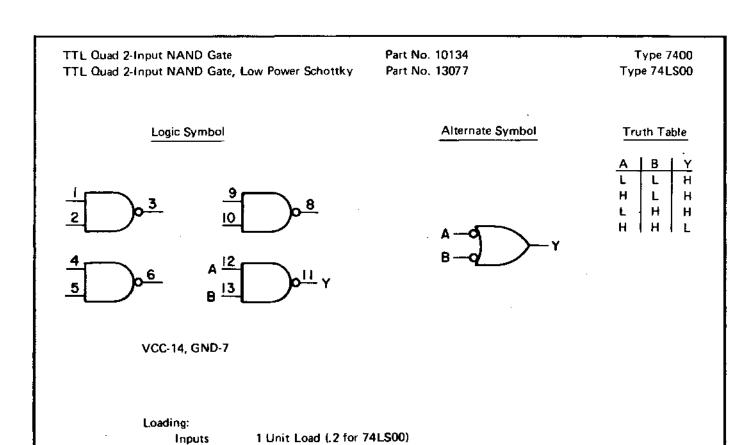

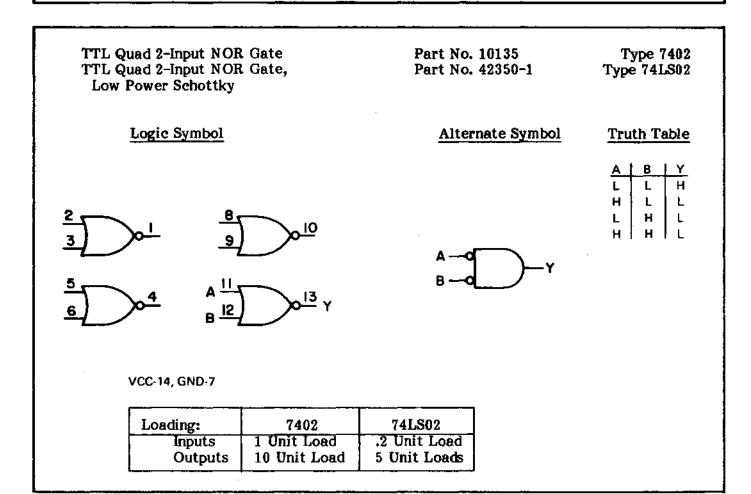

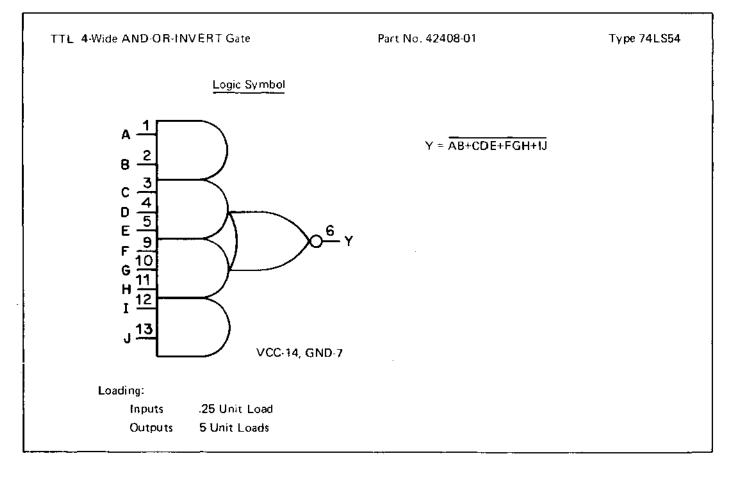

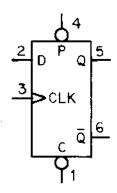

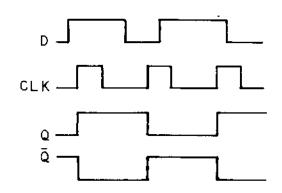

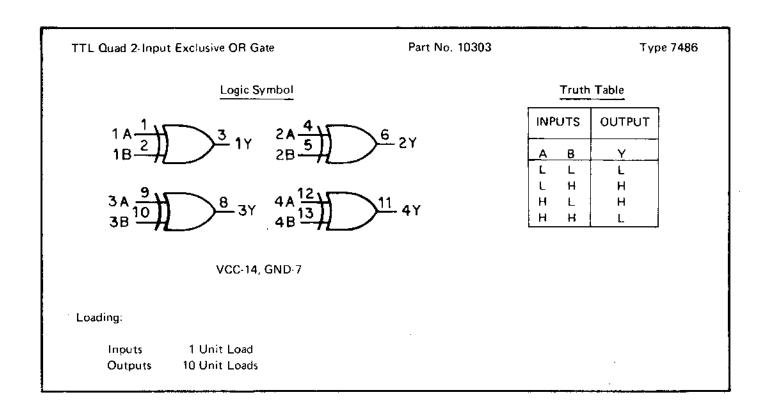

| 4.4     | LOGIC S   | YMBOL   | OGY .   |         | •       |      |       | •   |     |   |   |   |   |   | 4-2  |

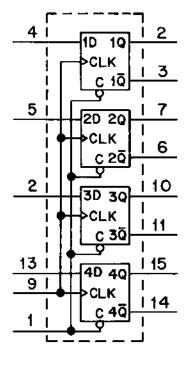

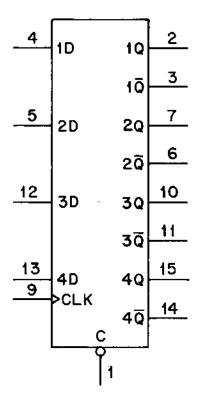

| 4.5     | INTEGR    | ATED C  | IRCUI   | TS .    | •       |      | •     | •   |     |   |   |   |   |   | 4-2  |

| 4.6     | ASCII CO  | ODE CH  | ART     |         |         | •    |       | ٠   |     | • | • |   | • | • | 4-62 |

| 4.7     | SCHEMA    | ATICS A | ND LO   | GIC D   | RAWIN   | NGS  |       |     |     |   |   |   |   |   | 4-62 |

| FIGURE | LIST OF ILLUSTRA                           | ATIC | DNS  |   |   |   |   |   | PA | GE   |

|--------|--------------------------------------------|------|------|---|---|---|---|---|----|------|

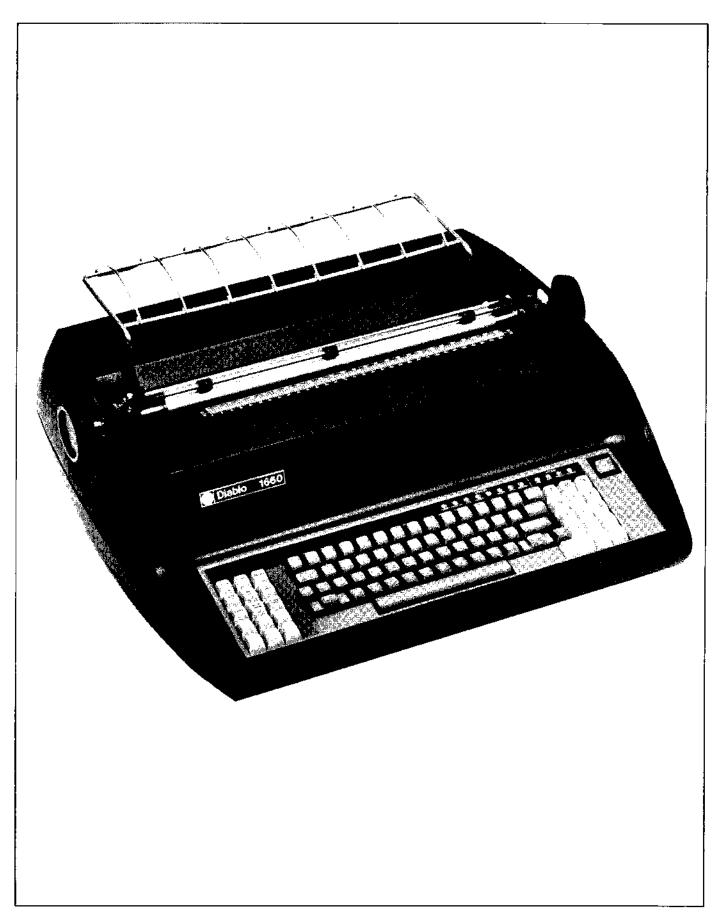

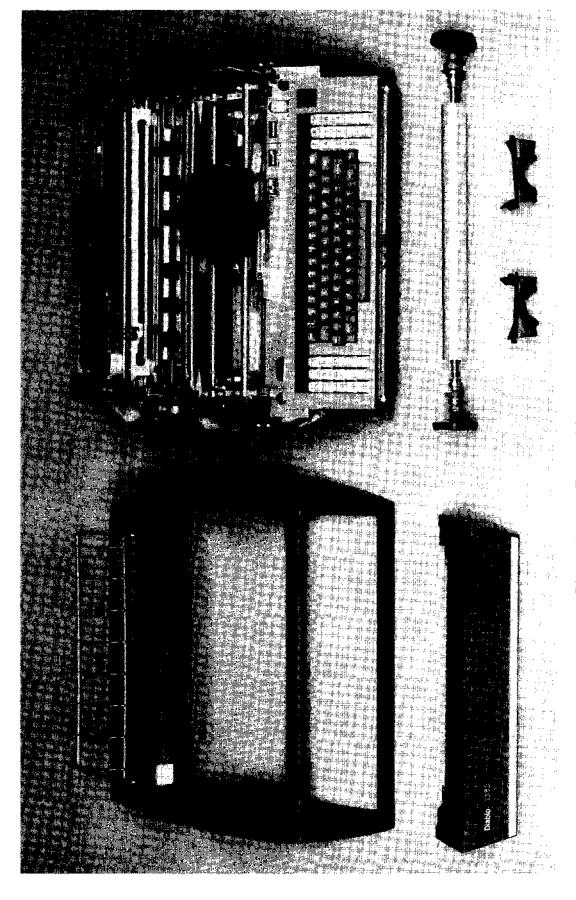

| 1-1    | Model 1660 Hyterm Communications Terr      | nina | l    | • | • | • | • |   |    | 1-0  |

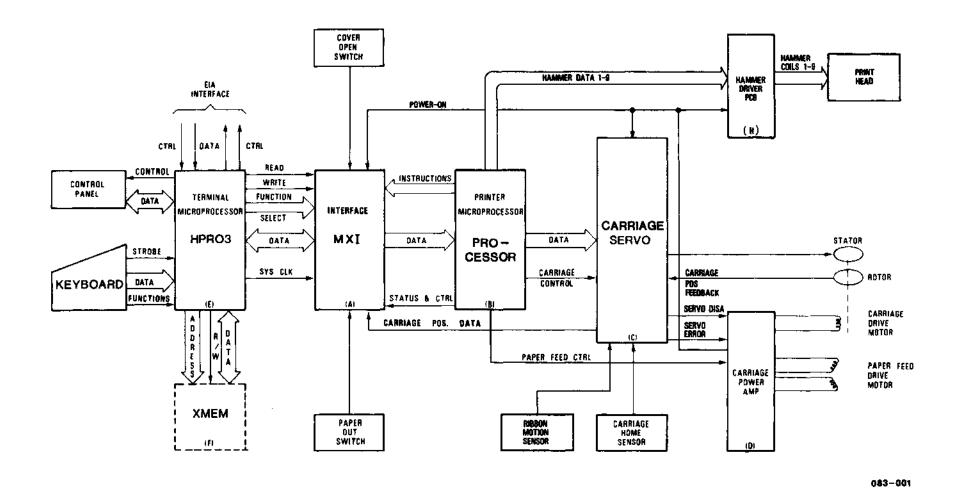

| 2-1    | Model 1660 Hyterm System Block Diagram     | n    | •    |   |   |   | • |   |    | 2-0  |

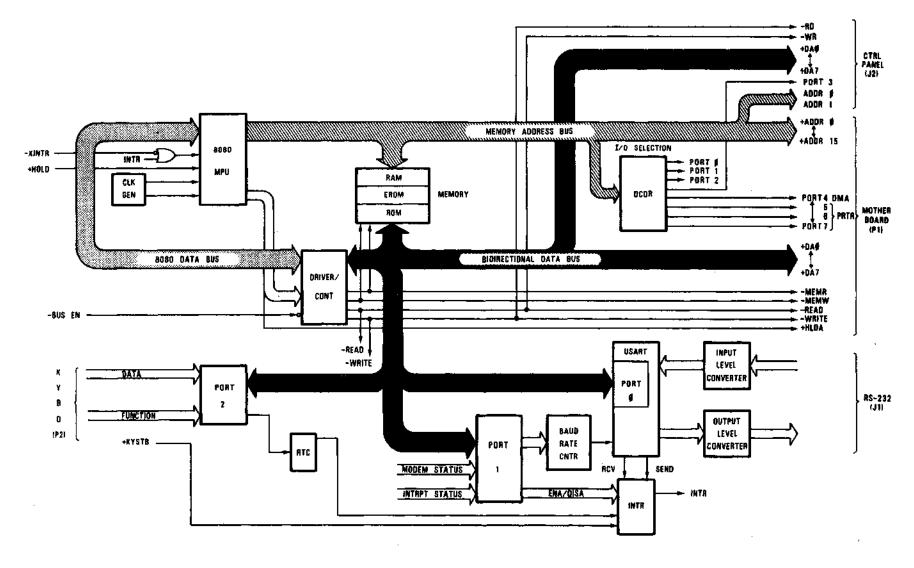

| 2-2    | Block Diagram, HPRO3 Board                 |      |      |   |   |   |   |   |    | 2-2  |

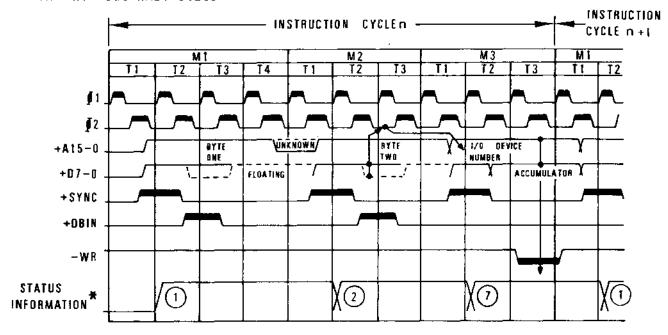

| 2-3    | Typical Instruction Cycle (Output Instruct | ion) |      |   |   |   |   |   |    | 2-6  |

| 2-4    | MPU Instruction Format                     |      | •    |   |   |   |   |   |    | 2-7  |

| 2-5    | MPU Status and Resultant Control Signals   | 5    |      |   | • |   |   |   |    | 2-9  |

| 2-6    | Memory Map                                 | •    |      |   |   |   |   |   |    | 2-12 |

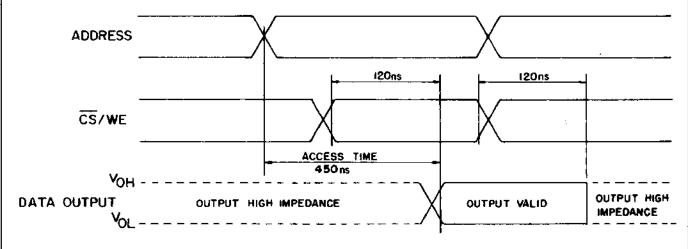

| 2-7    | Memory Timing                              | •    |      |   |   |   |   |   |    | 2-13 |

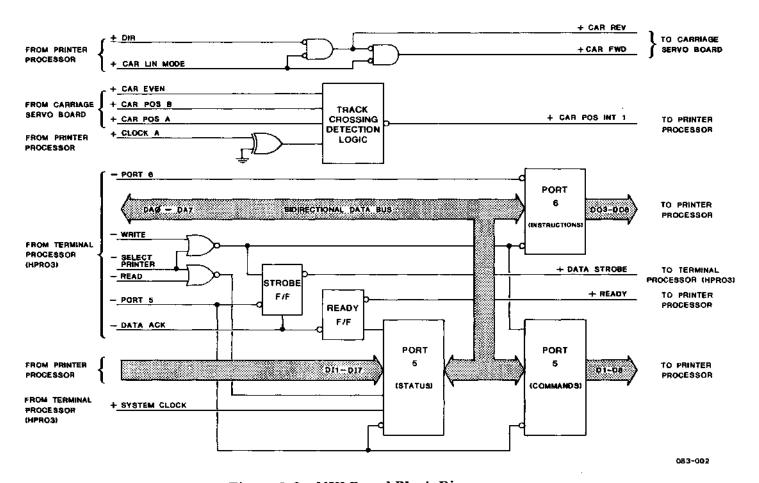

| 2-8    | MXI Board Block Diagram                    |      |      |   |   |   |   |   |    | 2-23 |

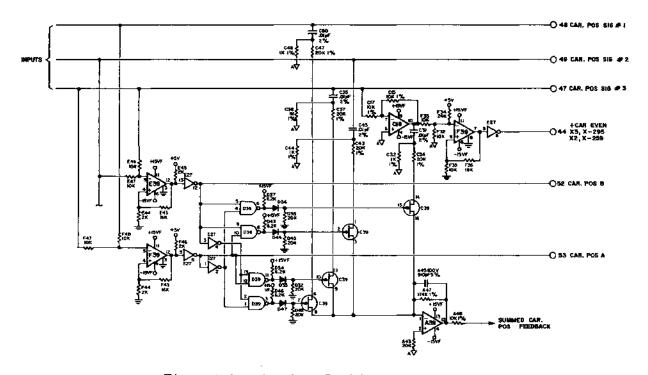

| 2-9    | Track Crossing Detection Logic             | •    |      |   |   |   |   |   |    | 2-24 |

| 2-10   | Track Crossing Detection Waveforms         |      | •    |   |   |   |   |   |    | 2-25 |

| 2-11   | Processor Simplified Block Diagram .       | •    |      |   |   | • |   |   |    | 2-26 |

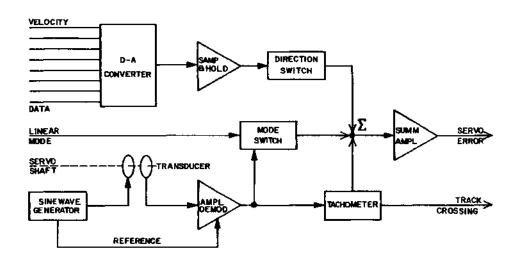

| 2-12   | Carriage Servo Block Diagram               |      |      | • |   |   |   |   |    | 2-29 |

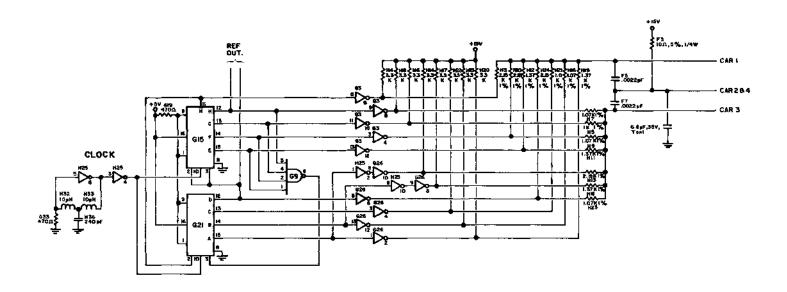

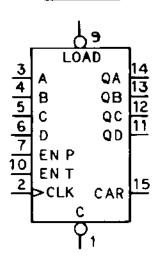

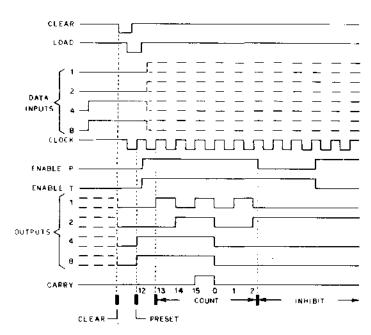

| 2-13   | Digital Sinewave Generator                 | •    |      |   |   |   |   |   |    | 2-29 |

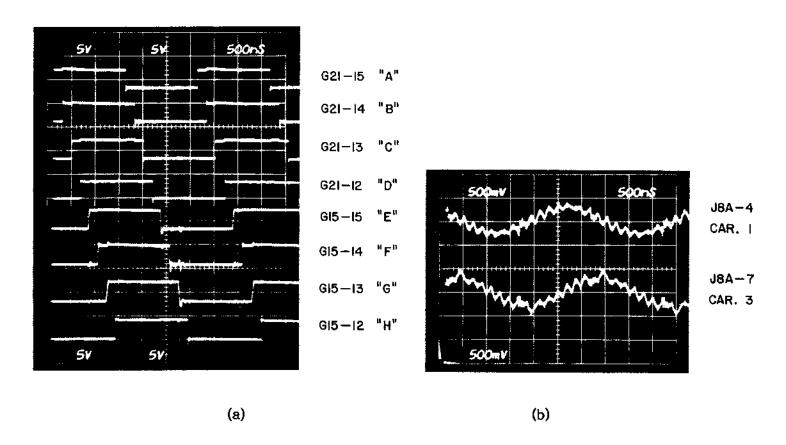

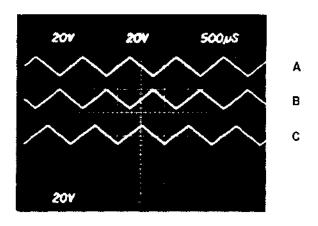

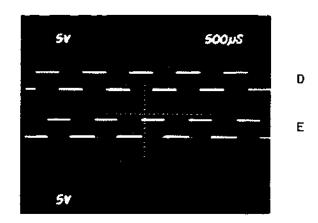

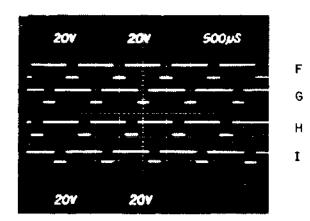

| 2-14   | Digital Sinewave Generator Waveforms       | •    |      |   |   |   |   |   |    | 2-30 |

| 2-15   | Servo Postion Transducer                   | •    |      |   |   |   |   |   |    | 2-31 |

| 2-16   | Servo Feedback Amplifier                   |      |      |   |   |   |   |   |    | 2-31 |

| 2-17   | Servo Feedback Amplifier Waveforms         | •    |      |   |   |   |   |   |    | 2-32 |

| 2-18   | Servo Feedback Demodulator/Amplifier       | •    |      |   |   |   |   |   |    | 2-33 |

| 2-19   | Servo Feedback Demodulator/Amplifier W     | lave | form | S |   |   |   |   |    | 2-33 |

| 2-20   | Waveform Analysis                          |      |      |   |   |   |   |   |    | 2-34 |

| 2-21   | Carriage Position Tachometer               |      |      |   |   |   | • |   |    | 2-35 |

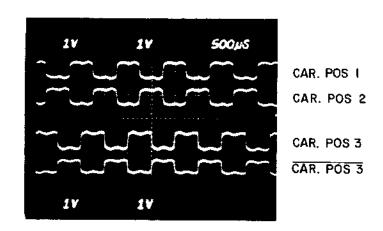

| 2-22   | Carriage Position Tachometer Waveforms     | 3    |      |   |   |   |   |   |    | 2-36 |

| 2-23   | Carriage Position FET Input Waveforms      | •    | •    |   |   |   |   |   |    | 2-36 |

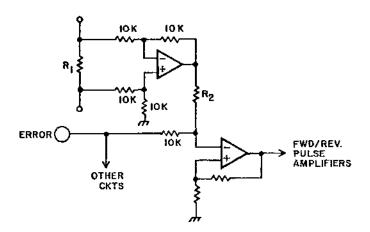

| 2-24   | Carriage Velocity Command Circuits         |      |      |   |   |   |   | • | •  | 2-38 |

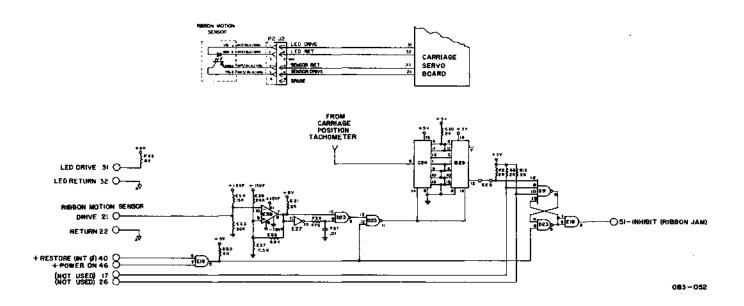

| 2-25  | Ribbon Motion Sensor                                                        | •  | • | - | ٠ | 2-38 |

|-------|-----------------------------------------------------------------------------|----|---|---|---|------|

| 2-26a | Carriage Power Amplifier Simplified Diagram                                 | •  | • | • | • | 2-40 |

| 2-26b | Carriage Power Amplifier                                                    |    | • | • | • | 2-40 |

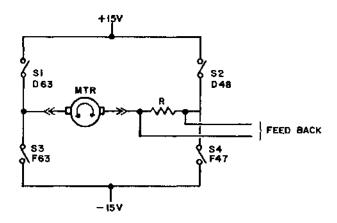

| 2-27  | Simplified Feedback Circuit                                                 |    | • | • | • | 2-42 |

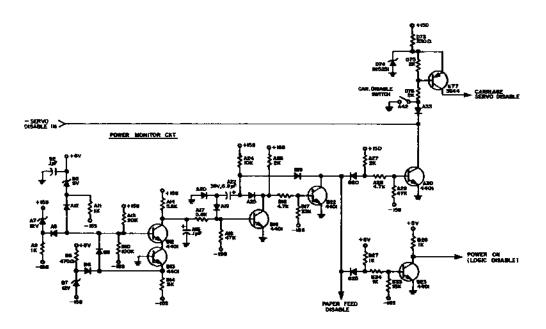

| 2-28  | Power Monitor Circuit                                                       |    | • | • |   | 2-43 |

| 2-29  | Paper Feed Drive Circuit                                                    |    | • | • |   | 2-44 |

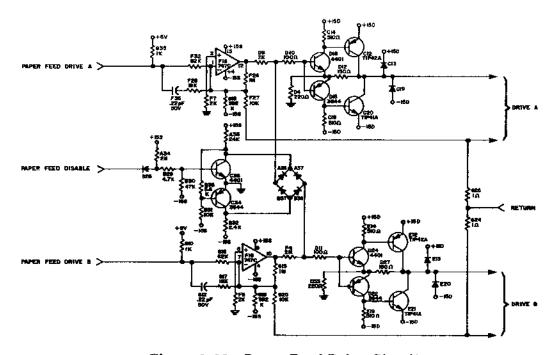

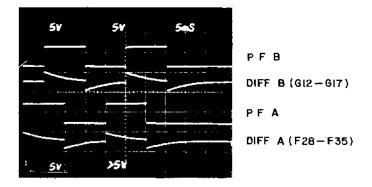

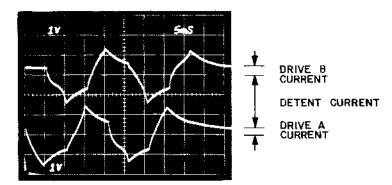

| 2-30  | Paper Drive Waveforms                                                       |    | • | • | • | 2-45 |

| 2-31  | Typical Stepping Motor Rotation                                             |    | • |   | • | 2-45 |

| 2-32  | Typical Hammer Driver and Common Protection Circuit                         | s. | • |   | • | 2-46 |

| 2-33  | Power Supply Block Diagram                                                  |    |   |   |   | 2-48 |

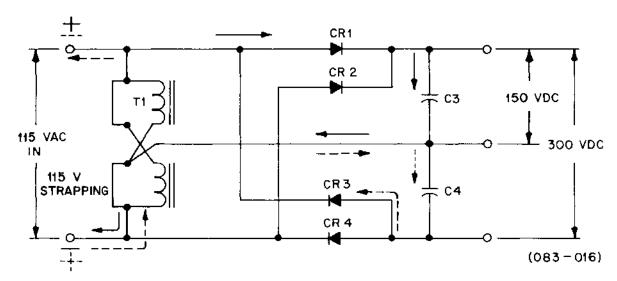

| 2-34  | Simplified Input Rectifier/Filter/Doubler Section (115 VAC Input Strapping) |    | • | • |   | 2-49 |

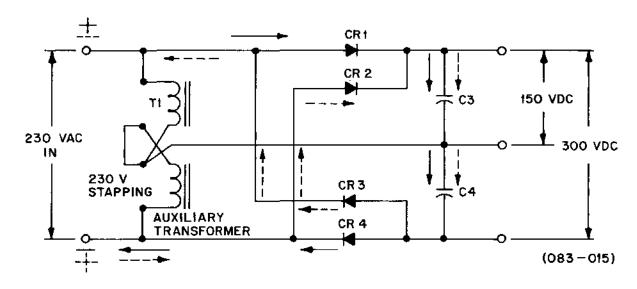

| 2-35  | Simplified Input Rectifier/Filter/Doubler Section (230 VAC Input Strapping) |    | • |   |   | 2-50 |

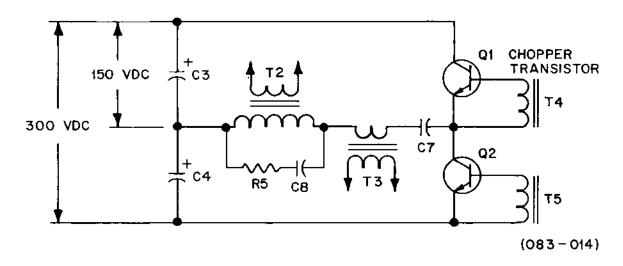

| 2-36  | Simplified Transistor Chopper (Half-Wave)                                   |    |   |   |   | 2-50 |

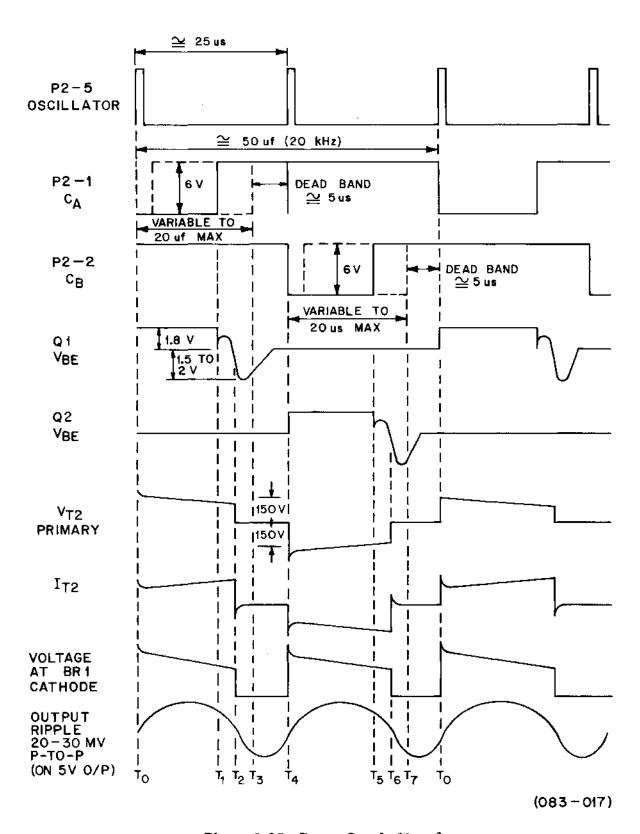

| 2-37  | Power Supply Waveforms                                                      | -  |   |   |   | 2-51 |

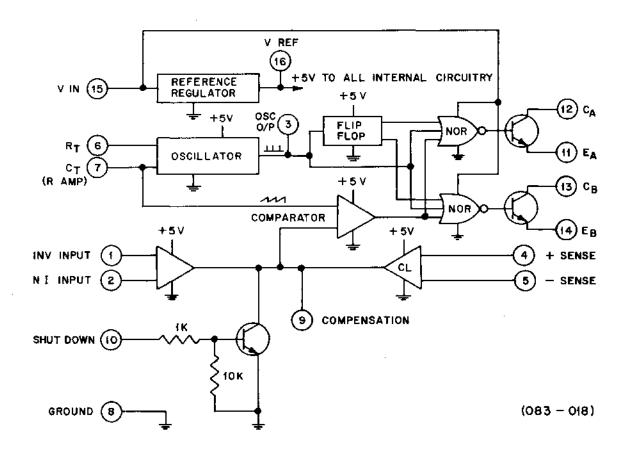

| 2-38  | Control Module Block Diagram                                                |    |   | • |   | 2-52 |

| 2-39  | Control Module Timing Diagram                                               |    | • | • |   | 2-52 |

| 2-40  | Key Position Layout                                                         |    | • |   | • | 2-56 |

| 2-41  | Keyboard Timing Diagram                                                     |    | • | • |   | 2-60 |

| 2-42  | Block Diagram, Control Panel                                                | •  | • | • | • | 2-62 |

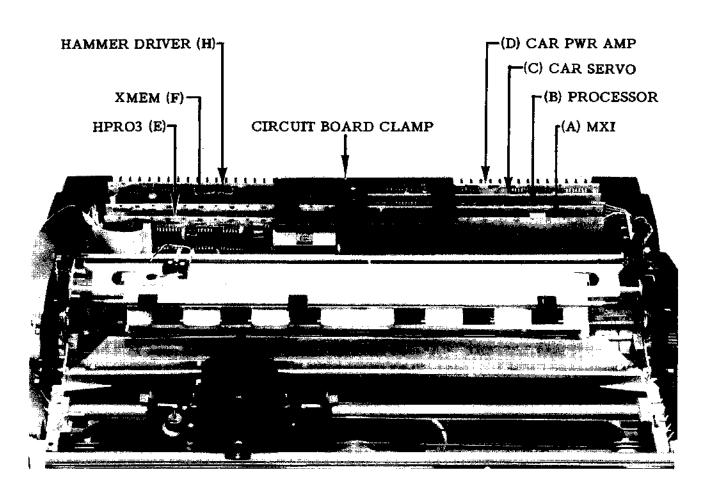

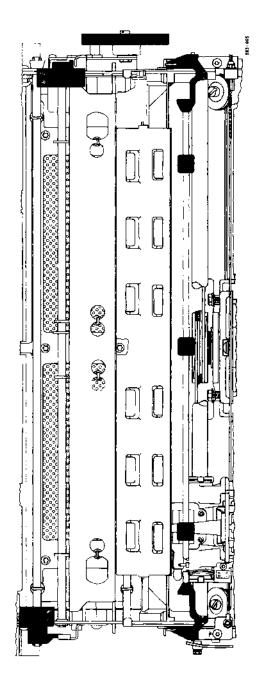

| 3-0   | Hyterm with Top Cover Removed                                               |    | • |   |   | 3-0  |

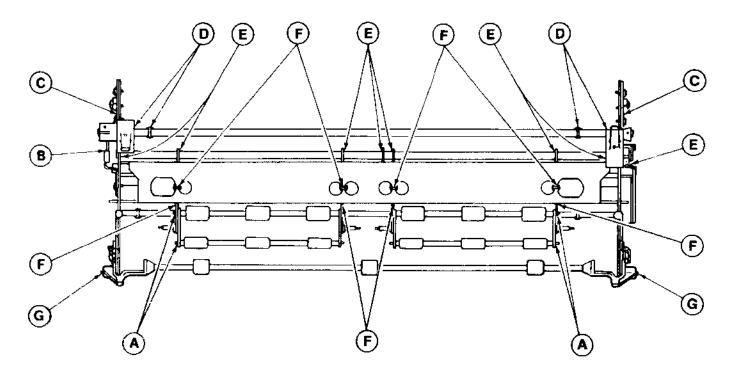

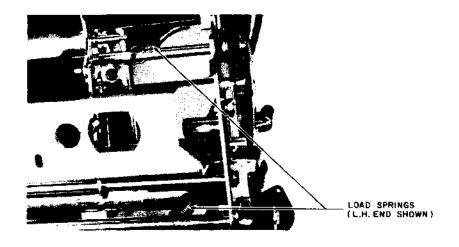

| 3-1   | Carrier System Lubrication Points                                           |    |   |   |   | 3-5  |

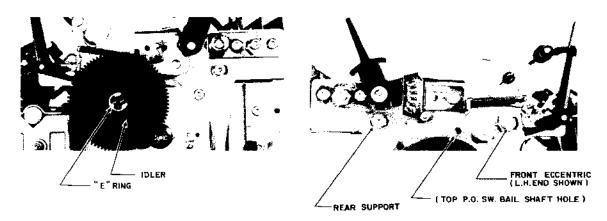

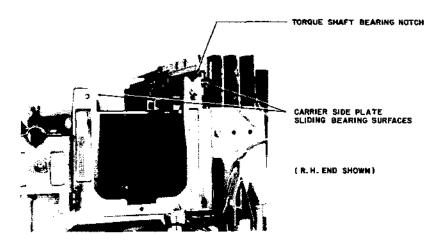

| 3-2   | Carriage System Lubrication Points                                          |    |   |   |   | 3-6  |

| 3-3   | Platen System Lubrication Points                                            |    |   |   |   | 3-7  |

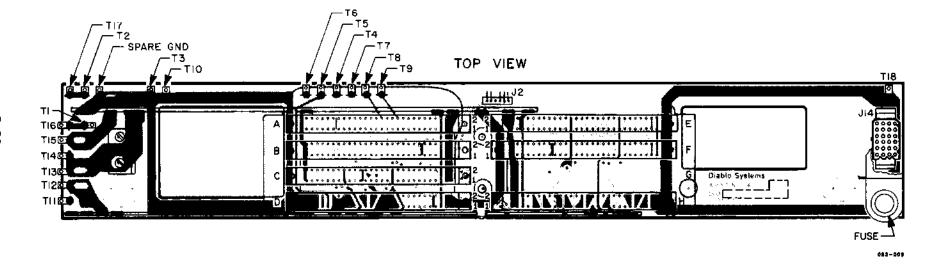

| 3-4   | Circuit Board Locations                                                     |    | • |   |   | 3-8  |

| 3-5   | Power Supply Mounting                                                       |    |   |   |   | 3-10 |

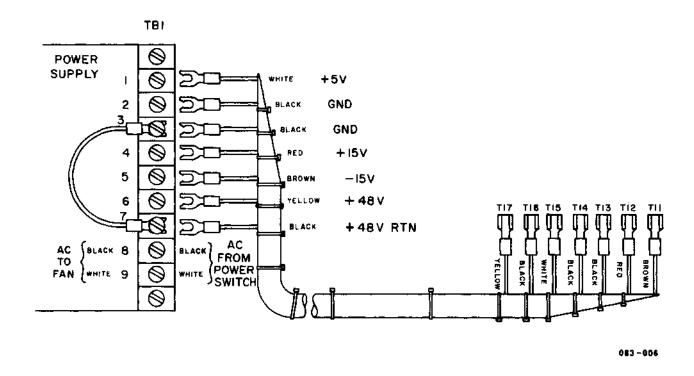

| 3-6   | Power Supply Connections                                                    |    | • |   |   | 3-11 |

| 3-7  | Control Panel Connections.      | •     | •      | •          | •     | •  | • | • | • | • | • | 3-14 |

|------|---------------------------------|-------|--------|------------|-------|----|---|---|---|---|---|------|

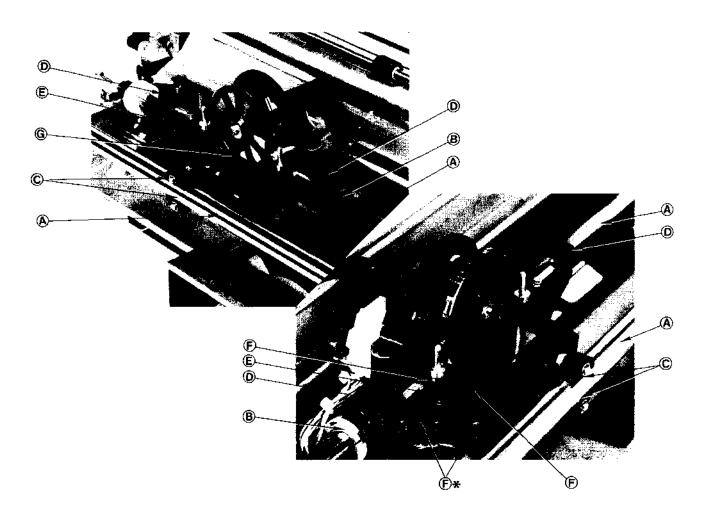

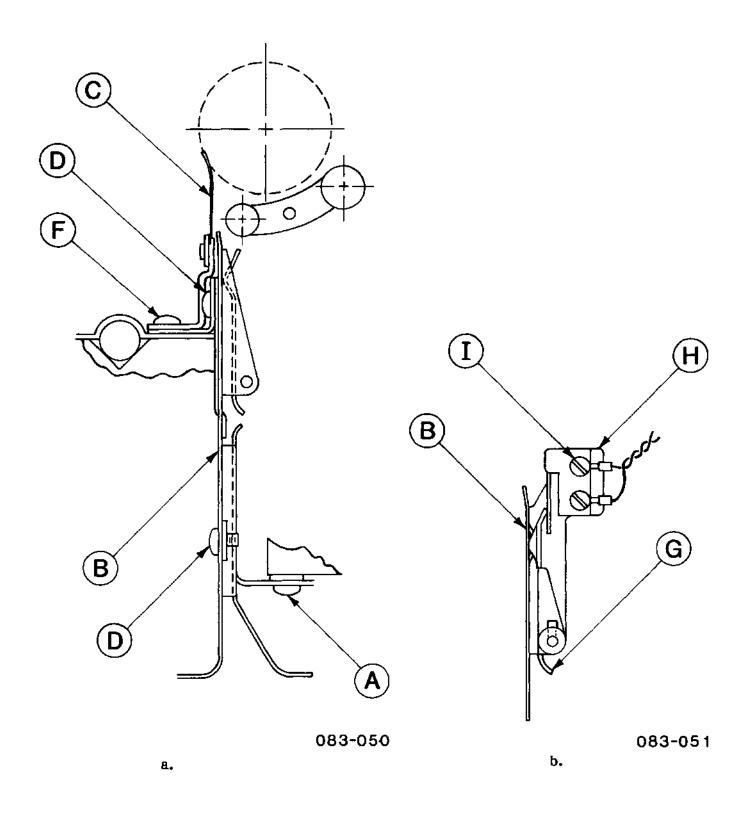

| 3-8  | Carrier System Removal - A      | •     |        | •          |       | •  |   | • |   | • | • | 3-20 |

| 3-9  | Carrier System Removal - B      | •     |        | •          |       | •  |   | • | • |   |   | 3-20 |

| 3-10 | Carrier System Removal - C      | •     |        | •          |       | •  |   |   | • |   | • | 3-20 |

| 3-11 | Carrier System Replacement      | •     | •      | •          |       | •  |   | • |   |   |   | 3-22 |

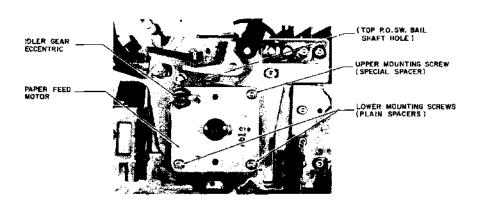

| 3-12 | Paper Feed Motor Removal/Rep    | place | ment   | t          |       | •  |   | • |   |   |   | 3-22 |

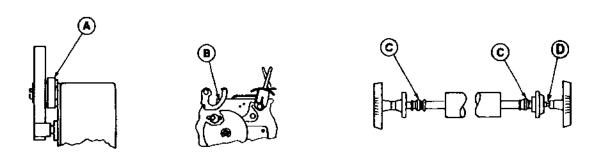

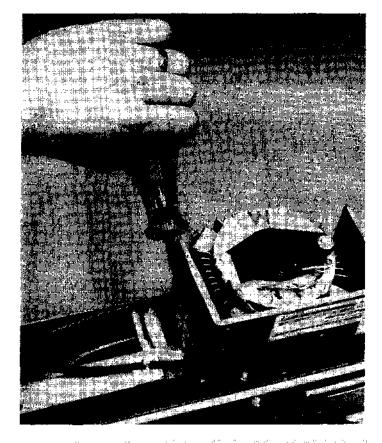

| 3-13 | Carriage Drive Pulley Removal   |       |        | •          |       | •  |   |   |   |   |   | 3-24 |

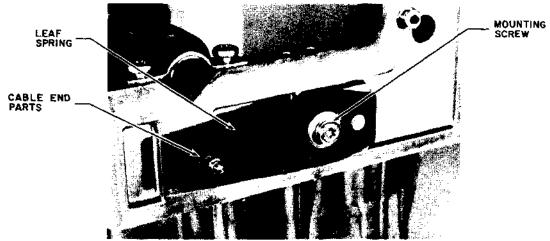

| 3-14 | Ribbon Drive Cable Replacemen   | nt    |        | •          | •     | •  | • |   |   |   | • | 3-26 |

| 3-15 | Carriage Drive Cable Tension S  | pring | Ç •    | •          |       |    |   |   |   |   |   | 3-28 |

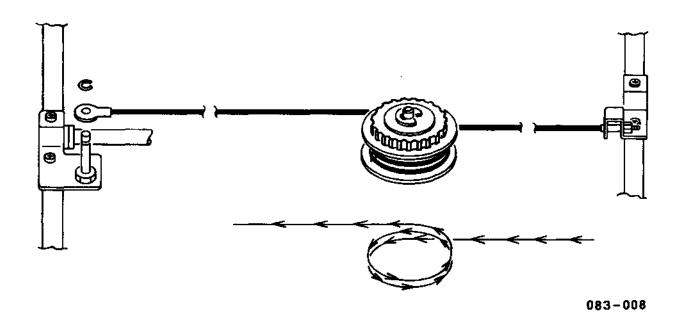

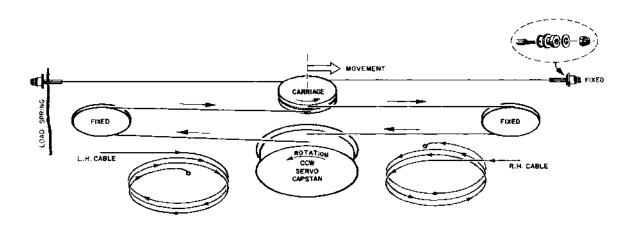

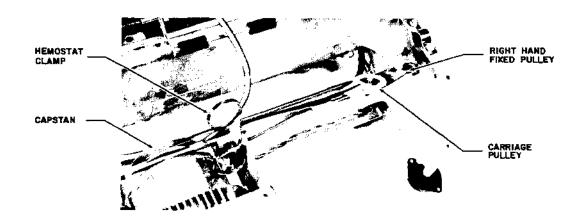

| 3-16 | Carriage Drive Cable Routing    |       |        |            | •     | •  | • |   |   |   |   | 3-29 |

| 3-17 | Right Hand Carriage Drive Cab   | le In | stalla | tion       |       |    |   |   | • | • |   | 3-30 |

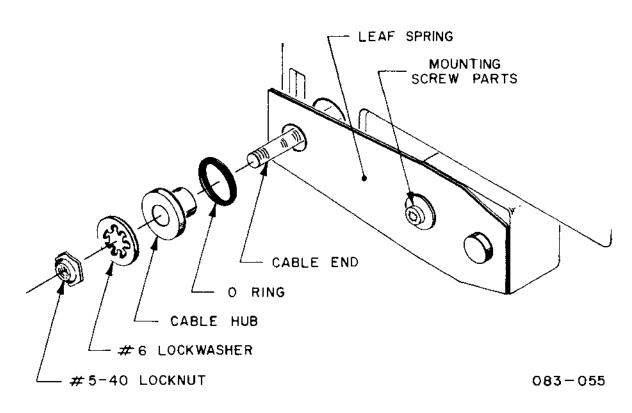

| 3-18 | Carriage Drive Cable Tension S  | pring | Ass    | embl       | у     |    |   |   |   |   |   | 3-30 |

| 3-19 | Mother Board Connections .      | •     |        |            |       |    | • |   |   |   |   | 3-32 |

| 3-20 | Dot Matrix Character Edge Var   | iatio | n      |            | •     |    | • |   | • |   |   | 3-35 |

| 3-21 | Carrier Assembly Adjustment P   | oints | š.     |            |       |    |   |   | • |   |   | 3-36 |

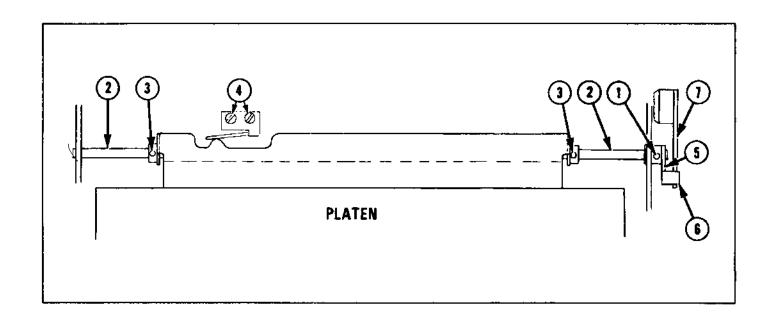

| 3-22 | Paper Feed Adjustment Points    | •     | •      |            |       |    |   |   | • | • | • | 3-37 |

| 3-23 | Platen Drive Adjustment Points  | · .   |        |            | •     |    | • |   | • |   | • | 3-38 |

| 3-24 | Front Guide Bearing Adjustmen   | t Poi | ints   |            |       |    | • |   |   |   |   | 3-39 |

| 3-25 | Platen-to-Print Head Adjustmen  | nt To | ol In  | stall      | ation | ١. | • |   |   | • |   | 3-40 |

| 3-26 | Platen-to-Print Head Adjustme   | nt Po | oints  |            |       |    |   |   |   | • | • | 3-41 |

| 3-27 | Variable Adjust Platen Knob's E | nd P  | lay A  | djus       | tmer  | ıt |   |   |   |   | • | 3-42 |

| 3-28 | Carriage Drive Cable Adjustme   | nt    |        |            |       |    | • |   |   |   | • | 3-43 |

| 3-29 | Ribbon Drive Cable Adjustment   |       |        |            |       |    | • |   |   | • |   | 3-43 |

| 3-30 | Ribbon Drive Gear Adjustment    |       |        |            |       | •  |   |   | • |   |   | 3-44 |

| 3-31 | Paper Clamp Adjustment .        |       | • .    |            | •     |    |   |   |   |   |   | 3-45 |

| 3-32 | Bottom Feed Paper Chute Adju    | stme  | nt     |            |       |    |   |   |   |   |   | 3-46 |

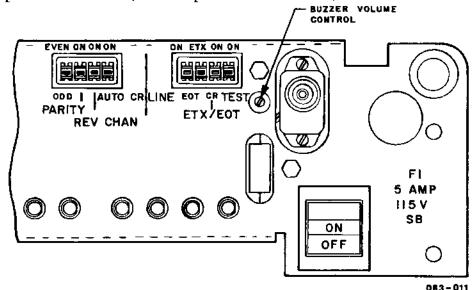

| 3-33 | Control Panel Alarm Volume Ac   | djust | ment   | : <b>.</b> |       |    |   |   |   |   |   | 3-48 |

| 3-34 | Paper-Out Switch Adjustment     |       |        |            |       |    |   |   |   |   |   | 3-51 |

| 3-35        | Circuit Board Component I    | Locat  | ion 8 | and F | in N  | umbe   | ering | • | • | • |   | • | 3-52 |

|-------------|------------------------------|--------|-------|-------|-------|--------|-------|---|---|---|---|---|------|

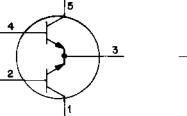

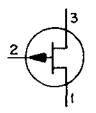

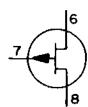

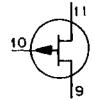

| 3-36        | Semiconductor Lead Identi    | ficati | on    |       |       | •      |       |   |   |   |   |   | 3-54 |

| 3-37        | Control Panel Assignment     | Table  | !     |       |       |        |       |   |   |   |   |   | 3-56 |

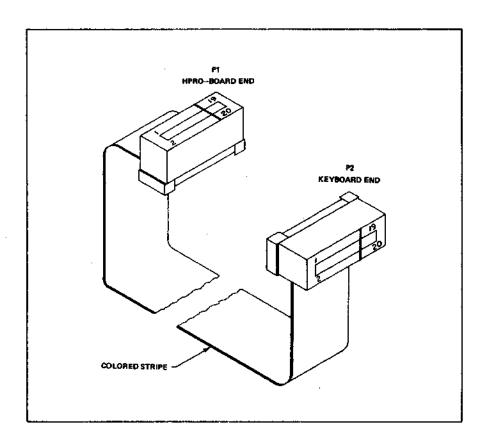

| 3-38        | Keyboard Cable               |        | •     | •     | •     | •      |       |   |   |   |   |   | 3-57 |

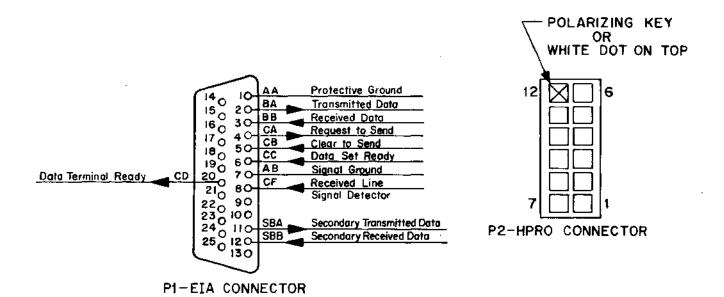

| 3-39        | EIA Cable Pin Identification | n      | •     | •     | •     | •      | •     | • | • | • | • |   | 3-58 |

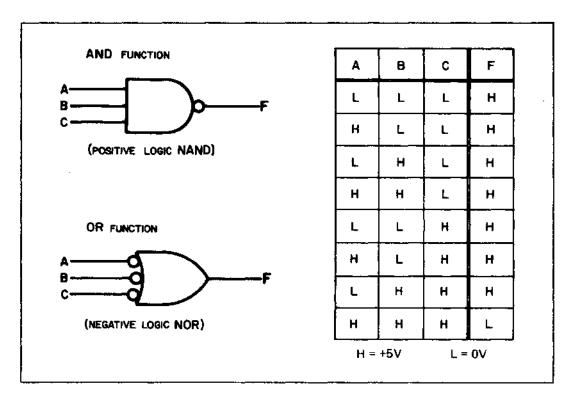

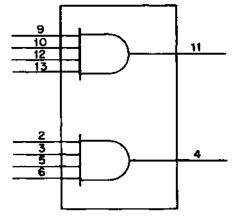

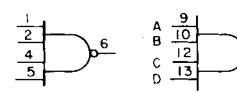

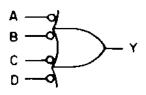

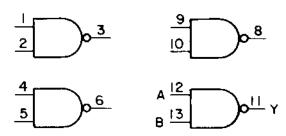

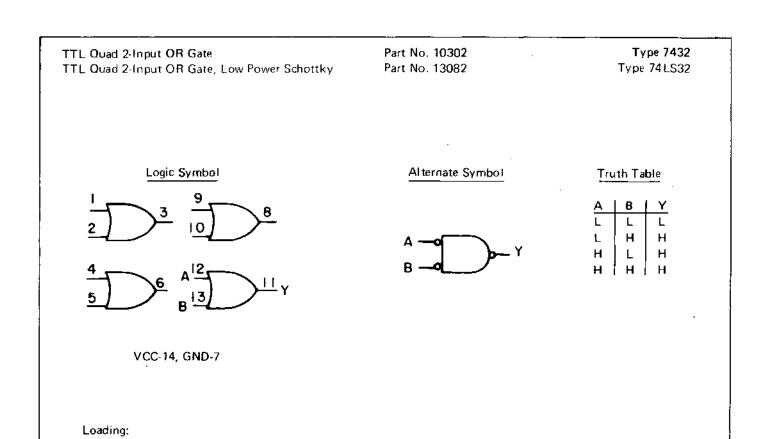

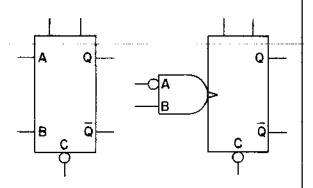

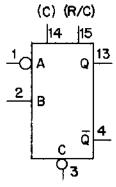

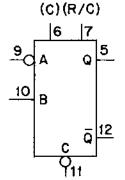

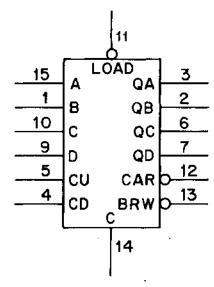

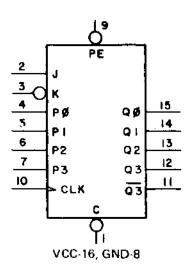

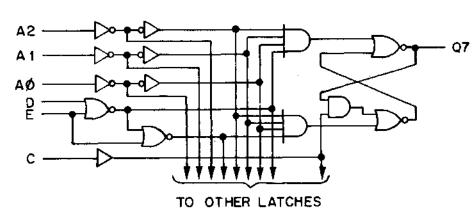

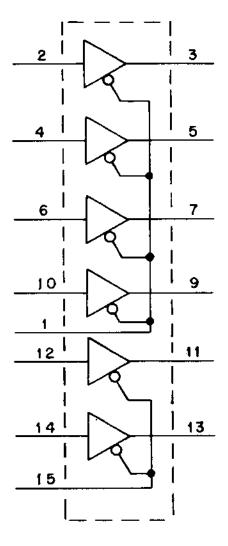

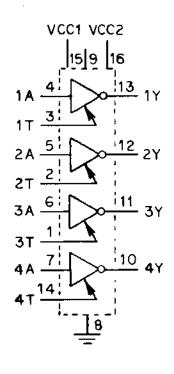

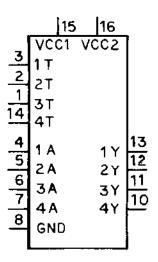

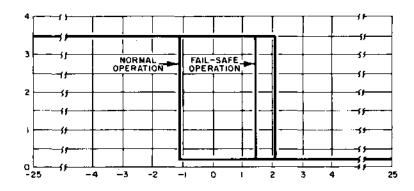

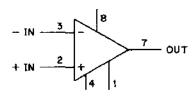

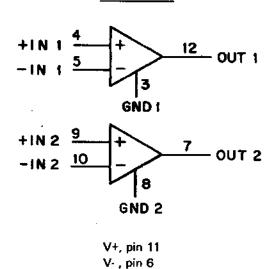

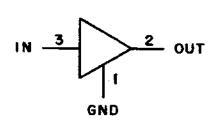

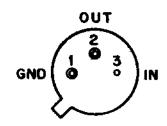

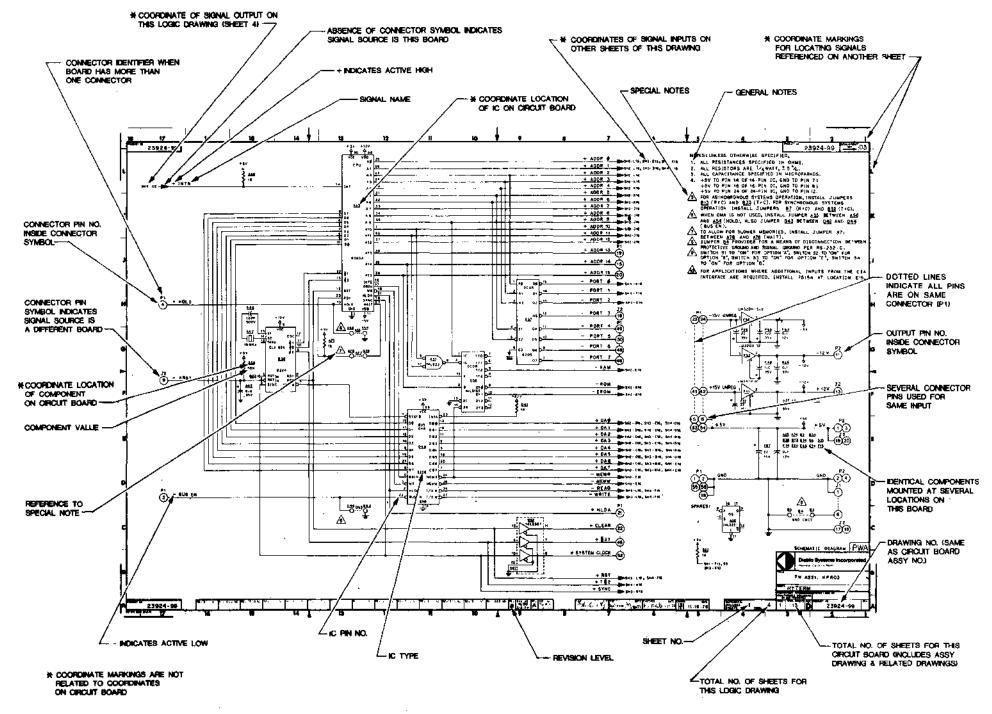

| 4-1         | Examples of Functional Log   | gic    |       |       |       |        |       |   |   |   |   |   | 4-1  |

| 4-2         | ASCII Code Chart             |        |       |       |       |        |       |   |   |   |   |   | 4-63 |

| 4-3         | Logic Drawing Notation       | •      | •     | •     |       |        |       | • |   |   |   |   | 4-64 |

|             |                              |        |       |       |       |        |       |   |   |   |   |   |      |

|             |                              | LIST   | OF    | ТАВ   | LES   |        |       |   |   |   |   |   |      |

| 2-1         | I/O Ports                    | •      | •     |       |       |        |       |   |   |   |   |   | 2-15 |

| 2-2         | Voltage/Current Levels       | •      | •     | •     |       |        |       |   |   |   |   |   | 2-53 |

| 2-3         | Cortron Key Position Numb    | oers a | nd P  | ositi | ion C | odes   |       | • |   |   |   | • | 2-57 |

| 2-4         | Micro Switch Key Position    | Numb   | ers   | and   | Posit | tion ( | Code  | s | • | • |   | • | 2-60 |

| 2-5         | I/O Interface Connections    | •      | •     |       |       |        | •     | • |   | • | • | • | 2-61 |

| 3-1         | Major Assemblies and Modu    | ules   | •     |       |       |        |       |   |   |   |   |   | 3-9  |

| 3-2         | Reference Designators.       |        |       |       |       |        |       | • |   |   |   |   | 3-53 |

| 3-3         | Keyboard Signal Names        |        | •     |       |       |        |       |   |   |   |   |   | 3-55 |

| <i>1</i> −1 | Integrated Cinquits          |        |       |       |       |        |       |   |   |   |   |   | 4-3  |

| 4-1         | Integrated Circuits .        | •      | •     | •     | •     | •      | •     | • | • | • | • | • |      |

| 4-2         | Schematic and Logic Drawi    | ing In | dex   |       |       |        |       | _ |   |   |   |   | 4-62 |

Figure 1-1. Model 1660 HyTerm Communications Terminal

#### Section 1 INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

The Diablo Model 1660 HyTerm Communications Terminal (see Figure 1-1) combines the field-proven Series 2300 Matrix Printer with 1) an integral power supply, 2) additional microprocessor control and Read-Only Memory/Random Access Memory (ROM/RAM), and 3) an Electronic Industries Association RS-232-C interface, to produce a fully-contained data communications terminal that is similar in size and mobility to the ordinary wide-carriage office typewriter. In the local mode of operation, the Model 1660 HyTerm will serve as a desktop document writer for correspondence and other secretarial functions. When used as a data communications terminal, the Model 1660 HyTerm transmits and receives asynchronous serial data over a communications link from a distant computer or data terminal. In this remote mode of operation, the Model 1660 HyTerm may also be used as a computer console or similar I/O device for data entry and data editing. In addition, the Model 1660 HyTerm is ideally suited for computer applications where a hard-copy printout is required on multi-copy forms.

The Model 1660 HyTerm utilizes a 9-wire print head and serial impact to construct characters in a 7 x 9 dot matrix. The matrix printer is capable of printing characters at a maximum speed of 200 characters per second (eps). The microprocessor control and ROM/RAM memory facilitate such features as motion accumulation, high speed horizontal and vertical tabbing, automatic reverse line printing, and complete local and remote control of all printer functions.

#### 1.2 SCOPE

This manual provides information on theory of operation, maintenance, and module replacement. It also includes data covering the electronic components used and explanations of the logic symbology and drawing conventions used. It does <u>not</u> include operating instructions, installation procedures, or information on the functional operation of the HyTerm; these are all contained in the Product Description manual listed in the related documents.

#### 1.3 RELATED DOCUMENTS

- (1) HYTERM COMMUNICATIONS TERMINAL MODEL 1660, PRODUCT DES-CRIPTION. Diablo Systems, Inc. Publication No. 400082-01.

- (2) SERIES 2300 MATRIX PRINTER PARTS CATALOG. Diablo Systems, Inc. Publication No. 82414-01.

- (3) INTERFACE BETWEEN DATA TERMINAL EQUIPMENT AND DATA COM-MUNICATION EQUIPMENT EMPLOYING SERIAL BINARY DATA INTER-CHANGE. EIA Standard RS-232-C, August, 1969. Engineering Dept., Electronic Industries Assn., 201 Eye St. N.W., Washington, D.C. 20006.

- (4) AMERICAN STANDARD CODE FOR INFORMATION INTERCHANGE. USAS X3.4-1977. American National Standards Institute, 1430 Broadway, New York, N.Y. 10018.

- (5) DATA SET 103A INTERFACE SPECIFICATION. February, 1967, Engineering Director, Data Communications, American Telephone and Telegraph Co. Publication 41101.

- (6) DATA SET 202C and 202D INTERFACE SPECIFICATION. May, 1964, Engineering Director, Data Communications, American Telephone and Telegraph Co., Publication 41202.

- (7) Data Set 212A Interface Specification. October, 1976. Director, Data and Special Services, American Telephone and Telegraph Co.

- (8) C.C.I.T.T. GREEN BOOK, VOL. VIII, DATA TRANSMISSION, 1973. The International Telephone and Telegraph Consultative Committee, International Telecommunication Union, Geneva, Switzerland.

Figure 2-1. Model 1660 HyTerm System Block Diagram

#### Section 2 THEORY OF OPERATION

#### 2.1 INTRODUCTION (Figure 2-1)

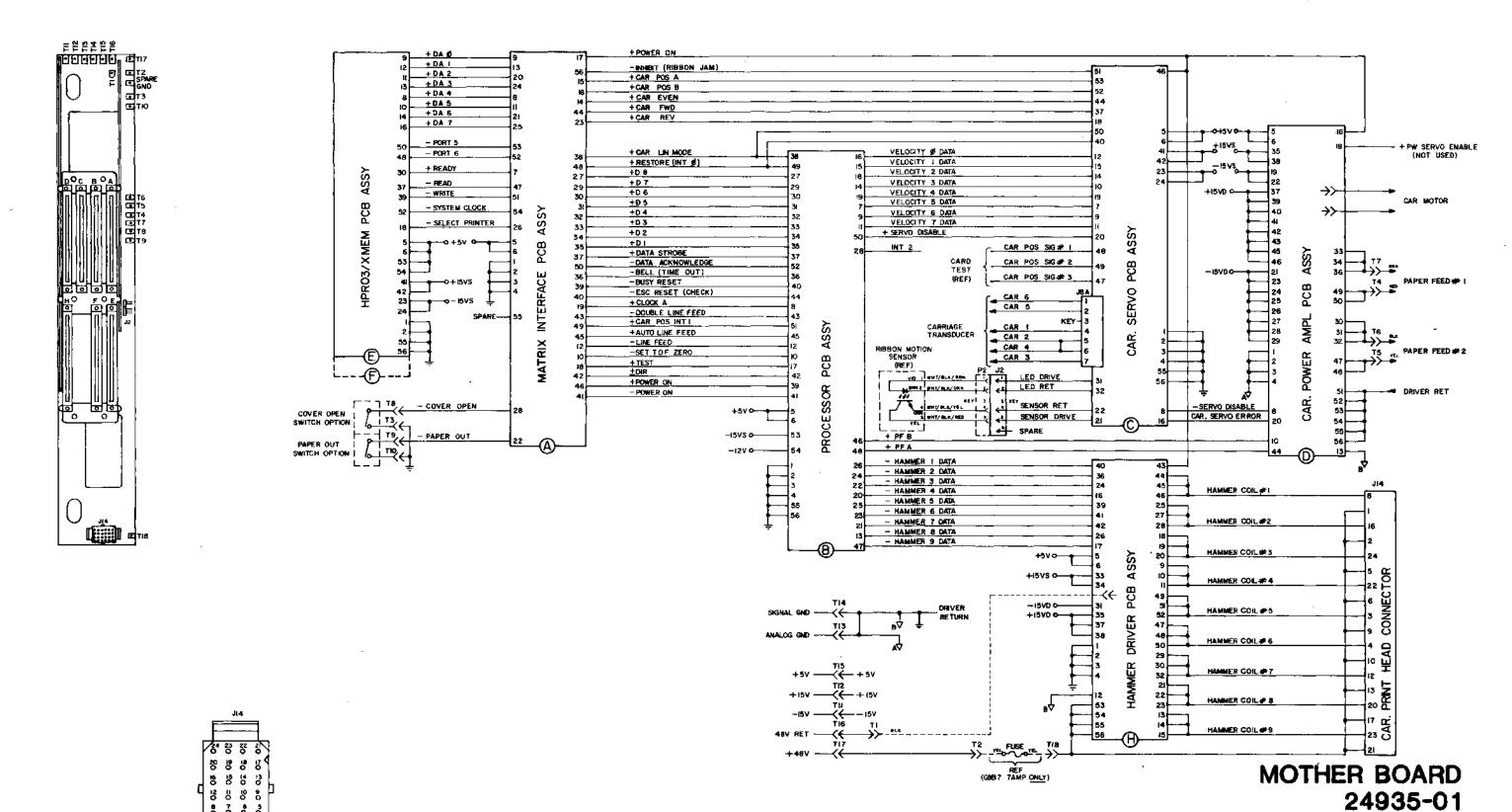

The 1660 employs two separate, asynchronous, processing systems. One, called the "printer microprocessor," is an integral part of all HyType printers. The other, called the "terminal microprocessor," provides the additional functions that transform a matrix printer into a 1660 communications terminal.

The terminal microprocessor, located on the HPRO3 board, controls the overall terminal functions of sending and receiving data over the EIA interface, receiving data from the keyboard, and monitoring the control panel. It also communicates with the printer microprocessor, contained on the PROCESSOR board. This second microprocessor system initiates movement of the printer carriage and paper feed drive motor, and it monitors feedback from the carriage position circuit to effect proper execution of these motion commands. It also issues hammer-fire instructions to the hammer driver board, it provides printer status information to the terminal microprocessor, and it performs other "housekeeping" functions.

The XMEM board is not part of all 1660 terminals. It is used during engineering development, in early production models, and for options when requirements exceed the memory available on the HPRO3 board.

The MATRIX INTERFACE board is located logically between the two microprocessors. It provides temporary storage for data and status information, and synchronizes the transfer of data from the terminal microprocessor to the printer microprocessor, and the transfer of status information back. It also contains some control logic for the servo feedback system.

The CARRIAGE SERVO board receives the carriage motion commands from the printer microprocessor in digital form and converts these to analog signals representative of the distance and direction to be moved. These servo "error" signals are passed on to the carriage power amplifiers, which drive their respective servo motors. Feedback signals, derived from the carriage rotary transducers, are amplified and passed on to the MATRIX INTERFACE board. Here they are available to the printer microprocessor, which uses them to regulate the error signals.

The HAMMER DRIVER board provides nine identical driver circuits for driving each of the nine print head hammers and a hammer protection circuit.

The CARRIAGE POWER AMPLIFIER drives the carriage servo motor and the paper feed step motor. It also monitors the input voltages and develops the POWER ON signal to initiate the Restore operation.

Figure 2-2. Block Diagram, HPRO3 Board

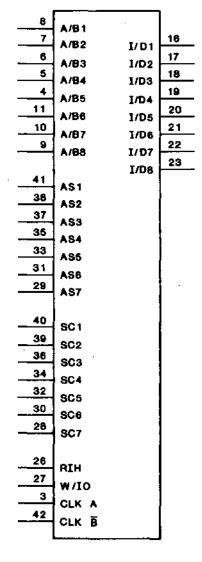

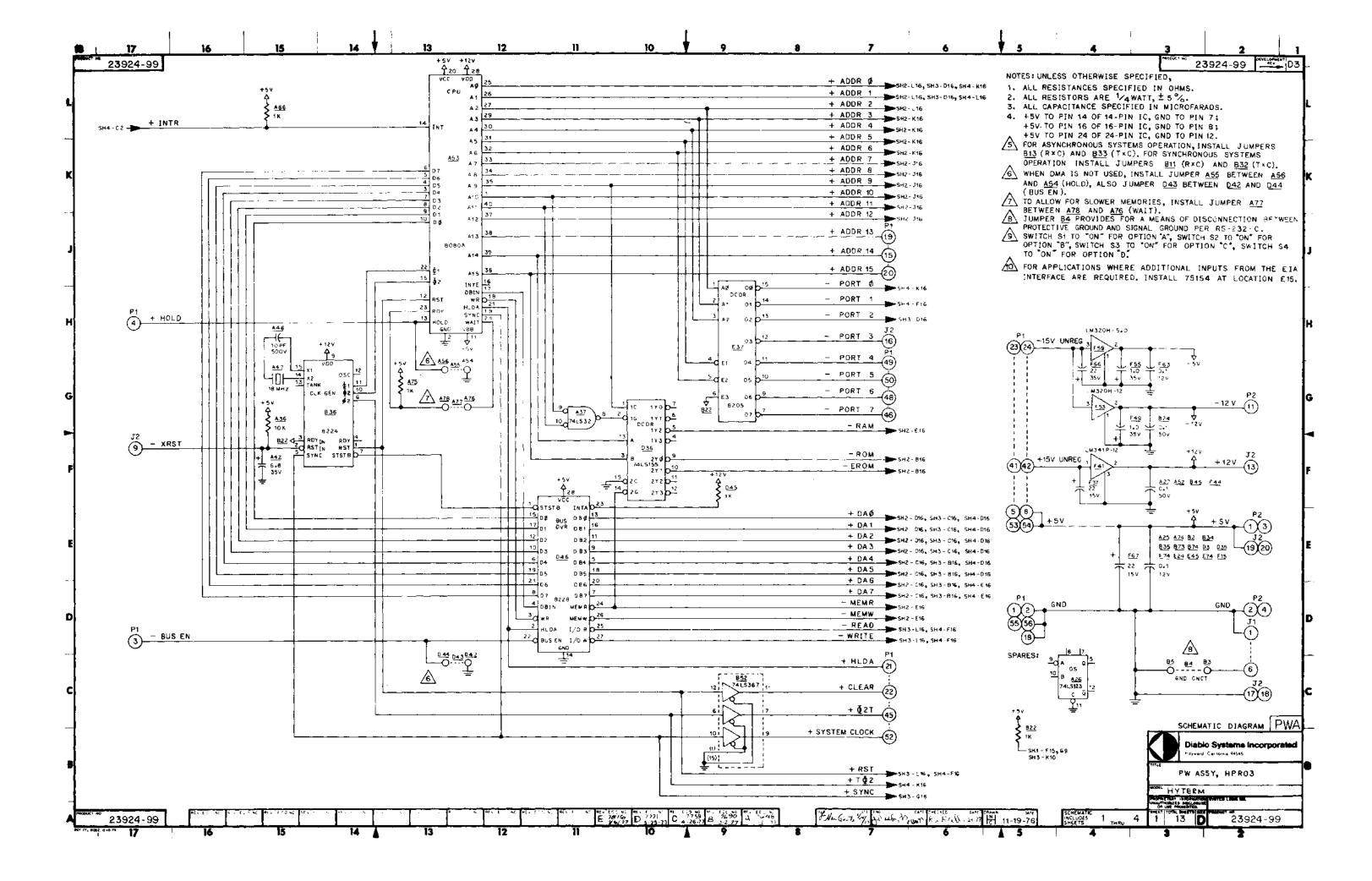

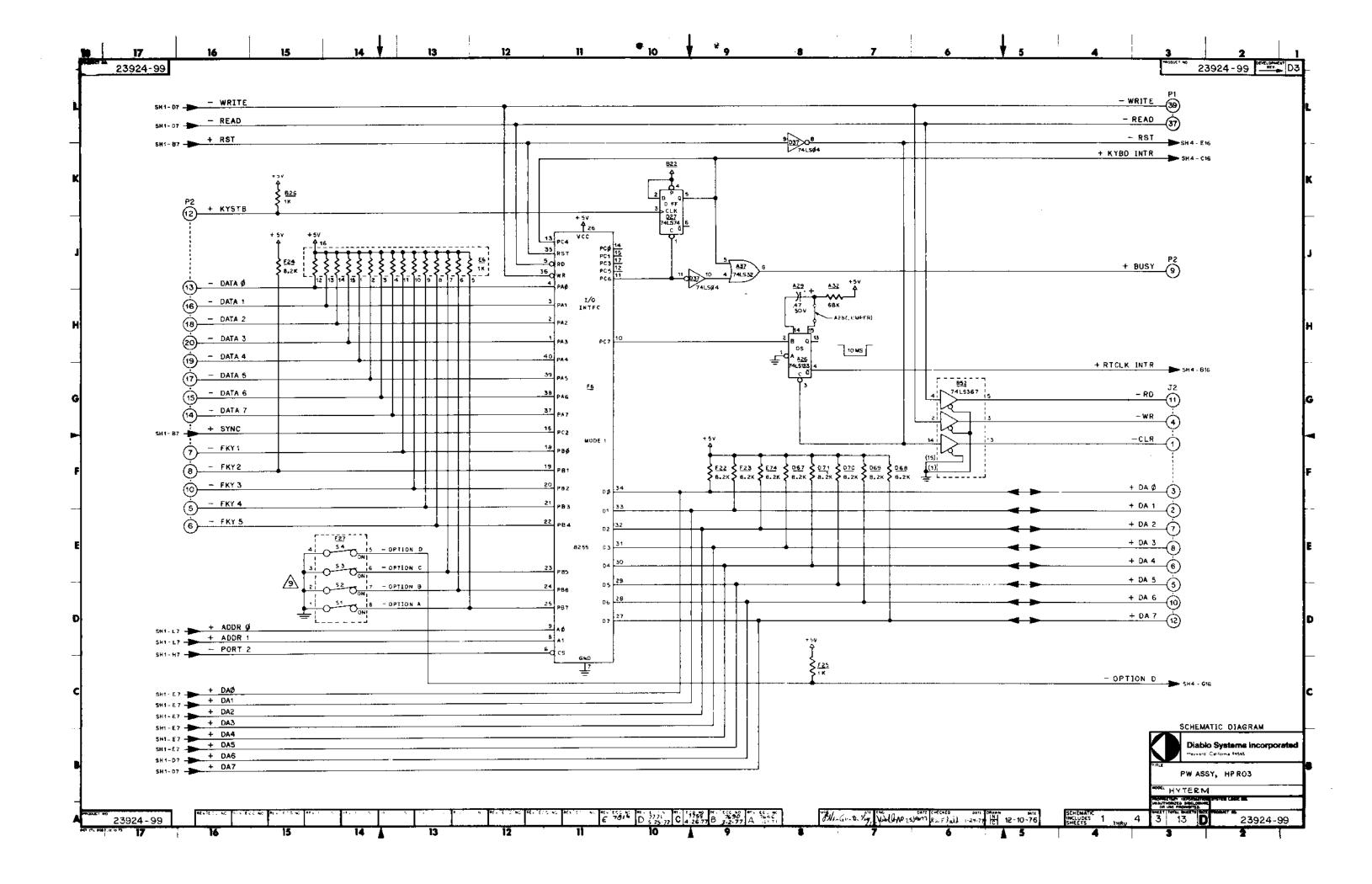

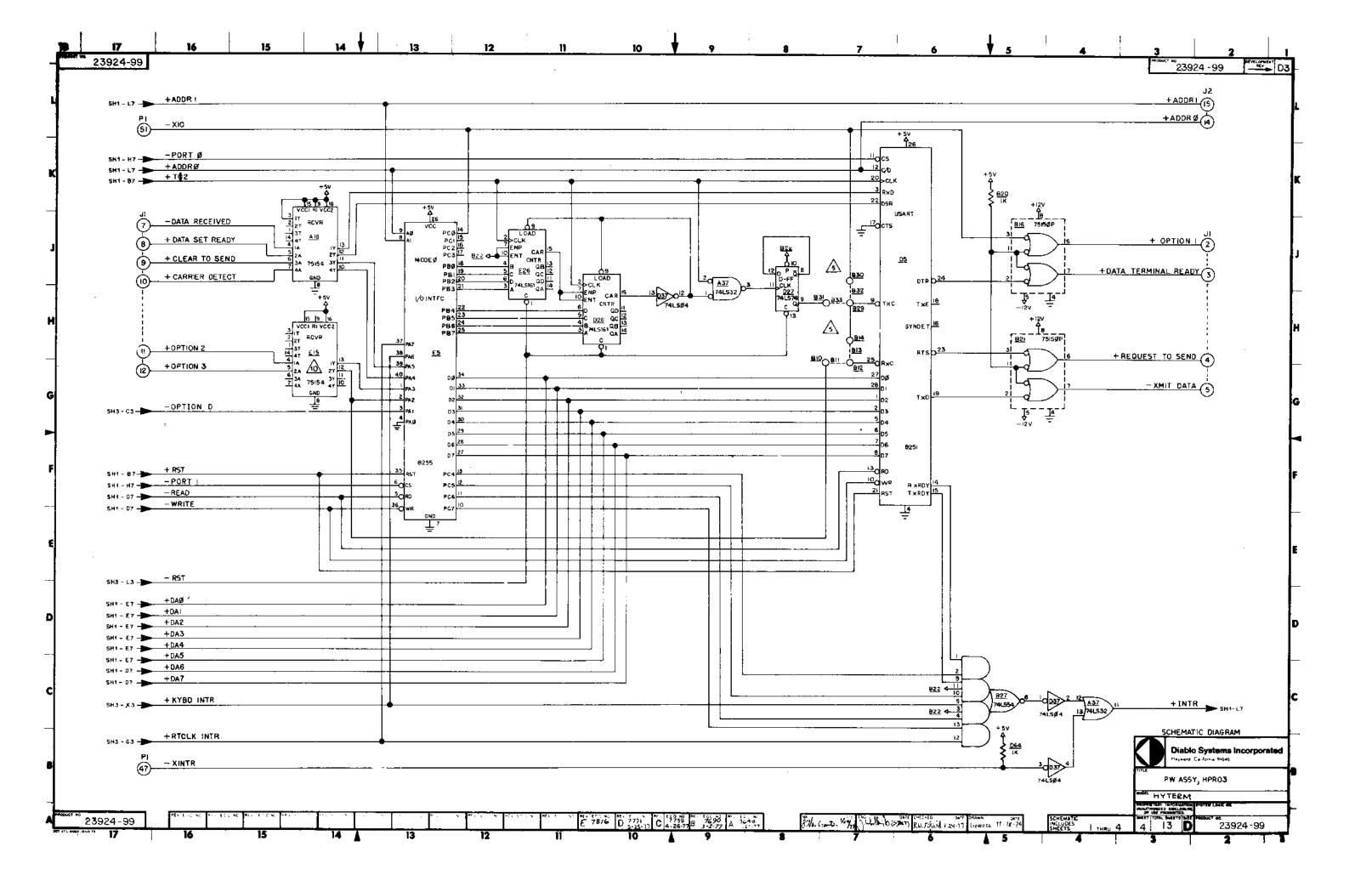

#### PROCESSOR (HPRO3) BOARD, PART NO. 23924-XX (Figure 2-2)

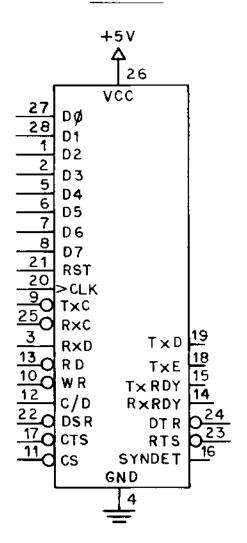

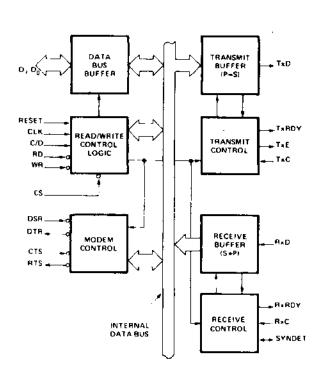

The HPRO3 board contains the terminal microprocessor system. This includes the 8080A Microprocessing Unit (MPU), Memory, several Input/Output (I/O) ports, the Universal Synchronous/Asynchronous Receiver/Transmitter (USART) and its associated RS-232 interface components, and all control electronics.

#### NOTE

Throughout this manual, two terms will be used extensively: terminal microprocessor refers mainly to the entire HPRO3 circuit board, whereas MPU refers to the 8080A integrated circuit.

#### 2.2.1 General Operation

2.2

The terminal microprocessor is actually a miniature computer. It receives its instructions from Read Only Memory (ROM), either locally or located on the XMEM board. These instructions are arranged to form a "microprogram." As it executes this microprogram, the MPU receives data from the various input ports and stores it in memory, or reads data out of memory and sends it to the various output ports. Between input and output instructions, the MPU may perform other operations on the data, make logical decisions concerning the data, or "jump" to a different portion of its program.

#### 2.2.1.1 Input/Output

Data can enter or leave the HPRO3 board via any of four channels. First, in the case of the keyboard, data enters the board over the "keyboard data bus" and is held in Port 2 until the MPU is ready for it. Then the MPU "reads" the data from Port 2, and the data is transferred to the MPU over the bidirectional data bus.

Second, data may enter (or leave) over the EIA interface, and be held temporarily in the USART (Port 0). The data is transferred between the MPU and the USART over the bidirectional data bus.

Third, data may enter or leave the board over the 8-bit bidirectional data bus through the J2 connector (normally used for the control panel). In this case, an "I/O port" or its equivalent must be located on another board cable-connected to the HPRO3 board via J2. This port is addressed as Port 3.

Fourth, data may enter or leave the board over the 8-bit bidirectional data bus through the mother board connector (P1). Again, an I/O port of some type must be located on another circuit board plugged into the printer mother board. The port must be addressed as Port 4, 5, or 6.

In this fourth case, the data transfer can be either between the MPU and the external port, or it can be directly between the memory and the external port, bypassing the MPU. If direct memory access is used, the external port or device must provide the necessary signals to delay, or "hold," the MPU while the data transfer is taking place.

Note that the MPU can also address Port 1 for either input or output. This port, however, is contained fully on the HPRO3 board, and does not transfer data onto or off the board. It is used for local control of the baud rate and interrupt enable/disable, and to monitor interrupt status.

When the XMEM board is supplied, it is addressed in the same manner as HPRO3 internal memory via address lines on the mother board. Data is also transferred via the mother board.

#### 2.2.1.2 Interrupts

The normal microprogram instruction sequence can be interrupted when necessary to enable the transfer of data to or from an I/O device, or for other purposes. Generally, when an interrupt occurs, the MPU completes the instruction it is presently performing, and then jumps to its interrupt servicing routine, which begins at memory location 0056<sub>10</sub>. This routine first determines what type of interrupt is occurring, and then performs the steps necessary to service the interrupt. If two or more interrupts occur simultaneously, the interrupt service routine in the microprogram determines which will be serviced first.

There are five types of interrupts, all of which can be individually enabled or disabled by the microprogram. The first four types can be independently enabled or disabled on the HPRO3 board, whereas the last type (external) must be disabled on the circuit board on which it is initiated (some external circuit board). The five types of interrupts are as follows:

| (1) | USART receive:   | the USART has received a character from the data link and is waiting to transfer it to the MPU.                                                  |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| (2) | USART send:      | the USART has shifted a character out to the data link and is ready to accept a new character from the MPU for transmission.                     |

| (3) | Keyboard:        | a data character has been received from the keyboard (or parallel data interface) accompanied by a strobe, and is waiting to be read by the MPU. |

| (4) | Real-Time Clock: | the Real-Time Clock has timed out, denoting that 10 ms has elapsed since it was activated.                                                       |

| (5) | External:        | an interrupt can be generated by logic on a different circuit board and applied to the HPRO3 board via the -XINTR input.                         |

#### 2.2.1.3 Memory

Either random-access memory (RAM), read-only memory (ROM), or erasable read-only memory (EROM) ICs (or all three) may be used. Maximum capacity of the HPRO3 board is 4K bytes of ROM, 1K of EROM, and 512 bytes of RAM. Additional memory on the XMEM board can be utilized by placing the necessary address on the memory address bus; data is transferred over the bidirectional data bus.

#### 2.2.1.4 Real-Time Clock

A 10-ms one-shot is used as a real-time clock, to allow the MPU to pole various I/O ports (eg, the control panel) at regular intervals.

#### 2.2.1.5 Special Voltage Supplies

The HPRO3 board also contains local voltage regulators to convert the  $\pm 15V$  from the main power supply to  $\pm 12V$  and -5V needed by the EIA interface, some of the memory ICs, the MPU, and some external circuits and devices.

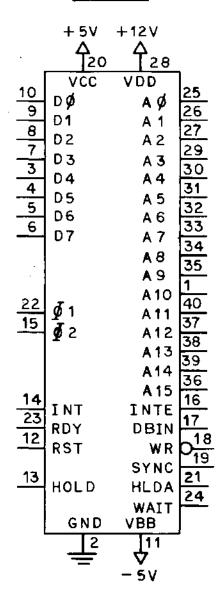

#### 2.2.2 <u>8080A Microprocessing Unit (MPU)</u>

The 8080A is an 8-bit microprocessor contained in a single 40-pin integrated circuit (IC) package. It has an 8-bit wide bidirectional data bus used for both input and output. It has a 16-bit address bus, capable of addressing up to 65,536 memory locations. The MPU's instructions are located in memory, from where they are fetched and executed sequentially. There are over 100 separate instructions possible, although many are similar, the difference being only in the various MPU internal registers specified.

#### 2.2.2.1 Architecture

To understand the operation of the terminal microprocessor, it is only necessary to know that the MPU contains an instruction register, a program counter, a memory address register, a stack pointer, and other registers and logic elements. The instruction register contains the 8-bit instruction op code. The program counter contains the 16-bit memory address of the next instruction to be fetched. The memory address register is made up of two 8-bit registers, referred to as the H and L register pair. It is used to address memory for memory read and memory write instructions. Other internal MPU registers can also be used to address memory. The stack pointer is generally used to "remember" the address of the next sequential main program instruction while an interrupt subroutine is being executed. Still other elements internal to the MPU perform the arithmetic and logic operations and control the input and output over the data bus.

This is admittedly a very brief description of the MPU architecture, but this background should be sufficient to allow understanding of the material to follow. Further information on the MPU can be found in the integrated circuit information presented in the Schematics/Reference section of this manual.

#### 2.2.2.2 Timing

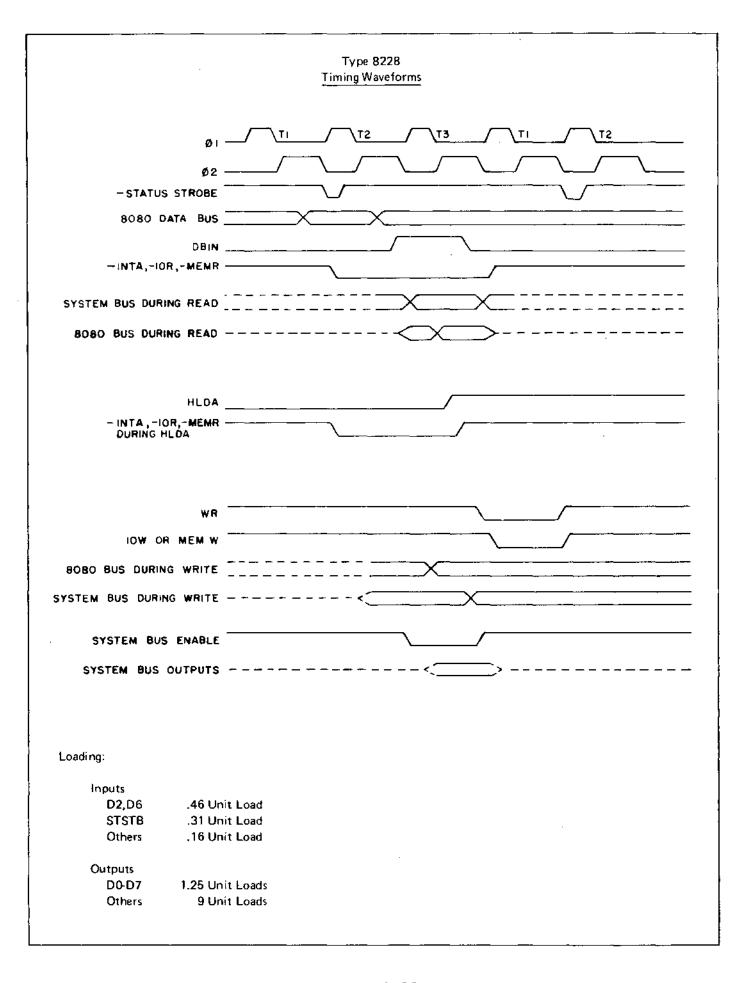

Timing is controlled by two 12V (nominal) non-overlapping clocks,  $\Phi 1$  and  $\Phi 2$ . These clocks are provided at a frequency of 2 MHz by a Clock Generator IC.

#### 2.2.2.3 Basic Processor Operation

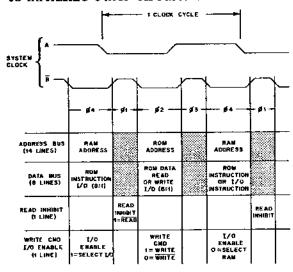

MPU operation is divided into time periods called "cycles" and "states." There are two types of cycles: instruction cycles and machine cycles. The material that follows is summarized in the timing chart in Figure 2-3.

#### A. Without WAIT State

#### B. With WAIT State

\*Numbers in circles refer to types of machine cycles.

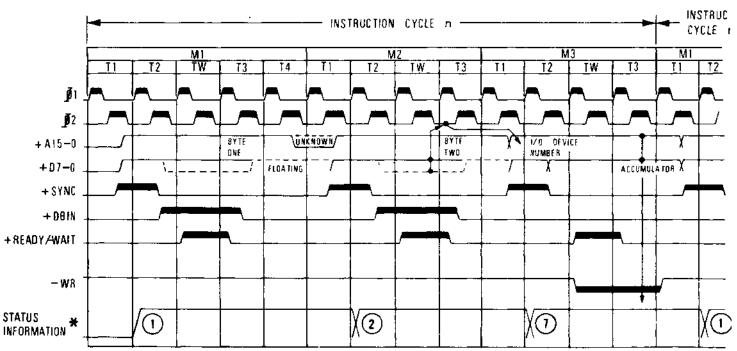

Figure 2-3. Typical Instruction Cycle (Output Instruction)

2.2.2.3.1 <u>Instruction Cycle.</u> An instruction cycle includes both the fetching of the instruction from memory and the execution of the instruction. Each instruction may contain one, two, or three 8-bit bytes. Multiple byte instructions must be stored in successive memory locations. Figure 2-4 illustrates the three instruction formats. The actual bit configuration of the op code is not important to the understanding of the terminal processor operation.

#### One Byte Instructions

|     | J        |            |        |    |    |    |    |    |                    |

|-----|----------|------------|--------|----|----|----|----|----|--------------------|

|     | D7       | D <b>6</b> | D5     | D4 | D3 | D2 | D1 | D0 | OP CODE            |

| Two | o Byte I | instruct   | ions   |    |    |    |    |    |                    |

|     | D7       | D6         | D5     | D4 | D3 | D2 | D1 | D0 | OP CODE            |

|     | D7       | D6         | D5     | D4 | D3 | D2 | D1 | D0 | DATA or<br>ADDRESS |

| Thr | ee Byte  | e Instruc  | etions |    |    |    |    |    |                    |

|     | D7       | D6         | D5     | D4 | D3 | D2 | D1 | D0 | OP CODE            |

|     | D7       | D6         | D5     | D4 | D3 | D2 | D1 | D0 | DATA or            |

|     | D7       | D6         | D5     | D4 | D3 | D2 | D1 | D0 | ADDRESS            |

|     |          |            |        |    |    |    |    |    |                    |

Figure 2-4. MPU Instruction Format

- 2.2.2.3.2 <u>Machine Cycle.</u> A machine cycle is required each time an I/O array or the memory is accessed. Each instruction cycle can contain from one to five machine cycles. There are ten different types of machine cycles possible, as follows:

- (1) Instruction Fetch

- (2) Memory Read

- (3) Memory Write

- (4) Stack Read

- (5) Stack Write

- (6) Input

- (7) Output

- (8) Interrupt Acknowledge

- (9) Halt Acknowledge

- (10) Interrupt Acknowledge While in Halt

- 2.2.2.3.3 States. A state is defined as the time interval (500 ns) from leading edge to leading edge of the  $\Phi$ 1 clock. There are 6 possible states, numbered T1 through T5 and TW (representing "wait"). All machine cycles include T1, T2, and T3. When the jumper wire is installed between pins 24 (WAIT) and 23 (RDY) of the 8080A, TW follows T2. This is to slow down the MPU so that slower memory ICs may be used. T4 and T5 are omitted during execution of instructions not requiring them.

2.2.2.3.3.1 T1. During state T1 either a memory address or an I/O port number is placed onto the memory address bus. Also, the MPU places eight bits of status information on the data bus which identify the type of machine cycle being performed. Following the rising edge of  $\Phi$ 2 the SYNC signal is produced by the MPU, which identifies the beginning of a machine cycle. See Figure 2-3.

2.2.2.3.3.2 T2. During state 2 the MPU monitors its RDY input. If it is high, the MPU goes on to state 3; if it is low, the MPU goes on to the Wait state.

During machine cycles that bring data into the MPU (Instruction Fetch, Memory Read, Stack Read, Input, and Interrupt Acknowledge), the Data Bus In signal, DBIN, is developed at  $\Phi$ 2 during T2. DBIN remains high through TW and into T3. This signal develops -READ and -MEMR at the proper time to provide the input data needed by the MPU. (This is covered more fully in 2.2.4.)

2.2.2.3.3.3 TW. The wait state provides the MPU delay required for proper memory access. No internal processing occurs during this state. The MPU monitors its RDY input, and if it is low, it remains in the Wait state; if it is high, the MPU goes on to state 3. If the RDY input is connected to the WAIT output, the MPU goes on to T3 after one state time (500 ns) in TW.

During machine cycles in which the MPU outputs data (Memory Write, Stack Write, Output), it develops the WR (Write) signal during TW or T3 and holds it low until after the end of T3. This signal is used by other logic on the HPRO3 board or another board to strobe the output data to memory or to the selected output port.

2.2.2.3.3.4 T3. During state T3 the data or instruction byte is actually transferred between the MPU and memory or an I/O port. The source and destination of the byte is determined by the type of machine cycle being performed. For example, during an instruction fetch cycle, the source of the data (instruction byte) is the memory location addressed during state 1; the destination is the MPU. During an Output machine cycle, the source is the MPU and the destination is the I/O port selected (addressed) in state 1.

2.2.2.3.3.5 T4 and T5. These two states are used only when required for manipulation of data within the MPU.

2.2.2.3.4 Hold. When the +HOLD signal goes high, it causes the MPU to stop operation at the end of the instruction currently being executed. This is used during direct memory access; when DMA is not used, the +HOLD line is held low by a jumper wire to GND.

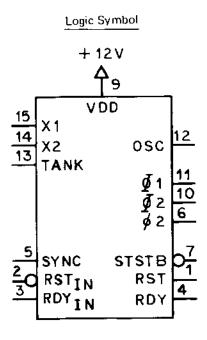

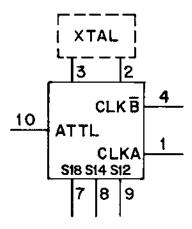

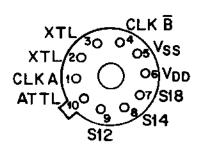

#### 2.2.3 Clock Generator (8224)

The clock generator is contained in a single integrated circuit that provides several functions. First, it provides the two non-overlapping 12V signals,  $\Phi$ 1 and  $\Phi$ 2, required by the MPU. The frequency of these signals (2 MHz) is controlled by an external quartz crystal. A TTL equivalent of the  $\Phi$ 2 signal, +T $\Phi$ 2, is also developed for use in timing other functions.

Second, the 8224 converts the MPU's SYNC signal into the Status Strobe signal, STSTB. This signal is used to load the status information, put out by the MPU at the beginning of each machine cycle, into the Bus Driver/System Controller IC. This is covered more fully in 2.2.4.

Third, at power-on, the clock generator IC develops +CLR, which is used to reset and initialize the entire HPRO3 board.

The 8224 has other capabilities not utilized by the terminal microprocessor.

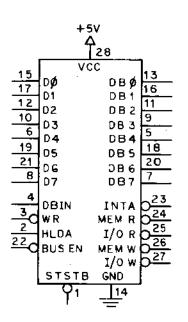

#### 2.2.4 Bus Driver/System Controller (8228)

This module is another single IC that performs three basic functions: bidirectional bus control, system logic control, and initial interrupt request processing.

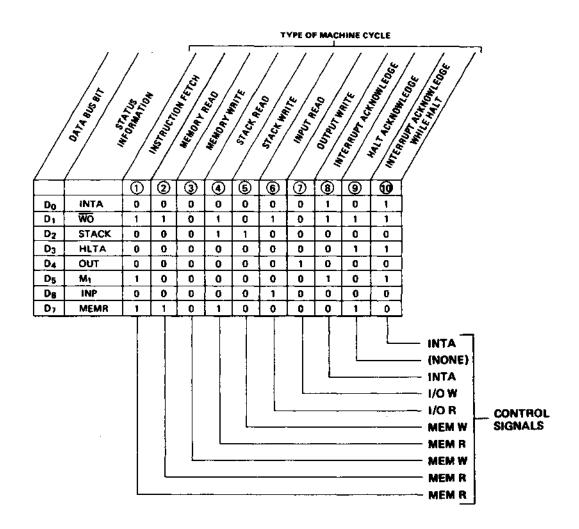

Figure 2-5. MPU Status and Resultant Control Signals

#### 2.2.4.1 Bus Control

The 8228 provides a buffer between the MPU and the memory and I/O ports. Controlling the two 8-bit data buses on the HPRO3 board involves not only switching the data on and off in the proper direction at the right time, but also in providing the required voltage and current levels. Since the MPU is an MOS device, it requires a voltage of at least +3.3 volts for a "logic 1" or "true" indication on its data inputs. The 8228 provides a minimum of +3.6 volts on the 8080 Data Bus, which is substantially higher than can be guaranteed by standard TTL devices. For output data, the MPU can provide only 1.9 mA of current drive. With many I/O ports and the memory connected to the bidirectional data bus, this value could easily be exceeded, so the 8228 is used to provide over 10 mA to satisfy this requirement. The buses can be "turned off" (forced into the high-impedance state) when direct memory access is used. See 2.2.4.4. The direction of data flow on the buses is controlled internally by the same signals that furnish the system control function performed by this IC.

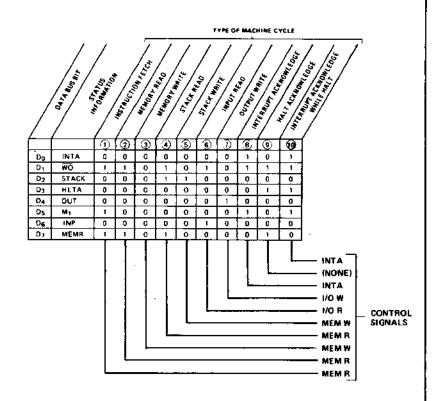

#### 2.2.4.2 System Logic Control

At the beginning of each machine cycle, the MPU issues "status" information on the 8080 data bus that indicates the type of cycle about to be performed. At the same time, the clock generator module develops STSTB, which loads this status information into a status latch inside the 8228. This status latch output is decoded, along with DBIN, WR, and HLDA (Hold Acknowledge) from the MPU, into the system control signals MEMR (Memory Read), MEMW (Memory Write), READ (I/O READ), and WRITE (I/O WRITE). (These decoded signals also provide the internal control of the bus driver.) Note that these signals are not levels, but that they are gated by DBIN or WR from the MPU at the proper time. The status information provided by the MPU, and the system control signals developed for each of the ten types of machine cycles are shown in Figure 2-5.

#### 2.2.4.3 Interrupt Handling

The 8228 is capable of handling interrupts in either of two different ways. Only one of these methods is used in this terminal, in which the Interrupt Acknowledge pin (23) is connected to +12V through a resistor. Connected this way, when the MPU is interrupted (by an input from the keyboard or USART, for example), it performs an INTERRUPT ACKNOWLEDGE machine cycle, and the 8228 automatically forces an RST 7 (Restart 7) instruction into the MPU. This instruction causes the MPU to fetch its next instruction from memory location 56<sub>10</sub>, which begins the routine needed to service the interrupt.

#### 2.2.4.4 Direct Memory Access

The BUS ENable input (pin 22) must be low for normal operation. When direct memory access is used, the DMA circuitry on another board drives this signal high, forcing all 8228 outputs into their high-impedance state. This allows the bidirectional data bus and the MEMR and MEMW signals to be controlled by the DMA logic. If the DMA feature is not used, -BUS EN is held low by a jumper wire to GND.

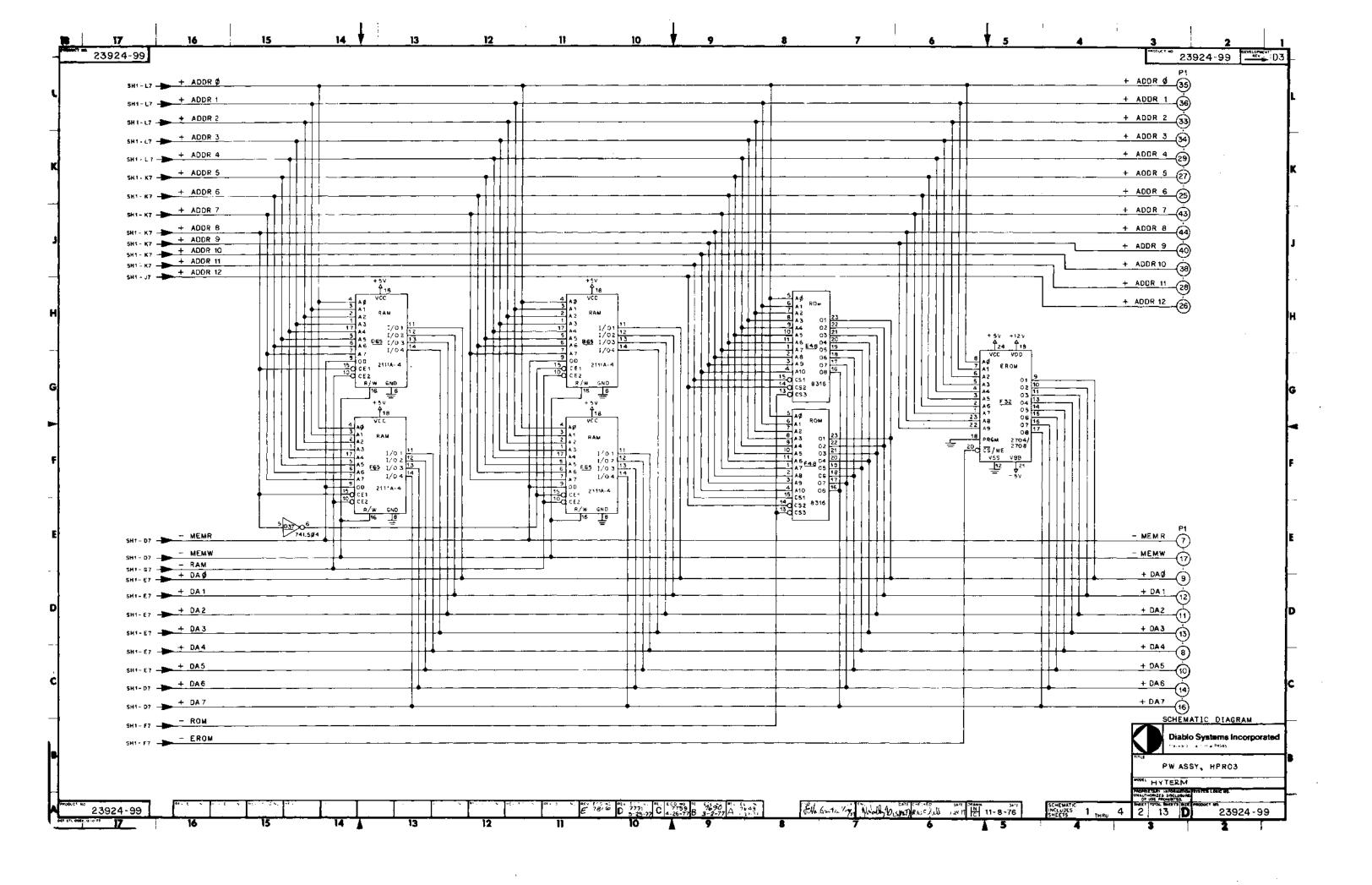

#### 2.2.5 Memory

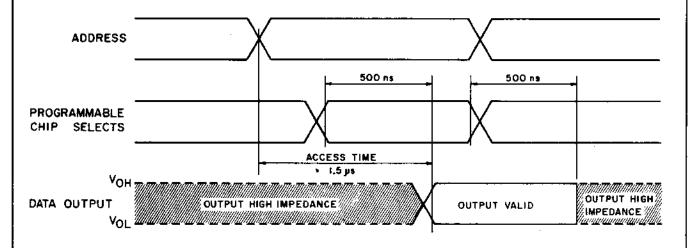

Maximum memory capacity of the HPRO3 board is 4K ROM, 512 bytes of RAM, and 1K of EROM. ROM memory consists or one or two 2K x 8-bit mask-programmed ROM ICs containing the terminal microprogram. RAM memory consists of two 256 x 4-bit ICs for each 256 bytes. The EROM portion can be either a 512 x 8-bit or 1K x 8-bit EROM IC. The EROM would normally contain keyboard position encoding data or similar data for terminals built in small quantities—too small to justify masked-ROM changes. When the XMEM board is supplied, the terminal microprogram can be stored there. See paragraph 2.3.

#### 2.2.5.1 Addressing

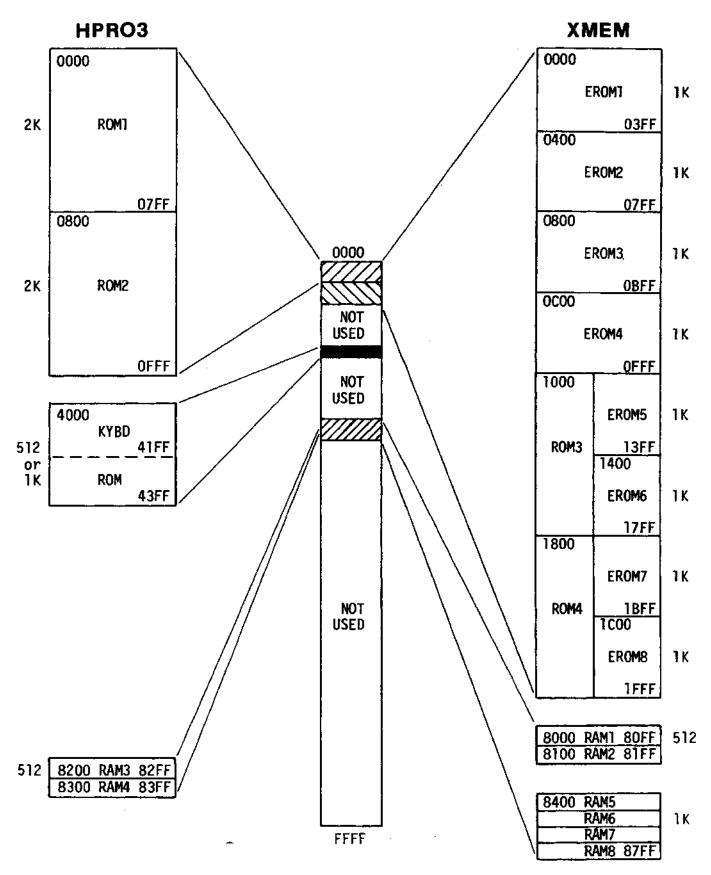

The memory map in Figure 2-6 shows the relationship of the various memory elements to their addresses.

The memory ICs on the HPRO3 board are addressed by the lower-order bits of the memory address bus. The higher-order bits A9, A10, A11, A14, and A15 are used to select, through a decoder, whether RAM, ROM, or EROM will be addressed. In the case of RAM, the state of the A8 line determines which pair of ICs will be addressed. For ROM, the A11 line selects which of the two possible ICs will be used. (Note that A11 goes to both ROM ICs; the internal programming of the ICs is such that one of the ICs will be activated when A11 is low and the other when A11 is high.)

Since the memory address bus is available on the HPRO3 board outputs, external memory can assume any memory address, so the terminal designer must assure that only one memory location exists for each address. For example, during program development, the microprogram can be contained in external memory beginning at location 0000. In this case, the HPRO3 board cannot have ROMs installed. After the microprogram is perfected, it can be "burned" into masked ROMs, which can be installed on the HPRO3 board, and the external memory board can be eliminated.

The memory address bus being available on the HPRO3 board's plug also enables the entire memory to be addressed from and external source, as is the case when the DMA function is utilized.

#### 2.2.5.2 Reading

All memory ICs are three-state devices. This means that the outputs remain in the high-impedance, or "off" state, at all times when the IC is not selected. (This allows the memory address bus to be used for addressing I/O devices; the address lines can assume any configuration, but there will be no input to or output from memory without the proper system control signals.) The MEMR signal is connected to the "output disable" input of the RAMs (pin 9). This maintains the RAM outputs in their high-impedance state at all times other than during a memory read. MEMR is also one of the inputs to the memory type decoder. This allows ROM and EROM to be selected only during a read operation.

NOTES: 1. First 4K can be either ROMs on HPRO3 or EROMs on XMEM.

2. Second 4K can be either ROMs or EROMs on XMEM.

Figure 2-6. Memory Map

#### 2.2.5.3 Writing

When memory write is performed, the RAM output remains disabled (MEMR is high), and MEMW being low allows information on the bidirectional data bus to be written into the addressed RAM location. Note that each pair of RAMs operates in parallel, one IC servicing the low-order four bits of the bidirectional bus, and the other taking care of the high-order four bits.

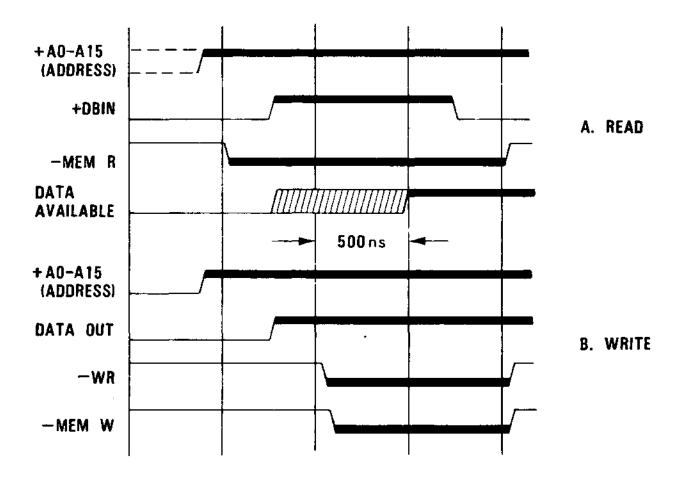

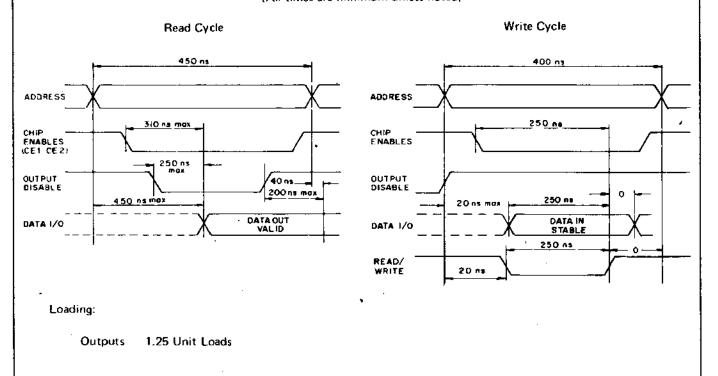

#### 2.2.5.4 Timing

Typical idealized timing waveforms are shown in Figure 2-7. Specific timing requirements for each of the memory IC types can be found in the IC information in the schematic/reference section. In all cases, the timing shown in Figure 2-7 is within the timing constraints of the individual ICs.

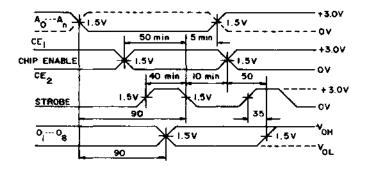

Figure 2-7. Memory Timing

#### 2.2.5.5 Direct Memory Access

When the DMA function is utilized, it conforms to the following general sequence:

- (1) DMA circuitry on another board raises the +HOLD line to the MPU.

- (2) The MPU finishes the instruction it is presently performing, and then raises its HLDA (Hold Acknowledge) line. It then suspends operations, and holds all data and address lines in their high-impedance state.

- (3) The DMA circuitry receives the hold acknowledgement and drives -BUSEN low. This forces the 8228 to place all of its outputs, both data and control signals, into their high-impedance state.

- (4) The external DMA circuitry then places the desired address on the memory address bus, and drives either -MEMR or -MEMW low. The data is then transferred over the bidirectional data bus.

- (5) When the DMA circuitry is finished, it raises -BUSEN and lowers +HOLD, and the MPU resumes processing at its next sequential instruction.

#### 2.2.6 Input/Output

The terminal microprocessor can address up to eight I/O ports. These ports, or "devices," such as keyboard, control panel, etc., are addressed over the Memory Address Bus, and data is transferred to and from the MPU over the bidirectional data bus. An I/O channel or device is first addressed by the MPU, which then develops the -READ or -WRITE signal to transfer the data. On output, for example, the MPU first addresses a particular output device, then places the output data on the bidirectional data bus, and finally develops -WRITE. Although the data is available to all "devices" on the bus, only the one that had been addressed can accept the data. Input is similar: only the addressed device places data onto the bus. All other devices are "observers."

The five low-order bits of the memory address bus are used for I/O device selection. Bits 2, 3, and 4 are applied to a decoder, the outputs of which (-PORT Ø through -PORT 6) are used to select one of the seven possible ports. Each port can comprise up to four 8-bit bytes, and bits 0 and 1 are used to select one of the four bytes.

Three of the seven possible I/O ports are located on the HPRO3 board. The rest of the ports may or may not be used in a particular terminal or printer. The possible ports and their typical functions are as shown in Table 2-1.

#### 2.2.6.1 USART (Port 0)

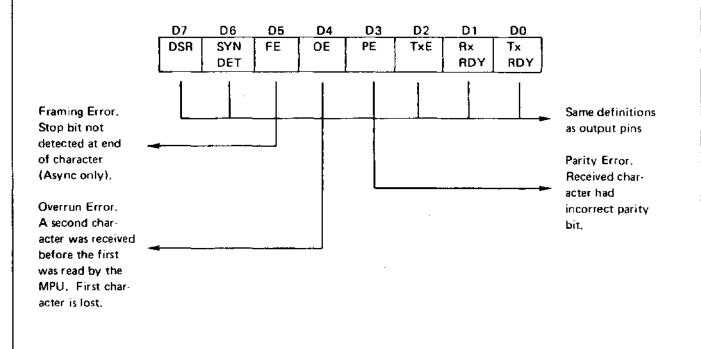

The type 8251 USART (Universal Synchronous/Asynchronous Receiver/Transmitter) IC accepts an 8-bit byte of data from the MPU in parallel format and converts it to a serial stream of data for transmission over the communications link. Similarly, it receives data characters from the link in serial format and converts them into parallel data bytes for the MPU. During transmission, the USART adds start, stop, and parity bits. During reception, it strips these bits and also checks parity, if desired. It also checks for data framing errors and overrun errors, and can monitor modem status. It has other capabilities that are not generally used (synchronous transmit/receive, character lengths down to 5 bits, etc.).

Table 2-1. I/O Ports

| Port<br>No. | Function                                        |

|-------------|-------------------------------------------------|

| 0           | USART                                           |

| 1           | Baud Rate, Interrupt<br>Enable/Disable & Status |

| 2           | Keyboard                                        |

| 3           | Control Panel                                   |

| 4           | DMA                                             |

2.2.6.1.1 Addressing. The CS (Chip Select) input is driven low whenever the MPU addresses Port 0. No information can be transferred between the USART and the MPU until the USART is selected.

The USART also has a C/D input, which is connected to the +ADDR Ø line of the Memory Address Bus. When this line is high, control information is transferred; when it is low, data is transferred. The USART does not utilize the +ADDR 1 line.

2.2.6.1.2 Timing. Refer to the baud rate counter discussion in 2.2.6.2.1.2.

2.2.6.1.3 <u>Information Transfer.</u> Two inputs, RD and WR, determine the direction of information transfer. When RD is low, the USART places data or status information (determined by the C/D input) on the bidirectional data bus for input to the MPU. When WR is low, data or control information from the MPU is taken off the data bus and loaded into the USART. The RD and WR inputs are controlled by -READ and -WRITE, respectively, from the 8228 bus driver/system controller.

Note that all information transfer between the MPU and the USART is over the bidirectional data bus, through a bidirectional, 3-state buffer within the USART. Information transfer between the USART and the data link is over individual lines for Send Data, Receive Data, and each of the modem status and control lines, through a voltage level converter, to (or from) the modem. (Refer to the integrated circuit data in the Schematics/Reference section for information on the level converter ICs.)

2.2.6.1.3.1 Read Data. When the USART receives a character from the data link, it raises its RXRDY (Receiver Ready) line, which goes to the interrupt logic. If USART interrupts are enabled, +INTR is developed and sent to the MPU. In servicing this interrupt, the MPU performs a sequence of instructions, one or which is an input from Port 0. With CS low, RD low, and C/D low, the USART puts an 8-bit byte of data onto the bidirectional data bus, from where it is accepted by the MPU. The USART, having presented the data byte to the bus, resets its RXRDY line, until the next character is received and the entire sequence repeats.

As the data is received from the data link, the USART strips off the start and stop bits, checks the parity bit (if parity checking is enabled-see 2.2.6.1.3.4), and checks for framing errors (lack of a stop bit at the proper time). If an error is detected, a bit is set in the internal Status Register. The USART also checks to see that the previous character has been accepted by the MPU-if RXRDY is still high (has not been reset by the MPU having read the previous character), the overrun status bit is set.

2.2.6.1.3.2 Write Data. When the MPU wishes to send data to the USART, it addresses Port 0, places the data character on the bidirectional data bus, and develops -WRITE. This combination (CS, WR, and C/D all low) loads the character into the USART, which then adds the start, stop, and parity bits, and immediately begins to shift the character out, one bit at a time through the level converter IC to the data link.

There are two status bits pertaining to data transmission: TXE (Transmitter Empty) and TXRDY (Transmitter Ready). Both of these become reset when a character is loaded into the USART from the MPU. If a relatively long time has passed since the previous character was loaded, TXRDY sets again almost immediately. This allows a second character to be loaded, even though the first has not been fully shifted out. TXRDY again resets as the second character is loaded, but this time it remains reset until the first character is completely shifted out. Then it sets again, allowing another character to be loaded. When all data characters have been fully transmitted, TXE again sets.

2.2.6.1.3.3 Read Status. When the MPU wishes to know the status of the USART, it performs an input from Port 0 with +ADDR Ø high. This occurs after any interrupt, since the MPU needs to know if it is the USART that is interrupting, and before every data output to the USART, because the MPU must check to see that the USART is able to accept the data character.

When Port 0 is addressed, the -PORT Ø signal enables the USART by driving its CS input low, and +ADDR Ø drives the USART'S C/D input high, which directs the USART to transfer control/status information. -READ again directs the USART to output information onto the bidirectional data bus, but because the C/D input is high, the USART outputs status information instead of data.

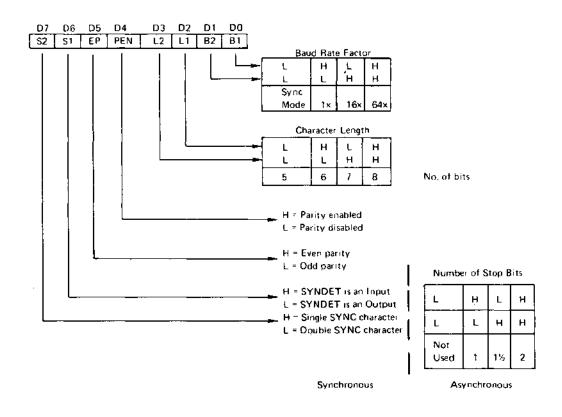

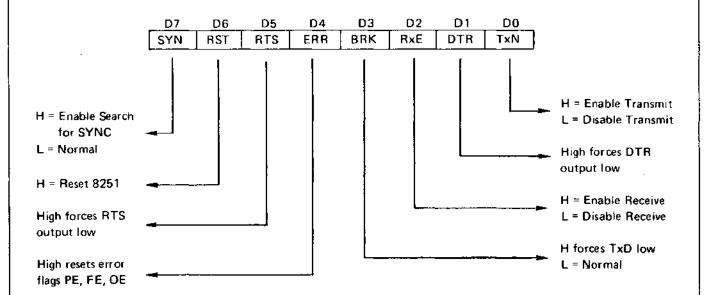

2.2.6.1.3.4 Write Control. A control write is used to program the USART for parity checking, byte length, number of stop bits, etc. When the MPU outputs control information for the USART, it addresses Port 0 while holding +ADDR # high. However, complete control of the USART requires more than 8 bits of information. The USART is designed to accept two different control bytes, a "Command" byte and a "Mode" byte. It accepts the Mode byte only as the first control instruction following a reset. All subsequent "control writes" are accepted as Command bytes. Each of the individual bits in the Command and Mode bytes is defined in the IC data for the 8251 in the Schematics/Reference section of this manual.

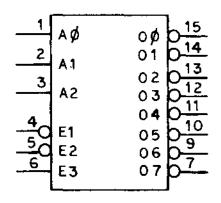

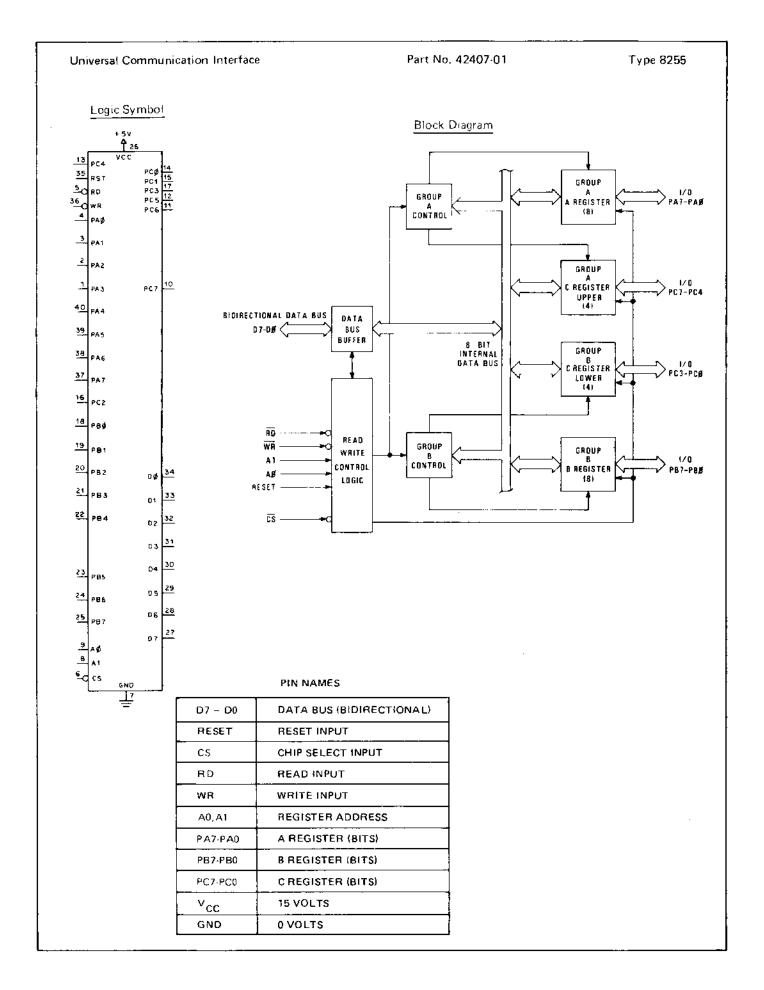

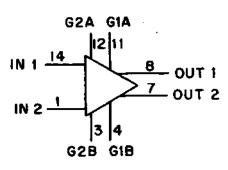

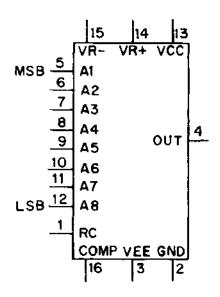

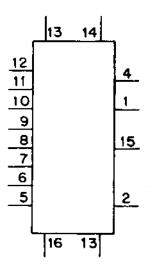

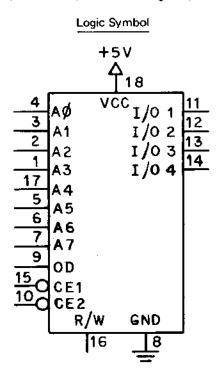

#### 2.2.6.2 I/O Port IC (8255)

The other two I/O ports on the HPRO3 board, Ports 1 and 2, utilize an 8255 Programmable Interface IC. This type of IC may also be used for ports located on the other circuit boards. This is a 40-pin IC having eight pins connected to the bidirectional data bus and three more sets of eight pins each that can interface to various "peripheral" devices. The balance of the pins are used for power supply connections and control signals.

The 8255 contains three 8-bit registers called A, B, and C, each of which can be used for either input or output. The C register can even be split into two 4-bit registers, each individually programmable for input or output, or for control and status signals.

There are three possible modes of operation, selected by a control word issued by the MPU. This control word is a part of the firmware microprogram stored in ROM, so it can be different for each 8255, and it can even change at different points in the execution of the program. (This control word can also be used to alter individual bits in Register C. while leaving the other seven bits unchanged.) The three possible modes are as follows:

Mode 0: Simple input or output for each register

Two 8-bit and two 4-bit registers

Outputs are latched Inputs are not latched

Mode 1: Strobed input or output for Registers A and B

Register C used as control/status for the other two registers

Inputs and outputs all latched

Mode 2: Strobed bidirectional bus (not used in HPRO3)

Each 8255 IC has the following connections to the terminal microprocessor:

DØ -D7: The bidirectional data bus, over which all data transfer occurs between

the MPU and the 8255.

CS: Chip Select Input. One of the decoded "port" signals is used to select only one 8255 at a time. Only -PORT 1 and -PORT 2 select 8255s on

the HPRO3 board. The other port signals may select 8255s on other

circuit boards.

A0&A1: ADDRESS # and ADDRESS 1 Inputs. The two low-order lines of the Memory Address Bus (ADDR # and ADDR 1) are used to select which of

the three registers is to be used, or to specify that a control word is

being sent out by the MPU.

| ADDR 1<br>(A1) | ADDR Ø<br>(AØ) |              |

|----------------|----------------|--------------|

| 0              | 0              | Register A   |

| 0              | 1              | Register B   |

| 1              | 0              | Register C   |

| 1              | 1              | Control Word |

When low, specifies a read (into the MPU) is RD: Read Input.

occurring. This is considered "input."

WR: Write Input. When low, specifies a write (from the MPU) is

occurring. This is considered "output."

Further details of the 8255 IC's operation can be found in the Schematics/Reference section.

2.2.6.2.1 Port 1 is enabled by the -PORT 1 signal. It is generally operated in Mode 0. The control word from the MPU programs the port for input through Register A and output through Registers B and C.

2.2.6.2.1.1 Status Inputs. The six bits of Register A that are used provide status to the MPU of the following:

| Bit 2 | EIA option 3              |

|-------|---------------------------|

| Bit 3 | EIA option 2              |

| Bit 4 | Carrier Detect            |

| Bit 5 | Clear to Stand            |

| Bit 6 | Keyboard Interrupt        |

| Bit 7 | Real-Time Clock Interrupt |

2.2.6.2.1.2 Baud Rate Counter. This counter produces a square wave at 1, 16, or 64 times the baud rate frequency. The USART clock frequency requirements vary according to the USART programming (the "mode" instruction) and the desired baud rate. The mode instruction determines whether this clock must be 1, 16, or 64 times the baud rate. (64 is generally used for baud rates below 1200.) A factor is loaded into Register B of the 8255 by the MPU, and the counter, driven by  $T\Phi 2$ , is counted up until it overflows. When this happens, the same factor is reloaded and the counting resumes. The overflow also toggles a D-type flip-flop, which further divides the count by 2 and makes the output symmetrical.

The USART clock can also be supplied by an external source via board pin 4, when the correct jumper wire is installed. Furthermore, during synchronous data transmission/reception, the USART's receive clock is provided by the modem. In this case, a jumper on the HPRO3 board must be changed to separate the transmit and receive clocks.

2.2.6.2.1.3 Interrupt Enable/Disable. Each of the four types of interrupts that can be generated on the HPRO3 board can be individually enabled or disabled. A "1" loaded into the C Register enables, while a "0" disables, as follows:

| Bit 4 | USART receive   |

|-------|-----------------|

| Bit 5 | USART send      |

| Bit 6 | Keyboard        |

| Bit 7 | Real-Time Clock |

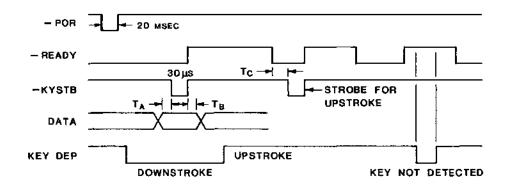

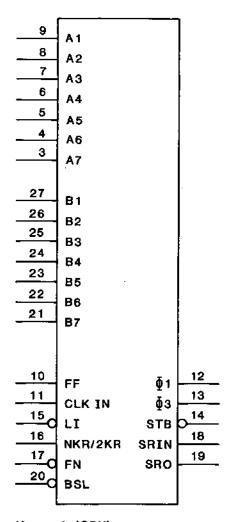

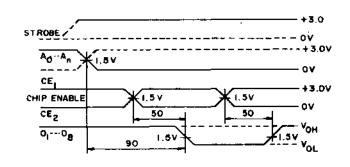

2.2.6.2.2 Port 2. Port 2 is selected by the -PORT 2 signal, and is generally operated in Mode 1. The control word from the MPU programs the port for input through Registers A and B. The Register C bits are used mostly for control/status in Mode 1, but two bits, PC6 and PC7, are still available for I/O, and in this port they are used for output.

2.2.6.2.2.1 Keyboard (Parallel) Input. This data, in the form of 8-bit parallel bytes on the -DATA# through -DATA7 lines, is continually applied to the Register A inputs. As long as the Register A strobe input, which is PC4 (pin 13) in the Mode I configuration, is low, this data is loaded into Register A. -KYSTB is normally high, so after it drops low and then goes high again, the KEYBOARD INTERRUPT flip-flop sets on the trailing (positive going) edge. As soon as this flop-flop sets, it latches the data into Register A; at this point the eight parallel inputs may be removed or changed without altering the data in the register.

When the KEYBOARD INTERRUPT flip-flop sets, it also presents an interrupt to the MPU (provided keyboard interrupts have been previously enabled). When the MPU recognizes the interrupt, part of its interrupt service routine is an instruction to read from Register A, to input the data to the MPU. Following this, it also performs a pair of "bit set/reset" instructions: the first to put a "low" on PC6 to clear the KEYBOARD INTERRUPT flip-flop; the second to put a "high" back on PC6 to enable the flip-flop to be set again by the next -KYSTB. The MPU also reads the function key status from Register B as part of this interrupt service routine.

Note that +BUSY is driven high when the KEYBOARD INTERRUPT flip-flop sets, and remains high until after the flip-flop is cleared and reenabled. This signal can be used by an 8-bit parallel input device as a ready/not ready indicator; when +BUSY is high, it indicates that -KYSTB signals will not be accepted. The 8-bit parallel input device should present -KYSTB only when +BUSY is low.

2.2.6.2.2.2 Function Key Status. The keyboard function key signals, as well as the status of the three options, are continually applied to Register B. In Mode 1, the Register B strobe is received on PC2 (pin 16). The +SYNC signal from the MPU thus latches the status of the function keys and jumper options into Register B.

These signals do not produce an interrupt. Instead, their status is read from Register B by the MPU each time it services an interrupt caused by -KYSTB.

2.2.6.2.2.3 Real-Time Clock One-Shot. The Real-Time Clock one-shot is controlled by the individual bit set/reset feature of the 8255. Bit 7 in the C Register (PC7, pin 10) is controlled by the MPU: when it goes high, the one-shot fires; when it goes low, the one-shot is enabled to fire again. PC7, when high, must first go low, then return to high to start the 10 ms timer.

#### 2.2.6.3 Off-Board I/O

Input from or output to logic circuits external to the HPRO3 board can be accomplished in either of two ways: programmed I/O or direct memory access. Programmed I/O can occur either through the mother board connector (P1) or the control panel connector (J2). DMA transfer can occur only through the mother board.

2.2.6.3.1 Programmed I/O. This is accomplished in the same manner used for onboard I/O. An I/O port, #3 through #6, is addressed, and -READ or -WRITE is developed. If necessary, +ADDR #6 and +ADDR 1 may be used to further define the address (as when an 8255 IC is used). All data is transferred between the MPU and the off-board port over the bidirectional data bus.

Port 3 must be accessed through the control panel connector. (-READ and -WRITE are passed through the drivers, and become -RD and -WR.) Ports 4,5, and 6 must be accessed through the mother board. Port 4 is generally reserved for DMA, and Ports 5 and 6 are generally used for the printer.

2.2.6.3.2 <u>Direct Memory Access.</u> Data can be transferred directly between memory and an external device following the procedure outlined in 2.2.5.5. In this case, data is transferred directly between memory and the external device over the bidirectional data bus; the MPU stops in a "Hold" condition while the transfer takes place.

# 2.2.7 Miscellaneous Circuitry

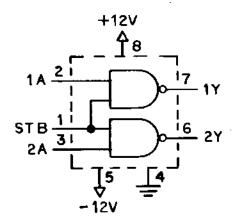

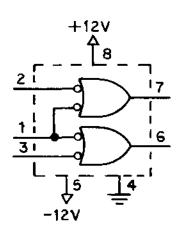

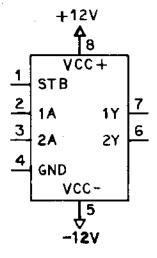

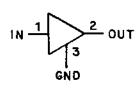

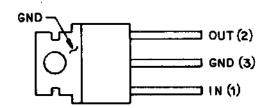

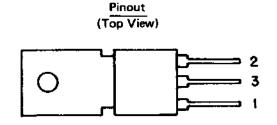

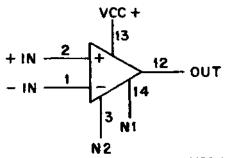

### 2.2.7.1 3-Terminal Voltage Regulators

There are three 3-terminal voltage regulator ICs, shown on sheet 1 of the HPRO3 logic drawing, that provide the source of -5V, -12V, and +12V. These voltages are derived from the  $\pm 15V$  provided by the power supply, which also provides +5V.

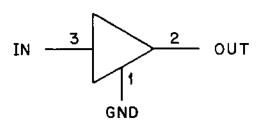

#### 2.2.7.2 Level Converters

The input and output voltage level converters provide the interface between the TTL inputs and outputs of the USART and the 12V (nominal) requirements of RS-232-C.

# 2.2.7.3 Options

There are four options on the HPRO3 board that provide variations in operation. These are covered in detail in the Product Description.

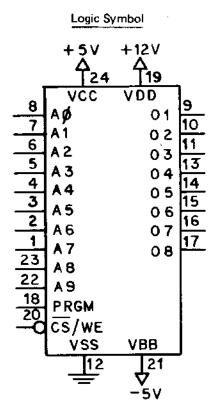

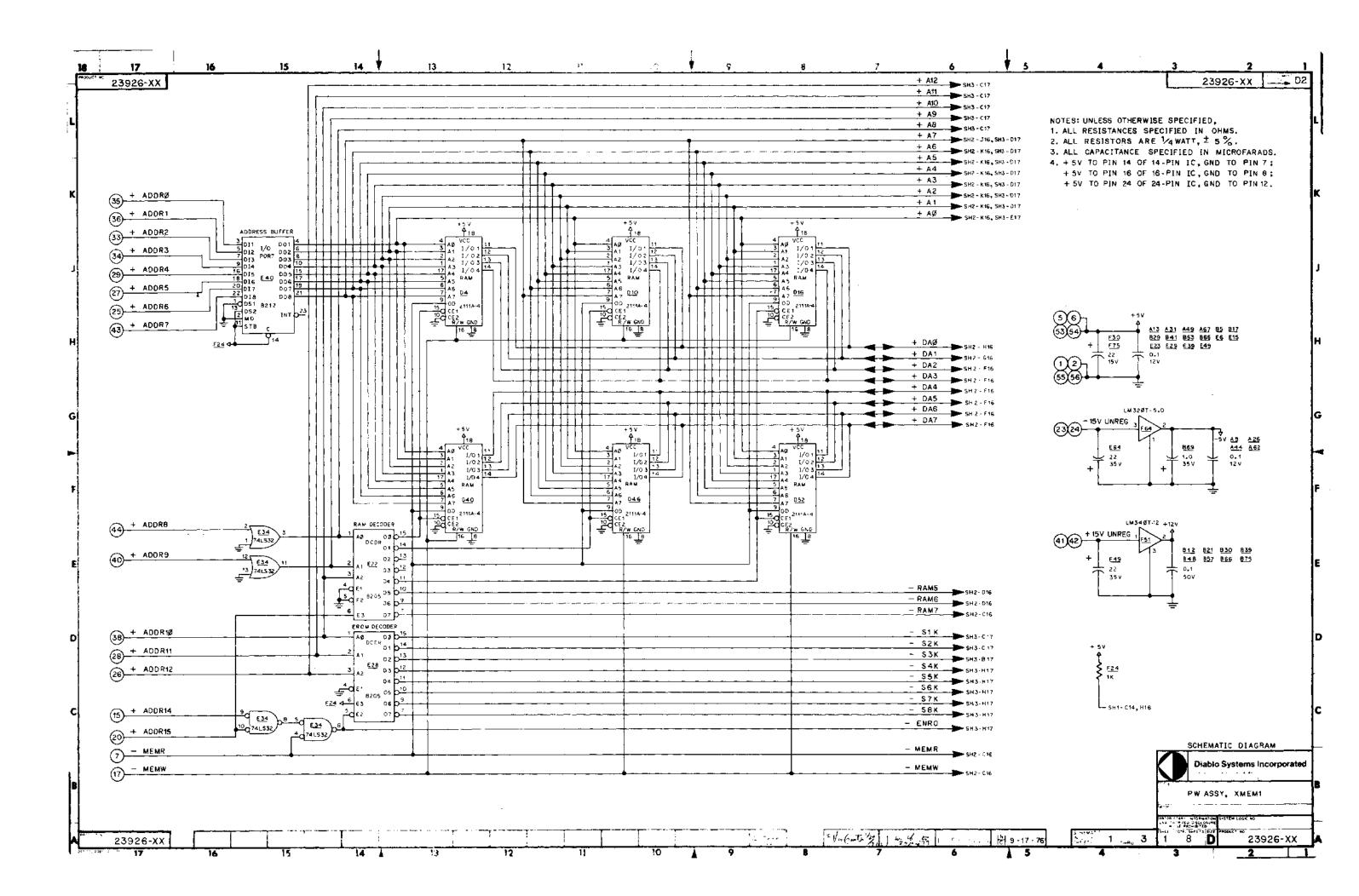

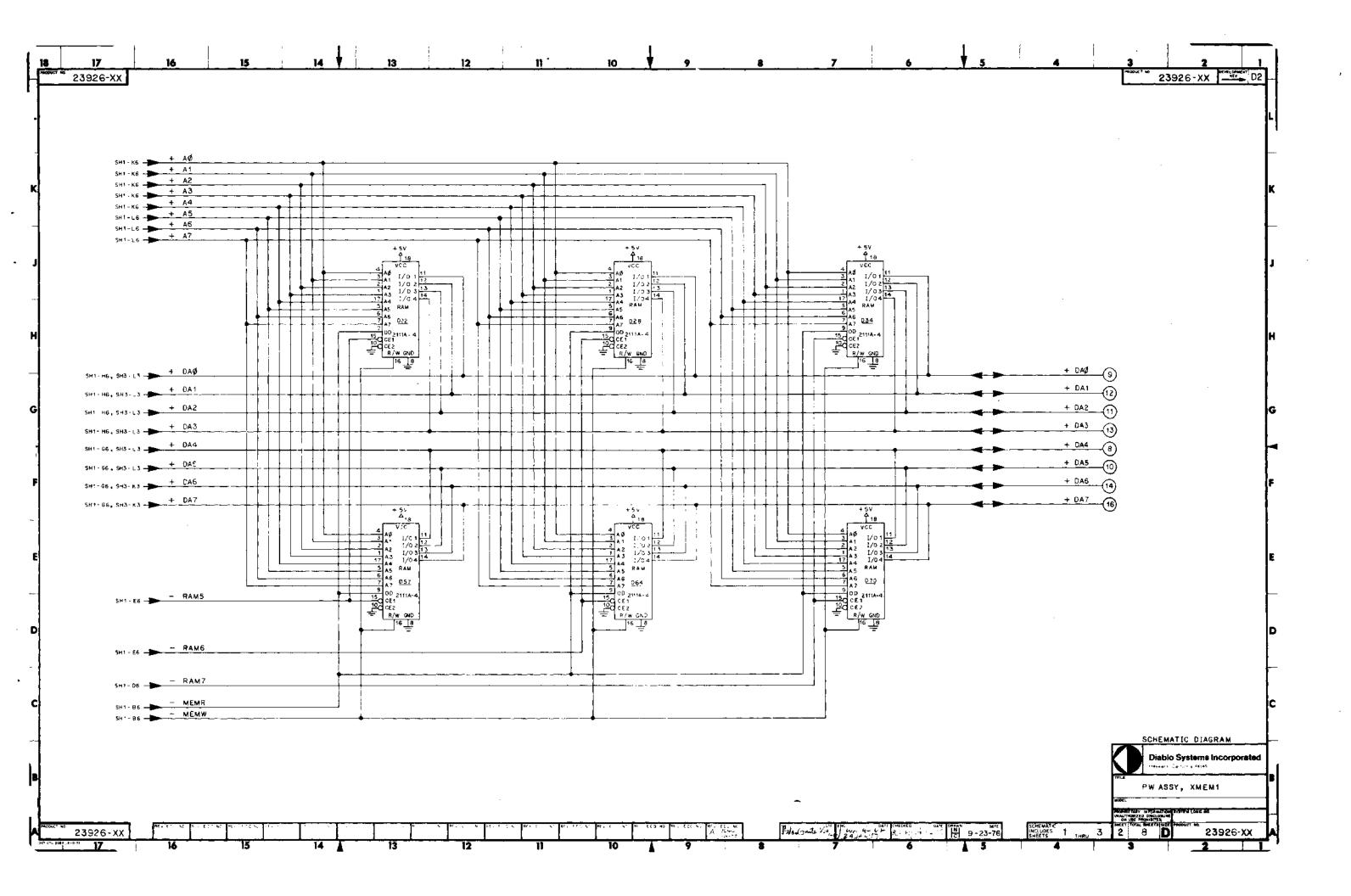

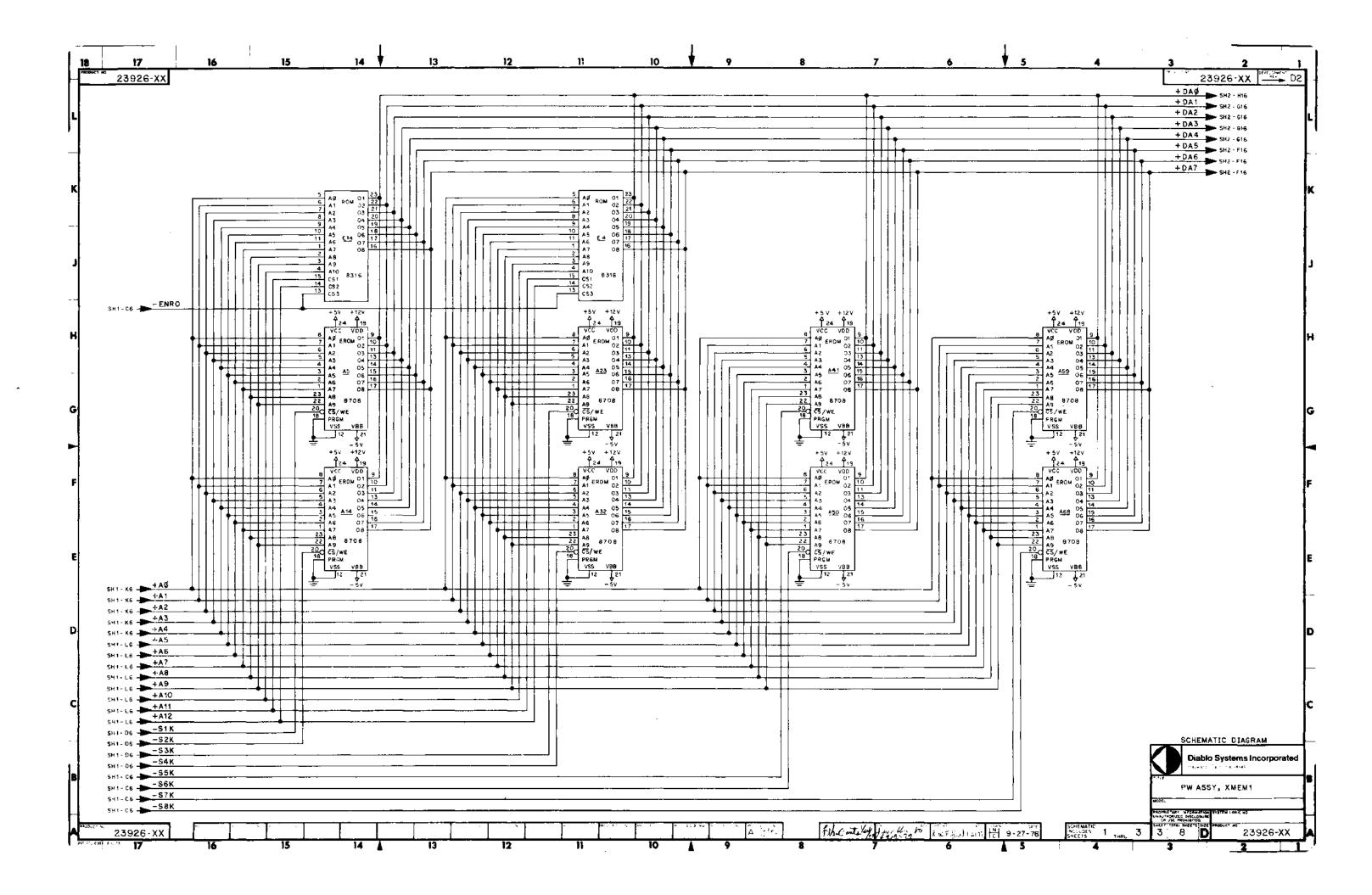

# 2.3 XMEM (EXTRA MEMORY) BOARD, PART NO. 23926-XX.

When the 4K bytes of ROM, 1K of EROM, and 512 bytes of RAM on the HPRO board are adequate for the programming application, the XMEM board is not supplied. When additional memory is required, the XMEM board is installed in slot F, directly behind the HPRO board; no connections other than plugging into the mother board are required. The XMEM1 board can contain up to 1.5K bytes of RAM, 4K of ROM, 8K of EROM, or a combination of memory types.

## 2.3.1 Applications

During program development, programs are stored on EROMs so they can be debugged, erased, and rewritten. When the program has been tested and validated, it is burned into the masked ROMs, which are installed on the HPRO board.

EROMs on the XMEM board are used to store development programs. Because of the time involved in manufacturing masked ROMs, early production terminals are often shipped with programs on EROMs on the XMEM board instead of on masked ROMs on the HPRO board. Also, when a program is larger than 4K bytes, additional memory chips, either ROMs or EROMs, are installed on the XMEM board to store part of the program. ROMs and EROMs on the XMEM board are addressed in the same manner as ROMs and EROMs located on the HPRO board. For applications requiring more than 512 bytes of working read/write memory, up to 1.5K bytes of RAM can be installed on the XMEM board.

### 2.3.2 Basic XMEM Board

The basic XMEM board (dwg. no. 23926-XX) contains an address buffer, address decoders, and voltage regulators. IC memory chips of the required type and number are added to suit a specific application.

# 2.3.3 XMEM Configurations

The XMEM can have the following numbers of memory chips installed:

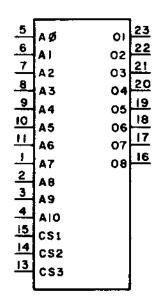

12 Type 2111A-4, 256 x 4-bit RAMs 2 Type 8316A, 2K x 8bit masked ROMs 8 Type 8708, 1K x 8bit EROMs

While it is possible to have all these memories installed (physically) on the same XMEM board, is is logically impractical, because both ROMs and EROMs use the same addresses, and two EROMs must be eliminated for each ROM installed. There is no address interference between RAMs and ROMs or EROMs, so a full complement of RAMs can be installed regardless of the number of ROMs and/or EROMs installed.

### 2.3.4 Addressing

Figure 2-6 shows the memory addressing scheme used by the MPU to access the entire memory, both on the HPRO board and on the XMEM board. Note that HPRO ROMs #1 and #2, and XMEM ROMs #3 and #4 use the same address areas as the EROMs on the XMEM board, so the EROMs can not be used when the masked ROMs are installed. This is done intentionally, so that a program can be written electrically into EROMs, tested and corrected as often as necessary, and when approved, the program can be used to generate masked ROMs without need for address modification. When masked ROMs are in production, the EROMs can be eliminated, and, if the program is less than 4K, the two ROMs containing the program can be installed on the HPRO board. If there is no need for the additional RAM storage, the XMEM board can be eliminated. If the program is larger than 4K, two additional ROMs can be installed on the XMEM board, along with as many RAMs as are required.

ROMs and EROMs can be mixed, as long as there is no direct address conflict. For example it would be possible to use EROMs 5, 6, 7, and 8 with HPRO ROMs 1 and 2, but these EROMs could not be used with XMEM ROMs 3 and 4. Since RAMs use an entirely different address area, their use is independent of ROM/EROM configuration.

# 2.3.5 Additional Applications

- o EROMs can be used in terminals produced in quantities too small to justify the expense of preparing masked ROMs.

- o A mixture of ROMs and EROMs can be used in applications requiring special programs.

- o RAMs can provide additional working memory.

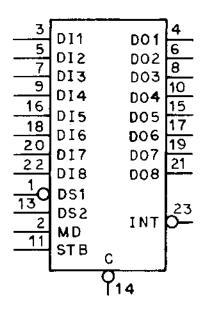

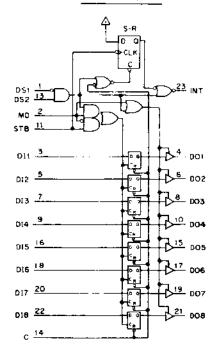

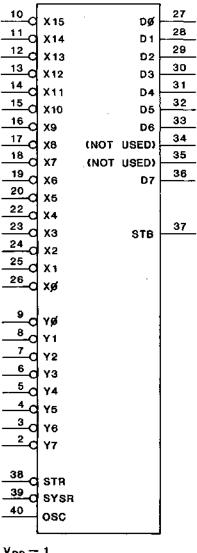

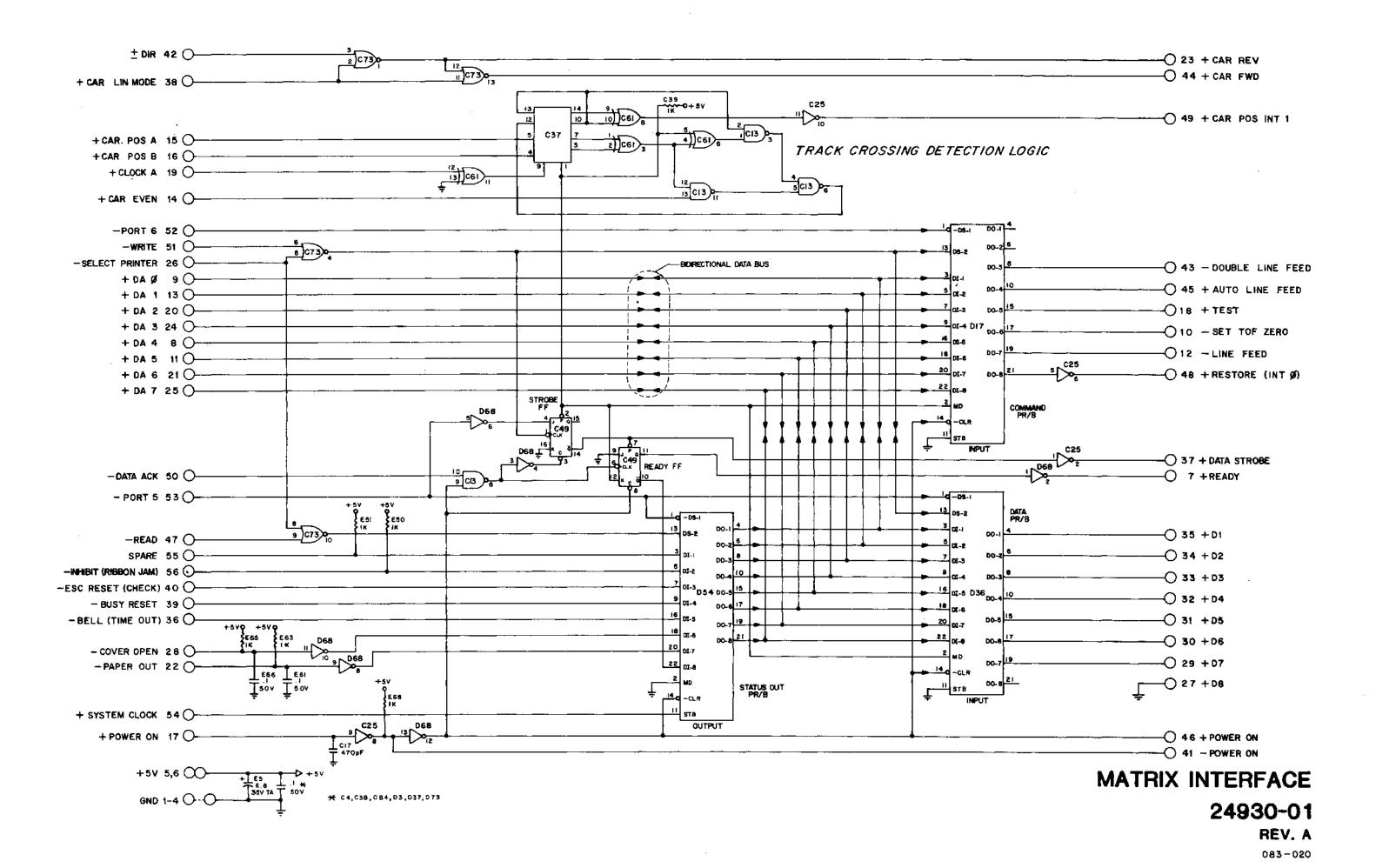

### 2.4 MATRIX INTERFACE BOARD, PART NO. 25930-XX

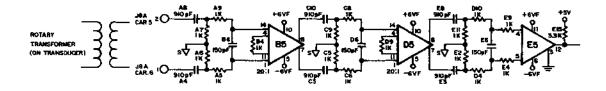

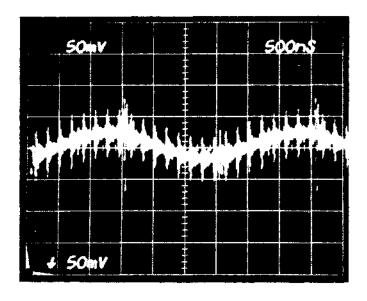

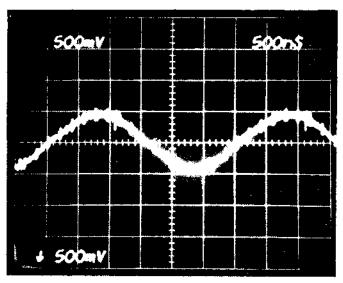

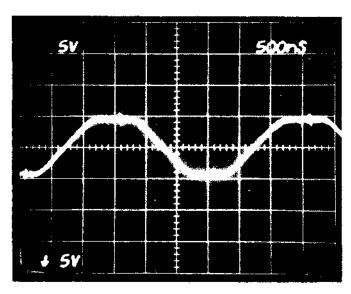

The MATRIX INTERFACE (MXI) board contains I/O Ports 5 and 6, which transfer data, control signals, and Status information between the terminal processor and the printer processor. Also contained on the MXI board is the logic for receiving and temporary storage of carriage position feedback signals from the CARRIAGE SERVO board enroute to the printer processor. Carriage directional commands are also produced on the MXI board from the data received from the printer processor. These signals are applied to the servo motor driver FETs on the CARRIAGE SERVO board. A block diagram of the MXI board is shown in Figure 2-8.

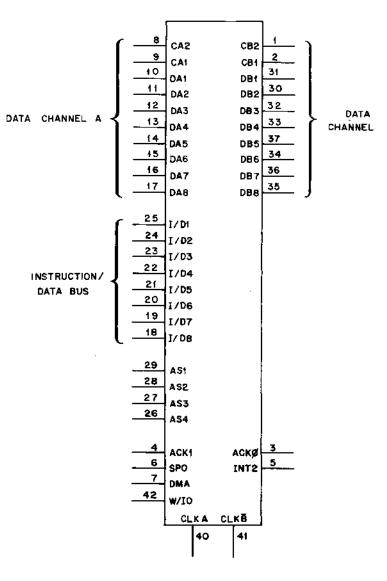

# 2.4.1 I/O Ports 5 and 6

I/O ports 5 and 6 are used to synchronize the transfer of information between the two processors. When the terminal processor performs an output instruction to Port 5 or 6, the output information is stored on the MXI board where it is available to the printer microprocessor. The printer microprocessor periodically "reads" the MXI board to see if there is any information that it should process. Similarly, as the printer microprocessor goes though its steps of controlling the printer operations, it provides status information to the MXI board. This status information is monitored by the terminal microprocessor prior to each output command.

#### 2.4.1.1 Transferring Information to the Printer Processor.

The prerequisites to actual transfer of data include the +POWER ON and -SELECT PRINTER signals. The +POWER ON signal energizes the 8212 ICs and is inverted to provide a -POWER ON signal. Both +POWER ON and -POWER ON are outputs to the printer processor. The -SELECT PRINTER signal will enable the transfer of information between the two processors.

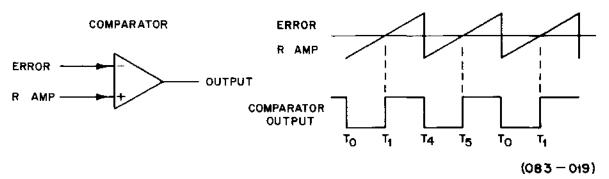

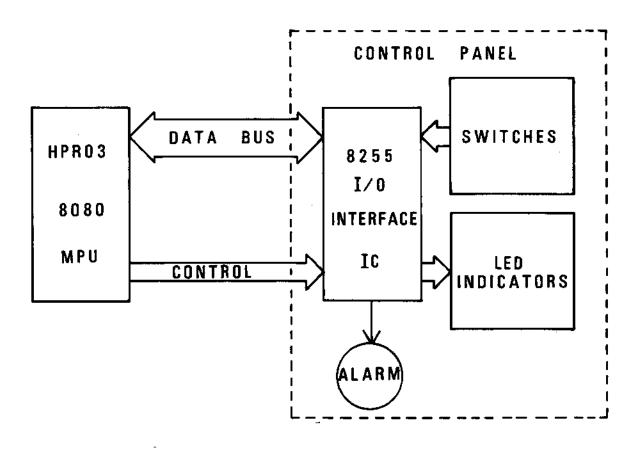

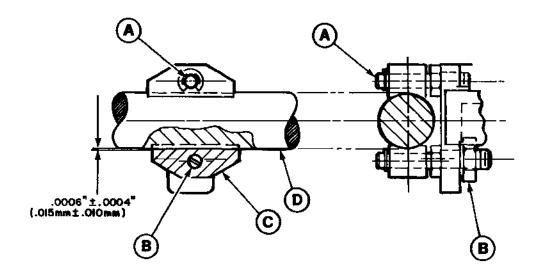

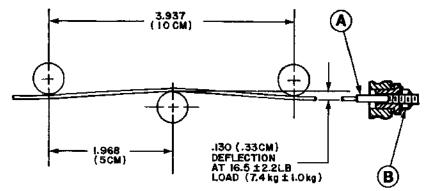

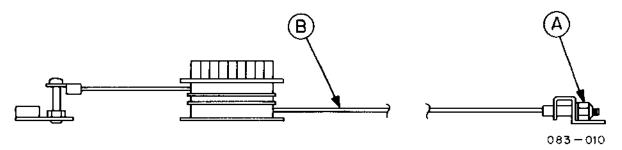

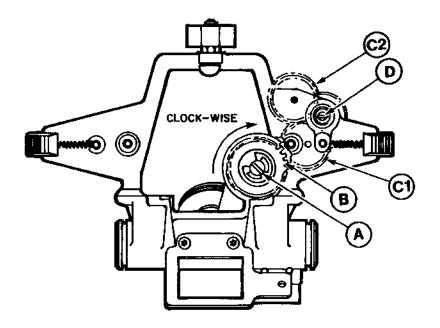

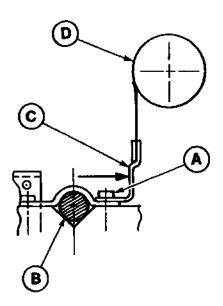

\*WRITE TO PORT 6: When -WRITE and -PORT 6 signals develop, the control information on the data bus is transferred to the printer microprocessor via the Port 6 latches. This data is output directly onto control lines to the printer and includes the following control signals: -DOUBLE LINE FEED, +AUTO LINE FEED, +TEST, -SET TOF ZERO, and +RESTORE (INT 6).