# SA1401 Controller PROMS WS30

Preliminary OEM Manual

**Shugart**

# TABLE OF CONTENTS

- 1.0 Introduction

- 2.0 SA1401 Controller

- 2.1 Features

- 2.2 System Configuration

- 2.3 Theory of Operation

- 3.0 Host Bus

- 3.1 Signal Definitions

- 3.2 Theory of Operation

- 4.0 Commands/Programming

- 4.1 Command Format

- 4.2 Status Format

- 4.3 Logical Address

- 4.4 Error Code Descriptions

- 5.0 Electrical/Mechanical Specifications

- 6.0 Diagnostic Philosophy

- 6.1 Error Indicators

- 6.2 Additional Microdiagnostics (Optional)

- 7.0 Sector Format

- 8.0 Host I/O Connector Pin Assignment

APPENDIX A Switch Setup Procedure

#### 1.0 INTRODUCTION

The SA1401 Controller consists of a microprocessor-based controller with on-board data separator logic, and is able to control a maximum of two Shugart SA1000 fixed disk drives. The SA1401 can be mounted on the SA1000 drive.

Commands are issued to the controller over a bidirectional bus connected to the host computer. The data separator/"serdes" logic serializes bytes and converts to MFM data, and deserializes MFM data into 8-bit bytes.

Due to the microprogrammed approach utilized in the controller, extensive diagnostic capabilities are implemented. This methodology increases fault isolation efficiency and reduces system down time. Error detection and correction will tolerate media imperfections up to 4-bit burst errors.

#### 2.0 SA1401 Controller

#### 2.1 Features

2.1.1 The capabilities supplied as standard with the SA1401 are listed below:

OVERLAPPED SEEK

In multiple drive configurations, the host can issue seeks to different drives without waiting for the first drive to complete its seek.

AUTOMATIC SEEK AND VERIFY A seek command is implied in every data transfer command (READ, WRITE, CHECK, etc.). If the heads are not positioned over the correct cylinder, a seek is initiated, and a cylinder verification is performed after the seek completes.

FAULT DETECTION

Two classes of faults are flagged to improve error handling:

- \* Controller faults

- \* Disk faults

AUTOMATIC HEAD AND CYLINDER SWITCHING If during a multi-block data transfer the end of a track is reached, the controller automatically switches to the next track. If the end of a cylinder is reached, the controller issues a seek and resumes the transfer.

DATA ERROR SENSING AND CORRECTION If a data error is detected during a disk data transfer, the controller indicates whether or not it is correctable. If correctable, either a pointer and mask can be requested by the host for applying the correction or the error can be automatically corrected.

LOGICAL TO PHYSICAL DRIVE CORRELATION Logical unit numbers (LUN's) are independent of physical port numbers. All accesses specify LUN's.

ON BOARD SECTOR BUFFER A sector buffer is provided on the controller to eliminate the possibility of data overruns during a data transfer.

EFFICIENT HOST INTERFACE PROTOCOL A bidirectional bus between the controller and host provides a simple yet efficient communication path. In addition, a high level command set permits effective command initiation.

SECTOR INTERLEAVE Sector interleaving is programmable with up to 16 way interleave.

ODD PARITY

The 8 data bits on the interface bus can have odd parity. Depending on user preference, parity can be disabled.

FIXED SECTOR SIZE

The sector size is fixed at 256 bytes of data.

NUMBER OF DRIVES The controller will connect to a maximum of two (2) SA1000 drives.

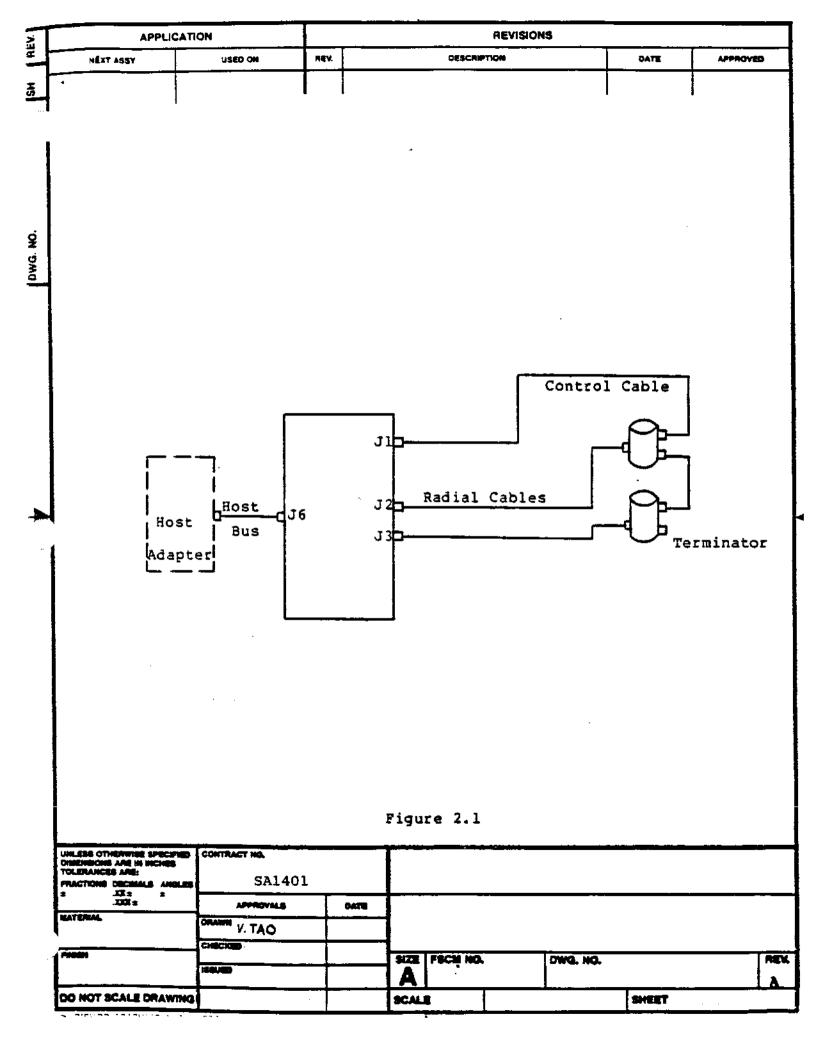

## 2.2 System Configuration

The controller and data separator comprise a single PCB that can be mounted onto the SA1000 drive. A maximum of two (2) drives may be connected as shown in Fig. 2.1.

#### 2.3 Theory of Operation

Disk commands are issued to the SA1401 via the host bus following a defined protocol. The host initiates a command sequence by selecting the controller on the bus. If the controller is not busy, it requests command bytes from the host for task execution. (Command structure is described in Section 4.0). Depending on the type of command, the controller will request up to 10 bytes. Upon reception of the last command byte, the controller begins execution of the command.

For the data transfer commands, a check is performed on the disk address and status flagged if it exceeds the drive limits. The data is stored in a sector buffer before transfer to the host or disk drive. This buffer eliminates any possibility of data overruns between the host and the disk.

Upon completion of the command, the controller will send completion status to the host. (Further delineation of the completion status may be requested by issuing the appropriate sense commands.)

Odd parity is generated by the SA1401 for all information that it puts on the I/O bus. If enabled, the SA1401 flags all information that it receives with bad parity.

#### 2.3.1 Electrical Interface

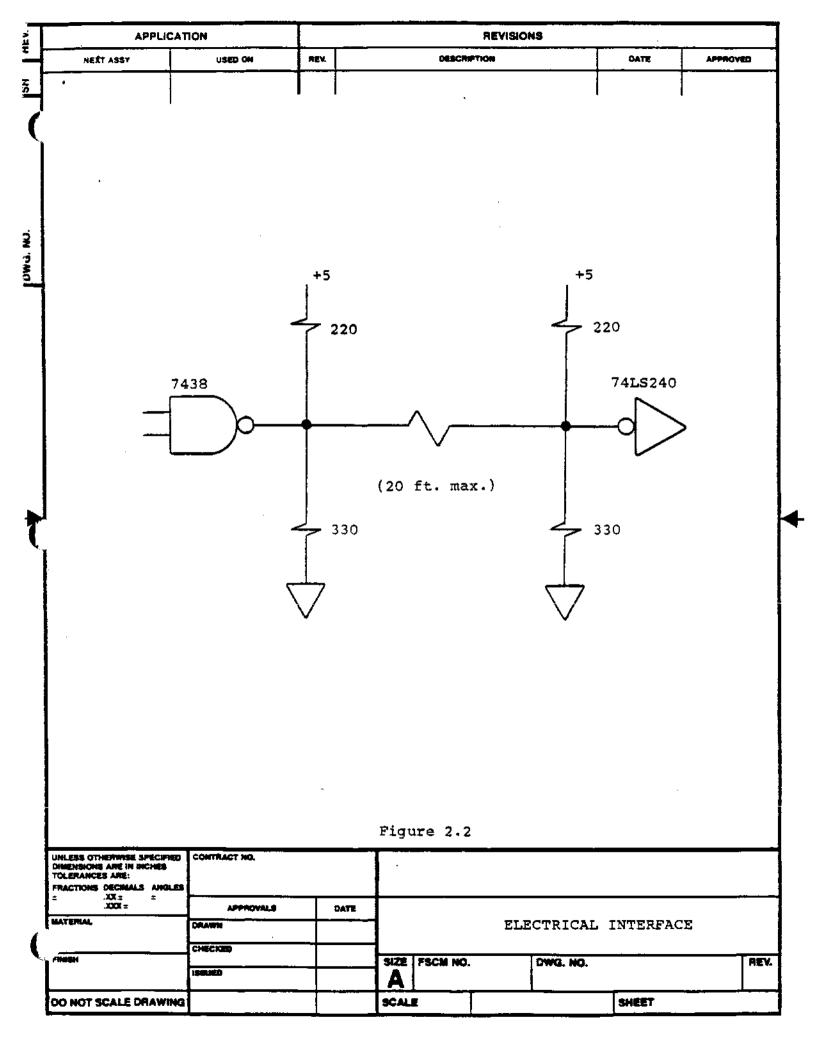

The electrical interface to the SA1000 will conform to the requirements described in the SA1000 interface specification. The electrical interface to the SA1401 Host Bus is shown in Fig. 2.2.

#### 3.0 SA1401 HOST BUS

The SA1401 Host Bus is as a negative-logic, bidirectional 8-bit data bus utilizing odd parity. The electrical interface consists of an open collector bus terminated on each end by a 220/300 ohm resistor network. The controller regulates transfers across the bus which eliminates data overruns that could occur during data transfers.

The term "asserted" means that the signal on the host bus is between 0V and 0.8V. The term "deasserted" means that the signal on the host bus is between 2.5V and 3.5V (Negative or Low True logic).

# 3.1 Signal Definition

# 3.1.1 Unidirectonal Signals Driven By Controller

- I/O Input/Output

When asserted, the data on the bus

is driven by the controller. When

deasserted, the data on the bus is

driven by the host adaptor. The

host adaptor will use this line to

enable its drivers onto the data bus.

- C/D Command/Data

When asserted, the data transmitted across the bus will be the command bytes. When deasserted, the data will be the disk data bytes.

- BUSY This bit is asserted as a response to the SEL line from the host adapter and to indicate that the host bus is currently in use.

- MSG Message

When asserted, indicates that the command is completed. This bit is always followed with the assertion of I/O, and the assertion of REQ.

- REQ Request

This bit operates in conjunction with I/O, C/D, & MSG. When asserted and I/O is asserted, REQ will mean that the data on the host bus is driven by the controller. When asserted and I/O is deasserted, REQ will mean that the data is driven by the host adaptor (H/A).

| 1/0 | C/D    | MSG    | Meaning                                   |

|-----|--------|--------|-------------------------------------------|

| đ   | a<br>đ | ₫<br>₫ | Get command from H/A<br>Get data from H/A |

| a   | đ      | đ      | Send data to H/A                          |

| a   | a      | đ      | Send status byte to H/A                   |

| a   | a      | a      | Command done to H/A                       |

a = asserted, d = deasserted

#### 3.1.2 Unidirectional Signals Driven By Host Adaptor

# ACK Acknowledge

This bit is asserted as a response to REQ from the controller. The timing requirements on this signal with respect to the data is described in REQuest section. ACK must be returned for each REQ assertion. Once REQ has been asserted, the controller waits 256us for ACK return before timing out.

# RST Reset

When asserted, this bit forces the controller to the beginning of its microcode. Any error status request will result in invalid information after RST has been asserted. All signals to the drives are deasserted. RST must be asserted for a minimum of 250ns and a maximum of 10us.

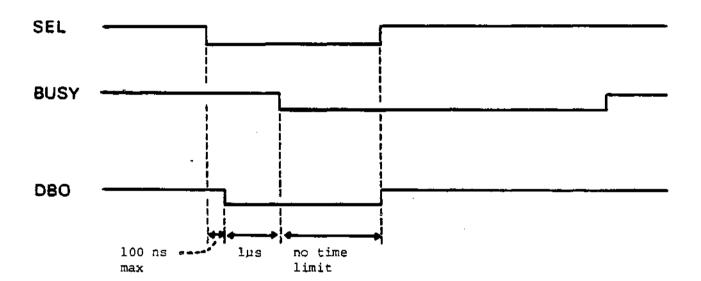

#### SEL Select

When asserted, indicates the beginning of the command transaction. The H/A asserts SEL to gain the attention of the controller. A data bit on the host host bus must also be asserted during SEL time to determine which controller is selected. SEL must not be asserted on the host bus before the data bit. The controller will return BUSY within lus. After the assertion of BUSY, the H/A will deassert SEL within 500ns.

#### 3.1.3 Bidirectional Data

DB(7-0,P) - Data lines 7 thru 0 represent the eight data bits (DB0=1sb). Parity is represented by P. The controller utilizes odd parity (the number of asserted bits on the host bus is always odd).

#### 3.2 Theory of Operation

Whenever the host adaptor has a command for the controller, it performs a selection sequence to gain the attention of the controller. The sequence is as follows:

The host adaptor asserts SEL and DBO (controller address bit) on the host bus. It then waits for the controller to respond with BUSY. Upon reception of BUSY, the H/A deasserts SEL. The controller now has control of the host bus.

After the controller asserts BUSY, it then asserts C/D (to indicate command mode transfer), and deasserts I/O (to indicate output from the host adaptor) to fetch the command bytes from the H/A. The command bytes are transferred over the host bus with the REQ/ACK handshake protocol until all command bytes are transferred to the controller. (The command byte fetch mode ends after the last REQ pulse from the controller is deasserted.)

For data transfer, the controller deasserts the C/D line to indicate data mode. Depending on the command type (read/write disk), the I/O bit on the host bus is asserted or deasserted by the controller, and the data is transferred (one byte at a time) with the same REQ/ACK handshake protocol. After all the data bytes have been transferred, a completion status is placed on the data bus by the controller - C/D and I/O are asserted. REQ is asserted and the controller waits for ACK from the host adaptor. After the status byte transfer, the controller places zeros on the data bus and asserts C/D, I/O and MSG along with REQ to indicate to the host that the command is complete (this action can be used to generate an interrupt on the host system). After the H/A responds with ACK, the controller deasserts REQ, BUSY and all other lines. This completes the command execution and the controller is now ready to be selected for the next command.

# 3.2.1

# TIMING REQUIREMENTS FOR CONTROLLER SELECTION

Note: SEL must be deasserted before the controller will assert REQ.

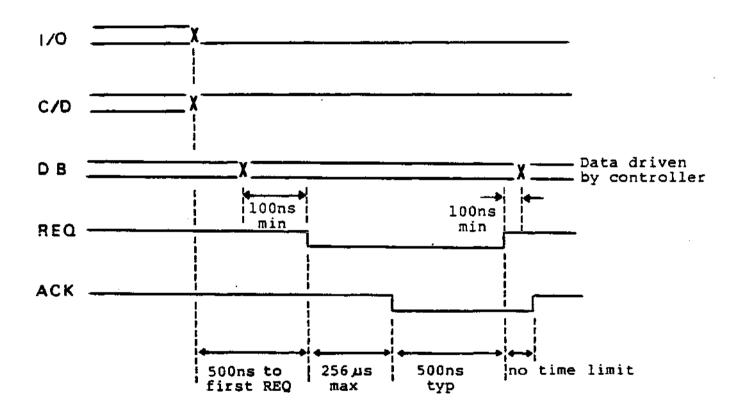

# TIMING REQUIREMENTS FOR DATA TRANSFER

(to host adapter - typical byte)

- Note 1: For Status Byte Transfer (I/O, C/D asserted and MSG deasserted); or Interrupt Byte Transfer (MSG, I/O, C/D asserted), REQ is asserted 500ns (typical) after the assertion of any of the above bits.

- 2: Data driven by the controller is stable 100ns min at the host adapter end before REQ is asserted, and 100ns min after REQ is deasserted.

# 3.2.3

# TIMING REQUIREMENTS FOR DATA TRANSFER

(from host adapter - one byte)

- Note I: Data driven by the host adapter is stable 50ns max at the host adapter end after ACK is asserted, and 50ns min after REQ is deasserted.

- 2: For command mode transfers, SEL must be deasserted before ACK is asserted. This sequence follows the selection protocol.

#### 4.0 COMMANDS

An I/O request to a disk drive is performed by passing a command descriptor block (CDB) to the controller. The first byte of a CDB is the command class and opcode. The remaining bytes specify the drive logical unit number (LUN), block address, control bytes, number of blocks to transfer or the destination device ID. The controller performs an implied seek and verify when required to access a block.

Commands are categorized into three classes as indicated:

Class 0 - Non-data Transfer, Data Transfer and Status

Commands

Class 1 - Disk Copy Commands

Class 2-6 - Reserved

Class 7 - Diagnostic Commands

The command descriptor blocks in Command Class 0 and 7 are 6 bytes long. and those in Class 1 are 10 bytes long.

# Command Description (Class 0)

| Opcode | Description |

|--------|-------------|

| (Hex)  | _           |

- OO Test drive ready. Selects the drive and verifies drive ready.

- Ol Recalibrate. Positions the R/W arm to Track00, clears possible error status in the drive.

- O2 Request Syndrome. Returns the offset and syndrome for data field error correction. The two bytes are as follows:

| M.S. BIT OFFSET (8) |              |

|---------------------|--------------|

| L.S. BIT OFFSET (3) | SYNDROME (4) |

The bit offset is relative from the first data bit, i.e., Bit 7 of Byte 0.

- Request Sense. This command must be issued immediately after an error. It returns 4 bytes of drive and controller sense for the specified LUN (see copy block for exception).

- O4 Format Drive. Formats all blocks with ID field according to interleave factor and data fields. The data field contains E5 Hex.

- O5 Check Track Format. Checks format on the specified track for correct ID and interleave. Does not read the data field.

- Of Format Track. Formats the specified track with bad block flag cleared in all blocks of that track. Writes E5 Hex in the data fields.

- 07 Format Bad Track (bad block flag). Formats the specified track with bad block flag set in the ID fields. Writes E5 Hex in the data fields.

- OR Read. Reads the specified number of blocks starting from initial block address given in the CDB.

- OA Write. Writes the specified number of blocks starting from initial block address given in the CDB.

- OB Seek. Initiates seek to specified block and immediately returns completion status before the seek is complete for those drives capable of overlap seek.

# Command Description (Class7)

| Opcode<br>(Hex) | Description                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 00              | RAM Diagnostic. Performs a data pattern test on the RAM buffer.                                                                                  |

| 01              | Write ECC. Displaces data on the disk by three bytes so that the ECC bytes can be written from the data specified. Used to verify the ECC logic. |

| 02              | Read ID. Transfers the cylinder, head, sector and 3 ECC bytes for the specified block ID field.                                                  |

| 03              | Drive Diagnostic 0. Performs a drive diagnostic. Reads<br>Sector 0 on all cylinders sequentially. Reads Sector 0 on<br>256 random cylinders.     |

#### 4.1 Command Format

# 4.1.1 Class 0 & 7 Commands

| Byte | 7   6   5   4   3   2   1   0 |

|------|-------------------------------|

| 0    | 0 or 7   opcode               |

| 1    | LUN   logical adr2**          |

| 2    | logical adrl**                |

| 3    | logical adr0**                |

| 4    | number of blocks*             |

| 5    | control field                 |

|      | **                            |

<sup>\*</sup>Interleave factor for Format, Check Track, and Read ID commands. \*\*Refer to section 4.3 Logical Address.

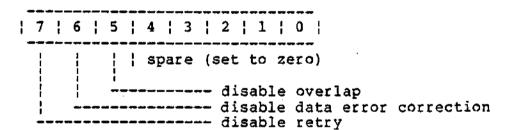

The control field is defined as follows:

# Commands in this group

- a) NOP

- b) Format Drive

- c) Check Format

- d) Request Sense

- e) Request Syndrome

- f) Recalibrate

- g) Read Block(s)

- h) Read ID

- i) Write Block(s)

- j) Format Track

- k) Format Track (bad track flag)

- 1) Seek

- m) Ram Diagnostic

- n) Drive Diagnostic

- o) Write ECC

# 4.1.2 Class 1 Commands

| Byte | 7   6   5   4   3   2   1   0 |

|------|-------------------------------|

| 0    | 0 0 1   opcode                |

| 1    | LUN/s   logical adr2/s*       |

| 2    | logical adrl/s*               |

| 3    | logical adr0/s*               |

| 4    | number of blocks              |

| 5    | LUN/d   logical adr2/d*       |

| 6    | logical adrl/d*               |

| 7    | logical adr0/d*               |

| 8    | spare !                       |

| 9    | control                       |

|      |                               |

"s" = the source device, "d" = the destination device

\*Refer to section 4.3 Lógical Address

Commands in this group: Copy Block

# 4.2 Status Format

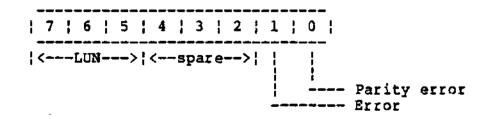

# 4.2.1 Completion Status Byte

Parity error occurred during transfer from host to controller.

Bit 1 Error occurred during command execution. Bit 2-4 Spare (set to zero). Bit 5-7 Logical unit number of the drive.

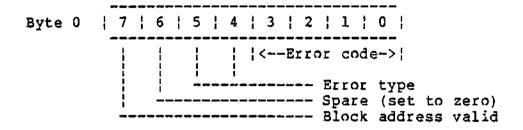

# 4.2.2 Drive and Controller Sense Bytes

The following bytes are returned from the controller for the Request Sense Command.

| Byte | ! | 7 | <br>: | 6  | ļ            | <br>5 |               | 4   |    | 3       |     | 2      |   | 1   | !  | 0 | -<br>!     |

|------|---|---|-------|----|--------------|-------|---------------|-----|----|---------|-----|--------|---|-----|----|---|------------|

| 1    | 1 |   | L     | JN | - <u>-</u> - |       | <del></del> - |     | 10 | <br>og: | ica | <br>⊋l | a | ir: | 2* |   | -<br> <br> |

| 2    |   |   |       |    |              | 10    | g:            | ica | 11 | ad      | ir. | 1*     |   |     |    |   | -          |

| 3    | - |   |       |    |              | 10    | g.            | ica | 11 | ac      | ir  | )*     |   |     |    |   | 1          |

|      | - |   |       |    |              | ~~.   |               |     |    |         |     |        |   |     |    |   | -          |

<sup>\*\*</sup>Refer to section 4.3

# 4.3 Logical Address

The logical address is computed as follows:

Logical adr = (CYADR \* HDCYL + HDADR) \* SETRK + SEADR

Where: CYADR = cylinder adress

HDADR = head address SEADR = sector address

HDCY = number of heads per cylinder SETRK = number of sectors per track

Bit 0 of Logical adr0 = the least significant bit. Bit 4 of Logical adr2 = the most significant bit.

- 4.4 Error Code Descriptions

- 4.4.1 Sense Command Results

# Type 0 (Drive) Error codes.

- 0 No status

- 1 No Index signal

- 2 No Seek Complete

- 3 Write fault

- 4 Drive not ready

- 5 Drive not selected

- 6 No Track00

- 7 Multiple Drives selected

# Type 1 (Controller) Error codes.

- O ID read error. ECC error in the ID field.

- 1 Uncorrectable data error during a read.

- 2 ID Address Mark not found.

- 3 Data Address Mark not found.

- 4 Record not found. Found correct cylinder and head but not

- 5 Seek error. R/W head positioned on a wrong cylinder and/or selected a wrong head.

- 6 (Not used).

- 7 (Not applicable).

- 8 Correctable data field error.

- 9 Bad block found.

- A Format Error. The controller detected that during the Check Track command, the format on the drive was not expected.

# Type 2 (Command) Error codes.

- O Invalid Command received from the host.

- Illegal disk address. Address is beyond the maximum address.

# Type 3 (Misc) Error codes.

O RAM error. Data error detected during Sector buffer RAM diagnostic.

#### 5.0 ELECTRICAL/MECHANICAL SPECIFICATIONS

# Physical Parameters

| Width  | 8.5  | inches |

|--------|------|--------|

| Length | 13.5 | inches |

| Height | 0.49 | inches |

| Weight | 1.12 | lbs.   |

# Environmental Parameters

|                                                                     | Operating:               | Storage:                 |

|---------------------------------------------------------------------|--------------------------|--------------------------|

| Temperatureegree (degrees F/C)                                      | 32/0 to 131/55           | -40/-10 to 167/75        |

| Relative Humidity (@ 40 degrees F, wet bulb temp., no condensation) | 10% to 95%               | 10% to 95%               |

| Altitude                                                            | sea level to<br>10K feet | sea level to<br>15K feet |

# Power Requirement

| Voltage @ current | +5  | VDC   | Ġ.       | 4.6A   | (max) |

|-------------------|-----|-------|----------|--------|-------|

| -                 | -5  | VDÇ   | <u>a</u> | 500 mA | (max) |

|                   | +24 | VDC - | æ        | 100 mA | (max) |

#### 6.0 DIAGNOSTIC PHILOSOPHY

## 6.1 Error Indicators

The controller contains 8 diagnostic LED error indicators. Each time an error occurs the controller deposits a value in the LED's and returns a failure status to the host adaptor. The LED value can be decoded, but the error it indicates will always be available to the host software. The errors that are returned by the controller are very detailed. As a result, preliminary fault isolation is made fairly easily, narrowing the failure to the particular interface portion of the controller. In addition, two diagnostic commands can be invoked via the host software interface. One is the RAM Diagnostic Command, and the other is the Drive Diagnostic Command.

#### 6.2 Additional Microdiagnostics (Optional)

The controller can be further checked out off-line by initiating explicit microdiagnostic routines via optional firmware diagnostic sets. The routines are initiated by a set of control switches. Errors will be displayed in a set of LED's. Each microdiagnostic checks the functionality of a particular section of the controller and is able to isolate failures in the following major categories:

ALU Registers Sector Buffer ECC Logic

Fault-isolation techniques can be concentrated on the failing section.

#### 7.0 SA1000 SECTOR FORMAT

The track layout for the SA1000 (typical for 32 sectors) is shown below.

| 1 |       |                 | ;     |              |       |       |   |

|---|-------|-----------------|-------|--------------|-------|-------|---|

|   |       | a F c h s e 0 0 |       | , - , ,      |       |       |   |

| ! | bytes | m E y d e c 0 0 | bytes | m¦8¦ bytes ¦ | c 0 0 | bytes |   |

|   | 00's  | 1   c   c       | 00's  | data         | c     | 4E's  | } |

|   |       |                 |       |              |       |       |   |

|   |       |                 |       |              |       |       |   |

am, FE, cyl, hd, sec, 00, F8 = 1 byte ecc = 3 bytes

314 bytes/sector

Last Gap = 352 bytes

Host I/O Connector Pin Assignment.

The Host I/O Bus uses a 50-pin connector (AMP P/N 2-87227-5 or equivalent). The unused signal pins are considered to be spares for future use. The pin assignments are as follows:

| Signal  | Pin | Number |

|---------|-----|--------|

| DATA0   | 2   |        |

| DATA1   | 4   |        |

| DATA 2  | 6   |        |

| DATA3   | 8   |        |

| DATA4   | 10  |        |

| DATA5   | 12  |        |

| DATA6   | 14  |        |

| DATA7   | 16  |        |

| PARITY  | 18  |        |

|         | 20  |        |

|         | 22  | 1      |

|         | 24  | ì      |

|         | 26  | Future |

|         | 28  | Usage  |

| <b></b> | 30  | 3      |

|         | 32  | į      |

|         | 34  |        |

| BUSY    | 36  |        |

| ACK     | 38  |        |

| RST     | 40  |        |

| TDN     | 42  |        |

| SEL     | 44  |        |

| C/D     | 46  |        |

| REQ     | 48  |        |

| I/O     | 50  |        |

| -, .    |     |        |

NOTE: All signals are negative true and all odd pins are connected to ground. The signal lines are terminated with 220 ohms to 5V and 330 ohms to ground.

# APPENDIX A

# CUSTOMER FIRMWARE: DIP SWITCH SETUP PROCEDURE FOR THE SA1401

Prom Set WS30 - I,II,III,IV

Location: 2H

| Switch Bits | 1 | 8           | 7 | 1         | 6          | 5 | 1 |            | 3 | • | _          | 1 | 1 |        |

|-------------|---|-------------|---|-----------|------------|---|---|------------|---|---|------------|---|---|--------|

| Field       |   | LUN<br>Driv | • | <br> <br> | LUN<br>Dri | _ | 1 | LUN<br>Dri |   |   | LUN<br>Dri | 3 |   | O<br>F |

| Definition  | İ | Тур         | 9 | <br> <br> | Тур        |   | Ì | Тур        |   | İ | Тур        |   | İ | F      |

|             | 1 |             |   | - 1       |            |   | - |            |   |   |            |   | Į | 0      |

|             | İ |             |   | İ         |            |   | į |            |   | İ |            |   | Ì | N      |

| Drive<br>  Type | Description                     |

|-----------------|---------------------------------|

| 0-on on         | SA1002   2 heads, 256 cylinders |

| 1-on off        | SA1004   4 heads, 256 cylinders |

| 2-off on        | reserved                        |

| 3-off off       | reserved                        |

all drives are 32 sectors/track, 256 bytes/sector

Location: 3D

| 18 7                   | l 6 5                  | 1 4 3                      | 2 I                        | •           |

|------------------------|------------------------|----------------------------|----------------------------|-------------|

| LUN 0<br>Drive<br>Type | LUN 1<br>Drive<br>Type | LUN 2<br>  Drive<br>  Type | LUN 3  <br>Drive  <br>Type | 0<br>F<br>F |

| on on                  | on on                  | on off                     | on on                      | <b>M</b>    |

Drive 0, 1, and 3 are set up for SA1002 Drive 2 is set up for SA1004 The following voltages are required:

- a) +24VDC (Pin 1); +24V return is Pin 2

- b) +5VDC (Pin 5); +5V return is Pin 6

- c) -5VDC (Pin 4); -5V return is Pin 3

DO NOT USE -15VDC ON THE SA1401!

SERIOUS DAMAGE WILL RESULT. READ THE

SPECIFICATION BEFORE ATTEMPTING POWER ON !

Copyright Shugart

475 Oakmead Parkway

Sunnyvale, CA 94086

Telephone: (408) 733-0100

TWX: 910 339 9355 SHUGART SUVL