AD01-D analog-to-digital conversion subsystem manual

1st Printing April 1971 2nd Printing October 1971 3rd Printing (Rev) June 1972

Copyright © 1971, 1972 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

UNIBUS

COMPUTER LAB

# CONTENTS

|              |                                                           | Page       |                                                                                | Page  |

|--------------|-----------------------------------------------------------|------------|--------------------------------------------------------------------------------|-------|

| CHAPTI       | ER 1 GENERAL INFORMATION                                  |            | CHAPTER 3 OPERATION AND PROGRAMMING                                            |       |

| 1.1          | Introduction                                              | 1-1        | 3.1 Introduction                                                               | 3-1   |

| 1.2          | Purpose                                                   | 1-1        | 3.2 Address Format                                                             | 3-1   |

| 1.3          | Functional Description                                    | 1-1        | 3.3 CSR Format                                                                 | 3-1   |

| 1.4          | Physical Description                                      | 1-1        | 3.4 DBR Format                                                                 | 3-1   |

| 1.5          | Specifications                                            | 1-2        | 3.5 Interrupt Structure                                                        | 3-2   |

| 1.5.1        | Environmental                                             | 1-2        | 3.6 External Clock Control                                                     | 3-2   |

| 1.5.2        | Power Requirements                                        | 1-2        | 3.6.1 EXT IN                                                                   | 3-2   |

| 1.5.3        | Packaging                                                 | 1-2        | 3.6.2 EXT IN A                                                                 | 3-2   |

| 1.5.4        | Performance Parameters                                    | 1-2        | 3.6.3 External Clock Timing Considerations                                     | 3-3   |

| 1.6          | Reference Documents                                       | 1-2        |                                                                                |       |

|              |                                                           |            | CHAPTER 4 PRINCIPLES OF OPERATION                                              |       |

|              |                                                           |            | 4.1 Introduction                                                               | 4-1   |

| CHAPT        | ER 2 INSTALLATION AND ADJUSTMENTS                         |            | 4.2 Block Diagram Analysis                                                     | 4-1   |

| 2.1          | Installation Planning                                     | 2-1        | 4.3 Detailed Circuit Analysis                                                  | 4-3   |

| 2.1          | Environmental Requirements                                | 2-1        | 4.3.1 Multiplexer                                                              | 4-3   |

|              | Configurations                                            | 2-1        | 4.3.2 Scaling Amplifier                                                        | 4-3   |

| 2.3          |                                                           | 2-1        | 4.3.3 A/D Converter                                                            | 4-3   |

| 2.3.1        | Channel Expansion                                         | 2-1        | 4.3.3.1 Unipolar with Wide Aperture                                            | 4-3   |

| 2.3.2        | Bipolar Option AH05                                       | 2-1<br>2-1 | 4.3.3.2 Unipolar with Narrow Aperture                                          | 4-3   |

| 2.3.3        | Sample and Hold Amplifier Option AH04 Unibus Connections  | 2-1        | 4.3.3.3 Bipolar with Wide Aperture                                             | 4-3   |

| 2.3.4        |                                                           | 2-1<br>2-1 | 4.3.3.4 Bipolar with Narrow Aperture                                           | 4-3   |

| 2.3.5        | Multiplexer Channel Connections External Clock Connection | 2-1<br>2-1 | 4.3.4 Timing                                                                   | 4-3   |

| 2.3.6        | Installation Procedure                                    | 2-1        | 4.3.5 Bus Interface                                                            | 4-3   |

| 2.4          |                                                           | 2-1        |                                                                                |       |

| 2.5          | Option Installation Adjustment Procedure                  | 2-2        | CHAPTER 5 MAINTENANCE                                                          |       |

| 2.6<br>2.6.1 | Power Supply Adjustments                                  | 2-2        | 5.1 AD01-D MainDEC-11-D6AB Diagnostic Program                                  | 5-1   |

| 2.6.2        | Timing Adjustment                                         | 2-3        | 5.2 Preventive Maintenance                                                     | 5-2   |

| 2.6.3        | A/D Converter                                             | 2-3        | 5.2.1 Preventive Maintenance Tasks                                             | 5-2   |

| 2.6.3.1      | A812                                                      | 2-3        | 5.3 Corrective Maintenance                                                     | 5-2   |

| 2.6.3.2      | A862 (AH05 Option)                                        | 2-4        |                                                                                | 5-2   |

| 2.6.4        | Sample and Hold A405 (AH04 Option)                        | 2-4        |                                                                                | 5-2   |

| 2.6.4.1      | AH04 Option Only                                          | 2-4        | 5.3.2 System Troubleshooting                                                   | 5-2   |

| 2.6.4.2      | AH04 option Only AH04 with AH05 Option Only               | 2-5        | 5.3.3 Logic Troubleshooting 5.3.4 Circuit Troubleshooting                      | 5-3   |

| 2.6.5        | Switched-Gain Amplifier A220                              | 2-5        | <ul><li>5.3.4 Circuit Troubleshooting</li><li>5.3.5 Validation Tests</li></ul> | 5-3   |

| 2.6.6        | Multiplexer Setup                                         | 2-5        | 5.3.6 Recording                                                                | 5-4   |

| 2.6.7        | External Sync                                             | 2-6        | 5.4 Test Equipment                                                             | 5-4   |

| 2.0.7        | LATORIAL SYRC                                             | 2-0        | J.4 Test Equipment                                                             | , 3-4 |

# **CONTENTS (Cont)**

|                                              |                                        | Page |           |                             |     |

|----------------------------------------------|----------------------------------------|------|-----------|-----------------------------|-----|

| 5.5                                          | Module Handling and Repair             | 5-4  | Table No. | Title                       | Pa  |

| 5.6                                          | Spare Parts                            | 5-4  | 3-2       | Output Notations            | 3-2 |

| CHAPTER 6 ENGINEERING DRAWINGS               |                                        |      | 5-1       | Test Equipment Required     | 5-4 |

|                                              | EN O ENGINEERING BINTINGS              |      | 5-2       | Spare Parts List            | 5-4 |

| APPENDIX A 10-BIT UNIPOLAR CALIBRATION CHART |                                        |      | 6-1       | AD01-D Engineering Drawings | 6-1 |

| APPEN                                        | DIX B 11-BIT BIPOLAR CALIBRATION CHART |      |           |                             |     |

# **ILLUSTRATIONS**

| Figure No. | Title                                                                                   | Art No.                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1        | AD01-D Configuration                                                                    | 11-0331                                                                                                                                                                                                                                                                                                                                       | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

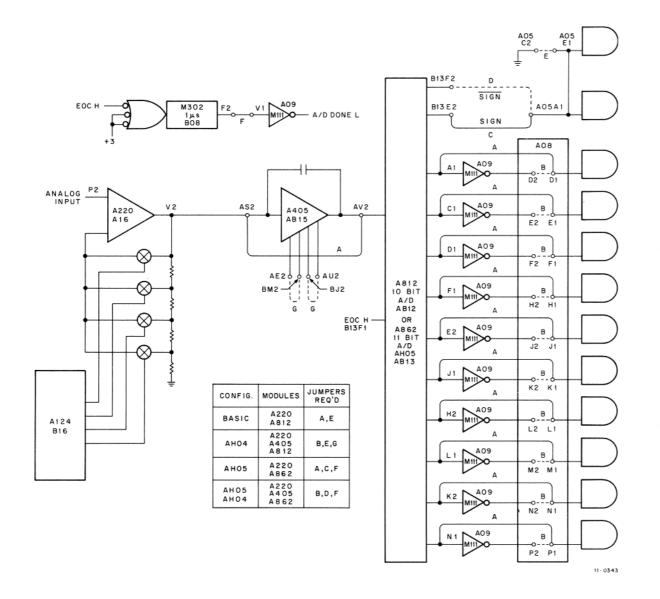

| 2-1        | Option Configuration Diagram                                                            | 11-0343                                                                                                                                                                                                                                                                                                                                       | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

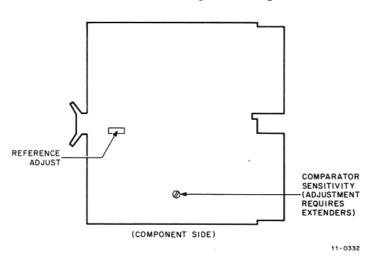

| 2-2        | A812 A/D Converter                                                                      | 11-0332                                                                                                                                                                                                                                                                                                                                       | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

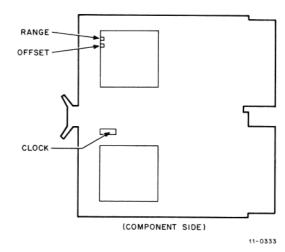

| 2-3        | A862 A/D Converter                                                                      | 11-0333                                                                                                                                                                                                                                                                                                                                       | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

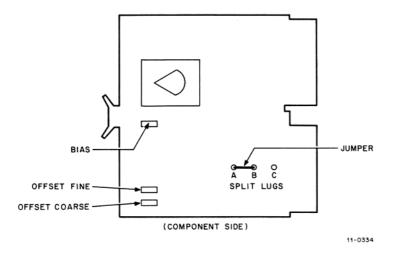

| 2-4        | A405 Sample and Hold                                                                    | 11-0334                                                                                                                                                                                                                                                                                                                                       | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

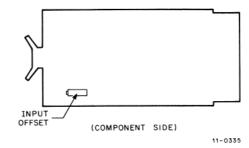

| 2-5        | A220 Switched-Gain Amplifier                                                            | 11-0335                                                                                                                                                                                                                                                                                                                                       | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

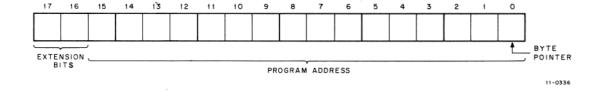

| 3-1        | Address Format                                                                          | 11-0336                                                                                                                                                                                                                                                                                                                                       | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

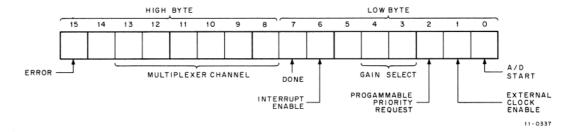

| 3-2        | CSR Format                                                                              | 11-0337                                                                                                                                                                                                                                                                                                                                       | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

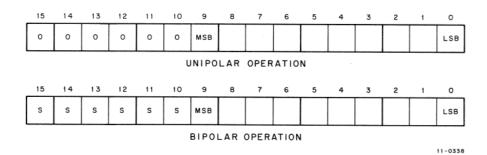

| 3-3        | DBR Format                                                                              | 11-0338                                                                                                                                                                                                                                                                                                                                       | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3-4        | External Clock Timing                                                                   | 11-0339                                                                                                                                                                                                                                                                                                                                       | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4-1        | AD01-D Block Diagram                                                                    | 11-0342                                                                                                                                                                                                                                                                                                                                       | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

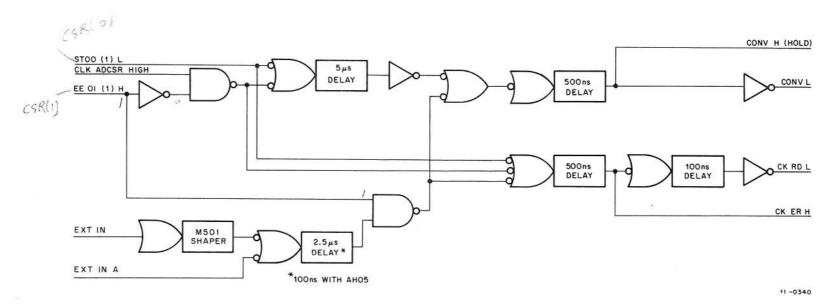

| 4-2        | Timing Generator Circuit                                                                | 11-0340                                                                                                                                                                                                                                                                                                                                       | 4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4-3        | AD01-D Interrupt Logic                                                                  | 11-0341                                                                                                                                                                                                                                                                                                                                       | 4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

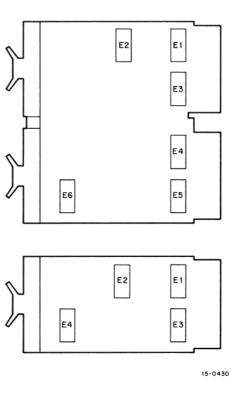

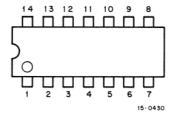

| 5-1        | IC Location                                                                             | 15-0430                                                                                                                                                                                                                                                                                                                                       | 5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5-2        | IC Pin Location                                                                         | 15-0430                                                                                                                                                                                                                                                                                                                                       | 5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-2<br>4-3<br>5-1 | 1-1 AD01-D Configuration 2-1 Option Configuration Diagram 2-2 A812 A/D Converter 2-3 A862 A/D Converter 2-4 A405 Sample and Hold 2-5 A220 Switched-Gain Amplifier 3-1 Address Format 3-2 CSR Format 3-3 DBR Format 3-4 External Clock Timing 4-1 AD01-D Block Diagram 4-2 Timing Generator Circuit 4-3 AD01-D Interrupt Logic 5-1 IC Location | 1-1 AD01-D Configuration 11-0331 2-1 Option Configuration Diagram 11-0343 2-2 A812 A/D Converter 11-0332 2-3 A862 A/D Converter 11-0333 2-4 A405 Sample and Hold 11-0334 2-5 A220 Switched-Gain Amplifier 11-0335 3-1 Address Format 11-0336 3-2 CSR Format 11-0337 3-3 DBR Format 11-0338 3-4 External Clock Timing 11-0339 4-1 AD01-D Block Diagram 11-0342 4-2 Timing Generator Circuit 11-0340 4-3 AD01-D Interrupt Logic 11-0341 5-1 IC Location 15-0430 |

# **TABLES**

| Table No. |     | Title                                                | Page |  |

|-----------|-----|------------------------------------------------------|------|--|

|           | 1-1 | AD01-D Module Complement                             | 1-1  |  |

|           | 2-1 | Channel, Module, and Pin Number Cross-Reference List | 2-2  |  |

|           | 2-2 | Power Supply Adjustments                             | 2-2  |  |

|           | 2-3 | Timing Adjustments                                   | 2-4  |  |

|           | 3-1 | CSR Bits                                             | 3-1  |  |

|           | 3-1 | CSR Bits                                             |      |  |

# CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

The AD01-D Analog-to-Digital Conversion Subsystem is a peripheral device used with the PDP-11 Computer Systems in data acquisition and control applications. Refer to the *PDP-11 Unibus Interface Manual* for information relevant to the architecture of the computer and peripheral devices.

#### 1.2 PURPOSE

The AD01-D operates under computer or external clock control as a highly flexible analog input device to digitize analog inputs connected to directly addressable, multiplex switch modules. As many as eight multiplex switch modules can be implemented. Each module can service four individual analog inputs.

The basic AD01-D provides 10-bit digitization of unipolar, high-level analog signals with a nominal full-scale range of 0V to +1.25V, +2.5V, +5.0V or +10V. These four ranges are program-selectable and are achieved by a selectable gain amplifier. Options are available for digitization of bipolar analog signals and for sample and hold applications.

#### 1.3 FUNCTIONAL DESCRIPTION

The AD01-D comprises

- a. An expandable solid-state input multiplexer

- b. A programmable input range selector

- c. A high-speed A/D converter

- d. The computer interface logic.

The interface logic includes two registers to store control and status information and data. The AD01-D is accessed and controlled by a control and status word with a Move (MOV) instruction. A single control and status word from the computer selects the input range and multiplexer channel and starts the conversion. Other novel features of the interface logic are the ability to place the AD01-D in an interrupting or noninterrupting mode and to select an external clock. In the interrupting mode, the AD01-D can issue an interrupt when conversion is done or when an error condition is produced by starting a new conversion before the previous conversion is complete. The noninterrupting mode enables the converter to approach its maximum throughput rate under program control. After the conversion is complete, the data is easily transferred from the AD01-D to the computer by programming another MOV instruction.

#### 1.4 PHYSICAL DESCRIPTION

The AD01-D Analog-to-Digital Converter Subsystem can be configured and modified according to application needs. All logic, options, and a Type H727 A/B Analog Power Supply are housed in a single, 5-1/4 in., rack-mountable assembly. Insertion slots for the multiplex switch modules, bipolar option, and sample and hold option are prewired to simplify field installation and modification. Only simple jumper wire changes are required. The module complement and optional modules for the AD01-D are listed in Table 1-1; the location of each module is shown in Figure 1-1. Logic power for the AD01-D is supplied by a separate H716 Logic Power Supply, which can be rack mounted. Operation with an input voltage of 115V requires an H727-A power supply and the system is designated AD01-DA; an input voltage of 230V requires an H727-B and the system is designated AD01-DB. If rack mounting of the subsystem is desired, DEC offers a 19-in. industrial Type H950 Cabinet with a blower fan and front and rear doors.

Table 1-1

AD01-D Module Complement

| Type/Part No.         | Name                             | Quantity | Location    |

|-----------------------|----------------------------------|----------|-------------|

| A124                  | Four Input Multiplex Switch      | 1        | B16         |

| A124*                 | Four Input Multiplex Switch      | 8 (max)  | A17-A20     |

|                       |                                  |          | B17-B20     |

| A220                  | Selectable Gain Buffer Amplifier | 1        | A16         |

| A862 (AH05)*          | Bipolar A/D Converter            | 1        | AB13 (AB12) |

| A405 (AH04)*          | Sample and Hold                  | 1        | AB15        |

| A708                  | Dual Voltage Regulator           | 1        | A24         |

| A812                  | 10-Bit A/D Converter             | 1        | AB12        |

| G736                  | Request Jumper                   | 1        | A10         |

| M105                  | Address Selector                 | 1        | A3          |

| M111                  | Inverter                         | 1        | A9          |

| M112                  | NOR Gate                         | 1        | B7          |

| M113                  | 10 2-Input NAND Gates            | 1        | A7          |

| M161                  | Binary to Octal/Decimal Decoder  | 1        | B10         |

| M206                  | Six Flip-Flops                   | 2        | AB6         |

| M302                  | Dual Delay Multivibrator         | 3        | AB11, B8    |

| M501                  | Schmitt Trigger                  | 1        | AB22        |

| M617                  | 6 4-Input NOR Buffers            | 1        | В9          |

| M782                  | Interrupt Control                | 1        | В3          |

| M783                  | Unibus TM Drivers                | 2        | AB5         |

| M784                  | Unibus Receivers                 | 1        | A4          |

| M785                  | Unibus Transceivers              | 1        | B4          |

| M908                  | Connector                        | 2        | AB21        |

| *Denotes optional mod | dules.                           |          |             |

TM Unibus is a trademark of Digital Equipment Corporation.

#### 1.5 SPECIFICATIONS

#### 1.5.1 Environmental

Temperature:

0°C to +55°C, operating

-25°C to +85°C, storage

Humidity:

to 90 % without condensation

#### 1.5.2 Power Requirements

Input voltage (ac):

115V/230V ± 10%

Input frequency (ac):

47 Hz to 63 Hz, single phase

Power dissipation:

<75W

# 1.5.3 Packaging

Size:

Height: 5-1/4 in.

Width: 19 in.

Depth: 12 in.

(plus separate power supply)

Weight:

15 lb

#### 1.5.4 Performance Parameters

Conversion time:

22  $\mu$ s, including channel and gain selection with or

without sample and hold option. Bipolar option

adds 7 μs.

Conversion aperture:

17.5  $\mu$ s,

24 µs with Bipolar Option AH05, or

0.1 µs with Sample and Hold Option AH04

Sample and Hold

Acquisition:

5  $\mu$ s to 0.01% of full-scale step change

Aperture:

100 ns

Number of analog

input channels:

4 minimum (expandable to 32 in groups of 4)

Input voltage range

(program-selectable)

Unipolar:

0V to 1.25V, +2.5V, +5.0V or +10.0V, full-scale

Bipolar:

0V to  $\pm$  1.25V,  $\pm$  2.5V,  $\pm$  5.0V or  $\pm$  10.0V, full-scale

System accuracy:

± 0.1% of full-scale

± 0.125% of full-scale with Sample and Hold Option AH04

- \* BIPOLAR OPTION AHOS

- \*\* SAMPLE AND HOLD AMPL OPTION AHO4

- \*\*\* MULTIPLEX SWITCH MODULES

11-0331

Figure 1-1 AD01-D Configuration

Input impedance:

$1000\;M\Omega\;$  in parallel with  $20\;pF$

Input isolation:

Enhancement mode MOS FET switches, off when

unselected or power off

Analog input connections:

Plug-in cable modules

Channel selection:

Overload capability:

6-bit address

(program-selectable)

±20V on all ranges without damage

Cross-Channel attenuation:

78 dB, dc to 80 Hz for 20V p-p signals,

100-Ω source impedance

Input gain:

2-bit code

(program-selectable)

#### 1.6 REFERENCE DOCUMENTS

The following documents are essential to understand the PDP-11 Computer System:

PDP-11 Handbook

PDP-11 Unibus Interface Manual PDP-11 Maintenance Manuals

The following diagnostic program is required to test the performance of the AD01-D:

AD01-D MainDEC-11-D6AB

A-SP-AD01-D-12 Acceptance Procedure

# CHAPTER 2 INSTALLATION AND ADJUSTMENTS

#### 2.1 INSTALLATION PLANNING

The AD01-D is a Type 1943 rack-mountable assembly, which can be installed in the Type H950 Equipment Cabinet. The Type 1943 Assembly has the following dimensions:

Width: 19 in.

Depth: 12 in.

Height: 5-1/4 in.

The associated H716 Logic Power Supply mounts on the rear door of the cabinet.

#### 2.2 ENVIRONMENTAL REQUIREMENTS

The AD01-D and PDP-11 operate in identical environments; the environmental limitations are listed in Chapter 1.

#### 2.3 CONFIGURATIONS

The basic AD01-D Subsystem consists of a 5-1/4 in. rack-mountable logic assembly and a H716 Logic Power Supply. A physical description of the AD01-D and associated options is presented in Chapter 1. The following paragraphs summarize the requirements for installing and configuring the AD01-D.

#### 2.3.1 Channel Expansion

Eight prewired insertion slots are provided in the logic shelf for the multiplex switch modules. The slots are A17 through A20 and B17 through B20 (see Figure 1-1). When expanding the channel capacity, modules must be added in the A level before the B level, progressing from slot 17 toward slot 20.

#### 2.3.2 Bipolar Option AH05

To accommodate A/D conversion of bipolar analog voltages, Bipolar Option AH05 must be installed in the AD01-D logic assembly. The option consists of a replacement Bipolar A/D Converter Module, A862.

The replacement A/D converter occupies two insertion slots while the A812 10-Bit A/D Converter occupies only one. The insertion slot is prewired to accept either A/D converter without wiring changes (see Figure 1-1).

#### 2.3.3 Sample and Hold Amplifier Option AH04

If skewless sampling of analog signals is desired, Sample and Hold Amplifier Option AH04 must be installed in the AD01-D logic assembly. The option consists of a single module designated the A405 Sample and Hold Module. A prewired insertion slot located at AB15 (see Figure 1-1) on the logic assembly is reserved for the module.

#### 2.3.4 Unibus Connections

Only one BC11-A Cable is required to connect the Unibus from the computer to the AD01-D. This cable must be inserted into slot AB01 on the logic assembly. If the AD01-D is the last peripheral device on the Unibus, Terminator Module M930 is inserted in slot AB02; otherwise, this slot is used to connect the Unibus to another peripheral device using another BC11-A Cable.

#### 2.3.5 Multiplexer Channel Connections

The input connections to the multiplexer switch modules are wired to two M908 Connector Modules located in slots AB21 of the logic assembly. The analog signals to be converted should be carried on user-supplied twisted pairs of wires (shielded if necessary). These twisted pairs should be soldered to the appropriate split lugs on the M908 Modules. The assigned channel numbers and the associated pin numbers on the M908 Modules are identified in Table 2-1.

#### 2.3.6 External Clock Connection

As with the multiplexer channel connections, external clock input connections to the timing circuits of the AD01-D are also wired to the M908 Connector Module located in slot A21. If an external clock is to be used in an AD01-D installation, the clock signal should be carried on user-supplied twisted pairs of wires (shielded if necessary). The twisted pair should be soldered to split lugs A1 and B1 or A2 and B1 on the M908 Connector Module in slot A21.

#### 2.4 INSTALLATION PROCEDURE

The installation procedure for the AD01-D Analog Subsystem is as follows:

| Step | Procedure                                                                                                                                                                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Unpack the equipment from the shipping container(s) and inspect the unit(s) for damage. Damage claims should be made to the DEC district supervisor.                                              |

|      | NOTE  DEC Field Service personnel should be available for consultation on potential problems.                                                                                                     |

| 2    | Remove the tape that secures the modules and cables in the AD01-D Assembly and varify that the modules and connectors are seated in the proper connector slots (refer to drawing D-MU-AD01-D-02). |

| 3    | Mount the AD01-D Assembly in the assigned location (H950 Equipment Cabinet), using the appropriate hardware.                                                                                      |

|      | (continued on page 2-2)                                                                                                                                                                           |

(continued on page 2-2)

Table 2-1 Channel, Module, and Pin Number Cross-Reference List

| Channel No.          | A124 Multiplex Switch | M908 Connector Module |                             |                      |

|----------------------|-----------------------|-----------------------|-----------------------------|----------------------|

| Channel No.          | Module Slot           | Slot                  | Hot Pin                     | Gnd Pin              |

| 0<br>1<br>2<br>3     | A17                   | A21                   | B2<br>C1<br>D2<br>E1        | C2<br>D1<br>E2<br>F1 |

| 4<br>5<br>6<br>7     | A18                   | A21                   | F2<br>H1<br>J2<br>K1        | H2<br>J1<br>K2<br>L1 |

| 8<br>9<br>10<br>11   | A19                   | A21                   | L2<br>M1<br>N2<br>P1        | M2<br>N1<br>P2<br>R1 |

| 12<br>13<br>14<br>15 | A20                   | A21                   | R2<br>S1<br>T2<br><u>U1</u> | S2<br>T1<br>U2<br>V1 |

| 16<br>17<br>18<br>19 | B17                   | B21                   | B2<br>C1<br>D2<br>E1        | C2<br>D1<br>E2<br>F1 |

| 20<br>21<br>22<br>23 | B18                   | B21                   | F2<br>H1<br>J2<br>K1        | H2<br>J1<br>K2<br>L1 |

| 24<br>25<br>26<br>27 | B19                   | B21                   | L2<br>M1<br>N2<br>P1        | M2<br>N1<br>P2<br>R1 |

| 28<br>29<br>30<br>31 | B20                   | B21                   | R2<br>S1<br>T2<br>U1        | S2<br>T1<br>U2<br>V1 |

| EXT IN<br>EXT IN A   |                       | A21                   | A1<br>A2                    | B1<br>B1             |

| Step | Procedure                                                                                                                                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | Install the logic power supply and chassis subassembly in the assigned location (refer to drawing D-UA-H716-B-0 for AD01-DA or drawing D-UA-H716-D-0 for AD01-DB).                         |

| 5    | Connect the H716 Logic Power Supply Cable from the power supply to the left end panel of the AD01-D Subsystem where noted.                                                                 |

| 6    | Determine where Unibus is terminated and connect BC11-A Cable to last device. If the AD01-D is the last device on the bus, install the Terminator Modules M930 in slot AB02 of the AD01-D. |

Perform the acceptance checkout of the AD01-D logic and analog circuits using the MainDEC-11-D6AB Diagnostic Program and A-SP-AD01-D-12 Acceptance Procedure. Adjustment should not be necessary because all potentiometers are sealed at the factory after adjustment.

8 If, at any time, the AD01-D is not within its stated specifications (accuracy), perform the adjustment procedure in Paragraph 2.6. When this adjustment is complete, perform the acceptance tests again.

# 2.5 OPTION INSTALLATION

The AD01-D options necessitate some changes in the back panel wiring. All information regarding the wiring for each option configuration is given in Figure 2-1. Add and/or delete wires according to this diagram when installing options.

# 2.6 ADJUSTMENT PROCEDURE

The adjustment procedure for the AD01-D depends on the particular option configuration. If a given option is not included in the AD01-D, disregard the corresponding adjustment procedure. To achieve accurate calibrations, perform the adjustments in the following sequence.

- 1. Power Supplies

- 2. Timing

- 3. A/D Converter (A812 or A862)

- 4. Sample and Hold A405

- 5. Switched-Gain Amplifier A220

- Multiplexer Setup

- 7. External Sync

# 2.6.1 Power Supply Adjustments

Table 2-2 summarizes the necessary information for adjusting the power supplies in the AD01-D.

Table 2-2 Power Supply Adjustments

| Supply | Voltage*    | Pin                  | Adjustment Location                    |

|--------|-------------|----------------------|----------------------------------------|

| H716   | +5V ± 0.25V | A03A2<br>A03C2 (GND) |                                        |

| H727   | +15V ± 0.1V | A24V2                | POWER MATE – Top Right<br>(Blue Case)  |

|        |             | A24T2 (GND)          | DELTRON – Bottom Right<br>(Black Case) |

|        | -20V ± 0.1V | A24N2                | POWER MATE – Top Left<br>(Blue Case)   |

|        |             | A24T2 (GND)          | DELTRON – Bottom Left<br>(Black Case)  |

| Jumper | From                                                                                   | То                                                                                     |

|--------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| • А    | A09A1<br>A09C1<br>A09D1<br>A09F1                                                       | A08D1<br>A08E1<br>A08F1<br>A08H1                                                       |

| -      | A09E2<br>A09J1<br>A09H2<br>A09L1<br>A09K2                                              | A08J1<br>A08K1<br>A08L1<br>A08M1<br>A08N1                                              |

|        | A09N1<br>A15S2                                                                         | A08P1<br>A15V2                                                                         |

| В      | A08D2<br>A08E2<br>A08F2<br>A08H2<br>A08J2<br>A08K2<br>A08L2<br>A08M2<br>A08N2<br>A08P2 | A08D1<br>A08E1<br>A08F1<br>A08H1<br>A08J1<br>A08K1<br>A08L1<br>A08M1<br>A08N1<br>A08P1 |

| С      | B13E2                                                                                  | A05A1                                                                                  |

| D      | B13F2                                                                                  | A05A1                                                                                  |

| Е      | A05C2                                                                                  | A05E1                                                                                  |

| F      | B08F2                                                                                  | A09V1                                                                                  |

| G      | A15E2<br>B15J2                                                                         | B15M2<br>A15U2                                                                         |

Figure 2-1 Option Configuration Diagram

Table 2-2 (Cont)

Power Supply Adjustments

| Supply                                                                                          | Voltage*    | Pin                  | Adjustment Location |  |

|-------------------------------------------------------------------------------------------------|-------------|----------------------|---------------------|--|

| A708                                                                                            | -15V ± 0.1V | A24S2<br>A24T2 (GND) | No Adjustment       |  |

| *Voltage measurement can be made with EDC null meter and DEC 10:1 Divider (refer to Table 5-1). |             |                      |                     |  |

# 2.6.2 Timing Adjustment

The timing of the AD01-D can be adjusted while running the WAS-IS TEST (SA 270<sub>8</sub>) of the diagnostics with inhibit printout option. The required timing adjustments are summarized in Table 2-3.

### 2.6.3 A/D Converter

2.6.3.1 A812 – The following adjustment should be performed while running the Display Conversion Loop (SA  $220_8$ ) of the diagnostic program.

Table 2-3

Timing Adjustments

| Module | Slot | Pin | Time                       |

|--------|------|-----|----------------------------|

| M302   | A11  | F2  | 5 μs                       |

| M302   | A11  | T2  | 0.5 μs                     |

| M302   | B11  | F2  | 0.5 μs                     |

| M302   | B11  | T2  | 0.1 μs                     |

| M302   | B08  | F2  | 1 μs/AH05 only             |

| M302*  | В08  | T2  | 2.5 μs<br>0.1 μs with AH05 |

<sup>\*</sup>External sync signal is required to set this single-shot, because it derives output signal from Ext Sync input.

#### NOTE

The procedure should be performed with the A220 and A405 Modules removed from their insertion slots.

| Step | Procedure                                                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Extend A812 Module using two W982 Extender Modules.                                                                                                                                       |

| 2    | Set EDC to 5 mV and connect to B12V2.                                                                                                                                                     |

| 3    | Adjust comparator sensitivity potentiometer (see Figure 2-2) for $000\ 000_8$ to $000\ 001_8$ on console DATA indicators. (Adjust for $001\ 777_8$ to $001\ 776_8$ if AH04 is installed.) |

| 4    | Set EDC to +9.9853V.                                                                                                                                                                      |

| 5    | Adjust reference potentiometer for 001 $777_8$ to 001 $776_8$ on console DATA indicators. (Adjust for 000 $000_8$ to 000 $001_8$ if AH04 is installed.)                                   |

Figure 2-2 A812 A/D Converter

Figure 2-3 A862 A/D Converter

2.6.3.2 A862 (AH05 Option) — The following adjustment procedure uses the WAS-IS TEST and the Display Conversion Loop of the diagnostic program. Adjust the A862 A/D Converter as follows:

#### NOTE

The procedure should be performed with the A220 and A405 Modules removed from their insertion slots.

| Step | Procedure                                                                                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Start the WAS-IS TEST (SA $270_8$ ) with inhibit printout bit $13 = 1$ .                                                                                                                 |

| , 2  | Connect scope to B13F1 and adjust clock potentiometer (conversion time) to obtain a 24-µs positive pulse (see Figure 2-3).                                                               |

| 3    | Stop program and restart at Display Conversion Loop (SA 2208).                                                                                                                           |

| 4    | Connect EDC to A13J2 and A13F2 (GND). Set EDC to +5 mV $\pm$ 2 mV.                                                                                                                       |

| 5    | Adjust offset potentiometer for 000 000 <sub>8</sub> to 000 001 <sub>8</sub> on console DATA indicators. (Adjust for 001 777 <sub>8</sub> to 001 776 <sub>8</sub> if AH04 is installed.) |

# 2.6.4 Sample and Hold A405 (AH04 Option)

The adjustment procedure of the A405 Module depends on the AD01-D option configuration. Two procedures are outlined below. One procedure applies to systems that have only the AH04 Option (Sample and Hold); the other procedure applies to systems that have both the AH04 and AH05 (Bipolar) Options.

# 2.6.4.1 AH04 Option Only — Adjust the A405 Module as follows:

# NOTE

The procedure should be performed with the A220 Module removed from its insertion slot.

| Step | Procedure                                                                              |

|------|----------------------------------------------------------------------------------------|

| 1    | Ensure that all proper jumpers (except those marked G) are installed (see Figure 2-1). |

| 2    | Ensure that split lugs A and B on the A405 Module are connected (see Figure 2-4).      |

| 3    | Start Display Conversion Loop (SA 2208) of the diagnostic program.                     |

| 4    | Connect EDC to A15S2 and A15F2 (GND). Set EDC to -5 mV.                                |

|      | (continued on Page 2-5)                                                                |

| Step | Procedure                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------|

| 5    | Adjust bias potentiometer (see Figure 2-4) on A405 Module for 001 $776_8$ to 001 $777_8$ on console DATA indicators.            |

| 6    | Stop program and turn off computer power.                                                                                       |

| 7    | Add jumper wire G to back panel wiring.                                                                                         |

| 8    | Turn on computer power and set EDC to 9.9853V.                                                                                  |

| 9    | Restart Display Conversion Loop (SA 2208).                                                                                      |

| 10   | Adjust offset coarse potentiometer on A405 for 001 $776_8$ to 001 $777_8$ (or as close as possible) on console DATA indicators. |

| 11   | Adjust offset fine potentiometer on A405 for 001 $776_8$ to 001 $777_8$ on console DATA indicators.                             |

# 2.6.4.2 AH04 with AH05 Option Only – Adjust the A405 Module as follows:

| Step | Procedure                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------|

| 1    | Ensure that all proper jumpers are installed (see Figure 2-1).                                                        |

| 2    | Ensure that split lugs A and B on the A405 Module are connected (see Figure 2-4)                                      |

| 3    | Connect EDC to A15S2 and A15F2 (GND). Set EDC to +5 mV.                                                               |

| 4    | Start the Display Conversion Loop (SA 2208) of the diagnostic program.                                                |

| 5    | Adjust bias potentiometer (see Figure 2-4) on A405 Module for 000 $001_8$ to $000\ 000_8$ on console DATA indicators. |

Figure 2-4 A405 Sample and Hold

# 2.6.5 Switched-Gain Amplifier A220

Adjust the A220 Switched-Gain Amplifier as follows:

| Step | Procedure                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------|

| 1    | Ensure that Module A220 is installed in slot A16 and that Module A124 is installed in slot B16.                                |

| 2    | Connect EDC to A16P2 and A16F2 (GND). Set EDC to +600 $\mu$ V.                                                                 |

| 3    | Start the Display Conversion Loop (SA $220_8$ ) of the diagnostic program with a gain of 8 (SW6 and SW7 = 1).                  |

| 4    | Adjust input offset potentiometer (Figure 2-5) on A220 Module for $000\ 001_8$ to $000\ 000_8$ on the console DATA indicators. |

| 5    | Set EDC to 0.625V and verify that DATA indicators display the following readouts                                               |

| Data (±1 bit) | SW6 | SW7 | Gain |

|---------------|-----|-----|------|

| 0001008       | 0   | 0   | 1    |

| 0002008       | 1   | 0   | 2    |

| 0004008       | 0   | 1   | 4    |

with specified gain settings:

0010008

Figure 2-5 A220 Switched-Gain Amplifier

# 2.6.6 Multiplexer Setup

Set up multiplexer as follows:

a. Verify that A124 Multiplexer Switch Modules are installed in the following slots:

| CH00 | CH03 | Slot A17 |

|------|------|----------|

| CH04 | CH07 | Slot A18 |

| CH08 | CH11 | Slot A19 |

| CH12 | CH15 | Slot A20 |

| CH16 | CH19 | Slot B17 |

| CH20 | CH23 | Slot B18 |

| CH24 | CH27 | Slot B19 |

| CH28 | CH31 | Slot B20 |

|      |      |          |

b. If the G735 Test Card Module is available, perform the following procedure:

#### NOTE

The G735 Module produces eight distinct voltage levels when fed from the EDC. The first level, fed to channels 0, 10<sub>8</sub>, 20<sub>8</sub>, 30<sub>8</sub> is equal to the input level from the EDC. Each successive level is half the previous one and appears on the next channel, except that the last level is ground. Jumper X should be connected on the module for testing the AD01-D.

| Step | Procedure                                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Insert the G735 Module in slot AB21.                                                                                                                  |

| 2    | Connect EDC to the tabs at the handle end, and set EDC to +10V.                                                                                       |

| 3    | Set the SR on the console to 2708 and press start.                                                                                                    |

| 4    | Load the initial channel of the multiplexer to be tested in DATA bits 00 <sub>8</sub> through 04 <sub>8</sub> then press CONT. The program will halt. |

| 5    | Load the number of channels to be tested in DATA bits $00_8$ through $04_8$ , then press CONT. The program will again halt.                           |

| 6    | Set the SR to all 0s and press CONT. The program should run. After one complete pass, the Teletype bell will sound.                                   |

| 7    | Set bit 06 of the SR to 1. The following table is printed:                                                                                            |

| Channel  | Initial Value | Final Value |

|----------|---------------|-------------|

| CH00     | 1777          | 1777        |

| CH01     | 1000          | 1000        |

| CH02     | 0400          | 0400        |

| CH03     | 0200          | 0200        |

| CH04     | 0100          | 0100        |

| CH05     | 0040          | 0040        |

| CH06     | 0020          | 0020        |

| CH07     | 0000          | 0000        |

| <b>\</b> |               | <b>₩</b>    |

| СН37     | 0000          | 00'00       |

#### NOTE

If differences between initial values and final values of more than one count occur, check the multiplexer channel in question. It may be noisy and should be replaced.

c. If the G735 Module is unavailable, perform the following procedure:

| Step | Procedure                                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | With the program running the Display Conversion Loop (SA 220 <sub>8</sub> ) check each multiplexer channel by moving the EDC to the proper input pins in slot AB21. |

| 2    | Verify the correct results on the DATA indicators of the computer.                                                                                                  |

# 2.6.7 External Sync

# NOTE

Before connecting the external sync to the AD01-D, associated jumpers must be removed. These jumpers are:

EXT IN - A22R2 to A22C2 EXT IN A - B08B2 to B08N2

After connecting the external sync (refer to Table 2-1), the EXTEST and EXFAST Diagnostic Subroutines can be run to verify proper operation of the AD01-D under control of external sync.

PZ

# CHAPTER 3 OPERATION AND PROGRAMMING

# 3.1 INTRODUCTION

Operation of the AD01-D is controlled entirely by the PDP-11 Computer program. All I/O and control programming is done by issuing the normal memory reference instructions. The nature of the program depends on the system application and the familiarity of the programmer with the particular application and the PDP-11 instruction set.

# 3.2 ADDRESS FORMAT

The AD01-D is assigned two bus addresses:

- a. 776770<sub>8</sub> for the control and status register (CSR)

- b. 7767728 for the data buffer register (DBR).

All information flows between the processor and the AD01-D through these registers. The address format is shown in Figure 3-1.

Figure 3-1 Address Format

### 3.3 CSR FORMAT

The operating condition of the AD01-D is established by transferring a 16-bit control word or an 8-bit control byte from the processor to the CSR. The status of the AD01-D can be determined by transferring the contents of the CSR to the processor and testing the status bits. The CSR format and bit assignments are illustrated in Figure 3-2. The purpose and description of each bit in the CSR is presented in Table 3-1.

#### 3.4 DBR FORMAT

On command, the AD01-D digitizes the unipolar analog voltage of the selected channel into a 10-bit binary code, using the successive-approximation technique. The bipolar option permits conversion of bipolar analog voltage

Figure 3-2 CSR Format

Table 3-1 CSR Bits

| Bit   | Description                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | ERROR(ER) — indicates device has been issued a START command during the time between Start Conversion and Read ADDB. Cleared by INIT. Set by CONVERT command if error condition is present. Cleared under program control when new Gain and MUX Channel data is loaded. |

|       | NOTE                                                                                                                                                                                                                                                                    |

|       | The main purpose of the Error Bit is to indicate timing prob-<br>lems that could occur if an external clock is starting conver-<br>sions at certain intervals and conversions are being made un-<br>der program control between the external clock pulses.              |

| 14    | Unused.                                                                                                                                                                                                                                                                 |

| 13-08 | MULTIPLEXER CHANNEL (MC) — Selects 1 of 64 multiplexer channels. Loaded under program control. Cleared by INIT.                                                                                                                                                         |

| 07    | DONE (DN) — Indicates state of converter. Reset by INIT. Set by A/D Done. Reset by reading ADDB. Read only.                                                                                                                                                             |

|       | (Continued on page 3-2)                                                                                                                                                                                                                                                 |

Table 3-1 (Cont) CSR Bits

| Bits  | Description                                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06    | INTERRUPT ENABLE (IE) — Allows interrupts on A/D Done or Error. Set under program control. Cleared by INIT.                                                                                                                                                                                                    |

| 05-03 | Unused.                                                                                                                                                                                                                                                                                                        |

| 4-3   | GAIN SELECT (GS) — Selects gain for programmable gain amplifier. Loaded under program control. Cleared by INIT.                                                                                                                                                                                                |

| 02    | PROGRAMMABLE PRIORITY REQUEST SELECT (PS) — Allows selection of bus request line under program control. When bit 02 = 0, bus requests are made at level 7. When bit 02 = 1, bus requests are made at a level determined by bus grant jumper socket on G736 Module. Set under program control. Cleared by INIT. |

| 01    | EXTERNAL CLOCK ENABLE (EE) – Allows converter to be controlled by external input. Loaded under program control. Cleared by INIT.                                                                                                                                                                               |

| 00    | A/D START — Start conversion. Loaded under program control. Cleared by INIT. Cleared by A/D Done (Write Only).                                                                                                                                                                                                 |

into an 11-bit two's complement code with an extended sign format. The digitized analog voltage is stored in the DBR when the conversion is done. A single move instruction can then be programmed to gate the contents of the DBR onto the Unibus. The data format for unipolar and bipolar operation is illustrated in Figure 3-3. Table 3-2 relates the octal representation of the data word to the input analog voltage to highlight differences between unipolar and bipolar operation.

Figure 3-3 DBR Format

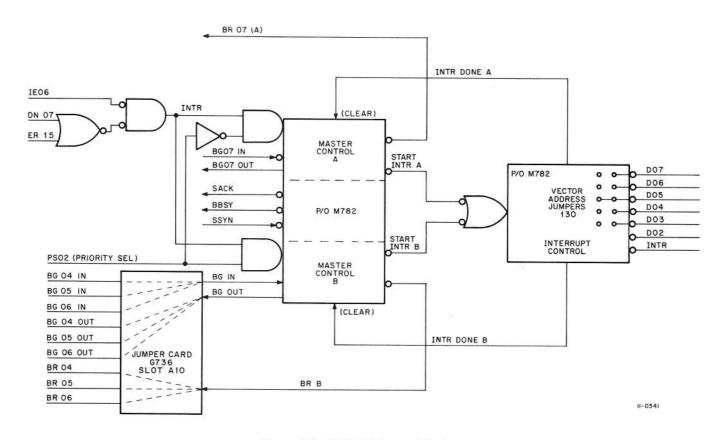

#### 3.5 INTERRUPT STRUCTURE

The AD01-D utilizes the interrupt structure of the PDP-11 System to inform the processor that the A/D conversion is done or to indicate that an error condition exists. The interrupt logic in the AD01-D can be enabled or disabled under program control. Bit 06 of the CSR is assigned to enable the interrupt logic. If the interrupt logic is enabled, one of two priority levels can be selected by the program. Bit 02 is assigned to select the priority level Priority level 7 is enabled when bit 02 is reset, and the priority level established by the bus grant jumper socket on the G736 Module is selected when bit 02 is set. Bus grant jumpers are available for priority levels 4, 5, and 6. When the AD01-D is shipped from the factory, jumper plug S408778 for priority level 5 is installed in the G736 Module.

Table 3-2

Output Notations

| Analog Input Voltage* | Unipolar | Bipolar |

|-----------------------|----------|---------|

| -10.0                 |          | 1760008 |

| - 5.0                 |          | 1770008 |

| 0.0                   | 0000008  | 0000008 |

| + 5.0                 | 0010008  | 0010008 |

| + 9.9902              | 0017778  | 0017778 |

#### 3.6 EXTERNAL CLOCK CONTROL

ranges.

The AD01-D contains two inputs for external control of the conversion process: EXT IN and EXT IN A.

#### 3.6.1 EXT IN

The EXT IN signal is brought into the converter on the M908 Analog Input Module in slot A21, pins A1 and B1 (B1 is EXT common). Input signal conditioning is provided by the M501 Schmitt Trigger circuit. The upper and lower thresholds are set at 1.7V and 1.1V. Input signal swing is limited to ±20V. Input standards are as follows:

Signal swing: ±20V

Loading:

2.7 K $\Omega$  to +5V or 1.8 mA at GND

### NOTE

Before connecting EXT IN to the AD01-D, the jumper wire from A22R2 to A22C2 should be removed.

# 3.6.2 EXT IN A

The EXT IN A signal is brought into the converter on the M908 Analog Input Module in slot A21, pins A2 and B1 (B1 is EXT common). This input is  $T^2L$  compatible. Triggering is accomplished by a level change from high to low or a pulse to low, the duration of which is  $\geq 50$  ns. The fall time of the input trigger should be < 400 ns.

Input standards are as follows:

Signal swing: T<sup>2</sup>L logic levels

Timing: Level – high to low fall time  $\leq$  400 ns

Pulse – high to low, duration  $\geq 50$  ns

Loading: 2-1/2 unit loads

### NOTE

Before connecting EXT IN A to the AD01-D, the jumper wire from B08B2 to B08N2 should be removed.

o s

# 3.6.3 External Clock Timing Considerations

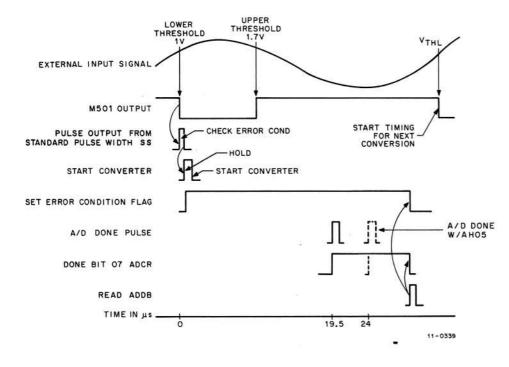

Figure 3-4 is a timing diagram that shows the operation of the AD01-D under external clock control. In the external mode, time is not allowed for the switched gain amplifier to settle, thereby initiating a conversion at the time the external signal is applied. Thus, the user must allow at least 5  $\mu$ s for settling of the input amplifier, if necessary.

Figure 3-4 External Clock Timing

# CHAPTER 4 PRINCIPLES OF OPERATION

#### 4.1 INTRODUCTION

The AD01-D (without options) employs a single high-speed analog-to-digital converter, a gain-selectable amplifier, and an input multiplexer to provide fast multichannel scanning, scaling, and conversion capability. Interface logic compatible with the PDP-11 Computer System is also included in the AD01-D to facilitate direct computer control of the subsystem. This subsystem is intended for use in applications where sampling and processing of analog data from sensors or other external sources is desired. Block and simplified diagrams of the AD01-D are contained in this chapter; detailed block and circuit schematics are included in Chapter 6.

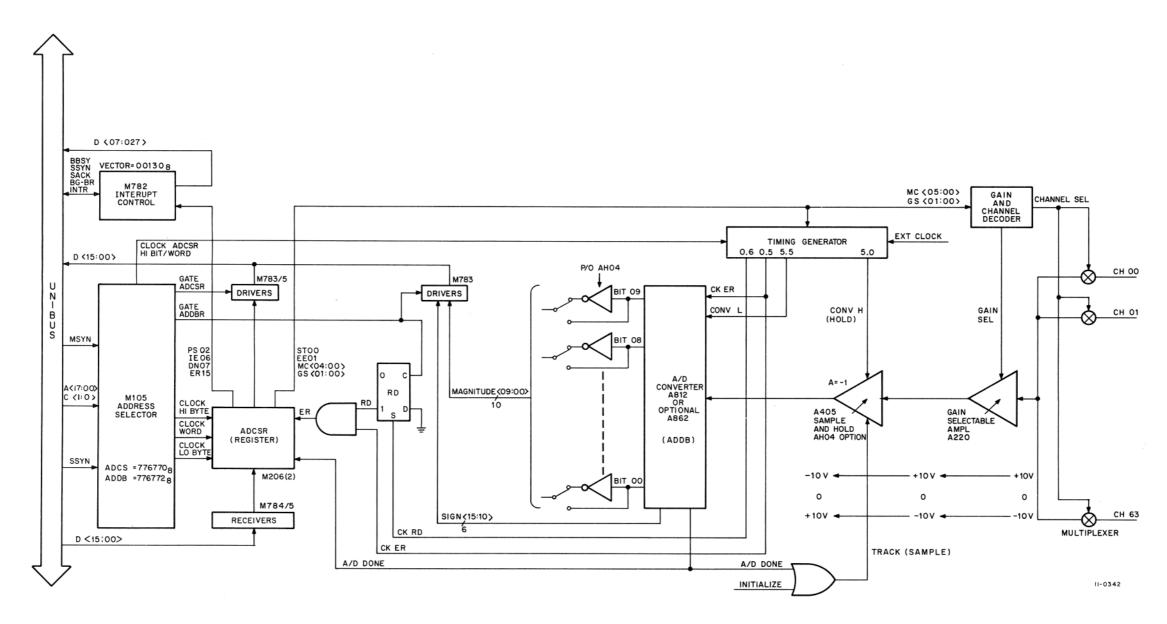

#### 4.2 BLOCK DIAGRAM ANALYSIS

Figure 4-1 is a detailed block diagram of the AD01-D, showing the multiplexer, the gain-selectable amplifier, A/D converter, interface and control logic, and available options. The AD01-D, connected to the Unibus along with other PDP-11 devices, remains dormant unless it is addressed. Two device addresses have been assigned to the AD01-D: One address (766770<sub>8</sub>) is used to gain access to the control and status register (CSR); the other address (766772<sub>8</sub>) is used to gain access to the data buffer register (DBR). Address Selector M105 recognizes these addresses (A 17:01) and generates clock and gating signals to move data into and out of the AD01-D registers. The mode control bits (C 1:0) and the byte control bit (A 00) determine which of the following clock or gating signals is to be generated by the M105 Address Selector:

- a. CLOCK ADCSR WORD

- b. CLOCK ADCSR LOW BYTE

- c. CLOCK ADCSR HIGH BYTE

- d. GATE ADCSR (word)

- e. GATE ADDBR (word)

An A/D conversion can be initiated in three different ways:

- a. Setting the START bit (ST bit 00) of the CSR by incrementing the CSR word or low byte. This action initiates a conversion of the channel and gain setting that has been established by a previous instruction.

- b. Loading a new multiplex channel address into the CSR with a move high byte or word instruction.

#### NOTE

When the external clock is enabled (EE bit 01 is set), conversions are not started by loading a new channel address or gain setting. The START bit must be set to start the conversion under program control. This feature makes it possible to change gain and multiplex address between external clock pulses.

c. By an external clock. When the external clock is enabled (EE bit 01 is set), a move word instruction cannot be used to enable the external clock and select channel and gain at the same time. This would set the error bit (ER 15).

When a conversion is initiated by setting the START bit, a timing train is generated by the timing generator (see Figure 4-1). The sequence of the timing train and the timing intervals are:

| 1. | Check error      | 0.5 μs |

|----|------------------|--------|

| 2. | Check read       | 0.6 μs |

| 3. | Hold (CONV H)    | 5.5 μs |

| 4. | Convert (CONV L) | 6.0 μs |

The multiplex channel (MC) and GAIN SELECT (GS) bits of the CSR are decoded by the gain and channel decoder to select the programmed channel and gain. The check error pulse produced by the timing generator initializes (clears) the A812 A/D Converter. The Check Error pulse also causes the ERROR bit (ER bit 15) in the CSR to be set if the data of the previous conversion has not been gated out of the DBR. Setting the ERROR bit initiates an interrupt and a trap vector if the interrupt logic is enabled. The second pulse in the timing train, the hold command, causes the A405 Sample and Hold Module to acquire and hold the input analog voltage.

Finally, the Convert pulse is produced to start the A/D converter and set the RD flip-flop. The converter produces 10 output bits, which correspond to the amplitude of the input voltage. The successive (serial) approximation technique is used by the converter. When 10 output bits have been determined, the converter produces an A/D Done pulse to release the A405 Sample and Hold Module so that it will start tracking again and to set the DONE bit (DN bit 07) of the CSR. Setting the DONE bit initiates an interrupt and a trap vector if the interrupt logic is enabled. When a conversion is done, the converter, which serves as the DBR, retains the data word until a new conversion is started. However, if the data is not read before a new conversion is started, an error results. This action is accomplished by the RD flip-flop. Data is read out of the AD01-D simply by programming a move DBR word instruction. This instruction is recognized by the M105 Address Selector, which then generates an ADDBR gate. This gate enables the DBR output drivers to transfer the data onto the Unibus. The gate also resets the RD flip-flop to prevent the error from occurring on the next conversion. Normally, the move DBR word instruction is issued by the processor in response to an interrupt signal from the AD01-D.

As noted before, an interrupt is generated by the M782 Interrupt Control (if enabled) when an error occurs and when the conversion is done. The M782 Module also issues a trap vector (address 000130<sub>8</sub>) to inform the processor that the AD01-D issued the interrupt. The processor responds to the interrupt by testing the DONE and ERROR bits of the CSR.

Subject to the result of the test, the program jumps to the move DBR word instruction or an error routine.

Figure 4-1 AD01-D Block Diagram

#### 4.3 DETAILED CIRCUIT ANALYSIS

The two AD01-D options offer four unique configurations; the following description is organized to reflect these configurations. The order of presentation is as follows:

- Multiplexer

- 2. Scaling Amplifier

- 3. A/D Conversion Configurations

- 4. Timing

- 5. Bus Interface

The four configurations accommodate unipolar or bipolar operation with a wide or narrow sampling aperture.

#### 4.3.1 Multiplexer

The multiplexer (drawing D-BS-AD01-D-03) includes at least 4 channels and is expanded to 32 channels in 4-channel increments simply by adding additional A124 Multiplex Modules. The desired channel is selected by a binary decoder that decodes the 6-bit multiplex channel (MC) address received by the CSR. The three most significant bits of the address are decoded by the M161 Octal Decoder to select an A124 Multiplex Module and the two least significant bits of the address are decoded by logic in the multiplexer module itself to select one channel.

#### 4.3.2 Scaling Amplifier

Scaling Amplifier A220 (drawing D-BS-AD01-D-05) provides the AD01-D with an extended dynamic range, the equivalent of up to 14 bits. The amplifier has program-selectable gains of X1, X2, X4, and X8 to achieve this range. The desired gain is selected by a binary decoder (in the associated A124 Module) that decodes the 2-bit gain code received by the CSR.

#### 4.3.3 A/D Converter

The A/D conversion circuits may be configured four different ways using the AH05 Bipolar Option and the AH04 Sample and Hold Option (see Figure 2-1). The sample and hold option reduces the aperture of the AD01-D for skewless sampling applications.

- 4.3.3.1 Unipolar with Wide Aperture This basic AD01-D configuration is capable of accurately converting unipolar analog voltages. The sampling aperture of this configuration is  $|17 \mu s|$ . The configuration consists of the A812 A/D Converter Module and a specific jumper combination as described in Chapter 2. The operation of the A812 Converter is similar to the A811 A/D Converter described in the Digital Logic Handbook.

- 4.3.3.2 Unipolar with Narrow Aperture A sampling aperture of 100 ns is obtained by installing AH04 Sample and Hold Option (see Figure 2-1). This configuration may be useful in analyzing frequency characteristics of unipolar signals or in signal averaging. Installation and calibration procedures are given in Chapter 2. The option consists of a single A405 Module, which is similar to the A404 Module described in the Digital Logic Handbook.