## SN5407, SN5417, SN7407, SN7417 HEX BUFFERS/DRIVERS WITH OPEN-COLLECTOR HIGH-VOLTAGE OUTPUTS

SDLS032E - DECEMBER 1983 - REVISED DECEMBER 2002

- Convert TTL Voltage Levels to MOS Levels

- High Sink-Current Capability

- Input Clamping Diodes Simplify System Design

- Open-Collector Driver for Indicator Lamps and Relays

- Inputs Fully Compatible With Most TTL Circuits

# SN5407, SN5417 . . . J OR W PACKAGE SN7407, SN7417 . . . D, N, OR NS PACKAGE

### description/ordering information

These TTL hex buffers/drivers feature high-voltage open-collector outputs for interfacing

with high-level circuits (such as MOS) or for driving high-current loads (such as lamps or relays), and also are characterized for use as buffers for driving TTL inputs. The SN5407 and SN7407 have minimum breakdown voltages of 30 V, and the SN5417 and SN7417 have minimum breakdown voltages of 15 V. The maximum sink current is 30 mA for the SN5407 and SN5417 and 40 mA for the SN7407 and SN7417.

These devices perform the Boolean function Y = A in positive logic.

These circuits are completely compatible with most TTL families. Inputs are diode clamped to minimize transmission-line effects, which simplifies design. Typical power dissipation is 145 mW, and average propagation delay time is 14 ns.

#### **ORDERING INFORMATION**

| TA             | PACKAGE <sup>†</sup> |               | PACKAGE <sup>†</sup> ORDERABLE PART NUMBER |          |

|----------------|----------------------|---------------|--------------------------------------------|----------|

| 0°C to 70°C    | SOIC - D             | Tube          | SN7407D                                    | 7407     |

|                |                      | Tape and reel | SN7407DR                                   | 7407     |

|                |                      | Tube          | SN7417D                                    | 7447     |

|                |                      | Tape and reel | SN7417DR                                   | 7417     |

|                | PDIP – N             |               | SN7407N                                    | SN7407N  |

|                |                      | Tube          | SN7417N                                    | SN7417N  |

|                | SOP - NS             | Tape and reel | SN7407NSR                                  | SN7407   |

|                |                      |               | SN7417NSR                                  | SN7417   |

| –55°C to 125°C | CDIP – J             | T. b.         | SNJ5407J                                   | SNJ5407J |

|                |                      | Tube          | SNJ5417J                                   | SNJ5417J |

|                | 055 144              | T. I          | SNJ5407W                                   | SNJ5407W |

|                | CFP – W              | Tube          | SNJ5417W                                   | SNJ5417W |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## logic diagram, each buffer/driver (positive logic)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SDLS032E - DECEMBER 1983 - REVISED DECEMBER 2002

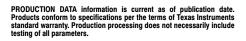

#### schematic

Resistor values shown are nominal.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                            | 0.5 V to 7 V   |

|------------------------------------------------------------------|----------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                 | 0.5 V to 5.5 V |

| Output voltage, VO (see Notes 1 and 2): SN5407, SN7407           | 30 V           |

| SN5417, SN7417                                                   | 15 V           |

| Package thermal impedance, $\theta_{JA}$ (see Note 3): D package | 86°C/W         |

| N package                                                        | 80°C/W         |

| NS package                                                       | e 76°C/W       |

| Storage temperature range, T <sub>stg</sub>                      | —65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values are with respect to GND.

- 2. This is the maximum voltage that should be applied to any output when it is in the off state.

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

#### recommended operating conditions (see Note 4)

|                                           |                                |                | MIN  | NOM | MAX  | UNIT |

|-------------------------------------------|--------------------------------|----------------|------|-----|------|------|

| V <sub>CC</sub> Supply voltage            | Operation of the ma            | SN5407, SN5417 | 4.5  | 5   | 5.5  | V    |

|                                           | Supply voltage                 | SN7407, SN7417 | 4.75 | 5   | 5.25 | · V  |

| ٧ <sub>IH</sub>                           | High-level input voltage       |                | 2    |     |      | V    |

| ٧ <sub>IL</sub>                           | Low-level input voltage        |                |      |     | 8.0  | V    |

| V <sub>OH</sub> High-level output voltage | I Pale Level and and an Harry  | SN5407, SN7407 |      |     | 30   | V    |

|                                           | High-level output voltage      | SN5417, SN7417 |      |     | 15   | V    |

| I <sub>OL</sub> Low-level output current  | Level book and and an extended | SN5407, SN5417 |      |     | 30   | 4    |

|                                           | Low-level output current       | SN7407, SN7417 |      |     | 40   | mA   |

| T <sub>A</sub> Operating free-ai          |                                | SN5407, SN5417 | -55  |     | 125  | °C   |

|                                           | Operating free-air temperature | SN7407, SN7417 | 0    |     | 70   |      |

NOTE 4: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                  | TEST CONDITIONS†         |                                          |  | TYP <sup>‡</sup> | MAX  | UNIT |  |

|-----------------|------------------|--------------------------|------------------------------------------|--|------------------|------|------|--|

| VIK             | $V_{CC} = MIN,$  | I <sub>I</sub> = -12 mA  |                                          |  |                  | -1.5 | V    |  |

| lOH             | N/ AMAI          | V <sub>IH</sub> = 2 V    | V <sub>OH</sub> = 30 V (SN5407, SN7407)  |  |                  | 0.25 | ^    |  |

|                 | $V_{CC} = MIN,$  |                          | V <sub>OH</sub> = 15 V (SN5417, SN7417)  |  |                  | 0.25 | mA   |  |

| V <sub>OL</sub> |                  | V <sub>IL</sub> = 0.8 V  | I <sub>OL</sub> = 16 mA                  |  |                  | 0.4  |      |  |

|                 | $V_{CC} = MIN,$  |                          | I <sub>OL</sub> = 30 mA (SN5407, SN5417) |  |                  | 0.7  | ٧    |  |

|                 |                  |                          | I <sub>OL</sub> = 40 mA (SN7407, SN7417) |  |                  | 0.7  |      |  |

| lį              | $V_{CC} = MAX$ , | V <sub>I</sub> = 5.5 V   |                                          |  |                  | 1    | mA   |  |

| lН              | $V_{CC} = MAX$ , | $V_{IH} = 2.4 \text{ V}$ |                                          |  |                  | 40   | μΑ   |  |

| Iլլ             | $V_{CC} = MAX$ , | $V_{IL} = 0.4 V$         |                                          |  |                  | -1.6 | mA   |  |

| ICCH            | $V_{CC} = MAX$   |                          |                                          |  | 29               | 41   | mA   |  |

| ICCL            | $V_{CC} = MAX$   | _                        |                                          |  | 21               | 30   | mA   |  |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

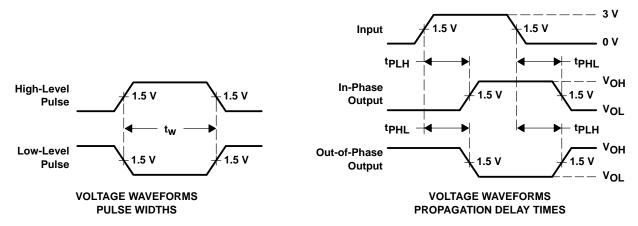

## switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |

|------------------|-----------------|----------------|------------------------------------|-----|-----|-----|------|

| t <sub>PLH</sub> | Α               | Y              | $R_L = 110 \Omega$ , $C_L = 15 pF$ |     | 6   | 10  |      |

| tPHL             |                 |                |                                    |     | 20  | 30  | ns   |

| <sup>t</sup> PLH | A               | V              | D: 450.0 C: 50.5                   |     |     | 15  |      |

| <sup>t</sup> PHL |                 | 1              | $R_L = 150 \Omega$ , $C_L = 50 pF$ |     |     | 26  | ns   |

<sup>&</sup>lt;sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

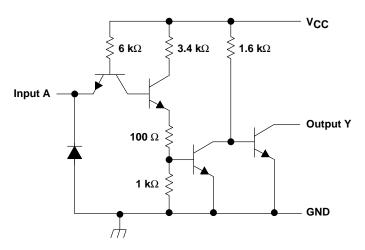

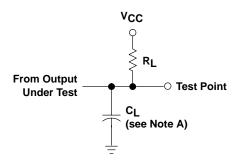

#### PARAMETER MEASUREMENT INFORMATION

**LOAD CIRCUIT**

NOTES: A. C<sub>I</sub> includes probe and jig capacitance.

- B. In the examples above, the phase relationships between inputs and outputs have been chosen arbitrarily.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_O = 50 \ \Omega$ ,  $t_f \leq 7 \ ns$ ,  $t_f \leq 7 \ ns$ .

- D. The outputs are measured one at a time, with one input transition per measurement.

Figure 1. Load Circuit and Voltage Waveforms