# PART 8 DISKS

# CHAPTER 11 RK8-E DISK DRIVE CONTROLLER

# SECTION 1 INTRODUCTION

# 11.1 PURPOSE

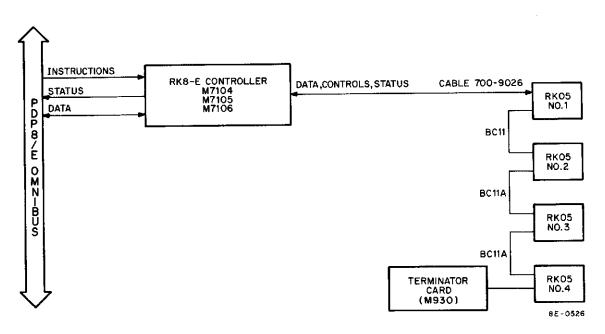

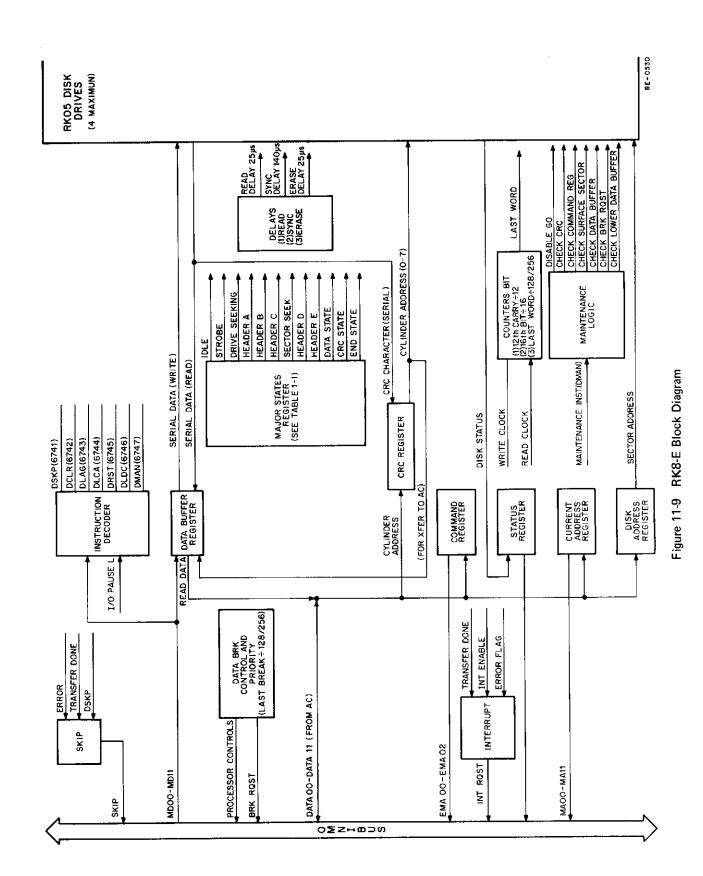

The RK8-E (Figure 11-1) provides the interface between the PDP-8/E OMNIBUS and the RK05 Disk Drive. As a part of this function the RK8-E

Figure 11-1 RK8-E Controller and RK05 Disk Drive System Block Diagram

- a. Decodes programmed IOT instructions.

- b. Accepts and stores current address, command, and extended memory address words.

- c. Selects the designated RK05 and starts the designated operation.

- d. Jointly (with the selected RK05) locates the disk address (track, sector, and surface).

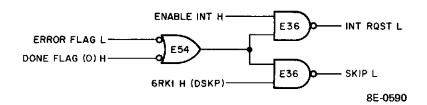

- e. Generates interrupts and skips for status checking operations.

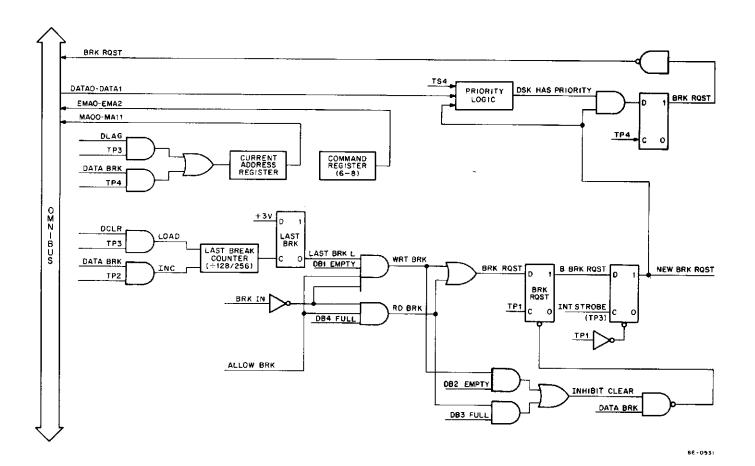

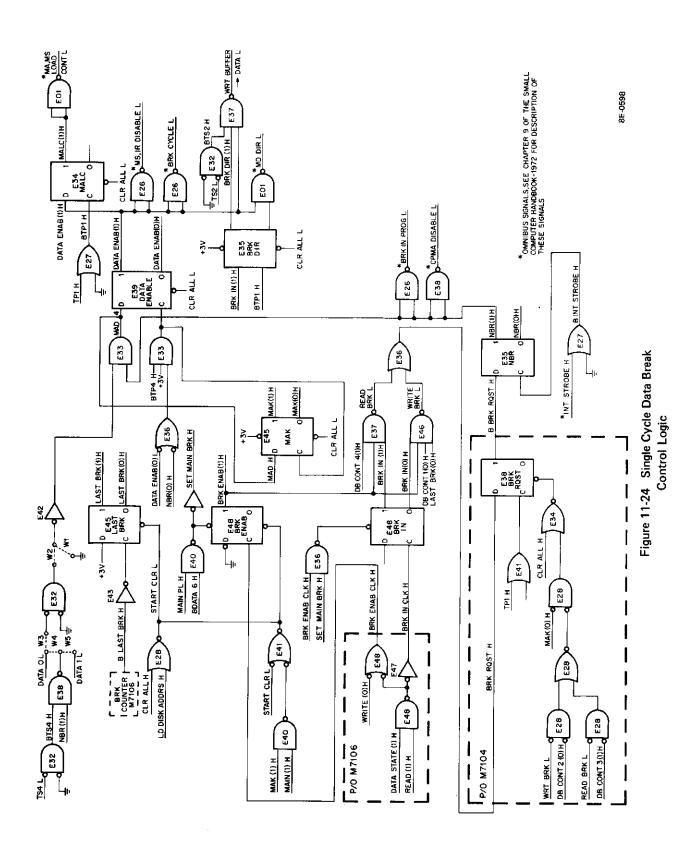

- f. Generates break requests to initiate single cycle data breaks (data transfers to or from memory).

- g. Buffers the input/output data and performs related conversions (serial to parallel and parallel to serial).

- h. Performs housekeeping chores for single cycle data break data transfers (i.e., increments Current Address Register and provides sequential memory addresses).

- i. Counts bits and words in a transfer to determine when to end a data transfer.

- i. Generates and checks CRC (parity) for each sector.

- k. Provides flags to indicate current conditions and error status.

- 1. Provides logic to aid in the maintenance of the RK8-E and RK05.

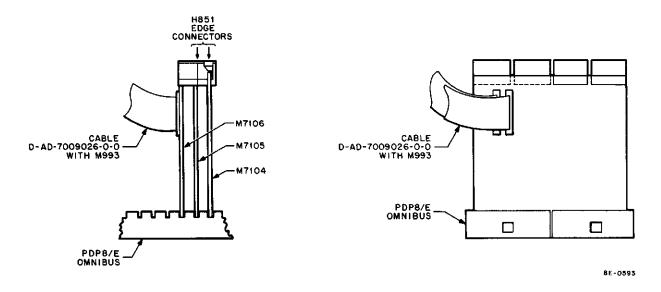

# 11.2 PHYSICAL DESCRIPTION

The RK8-E consists of the following quad modules, which are inserted into the OMNIBUS and used to control up to 4 (maximum) RK05 Disk Drives.

- M7104, RK8-E Data Buffer Register and Status Module

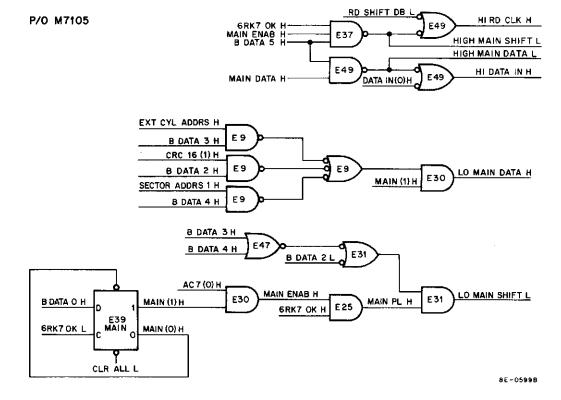

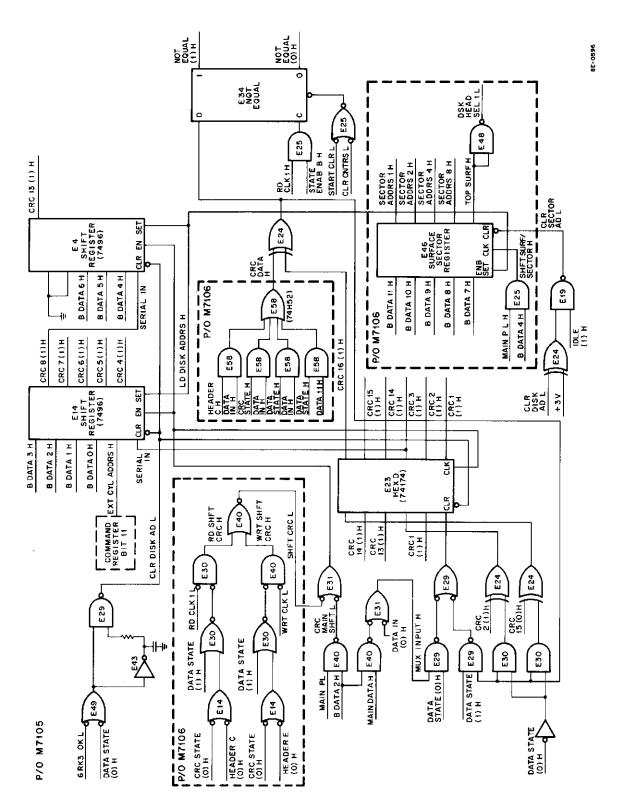

- M7105, RK8-E Major Registers Module

- M7106, RK8-E Control Module

The RK8-E modules are inserted into the OMNIBUS and connected together with H851 Top Connectors. The RK8-E is connected to the RK05 Disk Drives by a 7009026 cable.

# 11.2.1 RK05 Disk Drive

The RK05 Disk Drive contains the drive electronics and mechanism for accepting and releasing the disk, positioning the read/write heads, and reading and writing data from the RK8-E control. The drive contains a removable disk cartridge, control logic, and a power supply. No power is supplied to the RK05 by the RK8-E, and the RK05 supplies no power to the RK8-E. Table 11-1 lists the RK05 Disk Drive specifications.

# NOTE

The specifications in Table 11-1 apply to the RK05 when it is used with the RK8-E and a 16-sector cartridge. The RK05 may be used in other systems with other controllers and sector formats.

# 11.3 RECORDING METHODS AND FORMATS

This section describes the recording methods and the format used to write data on and read data from the RK05 Disk Drives.

Table 11-1

RK05 Disk Drive Specifications

| Characteristic              | Specification                             |

|-----------------------------|-------------------------------------------|

| Cylinder, Track, and Sector |                                           |

| Cylinder Density            | 200 CPI                                   |

| Cylinders/Drive             | 203                                       |

| Tracks/Cylinder             | 2                                         |

| Sectors/Track               | 16                                        |

| Sectors/Cylinder            | 32                                        |

| Bit Density and Storage     |                                           |

| Bit Density                 | 2200 BPI                                  |

| Bits/Cylinder               | 120,000                                   |

| Bits/Sector                 | 3750                                      |

| Bits/Drive                  | 24 million                                |

| Data Word Storage           |                                           |

| Words/Sector                | 400 <sub>8</sub> or 256 <sub>10</sub>     |

| Words/Track                 | 10,000 <sub>8</sub> or 4096 <sub>10</sub> |

| Words/Cylinder              | 20,000 or 8192 <sub>10</sub>              |

| Words/Disk                  | 1616K                                     |

| Transfer Rate               |                                           |

| Word Transfer               | 8.32 usec                                 |

| Bit Transfer Rate           | 1440 kHz                                  |

| Recording Method            | Double Frequency                          |

# 11.3.1 Double Frequency Recording Method

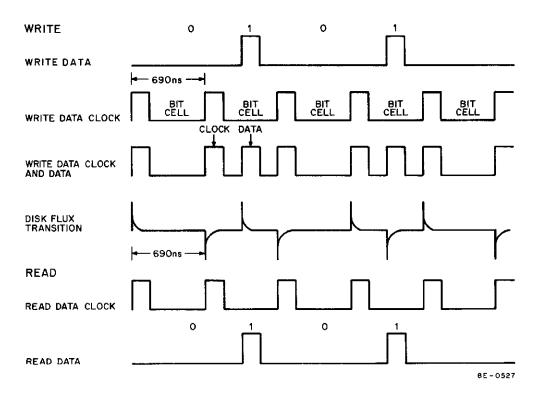

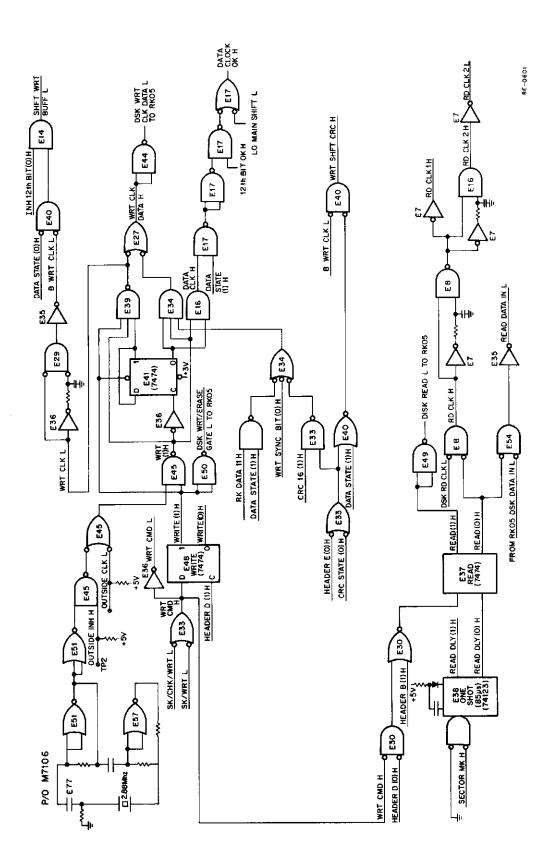

The RK8-E uses the double frequency recording method. During a write operation, the RK8-E control generates timing pulses called Write Data Clock pulses (Figure 11-2). The time between the pulses is called a bit cell (space for writing data). A pulse within the bit cell represents a data 1 and the absence of a pulse represents a data 0. The clock pulse and data (0 or 1) are sent to the drive as Write Data and Clock pulses. Each pulse is recorded on the disk as a flux transition. A pulse representing a data 1 and the clock pulses cause a change in direction of current flow through the write heads and thus a change in the magnetic flux on the surface of the disk. Zero data bits do not cause a change in current flow through the write head; thus, there is no change in the magnetic flux on the surface of the disk.

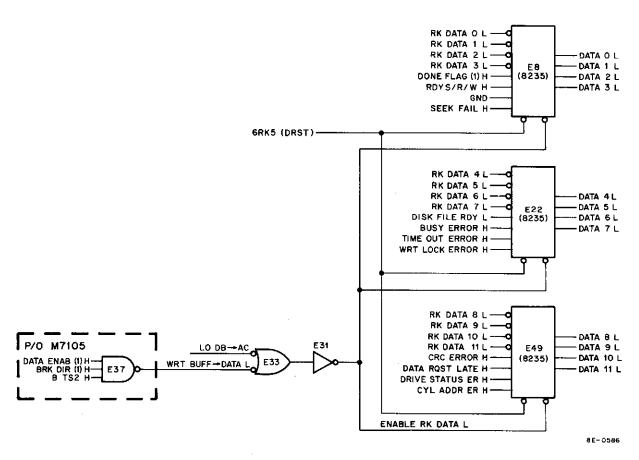

During a read operation, the drive electronics separates the bit cell flux transitions and the data flux transitions. The bit cell flux transitions are sent to the RK8-E as Read Data Clock pulses and the data transitions are sent as Read Data pulses (serial bits of data).

Figure 11-2 Double Frequency Recording Method

# 11.3.2 Disk Addressing

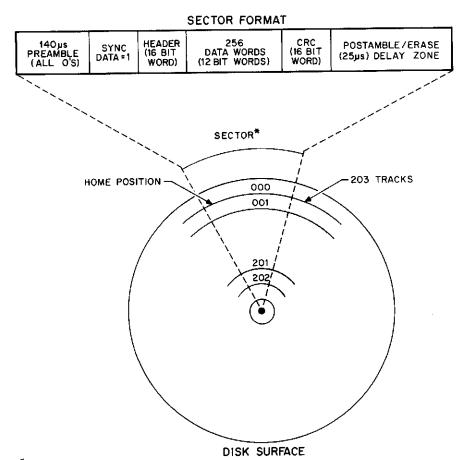

The surfaces of the RK05 Disk Cartridge are divided into 203 tracks and 16 sectors (Figure 11-3). Each surface has one read/write head.

A drive can be commanded to seek one of 203 cylinder addresses. The drive generates a signal and supplies it to the RK8-E when it is on the correct cylinder address. When the drive completes a seek, it is advisable to check the cylinder address to ensure the heads are positioned correctly.

The RK8-E can be commanded to read the cylinder address (HEADER) from the first cylinder it finds and check this against the cylinder address it previously sent to the disk drive. If the two addresses agree, the controller starts a data transfer; if they do not agree, an ERROR flag is set. The program must determine what to do about the ERROR flag.

A drive performing a seek can be deselected and another drive selected and commanded to seek; thus, overlapped seeks are possible.

#### 11.3.3 Sector Format

The sector format (Figure 11-3) consists of a 140  $\mu$ s PREAMBLE of zero data bits (time pulses only), a SYNC bit (data bit = 1), a 16-bit HEADER word containing the cylinder address, 256 12-bit data words, a 16-bit Cyclic Redundancy Check (CRC) character, and a 25  $\mu$ s POSTAMBLE (erase delay zone).

11.3.3.1 HEADER Word — The HEADER is a 16-bit word containing 5 zero bits and a 8-bit cylinder address followed by 3 zero bits.

\* SECTOR ADDRESS 08 TO 178 ON UPPER OR O SURFACE SECTOR ADDRESS 208 TO 378 ON LOWER OR 1 SURFACE TOTAL OF 32 SECTORS (16 ON TOP AND 16 ON BOTTOM)

8E-05:

Figure 11-3 Disk Format

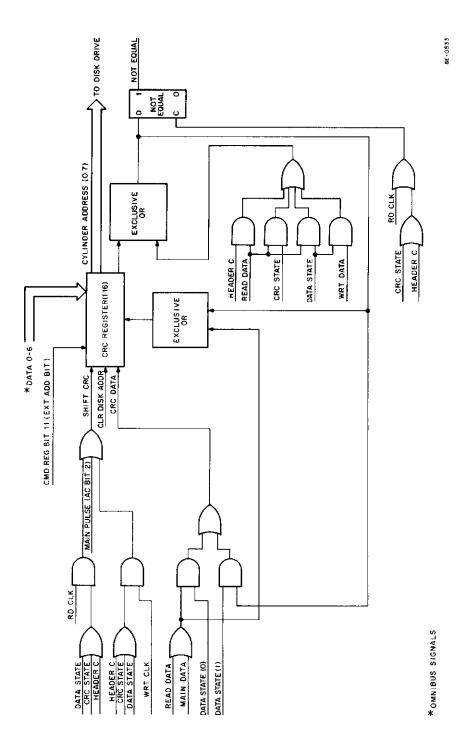

11.3.3.2 CRC Character — Data is recorded on the RK05 in blocks of 256 12-bit words (serial data); thus, each block contains 3072 bits of data recorded in a single string, with no separations to indicate word boundaries or record error checking bits.

A long string of data bits is susceptible to single bit errors caused by dropins, dropouts, or burst errors. Burst errors are caused by unwanted physical motion of the read/write heads. The RK8-E generates a Cyclic Redundancy Check (CRC) character to check for these errors. The CRC is a block check character that is calculated by the RK8-E during a read or write operation. The CRC character calculated during a write operation is written immediately following the data (Figure 11-3) and becomes part of the data string. The process used to calculate the block check word is such that if no errors occur, the CRC word calculated while reading data is identical to that calculated during a write operation.

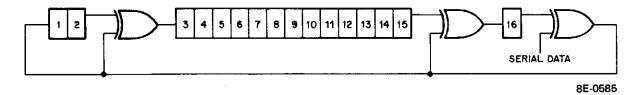

To calculate a CRC word, the data block is treated as a number 3072 bits long which is divided by a polynominal  $(X^{16} + X^{15} + X^2 + 1)$ . The hardware required to do this is a shift register with Exclusive OR gating (division being shift and subtract).

A maintenance instruction allows the program to read the CRC character written on the disk or the CRC character read from the disk.

11.3.3.3 Formatting A Cartridge — A disk cartridge is "formatted" when the cylinder address of a sector is written in the HEADER word of each sector. A special bit in the Command Register allows the program to write HEADER words in each sector (format). The program need only set the bit and write something in each sector. The RK8-E control writes the cylinder address automatically in the HEADER area (Figure 11-3) of each sector. The formatting program writes coded information in the data region of each sector and reads it back to verify that the disk is formatted correctly.

During a normal read or write operation, the disk seeks a cylinder specified by the RK8-E and reads the HEADER word of the first sector it finds after the seek is complete. This HEADER word is compared with the cylinder address specified by the RK8-E to ensure the correct cylinder has been found. The control then waits until the sector containing the address specified by the program passes under the read/write heads before reading or writing data.

11.3.3.4 Write Protect — WRITE PROTECT is turned on at the RK05 Disk Drive or by a bit in the Command Register when it is loaded by the program. WRITE PROTECT must be turned off by pressing a manual control (WT PROT) on each disk drive. If the program attempts to write on a disk that is write protected, the write operation is inhibited and an error condition is produced. WRITE PROTECT may be turned on manually at the RK05 by pressing the WT PROT switch.

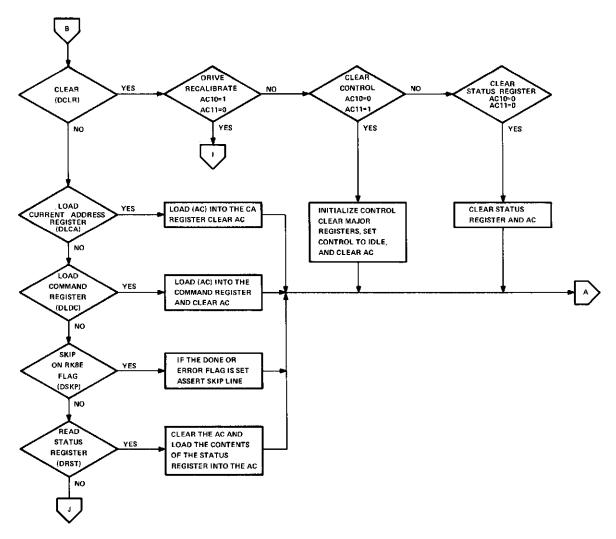

# 11.4 MAJOR REGISTERS

The major registers of the RK8-E are in two broad categories: those that are loaded or read by user software and those that are transparent to user software. The first category includes the Command Register, Current Address Register, Disk Address Register and Status Register. The second category includes the 4-word Data Buffer Register, the CRC Register, Major State Register, Modulo 12- and Modulo 16-bit counters, and the Modulo 128- or 256-Word Count Register.

The major registers must be loaded from the AC by IOT instructions in the correct sequence before they perform any control function. The individual flip-flops in the registers are set by a 1 (true) and cleared by a 0 (false) bit from the AC. Refer to Section 3 for a list of IOT instructions and a detailed discussion of the contents of each major register.

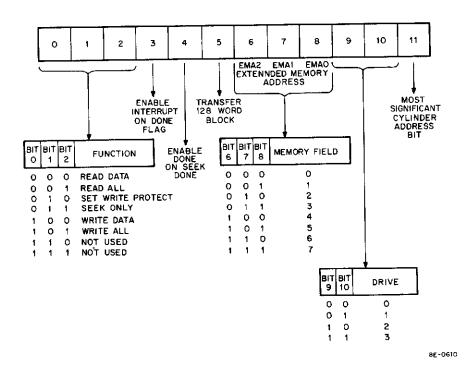

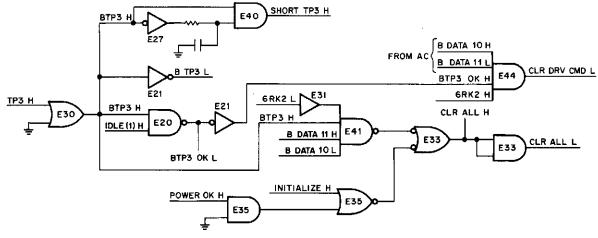

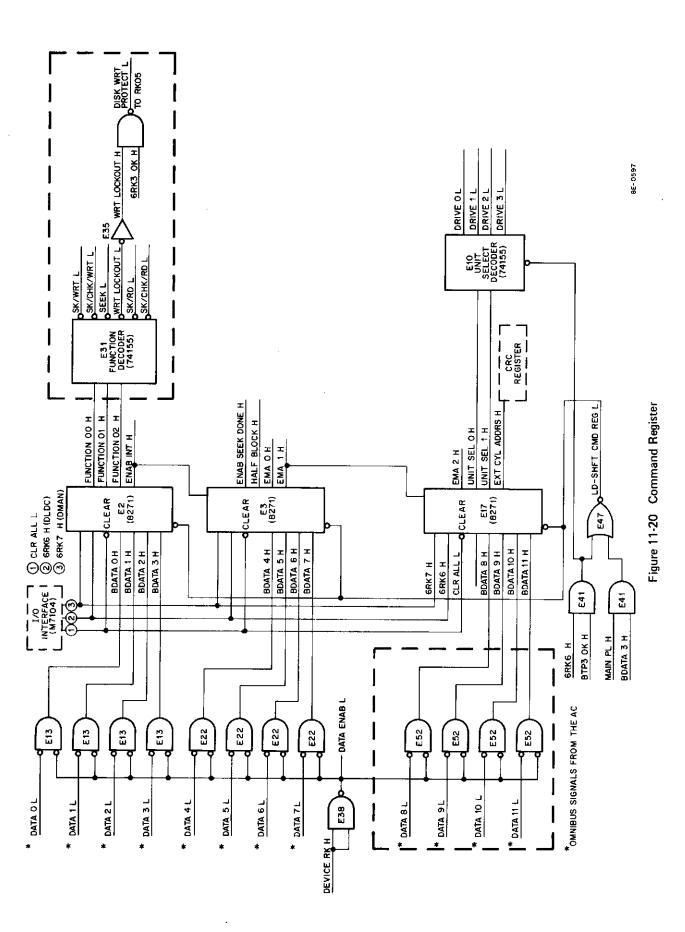

# 11.4.1 Command Register

The Command Register (Figure 11-4) is loaded from the AC by IOT 6746. This IOT also clears the AC and the Status Register.

# 11.4.2 Current Address Register

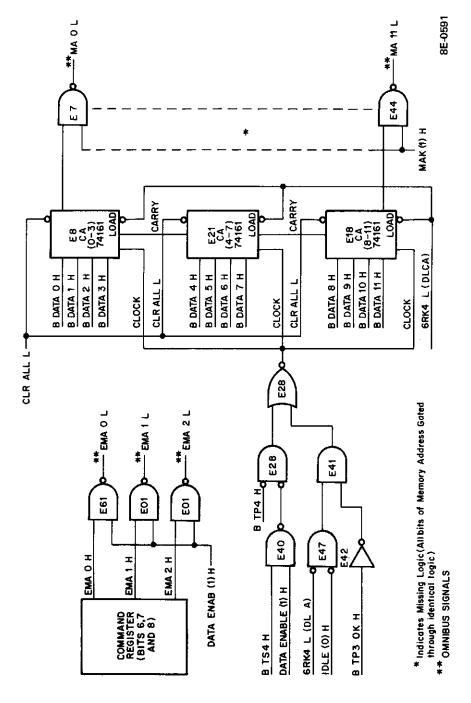

The Current Address Register is a 12-bit register loaded from the AC with IOT 6744, which also clears the AC. This register and 3 bits of the Command Register (Figure 11-4) are combined to make up a 15-bit Memory Address Register. The contents of the CA Register and the 3 bits in the Command Register are applied to the OMNIBUS to select a memory location during a data transfer. The CA Register is incremented before each data transfer to select the next sequential memory location. The EMA bits in the Command Register are not incremented, and these bits must be changed by the program to select new memory fields. If the CA Register is incremented past the last memory location in a field, it will wrap around in the same field. The data is stored in location 000 and starts incrementing through the field again.

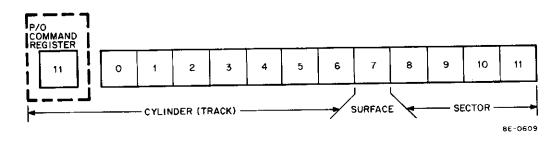

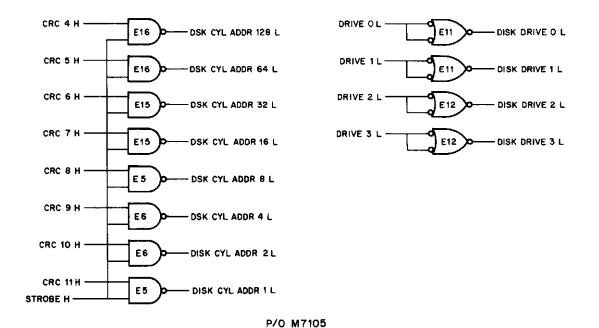

# 11.4.3 Disk Address Register

The Disk Address Register is loaded from the AC by IOT 6743, which also clears the AC and enables the contents of the Command Register to be applied to the control logic.

Figure 11-4 Contents of Command Register

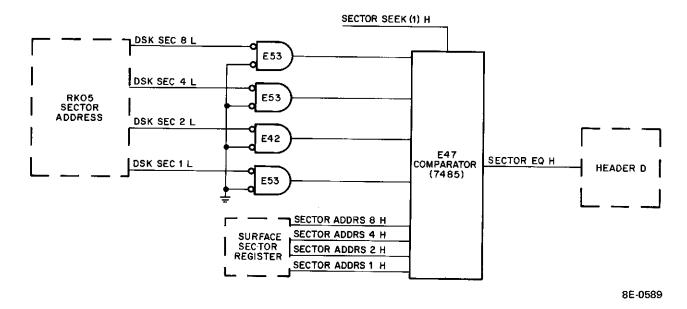

The Disk Address Register selects a sector to be used in a data transfer. To select an individual sector, the following must be selected (Figure 11-5).

Figure 11-5 Disk Address Register

- a. 1 of 203 cylinders

- b. 1 of 2 surfaces

- c. 1 of 16 sectors

The Disk Address Register and bit 11 in the Command Register (Figure 11-4) are combined to select a cylinder, surface, and sector. The largest valid address is  $14537_8$  (cylinder address  $202_{10}$ ).

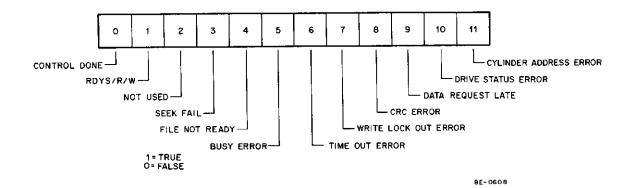

# 11.4.4 Status Register

The Status Register (Figure 11-6) contains all the information needed for the program to evaluate the operation of the RK8-E and RK05.

Figure 11-6 Contents of Status Register

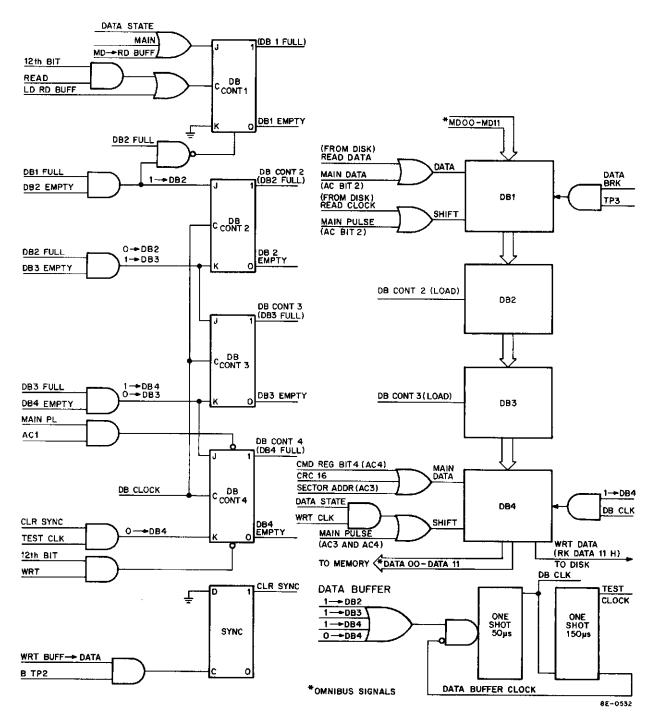

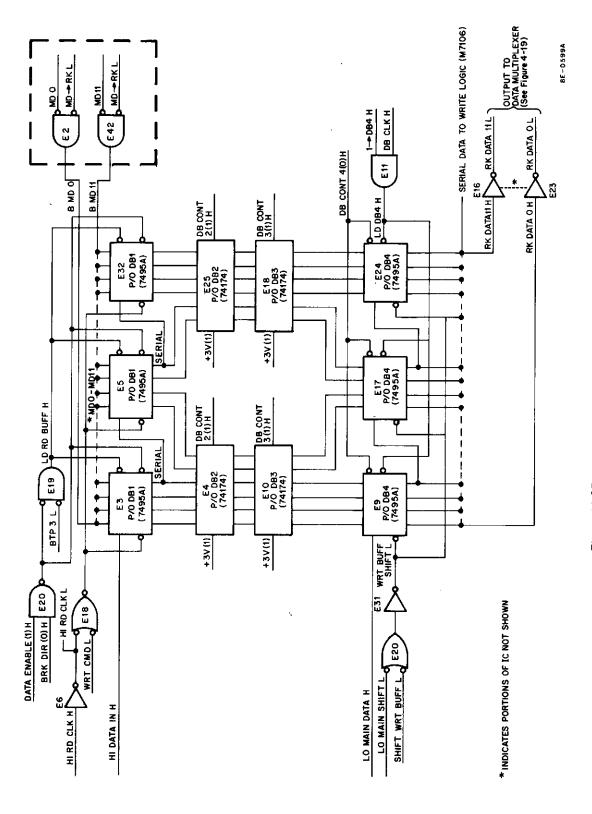

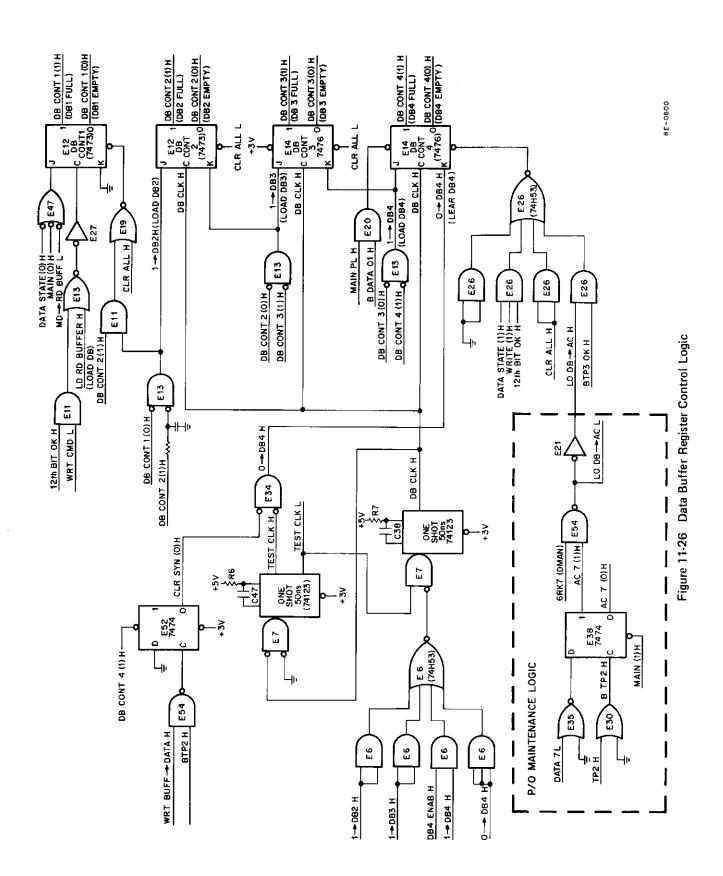

#### 11.4.5 Data Buffer Register

All data transfers between memory and a drive pass through the 4-word Data Buffer Register (DB1 through DB4). This 4-word register increases the latency of the RK8-E control from 6.2  $\mu$ s with a single serial register and one data buffer to 22.5  $\mu$ s with 4 Data Buffer Registers. Latency is defined as the maximum time the RK8-E control waits for access to the computer memory before data is lost. The numbers given above are for a memory cycle time of 1.2  $\mu$ s.

During a read operation, Data Buffer 1 accepts the serial data from the drive and transfers a complete word to the last unused buffer, which is eventually removed from Data Buffer 4 and transferred to computer memory. On a write, data from computer memory enters Data Buffer 1 in parallel mode, transfers to the last unused buffer, and is shifted out to the drive as a 12-bit serial word from Data Buffer 4.

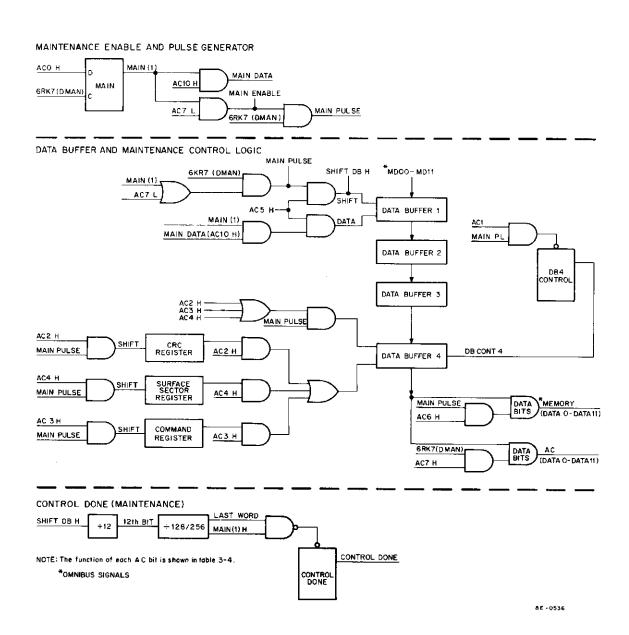

During maintenance operations, the contents of the CRC Register, Command Register, and the Surface/Sector Register (disk address) are shifted into Data Buffer 4 by the maintenance IOT for transfer to the AC or memory.

# 11.4.6 CRC Register

The CRC Register is a 16-bit register used to calculate the CRC character that is written onto the disk after the last data word. During a read, it calculates the CRC of the read data and does a bit-by-bit comparison with the CRC word read from the disk. It also contains the cylinder address loaded from the AC by the Load Address and GO instructions. The CRC Register does a bit-by-bit comparison of the HEADER word to confirm that the selected drive has found the correct cylinder address.

#### NOTE

The CRC Register and the Disk Address Register are physically the same logic with multipurposes.

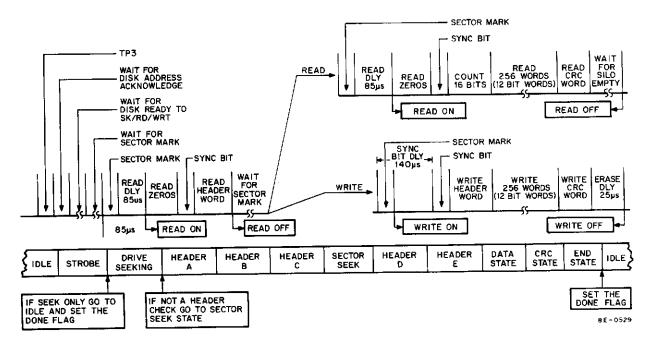

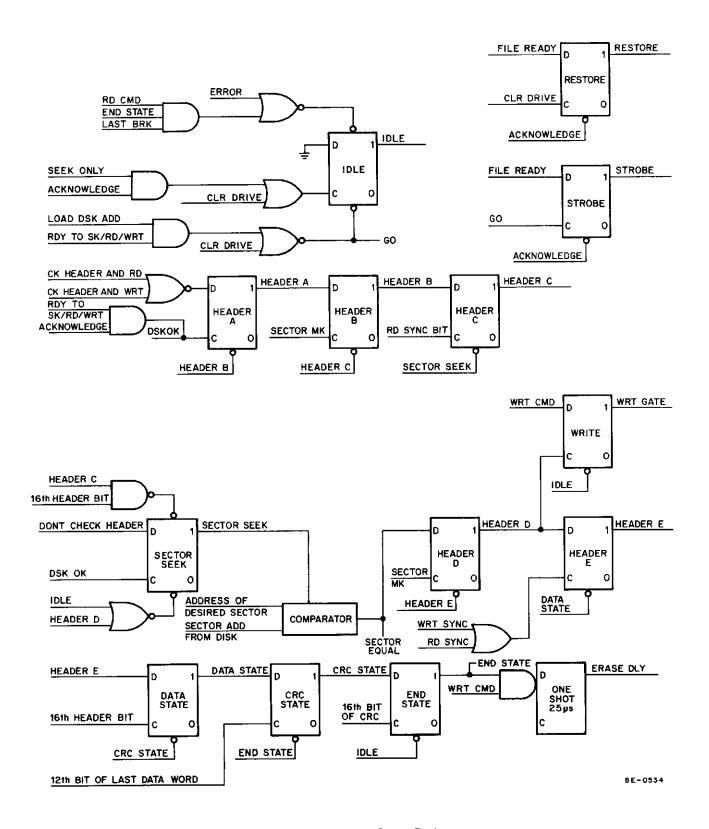

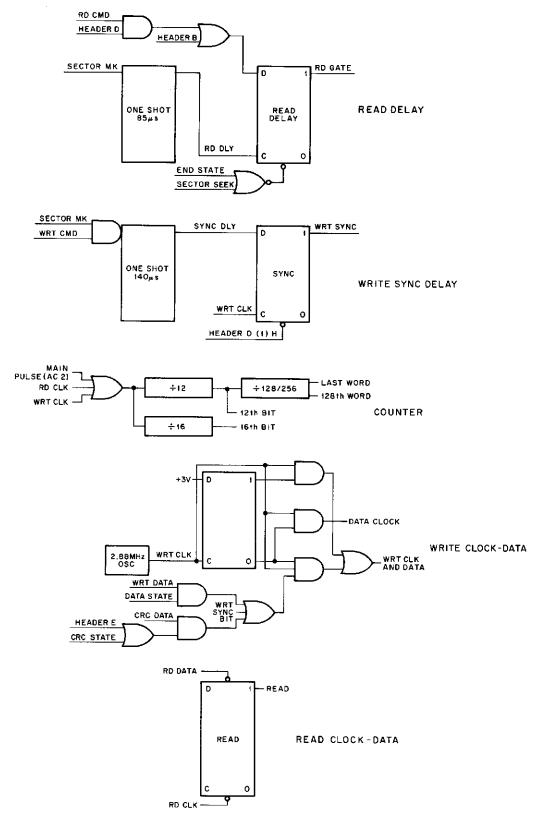

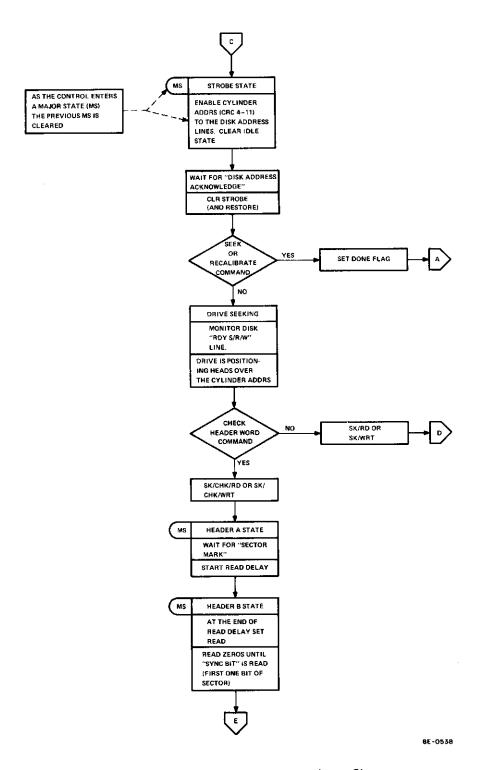

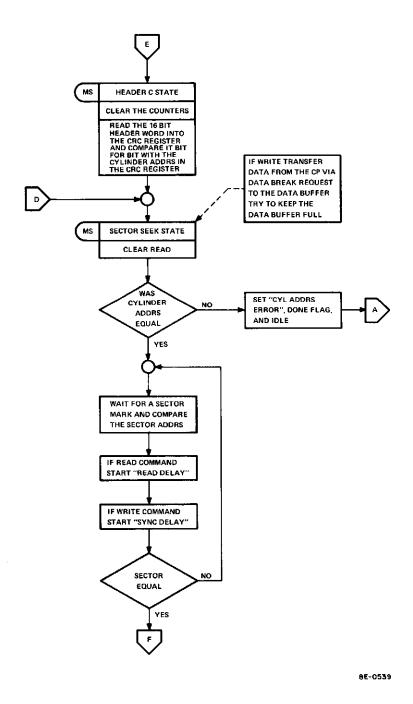

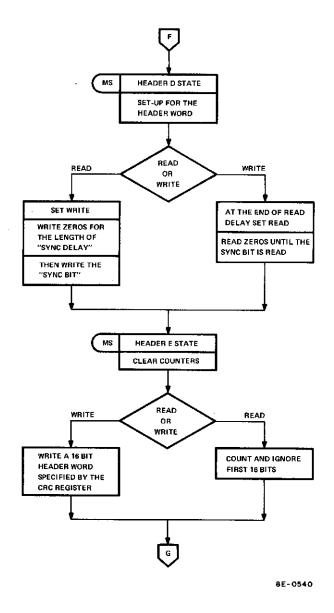

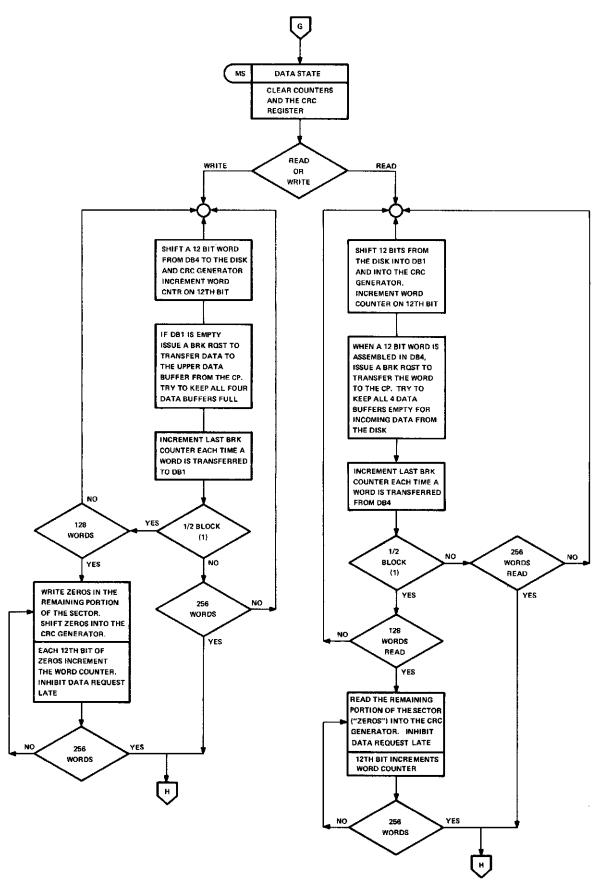

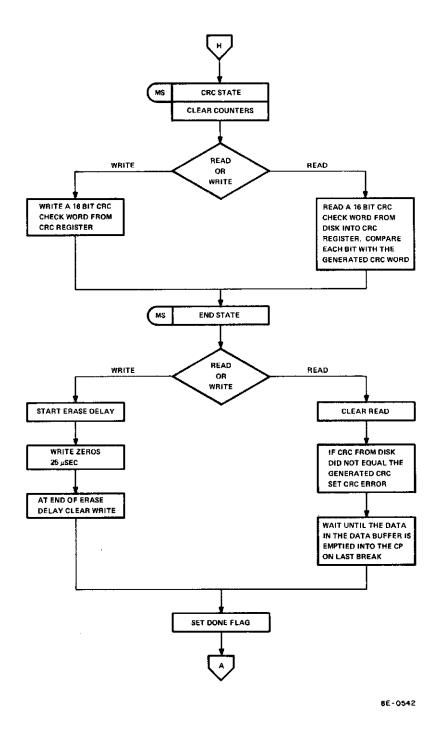

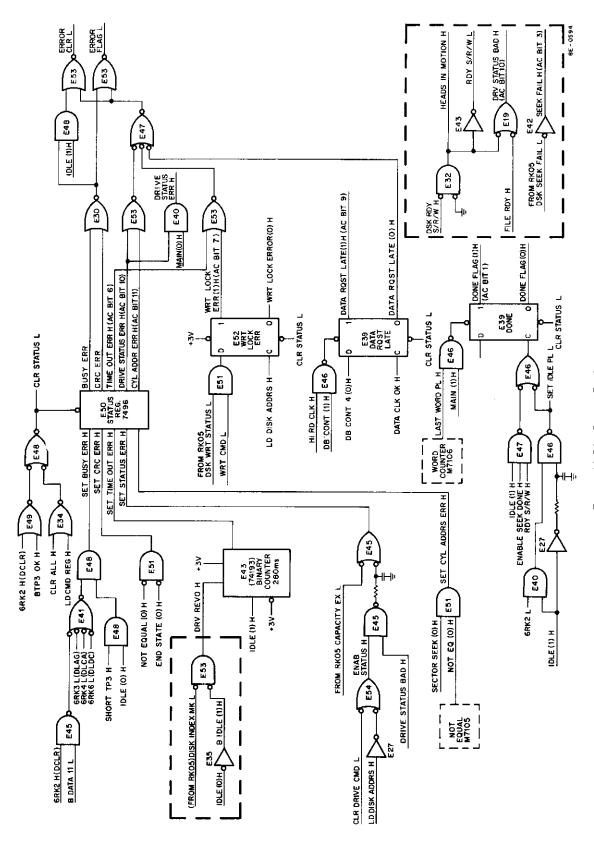

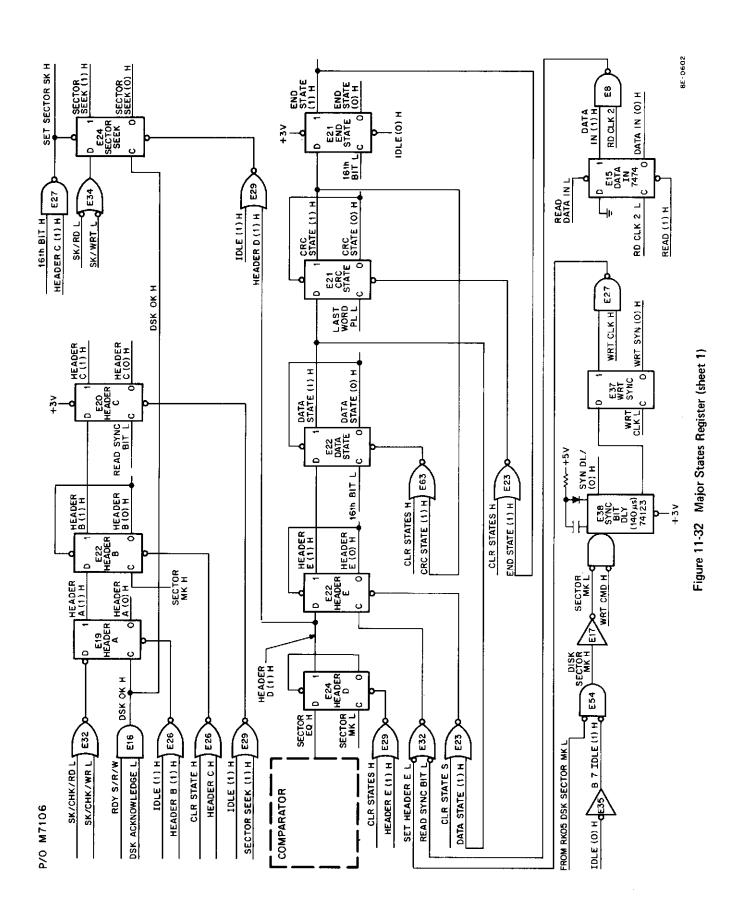

# 11.4.7 Major State Register

The Major State Register (Table 11-2 and Figure 11-7) is the control sequencer of the RK8-E; with its associated gating, this register performs the major portion of the control functions of the RK8-E. The Major State Register is incremented from one state to another, and its decoded outputs gate signals to or from the disk and perform housekeeping tasks such as determining whether the control is in the HEADER region, data region or CRC region of the disk format.

Table 11-2

| Major | States |

|-------|--------|

|-------|--------|

|                  | inajor occess                                                                                                                                                                                                                                                                                                                         |      | Operation     |      |      |   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|------|---|

| Major<br>State   | Function                                                                                                                                                                                                                                                                                                                              | Seek | Seek<br>Check | Seek | Seek |   |

| IDLE             | Control is not busy until the GO Command (DLAG) is issued and the contents of the AC are loaded into the CRC. The CRC Register contains the Cylinder/Surface Address (Disk Address)                                                                                                                                                   |      | X             | X    | ×    | X |

| STROBE           | Strobe the Cylinder Address from the CRC Register to the Disk Drive and wait for the Disk Drive ADDRESS ACKNOWLEDGE signal.                                                                                                                                                                                                           | x    | X             | х    | X    | × |

| DRIVE<br>SEEKING | Wait for DISK READY to SEEK, READ, or WRITE from the Disk Drive to indicate the heads are positioned over the Cylinder Address.                                                                                                                                                                                                       |      | ×             | X    | X    | × |

| HEADER A         | Wait for the first Sector Mark, then start READ DELAY.                                                                                                                                                                                                                                                                                |      | ×             | ×    |      |   |

| HEADER B         | At the end of READ DELAY turn the READ flip-flop on. Zeros are read until the SYNC bit is read at the beginning of a block of data.                                                                                                                                                                                                   |      | ×             | x    |      |   |

| HEADER C         | Read the 16-bit HEADER word and compare it with the cylinder address in the CRC Register.                                                                                                                                                                                                                                             |      | ×             | X    |      |   |

| SECTOR<br>SEEK   | If the HEADER word does not equal the cylinder address set CYLINDER ADDRESS ERROR and go to IDLE state. At each sector mark compare the sector address with the Disk Sector Address lines If the addresses are equal go to the next state. If this is a write operation transfer data from the processor to the Data Buffer Register. |      | X             | X    | X    | X |

# Table 11-2 (Cont)

Major States

|                       | iviajor States                                                                                                                                                                                                                                                                                  |      | 0    | peratio       | n    |   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------------|------|---|

| Major<br>State        | Function                                                                                                                                                                                                                                                                                        | Seek | Seek | Seek<br>Check | Seek |   |

| HEADER D<br>(Read)    | At the beginning of the sector start READ DELAY (85 µs). At the end of READ DELAY set the READ flip-flop. Note zeros are read until the SYNC bit is read.                                                                                                                                       |      | х    |               | X    |   |

| HEADER D<br>(Write)   | At the beginning of the sector start SYNC DELAY. Zeros are written during SYNC DELAY time and after SYNC DELAY times OUT (140 µs) a one SYNC bit is written.                                                                                                                                    |      |      | ×             |      | × |

| HEADER E<br>(Read)    | Count and ignore the first 16 bits.                                                                                                                                                                                                                                                             |      | Х    |               | x    |   |

| HEADER E<br>(Write)   | Write the HEADER word contained in the CRC Register.                                                                                                                                                                                                                                            |      |      | Х             |      | × |

| DATA STATE<br>(Read)  | Read 256 12-bit data words and a 16-bit CRC character from the Disk and compute a CRC. The 12 bit data words are transferred to the Data Buffer Register and the controller tries to keep the Data Buffer Register empty by transferring data to the processor via the single cycle data break. |      | ×    |               | x    |   |

| DATA STATE<br>(Write) | Write 256 data words on the Disk Drive. The Data words are transferred.from the processor via the Single Cycle Data Break.                                                                                                                                                                      |      |      | х             |      | × |

| CRC STATE<br>(Read)   | Read the CRC from the Disk Drive and compare it with the CRC computed by the controller.                                                                                                                                                                                                        |      | х    |               | ×    | , |

| CRC STATE<br>(Write)  | Write the computed CRC on the disk after 256 data words have been written.                                                                                                                                                                                                                      |      |      | Х             |      | × |

Table 11-2 (Cont)

Major States

|                      |                                                                                                                                                                                                                                         |      | Operation |                        |   |   |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|------------------------|---|---|

| Major<br>State       | Function                                                                                                                                                                                                                                | Seek |           | Seek<br>Check<br>Write |   |   |

| END STATE<br>(Read)  | If the CRC character read from the Disk Drive does not equal the computed CRC, set the CRC ERROR flag and clear Read. When the Data Buffer Registers are transferred into processor memory, set the DONE flag and go to the IDLE state. |      | ×         |                        | × |   |

| END STATE<br>(Write) | Start ERASE DELAY and Write zeros. At the end of ERASE DELAY (25 µs) clear WRITE, set the DONE flag and go to the IDLE state.                                                                                                           |      |           | ×                      |   | X |

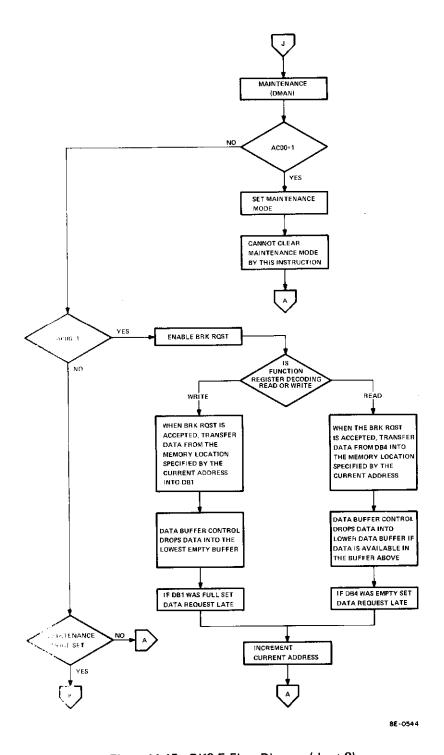

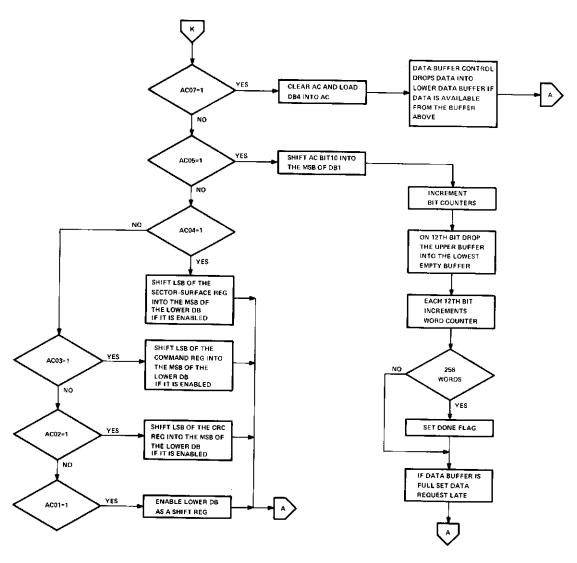

Figure 11-7 Read and Write Flow Diagram

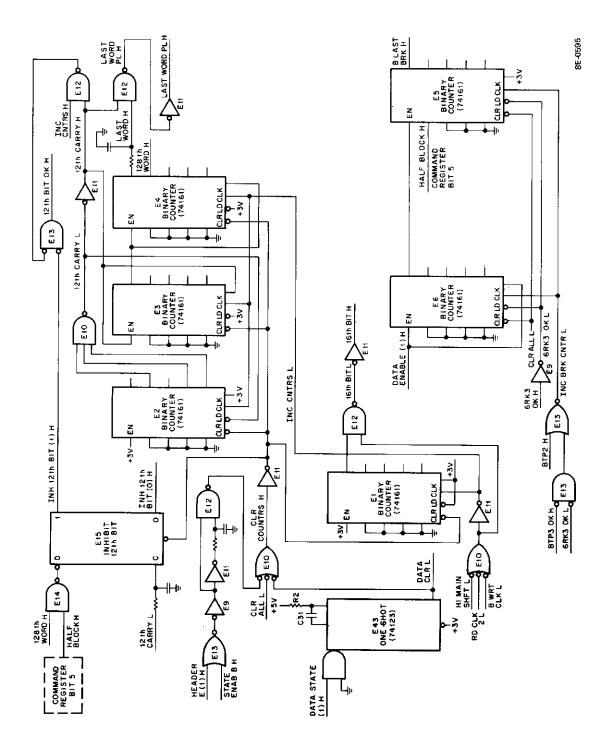

# 11.4.8 Bit Counters

The Modulo 12-bit counter determines PDP-8/E data word boundaries. The Modulo 16-bit counter determines where the HEADER and CRC character are, so that the control knows when to check the HEADER and CRC characters.

# 11.4.9 128- or 256-Word Counter

This register counts the output of the 12-bit counter to determine when the correct number of data words (normally 256 words) have been transferred to or from the disk. When the half block bit is set in the Command Register, the 128th word stops the data transfer instead of the usual 256th word.

# 11.5 COMPANION DOCUMENTS

The following is a list of companion documents needed to operate and maintain the RK8-E.

- a. PDP-8/E, PDP-8/F, and PDP-8/M Small Computer Handbook DEC 1973.

- b. PDP-8/E Maintenance Manual, Volumes I and II.

- c. Introduction to Programming DEC 1973 Volumes I and II.

- d. DEC Engineering Drawings, M7104-0-1, M7105-0-1, and M7106-0-1.

- e. RK05 Disk Drive Maintenance Manual (DEC-00-RK05-DA).

# 11.5.1 Software

The following programs and associated documents are used in the maintenance of the RK8-E.

- a. RK8-E Diskless Control Diagnostic, MAINDEC-08-DHRKA-A-PB or D

- b. RK8-E Drive Control Diagnostic, MAINDEC-08-DHRKB-A-PB or D

- c. RK8-E Disk Formatter, MAINDEC-08-DHRKD-A-PB or D

- d. RK8-E Data Reliability Test, MAINDEC-08-DHRKC-A-PB or D

#### NOTE

The MAINDEC number is followed by PB for papertape and D for Document, i.e., MAINDEC-08-DHRKA-A-PB for binary tape and MAINDEC-08-DHRKA-A-D for the diagnostic document. The latest revision of these documents and programs should be used to run RK8-E diagnostics.

# SECTION 2 SITE PREPARATION, INSTALLATION, AND ACCEPTANCE TEST

The RK8-E is installed on site by DEC Field Service personnel. The customer should not attempt to unpack, inspect, install, checkout, or service the equipment.

# 11.6 SITE PREPARATION

Adequate site planning and preparation simplifies the installation process and results in a more efficient and more reliable RK8-E installation. DEC Sales Engineers or Field Service Engineers are available for counseling and consultation with the user regarding the installation.

Site planning should include a list of the actual components to be used in the installation. This list should include such items as storage cabinets, Teletype supplies, work tables, etc.

Primary requirements for installation of the RK8-E are:

- A Teletype, Programmer's Console, and at least 4K of read/write memory must be available to run the RK8-E diagnostics.

- b. Adequate space and power must be supplied for the RK05 Disk Drives (refer to Chapter 10 of the RK05 Disk Drive Maintenance Manual for power and space requirements).

#### NOTE

# The RK8-E receives +5V, 3A of power from the OMNIBUS.

- c. RK8-E diagnostics and documents must be available to checkout the RK8-E and RK05 (Paragraph 11.5).

- d. Software to format RK05 disk cartridges must be available (Paragraph 11.5).

# 11.7 INSTALLATION

Perform the following steps to install the RK8-E:

| Step | Procedure                                                                                                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Unpack and inspect RK05, using the RK05 Disk Drive Maintenance Manual, Volume 2, Paragraph 2.1, RK05 Field Installation and Acceptance Procedure.                                                                     |

| 2    | Using the inventory list shipped with the equipment, verify all items have been received.                                                                                                                             |

| 3    | Ensure that PDP-8/E power is turned off.                                                                                                                                                                              |

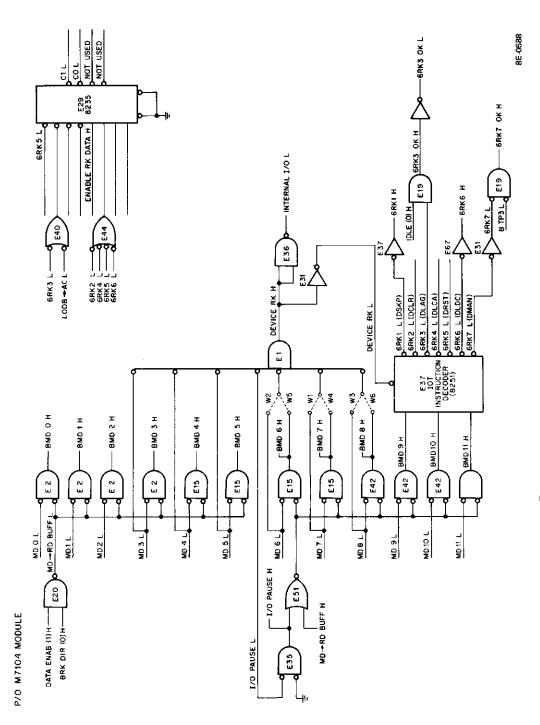

| 4    | Ensure correct jumpers are installed to select the device code assigned to this RK8-E. The M7104 is normally shipped with the 674X device code selected, but 675X through 677X device codes may be used (Table 11-3). |

| 5    | Install jumpers to select priority assigned to this RK8-E (Table 11-4).                                                                                                                                               |

| 6    | Connect the 7009026 cable to the Berg connector on the M7106 module.                                                                                                                                                  |

| 7    | Insert the RK8-E modules into the OMNIBUS (Figure 11-8), Refer to Table 11-5 in Volume I of the <i>PDP-8/E Maintenance Manual</i> for module installation priority.                                                   |

| 8    | Install H851 Top Connectors between the modules (Figure 11-8).                                                                                                                                                        |

# 11.8 ACCEPTANCE TEST

The following diagnostics must be run in the order shown and the specified number of passes to check the RK8-E. (Refer to the diagnostic document for instructions to run the diagnostic).

- a. RK8-E Diskless Control Diagnostic, MAINDEC-08-DHRKA-A-PB (2 passes)

- b. RK8-E Drive Control Diagnostic, MAINDEC-08-DHRKB-A-PB (1 pass)

- c. RK8-E Formatter, MAINDEC-08-DHRKD-A-PB (1 pass)

- d. RK8-E Data Reliability Test, MAINDEC-08-DHRKC-A-PB (1 pass)

Table 11-3

Device Select Jumper Installation

| Octal Code | Install following Jumpers on M7104 Module |

|------------|-------------------------------------------|

| 674X       | W2                                        |

|            | W4                                        |

|            | W6                                        |

| 675X       | W2                                        |

|            | W4                                        |

|            | W3                                        |

| 676X       | W2                                        |

|            | W1                                        |

|            | W6                                        |

| 677X       | W2                                        |

|            | W1                                        |

|            | W3                                        |

Table 11-4

RK8-E Priority Selection

| Priority             | Install Jumpers |

|----------------------|-----------------|

| Priority 0 (highest) | W1 and W4       |

| Priority 1           | W2, W3, and W5  |

Figure 11-8 RK8-E Module Installation

# 11.9 RK8-E INTERFACE

One 7009026 cable is used to connect the RK8-E controller to the first RK05 Disk Drive (four maximum). Note that the RK8-E is connected to only one drive and the input to and output from the RK05 are daisy-chained to the other three disks (the connectors on all four disk drives are connected in parallel by BC11A cables). The 7009026 cable is connected from two Berg connectors on the M7106 module to slot A07, A08, B07, or B08 on RK05 Disk Drive located closest to the RK8-E (Tables 11-5 and 11-6). The RK8-E modules on the OMNIBUS are tied together by H851 Top Connectors. The signals of the pins of the top connectors are shown in Tables 11-7 through 11-10. These tables give the origin of signals on the top connectors for troubleshooting and signal monitoring.

An M930 Terminator Card must be installed in the unused interface slot of the last RK05 Disk Drive.

Table 11-5

RK8-E--RK05 Interface Cable (P2)

| Connector J2<br>on RK8-E<br>Pin No. | Signal            | Description                                                                   |

|-------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Α                                   | GND               |                                                                               |

| В                                   |                   |                                                                               |

| С                                   | DSK CAP EX L      | The address sent to the selected disk drive was greater than 3128. (low=true) |

| E                                   | DSK SEEK FAIL     | Disk failed to seek the address specified                                     |

| F                                   | GND               |                                                                               |

| н                                   | DSK ACKNOWLEDGE L | Disk has received and acknowledged the disk address                           |

| J                                   | GND               |                                                                               |

| K                                   | DSK SEC 2 L       | Disk sector address bit 1 (low=1)                                             |

| L                                   | GND               |                                                                               |

| М                                   | DSK DRIVE 3 L     | Select disk drive 3 (low=true)                                                |

| N                                   | GND               |                                                                               |

| Р                                   | DSK RESTORE L     | Recalibrate the selected disk drive (low=true)                                |

| R                                   | GND               |                                                                               |

| S                                   | DSK DRIVE 2 L     | Select disk drive 2 (low=true)                                                |

| Т                                   | GND               |                                                                               |

| U                                   | DSK CYL ADD 4 L   | Disk cylinder address bit 2 (low=1)                                           |

| v                                   | GND               |                                                                               |

# Table 11-5 (Cont) RK8-E—RK05 Interface Cable (P2)

| Connector J2<br>on RK8-E<br>Pin No. | Signal                | Description                                       |

|-------------------------------------|-----------------------|---------------------------------------------------|

| W                                   | DSK DRIVE 1 L         | Select disk drive 1 (low=true)                    |

| ×                                   | GND                   |                                                   |

| Y                                   | DSK CYL ADD 1 L       | Disk cylinder address bit 0 (low=1)               |

| Z                                   | GND                   |                                                   |

| AA                                  | DSK DRIVE 0 L         | Select disk drive 0 (low=true)                    |

| ВВ                                  | GND                   |                                                   |

| cc                                  | DSK CYL ADD 32 L      | Disk cylinder address bit 5 (low=1)               |

| DD                                  | GND                   |                                                   |

| EE                                  | DSK RDY S/R/W L       | Selected disk drive ready to read, write, or seek |

| FF                                  | GND                   |                                                   |

| нн                                  | DSK CYL ADD 128 L     | Disk cylinder address bit 7 (low=1)               |

| ມ                                   | GND                   |                                                   |

| KK                                  | DSK WRT CLK<br>DATA L | Disk write clock data (low=true)                  |

| LL                                  | GND                   |                                                   |

| мм                                  | DSK CYL ADD 16 L      | Disk cylinder address bit 4 (low=1)               |

| NN                                  | GND                   |                                                   |

| PP                                  | DSK CYL ADD 64 L      | Disk cylinder address 6 (low=1)                   |

| RR                                  | GND                   |                                                   |

| SS                                  | DSK CYL ADD 2 L       | Disk cylinder address bit 1 (low=1)               |

| π                                   | GND                   |                                                   |

| υυ                                  | DSK CYL ADD 8 L       | Disk cylinder address bit 3 (low=1)               |

| vv                                  | GND                   |                                                   |

Table 11-6

RK8-E-RK05 Interface Cable (P1)

| Connector J1<br>on RK8-E<br>Pin No. | Signal            | Description                                                                                          |

|-------------------------------------|-------------------|------------------------------------------------------------------------------------------------------|

| Α                                   | Not used          |                                                                                                      |

| В                                   | Not used          |                                                                                                      |

| С                                   | GND               |                                                                                                      |

| D                                   | DSK DATA IN L     | Serial Data from the disk drive                                                                      |

| E                                   | GND               |                                                                                                      |

| F                                   | DSK RD CLK L      | Clock pulses from the selected disk drive during a read operation                                    |

| н                                   | GND               |                                                                                                      |

| J                                   | DSK WRT PROTECT L | Disk write protect (low=true). The selected disk drive does not write if this signal is true         |

| Κ                                   | GND               |                                                                                                      |

| L                                   | DSK READ L        | Disk read (low=true) causes the selected disk drive to read                                          |

| М                                   | GND               |                                                                                                      |

| N                                   | Not used          |                                                                                                      |

| Р                                   | GND               |                                                                                                      |

| R                                   | DSK WRT STATUS L  | Disk Write Status L (low=true, Disk OK)                                                              |

| s                                   | GND               |                                                                                                      |

| т                                   | DSK SECTOR MK L   | Disk sector mark (low=true) from the selected disk drive                                             |

| U                                   | GND               |                                                                                                      |

| V                                   | DISK FILE RDY L   | The selected disk drive is ready to read or write data (low=true)                                    |

| w                                   | GND               |                                                                                                      |

| ×                                   | DSK HEAD SEL 1    | Disk head select bit; when this bit is a 1, the lower or 1 surface of the disk cartridge is selected |

Table 11-6 (Cont)

RK8-E—RK05 Interface Cable (P1)

| Connector J1<br>on RK8-E<br>Pin No. | Signal                  | Description                                                    |

|-------------------------------------|-------------------------|----------------------------------------------------------------|

| Y                                   | GND                     |                                                                |

| Z                                   | DSK INDEX MK L          | Disk index mark (low=true) from the selected disk drive        |

| AA                                  | GND                     |                                                                |

| BB                                  | DSK WRT ERASE<br>GATE L | Disk write erase gate (low=true)                               |

| cc                                  | GND                     |                                                                |

| DD                                  | DSK SEC 1 L             | Disk sector address bit 0 (low=1) from the selected disk drive |

| EE                                  | GND                     |                                                                |

| FF                                  | DSK SEC 4 L             | Disk address bit 2 (low=1) from the selected disk drive        |

| НН                                  | GND                     |                                                                |

| JJ                                  | Not used                |                                                                |

| KK                                  | GND                     | 5<br>                                                          |

| LL                                  | DSK SEC 8 L             | Disk sector address bit 3 (low=1) from the selected disk drive |

| мм                                  | GND                     |                                                                |

| NN                                  | Not used                |                                                                |

| PP                                  | GND                     |                                                                |

| RR                                  | DSK STROBE L            | Disk strobe enables the disk to receive disk address           |

| SS                                  | GND                     |                                                                |

| π                                   | Not used                |                                                                |

| UU                                  | GND                     |                                                                |

| vv                                  | Not used                |                                                                |

Table 11-7

M7104 Top Connector Signal List

| Signal            | Pin No. | Origin | Description                                                                             |

|-------------------|---------|--------|-----------------------------------------------------------------------------------------|

| 12TH BIT OK H     | НМ1     | M7106  | Output of the divide by 12 counter each time 12 bits are read or written                |

| 6RK3 OK H         | HS1     | M7104  | 6RK3 (DLAG) load disk address and go if RK8-E is in the IDLE state                      |

| 6RK3 OK L         | HS2     | M7104  | Same as 6RK3 H except low is true                                                       |

| 6RK4 L            | JS2     | M7104  | 6RK4 (DLCA) load Current Address Register                                               |

| 6RK6 H            | HR1     | M7104  | 6RK6 (DLDC) load Command Register                                                       |

| 6RK7 H            | JC1     | M7104  | 6RK7 (DMAN) maintenance instruction                                                     |

| 6RK7 OK H         | HN2     | M7104  | 6RK7 (DMAN) OK asserted only at TP3 time                                                |

| WRT BRK L         | HH1     | M7105  | Write break request (use DB1 for data transfer)                                         |

| READ BRK L        | HL2     | M7105  | Read break request (use DB4 for data transfer)                                          |

| B DATA 10 H       | JA2     | M7104  | Buffered data bus bit 10 (high=true) (1)                                                |

| B DATA 10 L       | JP2     | M7104  | Buffered data bus bit 10 (low=true) (1)                                                 |

| B DATA 11 H       | JR1     | M7104  | Buffered data bus bit 11 (low=true) (1)                                                 |

| B DATA 11 L       | JH1     | M7104  | Buffered data bus bit 11 (low=true) (1)                                                 |

| BRK DIR (0) H     | HP2     | M7105  | Controls state of MD DIR L on the OMNIBUS                                               |

| втрз ок н         | нк1     | M7104  | Asserted at TP3 time if the RK8-E is in the IDLE state for timing                       |

| CLR DRV CMD L     | JC2     | M7104  | Clear commands to the selected disk drive (see DCLR instruction and Table 11-11)        |

| CLR ALL H         | HD1     | M7104  | Clear all logic (see DCLR instruction and Table 11-11)                                  |

| CLR ALL L         | JU2     | M7104  | Same as CLR ALL H except low=true                                                       |

| DRV REVO H        | JD2     | RK05   | Disk has read an index mark                                                             |

| DSK CAPACITY EX L | JK1     | RK05   | Disk capacity exceeded, a cylinder address greater than 3128 was sent to the disk drive |

| DSK FILE RDY L    | HE1     | RK05   | Selected disk drive is ready                                                            |

Table 11-7 (Cont)

M7104 Top Connector Signal List

| Signal           | Pin No. | Origin | Description                                                                                                     |

|------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------|

| DSK WRT STATUS   | JD2     | RK05   | Selected disk drive is in a write status                                                                        |

| SET IDLE PL L    | JJ1     | M7104  | Set the IDLE state flip-flop                                                                                    |

| ENAB INT H       | JB1     | M7105  | Enable the interrupt logic (see Table 3-2)                                                                      |

| ENAB SEEK DONE H | JS1     | M7105  | Enable seek done if bit 3 in the Command Register is set                                                        |

| END STATE (0) H  | JJ2     | M7106  | The RK8-E is in the END state                                                                                   |

| ERROR CLR L      | JD1     | M7104  | Clear the ERROR flip-flop                                                                                       |

| HI RD CLK H      | JM1     | M7105  | Maintenance clock or clock from the disk during a read                                                          |

| HI DATA IN H     | JR2     | M7105  | Maintenance data or data from the disk during a read                                                            |

| IDLE (0) H       | JN1     | M7106  | RK8-E is not in IDLE state when this signal is 0 (high)                                                         |

| IDLE (1) H       | JL2     | M7106  | RK8-E is in IDLE state when this signal is 1 (high)                                                             |

| LAST WORD PL H   | JN2     | M7106  | Output of the word counter each time 256 words are read or written                                              |

| LD CMD REG H     | JP1     | M7105  | Load Command Register asserted by 6RK6 (DLDC at TP3 time)                                                       |

| LO MAIN DATA H   | HV2     | M7105  | Load main data                                                                                                  |

| LO MAIN SHFT L   | HP1     | M7105  | Shift main data                                                                                                 |

| MAIN (0) H       | JE1     | M7105  | Clear side of MAIN enable flip-flop. This signal is true when the MAIN flip-flop is cleared (normal operations) |

| MAIN (1) H       | HA2     | M7105  | Set side of MAIN flip-flop. This signal is true when the MAIN flip-flop is set to enable maintenance operations |

| B DATA 01 H      | HT2     | M7104  | Buffered data bus bit 1                                                                                         |

| NOT EQUAL (0) H  | JF2     | M7105  | The cylinder address sent to the disk and the cylinder address read after seek is complete are not equal        |

Table 11-7 (Cont)

M7104 Top Connector Signal List

| Signal             | Pin No. | Origin | Description                                                                                               |

|--------------------|---------|--------|-----------------------------------------------------------------------------------------------------------|

| RDY S/R/W L        | HU1     | RK05   | Selected disk drive ready to seek, read, or write                                                         |

| в тр2 н            | HC2     | M7104  | Buffered time pulse 2                                                                                     |

| SECTOR SEEK (0) H  | JF1     | M7106  | RK8-E is in sector seek state if sector seek (0) is true high                                             |

| SEEK FAIL H        | HU2     | RK05   | Selected disk drive failed to seek                                                                        |

| MAIN PL H          | HT1     | M7105  | See maintenance instruction and Table 11-14                                                               |

| DATA ENABLE (1) H  | HN1     | M7105  | Enable gate to apply MA and EMA bits to the OMNIBUS                                                       |

| DATA STATE (0) H   | JM2     | M7106  | The RK8-E is not in data state when this signal is high (0)                                               |

| B DATA STATE (1) H | HL1     | M7106  | The RK8-E is in the data state when this signal is high (1)                                               |

| DB CONT 1 (0) H    | HV1     | M7106  | Data buffer 1 control                                                                                     |

| DB CONT 4 (1) H    | HE2     | M7104  | Data buffer 4 control                                                                                     |

| DEVICE RK H        | JA1     | M7104  | If device RK is high (true), the RK8-E is selected for this operation                                     |

| в трз н            | JT1     | M7104  | Buffered time pulse 3                                                                                     |

| DRIVE STATUS BAD H | JH2     | RK05   | Selected disk drive not operational (Table 11-12)                                                         |

| WRITE (1) H        | HM2     | M7106  | WRITE function is (1) high when a write operation is selected                                             |

| WRT CMD L          | JE2     | M7106  | WRT command to the disk during a write operation                                                          |

| WT BUFF TO DATA L  | HD2     | M7104  | Transfer DB4 to the data lines (used during maintenance operations to transfer contents of DB4 to the AC) |

| RK DATA 11 H       | HF1     | M7104  | Disk data bit 11                                                                                          |

| LD DISK ADDRESS H  | JB2     | M7106  | Load Disk Address Register when asserted by 6RK3                                                          |

| SHFT WRT BUFF L    | HR2     | M7106  | Shift write buffer (DB4)                                                                                  |

| AC7 (0) H          | HB1     | M7104  | Bit 7 from the AC                                                                                         |

# Table 11-7 (Cont) M7104 Top Connector Signal List

| Signal          | Pin No. | Origin | Description                                       |

|-----------------|---------|--------|---------------------------------------------------|

| RDY S/R/W SLO H | JL1     | RK05   | Selected disk drive ready to seek, read, or write |

| BRK RQ H        | HA1     | M7105  | Break request                                     |

| B BRK RQ H      | HB2     | M7104  | Buffered break request                            |

| MAK (0) H       | НЈ1     | M7105  | Data BRK ROST accepted (RK8-E has priority)       |

| DATA CLK OK H   | HC1     | M7106  | Data clock OK                                     |

Table 11-8

M7105 to M7104 Top Connector Signal List

| Signal             | Pin No. | Origin | Description                                                          |

|--------------------|---------|--------|----------------------------------------------------------------------|

| 12ТН ВІТ ОК Н      | HM1     | M7106  | Output of divide by 12 counter each time 12 bits are read or written |

| 6RK3 OK H          | HS1     | M7104  | 6RK3 (DLAG) load disk address and go if RK8-E is in the IDLE state   |

| 6RK3 OK L          | HS2     | M7104  | Same as 6RK3 H except low=true                                       |

| 6RK4 L             | JS2     | M7104  | 6RK4 (DLCA) Load Current Address Register                            |

| 6RK6 H             | HR1     | M7104  | 6RK6 (DLDC) load command address                                     |

| 6RK7 H             | JC1     | M7104  | 6RK7 (DMAN) maintenance                                              |

| 6RK7 OK H          | HN2     | M7104  | Same as 6RK7 except it is enabled at TP3 time                        |

| WRT BRK L          | HH1     | M7105  | Write break request (use DB1 for data transfer)                      |

| READ BRK L         | HL2     | M7105  | Read break request (use DB4 for data transfer)                       |

| B DATA 10 H        | JA2     | M7104  | Buffered data bus bit 10 (high=true)                                 |

| B DATA 10 L        | JP2     | M7104  | Buffered data bus bit 10 (low=true)                                  |

| B DATA 11 H        | JR1     | M7104  | Buffered data bus bit 11 (high=true)                                 |

| B DATA 11 L        | JH1     | M7104  | Buffered data bus bit 11 (low=true)                                  |

| BRK DIR (0) H      | HP2     | M7105  | Controls MD DIR L on the OMNIBUS                                     |

| в трз ок н         | HK1     | M7104  | Buffered time pulse 3                                                |

| CLR DRIVE CMD L    | JC2     | M7104  | Clear selected disk drive (DCLD)                                     |

| CLR ALL H          | HD1     | M7104  | Clear all logic (see DCLR instruction and Table 11-11)               |

| CLR ALL L          | JU2     | М7105  | Same as clear all H except low=true                                  |

| ENABLE DATA (1) H  | HN1     | M7105  | Enable gates to apply MA and EMA bits to the OMNIBUS                 |

| DATA STATE (0) H   | JM2     | M7106  | The RK8-E is in the DATA state (data transfers are enabled)          |

| B DATA STATE (1) H | HL1     | M7106  | Buffered DATA state                                                  |

Table 11-8 (Cont)

M7105 to M7104 Top Connector Signal List

| Signal             | Pin No. | Origin | Description                                                                          |

|--------------------|---------|--------|--------------------------------------------------------------------------------------|

| DB CONT 1 (0) H    | HV1     | M7104  | Data buffer 1 control                                                                |

| DB CONT 4 (1) H    | HE2     | M7104  | Data buffer 4 control                                                                |

| DEVICE RK H        | JA1     | M7104  | If device RK is high (true), the RK8-E is selected for this operation                |

| В ТРЗ Н            | JT1     | M7104  | Buffered time pulse 3                                                                |

| DRIVE STATUS BAD H | JH2     | M7105  | The selected disk drive is not ready (Table 11-12 bit 10)                            |

| WRITE (1) H        | HM2     | M7106  | The write function is selected                                                       |

| WRT CMD L          | JE2     | M7106  | Write command to selected disk drive                                                 |

| WT BUFF TO DATA L  | HD2     | M7104  | Transfer contents of write buffer (DB4) to the Data lines                            |

| RK DATA 11 H       | HF1     | M7104  | Disk data bit 11 (serial data to disk)                                               |

| LD DISK ADDRESS H  | JB2     | M7106  | Load Disk Address Register when asserted by 6RK3                                     |

| SHFT WRT BUFF L    | HR2     | M7106  | Shift the Write Buffer out to the disk drive                                         |

| AC7 (0) H          | HB1     | M7104  | Bit 7 from the AC                                                                    |

| RDY S/R/W H        | JL1     | M7105  | Selected disk drive ready to seek, read, or write                                    |

| BRK RQ H           | HA1     | M7105  | Break request                                                                        |

| B BRK RQ H         | HB2     | M7105  | Buffered break request                                                               |

| MAK (0) H          | HJ1     | M7105  | Data BRK ROST has been accepted (RK8-E has highest priority)                         |

| DATA CLK OK H      | HC1     | M7106  | DATA clock OK                                                                        |

| DRV REVO H         | JK2     | M7106  | Disk index mark is applied to RK8-E during IDLE state                                |

| DSK CAPACITY EX L  | JK1     | RK05   | Disk capacity exceeded, address greater than 312 <sub>8</sub> sent to the disk drive |

| DSK FILE RDY L     | HE1     | RK05   | Selected disk drive is ready (on-line)                                               |

| DSK WRT STATUS L   | JD2     | RK05   | Disk drive write status (low=true)                                                   |

Table 11-8 (Cont)

M7105 to M7104 Top Connector Signal List

| Signal            | Pin No. | Origin | Description                                                                                              |

|-------------------|---------|--------|----------------------------------------------------------------------------------------------------------|

| SET IDLE PL L     | JJ1     | M7104  | Set IDLE state flip-flop                                                                                 |

| ENAB INT H        | JB1     | M7105  | Enable interrupt logic (Table 11-12)                                                                     |

| ENAB SEEK DONE H  | JS1     | M7105  | Enable seek done if bit 3 in Command Register is set                                                     |

| END STATE (0) H   | JJ2     | M7106  | RK8-E in the END state when asserted                                                                     |

| ERROR CLR L       | JD1     | M7104  | Clear the ERROR flip-flop                                                                                |

| HI RD CLK H       | JM1     | M7105  | Main clock OR clock from the disk during a read                                                          |

| HI DATA IN H      | JR2     | M7105  | Serial DATA from the disk drive during a read                                                            |

| IDLE (0) H        | JN1     | M7106  | RK8-E is not in the IDLE state when this signal is high                                                  |

| IDLE (1) H        | JL2     | М7106  | RK8-E is in the IDLE state when this signal is 1 (high)                                                  |

| LAST WORD PL H    | JN2     | M7106  | Output of word counter each time 256 words are read or written                                           |

| LD CMD REG H      | JP1     | M7106  | Load Command Register (DLDC)                                                                             |

| LO MAIN DATA H    | HV2     | M7105  | Maintenance data (Table 11-14)                                                                           |

| LO MAIN SHFT L    | HP1     | M7105  | Maintenance shift pulse (Table 11-14)                                                                    |

| MAIN (0) H        | JE1     | M7105  | Maintenance command (DMAN instruction)                                                                   |

| MAIN (1) H        | HA2     | M7105  | Maintenance command (DMAN instruction)                                                                   |

| B DATA 01 H       | HT2     | M7104  | Buffered data bit 2                                                                                      |

| NOT EQUAL (0) H   | JF2     | М7105  | The cylinder address sent to the disk and the cylinder address read after seek is complete are not equal |

| RDY S/R/W L       | HU1     | RK05   | Selected disk drive ready to seek, read, or write                                                        |

| в тр2 н           | HC2     | M7104  | Buffered time pulse 2                                                                                    |

| SECTOR SEEK (0) H | JF1     | M7106  | RK8-E is in sector seek state if sector seek (0) is true high                                            |

| SEEK FAIL H       | HU2     | RK05   | Selected disk drive failed to seek                                                                       |

| MAIN PL H         | HT1     | M7105  | See maintenance instruction and Table 11-14                                                              |

Table 11-9

M7105 to M7106 Top Connector Signal List

| Signal           | Pin No. | Origin | Description                                                                                     |

|------------------|---------|--------|-------------------------------------------------------------------------------------------------|

| 12TH BIT OK H    | FA1     | M7106  | Output of divide by 12 counter each time 12 bits are read or written                            |

| 6RK3 OK H        | FA2     | M7104  | 6RK3 (DLAG) load disk address and go if RK8-E is in IDLE state                                  |

| B DATA 7 H       | ER2     | M7104  | Buffered data bit 7 (high=true) (1)                                                             |

| B DATA 10 H      | EK1     | M7104  | Buffered data bit 10 (high=true) (1)                                                            |

| B DATA 11 H      | EJ1     | M7104  | Buffered data bit 11 (high=true) (1)                                                            |

| CLR DRIVE CMD L  | FB2     | M7104  | Clear commands to the selected drive                                                            |

| CLR ALL L        | EH1     | M7104  | Clear all logic (see the DCLR instruction and Table 11-11)                                      |

| DATA STATE (0) H | FP1     | M7106  | Data state (read or write data)                                                                 |

| в трз н          | FJ1     | M7104  | Buffered time pulse 3                                                                           |

| DRV REVOH        | FC2     | M7106  | Disk index mark is applied to the RK8-E during IDLE state                                       |

| DSK FILE RDY L   | FB1     | RK05   | Selected disk drive is operational                                                              |

| DSK WRT STATUS L | FD2     | RK05   | Selected disk drive is in a write status (low=true)                                             |

| SET IDLE PL L    | FK1     | M7104  | Set the IDLE state flip-flop                                                                    |

| END STATE (0) H  | FD1     | M7106  | END state (true=0)                                                                              |

| ERROR CLR L      | FE2     | M7104  | Clear the ERROR flip-flop                                                                       |

| IDLE (0) H       | FR2     | M7106  | The RK8-E is not in the IDLE state when this signal is (0) high                                 |

| IDLE (1) H       | EC1     | M7106  | The RK8-E is in the IDLE state when this signal is (1) high                                     |

| LAST WORD PL H   | FE1     | M7106  | LAST WORD is asserted when 256 words are read or written                                        |

| MAIN (0) H       | FP2     | M7105  | Clear side of MAIN flip-flop. This signal is true when the RK8-E is not in the maintenance mode |

| RDY S/R/W H      | ED1     | M7105  | Selected disk drive is ready to seek, read, or write                                            |

Table 11-9 (Cont)

M7105 to M7104 Top Connector Signal List

| Signal            | Pin No. | Origin | Description                                                                   |

|-------------------|---------|--------|-------------------------------------------------------------------------------|

| DATA ENABLE (1) H | EU1     | M7105  | Enable gates to apply MA and EMA bits to the OMNIBUS                          |

| SECTOR SEEK (0) H | FF2     | M7106  | The RK8-E is in the sector seek state if SECTOR SEEK is true (high)           |

| LAST BRK (1) H    | FN2     | M7105  | Last break (1=true) ends data transfer operations                             |

| WRITE (1) H       | FF1     | M7106  | The write function is selected by the program                                 |

| WRT CMD L         | FV2     | M7106  | Write command to the RK05                                                     |

| в тр2 н           | FH2     | M7104  | Buffered time pulse 2                                                         |

| B DATA 8 H        | EM1     | M7104  | Buffered data bus bit 8                                                       |

| B DATA 9 H        | EL1     | M7104  | Buffered data bus bit 9                                                       |

| BRK ENABLE CLK H  | FK2     | M7106  | Break enable clock pulse                                                      |

| BRK IN CLK H      | FU2     | M7106  | Break in clock pulse                                                          |

| CLR CNTRS L       | FS1     | M7106  | Clear counters asserted by CLR ALL, DATA CLR, or HEADER E during STATE ENABLE |

| CLR SECTOR AD L   | EF1     | M7105  | Clear Sector Address Register                                                 |

| CRC 16 (1) H      | EN2     | M7105  | CRC Register bit 16                                                           |

| CRC DATA H        | EA1     | M7106  | Serial CRC data                                                               |

| DATA IN (0) H     | FR1     | M7106  | Serial data from the disk during a read                                       |

| RD CLK (1) H      | EB1     | M7105  | Read clock from the disk during a read                                        |

| RD SHFT DB L      | FS2     | M7106  | Shift Data Buffer during read operations                                      |

| SECTOR ADDR 01 H  | EP2     | M7105  | Sector address bit 0 high                                                     |

| SHFT SURF SEC H   | FU1     | M7105  | Shift Surface Sector Register                                                 |

| ENAB DATA L       | EV1     | M7105  | Enable data to the buffers                                                    |

| SHFT CRC L        | FN1     | M7106  | Shift CRC out to the disk drive                                               |

| FILE RDY H        | EE1     | RK05   | Selected disk drive is READY                                                  |

Table 11-9 (Cont)

M7105 to M7104 Top Connector Signal List

| Signal            | Pin No. | Origin | Description                                                                              |

|-------------------|---------|--------|------------------------------------------------------------------------------------------|

| STROBE (1) H      | EF2     | M7106  | Asserted when file is ready and GO bit is set (1)                                        |

| FUNCTION 00 H     | EU2     | M7106  | Function bit 00 )                                                                        |

| FUNCTION 01 H     | EV2     | M7106  | ) Select disk drive<br>Function bit 01 ) operation, i.e., read                           |

| FUNCTION 02 H     | ET2     | M7106  | Function bit 02 )                                                                        |

| HALF BLOCK H      | ES2     | M7105  | Transfer 128 words instead of 256                                                        |

| DATA CLK OK H     | FM1     | M7106  | Data clock OK                                                                            |

| LO MAIN SHFT L    | FL1     | M7106  | Maintenance shift                                                                        |

| DSK DRIVE 2 L     | EP1     | M7105  | Select disk drive 2 when low (true)                                                      |

| DSK DRIVE 3 L     | EN1     | M7105  | Select disk drive 3 (low=true)                                                           |

| DSK CYL AD 128 L  | EE2     | M7106  | Disk cylinder address bit 7 (MSB)                                                        |

| DSK CYL AD 64 L   | EB2     | M7106  | Disk cylinder address bit 6                                                              |

| DSK CYL AD 32 L   | EJ2     | M7106  | Disk cylinder address bit 5                                                              |

| DSK CYL AD 16 L   | EC2     | M7106  | Disk cylinder address bit 4                                                              |

| DSK CYL AD 8 L    | ET1     | M7106  | Disk cylinder address bit 3                                                              |

| DSK CYL AD 4 L    | EH2     | M7106  | Disk cylinder address bit 2                                                              |

| DSK CYL AD 2 L    | EK2     | M7106  | Disk cylinder address bit 1                                                              |

| DSK CYL AD 1 L    | ES1     | M7106  | Disk cylinder address bit 0 (LSB)                                                        |

| DSK CAPACITY EX L | FC1     | RK05   | Disk capacity exceeded, address sent to the disk greater than $312_8$                    |

| HI MAIN SHIFT L   | FT2     | M7106  | Maintenance shift pulse                                                                  |

| B LAST BRK H      | FL2     | M7106  | Buffered last break                                                                      |

| LD DSK ADDRS H    | EM2     | M7106  | Load Disk Address Register when asserted by 6RK3                                         |

| RK DATA 11 H      | FH1     | M7105  | Disk data bit 11                                                                         |

| В ТРЗ ОК Н        | FM2     | M7104  | Asserted during TP3 time of the IDLE state only for timing and execution of instructions |

Table 11-9 (Cont)

M7105 to M7104 Top Connector Signal List

| Signal           | Pin No. | Origin | Description                                          |

|------------------|---------|--------|------------------------------------------------------|

| SHFT WRT BUFF L  | FJ2     | M7104  | Shift write buffer (DB4)                             |

| STATE ENABLE B H | FV1     | M7106  | Buffered STATE ENABLE                                |

| DSK RDY S/R/W L  | EL2     | RK05   | Selected disk drive ready to seek, read, or write    |

| DSK SEEK FAIL L  | EA2     | RK05   | The seek operation on the selected disk drive failed |

| DSK DRIVE 0 L    | ED2     | M7105  | Select disk drive 0 when low (true)                  |

| DSK DRIVE 1 L    | ER1     | M7105  | Select disk drive 1 when low (true)                  |

Table 11-10

M7106 Top Connector Signal List

| Signal            | Pin No. | Origin | Description                                                                                          |

|-------------------|---------|--------|------------------------------------------------------------------------------------------------------|

| 12TH BIT OK H     | FA1     | M7106  | Output of divide by 12 counter each time 12 bits are read or written                                 |

| 6RK3 OK H         | FA2     | M7104  | 6RK3 (DLAG) load disk address and go                                                                 |

| B DATA 7 H        | ER2     | M7104  | Buffered data bus bit 7 (high=true)                                                                  |

| B DATA 10 H       | EK1     | M7104  | Buffered data bus bit 10 (high=true)                                                                 |

| B DATA 11 H       | EJ1     | M7104  | Buffered data bus bit 11 (high=true)                                                                 |

| CLR DRIVE CMD L   | FB2     | M7104  | Clear commands to the selected disk drive clear all logic (see the DCLR instruction and Table 11-11) |

| CLR ALL L         | EH1     | M7104  | Clear all logic on the RK8-E                                                                         |

| DATA STATE (0) H  | FP1     | M7106  | Data state (read or write data)                                                                      |

| в трз н           | FJ1     | M7104  | Buffered time pulse 3                                                                                |

| DRV REVOH         | FC2     | M7106  | Disk INDEX MARK is applied to the RK8-E during the IDLE state                                        |

| DSK FILE RDY L    | FB1     | RK05   | Selected disk drive is operational                                                                   |

| DSK WRT STATUS L  | FD2     | RK05   | Selected disk drive is in a write status (low=true)                                                  |

| SET IDLE PL L     | FK1     | M7104  | Set the IDLE state flip-flop                                                                         |

| END STATE (0) H   | FD1     | M7106  | The RK8-E is in the END state                                                                        |

| ERROR CLR L       | FE2     | M7104  | Clear the ERROR flip-flops                                                                           |

| IDLE (0) H        | FR2     | M7106  | RK8-E is not in the IDLE state when this signal is high                                              |