# A/D/A

ANALOG TO DIGITAL

AND

DIGITAL TO ANALOG

# CONVERTER BOARD USER MANUAL

#### A / D / A

ANALOG TO DIGITAL

AND

DIGITAL TO ANALOG

CONVERTER BOARD

P/N 52748-900

U S E R M A N U A L Revision 6, 5/84

COPYRIGHT, I/O TECHNOLOGY 1982

INPUT/OUTPUT TECHNOLOGY, INC.

25327 AVENUE STANFORD, UNIT 113 VALENCIA, CA. 91355

#### TABLE OF CONTENTS

|         |       |                                      | PAGE    |

|---------|-------|--------------------------------------|---------|

| SECTION | 1.0   | Introduction and General Information | 1-1     |

|         | 1,1   | General Information                  | 1-1     |

|         | 1.1.1 | Receiving Inspection                 | .1-1    |

|         | 1.1.2 | Factory Service                      | .1-1    |

|         | 1.1.3 | Replacement Parts                    | .1-2    |

|         | 1.1.4 | Warranty                             | .1-2    |

|         | 1.1.5 | Life Support Policy                  | .1-2    |

|         | 1.1.6 | Tools and Supplies                   | .1-2    |

|         | 1.2   | A/D/A Board Specifications           | .1-6    |

|         | 1.2.1 | A/D Characteristics                  | .1-6    |

|         | 1.2.2 | D/A Characteristics                  | .1-6    |

|         | 1.2.3 | Support Circuitry Characteristics    | .1-7    |

|         | 1.2.4 | Physical Characteristics             |         |

|         | 1.2.5 | Input Power Requirements             | . 1-7   |

|         | 1.3   | Parts List                           | .1-8    |

|         |       |                                      |         |

| SECTION | 2.0   | Assembly and Check-Out               | .2-1    |

|         | 2.1   | Factory Configuration                | .2-1    |

| SECTION | 3.0   | Theory of Operation                  | .3-1    |

|         | 3.1   | A/D Section                          | . 3 – 1 |

|         | 3.1.1 | Input Protection Networks            | . 3 – 1 |

|         | 3.1.2 | Multiplexer                          | .3-1    |

|         | 3.1.3 | Gain Select Circuit                  | .3-1    |

|         | 3.1.4 | Track and Hold Amplifier             | . 3 – 1 |

|         | 3.1.5 | Voltage Reference                    |         |

| SECTION | 3.1.6   | Successive Approximation Register and Comparator3-1 |

|---------|---------|-----------------------------------------------------|

|         | 3.2     | D/A Section                                         |

|         | 3.2.1   | Data Buffer3-5                                      |

|         | 3.2.2   | Programmable References3-6                          |

|         | 3.2.3   | Analog Outputs                                      |

|         | 3.3     | Digital Section                                     |

| SECTION | 4.0     | Board Configuration4.1                              |

|         | 4.1     | Addressing4.1                                       |

|         | 4.1.1   | Lower Byte Address Selection4-2                     |

|         | 4.1.2   | Upper Byte Address Selection4-3                     |

|         | 4.1.2.1 | Upper Byte Address Deselection4-5                   |

|         | 4.1.3   | Extended Address Selection/Deselection*4-6          |

|         | 4.1.3.1 | Selection4-6                                        |

|         | 4.1.3.2 | Extended Byte Address Deselection4-8                |

|         | 4.2     | Data Transfer Mode Selection4-8                     |

|         | 4.2.1   | Older S-100 System Incompatibilities4-9             |

|         | 4.3     | Phantom Select Option4-10                           |

|         | 4.4     | DMA Operation4-10                                   |

|         | 4.5     | 16/8 Bit Operation4-11                              |

|         | 4 . 6   | Address Verify Indicator4-12                        |

| SECTION | 5.0     | A/D Operation                                       |

|         | 5.1     | A/D Control Word5-1                                 |

|         | 5.1.1   | Channel Selection                                   |

|         | 5.1.1.1 | Input Connector Pin Designations (CA)5-3            |

|         | 5.1.2   | Single Ended/Differential Selection5-3              |

|         | 5 1 2   | Cain Salastion                                      |

| SECTION | 5.1.4   | Input Level Restrictions vs. Gain                 | 5-4   |

|---------|---------|---------------------------------------------------|-------|

|         | 5.1.5   | Start Conversion Command                          | 5 – 4 |

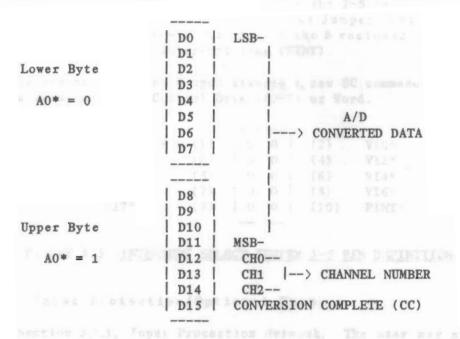

|         | 5.1.6   | Conversion Data Word Read                         | 5 – 5 |

|         | 5.1.7.1 | Conversion Complete                               | 5 – 5 |

|         | 5.1.7.2 | Conversion Complete Interrupt                     | 5-6   |

|         | 5.2     | Input Protection/Optional Fuse                    | 5 – 6 |

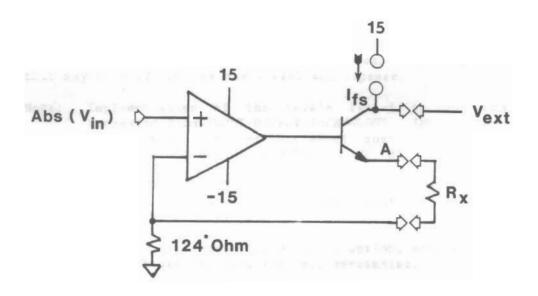

|         | 5.3     | Current Input Option                              | 5-6   |

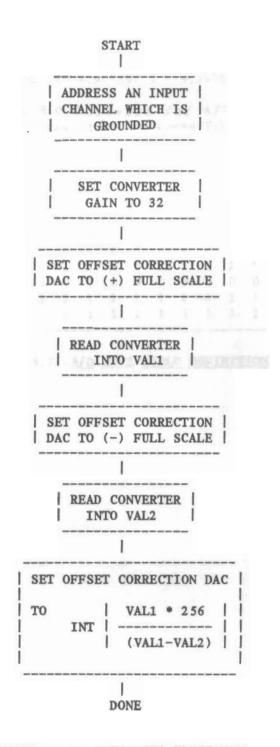

|         | 5.4     | A/D Offset Voltage Nulling                        | 5-7   |

|         | 5.4.1   | Input Offset Correction Range                     | 5-7   |

|         | 5.5     | Data Field Input Level Conversion                 | 5-7   |

|         |         |                                                   |       |

| SECTION | 6.0     | D/A Section Operation                             | i – 1 |

|         | 6.1     | Voltage/Current Output Selection                  | 5-1   |

|         | 6.2     | Power-On Condition                                | 5-2   |

|         | 6.3     | RAM Location Vs. Channel Allocation6              | 5-3   |

|         | 6.3.1   | Output Connector Pin Designations (CB)6           | 5-3   |

|         | 6.4     | Refresh Vs. Single Channel Operation6             | 5-4   |

|         | 6.5     | Programmable Reference Levels                     | 5 - 5 |

|         | 6.6     | Voltage Output Level Set                          | 5 – 5 |

|         | 6.6.1   | D/A Voltage Output Performance                    | 5 – 6 |

|         | 6.7     | Current Output Level Set                          | 5 – 6 |

|         |         |                                                   |       |

| SECTION | 7.0     | Customizing the A/D/A Board                       | 7-1   |

|         | 7.1     | Customizing the Gain Network                      | 7 – 1 |

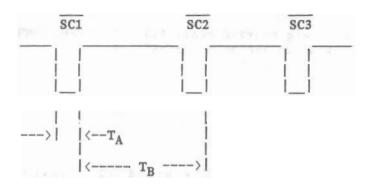

|         | 7.2     | External SC Trigger Source Generation7            | 7-2   |

|         | 7.3     | Reduce A/D Conversion Time Thru an External Clock | 7 – 3 |

|         | 7.3.1   | Alternate On-Board A/D Clock Source               |       |

|         | 7.4     | Unipolar Voltage Input Option                     |       |

|         | 1 . **  | Unitodial vollage indul upilon                    | / 4   |

| SECTION                                 | 7.4.1  | Unip |       |     |     |     |     | _   |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     |       |     |

|-----------------------------------------|--------|------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|------|-----|---|-----|-----|---|---|-----|-----|-----|-----|-------|-----|

|                                         |        | Modi | fic   | at  | io  | ns  |     | •   | ٠.  | •   |     |     | ٠.  | •  |     | ٠    |     | • |     | •   | ٠ |   | ٠.  | ٠   | •23 | • • | 7-    | - 5 |

|                                         | 7.4.2  | Unip | 01    | ar  | Ιn  | pu  | t   | D   | a t | a   | R   | e   | d u | C  | t i | 0    | n   | Ι | mj  | pr  | 0 | v | еп  | n e | n   | t.  | 7 -   | - 5 |

|                                         | 7.5    | Redu | се    | A / | D   | Co  | n   | z e | T S | i   | οп  |     | Гi  | m  | e   | b    | v   | R | e   | d u | c | t | ic  | n   |     |     |       |     |

|                                         |        | in R |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     | 7-    | - 6 |

|                                         | 7.6    | Incr | e a s | s e | D/  | A   | CI  | 1 a | nı  | ı e | 1   | Re  | e f | r  | e s | h    | R   | a | te  | е.  |   |   |     |     |     |     | 7 -   | - 7 |

|                                         | 7.7    | Unip | 01    | ar  | D/  | A   | V   | 1   | ta  | g   | е   | 01  | a t | pı | u t | : .  |     |   |     |     |   |   |     |     |     |     | 7-    | - 7 |

|                                         | 7.7.1  | Unip | 011   | a r | D/  | Α   | 01  | ıt  | מס  | ıt  | Н   | 8 1 | r d | w  | ат  | · e  |     |   |     |     |   |   |     |     |     |     |       |     |

|                                         |        | Modi |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     | • | • | į.  | •   |     |     | 7-    | - 8 |

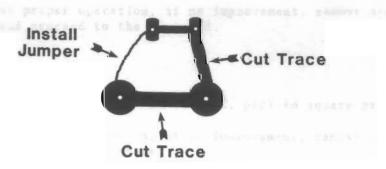

|                                         | 7.8    | PAL  | Ι.(   | С.  | Up  | da  | te  | в   | (Į  | 15  | - 4 | )   |     |    |     |      |     |   | •   |     |   |   |     | •   |     | ٠.  | 7-    | - 9 |

| SECTION                                 | 8.0    | Soft | wai   | re. |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   | 500 |     |     |     | 8-    | -1  |

|                                         |        |      |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     |       |     |

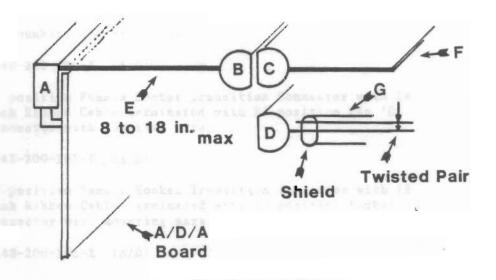

| SECTION                                 | 9.0    | Exte | rna   | a 1 | Ca  | ъ 1 | е   | C   | or  | ı f | ig  | u   | ra  | t  | io  | n    |     |   |     |     |   |   |     |     |     |     | 9-    | -1  |

|                                         | 9.1    | Exte | rn    | a 1 | Ca  | b 1 | e   | S   | h i | e   | 1 d | iı  | n g |    | Сс  | n    | s i | d | e i | ra  | t | i | o r | 1 S |     |     | 9-    | - 3 |

|                                         | 9.2    | CA a | nd    | CB  | C   | on  | ne  | ес  | to  | r   | S   | p.  | e c | i  | fi  | c    | a t | i | 01  | n.  |   |   |     |     |     |     | 9 -   | - 4 |

|                                         |        |      |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     |       |     |

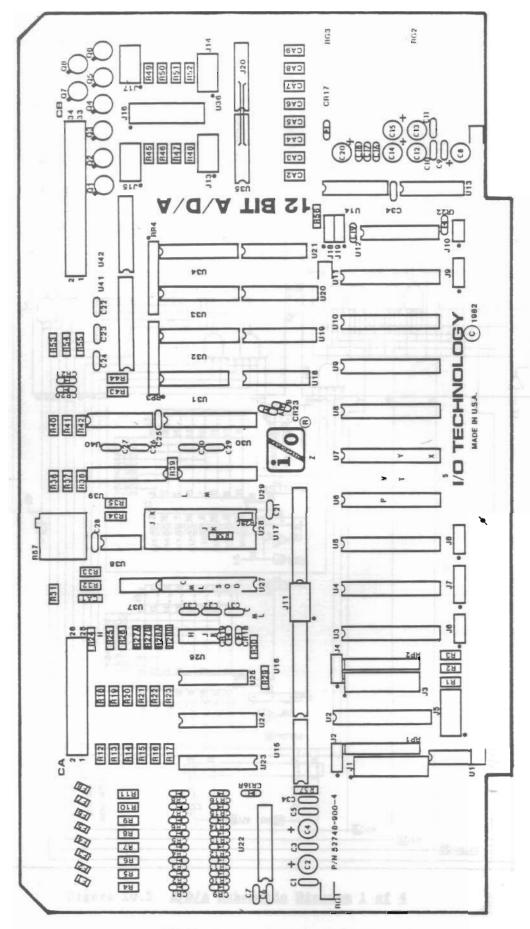

| SECTION                                 | 10.0   | Sche |       |     |     |     |     |     |     |     |     |     | n t | ]  | L a | у    | o u | t | •   |     | • | • |     | •   | ٠   | . 1 | .0-   | - 1 |

|                                         | 10.1   | Lege | nd    |     |     | ٠.  |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     | •   | . 1 | 0-    | -1  |

|                                         | 10.1.1 | Comp | on    | ent | 0   | )ri | eı  | n t | a t | i   | o n |     |     |    |     | . 10 |     |   |     |     | • | ٠ |     |     |     | . 1 | 0-    | -1  |

| SECTION                                 | 11.0   | Buff | er    | ing | 8   | nd  | 1 1 | Fi  | 11  | e   | ri  | n   | g   | A  | PI  | 1    | ic  | a | t   | io  | n | s |     |     |     | . 1 | 1-    | -1  |

| a = a = = a = a = a = a = a = a = a = a | 12.0   |      |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     | •     |     |

| SECTION                                 | 12.0   |      |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     |       |     |

|                                         | 12.1   | A/D  | Ca    | lib | ra  | ti  | 01  | n.  |     | ٠   | ٠.  |     |     |    |     |      |     | • |     |     |   | • |     |     |     | . 1 | 2-    | -1  |

|                                         | 12.2   | D/A  | Ca    | lib | ra  | ti  | 01  | n.  |     |     |     | •   |     | •  |     |      | ٠.  |   | •   |     |   |   |     |     | •   | . 1 | 2-    | - 1 |

|                                         | 12.2.1 | Fact | OF    | у С | a 1 | ib  | r   | a t | i   | n   |     |     |     |    |     |      |     |   |     |     | • |   |     |     | •   | . 1 | 2-    | - 1 |

|                                         | 12.2.2 | User | C     | ali | bı  | at  | i   | on  |     |     |     |     |     |    |     |      |     |   |     |     | • |   |     |     | ٠   | . 1 | 2-    | -1  |

|                                         |        |      |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     |       |     |

| SECTION                                 | 13.0   | User | N     | ote | s.  | ٠.  |     |     |     | •   |     |     |     |    |     |      |     |   | *   |     | • | * |     |     |     | . 1 | . 3 - | - 1 |

|                                         |        |      |       |     |     |     |     |     |     |     |     |     |     |    |     |      |     |   |     |     |   |   |     |     |     |     |       |     |

#### 1.0 Introduction and General Information

We thank you for selecting the A/D/A (Analog to Digital and Digital to Analog) Converter Board and we hope that you find our product to your satisfaction.

The A/D/A Board design provides maximum flexibility and capability to operate in existing 8-bit S-100 systems and in the 8/16-bit IEEE-696 systems.

The 8 channels of A/D and 8 channels of D/A make the A/D/A Board a versatile tool in an unlimited range of analog applications.

All of our products are manufactured to high standards thus providing you with a reliable and low maintenance product. We have compiled this voluminous manual to provide maximum information, procedures and data so to enable the user to fully utilize the on-board features.

#### 1.1 General Information

#### 1.1.1 Receiving Inspection

Carefully inspect the module or kit for signs of damage during shipment. Also cheek packing list to insure that contents correspond with list.

Should any discrepancies or damage be found, please notify us at once, describing the discrepancy, so that we can take appropriate action.

#### 1.1.2 Factory Service

Factory Service is available for in-warranty and out-of-warranty boards.

In order to utilize INPUT/OUTPUT TECHNOLOGY, INC. services, it is required that you obtain an authorization number. Upon receipt of the factory service authorization number, package the unit (preferably in original container to prevent damage during shipment) and return postpaid to:

INPUT/OUTPUT TECHNOLOGY, INC.

UNIT 113

25327 AVENUE STANFORD

VALENCIA, CA.

91355

Under separate correspondence, send information of shipment and description of problem. We suggest that you insure the package: if you do not want us to insure the return shipment, please specify in your correspondence.

#### 1.1.3 Replacement Parts

Replacement parts are available from INPUT/OUTPUT TECHNOLOGY, INC. upon request. When requesting in-warranty parts, you must return the faulty part: this excludes resistors, capacitors, jumper connectors and edge connectors. This will enable us to analyze faulty part(s) for type and cause(s) of failure.

#### 1.1.4 Warranty

Because of the diversity of conditions and hardware under which this product may be used, no warranty of fitness for particular purpose is offered. INPUT/OUTPUT TECHNOLOGY, INC. assumes no liability whatsoever from use or sale of this product.

All INPUT/OUTPUT TECHNOLOGY, INC. modules have a 3 month warranty. For specifics of warranty see page 1-4.

The user shall restore the A/D/A board to the original factory configuration prior any in or out-of-warranty repair service can be rendered by INPUT/OUTPUT TECHNOLOGY, INC..

#### 1.1.5 Life Support Policy

INPUT/OUTPUT TECHNOLOGY, INC.'s products are not authorized for use as critical components in life support devices or systems without the express written approval of INPUT/OUTPUT TECHNOLOGY, INC.. As used herein:

- 1. Life support devices or systems are devices or systems which

(a) are intended for surgical implant into the body, or (b)

support or sustain life, and whose failure to perform, when

properly used in accordance with instructions for use provided in

the labeling, can be reasonably expected to result in a

significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### 1.1.6 Tools and Supplies

The tools and supplies required to configure the A/D/A Board are as follows:

- -Wire Wrap Tool, i.e., O.K. Machine and Tool makes several types for AWG 30 .025 in. square post.

- -AWG 30 wire.

- -25W Soldering Iron

- -60/40 Rosin Flux Solder

INPUT/OUTPUT TECHNOLOGY, INC. 25327 AVENUE STANFORD, UNIT 113 VALENCIA, CA. 91355

#### IMPORTANT

PLEASE FILL OUT AND RETURN TO

INPUT/OUTPUT TECHNOLOGY, INC. SO THAT WE MAY KEEP YOU

INFORMED OF ALL CHANGES AND PROVIDE YOU WITH

ADDITIONAL INFORMATION AS IT BECOMES AVAILABLE

| EGISTERED OWNER                                                                          |                                                                                       |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| DDRESS                                                                                   |                                                                                       |

| ITY                                                                                      | STATE ZIP                                                                             |

|                                                                                          |                                                                                       |

| URCHASED FROM                                                                            | DATE PURCHASED                                                                        |

| ITY                                                                                      | STATEZIP                                                                              |

|                                                                                          |                                                                                       |

| ODEL #52748                                                                              | SERIAL #                                                                              |

|                                                                                          |                                                                                       |

|                                                                                          |                                                                                       |

| PTIONAL:                                                                                 |                                                                                       |

| THE BUILD DIE IN THE                                                                     |                                                                                       |

| THIS PRODUCT WILL BE USED                                                                | ) IN                                                                                  |

| THIS PRODUCT WILL BE USED                                                                | DEED THE CONTRACT                                                                     |

| THIS PRODUCT WILL BE USED                                                                | DEED THE CONTRACT                                                                     |

| THIS PRODUCT WILL BE USED MY COMPUTER IS                                                 | DEED THE CONTRACTOR                                                                   |

| THIS PRODUCT WILL BE USED MY COMPUTER IS                                                 | USED IN INDUSTRY USED IN BUSINESS                                                     |

| THIS PRODUCT WILL BE USED MY COMPUTER IS                                                 | USED IN INDUSTRY                                                                      |

| THIS PRODUCT WILL BE USED MY COMPUTER IS                                                 | USED IN INDUSTRY USED IN BUSINESS A HOBBY COMPUTER                                    |

| THIS PRODUCT WILL BE USED  MY COMPUTER IS  HOW DID YOU HEAR ABOUT T                      | USED IN INDUSTRY USED IN BUSINESS A HOBBY COMPUTER                                    |

| THIS PRODUCT WILL BE USED  MY COMPUTER IS  HOW DID YOU HEAR ABOUT T                      | USED IN INDUSTRY USED IN BUSINESS A HOBBY COMPUTER THIS PRODUCT:                      |

| THIS PRODUCT WILL BE USED  MY COMPUTER IS  HOW DID YOU HEAR ABOUT TO IF MAGAZINE AD, PLE | USED IN INDUSTRY  USED IN BUSINESS  A HOBBY COMPUTER  THIS PRODUCT: EASE SPECIFY NAME |

| THIS PRODUCT WILL BE USED  MY COMPUTER IS  HOW DID YOU HEAR ABOUT TIF MAGAZINE AD, PLE   | USED IN INDUSTRY USED IN BUSINESS A HOBBY COMPUTER THIS PRODUCT:                      |

#### 1.2 A/D/A Board Specifications

| 1.2.1 | A/D | Charac | ter | istics |

|-------|-----|--------|-----|--------|

|-------|-----|--------|-----|--------|

| Resolution 12 Bits                                  |

|-----------------------------------------------------|

| Converson Time 12 µsec.                             |

| Dynamic Channel Sample Rate (Nom.) 50 KHz           |

| Input Channels                                      |

| Input Voltage Range                                 |

| Gain Steps X.5, X2, X8, X32 (Under Program Control) |

| Input Impeadance Greater than 10 $M\Omega$          |

| Offset Voltage Less than 1 LSB*                     |

#### Other A/D Features:

- \*-Auto Offset voltage correction using dedicated 8-Bit DAC in A/D converter under full software control.

- -Optional current input mode on-board selectable for any channel.

- -'Conversion Complete' signal thru interrupt and/or status word read.

- -A/D Channel Address tag contained with each converted word (upper byte).

#### 1.2.2 D/A Characteristics

| Resolution 12 Bits                          |

|---------------------------------------------|

| Settling Time                               |

| Dynamic Channel Refresh Rate (Nom.) 250 KHz |

| Output Channels 8 Single Ended              |

| Type of Outputs: Bipolar Voltage            |

| Unipolar Current 0-10 MA                    |

| (Jumper Selectable) 0-20 MA                 |

| Programmable Reference Levels 10, 5, 2.5V                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage Load Current 2 MA                                                                                                                                                                                                                                                                  |

| Output Impeadance (Voltage) 0.25 Ω                                                                                                                                                                                                                                                         |

| Other D/A Features:                                                                                                                                                                                                                                                                        |

| -All Outputs set to 0.V at Power-OnAuto Refresh for each D/A channel using on-board Dual-Ported RAMTwo Page Dual-Ported RAM may be used for rapid D/A set up, i.e. calibration or test waveformAuto Refresh with software override on individual D/A channel for maximum waveform control. |

| 1.2.3 Support Circuitry Characteristics                                                                                                                                                                                                                                                    |

| -8/16-Bit Access using I/O Port or Memory Mapped Data Transfers24 Bit Extended Addressing with Extended Address Disable LogicPhantom Select Logic and SIXTEEN Acknowledge Status Logic'PHOLDA' Status Select Logic for DMA ApplicationsNo Wait Cycles RequriedFully Socketed.              |

| 1.2.4 Physical Characteristics                                                                                                                                                                                                                                                             |

| Dimensions 5.125 in. H x .10 in. W x .5 in. Max. D                                                                                                                                                                                                                                         |

| Weight 12 oz.                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                            |

| 1.2.5 Input Power Requirements                                                                                                                                                                                                                                                             |

| 8 VDC Input 950 ma. Max                                                                                                                                                                                                                                                                    |

| 18 VDC Input 100 ma. (NOM)*                                                                                                                                                                                                                                                                |

| -18 VDC Input 80 ma. (NOM)*                                                                                                                                                                                                                                                                |

| *Quiescent level                                                                                                                                                                                                                                                                           |

#### 1.3 Parts List

| ITEM  |   | QI  | UAN | TITY | DESCRIPTION                | SCHEMATIC DESIGNATION                                 |

|-------|---|-----|-----|------|----------------------------|-------------------------------------------------------|

| 1 (   | ) | 1   | (   | )    | P.C. Board                 | P/N 52748-9XX                                         |

| 2 (   | ) | 1   | (   | )    | 24 Pin Socket              | U28                                                   |

| 3 (   | ) | 15  | (   | )    | 20 Pin Socket              | U2, U3-U11, U16, U17,<br>U27, U31, U41                |

| 4 (   | ) | 12  | (   | )    | 16 Pin Socket              | U12, U19, U20, U22-<br>U24, U29, U32-U34,<br>U39, U42 |

| 5 (   | ) | 10  | (   | )    | 14 Pin Socket              |                                                       |

| 6 (   | ) | 4   | (   | )    | 8 Pin Socket               | U1, U26, U37-U38                                      |

| 7 (   | ) | 3   | (   | )    | 2.2 KΩ, 1/4W, 5%           | R1-R3                                                 |

| 8 (   | ) | 4   | (   | )    | 2.2 KΩ X 7 SIP, 5%         | RP1 - RP4                                             |

| 9 (   | ) | 2   | (   | )    | 80.0 KΩ, 1/4W, .1%         | R17, R22                                              |

| 10 (  | ) | 3   | (   | )    | 20.0 KΩ, 1/4W, .1%         | R16, R21, R34                                         |

| 11 (  | ) | 9   | (   | )    | 10.0 KΩ, 1/4W, .1%         | R18, R23, R24,<br>R32, R33, R35,                      |

|       |   |     |     |      |                            |                                                       |

|       |   |     |     | )    | 1/4W, .1%                  | [R12, R13],<br>[R14, R15],                            |

|       |   |     |     |      |                            | [R19, R20]                                            |

| 12 (  | ) |     |     |      | 5.0 KΩ, 1/4W, .1%          | R26, R25                                              |

| 13 (  | ) | 2   | (   | )    |                            | R41, R54                                              |

| 13A(  | ) | 6/3 | (   | )    | 2.5 KΩ/1.25KΩ<br>1/4W, .1% | [R28A, R28B]<br>[R27A, R27B]<br>[R43, R44]            |

| 14 (  | ) | 2   | (   | )    | 4.3 KΩ, 1/4W, 5%           | R29, R30                                              |

| 15 (  |   |     | (   | )    | 1 MΩ, 1/4W, 5%             | R39                                                   |

| 16 (  | ) | 1   | (   | )    | 150 Ω, 1/4W, 5%            | R56                                                   |

| 16A(  |   |     | (   | )    | 470 Ω, 1/4W, 5%            | R57                                                   |

| 151 f |   | 1   |     | 1    | 7.41.51 ()                 |                                                       |

<sup>\* [ ]</sup> Paralleled resistor pairs may be supplied as single equivalent values

#### 1.3 Parts List (continued)

| ITEM   | QUANTITY          | DESCRIPTION                                              | SCHEMATIC DESIGNATION                                                  |

|--------|-------------------|----------------------------------------------------------|------------------------------------------------------------------------|

|        | ) 16 ( )          | 0.1 µF, 20 VDC Disk<br>or Monolithic<br>Capacitor        | C1, C5, C6, C7,<br>C10, C11, C17, C18<br>C22, C24, C26-C29<br>C31, C32 |

| 18 (   | ) 6 ( )           | .01 $\mu F$ , 20 VDC Disk or Monolithic Capacitor        | C3, C23, C25<br>C30, C33, C34                                          |

| 19 (   | ) 4 ( )           | 120 pF, 20 VDC Disk<br>or Mica Capacitor                 | C21, C34A<br>CX1, CX2                                                  |

| 20 (   | ) 1 ( )           | 470 pF, 20 VDC Disk<br>or Mica Capacitor                 | C19                                                                    |

| 21 (   | ) 4 ( )           | 2.2 μF - 6.8 μF,<br>20 VDC min.Tantalum<br>Capacitor     | C8, C12, C14, C20                                                      |

| 22 (   | ) 2 ( )           | 2.2 μF - 6.8 μF<br>8 VDC min. Tantalum<br>Capacitor      | C2, C4                                                                 |

| 22A(   |                   | 2200 pF, 35 VAC<br>Polystyrene<br>Capacitor              | CA1-CA9                                                                |

| 100000 | ) 19 ( )          | Single Row Header<br>Pins<br>.100 in spacing             | Ј2, Ј4, Ј6-Ј9                                                          |

| 24 (   | ) 49 ( )<br>PAIRS | Double Row Header<br>Pins<br>.100 in spacing             | J1, J3, J5, J11,<br>J13-J17                                            |

| 25 (   | ) 30 ( )<br>PAIRS | Double Row Header<br>Right Angle Pins<br>.100 in spacing | CA, CB                                                                 |

| 26 (   | ) 1 ( )           | 74LS02 I.C.                                              | U21                                                                    |

| 27 (   | ) 4 ( )           | 74LS74 I.C.                                              | U13, U15, U18,<br>U31                                                  |

| 28 (   | ) 1 ( )           | 74LS86 I.C                                               | U14                                                                    |

| 29 (   | ) 1 ( )           | 74LS163 I.C.                                             | U19                                                                    |

| 30 (   | ) 1 ( )           | 74LS174 I.C                                              | U12                                                                    |

| 31 (   | ) 1 ( )           | 74LS240 I.C.                                             | υ4                                                                     |

#### 1.3 Parts List (continued)

| ITEM |   | QU | ANI | TTY | DESCRIPTION                 | SCHEMATIC DESIGNATION |

|------|---|----|-----|-----|-----------------------------|-----------------------|

| 32 ( | ) | 2  | (   | )   | 74LS244 I.C.                | U9, U11               |

| 33 ( | ) | 1  | (   | )   | 74LS157 I.C.                | U20                   |

| 34 ( | ) | 3  | (   | )   | 74LS289 I.C.                | U32, U33, U34         |

| 35 ( | ) | 1  | (   | )   | 74LS373 I.C.                | Π6                    |

| 36 ( | ) | 5  | (   | )   | 74LS374 I.C.                | U7, U8, U10, U16, U30 |

| 37 ( | ) | 2  | (   | )   | 25LS2521 I.C.               | U2, U3                |

| 38 ( | ) | 1  | (   | )   | 75452 I.C.                  | U1                    |

| 39 ( | ) | 2  | (   | )   | PAL16L8 I.C.                | U5, U7                |

| 40 ( | ) | 1  | (   | )   | DG508A I.C.                 | U42                   |

| 41 ( |   |    |     |     | DG509 I.C.<br>or MUX-24     | U22, U23, U24, U39    |

| 42 ( |   |    |     |     |                             | U28                   |

| 43 ( | ) | 3  | (   | )   | LF347B I.C.<br>or MC34004B  | U35, U36, U40         |

| 43A( | ) | 1  | (   | )   | LF347B I.C.                 | U2 5                  |

| 44 ( | ) | 2  | (   | )   | Am6012 I.C.                 | U27, U41              |

|      |   |    |     |     | DAC-08 I.C.                 | U29                   |

| 46 ( | ) | 1  | (   | )   | REF-01 I.C.<br>MC1404-10    | U3 8                  |

| 47 ( | ) | 1  | (   | )   | CMP-01 I.C.                 | U26                   |

| 48 ( | ) | 1  | (   | )   | LF398 I.C.                  | U37                   |

| 49 ( | ) | 8  | (   | )   | 2N2222A Transistor          | Q1-Q8                 |

| 50 ( | ) | 20 | (   | )   | 1N914A Diode                | CR1-CR16, CR18-CR21   |

| 50A( | ) | 2  | (   | )   | 1N966B Zener Diode          | CR16A, CR17           |

| 50B( | ) | 2  | (   | )   | 1N6263 Schotky Diode        | CR23A, CR23B          |

| 51 ( | ) | 1  | (   | )   | 20.0K Potentiometer         | R57                   |

| 52 ( | ) | 1  | (   | )   | LM323K, 5V, 3A<br>Regulator | VR1                   |

#### 1.3 Parts List (continued)

| IT | EM |   | QUA | ANI | TTY | DESCRIPTION                          | SCHEMATIC DESIGNATION                 |

|----|----|---|-----|-----|-----|--------------------------------------|---------------------------------------|

|    |    |   | 1   |     | )   | 7815, 15V, .5 A<br>Regulator         | VR2                                   |

| 54 | (  | ) | 1   | (   | )   | 7915, -15V, .5 A<br>Regulator        | VR3                                   |

| 55 | (  | ) | 1   | (   | )   | TO-3 Style Heatsink                  |                                       |

| 56 | (  | ) | 2   | (   | )   | TO-220 Style<br>Heatsink             |                                       |

| 57 | (  | ) | 1   | (   | )   | LED (Diode)                          | CR22                                  |

| 58 | (  | ) | 2   | (   | )   | Laminated Bus Bar (15 pin)           | 140                                   |

| 59 | (  | ) | 2   | (   | )   |                                      | Mode for economy<br>Lored to estample |

| 60 | (  | ) | 2   | (   | )   | 4 / 4                                | Note the resident rose                |

| 61 | (  | ) | 4   | (   | )   | Y 4 107 1                            | Addre                                 |

| 62 | (  | ) | 4   | (   |     |                                      | ATT - hasen to are                    |

| 63 | (  | ) | 2   | (   | )   | Card Ejector Handle                  | res surrett mission                   |

| 64 | (  | ) | 2   | (   | )   | Locking pin for<br>Item 63           | e district on the and                 |

| 65 | (  | ) | 1   | (   | )   | 28-30 GA. Wire 4.5 in.               |                                       |

| 66 | (  | ) | 1   | (   | )   | Twisted Pair Wire 28-30 GA., 3.5 in. |                                       |

| 67 | (  | ) | 1   | (   | )   | 26-30 GA. Wire                       | R55 Shorting<br>Jumper                |

| 68 | (  | ) | 14  | (   | )   | Shorting Plugs                       |                                       |

#### 2.0 Assembly and Check-Out

The assembly portion of the manual was not available at the time this manual was released. When available all registered users will be forwarded a copy of this section at no charge.

You may utilize the sample software procedures in section 8.0 for functional check-out of the board.

#### 2.1 Factory Configuration

The factory assembled and tested A/D/A Board has been configured as follows:

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Address Field<br>(A16 thru A23)  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (1120 )                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e Address Field<br>(A8 thru A15) |

| and the second s | for writing to                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | for reading from d is selected   |

| J8 pin 1 to 8 Base Add and J8 pin 4 to 5 is selec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iress of 80 Hex                  |

| J13 and J14 A11 D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | channels are voltage output      |

The above base address selection will enable direct execution of the sample Basic programs without any modifications to the code.

1.1.1 Successive Approximation of Comparation

#### 3.0 Theory of Operation

#### 3.1 A/D Section

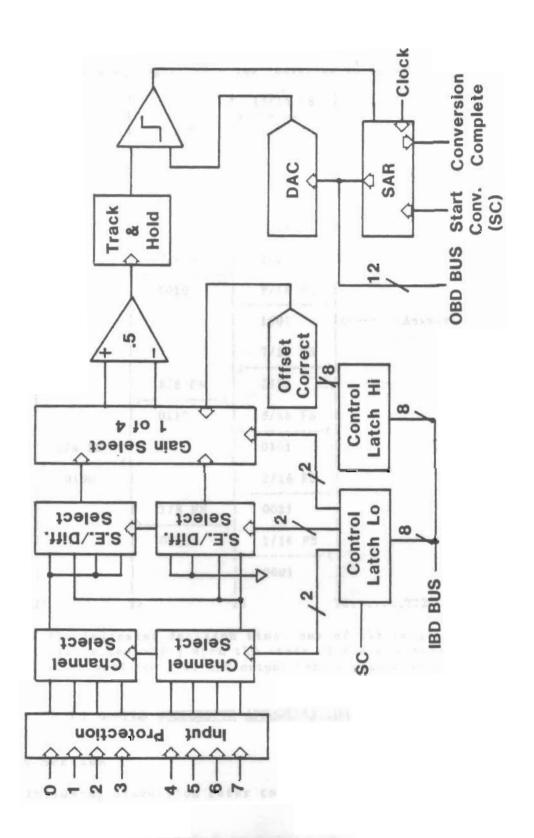

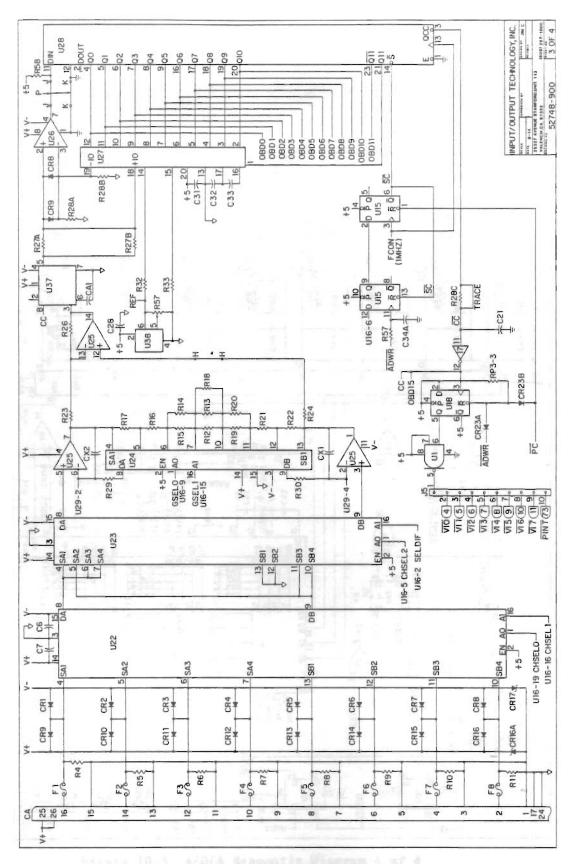

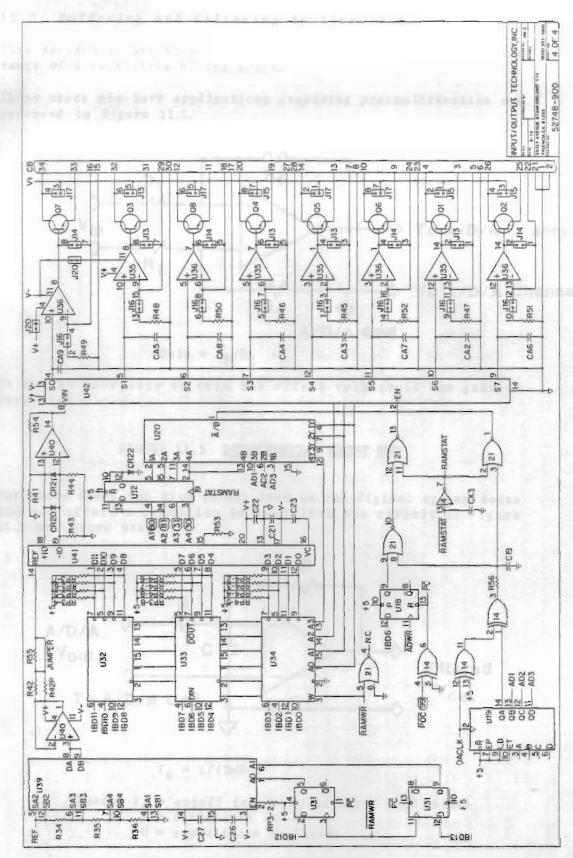

For the following discussion refer to Figure 3.1 A/D Section Block Diagram and Section 10 Schematics.

#### 3.1.1 Input Protection Networks

The eight analog inputs incorporate a protection network composed of a fuse device (optional), clamp diodes CR1 through CR16 and zener diodes CR16A and CR17. Input voltages in excess of  $\pm$  16.5 volts will be clamped and if sufficient current is available the fuse will be blown. This protects the A/D/A from serious damage resulting from excessive input voltage.

#### 3.1.2 Multiplexer

The analog switches U22 and U23 are controlled from command latch U16 to select the desired channel and to control whether that channel will be received singly or as a differential pair.

#### 3.1.3 Gain Select Circuit

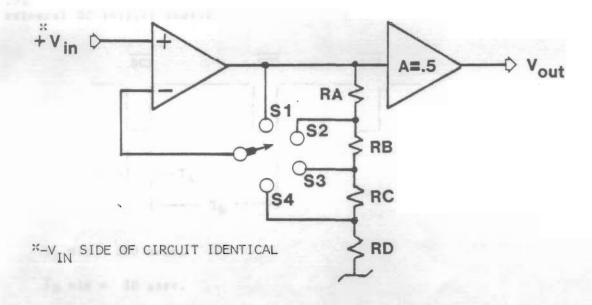

The gain select curcuit is composed of analog switch U24, op-amps U25(A,B), and resistors R12 through R22. Gain is selected by the GSELO and GSEL1 bits from control latch U16.

#### 3.1.4 Track and Hold Amplifier

This amplifier prevents slewing of the desired channel during convert time. It is permitted to track the input voltage for a period of time. Then it holds a constant voltage at the comparator input during the time of the conversion.

#### 3.1.5 Voltage Reference

This reference (U38) is a stable voltage source which is used to define the full scale voltages of all A/D and D/A conversions performed by the A/D/A. It has a fine adjust potientiometer which should not be adjusted by the user unless a precision voltmeter  $(\pm\ 0.01\%)$  is available.

#### 3.1.6 Successive Approximation Register and Comparator

These parts U27, U28, and U37 are involved in a binary search during convert time.

FIGURE 3.1 A/D SECTION BLOCK DILAGRAM

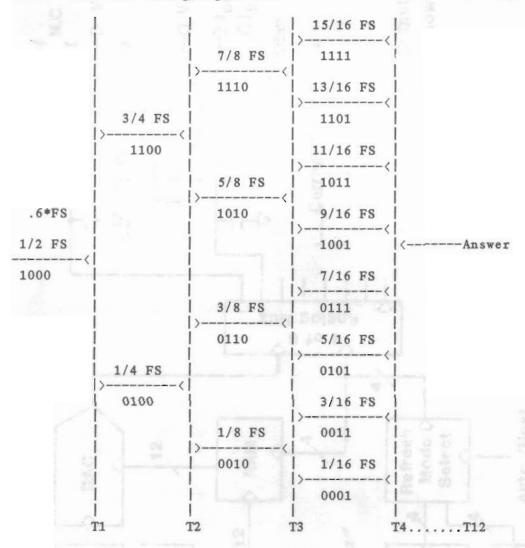

The first four bits of this algorithm will be shown here in Figure 3.2 for the benefit of those unfamilar with successive approximation techniques.

Assume that the analog signal into the converter is at 0.6 \* FS.

At each of the indicated decision times one of the indicated branches is taken depending upon the state of the comparator. i.e. the relative amplitudes of DAC output versus analog input.

#### FIGURE 3.1 SAMPLE SUCCESSIVE APPROXIMATION SEARCH

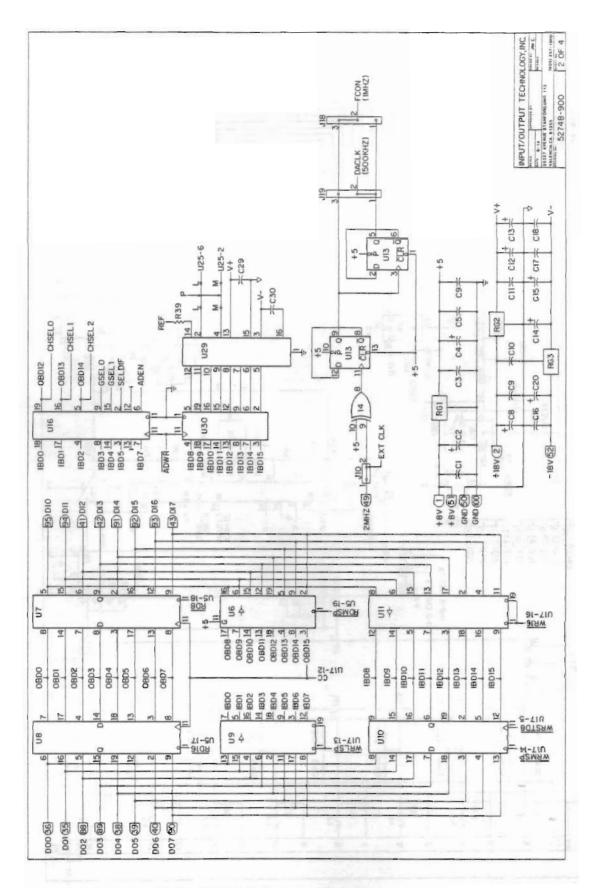

#### 3.2 D/A Section

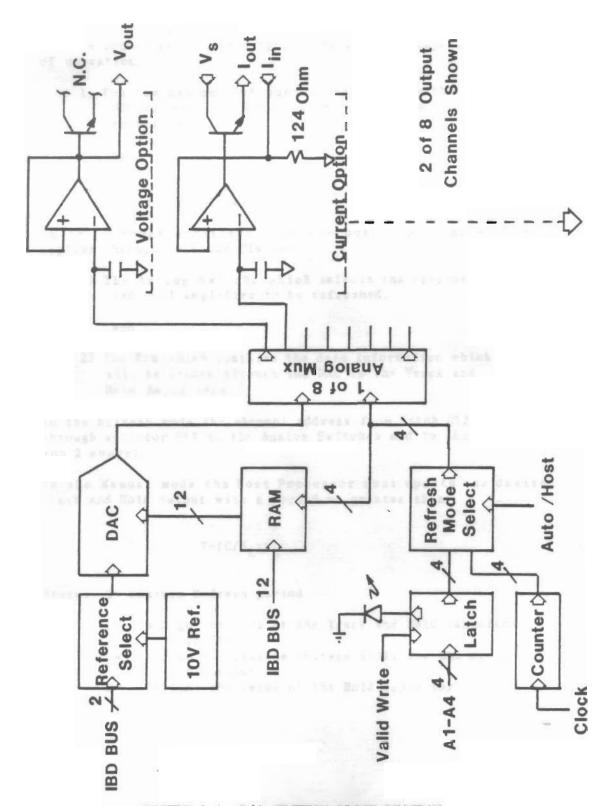

For the following discussion refer to Figure 3.3 D/A Section Block Diagram.

FIGURE 3.3 D/A SECTION BLOCK DIAGRAM

#### 3.2.1 Data Buffer

A 12-bit Ram (U32-U34) receives binary data from the host system data bus. The contents of this Ram is then presented to the 12-bit D/A converter U41. This type of data input supports two modes of operation:

The ram can be continuously recycled by the counter U20 to keep the output track and hold amplifiers refreshed,

OT

2) For tighter control of a given output, this burden may be assumed by the host processor.

In the Automatic Refresh mode the output of counter U20 is applied through selector U19 to:

The Analog Switch, which selects the current Track and Hold amplifier to be refreshed,

the sich and threat but the recipied and conversed to a larking

The Ram which contains the data information which will be loaded through the DAC to the Track and Hold Amplifiers.

In the Refresh mode the channel address from latch U12 is applied through selector U19 to the Analog Switches and to the Ram (see 1 and 2 above).

In the Manual mode the Host Processor must update the desired Track and Hold output with a period no greater than

#### $T=(C/I_L)V_S$

Where: T= maximum Refresh period

IL = leakage currents at the Track and Hold capacitor (typ 5nA)

$V_S$ = maximum permissable voltage shift for the given application

C= .0022μF, the value of the Hold capacitor

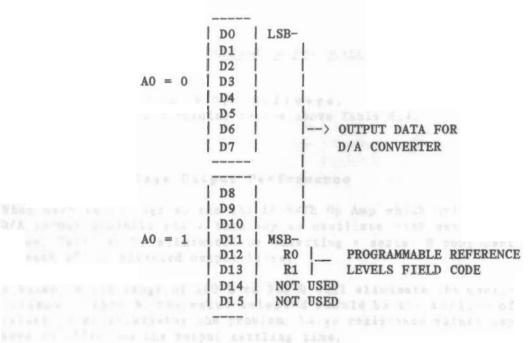

#### 3.2.2 Programmable References

Op-Amp U40, analog switch U39, and resistors R34-36 control the reference voltage applied to the DAC U41 through R42. The latch U31 is loaded with a two-bit code which selects one of four reference levels. (10V, 5V, 2.5V, and 0V).

NOTE: At power on OV is selected for the reference.

#### 3.2.3 Analog Outputs

Eight analog outputs are provided by Track and Hold amplifiers composed of analog switch U43 and Quad op-amps U35 and U36. These analog outputs are offered with a considerable number of options with regards to configuration. (See A/D configuration section 6.0.)

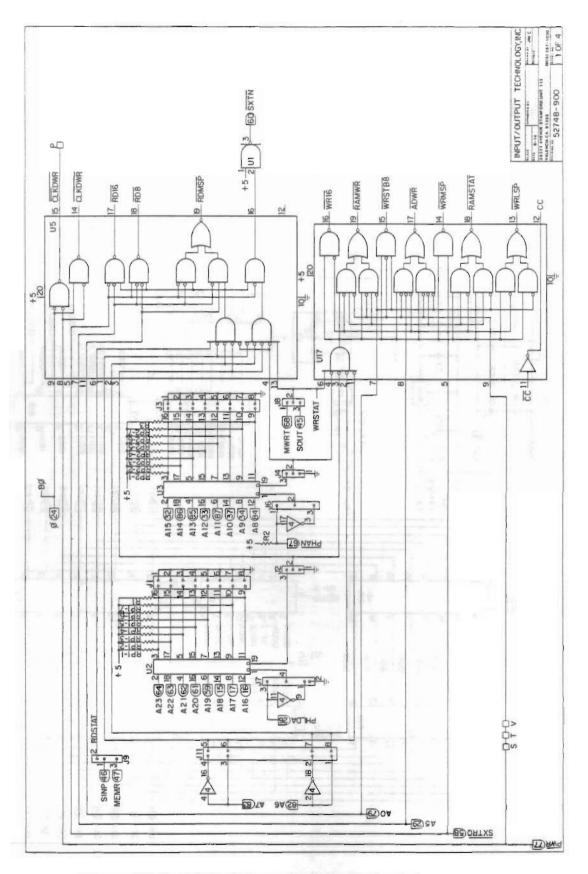

#### 3.3 Digital Section

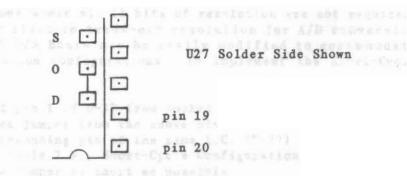

The eight-bit data buses are recieved and converted to a 16-bit input by U6 through U11. These latches and buffers are controlled by PAL'S\* (Programmable Array Logic) U5 and U17 and the Address Decoders U2 and U3. This structure is designed to support either 8 - or 16-bit data transfers according to the proposed IEEE-696 specification.

\*PAL is a trademark of Monolithic Memories,

#### 4.0 Board Configuration

The configuration process described herein should be followed in order presented in this manual. For quick look-up of specific configuration refer to the index in front of this manual.

#### 4.1 Addressing

Addressing of the A/D/A Board is accomplished through jumper selections of an upper byte, lower byte and an extended byte address value. In addition the user may select I/O or Memory Mapped I/O operation as discussed in Section 4.2.

In order to understand the selection process described in the subsequent paragraphs refer to Figure 4.1 for clarification.

# Extended Address\* For Memory Mapped I/O Application Cont'd | A7 A6 A5 A4 A3 A2 A1 A0 | | High/Low Byte

<sup>\*</sup> When A/D is selected bits A3 thru A1 are don't care.

#### FIGURE 4.1 A/D/A ADDRESSING STRUCTURE

As can be seen in Figure 4.1 the A/D/A Board may be addressed using 8, 16 or 24 bit long address fields. The user must make the proper selections and/or deselections using the on-board jumper connectors for proper operation as described in subsequent paragraphs.

<sup>\*\*</sup> Established thru hardware configuration using jumper connectors.

#### 4.1.1 Lower Byte Address Selection

The lower address byte is selected using jumper connector J-11. Only address bits A7 and A6 are user selectable thus allowing the board to reside in any one of four possible address blocks. It should be noted that the upper address byte selection described in next paragraph allows for an additional 256 possible blocks/locations, providing the CPU can support such addressing modes.

Refer to Figure 4.2 for jumper connector J-11 pin definition and Table 4.1 for the corresponding block address values.

| PIN | (1) | 1   | 0 | 0 | 1 | (8) | A6* |

|-----|-----|-----|---|---|---|-----|-----|

|     |     |     |   |   |   |     | A6  |

|     |     |     |   |   |   |     | A7* |

|     | (4) | 1   | 0 | 0 | 1 | (5) | A7  |

|     |     | 194 |   |   |   |     |     |

FIGURE 4.2 JUMPER CONNECTOR J-11 LOWER BYTE ADDRESS DEFINITION

| BLO<br>VAL | CK**                    |    | TION<br>-6 | SELECTED<br>A-7 |   |  |

|------------|-------------------------|----|------------|-----------------|---|--|

| HEX        | N. S. S. S. S. S. S. S. |    | 2-7        | 2-7 3-6 4-      |   |  |

| 00         | 00                      | Y  | N          | Y               | N |  |

| 40         | 64                      | NI | Y          | Y               | N |  |

| 80         | 128                     | Y  | N          | N               | Y |  |

| co I       | 192                     | NI | Y          | N               | Y |  |

\*\* Each block occupies 64 contiguous address locations.

TABLE 4.1 SELECTED BLOCK ADDRESS VALUES

#### Example 1:

A low byte base address of 80H (128 DEC) results in J-11 switch settings as shown in Figure 4.3 and occupies addresses 80H thru BFH.

| PIN | (1) | 1 0 | 0 1 | (8) | A6* |

|-----|-----|-----|-----|-----|-----|

|     |     | 10  |     |     |     |

|     |     | 10  |     |     |     |

|     | (4) | 1 0 | 0 1 | (5) | A7  |

FIGURE 4.3 J-11 SAMPLE JUMPER CONFIGURATION FOR 80H/128D

#### 4.1.2 Upper Byte Address Selection

The upper byte address selection applies only to processors that utilize more then 8-bits of address in their I/O addressing modes, i.e. non 8080/8085 processors or when using the Memory Mapped I/O mode.

Figure 4.4 defines jumper connector J-3 pin assignment and Table 4.2 defines the hex and decimal equivalents for these selections.

When this address option is not being utilized it must be disabled thru jumper connector J-4 as shown in next paragraph.

| 16) A15 | į,                                                 |

|---------|----------------------------------------------------|

|         | )                                                  |

| 15) A14 | +                                                  |

| 14) A13 |                                                    |

| 13) A12 |                                                    |

| 12) A11 |                                                    |

| 11) A10 | ,                                                  |

| 10) A9  |                                                    |

| 9) Á8   |                                                    |

|         | 14) A13<br>13) A12<br>12) A11<br>11) A10<br>10) A9 |

NOTE: No jumper indicates corresponding address bit as high (1).

Jumper in place indicates corresponding address bit as low (0).

FIGURE 4.4 JUNPER CONNECTOR J-3 UPPER BYTE SELECT PIN DESIGNATIONS

| DECIMAL<br>VALUE | MSB<br>  1-16<br> | 2-15 | 3-14 | 4-13 | 5-12 | 6-11 | 7-10 | LSB<br>8-9 | HEX<br>VALUE |

|------------------|-------------------|------|------|------|------|------|------|------------|--------------|

| 0                | Y                 | Y    | Y    | Y    | Y    | Y    | Y    | Y          | 0000         |

| 256              | Y                 | Y    | Y    | Y    | Y    | Y    | Y    | N          | 0100         |

| 512              | Y                 | Y    | Y    | Y    | Y    | Y    | N    | Y          | 0200         |

| 1024             | Y                 | Y    | Y    | Y    | Y    | N    | Y    | Y          | 0400         |

| 2048             | Y                 | Y    | Y    | Y    | N    | Y    | Y    | Y          | 0800         |

| 4096             | Y                 | Y    | Y    | N    | Y    | Y    | Y    | Y          | 1000         |

| 8192             | Y                 | Y    | N    | Y    | Y    | Y    | Y    | Y          | 2000         |

| 16,384           | Y                 | N    | Y    | Y    | Y    | Y    | Y    | Y          | 4000         |

| 32,768           | N                 | Y    | Y    | Y    | Y    | Y    | Y    | Y          | 8000         |

TABLE 4.2 UPPER ADDRESS BYTE JUMPER CONNECTOR J-3

PIN DESIGNATIONS

Example 2: A high byte base address of 8200H (33,280 DEC) results in J-3 jumper setting as shown in Figure 4.5. The jumper configuration was based on calculations shown in Table 4.3.

| The second second second |      | 72.  |      |      | and the second second | Calculation To Co. |      | 4   |       |

|--------------------------|------|------|------|------|-----------------------|--------------------|------|-----|-------|

| VALUE 1                  | MSB  |      |      |      |                       |                    |      | LSB | 1     |

| DECIMAL                  | 1-16 | 2-15 | 3-14 | 4-13 | 5-12                  | 6-11               | 7-10 | 8-9 | HEX   |

| VALUE                    |      |      |      |      |                       |                    |      |     | VALUI |

|                          |      |      |      |      |                       |                    |      |     |       |

| !                        |      |      |      |      |                       |                    |      | Y   |       |

| 512                      |      |      |      |      |                       |                    | N    |     | 0200  |

| !                        |      |      |      |      |                       | Y                  |      |     | !     |

| !                        |      |      |      |      | Y                     |                    |      |     |       |

| !                        |      |      |      | Y    |                       |                    |      |     | !     |

|                          |      | 9933 | Y    |      |                       |                    |      |     |       |

|                          |      | Y    |      |      |                       |                    |      |     |       |

| 32,768                   | N    |      |      |      |                       |                    |      |     | 8000  |

33,280......8200

TABLE 4.3 SAMPLE UPPER BYTE ADDRESS CALCULATION

|         | Section tion |

|---------|--------------|

| PIN (1) |              |

|         | 00           |

|         | 00           |

|         | 00           |

|         | 00           |

|         | 00           |

|         | 1001         |

|         | 00           |

|         |              |

FIGURE 4.5 J-3 SAMPLE JUMPER CONFIGURATION FOR 8200H (33,280 DEC)

For convenience, an Upper Byte Address calculation/configuration worksheet is provided in Table 4.4.

| · 12月1日日 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | MSB  |      |      |      |      |      |      | LSB  |       |

|----------------------------------------------|------|------|------|------|------|------|------|------|-------|

| DECIMAL                                      | 1-16 | 2-15 | 3-14 | 4-13 | 5-12 | 6-11 | 7-10 | 8-9  | HEX   |

| VALUE                                        |      |      |      |      |      |      |      |      | VALUE |

|                                              |      |      |      |      |      |      |      |      |       |

|                                              |      |      |      |      |      |      |      |      |       |

|                                              |      |      |      |      |      |      |      | - 1  |       |

|                                              |      |      |      |      |      |      |      | - 1  |       |

|                                              |      |      |      |      |      |      |      | 1    |       |

|                                              |      |      |      |      |      |      |      | 1    |       |

|                                              |      |      |      |      |      |      |      | 1    |       |

|                                              |      |      |      |      |      |      |      | 1    |       |

|                                              |      |      |      |      |      |      |      | 1021 |       |

#### TABLE 4.4 UPPER BYTE ADDRESS CALCULATION FORM

#### 4.1.2.1 Upper Byte Address Deselection

It is required that the Upper Byte Address selection logic be disabled if it is not being used. Jumper connector J-4 as shown in Figure 4.6 below.

| PI |     |    |    | DISABLE |

|----|-----|----|----|---------|

|    | (2) | 0  | 1  | COMMON  |

|    | (3) | 10 | 1  | ENABLE  |

|    |     |    | 50 |         |

(8) | 0 <u>6.</u> (9) Lin

MAKE PROPER SELECTION TO COMMON PIN (2)

FIGURE 4.6 JUMPER CONNECTOR J-4 UPPER ADDRESS BYTE ENABLE/DISABLE

#### 4.1.3 Extended Address Selection/Deselection\*

The purpose for this selection is to accommodate the extended addressing range as defined in IEEE-696 when using the Memory Mapped I/O mode. Namely, the standard 16 address lines are expanded to 24, thus allowing for greater addressing range. If your system does not support extended addressing skip to paragraph 4.1.3.2 Deselection.

\*Deselection applies to most 8-bit processors, i.e., Z-80, 80/85, etc., or when operating in the I/O mode.

#### 4.1.3.1 Extended Byte Address Selection

This addressing is accomplished via jumper connector J-1 and J-2. Figure 4.7 and Table 4.5 define the J-1 connector jumper pin-out and their corresponding magnitude designations, respectively.

J-2 provides the enable for the extended addressing and it must be enabled as shown in next paragraph.

| PIN | (1) | 10 | 0 | (16) | A23 |  |

|-----|-----|----|---|------|-----|--|

|     | (2) | 10 | 0 | (15) | A22 |  |

|     | (3) | 10 | 0 | (14) | A21 |  |

|     | (4) | 0  | 0 | (13) | A20 |  |

|     | (5) | 10 | 0 | (12) | A19 |  |

|     | (6) | 10 | 0 | (11) | A18 |  |

|     | (7) | 10 | 0 | (10) | A17 |  |

|     | (8) | 10 | 0 | (9)  | A16 |  |

|     |     |    |   |      |     |  |

Note: No jumper indicates corresponding address bit as high (1).

Jumper in place indicates corresponding address bit as low (0).

FIGURE 4.7 JUMPER CONNECTOR J-1 PIN DEFINITION

| DEC       | A23  | A22  | A21  | A20  | A19  | A18  | A17  | A16 | HEX       |

|-----------|------|------|------|------|------|------|------|-----|-----------|

| ROW VALUE | 1-16 | 2-15 | 3-14 | 4-13 | 5-12 | 6-11 | 7-10 | 8-9 | ROW VALUE |

| 00 000    | Y    | Y    | Y    | Y    | Y    | Y    | У    | Y   | 0 0000    |

| 65,536    | l N  |      |      |      |      |      |      |     | 1 0000    |

| 131,072   | 1    | N    |      |      |      |      |      |     | 2 0000    |

| 262,144   | 1    |      | N    |      |      |      |      |     | 4 0000    |

| 524,288   | 1    |      |      | N    |      |      |      |     | 8 0000    |

| 1,048,576 | 1    |      |      |      | N    |      |      |     | 10 0000   |

| 2,097,152 | 1    |      |      |      |      | N    |      |     | 20 0000   |

| 4,194,304 |      |      |      |      |      |      | N    |     | 40 0000   |

| 8,388,608 | 1    |      |      |      |      |      |      | N   | 80 0000   |

TABLE 4.5 JUMPER CONNECTOR J-1 EXTENDED ADDRESS DEFINITION

The extended address has no effect on other jumper selections, except that it provides an extension to the already preselected upper and lower values described in previous paragraphs.

Example 3: Table 4.6 and Figure 4.8 show how the extended address range is being calculated and configured. In similar fashion, Example 1 upper and lower values could be extended using the herein described procedure.

For convenience, an extended calculation/configuration worksheet is provided as shown in Table 4.7.

| PIN | (1) | 10-01 | (16) |                  |

|-----|-----|-------|------|------------------|

|     | (2) | 0-0   | (15) |                  |

|     | (3) | 1001  | (14) | EXTENDED ADDRESS |

|     | (4) | 0-0   | (13) | 10,747,904 DEC   |

|     | (5) | 0-0   | (12) | A4 0000 HEX      |

|     | (6) | 1001  | (11) |                  |

|     | (7) | 0-0   | (10) |                  |

|     | (8) | 1001  | (9)  |                  |

|     |     |       |      |                  |

FIGURE 4.8 SAMPLE JUMPER J-1 ADDRESS ASSIGNMENT

| DEC        | A23  |      |      |      | A19  | A18  |       | A16    | HEX         |

|------------|------|------|------|------|------|------|-------|--------|-------------|

| ROW VALUE  | 1-16 | 2-15 | 3-14 | 4-13 | 5-12 | 6-11 | 7-10  | 8-9    | ROW VALUE   |

| 14514 1444 |      |      |      |      |      |      | FALLS |        | 100 100 200 |

| 0.00       | Y    |      |      |      |      |      |       | n care |             |

| 262 144    |      | X    | AT   |      |      |      |       |        |             |

| 262,144    | 1    |      | N    | ••   |      |      |       |        | 4 0000      |

|            | 7.00 |      |      | Y    |      |      |       |        |             |

|            | 166  |      |      |      | Y    |      |       |        |             |

| 2,097,152  | 1111 |      |      |      |      |      | V     |        | 20 0000     |

|            |      |      |      |      |      |      | Y     |        |             |

| 8,388,608  | 1    |      |      |      |      |      |       | N      | 80 0000     |

10,747,904......A4 0000

TABLE 4.6 SAMPLE EXTENDED ADDRESS

THE RESERVE OF STREET, ASS. ASS.

| DEC       | A23  | A22  | A21  | A20     | A19  | A18  | A17    | A16  | HEX       |

|-----------|------|------|------|---------|------|------|--------|------|-----------|

| ROW VALUE | 1-16 | 2-15 | 3-14 | 4-13    | 5-12 | 6-11 | 7-10   | 8-9  | ROW VALUE |

|           | P77  |      |      |         |      |      |        | 100  |           |

|           | ĺ    | 2    |      |         |      |      |        |      |           |

|           |      |      |      |         |      |      |        |      |           |

|           |      |      |      |         |      |      |        |      |           |

|           | 1    |      |      |         |      |      |        | 1    |           |

|           | 1    |      |      |         |      |      |        |      |           |

|           |      |      |      |         |      |      |        |      |           |

|           |      |      |      |         |      |      |        |      |           |

|           |      |      |      | TOTAL   | PYTE | TOED |        |      |           |

|           |      |      |      |         |      |      |        | •••• |           |

|           |      |      |      | . TOTAL |      |      |        |      |           |

| 5.0       |      |      |      |         |      |      | DRESS. |      |           |

#### TABLE 4.7 EXTENDED ADDRESS CALCULATION FORM

#### 4.1.3.2 Extended Byte Address Deselection

It is required that the extended addressing option be disabled if your system does not support extended addressing. Failure to disable this option may cause erroneous operation of the address decode logic, and thus improper operation of the board.

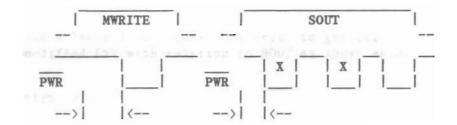

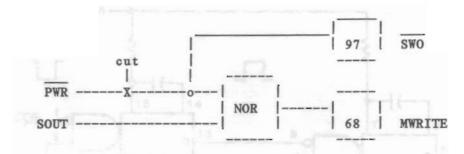

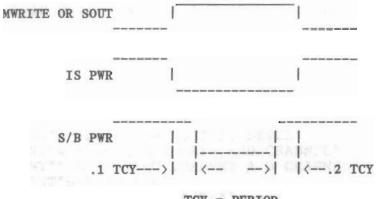

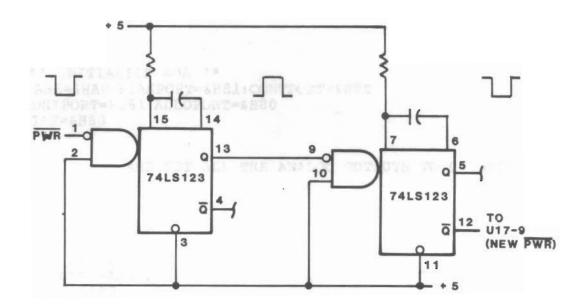

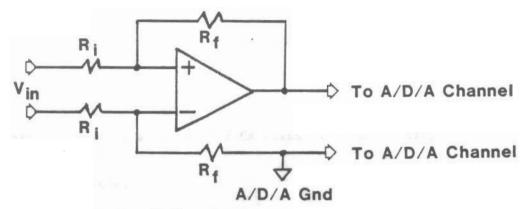

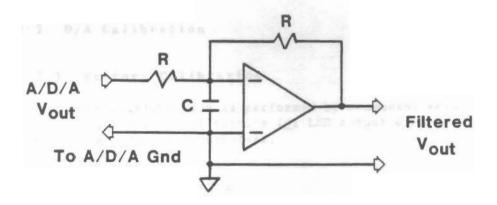

| PIN (1)   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DISABLE | MAKE PROPER    |  |