### 3.0 INPUT-OUTPUT BOARD

#### GENERAL INFORMATION

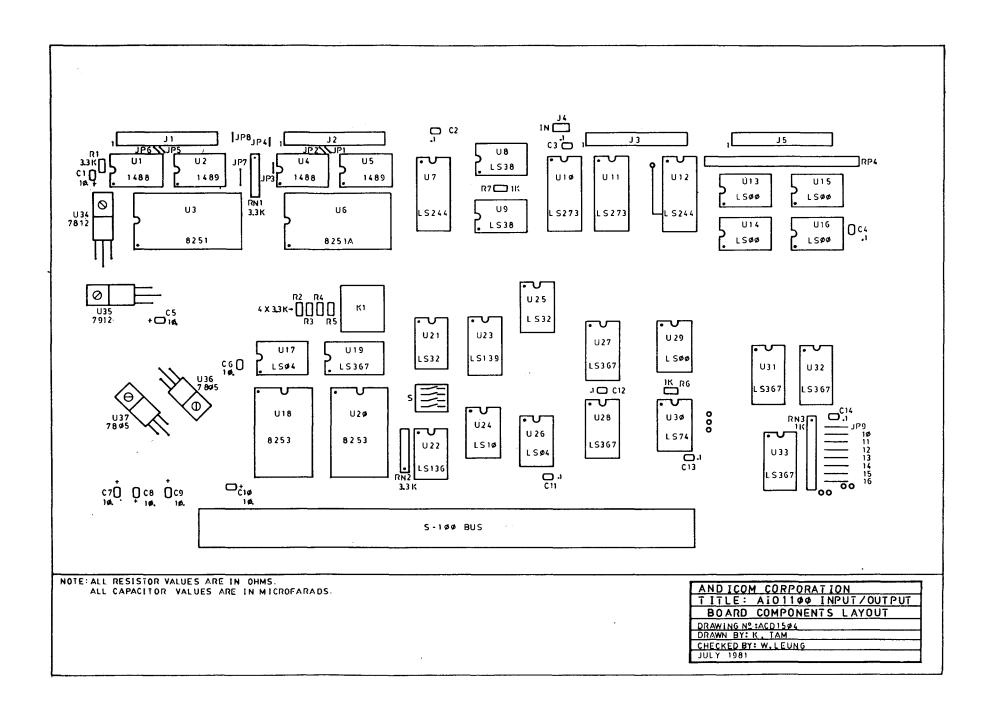

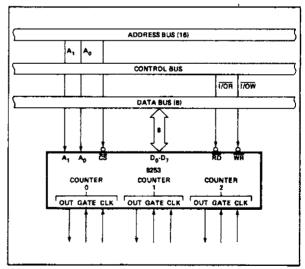

The Nabu input/output board AIO-1100 provides two serial input/output ports, one parallel output port, and six programmable 16 bit timers. The board is S-100 bus compatible and all data lines are buffered with line drivers to increase current drive capability.

The serial ports are implemented by two 8251 programmable communication interfaces (PCI's), and each has separate software programmable baud rate selection. Line drivers and receivers are provided for EIA RS-232C standard signals. The parallel output port is a simple 8-bit, D-type latch; which can be easily programmed to interface with any parallel printer.

The six programmable counters are implemented by two 8253 programmable interval timers (PIT's). Two of the six counters are configured as baud rate generators for the two serial ports, while the remaining four counters may be used as desired by the user (eg. rate generators, real time clocks, etc.).

In the Nabu 1100 System, input and output functions are done by polling through software interrogation loops. However, the I/O board is also capable of operating in an interrupt driven system. The board provides a selectable interrupt vector which allows the programmer to locate the interrupt service routine anywhere in memory.

## SPECIFIC FEATURES

#### <u>Serial Ports</u>

Full duplex RS-232C serial data communication with two external devices is permitted via the two programmable communication interfaces. The PCI features parity, overrun and framing error detection. As well, there is a choice of 1, 1 1/2, or 2 stop bits with false start bit detection, and modem control signals DSR, DTR, CTS, and RTS. The baud rates of the serial ports are software selectable and are available in a range from 110 to 9600.

In the Nabu 1100 System, connector J2 is assigned as the main console device. The associated PCI (U6) is programmed for the asynchronous transmit/receive mode, with one stop-bit, no parity, eight data bits, a 16x transmitter clock, and a baud rate of 9600.

Connector Jl is assigned as the list device in the system, which is normally a NEC Spinwriter. The associated PCI (U3) is programmed the same way as U6; the only exception being the baud rate is 1200. By connecting the reverse channel signal from the NEC printer to CTS of U3, no communication protocol is needed. However, if an 8251A is used in U3, a problem of repeating characters will occur whenever the reverse channel becomes active. This problem can be overcome by making use of DSR on U3 and performing a slight modification in the operating system (which will not be discussed here).

The port addresses are assigned as follows:

| <u>Device</u> | Connector | <u>PCI</u> | Port Address    |     |

|---------------|-----------|------------|-----------------|-----|

| Console       | J2        | U6         | Status register | 82H |

|               |           |            | Data register   | 83Н |

| List          | J1 U3     |            | Status register | 80н |

|               |           |            | Data register   | 81H |

The two 26-pin header strips (Jl and J2) are connected through two ribbon cables to the RS-232C connectors located on the back of the system. The connector associated with J1 is located above that associated with J2.

The pins are assigned as follows:

| J1 or J2 Pin Number | Pin Name   | Data Direction |

|---------------------|------------|----------------|

| 2                   | RXD        | Input          |

| 3                   | TXD        | Output         |

| 4                   | CTS        | Input          |

| 5                   | RTS        | Output         |

| 6                   | DTR        | Output         |

| 7                   | GND        | _              |

| 20                  | GND<br>DSR | Input          |

The pin numbers of the rear panel DB connector are the same as those for Jl or J2.

Jumpers JP-1 through JP-4 (on pins 6, 5, 4, and 20 respectively on connector J2) are normally not installed, since none of these modem control signals are used by the main console. However, in order for data transmission, the resistor R1 must be present to make CTS active.

Jumpers JP-5 through JP-8 (on pins 6, 5, 4 and 20 respectively on connector J1) are factory installed for interfacing to the NEC Spinwriter.

## Parallel Ports

One parallel output port is available from J3 to the user, and is normally used to interface to a parallel printer, if needed. It is assigned the address 8DH in the Nabu 1100 System. The interface cable to a Centronics parallel printer would be wired as follows:

| Signals        | J3 Pin No    | ımber | Centronics Printer Pin # |

|----------------|--------------|-------|--------------------------|

| D0             | _            |       | > 2                      |

| D2             | <del>.</del> |       | ·> 4                     |

| D3<br>D4       | <u>-</u>     |       | > 5<br>> 6               |

| D5             | 6            |       | ·> 7                     |

| D6<br>DATA STR | •            |       |                          |

| BUSY           | 9            | <     | 11                       |

| GND            | 22           | <     | >16                      |

A parallel input port is available as an option. It uses connector J4 and is assigned the same address as the parallel output port.

## Programmable Timers

Six programmable 16-bit counters are available from the two PIT's (U18 and U20). Two 16-bit counters from U18 are used as baud rate generators for the two serial ports. They are software programmable, and the baud rate can be selected to suit each user's requirements.

The four remaining counters are not used in the Nabu 1100 System. They are available to the user (through wirewrapping) for implementing a real time clock, which will be discussed in the next section.

The address assignments for the timer are as follows:

| 8253 PIT | Counter                       | Address                     | Function                                    |

|----------|-------------------------------|-----------------------------|---------------------------------------------|

| U20      | 0<br>1<br>2<br>Control regist | 84H<br>85H<br>86H<br>er 87H | Available to the user                       |

| U18      | 0<br>1<br>2<br>Control regist | 88H<br>89H<br>8AH<br>er 8BH | Clock for List PCI<br>Clock for console PCI |

For the timers used as baud rate generators, the following table relates the programmed count to the generated baud rate:

| Baud Rate                                         | Programmed Count                                            |

|---------------------------------------------------|-------------------------------------------------------------|

| 110<br>300<br>600<br>1200<br>2400<br>4800<br>9600 | 1136H<br>0417H<br>0208H<br>0104H<br>0052H<br>0026H<br>0013H |

|                                                   |                                                             |

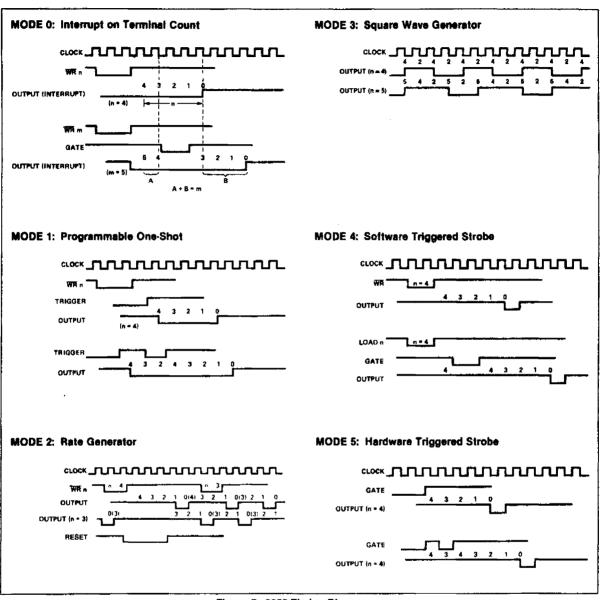

NOTE: The PIT must be programmed for mode 3 operation with binary coded decimal (BCD) counter format for these values.

## Jumper Connections

Four jumpers located near the middle of the board are used for setting the board address. They are set to 80H for the Nabu 1100 System, by installing a jumper at A7.

| 0 0 | Α4         |

|-----|------------|

| 0 0 | <b>A</b> 5 |

| 0 0 | Α6         |

| 00  | A7         |

NOTE: With jumper means logic one.

The eight jumpers located in the lower right hand corner of the board are used to establish an interrupt capability on the I/O board. The top seven jumper spaces are used to set the interrupt vector, while the bottom space enables the interrupt. Interrupts are not used in the input/output scheme for the Nabu 1100 system. However, the board is preset to enable interrupts with the interrupt vector set to 10H for future expansion to a multi-user system. Thus, the standard board is shipped with interrupt jumpers installed, as shown:

| 00  | <b>A</b> 7 |

|-----|------------|

| 00  | <b>A6</b>  |

| 00  | <b>A</b> 5 |

| 0 0 | A4         |

| 00  | <b>A3</b>  |

| 00  |            |

| 00  | Al         |

| 00  | ET         |

NOTES: 1) Interrupt vector setting: without jumper means logic one.

- 2) A0 is always logic zero.

- 3) EI setting: with jumper means enable.

The 24-pin wirewrap pad (located above the board base address setting jumpers), is used for interconnection of the timers. A connection for a real time clock implementation is shown below:

|   | GATES | VCC | GND | 2 MHz | OUTS | CKS |

|---|-------|-----|-----|-------|------|-----|

| 3 | 0     | 0   | o   | 0     | 0    |     |

| 2 | O     | 0   | 0   | 0     | 0    | مر  |

| 1 | 0     | o   | 0   | 0     | 0    |     |

| 0 | 0     | 0   | 0   | ٩     | 0    | مر  |

|   |       |     |     |       |      |     |

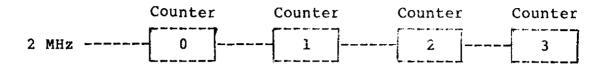

The equivalent block diagram is:

Counters #0 and 1 can be programmed to be a frequency divider so that the output of Counter #1 is a 1 Hz clock (1 second period). Counters #2 and 3 are used to accumulate the count. The counter contents can then be read by the CPU to determine the time.

By connecting the timer's output to the Interrupt Request pin of the CPU, the timer can be programmed to interrupt the CPU at a preset time. Detailed instructions on the configuration of the 8253 PIT are provided in the manufacturer's data sheets.

# NABU AIO-1100 INPUT/OUTPUT BOARD PARTS LIST

| Integrated Cir               | cuits:       |                                                                     |

|------------------------------|--------------|---------------------------------------------------------------------|

| U1, U4<br>U2, U5             | 1488<br>1489 | RS232 hex driver<br>RS232 hex receiver                              |

| U3                           | 8251         | Intel programmable communication interface                          |

| <b>U6</b>                    | 8251A        | Intel programmable communication interface (improved version)       |

| U7, U12                      | 74LS244      | Octal buffer/line-driver with 3-state outputs                       |

| u8, u9                       | 74LS38       | Quadruple 2-input positive-NAND buffer with open-collector outputs  |

| U10, U11                     | 74LS273      | Octal D-type flip-flop                                              |

| U13-U16, U29                 | 74LS00       | Quadruple 2-input NAND                                              |

| U17, U26                     | 74LS04       | Hex inverter Intel programmable interval timer                      |

| U18, U20                     | 8253         | intel programmable interval cimer                                   |

| U19, U27-U28,<br>U31-U33     | 74LS367      | Hex bus driver                                                      |

| U21, U25                     | 74LS307      | Quadruple 2-input OR                                                |

| U22                          | 74LS136      | Quad exclusive-OR with open-collector                               |

| 022                          |              | outputs                                                             |

| U23                          | 74LS139      | Dual 2-to-4-line decoder/demulti-<br>plexer                         |

| U24                          | 74LS10       | Triple 3-input NAND                                                 |

| U30                          | 74LS74       | Dual D-type positive-edge-triggered flip-flop with preset and clear |

| U34                          | 7812         | 12 V positive voltage regulator                                     |

| U35                          | 7912         | 12 V negative voltage regulator                                     |

| U36, U37                     | 7805         | 5 V positive voltage regulator                                      |

| Capacitors:                  |              |                                                                     |

| C1, C5-C10<br>C2-C4, C11-C14 | ŀ            | 10 µF 35 V tantalum electrolytic 0.1 µF                             |

| Resistors:                   |              |                                                                     |

| Rl-R5                        |              | 3.3 k <b>↑</b>                                                      |

| R6, R7                       |              | 1 k                                                                 |

| RN1, RN2                     |              | 3.3 k <b>Λ</b>                                                      |

| RN3                          |              | 1 k 🔨                                                               |

| <u>Ouantity</u>              | Description  | מפ                                                                  |

| nanicity. | Description      |

|-----------|------------------|

| 14        | 14 pin IC socket |

| 7         | 16 pin IC socket |

| 4         | 20 pin IC socket |

| 4         | 28 pin IC socket |

| <u>Ouantity</u>            | Description                                                                                                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>3<br>4<br>6<br>6 | delta 1-630-0.50 dual TO-220 heatsink 4 position dip switch 26 pin right angle pin connector 2 pin straight pin connector #6-32 x 3/8" machine screw #6-32 nuts |

| 1                          | p.c. board                                                                                                                                                      |

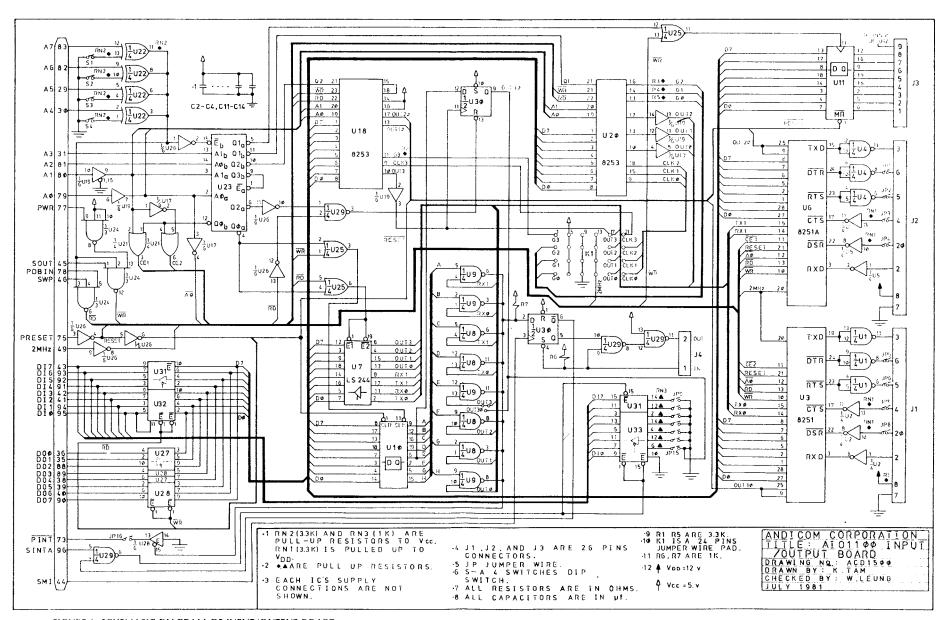

FIGURE 6: SCHEMATIC DIAGRAM OF INPUT/OUTPUT BOARD

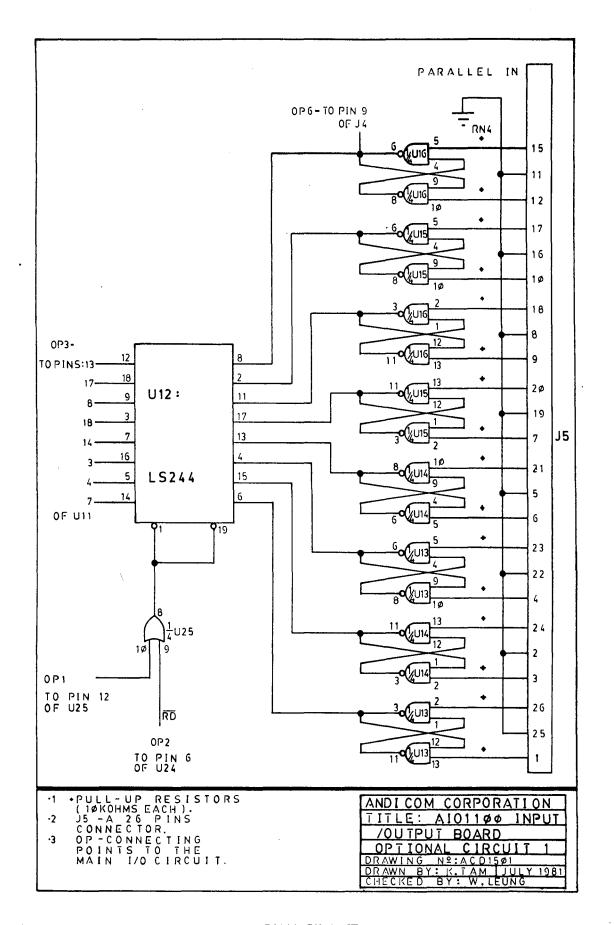

FIGURE 7: INPUT/OUTPUT BOARD OPTIONAL CIRCUIT #1

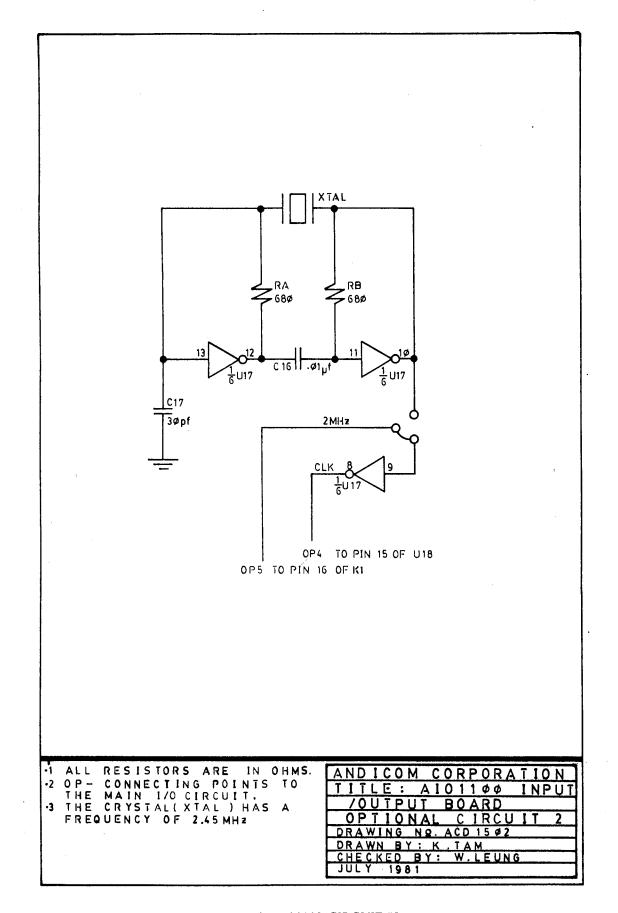

FIGURE 8: INPUT/OUTPUT BOARD OPTIONAL CIRCUIT #2

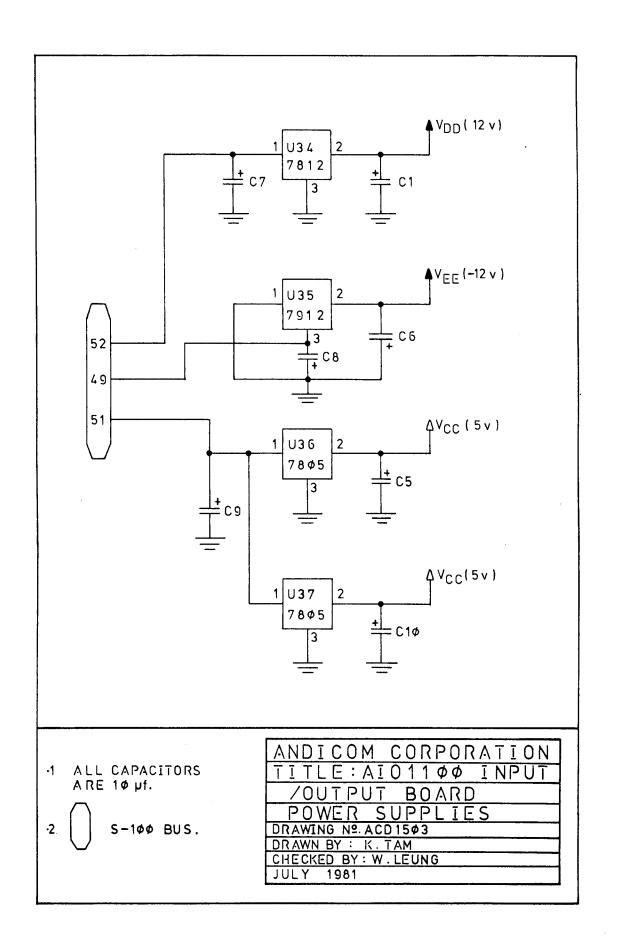

FIGURE 9: INPUT/OUTPUT BOARD POWER SUPPLY

# intel

# 8251A/S2657 PROGRAMMABLE COMMUNICATION INTERFACE

- Synchronous and Asynchronous Operation

- Synchronous 5-8 Bit Characters; Internal or External Character Synchronization; Automatic Sync Insertion

- Asynchronous 5-8 Bit Characters; Clock Rate—1, 16 or 64 Times Baud Rate; Break Character Generation; 1, 1½, or 2 Stop Bits; False Start Bit Detection; Automatic Break Detect and Handling

- Synchronous Baud Rate DC to 64K Baud

- Asynchronous Baud Rate DC to 19.2K Baud

- Full Duplex, Double Buffered, Transmitter and Receiver

- Error Detection Parity, Overrun and Framing

- Fully Compatible with 8080/8085 CPU

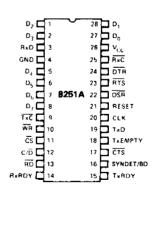

- 28-Pin DIP Package

- All inputs and Outputs are TTL Compatible

- Single + 5V Supply

- Single TTL Clock

The intel® 8251A is the enhanced version of the industry standard, Intel® 8251 Universal Synchronous/Asynchronous Receiver/Transmitter (USART), designed for data communications with Intel's new high performance family of microprocessors such as the 8085. The 8251A is used as a peripheral device and is programmed by the CPU to operate using virtually any serial data transmission technique presently in use (including IBM "bi-sync"). The USART accepts data characters from the CPU in parallel format and then converts them into a continuous serial data stream for transmission. Simultaneously, it can receive serial data streams and convert them into parallel data characters for the CPU. The USART will signal the CPU whenever it can accept a new character for transmission or whenever it has received a character for the CPU. The CPU can read the complete status of the USART at any time. These include data transmission errors and control signals such as SYNDET, TXEMPTY. The chip is constructed using N-channel silicon gate technology.

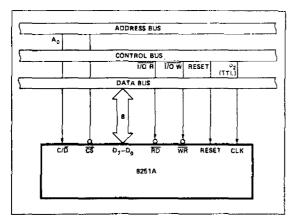

Figure 2. Pin Configuration

#### **FEATURES AND ENHANCEMENTS**

8251A is an advanced design of the industry standard USART, the Intel® 8251. The 8251A operates with an extended range of Intel microprocessors that includes the new 8085 CPU and maintains compatibility with the 8251. Familiarization time is minimal because of compatibility and involves only knowing the additional features and enhancements, and reviewing the AC and DC specifications of the 8251A.

The 8251A incorporates all the key features of the 8251 and has the following additional features and enhancements:

- 8251A has double-buffered data paths with separate I/O registers for control, status, Data In, and Data Out, which considerably simplifies control programming and minimizes CPU overhead.

- In asynchronous operations, the Receiver detects and handles "break" automatically, relieving the CPU of this task.

- A refined Rx initialization prevents the Receiver from starting when in "break" state, preventing unwanted interrupts from a disconnected USART.

- At the conclusion of a transmission, TxD line will always return to the marking state uhless SBRK is programmed.

- Tx Enable logic enhancement prevents a Tx Disable command from halting transmission until all data previously written has been transmitted. The logic also prevents the transmitter from turning off in the middle of a word.

- When External Sync Detect is programmed, Internal Sync Detect is disabled, and an External Sync Detect status is provided via a flip-flop which clears itself upon a status read.

- Possibility of false sync detect is minimized by ensuring that if double character sync is programmed, the characters be contiguously detected and also by clearing the Rx register to all ones whenever Enter Hunt command is issued in Sync mode.

- As long as the 8251A is not selected, the RD and WR do not affect the internal operation of the device.

- The 8251A Status can be read at any time but the status update will be inhibited during status read.

- The 8251A is free from extraneous glitches and has enhanced AC and DC characteristics, providing higher speed and better operating margins.

- Synchronous Baud rate from DC to 64K.

- Fully compatible with Intel's new industry standard, the MCS-85.

#### **FUNCTIONAL DESCRIPTION**

#### General

The 8251A is a Universal Synchronous/Asynchronous Receiver/Transmitter designed specifically for the 80/85 Microcomputer Systems. Like other I/O devices in a Microcomputer System, its functional configuration is programmed by the system's software for maximum flexibility. The 8251A can support virtually any serial data technique currently in use (including IBM "bi-sync").

In a communication environment an interface device must convert parallel format system data into serial format for transmission and convert incoming serial format data into parallel system data for reception. The interface device must also delete or insert bits or characters that are functionally unique to the communication technique. In essence, the interface should appear "transparent" to the CPU, a simple input or output of byte-oriented system data.

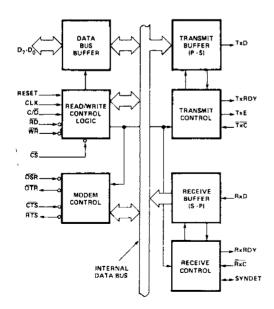

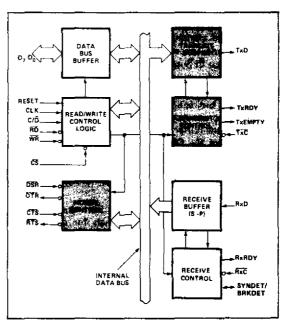

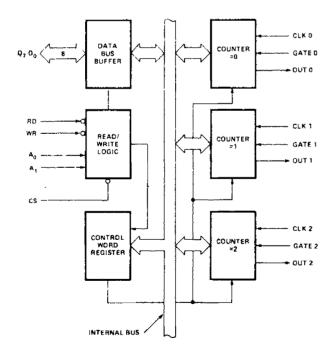

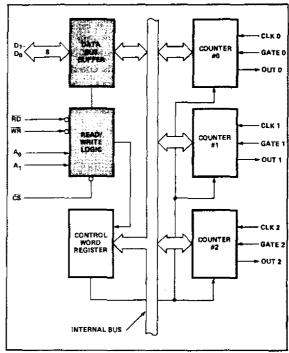

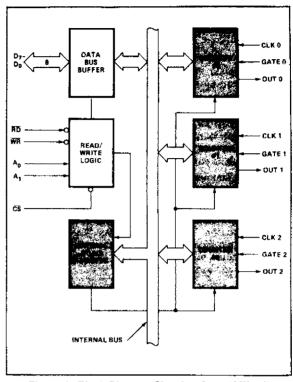

#### **Data Bus Buffer**

This 3-state, bidirectional, 8-bit buffer is used to interface the 8251A to the system Data Bus. Data is transmitted or received by the buffer upon execution of INput or OUTput instructions of the CPU. Control words, Command words and Status information are also transferred through the Data Bus Buffer. The command status and data in, and data out are separate 8-bit registers to provide double buffering.

This functional block accepts inputs from the system Control bus and generates control signals for overall device operation. It contains the Control Word Register and Command Word Register that store the various control formats for the device functional definition.

#### RESET (Reset)

A "high" on this input forces the 8251A into an "Idle" mode. The device will remain at "Idle" until a new set of control words is written into the 8251A to program its functional definition. Minimum RESET pulse width is 6 t<sub>CY</sub> (clock must be running).

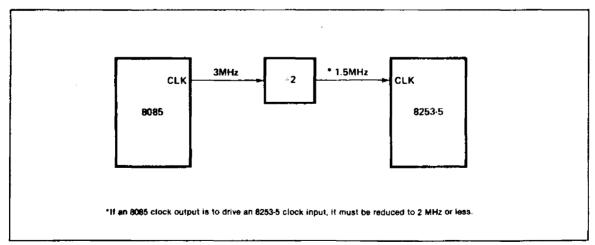

#### CLK (Clock)

The CLK input is used to generate internal device timing and is normally connected to the Phase 2 (TTL) output of the 8224 Clock Generator. No external inputs or outputs are referenced to CLK but the frequency of CLK must be greater than 30 times the Receiver or Transmitter data bit rates.

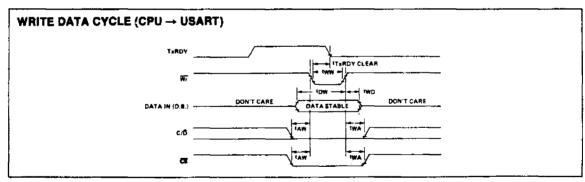

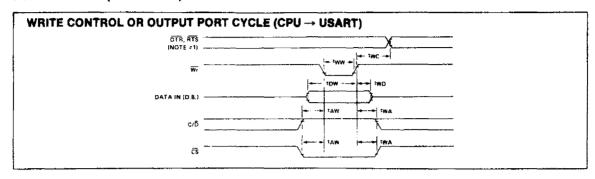

#### WR (Write)

A "low" on this input informs the 8251A that the CPU is writing data or control words to the 8251A.

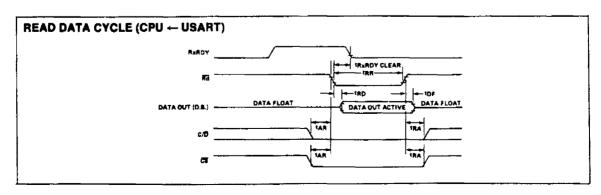

#### RD (Read)

A "low" on this input informs the 8251A that the CPU is reading data or status information from the 8251A.

#### C/D (Control/Data)

This input, in conjunction with the  $\overline{WR}$  and  $\overline{RD}$  inputs, informs the 8251A that the word on the Data Bus is either a data character, control word or status information. 1 = CONTROL/STATUS 0 = DATA

#### CS (Chip Select)

A "low" on this input selects the 8251A. No reading or writing will occur unless the device is selected. When  $\overline{CS}$  is high, the Data Bus in the float state and  $\overline{RD}$  and  $\overline{WR}$  will have no effect on the chio.

Figure 3. 8251A Block Diagram Showing Data Bus Buffer and Read/Write Logic Functions

| C/D | RD | WR | CS |                       |

|-----|----|----|----|-----------------------|

| O   | 0  | 1  | 0  | 8251A DATA - DATA BUS |

| 0   | 1  | 0  | 0  | DATA BUS - 8251A DATA |

| 1   | 0  | 1  | 0  | STATUS - DATA BUS     |

| 1   | 1  | 0  | 0  | DATA BUS → CONTROL    |

| ×   | 1  | 1  | 0  | DATA BUS → 3-STATE    |

| ×   | ×  | ×  | 1  | DATA BUS → 3-STATE    |

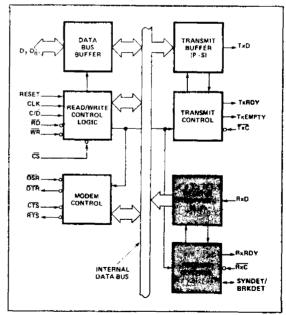

#### **Modem Control**

The 8251A has a set of control inputs and outputs that can be used to simplify the interface to almost any Modem. The Modem control signals are general purpose in nature and can be used for functions other than Modem control, if necessary.

#### **DSR (Data Set Ready)**

The DSR input signal is a general purpose, 1-bit inverting input port. Its condition can be tested by the CPU using a Status Read operation. The DSR input is normally used to test Modem conditions such as Data Set Ready.

#### **DTR (Data Terminal Ready)**

The DTR output signal is a general purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction word. The DTR output signal is normally used for Modem control such as Data Terminal Ready or Rate Select.

## **RTS (Request to Send)**

The RTS output signal is a general purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction word. The RTS output signal is normally used for Modem control such as Request to Send.

### CTS (Clear to Send)

A "low" on this input enables the 8251A to transmit serial data if the Tx Enable bit in the Command byte is set to a "one," If either a Tx Enable off or CTS off condition occurs while the Tx is in operation, the Tx will transmit all the data in the USART, written prior to Tx Disable command before shutting down. On the 8251A/S2657 if CTS off or Tx Enable off condition occurs before the last character written appears in the serial bit stream, that character will be transmitted again upon CTS on or Tx Enable on condition.

#### **Transmitter Buffer**

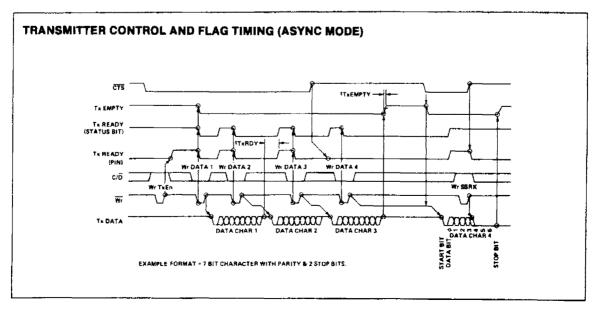

The Transmitter Buffer accepts parallel data from the Data Bus Buffer, converts it to a serial bit stream, inserts the appropriate characters or bits (based on the communication technique) and outputs a composite serial stream of data on the TxD output pin on the falling edge of TxC. The transmitter will begin transmission upon being enabled to TTS = 0. The TxD line will be held in the marking state immediately upon a master Reset or when Tx Enable/CTS off or TxEMPTY.

#### Transmitter Control

The transmitter Control manages all activities associated with the transmission of serial data. It accepts and issues signals both externally and internally to accomplish this function.

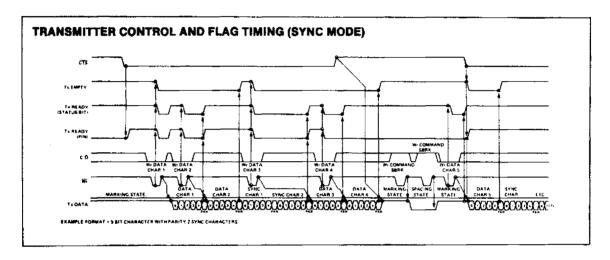

#### TxRDY (Transmitter Ready)

This output signals the CPU that the transmitter is ready to accept a data character. The TxRDY output pin can be used as an interrupt to the system, since it is masked by Tx Disabled, or, for Polled operation, the CPU can check TxRDY using a Status Read operation. TxRDY is automatically reset by the leading edge of WR when a data character is loaded from the CPU.

Note that when using the Polled operation, the TxRDY status bit is *not* masked by Tx Enabled, but will only indicate the Empty/Full Status of the Tx Data input Register.

#### TxE (Transmitter Empty)

When the 8251A has no characters to transmit, the TxEMP-TY output will go "high". It resets automatically upon receiving a character from the CPU if the transmitter is enabled. TxEMPTY can be used to indicate the end of a transmission mode, so that the CPU "knows" when to "turn the line around" in the half-duplexed operational mode.

In SYNChronous mode, a "high" on this output indicates that a character has not been loaded and the SYNC character or characters are about to be or are being transmitted automatically as "fillers". TxEMPTY does not go low when the SYNC characters are being shifted out.

Figure 4. 8251A Block Diagram Showing Modem and Transmitter Buffer and Control Functions

#### TxC (Transmitter Clock)

The Transmitter Clock controls the rate at which the character is to be transmitted. In the Synchronous transmission mode, the Baud Rate (1x) is equal to the  $\overline{TxC}$  frequency. In Asynchronous transmission mode the baud rate is a fraction of the actual  $\overline{TxC}$  frequency. A portion of the mode instruction selects this factor; it can be 1, 1/16 or 1/64 the  $\overline{TxC}$ .

#### For Example:

If Baud Rate equals 110 Baud, TxC equals 110 Hz (1x)

TxC equals 1.76 kHz (16x)

TxC equals 7.04 kHz (64x).

The falling edge of  $\overline{TxC}$  shifts the serial data out of the 8251A.

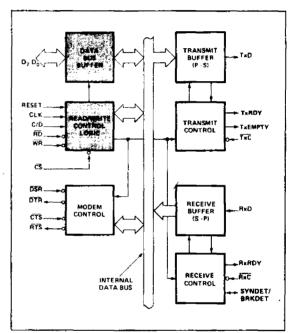

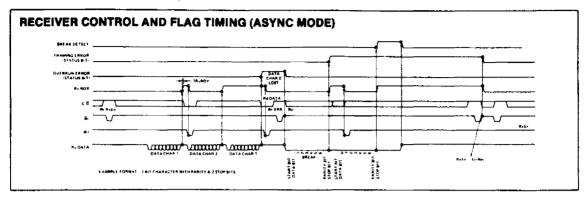

#### Receiver Buffer

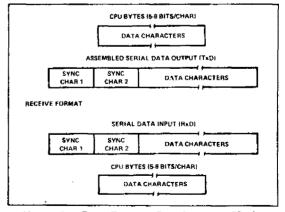

The Receiver accepts serial data, converts this serial input to parallel format, checks for bits or characters that are unique to the communication technique and sends an "assembled" character to the CPU. Serial data is input to RxD pin, and is clocked in on the rising edge of RxC.

#### **Receiver Control**

This functional block manages all receiver-related activities which consist of the following features:

The RxD initialization circuit prevents the 8251A from mistaking an unused input line for an active low data line in the "break condition". Before starting to receive serial characters on the RxD line, a valid "1" must first be detected after a chip master Reset. Once this has been determined, a search for a valid low (Start bit) is enabled. This feature is only active in the asynchronous mode, and is only done once for each master Reset.

The False Start bit detection circuit prevents false starts due to a transient noise spike by first detecting the falling edge and then strobing the nominal center of the Start bit (RxD = low).

The Parity Toggle F/F and Parity Error F/F circuits are used for parity error detection and set the corresponding status bit.

The Framing Error Flag F/F is set if the Stop bit is absent at the end of the data byte (asynchronous mode), and also sets the corresponding status bit.

#### RxRDY (Receiver Ready)

This output indicates that the 8251A contains a character that is ready to be input to the CPU. Rx RDY can be connected to the interrupt structure of the CPU or, for Polled operation, the CPU can check the condition of RxRDY using a Status Read operation.

Rx Enable off both masks and holds RxRDY in the Reset Condition. For Asynchronous mode, to set RxRDY, the Receiver must be Enabled to sense a Start Bit and a complete character must be assembled and transferred to the Data Output Register. For Synchronous mode, to set RxRDY, the Receiver must be enabled and a character must finish assembly and be transferred to the Data Output Register.

Failure to read the received character from the Rx Data Output Register prior to the assembly of the next Rx Data character will set overrun condition error and the previous character will be written over and lost. If the Rx Data is being read by the CPU when the internal transfer is occurring, overrun error will be set and the old character will be lost.

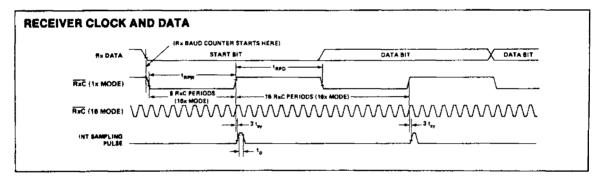

#### RxC (Receiver Clock)

The Receiver Clock controls the rate at which the character is to be received. In Synchronous Mode, the Baud Rate (1x) is equal to the actual frequency of RxC. In Asynchronous Mode, the Baud Rate is a fraction of the actual RxC fre-

quency. A portion of the mode instruction selects this factor; 1, 1/16 or 1/64 the  $\overline{R\times C}$ .

For Example:

Baud Rate equals 300 Baud, if RxC equals 300 Hz (1x)

RxC equals 4800 Hz (16x)

RxC equals 19.2 kHz (64x).

Baud Rate equals 2400 Baud, if RxC equals 2400 Hz (1x)

RxC equals 38.4 kHz (16x)

RxC equals 153.6 kHz (64x).

Data is sampled into the 8251A on the rising edge of RxC.

NOTE: In most communications systems, the 8251A will be handling both the transmission and reception operations of a single link. Consequently, the Receive and Transmit Baud Rates will be the same. Both TxC and RxC will require identical frequencies for this operation and can be tied together and connected to a single frequency source (Baud Rate Generator) to simplify the interface.

#### SYNDET (SYNC Detect)/BRKDET (Break Detect)

This pin is used in SYNChronous Mode for SYNDET and may be used as either input or output, programmable through the Control Word. It is reset to output mode low upon RESET. When used as an output (internal Sync mode), the SYNDET pin will go "high" to indicate that the 8251A has located the SYNC character in the Receive mode. If the 8251A is programmed to use double Sync characters (bisync), then SYNDET will go "high" in the middle of the last bit of the second Sync character. SYNDET is automatically reset upon a Status Read operation.

Figure 5. 8251A Block Diagram Showing Receiver Buffer and Control Functions

When used as an input (external SYNC detect mode), a positive going signal will cause the 8251A to start assembling data characters on the rising edge of the next RXC. Once in SYNC, the "high" input signal can be removed. When External SYNC Detect is programmed, the Internal SYNC Detect is disabled.

## **BREAK DETECT (Async Mode Only)**

This output will go high whenever the receiver remains low through two consecutive stop bit sequences (including the start bits, data bits, and parity bits). Break Detect may also be read as a Status bit. It is reset only upon a master chip Reset or Rx Data returning to a "one" state.

NOTE: On the 8251A/S2657, if the RxData returns to a "one" state during the last bit of the next character after the break, break detect will latch-up, and the device must be cleared by a Chip Reset.

Figure 6. 8251A Interface to 8080 Standard System Bus

#### **DETAILED OPERATION DESCRIPTION**

#### General

The complete functional definition of the 8251A is programmed by the system's software. A set of control words must be sent out by the CPU to initialize the 8251A to support the desired communications format. These control words will program the: BAUD RATE, CHARACTER LENGTH, NUMBER OF STOP BITS, SYNCHRONOUS or ASYNCHRONOUS OPERATION, EVEN/ODD/OFF PARITY, etc. In the Synchronous Mode, options are also provided to select either internal or external character synchronization.

Once programmed, the 8251A is ready to perform its communication functions. The TxRDY output is raised "high" to signal the CPU that the 8251A is ready to receive a data character from the CPU. This output (TxRDY) is reset automatically when the CPU writes a character into the 8251A. On the other hand, the 8251A receives serial data from the MODEM or \$1/0\$ device. Upon receiving an entire character, the RxRDY output is raised "high" to signal the CPU that the 8251A has a complete character ready for the CPU to fetch. RxRDY is reset automatically upon the CPU data read operation.

The 8251A cannot begin transmission until the Tx Enable (Transmitter Enable) bit is set in the Command Instruction and it has received a Clear To Send (CTS) input. The TxD output will be held in the marking state upon Reset.

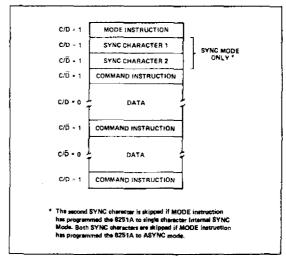

## Programming the 8251A

Prior to starting data transmission or reception, the 8251A must be loaded with a set of control words generated by the CPU. These control signals define the complete functional definition of the 8251A and must immediately follow a Reset operation (internal or external).

The control words are split into two formats:

- 1. Mode Instruction

- 2. Command Instruction

#### Mode Instruction

This format defines the general operational characteristics of the 8251A. It must follow a Reset operation (internal or external). Once the Mode Instruction has been written into the 8251A by the CPU, SYNC characters or Command Instructions may be inserted.

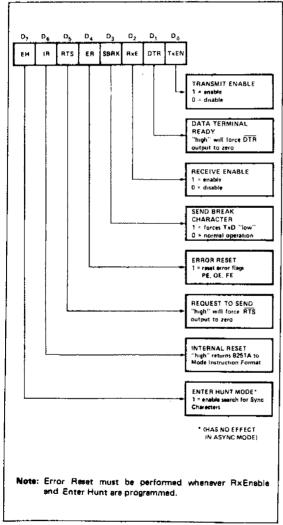

#### Command Instruction

This format defines a status word that is used to control the actual operation of the 8251A.

Both the Mode and Command Instructions must conform to a specified sequence for proper device operation. The Mode Instruction must be inserted immediately following a Reset operation, prior to using the 8251A for data communication.

All control words written into the 8251A after the Mode Instruction will load the Command Instruction. Command Instructions can be written into the 8251A at any time in the data block during the operation of the 8251A. To return to the Mode Instruction format, the master Reset bit in the Command Instruction word can be set to initiate an internal Reset operation which automatically places the 8251A back into the Mode Instruction format. Command Instructions must follow the Mode Instructions or Sync characters.

Figure 7. Typical Data Block

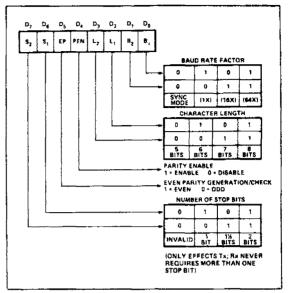

#### **Mode Instruction Definition**

The 8251A can be used for either Asynchronous or Synchronous data communication. To understand how the Mode Instruction defines the functional operation of the 8251A, the designer can best view the device as two separate components sharing the same package, one Asynchronous the other Synchronous. The format definition can be changed only after a master chip Reset. For explanation purposes the two formats will be isolated.

NOTE: When parity is enabled it is not considered as one of the data bits for the purpose of programming the word length. The actual parity bit received on the Rx Data line cannot be read on the Data Bus. In the case of a programmed character length of less than 8 bits, the least significant Data Bus bits will hold the data; unused bits are "don't care" when writing data to the 8251A, and will be "zeros" when reading the data from the 8251A.

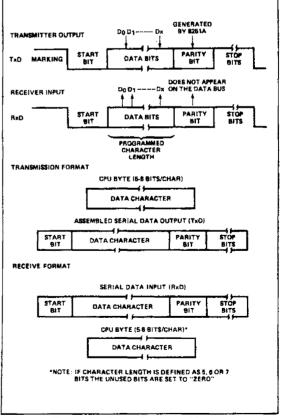

#### Asynchronous Mode (Transmission)

Whenever a data character is sent by the CPU the 8251A automatically adds a Start bit (low level) followed by the data bits (least significant bit first), and the programmed number of Stop bits to each character. Also, an even or odd Parity bit is inserted prior to the Stop bit(s), as defined by the Mode Instruction. The character is then transmitted as a serial data stream on the TxD output. The serial data is shifted out on the falling edge of TxC at a rate equal to 1, 1/16, or 1/64 that of the TxC, as defined by the Mode Instruction. BREAK characters can be continuously sent to the TxD if commanded to do so.

When no data characters have been loaded into the 8251A the TxD output remains "high" (marking) unless a Break (continuously low) has been programmed.

#### Asynchronous Mode (Receive)

The RxD line is normally high. A falling edge on this line triggers the beginning of a START bit. The validity of this START bit is checked by again strobing this bit at its nominal center (16X or 64X mode only). If a low is detected again, it is a valid START bit, and the bit counter will start counting. The bit counter thus locates the center of the data bits, the parity bit (if it exists) and the stop bits. If parity error occurs, the parity error flag is set. Data and parity bits are sampled on the RxD pin with the rising edge of RxC. If a low level is detected as the STOP bit, the Framing Error flag will be set. The STOP bit signals the end of a character. Note that the receiver requires only one stop bit, regardless of the number of stop bits programmed. This character is then loaded into the parallel I/O buffer of the 8251A. The RxRDY pin is reised to signal the CPU that a character is ready to be fatched. If a previous character has not been fetched by the CPU, the present character replaces it in the I/O buffer, and the OVERRUN Error flag is raised (thus the previous character is lost). All of the error flags can be reset by an Error Reset Instruction. The occurrence of any of these errors will not affect the operation of the 8251A.

Figure 8. Mode Instruction Format, Asynchronous Mode

Figure 9. Asynchronous Mode

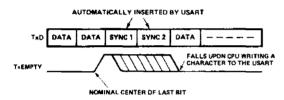

#### Synchronous Mode (Transmission)

The TxD output is continuously high until the CPU sends its first character to the 8251A which usually is a SYNC character. When the CTS line goes low, the first character is serially transmitted out, All characters are shifted out on the falling edge of TxC. Data is shifted out at the same rate as the TxC.

Once transmission has started, the data stream at the TxD output must continue at the TxC rate. If the CPU does not provide the 8251A with a data character before the 8251A Transmitter Buffers become empty, the SYNC characters (or character if in single SYNC character mode) will be automatically inserted in the TxD data stream. In this case, the TxEMPTY pin is raised high to signal that the 8251A is empty and SYNC characters are being sent out. TxEMPTY does not go low when the SYNC is being shifted out (see figure below). The TxEMPTY pin is internally reset by a data character being written into the 8251A.

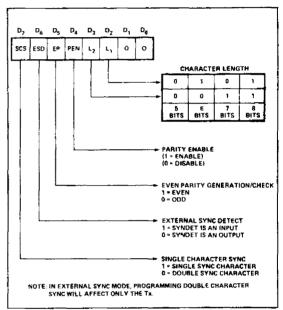

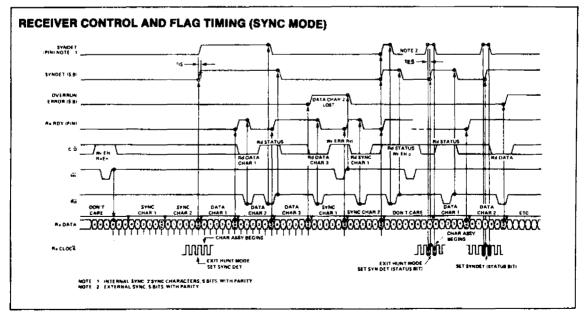

#### Synchronous Mode (Receive)

In this mode, character synchronization can be internally or externally achieved. If the SYNC mode has been programmed, ENTER HUNT command should be included in the first command instruction word written. Data on the RxD pin is then sampled in on the rising edge of RxC. The content of the Rx buffer is compared at every bit boundary with the first SYNC character until a match occurs. If the 8251A has been programmed for two SYNC characters, the subsequent received character is also compared; when both SYNC characters have been detected, the USART ends the HUNT mode and is in character synchronization. The SYNDET pin is then set high, and is reset automatically by a STATUS READ. If parity is programmed, SYNDET will not be set until the middle of the parity bit instead of the middle of the last data bit.

In the external SYNC mode, synchronization is achieved by applying a high level on the SYNDET pin, thus forcing the 8251A out of the HUNT mode. The high level can be removed after one RXC cycle. An ENTER HUNT command has no effect in the asynchronous mode of operation.

Parity error and overrun error are both checked in the same way as in the Asynchronous Rx mode. Parity is checked when not in Hunt, regardless of whether the Receiver is enabled or not.

The CPU can command the receiver to enter the HUNT mode if synchronization is lost. This will also set all the used character bits in the buffer to a "one", thus preventing a possible false SYNDET caused by data that happens to be in the Rx Buffer at ENTER HUNT time. Note that

the SYNDET F/F is reset at each Status Read, regardless of whether internal or external SYNC has been programmed. This does not cause the 8251A to return to the HUNT mode. When in SYNC mode, but not in HUNT, Sync Detection is still functional, but only occurs at the "known" word boundaries. Thus, if one Status Read indicates SYNDET and a second Status Read also indicates SYNDET, then the programmed SYNDET characters have been received since the previous Status Read. (If double character sync has been programmed, then both sync characters have been contiguously received to gate a SYNDET indication.) When external SYNDET mode is selected, internal Sync Detect is disabled, and the SYNDET F/F may be set at any bit boundary.

Figure 10. Mode Instruction Format, Synchronous Mode

Figure 11. Data Format, Synchronous Mode

## **COMMAND INSTRUCTION DEFINITION**

Once the functional definition of the 8251A has been programmed by the Mode Instruction and the Sync Characters are loaded (if in Sync Mode) then the device is ready to be used for data communication. The Command Instruction controls the actual operation of the selected format. Functions such as: Enable Transmit/Receive, Error Reset and Modem Controls are provided by the Command Instruction.

Once the Mode Instruction has been written into the 8251A and Sync characters inserted, if necessary, then all further "control writes"  $(C/\overline{D}=1)$  will load a Command Instruction. A Reset Operation (internal or external) will return the 8251A to the Mode Instruction format.

Figure 12. Command instruction Format

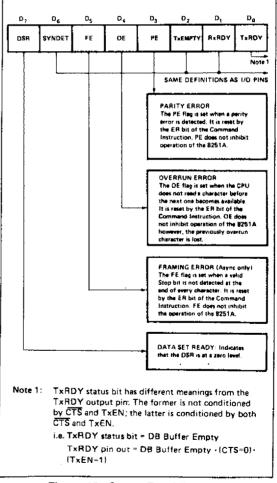

#### STATUS READ DEFINITION

In data communication systems it is often necessary to examine the "status" of the active device to ascertain if errors have occurred or other conditions that require the processor's attention. The 8251A has facilities that allow the programmer to "read" the status of the device at any time during the functional operation. (The status update is inhibited during status read).

A normal "read" command is issued by the CPU with  $C/\overline{D} = 1$  to accomplish this function.

Some of the bits in the Status Read Format have identical meanings to external output pins so that the 8251A can be used in a completely Polled environment or in an interrupt driven environment. TxRDY is an exception.

Note that status update can have a maximum delay of 28 clock periods from the actual event affecting the status.

Figure 13. Status Read Format

## **APPLICATIONS OF THE 8251A**

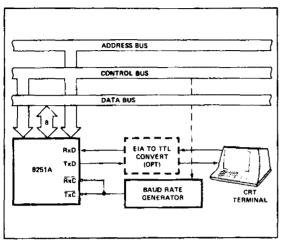

Figure 14. Asynchronous Serial Interface to CRT Terminal, DC—9600 Baud

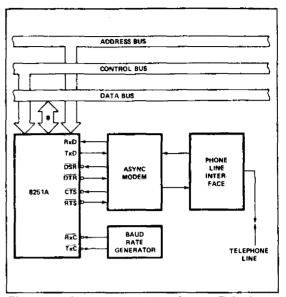

Figure 16. Asynchronous Interface to Telephone Lines

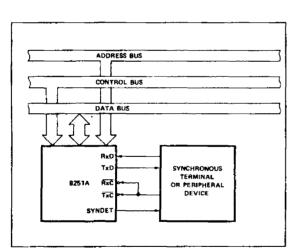

Figure 15. Synchronous Interface to Terminal or Peripheral Device

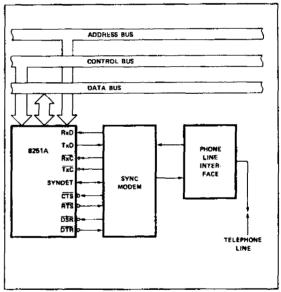

Figure 17. Synchronous Interface to Telephone Lines

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias | 0°C to 70°C    |

|--------------------------------|----------------|

| Storage Temperatura            | 65°C to +150°C |

| Voltage On Any Pin             |                |

| With Respect to Ground         | 0.5V to +7V    |

| Power Dissipation              | 1 Watt         |

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **D.C. CHARACTERISTICS** $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{CC} = 5.0V \pm 5\%, \text{ GND} = 0V)$

| Symbol           | Parameter            | Min. | Max. | Unit | Test Conditions                             |

|------------------|----------------------|------|------|------|---------------------------------------------|

| VIL              | Input Low Voltage    | -0.5 | 0.8  | V    |                                             |

| V <sub>IH</sub>  | Input High Voltage   | 2,2  | Vcc  | v    |                                             |

| VOL              | Output Low Voltage   |      | 0.45 | v    | I <sub>OL</sub> = 2.2 mA                    |

| V <sub>OH</sub>  | Output High Voltage  | 2.4  |      | V    | l <sub>OH</sub> = -400 μA                   |

| I <sub>OFL</sub> | Output Float Leakage |      | ±10  | μΑ   | V <sub>OUT</sub> = V <sub>CC</sub> TO 0.45V |

| 1 <sub>IL</sub>  | Input Leakage        |      | ±10  | μА   | V <sub>IN</sub> = V <sub>CC</sub> TO 0.45V  |

| Icc              | Power Supply Current |      | 100  | mA   | All Outputs = High                          |

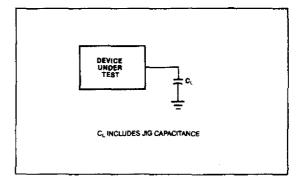

## **CAPACITANCE** $(T_A = 25^{\circ}C, V_{CC} = GND = 0V)$

| Symbol           | Parameter         | Min. | Max. | Unit | Test Conditions                 |

|------------------|-------------------|------|------|------|---------------------------------|

| CIN              | Input Capacitance |      | 10   | pF   | fc = 1MHz                       |

| C <sub>1/O</sub> | I/O Capacitance   |      | 20   | ρF   | Unmeasured pins returned to GND |

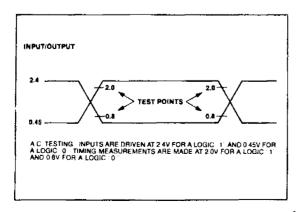

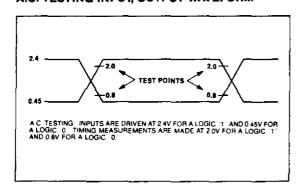

## A.C. CHARACTERISTICS $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{CC} = 5.0V \pm 5\%, \text{ GND} = 0V)$

#### **Bus Parameters** (Note 1)

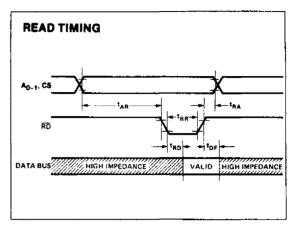

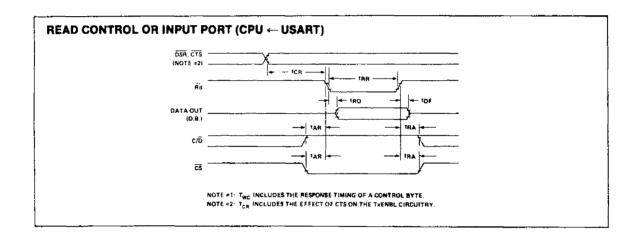

### READ CYCLE

| Symbol          | Parameter                            | Min. | Max. | Unit | Test Conditions            |

|-----------------|--------------------------------------|------|------|------|----------------------------|

| tar             | Address Stable Before READ (CS, C/D) | 50   |      | กร   | Note 2                     |

| t <sub>RA</sub> | Address Hold Time for READ (CS, C/D) | 50   |      | пs   | Note 2                     |

| tee             | READ Pulse Width                     | 250  |      | ns   |                            |

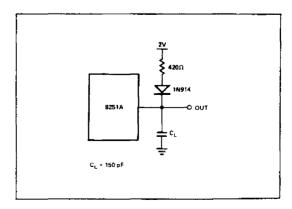

| t <sub>RD</sub> | Data Delay from READ                 |      | 250  | ns   | 3, C <sub>L</sub> = 150 pF |

| tor             | READ to Data Floating                | 10   | 100  | ns   |                            |

# A.C. CHARACTERISTICS (Continued)

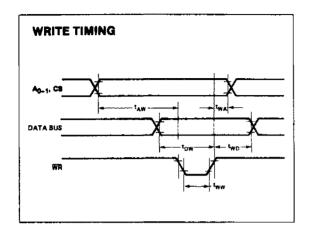

## WRITE CYCLE

| Symbol          | Parameter                    | Min. | Max.         | Unit | Test Conditions |

|-----------------|------------------------------|------|--------------|------|-----------------|

| <sup>t</sup> AW | Address Stable Before WRITE  | 50   |              | ns   |                 |

| twa             | Address Hold Time for WRITE  | 50   | -            | ns   |                 |

| tww             | WRITE Pulse Width            | 250  |              | ns   |                 |

| t <sub>DW</sub> | Data Set Up Time for WRITE   | 150  |              | ns   |                 |

| two             | Data Hold Time for WRITE     | 50   |              | ns   |                 |

| t <sub>RV</sub> | Recovery Time Between WRITES | 6    | <del> </del> | tcy  | Note 4          |

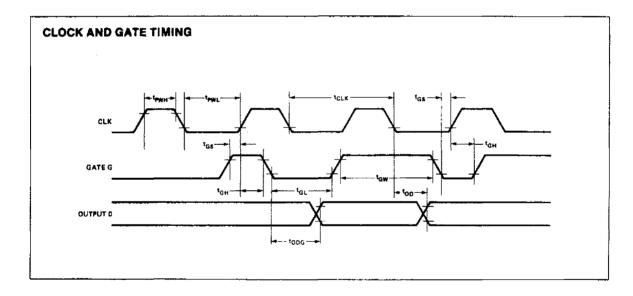

## OTHER TIMINGS

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parameter                                                 | Min. | Max.                | Unit            | Test Conditions |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|---------------------|-----------------|-----------------|

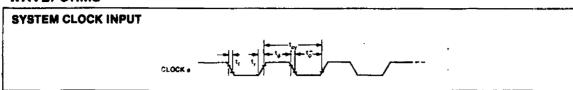

| tcy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clock Period                                              | 320  | 1350                | ns              | Notes 5, 6      |

| tφ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Clock High Pulse Width                                    | 140  | t <sub>CY</sub> -90 | ns              |                 |

| <b>t</b> \$\overline{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sq}}\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sq}}}}}}}}\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sq}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}} | Clock Low Pulse Width                                     | 90   |                     | ns              |                 |

| t <sub>R</sub> , t <sub>F</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Clock Rise and Fall Time                                  |      | 20                  | ns              |                 |

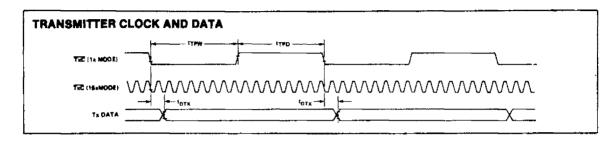

| t <sub>OTx</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TxD Delay from Falling Edge of TxC                        | 1    | 1                   | μs              |                 |

| f <sub>Tx</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transmitter Input Clock Frequency                         |      |                     |                 |                 |

| ł                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1x Baud Rate                                              | DC   | 64                  | kHz             |                 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16x Baud Rate                                             | DC   | 310                 | kHz             |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64x Baud Rate                                             | DC   | 615                 | kHz             |                 |

| t <sub>⊤PW</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Transmitter Input Clock Pulse Width                       | ]    | ]                   |                 |                 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1x Baud Rate                                              | 12   |                     | tcy             |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16x and 64x Baud Rate                                     | 1    | Ĺ                   | tcy             |                 |

| t <sub>TPD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Transmitter Input Clock Pulse Delay                       |      |                     |                 |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1x Baud Rate                                              | 15   |                     | tcy             |                 |