ANALOG CONVERSION SYSTEM

ANALOG CONVERSION SYSTEM

ANALOG TO

DIGITAL CONVERTER (88-ADG)

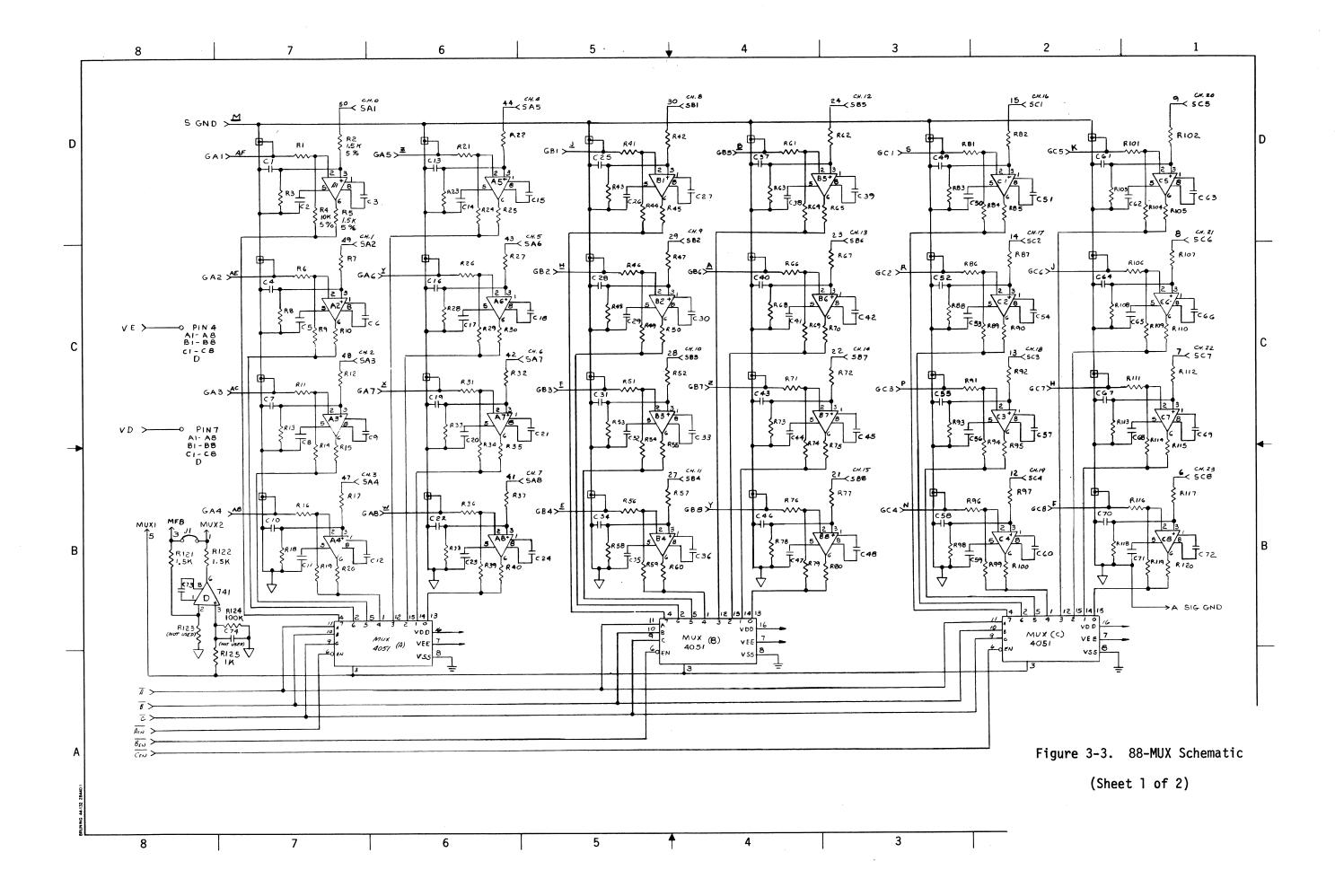

MULTIPLEXER (88-MUX)

#### MEMORANDUM

TO: Marketing, Testing and Production

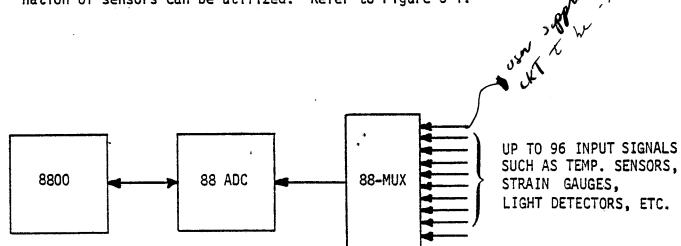

SUBJECT: 88-ADC and 88-MUX System

FROM: Engineering

DATE: 1/19/77

The following items should be noted for future reference concerning ordering, shipping and technical advice for these cards:

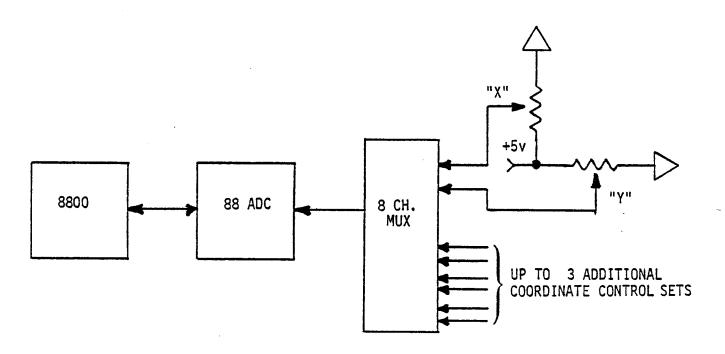

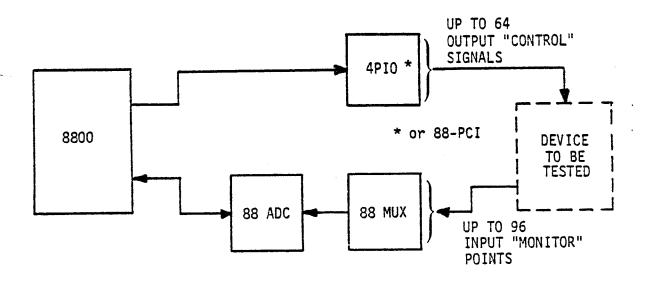

1. An A/D system is one of two basic types:

Type 1. -- 8 Channel

Type 2. -- 24 Channel

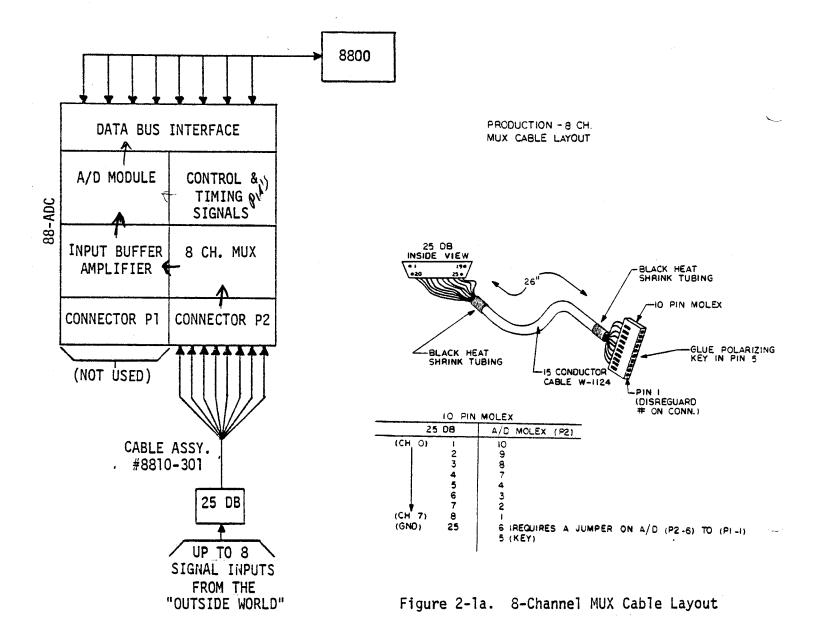

- 2. An 88-ADC card ordered without 88-MUX will be shipped with cable assembly #8810-301. (System Type 1)

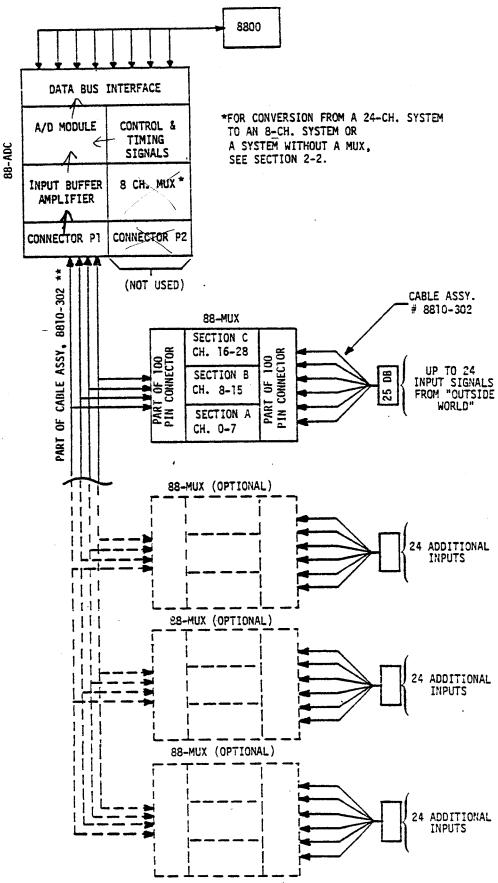

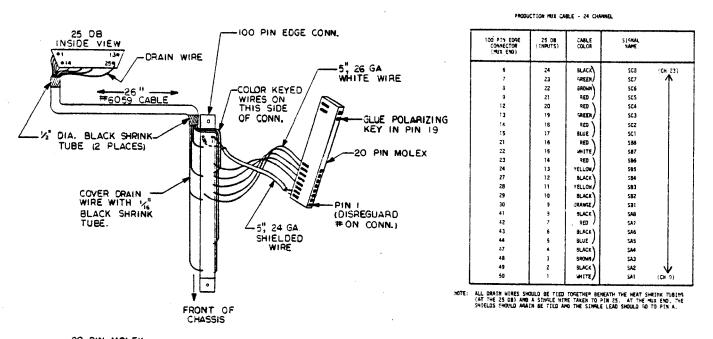

- 3. An 88-ADC card ordered in conjunction with an 88-MUX (Type 2 system) will be shipped with cable assembly #8810-302. If additional 88-MUX cards are ordered for other systems, an additional cable assembly will be shipped for each additional MUX card. If more than one 88-MUX is ordered to be used within the same system, 88-MUX option #2 below must be specified.

- 4. If an 88-MUX is ordered for a previously purchased 88-ADC and will be the only 88-MUX in the system, it will be shipped with cable assembly #8810-302.

NOTE: If additional 88-MUX cards are ordered to be used with an already existing 88-MUX card, the old cable assembly must be returned and re-worked.

- 5. Additional options are listed below:

#### Contact Engineering on all options before making a quote!!!!

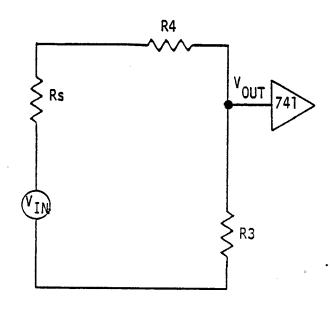

88-ADC Option #1: Differential instrumentation amplifier (AD 521). --- \$25 Extra

(Useful in noisy environments and small signal applications)

88-MUX Option #1: Differential inputs to amplifiers + special cable. -- \$15 Extra

(Useful in noisy environments)

88-MUX Option #2: Required by all systems using more than one 88-MUX. -- \$15 Extra

Special Cable Assembly

Quote 60 Days Delivery on all Options

## 68-ADC OPTION #1

(Differential Configuration)

The AD 521 should be implemented as follows:

- 1. Drill out drill hole (D2). (D2) is a square pad directly beneath R6 on the board. This isolates input pin 3 of the amplifier from ground. (Use a #61 drill)

- 2. Remove the 741 (B) and insert the AD 521 (C).

- 3. If resistor (R3) is present, remove it. (Note that scaling and/or filtering are not offered in differential configuration)

- 4. If the (4051) MUX IC (U) is present, remove it.

- 5. Select gain desired according to:

| GAIN | R7               |                | 4.     |

|------|------------------|----------------|--------|

| 1    | 100K ohaw a c.4K |                | 164 10 |

| 10   | 10K ohm          | R8 = 100K  ohm |        |

| 100  | 1K ohn           |                | 161    |

| 1000 | 100 olua         |                | ,      |

Use precision resistors and solder R7 and R8 into the board.

- 6. A suitable cable may be made by using 2 conductor shielded wire. One conductor goes to PI-2 and the other, PI-4. The shield should go to PI-1.

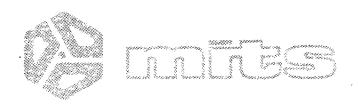

- 7. If AC ground loops are present, erratic results may be obtained especially in high gain or lowlevel signal applications. Try ungrounding the shield or tying the shield first to one side, then the other differential input line.

If some form of internal AC ground path is inavertently supplied at the A/D (-) terminative signal sean by the (+) amplifier terminal will vary according to changing current in the ground loop. Thus output of the amplifier will reflect this variation subtiplied by the gain factor!

8. At high gains, noise may be improved by adding a IR ohm resistor in series with Pl-Pin 4 and the ADS21 - Pin 3. Also task a 47 bpf capacitor between Pins 1 and 3 of the amplifier, hosping all leads as short as possible.

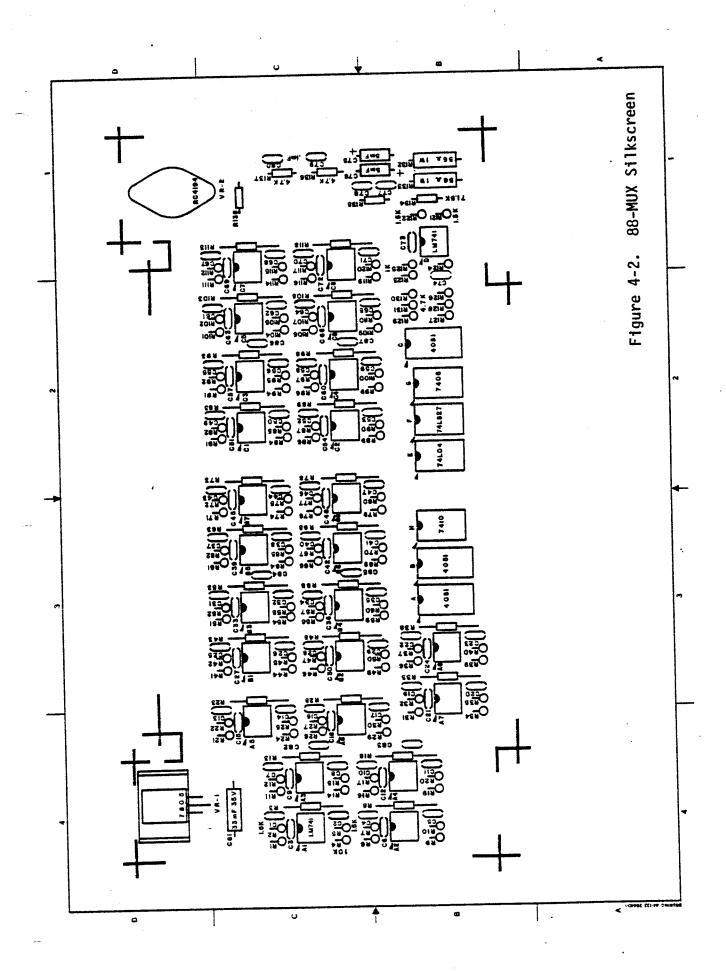

#### 88-MUX OPTION #1

(Differential Configuration)

To modify an 88-MUX, perform the following steps:

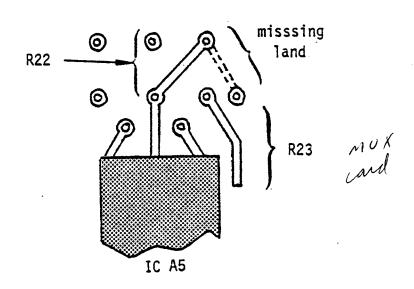

1. Drill out all drill holes in ground lines of PC Card. Refering to the PC card layout there are 24 lands with double feed thru holes near the top of the card. The bottom feedthru of each land should be drilled out with a #61 bit (.039"). Care should be taken not to break the land away from the top feedthru yet insure the entire removal of the plating-thru the card on the bottom hole.

2. For amplifier #1, gain is determined by the formula:

Gain Factor =

$$\frac{R4}{R1}$$

where  $R4$  =  $R3$  and  $R2$  =  $R1$ .

Choose R4  $\leq$  1 meg ohm for optimum noise and frequency response. Use of precision resistors is recommended for R1 - R4. Note also that for amplifier #2, R6-R9 replace R1-R4, respectively, and so on for all 24 circuits. Note that scaling and filtering is not possible in differential mode.

3. A differential-type special cable must be used for each 88-MUX with differential option. (Assy. #8810-303)

#### 88-MUX OPTION #2

(For conversion from single to multiple 88-MUX systems.)

- 1. Each 88-MUX requires one cable assy. #8810-302 (Assy # 8810-303 if differential MUX Option #1).

- 2. Remove the connection to Pin #1 at the 100 pin edge connector end and reconnect to Pin #5. The ten wires going to the 20 pin Molex connector should be cut off all cables except for one cable which will interface the 88-ADC.

NOTE: It may be necessary to remove the connection at Pin A, strip back the wire, and reconnect Pin A. Use care not to short the shield wire to any other pins.

- 3. Connect a short length of wire from Pin 16 on one edge connector to Pin 16 on the next connector thus tying Pin 16 on all MUX edge connectors together via a "daisy-chain".

- 4. In a similar manner daisy-chain Pin 17, 18, 20, X, V, U and T on all edge connectors.

- 5. In a similar manner daisy-chain Pin 5 across all edge connectors. If desired, use a short piece of shielded cable and tie the shield ends to Pin A at each connector. Be careful not to short any pins with the exposed shield.

is intechoper

# 168-120Z Analog-to-Digital Converter

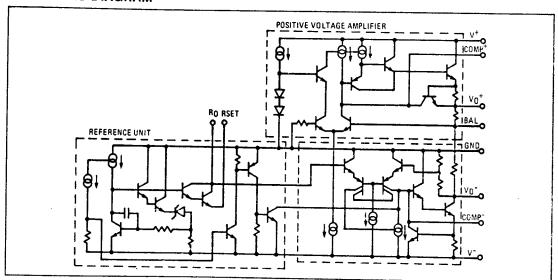

#### DESCRIPTION

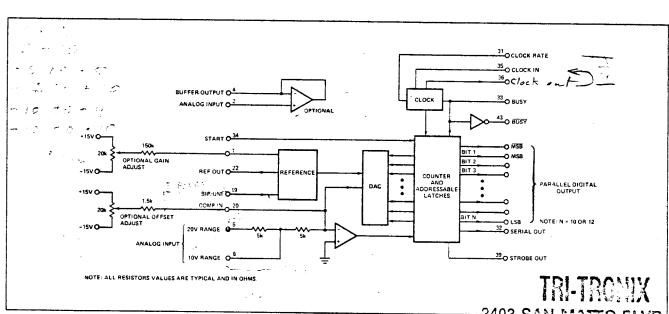

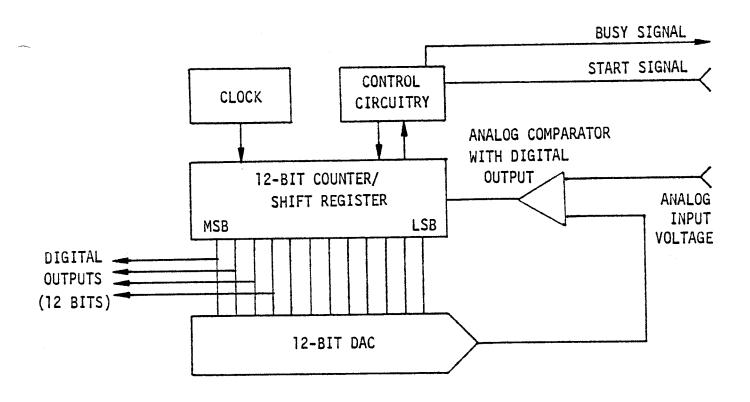

The 168-12QZ Analog-to-Digital Converter is designed for accurate and reliable performance with adjustment-free but versatile operation, at low cost. An improved form of the successive-approximation technique of conversion is used to convert unipolar input voltages (0 to +5 V, 0 to +10 V) or bipolar input voltages ( $\pm$ 5 V, or  $\pm$ 10 V) to corresponding digital output codes of straight binary, offset binary or two's complement binary. The successive-approximation technique compares the analog input with the output of a D/A converter that tests each bit successively (MSB first) until the D/A output is equal to the analog input, within the quantizing error.

Versatility and convenience of operation are key features of the 168-12QZ. Based on the unprecedented circuit design of the 170/171 family, these converters are completely self-contained, low-profile modules that include a precision D/A converter, high-speed voltage comparator, precision temperature compensated reference network, clock, counter and latch circuitry. They are designed for user flexibility. By varying external pin connections, four different analog input ranges and three different types of digital output codes can be obtained. Both BUSY and it's complement are provided to allow synchronization with other external components: such as output storage latches, sample/hold amplifiers, or multiplexers.

With this pin-compatible and function compatible converter, Intech/Function Modules takes the worry out of single sourcing.

#### **FEATURES**

- 12-Bit Resolution and Accuracy

- No Missing Codes from 0 to +70°C

- 40 μs Conversion Time

- DTL/TTL Logic Levels

- Versatile Configurations

- A Real Pin-for-Pin and Function Replacement for Analog Devices ADC-12QZ

Figure 1. Function Block Diagram

2403 SAN MATEO BLVD., N.E.

SUITE 2 SOUTH BUILDING

ALBUQUERGUE, NEW MEXICO 87110

Roberthopez

# ELECTRICAL SPECIFICATIONS (Typical @ 25°C and ±15 V Supply)

| Parameter                                                              | 168-12QZ                                                                                        | Unit                       |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------|

| RESOLUTION, Binary                                                     | 12                                                                                              | bits                       |

| RESOLUTION, Billary                                                    | 16                                                                                              | 576                        |

| ACCURACY Quantizing Error Nonlinearity Error max                       | ± ½<br>± ½                                                                                      | LSB<br>LSB                 |

| Differential Nonlinearity Error max Missing Codes, 0 to 70° C          | ±½<br>None                                                                                      | LSB                        |

| Offset Error <sup>1</sup><br>Gain Error <sup>1</sup>                   | ±10<br>±0.05                                                                                    | mV<br>%                    |

| STABILITY                                                              |                                                                                                 |                            |

| Offset vs Temperature Unipolar max Bipolar max Gain vs Temperature max | ±5<br>±10<br>±30                                                                                | ppm/°C<br>ppm/°C<br>ppm/°C |

| Differential Nonlinearity vs Temperature max Power Supply Sensitivity  | ±10                                                                                             | ppm/°C                     |

| Offset Gain Warm-up Time                                               | ±10<br>±20<br>5                                                                                 | ppm/%<br>ppm/%<br>minutes  |

| CONVERSION TIME <sup>2</sup>                                           | 40                                                                                              | μs                         |

|                                                                        |                                                                                                 | 1                          |

| ANALOG INPUT Input Voltage Range Unipolar Bipolar Input Impedance      | 0 to +5, +10<br>-5 to +5, -10 to +10                                                            | <b>V</b>                   |

| 0 to +5 V FS<br>0 to +10 V, ±5 V FS<br>±10 V FS                        | 2.5<br>5<br>10                                                                                  | kΩ<br>kΩ<br>kΩ             |

| Buffered <sup>3</sup>                                                  | 1000                                                                                            | MΩ                         |

| LOGIC INPUT <sup>4</sup> Start  Clock In                               | Positive pulse, DC coupled 100 ns min width, rise & fall time 1 µs max, 2 TTL loads 1 TTL load  |                            |

| LOGIC OUTPUTS <sup>4</sup>                                             |                                                                                                 |                            |

| Data (Parallel or Serial)                                              | T.T.L level, 5 unit loads/<br>bit                                                               |                            |

| Busy                                                                   | HI during conversion,<br>5 unit loads                                                           |                            |

| Strobe                                                                 | Serial data synchroni-<br>zation, 5 unit loads                                                  |                            |

| Codes Unipolar (Parallel or Serial) Bipolar                            | Binary, positive true                                                                           |                            |

| Parallel<br>Serial                                                     | Offset Binary, positive true or two's complement binary, positive true  Offset Binary, positive |                            |

| Serial                                                                 | true true                                                                                       | 1                          |

| INTERNAL REFERENCE                                                     | yes                                                                                             |                            |

| TEMPERATURE RANGE                                                      | 2                                                                                               | 00                         |

| Rated Operation                                                        | 0 to +70<br>-25 to +85                                                                          | °C<br>°C                   |

| Storage                                                                | -55 to +125                                                                                     | °c                         |

| POWER SUPPLY Voltage Current                                           | ±15 ±2%, +5 ±5%                                                                                 | v                          |

| +15 V<br>-15 V                                                         | 20<br>30<br>210                                                                                 | mA<br>mA                   |

210

#### NOTES:

- . Offset and gain errors are adjustable to zero.

- Conversion time is measured from the trailing edge of the START pulse to the HI going LO transition of the BUSY output.

- Units with buffer available on special order only. Add \$20.00 to price for 1 to 24 quantity.

Specify B on order.

- All digital inputs and outputs are completely TTL compatible. One unit load is identical to that defined for standard 54/74 series TTL.

#### **ACCURACY**

For an analog-to-digital converter, the accuracy specifications provide a "window" of analog input level that can cause a particular digital output. All ADC's have an inherent quantizing effect that causes an uncertainty of  $\pm \frac{1}{2}$  LSB. This  $\pm \frac{1}{2}$  LSB is the limit in resolution of a particular ADC. With a resolution of 12 bits binary and with a maximum differential nonlinearity of  $\pm \frac{1}{2}$  LSB or  $\pm 0.0122\%$  of full scale, the 168-12QZ ADC offers excellent accuracy and performance for general purpose, low cost systems.

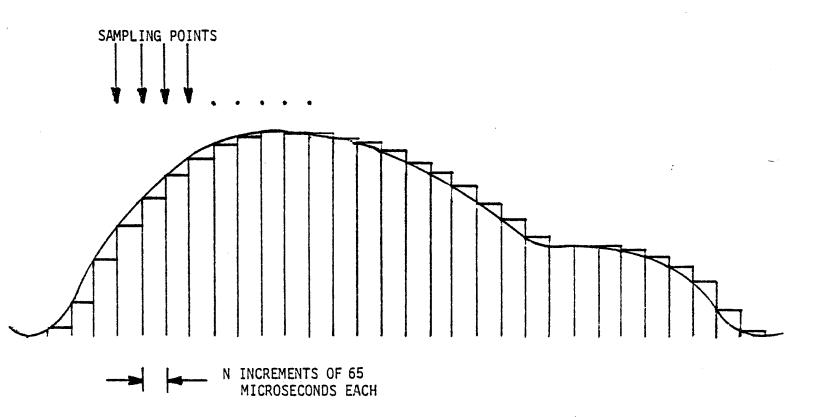

#### **CONVERSION TIME**

The total time necessary to make a conversion is independent of input signal level. This is because the successive-approximation technique of conversion must make all bit comparisons regardless of input level. The actual conversion time will depend on clock frequency which may vary as much as  $\pm 20\%$  from unit to unit. But the absolute maximum conversion time including temperature variation will never be more than  $40~\mu s$ .

#### CODING

Full-scale for the 168-12QZ is determined by external pin connections. The converter can accept unipolar inputs of 0 to  $\pm$ 5 V or 0 to  $\pm$ 10 V and bipolar analog inputs of  $\pm$ 5 V or  $\pm$ 10 V. One least-significant-bit (LSB) and converter coding is shown in the following table.

|          |                 | Bits (Data Output) |   |   |     |    |    |    |

|----------|-----------------|--------------------|---|---|-----|----|----|----|

|          | Analog<br>Input | 1 MSB              | 2 | 3 | . 9 | 10 | 11 | 12 |

| Unipolar | +(FS-1 LSB)     | 1                  | 1 | 1 | 1   | 1  | 1  | 1  |

| Straight | ½ FS            | 1                  | 0 | 0 | 0   | 0  | 0  | 0  |

| Binary   | 1 LSB           | 0                  | 0 | 0 | 0   | 0  | 0  | 1  |

|          | 0               | 0                  | 0 | 0 | 0   | 0  | 0  | 0  |

|          | (+(FS-1 LSB)    | 1                  | 1 | 1 | 1   | 1  | 1  | 1  |

|          | ½ FS            | 1                  | 1 | 0 | 0   | 0  | 0  | 0  |

| Bipolar  | 1 LSB           | 1                  | 0 | 0 | 0   | 0  | 0  | 1  |

| Offset   | 0               | 1                  | 0 | 0 | 0   | 0  | 0  | 0  |

| Binary   | -1 LSB          | 0                  | 1 | 1 | 1   | 1  | 1  | 1  |

|          | - 1/2 FS        | 0                  | 1 | 0 | 0   | 0  | 0  | 0  |

|          | -FS             | 0                  | 0 | 0 | 0   | 0  | 0  | 0  |

|          |                 |                    |   |   |     |    |    |    |

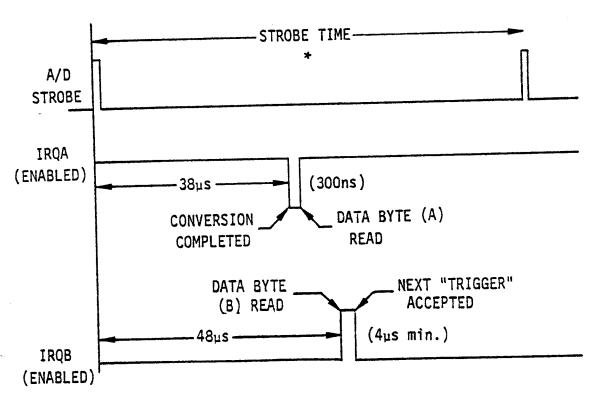

#### **OPERATION**

A positive-going pulse with a minimum width of 100 ns to the START convert input will initiate the conversion cycle. This pulse must be a TTL level (+2.4 minimum for HI, +0.4 maximum for LO) and capable of

250 KHz

+5 V

toberthopez

driving 2 TTL loads. The BUSY output will switch to a logic HI approximately 75 ns later. The trailing edge of the START convert pulse begins the conversion by setting the most significant bit, bit 1 (MSB) to the LO state and bits 2 through 12 to the HI state. At the end of conversion, the BUSY output goes from HI to LO (+2.4 V minimum to +0.4 V maximum). At this time, the conversion is completed and the parallel digital output is valid.

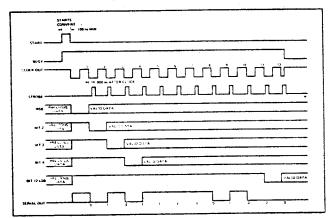

The conversion will be completed approximately 150 ns ahead of the BUSY output negative-going transition, so the leading edge of the BUSY or  $\overline{\rm BUSY}$  can be used as a strobe to transfer the output data. Because of the technique of conversion, the total conversion time will always be the same regardless of the input level, but will never be more than 40  $\mu \rm s$ . Therefore, the converter can be externally commanded to convert at rates of up to 25,000 conversions per second. See Figure 2 for timing diagram.

#### CONNECTING THE CLOCK

Although the 168-12QZ contains its own internal clock oscillator, connection to it is accomplished with an external jumper between pins 35 and 36 of the module. This jumper between CLOCK OUT (pin 36) and CLOCK IN (pin 35) must be installed unless otherwise specified. The 168-12QZ is intended to operate only with the internal clock.

The internal clock is set to run at the maximum permissable rate. Although running it at a slower rate will not nprove the converter's accuracy, in some applications a slower conversion time may permit synchronization or compatibility with interfacing equipment. This may be accomplished by connecting a capacitor between CLOCK OUT (pin 36) and CLOCK RATE ADJ (pin 31). The conversion time can be extended to at least 35 ms in this manner. The capacitor's value is determined by the formula:

Conversion Time (in

$$\mu$$

s)  $\approx (1 + \frac{C_{ext}}{2000})$ .

where Cext = external capacitance in pF.

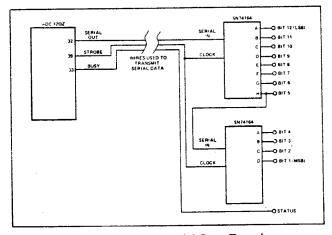

#### SERIAL DATA OUTPUT

A latched serial output (taken from the output of a TTL flip-flop) is brought out to pin 32. The data is transmitted MSB first, and is coded positive-true offset binary for bipolar input ranges. Prior to the beginning of a conversion this output will match the state of the twelfth bit (LSB) of the previous conversion (assuming the previous conversion was allowed to go to completion). In most applications the state of the serial output prior to the beginning of a conversion will be of no consequence.

Figure 3 indicates one method for transmitting data serially to a remote location using only three wires plus a digital ground). The data is clocked into a receiving shift register using the 168-12QZ strobe output as a clock source for the shift register.

The Timing Diagram (Figure 2) shows that the serial data bits are valid on successive strobe pulse leading edges ("0" to "1" transitions). This allows the strobe

pulse to clock the shift register directly, since the shift register transfers information on "O" to "1" transitions of the clock input. The first bit, which is the MSB is valid on the first strobe pulse's leading edge. Each complete conversion has exactly twelve strobe pulses, one for each bit.

Figure 2. Timing Diagram

## **OPTIONAL EXTERNAL ADJUSTMENTS**

#### **OFFSET ADJUST**

As a user option, the analog input offset can be adjusted by applying an offset voltage to Comp In input (pin 20). A 20  $k\Omega$  trim potentiometer with excitation voltage of  $\pm 15$  V and the wiper connected to pin 20 through a 1.5  $M\Omega$  resistor will provide approximately  $\pm 20$  LSB of adjustment. If finer adjustment is required, then the range of adjustment can be reduced by adding a larger resistor in series with the potentiometer wiper. Pin 20 should be left open if an offset adjustment is not needed.

#### **GAIN ADJUST**

The gain, or scale factor, may also be externally adjusted. A 20 k $\Omega$  trim potentiometer with excitation voltage of  $\pm 15$  V and the wiper connected to GAIN ADJUST (pin 1) through a 150 k $\Omega$  resistor will provide approximately  $\pm 13$  LSB range of adjustment. If finer adjustment is required, then the range of adjustment can be reduced by adding a larger resistor in series with the potentiometer wiper. Pin 1 should be left open if a gain adjustment is not needed.

Figure 3. Block Diagram - Serial Data Transfer

# Roberthopez

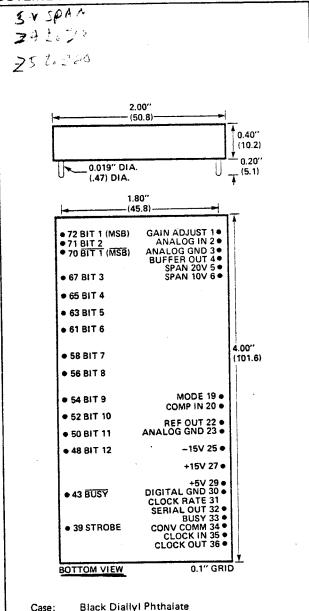

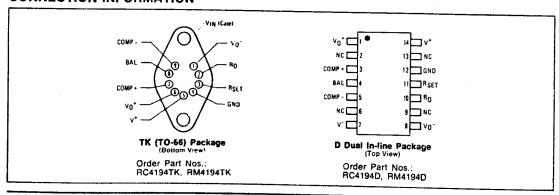

#### PIN CONNECTIONS

#### INPUT SCALING

The input voltage range is selectable by pin connection. When the optional internal, high-impedance, buffer amplifier is used, the BUFFER output is connected to the SPAN inputs. For a 10 V SPAN, connect the BUFFER output (pin 4) to SPAN 10 V (pin 6). For a 20 V SPAN, connect BUFFER output (pin 4) to SPAN 20 V (pin 5). For a 5 V SPAN, connect the BUFFER output (pin 4) to SPAN 10 V (pin 6) and connect SPAN 20 V (pin 5) to COMP IN (pin 20). When not using the internal buffer amplifier, connect the analog input directly to the SPAN inputs.

UNIPOLAR OPERATION (0 to +5 V or 0 to +10 V With Or Without Optional Buffer Input)

Connect the MODE output (pin 19) to ANALOG COM-MON (pin 23) Use SPAN 10 V (pin 6) for 0 to +10 V input range. For 0 to +5 V input range use SPAN 10 V (pin 6) as ANALOG INPUT and connect SPAN 20 V (pin 5) to COMP IN (pin 20). The output code will be natural binary.

#### **BIPOLAR OPERATION**

Connect the MODE output (pin 19) to COMP IN (pin 20). Use SPAN 10 V (pin 6) for ±5 V input range, SPAN 20 V (pin 5) for ±10 V input range. The output code will be natural offset binary. For Two's Complement coding use MSB (pin 70) as the most-significantbit (<del>bit 1</del>).

#### ZERO ADJUSTMENT PROCEDURE

- 1. Unipolar operation:

- a. Set input voltage to precisely +½ LSB.

- b. Adjust offset control until converter just barely switches from 000000000000 to 00000000001.

- 2. Bipolar operation:

- a. Set input voltage to precisely minus full scale +% LSB.

- b. Adjust offset control until converter just barely switches from 000000000000 to 00000000001.

# GAIN ADJUSTMENT PROCEDURE

- 1. Set input voltage to precisely full scale less ½ LSB. Note this is 11/2 LSB less than nominal full scale.

- 2. Adjust gain control until converter just barely switches from 111111111110 to 111111111111.

#### GROUNDING CONNECTIONS

The DIGITAL COMMON (pin 30) must be connected externally to the ANALOG COMMON (pin 23) at same point in the system. Also, the commons of the +5 V and  $\pm 15$  V power supplies must be tied to this same common. For optimum performance, the system common should be located at the A/D converter and separate power supplies should be committed to the A/D converter. But if the power supplies are shared among several loads, then the recommended practice is to connect the DIGITAL COMMON directly to the +5 V common. The supply commons are then connected to a central common.

### **OUTLINE DIMENSIONS**

Case:

Gold-flashed over silver plated 1/2 hard brass Pins:

4007 Weight: MS 2040 Socket:

#### PIN CONNECTIONS

- 1. Pins 23 and 30 must be connected together externally.

- 2. Pins 3 and 23 are connected internally.

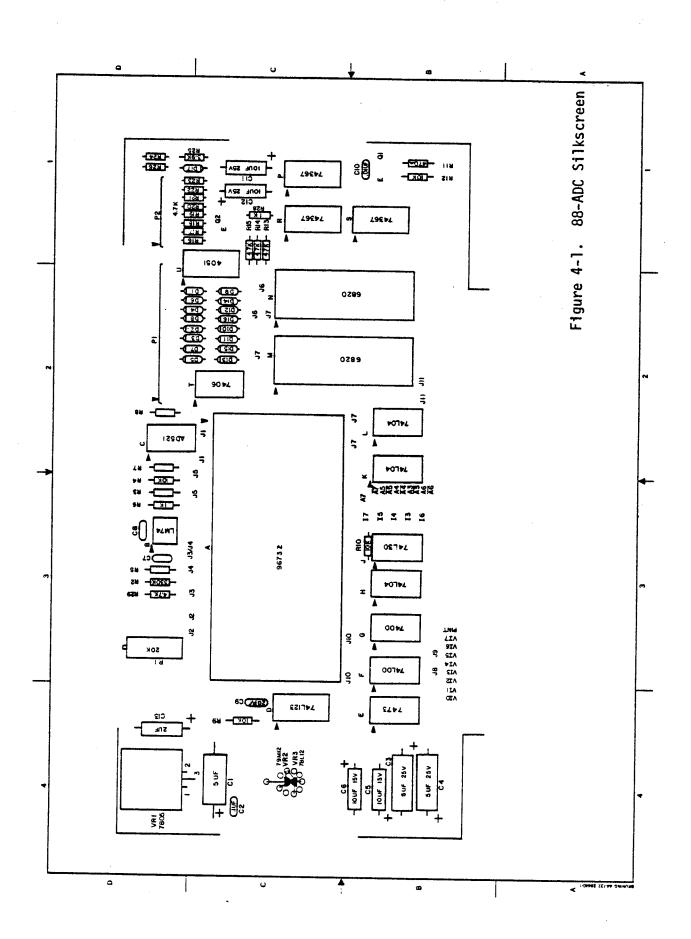

88-ADC TEST

Equipment Required

You will need a 8800 A, B, or Sherwood Chassis, (\*Sherwood A to D Cards must) CLOAD D be tested in a Sherwood Chassis) and a Terminal. The chassis should contain the following: A CPU, at least 8K of memory; IO Card and two switchable Extender Cards. You will also need a voltage source. Optional cards which will help include: ACR. (3.2) 8K Basic on Proms. Switches down examine back to tero, lift fill backup if to I have a 25 TO, then hit run. write CluADB -> start tage

Load Basic and load MUX Diagnostic program either from paper tape or cassette Spasses10 -> n.+ reterra, when it reaches 46, TTY Will 15/2+ tape. Examine the 88 ADC Card for the following before you place it in the chassis. Sec zero adjustme

# PRODUCTION 88-ADC

Production A to D Cards can be identified by 2 small regulators located under the +5V regulator on the left side of the card. Production A to D Cards also have 2 connectors along the top and most components holes will have parts installed.

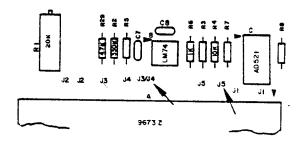

Inspect the card for the following jumpers. 5 address jumpers @ approx. lower center of the board. Above the A to D module jumper @ J2 and jumper @ J3 to J4. Correct J3 to use in the right hand J3. NOTE

Inspect the back side of the card for jumpers between pin 6 and pin 8 of IC U(CD 4051) jumper from Pl pin 1 to P2 pin 6. +5VDC land going to R13. R14 & \$15 should be cut very near the resistors and a jumper should go from the common resistor pad to the +12VDC land. This is the 2nd land down from the top of the There should be no other jumpers on the card.

#### TEST

Stop and reset the computer. Turn off all three switches on the extender IMPORTANT card. Carefully plug the A to D Card into the extender card. Turn on all three \_\_\_itches. Verify that the computer is still at location 0 and that it contains an octal 363 at location 0.

on mux Bd Black Box Leads

go on right side of thepacitors

Fower Supplies in left hand corner of bd.

Check with a scope or meter pins 25(-12V), 27(+12) and 29(+5V) on the A to D

Ko heithope z

ile. These three voltages should be within +.5VDC of the listed value.

Power supply voltage must be correct before you proceed.

## Zero Adjustment

24 channels

Run program, enter "3,3" and ch "0": the teletype should start printing a voltage. Connect the voltage source cable to connector Pl on the A to D Card.

Measure the voltage going into Pl with a digital voltmeter, adjust this voltage for -5.000 volts (+.005 volts leave DVM connected while setting zero comp).

between -4.5 and -5. volts. If not locate and correct the defect. Adjust RI (located at the top left side of the A to D) until the teletype is printing -5. Teletype to the left the teletype is printing -5 when you start you will have to adjust RI until the teletype prints -4.9xxx volts. The teletype will not print values more negative than -5 volts. With the teletype printing -4.9xxx now adjust RI until it just prints -5.0. This completes the zero compensation adjustment.

### Tracking

\*\*Disreguard stamped "1" on plastic connector

Page 3 Roberthops =

# 24 Channel Control Test

Stop and reset the computer. Turn all 3 switches off on the extra extender card. Connect a known good 24 channel mux cable to a known good 88-(Production)

Mux Card. Carefully insert the Mux card into the extender card. Turn on all three switches. Insure that the computer is at address zero and data is octal 363.

If not reset and deposit as required. Connect the 20 pin connector to the A to D card and connect the mux cable to the voltage source. Run the program. Enter "3,3" and ch "#0". Set voltage source selector switch to "decrement" position. Set the gain switch for gain 1. Adjust source until TTY just prints 5. "Control C" on the teletype. Run the program. Enter "2,3". The teletype print out should have ch#0 = 500. All other channels should descend in value (example ch#0 = 500 ch #1 = 487)

1#2 = 450). Absolute value is not important-only that each channel is lower in value then the next higher channel #.

Place voltage source selector in the "incr" position. Run the program & enter "2,3". Ch #0 should now be the lowest value and Ch #23 should be the highest value. Each channel should be slightly higher in value then the previous channel.

This completes the A to D test.

Toberthope 2

| STOCK WI                                             | THORAWL SHEET DEPT:         |         |           |        | 1     | DATE:       |       |                                              |

|------------------------------------------------------|-----------------------------|---------|-----------|--------|-------|-------------|-------|----------------------------------------------|

| PAGE /                                               | OF <u>2</u> ,               |         | ED BY: _  |        |       |             |       |                                              |

| TO BUILD                                             | QTY: OF: 88 A/D COM         | HERTE   | R BOAR    | D Aus  | C4726 | E - Panno   | 10571 | <u>-                                    </u> |

| ing the specific to the specific terms of the second | PLEASE ENTER QUANTITIES IN  | PENCIL  | TO FACI   | LITATE | CHAN  | GES         |       |                                              |

| IITS P/N                                             | NAME AND DESCRIPTION        | QTY. PE | RI QTY    | SSUED  | SHORT | REMARKS     | COST  |                                              |

| 100190                                               | A/D PRINTED CIRCUIT BOARD   | 1       |           |        |       |             |       |                                              |

|                                                      | HEAT SINK, SMALL            | 1       |           |        |       |             |       |                                              |

|                                                      | 6-32 × 3/3 SEREW            | J       |           |        |       |             |       | <u> </u>                                     |

|                                                      | 6 LOCKINASHER               | 1       |           |        |       |             |       |                                              |

|                                                      | 6-32 HEX NUT                | 1       |           |        |       |             |       |                                              |

|                                                      | MA7305 VOLTAGE REGULTON     | /       |           |        |       |             |       | <u> </u>                                     |

|                                                      | 20KloTHONTRIM POT 43P203    |         |           | -      |       | SI HETTE IL |       | _                                            |

|                                                      | 20 PIN RIGHT ANGIE WAFER    | /       |           |        |       |             |       | <u> </u>                                     |

|                                                      | 10 PIN RISHT ANGLE WAFER    | 1.      |           |        |       |             |       | 1                                            |

| -                                                    | PLUG IN PLUS 50462-6 AMP    | 35      |           |        | İ     |             |       |                                              |

|                                                      | 9673 Z AB CONVERTER         | /       |           |        |       |             |       |                                              |

|                                                      | 8. PIN I.C. SOCKET          | . /     |           | `      | į     |             |       |                                              |

|                                                      | 14 PIN I.C. SOLNET          | 9       |           |        | į     |             | i     | 1                                            |

|                                                      | 16 PIN I.C. SSEMET          | 5       |           |        |       |             |       | Ì                                            |

|                                                      | HO PIN I.C. SOLKET          | 2       |           |        | !     |             |       |                                              |

|                                                      | S6920 40 PIN CHIP           | 2       |           |        |       |             |       | 1                                            |

|                                                      | MATHI 8PIN 1.C. CHIP        | 1       |           |        |       |             |       |                                              |

|                                                      | 7400 14 PIN 1.1. CALD       | 1       |           |        | 1     |             |       | Ì                                            |

|                                                      | 7406 14 PINIC CAID          | 1 /     |           |        |       |             |       | i                                            |

| ···                                                  | 74104 14 PM 1.C. CUP        | 3       |           |        |       |             |       | į                                            |

|                                                      | 74400 14 PIN 1.C. CHIP      | 1 /     |           |        | }     |             | •     | 1                                            |

|                                                      | 74130 14 PIN 1.C. CHIP      | 1       | •         |        | }     |             |       | •                                            |

|                                                      | 741573 14 PIN 113. CHIP     | 1       |           |        |       |             |       | į                                            |

|                                                      | 4051 CNAS 16 PIN 1.C. CHIP  | 1 /     |           |        |       |             |       | :                                            |

|                                                      | 174367 16 PIN 1. C. SHIP    | 3       |           |        |       | 1797-00     |       | į                                            |

|                                                      | 741123 16 PINIC. CHIP       | 1       |           |        | i     |             |       | 1                                            |

|                                                      | 2N2907 TRANSISTOR METAL CAN |         |           |        |       |             |       |                                              |

|                                                      | 78112 REGULATEL TRANSISTOR  |         | Plastic.  |        |       | -           | i     | ł                                            |

|                                                      | 79M12 REGULATO TRANSISTAR   |         | Metal Cal | ^      |       |             | i     |                                              |

|                                                      | 111914 DIOJE                | 17      |           |        | 1     |             | į     |                                              |

|                                                      |                             |         |           |        |       |             |       |                                              |

|                                                      |                             |         |           |        | Ì     |             |       |                                              |

|                                                      |                             |         |           |        |       |             | !     |                                              |

|                                                      | 1                           |         |           |        | 1     |             |       | !                                            |

|                                                      | 1                           |         |           |        |       |             |       | -                                            |

| STOCK WI | THORAWL SHEET DEPT:          |     |          | <u>-</u> | Kobe  | NATER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ·<br> |

|----------|------------------------------|-----|----------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

|          | OF _كي                       |     | ED BY:   |          |       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |       |

|          | QTY: OF: 88 A/D CON          |     | •        |          | CARE  | A - Propo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ノンナノの |       |

|          | PLEASE ENTER QUANTITIES IN   |     |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| S P/N    | NAME AND DESCRIPTION         |     | REQ'D.   |          | SHORT | REMARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UNIT  |       |

| 01902    | 470 OHM YAW 5% RESISTOR      | /   |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -     |       |

| 01903    | 1K Y4W 5% P.ESISTOR          | 3   | ¥        |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 01945    | 2.2KKWI5% RESISTOR           | 1   | L        |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 01912    | 4.7K YUW 5% RESISTOR         | 12  | ~        |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 01905    | 10K Y4W 5% RESISTOR          | 4   | ~        |          |       | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | -     |

| 02081    | 330K YZW 59, RESISTOR        | 1   | <b>/</b> |          |       | المستعدد والمستعدد والمستعد والمستعدد والمستعد والمستعدد والمستعد |       |       |

| 00331    | .OIMF50V CAP, SK20Y5V103M050 | 1   |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 00380    | .IMF50V CAP, SK30Y5V104MOSO  | 1   | ·        |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 00323    | 5MF 25V CAP. ELECT.          | 3.  |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 00352    | IDMF 25V CAP. ELECT.         | 4   |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 00334    | 20PF 10V CAP, DISC           | /   |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 03083    | #30 GAGE KYNAR WIRE          | 1FT |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

| 01982    | 3.9K 1/2W572 RESISTOR        | 1   |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |

|          | ·                            |     |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |