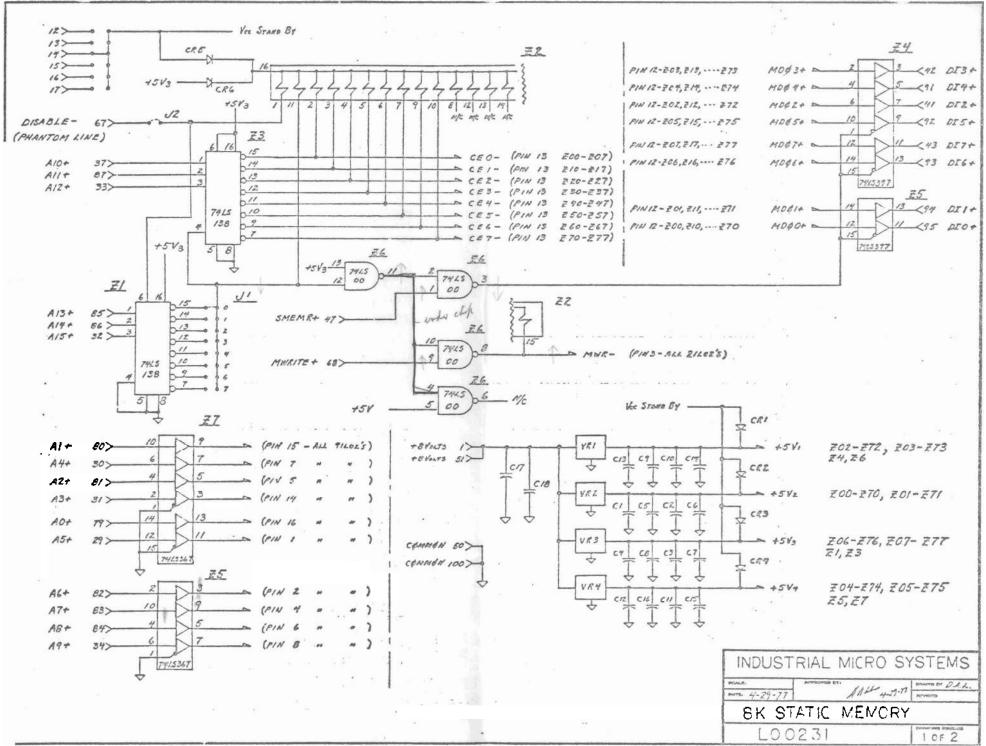

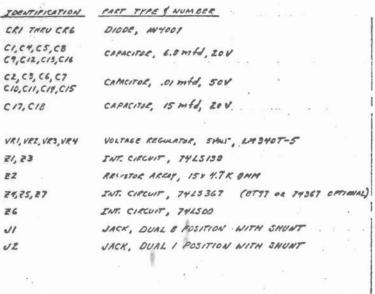

## IMS-C00231 8K MEMORY BOARD

Your 8K STATIC RAM Memory Board (C00231) has been built and tested to industrial standards and can be expected to provide long, trouble free operation. The C00231 board is compatible with the S-100 Bus and will work with Altair, IMSAI, and other 8080 or Z80 computers using the S-100 Bus.

Memory "Strapping" is done by plugging the 2 position shunt on the appropriate pins of the address selection header.

| Shunt Position | Address Range | (Hexidecimal) |

|----------------|---------------|---------------|

| 0              | 0 to 8K       | 0000 to 1FFF  |

| 1              | 8 to 16K      | 2000 to 3FFF  |

| 2              | 16 to 24K     | 4000 to 5FFF  |

| 3              | 24 to 32K     | 6000 to 7FFF  |

| 4 ·            | 32 to 40K     | 8000 to 9FFF  |

| 5              | 40 to 48K     | A000 to BFFF  |

| 6              | 48 to 56K     | C000 to DFFF  |

| 7              | 56 to 64K     | E000 to FFFF  |

The C00231 Board has a "Phantom Line" incorporated in the logic for compatability with computers using this feature. (Processor Technology). The "Phantom Line" disables the memory board whenever it is at a logic low. A two pin header with shunt is provided for enabling the "Phantom Line" feature. If the "Phantom Line" is not used, it is recommended that the shunt be removed, disabling this logic. (Pin 67 of the S100 bus is used for the "Phantom Line".) We suggest storing the shunt on two unused pins of the address selection header if you do not use the Phantom Line feature. The pins on the numbered side of the address selection are all common and the shunt may be placed on any two of these pins.

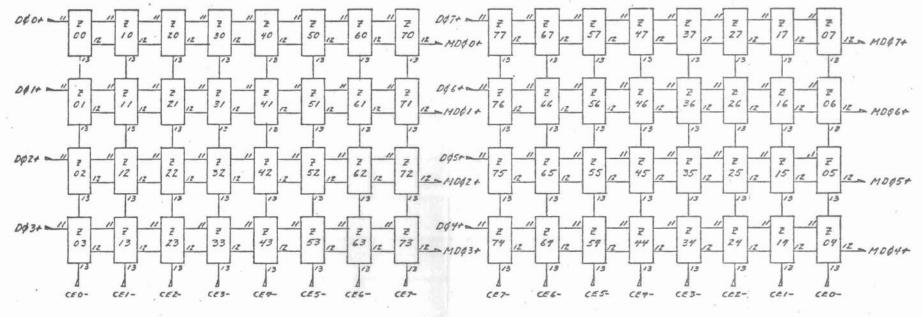

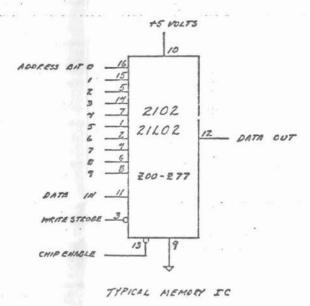

The memory matrix as shown on page 2 of the schematic is in a one to one relationship with the physical board. Each row of 8 IC's services one bit of all addresses on the board. Bit identification is shown on the board as DØO through DØ7. The columns labeled CEO through CE7 correspond to the individual lK increments of the 8K memory. CEO is the first K Bytes, CEl is the second K Bytes, and so on through CE7.

Address lines Al3+, Al4+, Al5+ are decoded by IC Zl and applied to the address strapping jack, Jl. When Al3+, Al4+, Al5+ decode to the address selected by the shunt, IC Z3 is enabled and decodes address lines Al0+, Al1+, Al2+ selecting the particular IK memory increment on the board. During a READ operation, the SMEMR+ signal from the processor enables the bus drivers to gate the memory data onto the the data bus. During a WRITE operation, the MWRITE+ signal from the processor causes data to be written into the selected memory IC's. The DISABLE- line (pin 67) disables IC Zl when it is at a logic low thereby deselecting the memory board.

The IC sockets used on this board were chosen for their ability to provide a true gas tight joint necessary for long term reliability. The beryllium copper contact material in these sockets will not weaken with age and is superior to the normally used phosphur bronze material. The high contact pressure in these sockets makes IC removal slightly more difficult than some of the lower contact pressure sockets which cannot provide a true gas tight joint. Care should be taken when removing an IC from its socket not to bend the leads. Use either a "Chip-Clip" or a small soldering aid of screwdriver to carefully pry them out. Removal by fingers -- Ouch!

The power distribution on the board has been laid out to "share the load" during operation. During any Read or Write operation, two (2) enabled memory IC's are on each of the four regulators. In a similar manner, the decoupling capacitors also share the load.

The gold contact material on the edge connector is plated over a nickel base to prevent "copper migration" which occurs when gold is plated directly over copper. Copper molecules which reach the surface will oxidize and cause a large increase in contact resistance after an extended period of time. The underplating with nickel prevents this problem from occurring. Contact lubricants are not recommended and shouldn't be used.

As a word of caution, please remove power from your system when plugging or unplugging boards. Many IC's are destroyed by not following this simple rule and occasionally catastrophic failures occur. Nuff Said!

## TOP OF BOARD

|     |        | 19       |     |       |

|-----|--------|----------|-----|-------|

|     | PIN II | 200-270  | <36 | 000+  |

|     | **     | Z01- Z71 | <35 | 00 1+ |

| 9   | **     | 202-272  | <88 | 002+  |

|     | **     | 203-273  | <89 | 003+  |

|     | "      | Z 04-Z74 | <38 | 00 4+ |

| . 6 | "      | Z'05-Z75 | <39 | 00 5+ |

|     | "      | 206-276  | <40 | 00 6+ |

|     | "      | 207-277  | <90 | 00 7+ |

|     |        |          |     |       |

|     |        |          |     |       |

|     |        |          |     |       |

INDUSTRIAL MICRO SYSTEMS

8K STATIC MEMORY

1 C C 2 3 1 2 0 F 2