# Cromemco® WDI-II

Instruction Manual

CROMEMCO, Inc. 280 Bernardo Avenue Mountain View, CA. 94043

Part No. 023-2011

August 1982

Copyright © 1982 CROMEMCO, Inc. All Rights Reserved This manual was produced using a Cromemco System Three computer with a Cromemco HDD-22 Hard Disk Storage System running under the Cromemco Cromix<sup>TM</sup> Operating System. The text was edited with the Cromemco Cromix Screen Editor. The edited text was proofread by the Cromemco SpellMaster<sup>TM</sup> Program and formatted by the Cromemco Word Processing System Formatter II. Camera-ready copy was printed on a Cromemco 3355A printer.

# TABLE OF CONTENTS

| Chapter 1: GENERAL INFORMATION                                                                                                                                                                                         | 1                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Introduction Specifications Description User Selected Options System Compatibility                                                                                                                                     | ]<br>2<br>2<br>2<br>3<br>3<br>4              |

| Hardware<br>Software<br>Reference Material                                                                                                                                                                             | 3<br>3<br>4                                  |

| Chapter 2: GETTING STARTED                                                                                                                                                                                             | 5                                            |

| Introduction System Installation User Selectable Options CPU Selection Interboard Interrupt Priority Selection Interboard Bus Request Priority Selection Onboard Bus Request Priority Selection Port Address Selection | 5<br>6<br>6<br>8<br>11<br>12                 |

| Chapter 3: I/O INTERFACE CHARACTERISTICS                                                                                                                                                                               | 15                                           |

| Introduction I/O Addressing Address E0h Address E1h Address E2h and E3h Addresses E4h through E7h Address E8h Address E8h Addresses E9h through EBh Addresses ECh through EEh Address EFh Disk Drive Interface         | 15<br>15<br>15<br>15<br>16<br>16<br>16<br>16 |

| Address, Selected Unit Clock, Differential Systems Command/Status Bus Command/Status Bus Control Signals Data, Differential Read/Write Disk Position Signals Seek Complete                                             | 19<br>19<br>19<br>19<br>21<br>21<br>21       |

| Fault                                                                                                                                                                                                                  | 21                                           |

| Chapter 4: PROGRAMMING AND PROGRAMMING CONTROL              |                |

|-------------------------------------------------------------|----------------|

| INFORMATION                                                 | 23             |

| Introduction                                                | 23             |

| Programming and Program Control                             | 27             |

| Disk Data Transfer Mode                                     | 23<br>24       |

| Microcircuit Programming                                    | 24             |

| Initial Program Control of the Read and Write               | ۷. ٦           |

| Commands                                                    | 24             |

| Controlling the Disk Drive Operation                        | 24             |

| Choosing the Disk Location for the Data Transfer            | 24             |

| Determining Instantaneous Sector Position                   | 24             |

| Using Instantaneous Sector Position                         |                |

| Implementation of Final Pre-Data Transfer Events            | 25<br>25<br>26 |

| Write-to-Disk Mode                                          | 26             |

| Read-from-Disk Mode                                         | 26             |

| Memory-to-Memory Data Transfer Mode                         | 27             |

| Extended Address Function                                   | 27             |

| Microcircuit Programming                                    | 28             |

| DMA (Direct Memory Access) Controller Programming           | 28             |

| DMA Search                                                  | 30             |

| DMA Transfer                                                | 31             |

| PIO (Parallel Input/Output) Controller Programming          | 31             |

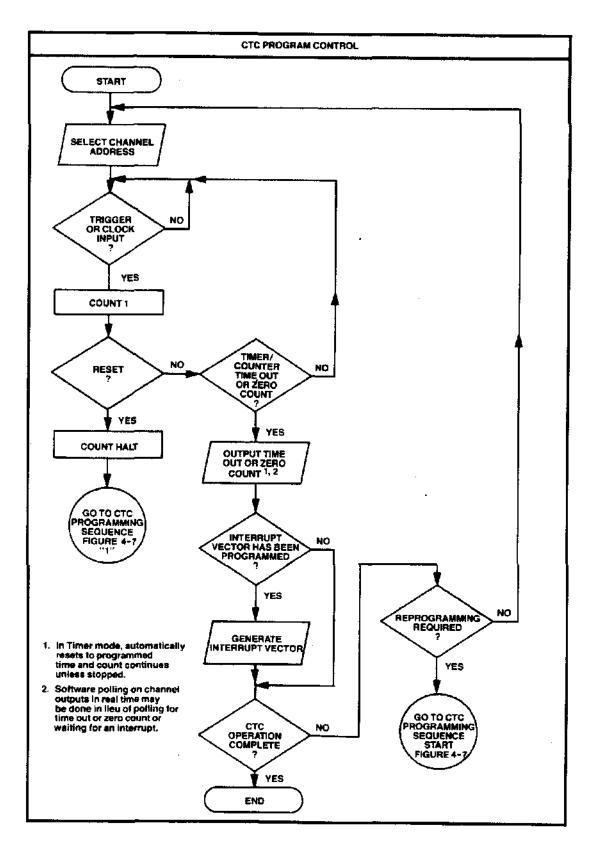

| CTC (Counter/Timer Circuit) Programming                     | 35             |

| Programming Control through WDI-II Microcircuits,           |                |

| Registers and Counters                                      | 38             |

| Command/Status Bus                                          | 40             |

| Disk Drive Unit Address Select/Verify and Related           |                |

| Commands                                                    | 40             |

| Head Address Select/Verify                                  | 41             |

| Cylinder Address Select/Verify and Related Commands         | 41             |

| Servo Command and Status Signals                            | 41             |

| Diagnostic                                                  | 42             |

| Write (to disk) and Read (from disk) Control                |                |

| Signals                                                     | 42             |

| Rezero/Rezeroing                                            | 43             |

| Fault Clear                                                 | 43             |

| Guard Band                                                  | 43             |

| PLO (Phase Locked Oscillator) Error<br>POR (Power-On Reset) | 43<br>43       |

| Speed Error                                                 | 43             |

| Unit Ready                                                  | 43             |

| Extended Address Function                                   | 43             |

| PIO (Parallel Input/Output Controller) Control              | 43             |

| Port A Data Mode                                            | 44             |

| Port B Data Mode                                            | 46             |

| Port A Programming Mode                                     | 47             |

| Port B Programming Mode                                     | 47             |

| DMA Control                                                 | 48             |

| CTC Control                                                 | 40             |

| Chapter 5: PRINCIPLES OF OPERATION                                      | 51                    |

|-------------------------------------------------------------------------|-----------------------|

| Introduction                                                            | 51                    |

| Principles of Operation                                                 | 51                    |

| Operating Modes                                                         | 51                    |

| Disk Data Transfer Mode                                                 | 51                    |

| Memory-to-Memory Transfer Mode                                          | 53                    |

| Extended Address Function                                               | 53                    |

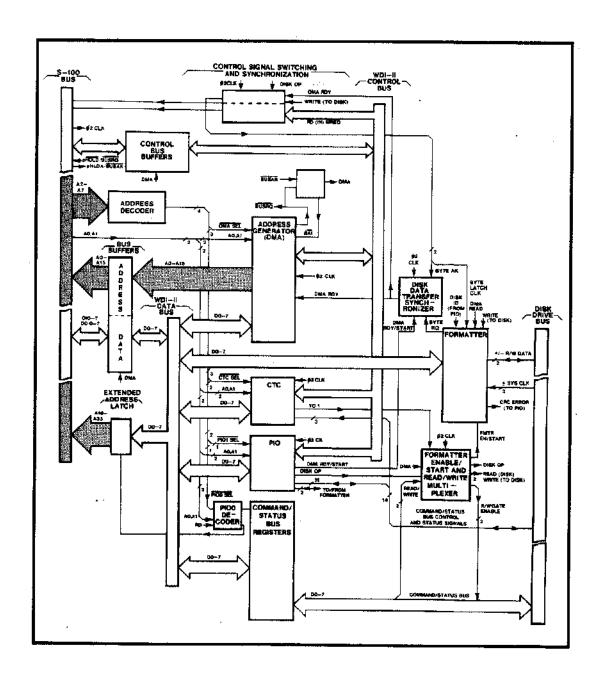

| Principles of Circuit Operation                                         | 54                    |

| Address Decoder                                                         | 54                    |

| Address and Data Bus Buffers                                            | 54                    |

| Control Bus Buffers                                                     | 55                    |

|                                                                         | <b>5</b> 5            |

| Control Signals Switching and Synchronization                           | 55<br>55              |

| Disk Data Transfer Mode                                                 | 56                    |

| Memory-to-Memory Transfer Mode                                          |                       |

| Synchronization                                                         | 56                    |

| Direct S-100 Bus/WDI-II Control Signals                                 | 56                    |

| 2 Clock Input Circuits                                                  | 56                    |

| Address Generator                                                       | 56<br>57<br><b>57</b> |

| Disk Data Transfer                                                      | 57                    |

| Memory-to-Memory Transfer                                               | 57                    |

| DMA Bus Request Priority                                                | 58                    |

| Disk Data Transfer Synchronizer                                         | 58                    |

| DMA Response to the DMA RDY Signal                                      | 58                    |

| Control Signal Switching and Synchronization                            |                       |

| Circuit Response to DMA RDY                                             | 59                    |

| DMA and Disk Data Transfer Synchronizer Response                        |                       |

| to Setting the Synchronizer Flip-Flops                                  | 59                    |

| Formatter Enable/Start and Formatter Response                           |                       |

| to the DMA Signal                                                       | 59                    |

| Summary of Disk Data Transfer Synchronization                           |                       |

| Operation                                                               | 59                    |

| Formatter                                                               | 60                    |

| Formatter Control                                                       | 61                    |

| Parallel to Serial Converter                                            | 61                    |

| Serial to Parallel Converter                                            | 61                    |

| Formatter Synchronization                                               | 62                    |

| Data Error Checking                                                     | 62                    |

| CTC (Counter/Timer Circuit)                                             | 63                    |

| PIO (Parallel Input/Output) Controller Circuit                          | 63                    |

|                                                                         | •                     |

| Command/Status Bus Circuits, PIOO Decoder and<br>Extended Address Latch | 64                    |

| Formatter Enable/Start and READ/WRITE Multiplex                         | 04                    |

| · · · · · · · · · · · · · · · · · · ·                                   | 64                    |

| Circuits                                                                | 65                    |

| On- and Off-Board Interrupt Priorities                                  | <b>v</b> 3            |

| Chapter 6: REPLACEMENT PARTS                       | 67             |

|----------------------------------------------------|----------------|

| Introduction<br>Ordering Information<br>Parts List | 67<br>67<br>68 |

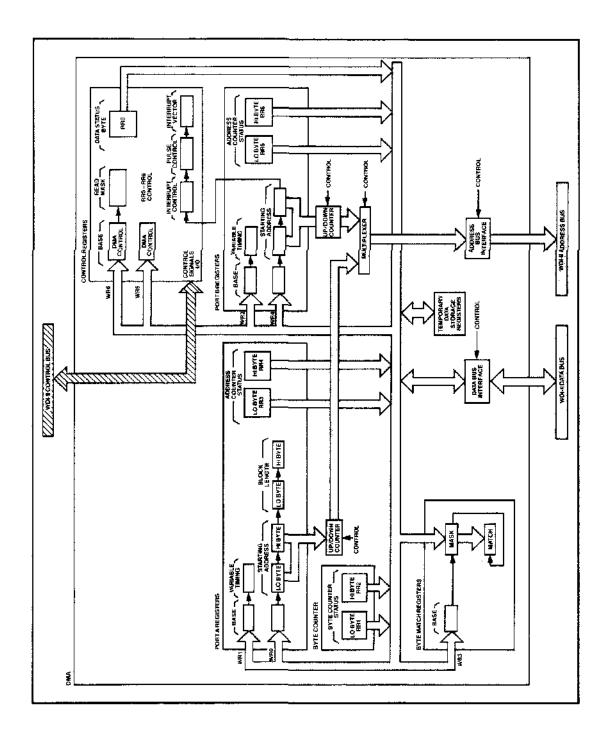

| Appendix A: WDI-II BLOCK DIAGRAM                   | 73             |

| Appendix B: LIMITED WARRANTY                       | 75             |

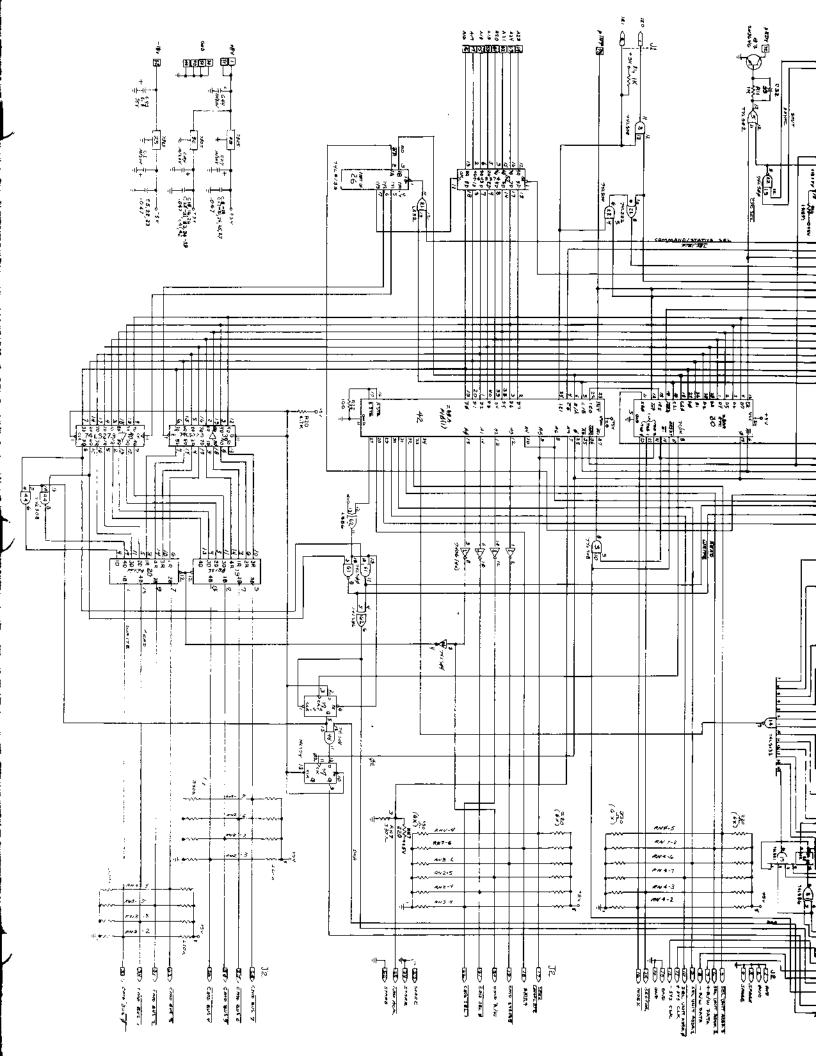

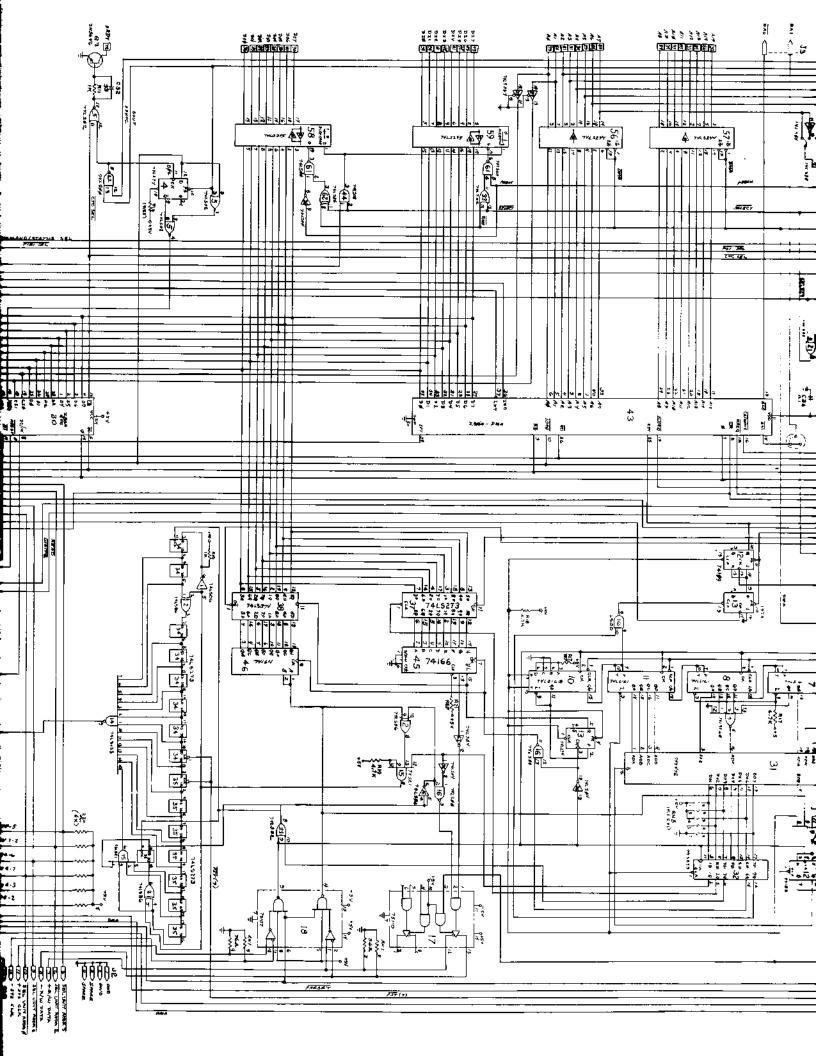

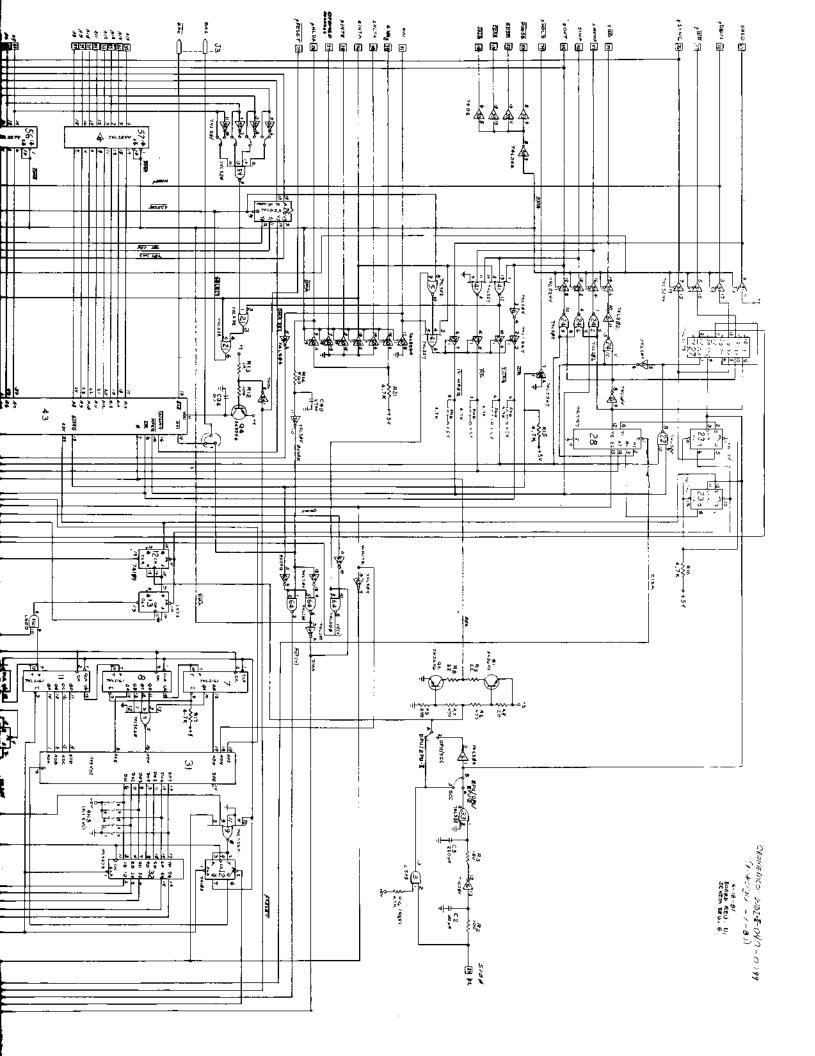

| SCHEMATIC                                          |                |

# LIST OF FIGURES AND TABLES

| Table<br>Table | 1-1:<br>1-2: | Specifications<br>List of Reference Material         | 4  |

|----------------|--------------|------------------------------------------------------|----|

|                |              | • .                                                  |    |

| Figure         | 2-1:         | Option Cable Connector and Jumper Pad Locations      | 7  |

| Figure         | 2-2:         | CPU Selection                                        | 8  |

| Figure         |              | Interboard Interrupt Priority Selection              | 9  |

| Figure         |              | Interboard Interrupt Priority Select<br>Connector Jl | 9  |

| Figure         | 2-5:         | Interboard Bus Request Priority Selection            | 10 |

| Figure         |              | Interboard Bus Request Priority Select               |    |

|                |              | Connector                                            | 10 |

| Figure         | 2-7:         | Bus Request Priority Selection Jumper                | īi |

| Table          |              | Base Address Selection                               | 12 |

| Figure         |              | · · · · · · · · · · · · · · · · · · ·                | 13 |

|                |              | TOTO MADE DELEGIZON CAMPETE                          |    |

| Table          | 3-1:         | WDI-II I/O Port Assignments                          | 17 |

| Table          | 3-2:         |                                                      | 18 |

| Figure         | 3-1:         | Disk Drive Interface                                 | 20 |

| Figure         | 4-1:         | DMA Simplified Block Diagram                         | 29 |

| Figure         |              | PIO I/O Signal Flow Definition                       | 32 |

| Figure         |              | Programmed PIO Control Byte Format                   | 33 |

| Figure         | 4-4:         | PIO Programming Sequence                             | 34 |

| Figure         |              | Programmed CTC Control Byte Formats                  | 35 |

| Figure         |              | Simplified CTC Internal Structure                    | 36 |

| Figure         |              | CTC Programming Sequence                             | 37 |

| Figure         |              | WDI-II/Disk Drive Interface Bus                      | 39 |

| Table          | 4-l:         | Hard Disk Drive Command/Status Bus                   |    |

| -40            |              | Signals                                              | 40 |

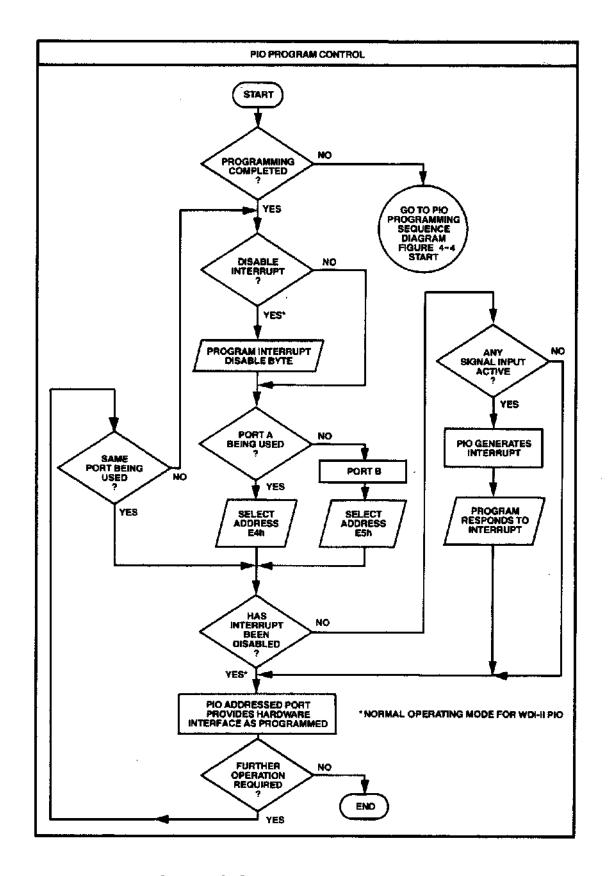

| Figure         | 4-9:         | PIO Program Control                                  | 45 |

| Figure         |              | CTC Program Control                                  | 50 |

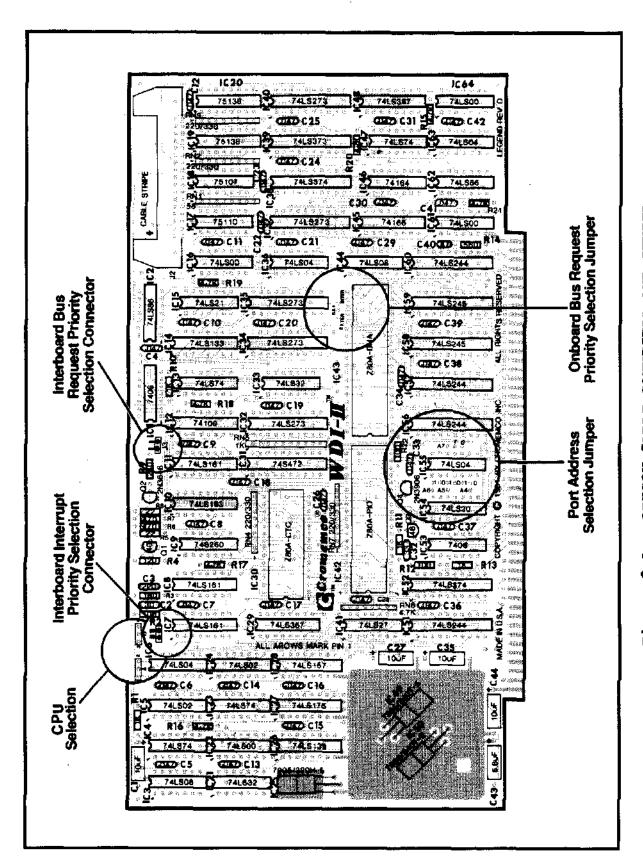

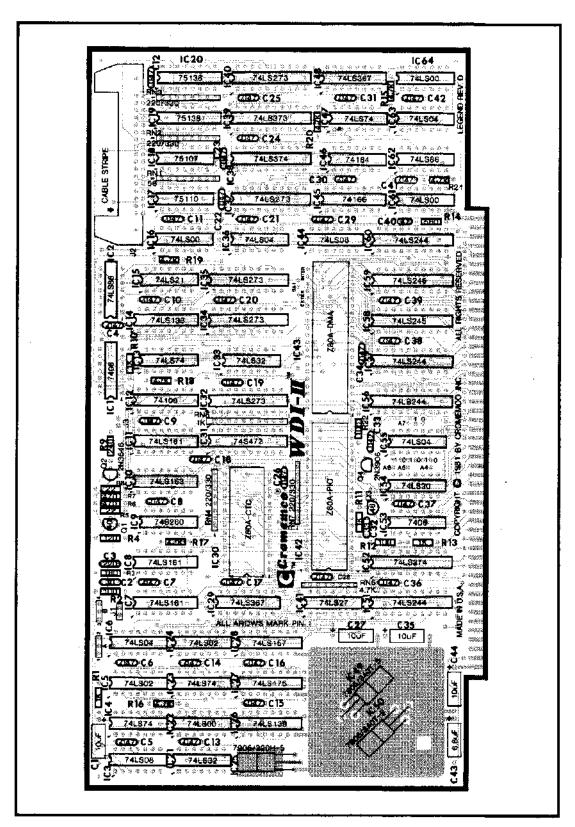

| Figure         | 6-1:         | WDI-II Component Location Diagram                    | 71 |

| D              | <b>3</b> . 7 | NDT TT Dlack Discuss                                 |    |

| Figure         | A-1:         | WDI-II Block Diagram                                 | 73 |

# Chapter 1

#### GENERAL INFORMATION

#### INTRODUCTION

This manual contains information needed to install, select options, program, control, and understand the operation of the Cromemco WDI-II Winchester Disk Interface printed circuit board. This board will be referred to as the WDI-II throughout this manual. Cromemco instruction manuals and other related information will be referred to as required.

This chapter includes the WDI-II specifications, a board description, a list of documentation referenced in this manual, and a list of WDI-II/software compatibility, including diagnostic programs recommended by Cromemco.

Chapter 2, Getting Started, describes the WDI-II user selected options. For situations where a WDI-II is installed in an existing system, WDI-II installation information is also included.

Chapter 3, I/O Characteristics, covers the board interface characteristics of the system S-100 Bus and the hard disk drives.

Chapter 4, Programming and Program Control, describes programming the WDI-II microcircuits, registers, and counters, as well as program control considerations for these circuits. This manual is not intended as a complete reference guide to programming and controlling these circuits. More information may be found in the manufacturer's data book, referred to in this book as necessary.

Chapter 5, Principles of Operation, covers circuit operation in terms of the major operating capabilities of the WDI-II board and the individual circuits.

Chapter 6, Replacement Parts, provides information needed to order replacement parts for the WDI-II, including a complete parts list.

#### SPECIFICATIONS

The specifications for the WDI-II are contained in Table 1-1.

#### Table 1-1: SPECIFICATIONS

Modes and Functions: Hard Disk Data Transfer

Memory-to-Memory Data Transfer

Extended Addressing

Disk Drive Compatibility: Cromemco Hard Disk Drives

H5, HD11 and HD22

Disk Drive Capacity:

6 Maximum S-100

Bus: Power Requirements:

+8 VOLTS @ 1.4 Amps -18 VOLTS @ 0.1 Amps

Operating Environment:

0 to 55°C

#### DESCRIPTION

The WDI-II provides an interface between the system S-100 Bus and a hard disk drive. The WDI-II circuits, together with the operating system, format and control data transfer between the system main memory and the disk surface media. High speed memory-to-memory data transfers may be made between addressed locations in system main memory. The extended address function allows extended addressing using address-as-data information received from the S-100 Bus.

The WDI-II is installed in one of the S-100 Bus connectors. The disk drive(s) connect to the WDI-II through one or more flat ribbon cables. Memory-to-memory data transfer and extended address functions require only that the WDI-II be inserted into an S-100 Bus connector. Refer to Chapter 2 for additional installation information.

## USER SELECTED OPTIONS

There are two types of user selected options available for the WDI-II. Interboard functions may be selected using interconnecting cables, and intraboard functions may be selected using onboard jumpers. Refer to Chapter 2 for information explaining option selection methods.

... .. -

The interboard options set up priorities between boards for system bus requests and system interrupts. WDI-II bus requests are generated by the Address Generator (DMA). WDI-II interrupts are generated by the Address Generator, CTC (Counter/Timer Circuit), and the PIO (Parallel Input/Output) controller circuits.

The intraboard (WDI-II onboard) options are 1) system bus request priority selection similar to interboard bus request priority selection, 2) base address selection in the Address Decoder circuit, and 3) CPU selection in the  $\phi$ 2 Clock Input circuit.

#### SYSTEM COMPATIBILITY

#### Hardware

The WDI-II is designed for S-100 Bus systems. All Cromemco systems are hardware compatible with the WDI-II. Only the HDD-22, HDD-11, and HD5 Hard Disk Drives are compatible with the WDI-II.

#### Software

Cromemco recommends that the WDI-II be used only with operating systems and programs capable of driving the WDI-II directly. The WDI-II will operate directly with the following operating systems and programs.

- Cromemco Cromix Multi-user Multi-tasking Operating System--Version 11.07 and above. For more information refer to the Cromix manual.

- Cromemco CDOS Single User Operating System--Version 02.44 and above. For more information refer to the CDOS manual.

- 3. Cromemco INIT Disk Initialization Program--Version 02.23 and above. This program allows the user to initialize the diskette. For more information refer to the CDOS manual.

- 4. Cromemco HDTEST Hard Disk Testing Program-Version 00.10 and above. This program exercises the hard disk drive and displays any detected errors on the console terminal. Refer to the Cromemco System Diagnostic Software manual.

5. Cromemco HDIAG Hard Disk Diagnostic Program-Version 00.13 and above. This program is used for executing special hard disk drive operations such as reading or writing data, declaring alternate tracks, saving data from bad tracks, verifying that all data can be read, and initializing all or part of the hard disk. Refer to the Cromemco System Diagnostic Software manual.

# REFERENCE MATERIAL

Table 1-2 provides a list of the instruction manuals and other written information to which reference is made in this manual.

#### Table 1-2: LIST OF REFERENCE MATERIAL

#### LIST OF REFERENCE MATERIAL

- Cromemco Cromix Multi-User Multi-tasting Operating System Instruction Manual--Part Number 023-4022.

- Cromemco CDOS Single User Operating System Instruction Manual--Part Number 023-0036.

- 3. Cromemco System Diagnostic Software Instruction Manual--Part Number 023-6013.

- 4. Cromemco Z-2H and HDD Hard Disk Systems Instruction Manual--Part Number 023-5020.

- 5. Cromemco ZPU Central Processing Unit Instruction Manual--Part Number 023-0012.

- 6. Zilog Microcomputer Components Data Book--March 1981.

- 7. 7710 Hard Disk User's Manual (HDD11 and 22)--Part Number 023-6027.

- HD5 Product Description Manual for 5" Hard Disk Drive--Part Number 023-6028.

# Chapter 2

#### GETTING STARTED

#### INTRODUCTION

This chapter provides information about system installation and user selected options for the WDI-II. System installation explains how the WDI-II, if received separately from the system in which it is to be used, is installed in the system and connected to the disk drive. Both interboard and intraboard (onboard) user selected options are available.

The operating system, through the WDI-II, can control one of up to six hard disk drives in a system. Refer to the Cromemco Cromix or CDOS Operating System manuals for hard disk drive addressing information.

# SYSTEM INSTALLATION

The WDI-II may be a part of a Cromemco System Zero, One, Two, or Three. In any of these systems, the WDI-II board should be installed firmly in one of the S-100 Bus circuit board connectors.

The WDI-II, with accompanying cables and hard disk drive, may be received either as a part of a complete system or separately, to be installed in an existing system.

The hard disk drive may be installed either within the system cabinet or externally. If the hard disk drive is installed within the system cabinet, one cable (Cromemco Part Number 519-0033) is required to connect the WDI-II to the hard disk drive. If the hard disk drive is installed outside the cabinet, a cable with two rear panel connectors (Cromemco Part Number 519-0037) is installed within the cabinet. External cables (Cromemco Part Number 519-0036) then serve to connect the hard disk drive(s) to these system cabinet rear panel connectors. Refer to the Cromemco Z-2H and HDD manual for more information.

# Cromemco WDI-II Instruction Manual 2. Getting Started

NOTE: The WDI-II will not function properly if the ZPU clock switch is set for 2 MHz operation. Refer to the Z-2H and HDD manual for more information.

#### USER SELECTABLE OPTIONS

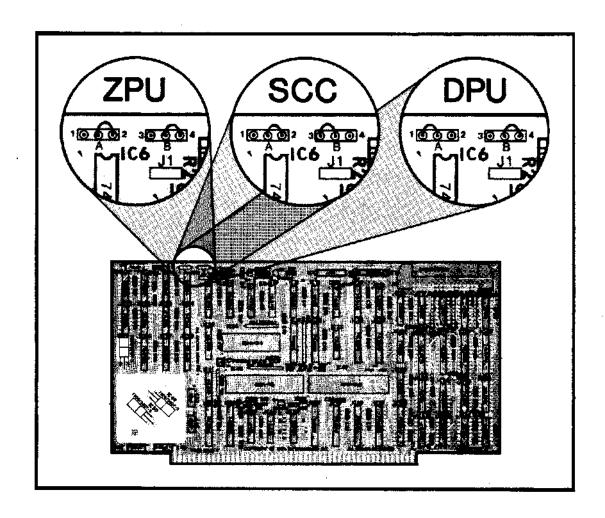

The interboard options are selected using interconnecting cables. The intraboard or onboard options are selected using jumpers. Explanations and instructions for the selection of each option are included in the following paragraphs. Figure 2-1 shows where each cable connector or circuit board solder pad is located on the WDI-II board.

#### CPU Selection

The WDI-II, as received from the factory, is ready for use in a system using a DPU central processor. The CPU selection circuit traces can be cut and new jumpers installed for other CPUs. The jumper locations for each CPU are shown in Figure 2-2.

#### Interboard Interrupt Priority Selection

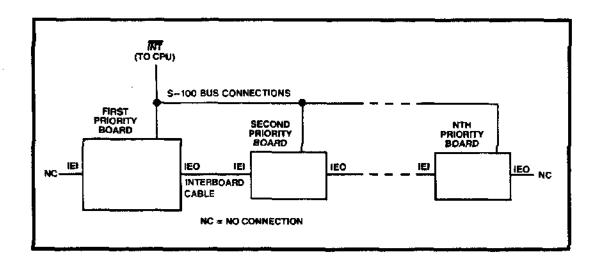

Figure 2-3 illustrates how interboard interrupt priorities are selected. Figure 2-4 shows a closeup of connector Jl. A Priority Interrupt Cable (Cromemco Part Number 519-0029) may be used to establish interrupt priorities between circuit boards. These cables interconnect all of the boards that are part of the interrupt priority chain. Note that the Interrupt (INT\*) signals from each board form a wired-or output to the system CPU. This signal tells the CPU that one of the boards has issued an interrupt request.

The circuit board with the highest interrupt priority has no connection at the Interrupt Enable Input (IEI). An onboard pull-up resistor to the +5 volt supply places a high on the input to the circuit generating the interrupt. A high on any of the circuit board Interrupt

Enable Outputs (IEO) indicates that an interrupt was issued either by the board with the high output or another board with a higher interrupt priority. A low on IEO indicates that the higher priority boards did not issue an interrupt request or that the interrupt has already been serviced.

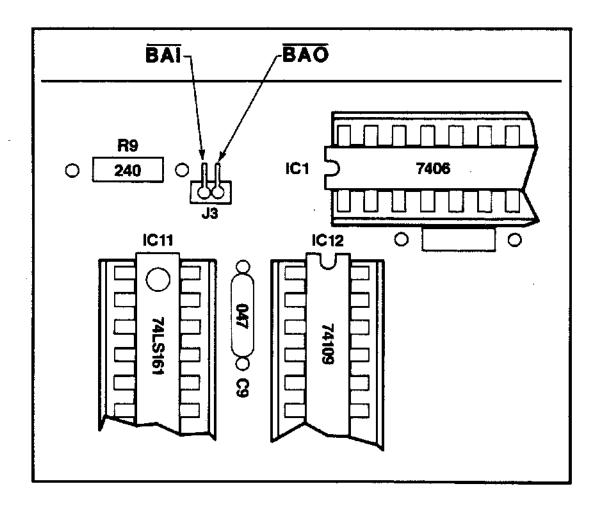

Figure 2-1: OPTION CABLE CONNECTOR AND JUMPER PAD LOCATIONS

NOTE: Cromemco software does not require the use of this option on the WDI-II.

Figure 2-2: CPU SELECTION

# Interboard Bus Request Priority Selection

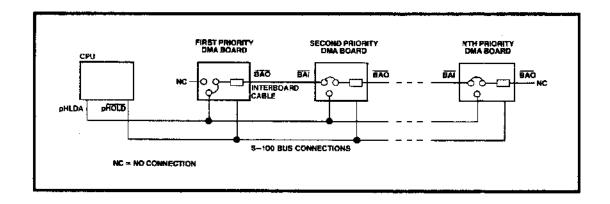

All boards with a DMA controller have the ability to control the address and data buses and may be connected in a daisy chain arrangement, as illustrated in Figure 2-5. A closeup view of the WDI-II connector is shown in Figure 2-6.

The highest priority board's bus acknowledge input (BAI\*) is connected directly to the system CPU hold acknowledge (pHLDA) output. A high on pHLDA indicates that the system bus is released for DMA control. A low on bus acknowledge output (BAO\*) indicates that a higher priority DMA has not issued a bus request or that the DMA has issued a bus request but has already been

serviced. At this time, the board with a high on the bus acknowledge input (BAI\*) has priority and is currently being serviced. A high on BAO\* indicates that the bus has not been released by the system CPU or that a higher priority DMA has requested the bus and, as of this time, has not been serviced. See also Onboard Bus Request Priority Selection as follows.

Pigure 2-3: INTERBOARD INTERRUPT PRIORITY SELECTION

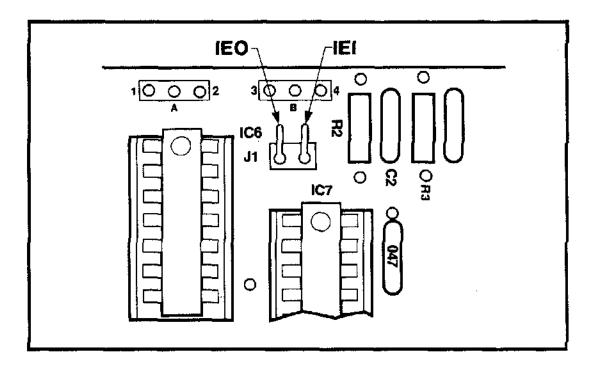

Figure 2-4: INTERBOARD INTERRUPT PRIORITY SELECT CONNECTOR J1

Figure 2-5: INTERBOARD BUS REQUEST PRIORITY SELECTION

Figure 2-6: INTERBOARD BUS REQUEST PRIORITY SELECT CONNECTOR

# Onboard Bus Request Priority Selection

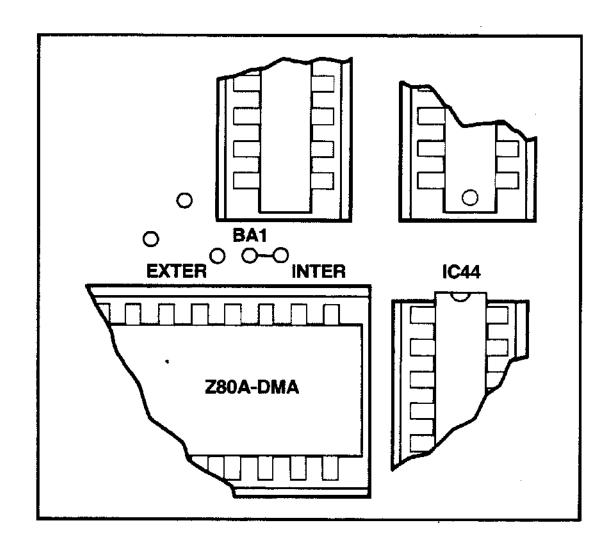

On the WDI-II, the bus request priority jumper indirectly connects the pHLDA signal to the BAI\* input of the Address Generator (DMA). If the WDI-II has the highest interboard bus request priority, the jumper is connected from BAI\* to internal (INTER). The printed circuit traces are shipped this way from the factory. If the WDI-II does not have the highest interboard interrupt priority, the trace must be cut and a jumper inserted between BAI\* and external (EXTER). Refer to Figure 2-7. See also, Interboard Bus Request Priority Selection and Figure 2-5.

Figure 2-7: BUS REQUEST PRIORITY SELECTION JUMPER

# Port Address Selection

The WDI-II board is shipped from the factory with E set as the base address. Figure 2-8 shows the original jumper locations. If the base address is to be changed, one or more of the traces must be cut. Jumpers must be inserted as indicated by Table 2-1. A 1 shows that a jumper should be inserted, and a 0 indicates that the jumper is omitted.

Table 2-1: BASE ADDRESS SELECTION

| Base                     | Binary Equivalent |             |                  |                  |

|--------------------------|-------------------|-------------|------------------|------------------|

| Address                  | A7                | A6          | A5               | A4               |

| 0Xh<br>1Xh<br>2Xh<br>3Xh | 0<br>0<br>0       | 0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0      |

| 4Xh<br>5Xh<br>6Xh<br>7Xh | 0<br>0<br>0       | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

| 8Xh<br>9Xh<br>AXh<br>BXh | 1<br>1<br>1       | 0 0 0       | 0<br>0<br>1<br>1 | 0<br>1<br>0      |

| CXh<br>DXh<br>EXh<br>FXh | 1<br>1<br>1       | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

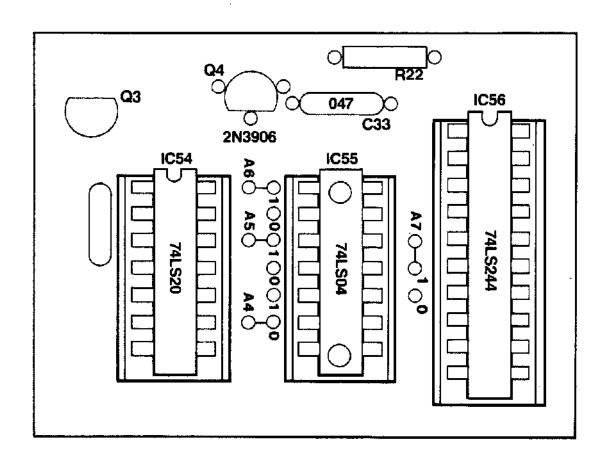

Figure 2-8: PORT ADDRESS SELECTION JUMPERS

# Chapter 3

#### I/O INTERFACE CHARACTERISTICS

#### INTRODUCTION

The WDI-II and the system are connected with the standard 100-pin printed circuit board connector. The WDI-II appears to the operating system as a 16-port I/O peripheral. Refer to the Cromemco ZPU manual for more information pertaining to the S-100 Bus. Refer also to the CDOS or Cromix Operating Systems manuals for information pertaining to I/O drivers and addressing.

## I/O ADDRESSING

As received from the factory, the addresses of the 16 I/O ports of the WDI-II are E0h through EFh. While the base address E can be changed, it is recommended that the number remain E unless a situation arises requiring the change. This assures compatibility with Cromemco software. Table 3-1 lists the I/O addresses of the WDI-II. The following paragraphs provide more detailed information on addressing. For information on programming and program control of the WDI-II microcircuits and board functions, refer to Programming and Program Control in Chapter 4.

#### Address E0h

This address enables the Extended Address Latch. This allows addresses in the form of data from the S-100 Bus to be latched onto the extended address lines A16-A23.

#### Address Elh

This address enables the Command/Status Bus registers. These lines carry command and status information for selecting, controlling and verifying proper operation of one of several hard disk drives. These signals are used throughout the Disk Data Transfer mode.

## Addresses E2h and E3h

These addresses are not used at this time.

# Addresses E4h through E7h

These addresses select one-of-four PIO (Parallel Input/Output) Controller modes. In the command modes, the internal registers interface the operating system to WDI-II circuits as required in the Disk Data Transfer mode. In the data (operational) modes, the internal registers interface with the WDI-II circuits.

#### Address E8h

This address selects the DMA controller microcircuit. The DMA mode is software selected and determines the WDI-II interface mode. Once the DMA mode is selected, the controller microcircuit enters the operational phase. In the Disk Data Transfer mode, the DMA takes control of the S-100 Bus. The DMA, in turn, is controlled by other WDI-II circuits. In the Memory-to-Memory Transfer mode, as soon as the CPU allows, the DMA takes control of the S-100 Bus and begins operation.

# Addresses E9h through EBh

These addresses may also be used to select the DMA microcircuit. It is, however, recommended that E8h be used exclusively for DMA control to maintain compatibility with current Cromemco software. Addresses E9h through EBh are reserved for future WDI-II operating mode expansion.

#### Addresses ECh through EEh

These addresses select one-of-three CTC (Counter/Timer Circuit) channels. CTC operation is related to disk drive control and to finding data and reading and writing it to exact disk locations.

#### Address EFh

This address may be used to select CTC channel 3. Note, however, that channel 3 is not used in any of the WDI-II operating modes at this time.

| Table | 3-1: | WDI-II  | T/O  | PORT | ASSIGNMENTS |

|-------|------|---------|------|------|-------------|

| TONTE | J-1: | MULTITA | 1/ V | FURI | CIDAMBICON  |

| Address<br>(Hexadecimal) | Control<br>Signals <sup>1</sup> | Use                                                      |

|--------------------------|---------------------------------|----------------------------------------------------------|

| E0                       | PIOO SEL, AO, A12               | Selects Extended address<br>Latch                        |

| El                       | PIOO SEL, A0, A12               | Selects Command/Status Bus                               |

| E2,E3                    |                                 | Not Used                                                 |

| E4-E7                    | PIOL SEL                        | Selects Parallel Input/Output<br>Controller microcircuit |

| E8                       | DMA SEL                         | Selects Direct Memory Access microcircuit                |

| E9-EB                    | DMA SEL                         | Same as E8 <sup>3</sup>                                  |

| EC-EF                    | CTC SEL                         | Selects Counter Timer<br>Circuit <sup>4</sup>            |

#### Notes:

- 1. Refer to Schematic.

- 2. Clocked by S-100 Bus RD signal.

- Address use not recommended.

- Selection of address EFh serves no useful purpose.

#### DISK DRIVE INTERFACE

A hard disk drive located within the system cabinet is connected directly to the WDI-II circuit board with a special interconnecting cable. Hard disk drives outside the system cabinet are connected to each other and to the WDI-II cable connectors on the cabinet rear panel using separate interconnecting cables. Refer to the Cromemco Z-2H and HDD manual for more information.

If the WDI-II circuit board, cables, and hard disk drives are received from the factory or dealer separately from the computer, they will have to be installed before they are usable. Refer to Chapter 2 for installation information.

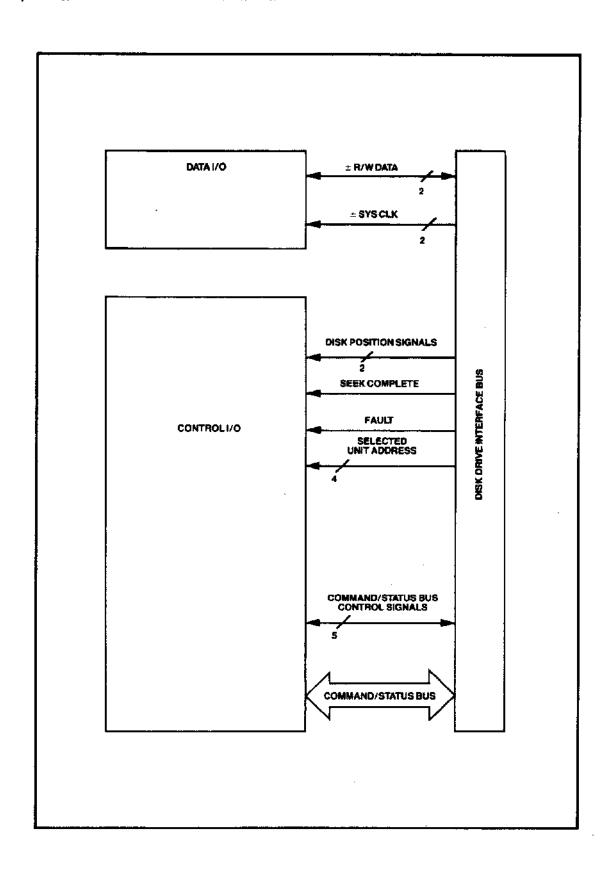

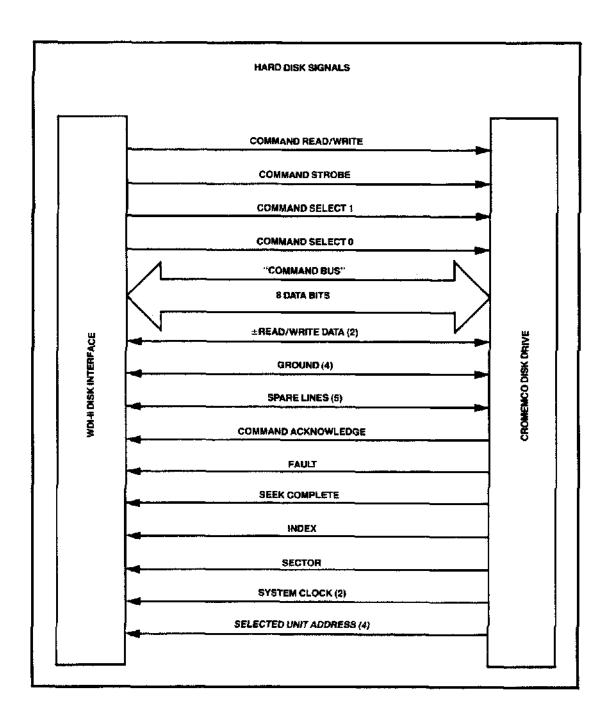

Each connection between the WDI-II and the hard disk drive(s) has a specific purpose. Table 3-2 shows the connector pin number, the signal name, and indicates the active true state or pulse characteristics. Figure 3-1 is a simplified block diagram that shows the disk drive interface. The following paragraphs list each signal name and indicate the effect each has on hard disk drive operation.

Table 3-2: WDI-II/DISK DRIVE CONNECTIONS

| Pin 1,2                                                                                             |                                        | Signal<br>Transition<br>or Active |

|-----------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------|

| Name                                                                                                | Signal on J2-Pin #                     |                                   |

| Address, Selected Unit -3 -2 -1 -0                                                                  | 5<br>6<br>9<br>10                      | low<br>low<br>low<br>low          |

| Data (Read/Write) Differential + -                                                                  | 7<br>8                                 | <b>.</b>                          |

| Servo Clock,<br>Differential<br>+<br>-                                                              | 11<br>12                               | 7                                 |

| Disk Position<br>Sector<br>Index<br>Seek Complete                                                   | 15<br>16<br>17                         | —PW=3µs                           |

| Fault                                                                                               | 18                                     | low                               |

| Command Strobe<br>Command Acknowledge<br>Command Read/Write<br>Command Select D<br>Command Select 1 | 19<br>25<br>20<br>21<br>22             | 200ns                             |

| Command/Stauts Bus <sup>3</sup> -6 -7 -4 -5 -2 -3 -0                                                | 27<br>28<br>29<br>30<br>31<br>32<br>33 | low low low low low low low low   |

# Notes:

- 1. J2-Pins 1, 2, 13 and 14 are grounds.

- Unassigned lines, J2-pins 3, 4, 23, 24 and 26 are all grounded at J2.

- Command/Status Bus Signals must remain low while command control signals CMD STB, CMD AK, CMD R/W, CMD SEL 1, and CMD SEL 2 are active.

- 4. SYS CLK is the 5.184 MHz disk drive clock signal. When the Command/Status Bus READ GATE is true, SYS CLK is synchronized to the data transitions. Otherwise, SYS CLK is locked to the servo surface INDEX pulse through the phase locked oscillator.

## Address, Selected Unit

The bit pattern on SELECTED UNIT ADDRESS\* indicates which disk drive has been selected to participate in a data exchange with the system main memory.

# Clock, Differential Systems

The ± SYS CLOCK signal is generated within the disk drive from either synchronization data placed on the disk media servo surface at the factory or the data transitions recorded on the disk media. The first example synchronizes the data in the write-to-disk mode while the latter synchronizes the data being read from the disk. During operation, the WDI-II Formatter uses the clock signal to synchronize the transmission of data between the WDI-II and disk drive.

#### Command/Status Bus

This bus carries an 8-bit byte which passes command (control) or status information between the system and the disk drive unit. One-of-eight bytes is selected. For more information, refer to Programming Control Through WDI-II Microcircuits, Registers and Counters in Chapter 4.

#### Command/Status Bus Control Signals

These signals select and control the information that is transmitted on the Command/Status Bus.

Command acknowledge (CMD ACK\*) indicates to the operating system (with a low) that a command has been received or that status information is on the Command/Status Bus.

Command Read/Write (CMD R\*/W) selects the Command or Status mode (four-of-eight bytes).

Command Select 1 and 2, (CMD SEL 1 and CMD SEL 2), select one-of-four bytes in either the Command or Status mode.

Command Strobe (CMD STROBE\*), with a momentary low, indicates that a command is being sent to the hard disk drives. The command may be used to control the drive unit's mechanical operation or to indicate that the unit should place status information on the Command/Status Bus.

Figure 3-1: DISK DRIVE INTERFACE

# Data, Differential Read/Write

A  $\pm R/W$  DATA signal on these lines indicates that data is being transmitted to or received from the hard disk drive.

# Disk Position Signals

The following pulses are written to the disk servo surface at the factory. In practice they are accessed in a read only mode.

INDEX\* is a pulse generated once for each rotation of the disk. It is a reference that indicates the position of the disk at a given instant. It may be used to locate or place information on the disk media, or monitor the speed of the disk.

SECTOR\* is a pulse generated once for each sector on the disk. It functions as a reference and may be used the same way as the Index pulse.

# Seek Complete

Seek Complete\* is generated when the read/write head has located the target track that it has been seeking.

#### Fault

Fault\* goes low whenever a fault associated with control of the addressed hard disk drive unit occurs.

# Chapter 4

#### PROGRAMMING AND PROGRAM CONTROL INFORMATION

#### INTRODUCTION

This section includes information to aid in programming and controlling the modes and functions of the WDI-II. Programming and program control information on overall board operation is included, followed by information on microcircuit programming and the onboard registers and counters. The final portion of this chapter concerns programming control through WDI-II microcircuits, registers and counters.

#### PROGRAMMING AND PROGRAM CONTROL

The WDI-II appears to the operating system as a 16-port addressable peripheral. Under program control, the different operating modes and functions of the WDI-II may be implemented as desired. Selecting the Disk Data Transfer Mode causes the WDI-II circuits to interface the system S-100 Bus and the selected hard disk drive. Selecting the Memory-to-Memory Data Transfer Mode causes the Address Generator (DMA) to control main memory data transfer at a rate up to 10 times faster than a conventional program controlled data transfer. The Extended Address Function allows addresses in the form of data, received from the S-100 Bus, to be placed on the extended address lines.

The onboard microcircuits must be programmed at the beginning of most WDI-II operations. The PIO (Parallel Input/Output) Controller falls into this category because it plays a major role in the two main WDI-II modes of operation. The DMA (Direct Memory Access) Controller also requires immediate programming because it determines the WDI-II mode of operation. The CTC (Counter/Timer Circuit) is involved in various timing and control functions occurring throughout the Disk Data Transfer mode, and thus must be reprogrammed at various times in order to accomplish all of its assigned tasks. During each WDI-II operation, the microcircuits are selected and placed into their operating modes, allowing them to perform their programmed function(s). For more information on the operation of the microcircuits with the other WDI-II circuits, refer to Chapter 5.

#### Disk Data Transfer Mode

A particular series of program controlled steps must occur to implement disk data transfer. It is possible to perform some of these out of the order shown. However, this sequence is recommended to prevent problems in implementing this mode of operation.

Microcircuit Programming—At the beginning of the Disk Data Transfer Mode, the PIO is programmed to provide the required hardware interface. Then the DMA is programmed for the search continuous mode and other related parameters required for the disk data transfer. For more information pertaining to PIO and DMA programming, refer to the section on microcircuit programming later in this chapter.

In the Disk Data Transfer Mode, the Formatter controls DMA operation. More information about this may be found in the sections entitled **Disk Data Transfer Synchronizer** and **Formatter** in Chapter 5.

Initial Program Control of the READ and WRITE Commands—Under program control, the READ (from disk) and WRITE (to disk) commands on the Command/Status Bus are initially held inactive until later.

Controlling the Disk Drive Operation—To implement the disk data transfer, the system must control the hard disk drive unit. Selecting the disk drive allows the operating parameters of that unit to be polled by the operating system through the Command/Status Bus Registers. The operating system then responds with the appropriate commands to bring the disk drive under control.

Choosing the Disk Location for the Data Transfer—The disk data transfer location where data is to be written to or read from the disk media must be chosen. The disk location is chosen in terms of disk surface, track and sector. The particular disk surface is selected in terms of the addressed read/write head; the data track is selected by the addressed cylinder. The operating system may verify the addresses by requesting a status check on each.

Determining Instantaneous Sector Position--Instantaneous sector position must be determined to enable WDI-II timing circuits to transfer data to or from the correct

sector. This is a dynamic transfer condition and must be done properly to avoid destroying data in the write-to-disk mode or reading incorrect data in the read-from-disk mode. Instantaneous sector position may be established by programming the CTC Channel 0 counter to one. The counter will decrement to zero upon receiving an INDEX\* pulse from the disk drive unit, and the operating system can poll CTC Channel 0 to determine exactly when this occurs. Instantaneous sector position may also be determined or double checked by reading the header data currently under the read/write head. When a sector pulse is received, the header read mode is immediately implemented. The header contains data that indicates the selected disk surface, track and sector. For more information, refer to the Header Read paragraph in this chapter.

Using Instantaneous Sector Position to Determine when to Implement the Final Pre-Data Transfer Events—When the instantaneous disk location is determined, CTC Channel l is immediately programmed to one less than the difference between the sector currently under the read/write head and the sector where the data transfer will occur. The counter decrements by one as each sector pulse is received. When the zero count is reached, the zero count ZCl is output. At this point, the head is above the sector just preceding the data transfer sector.

Implementation of Final Pre-Data Transfer Events--When the read/write head position is above the sector immediately preceding the data transfer sector, the final series of events leading to the actual data transfer must be implemented. These events are:

- 1. CTC Counter 1 is reprogrammed to count  $\phi 2$  clock pulses for an 8us time period (12us for 5" disk drives).

- By operating system control, place the READ or WRITE command on the Command/Status Bus. The command is latched into the Command/Status Bus register.

- 3. By operating system control, activate the PIO B0 port, DISK OP\*. This enables the Formatter via the ± SYS CLK and the Control Signal Switching and Synchronization circuit. The READ or WRITE command is gated to the disk drive where it is called the READ or WRITE GATE enable signal.

4. Program DMA RDY/START through PIO B2 to the Disk Data Transfer Synchronizer, providing the "first byte" trigger. Operation from this point on is completely under the control of the WDI-II hardware circuits.

For more information about the continued operation of the WDI-II circuits in this mode, refer to Principles of Circuit Operation found in Chapter 5. The Disk Data Transfer Synchronizer circuit description provides information on the operation of the control circuits in conjunction with the Formatter and the Address Generator (DMA). Refer also to the Formatter Enable/Start circuit description which takes the 8 or 12us timing signal TOI from the CTC and enables or starts the Formatter operation.

Write-to-Disk Mode--The data to be written to the disk must be placed in system main memory in sequential order as follows:

- 1 Synchronization Byte

- 4 Header Bytes

- 512 Data Bytes

Part of the DMA programming indicates the location of this data in memory and how much data is to be written to the disk. In this mode, 517 bytes is always transferred from system main memory to one sector on one track. Data transfer from main memory to the disk occurs one byte at a time controlled by the Formatter. Refer to Chapter 5 for more information.

The write-to-disk mode may be followed up by data transfer error checking. This is done by immediately entering the read-from-disk mode and comparing the recorded error check bytes against those calculated by the WDI-II circuits.

Read-from-Disk Mode--As far as the operating system is concerned, only the 4 header bytes, or the 4 header bytes and the 512 data bytes, are output to the system main memory. Once started, data transfer is a continuous flow from the disk to main memory.

The hardware performs an error check on the header and data information in this mode. The CRC (Cyclic Redundancy Check) error verification data bytes are inserted on the disk by the Formatter in the write-to-disk mode. They are then checked against the number calculated from the data read from the disk in

the read-from-disk mode. The error check signal is output to the system program through PIO B7 CRC ERROR. This signal is held until the next CRC check is made. For more information on hardware operation in this mode, refer to Chapter 5.

1. Header Read--In order to perform a header read only, the DMA circuit must be programmed to read only 4 data bytes. After reading the bytes, the error check is made to assure that the header data transfer was accurate.

The header read may be used to determine the disk surface, the track, and the sector currently under the carriage head. With the sector information, the system program may enable CTC Counter 1 to count sector pulses until the disk position is reached which ensures correct disk data transfer. Refer to the paragraphs entitled Disk Data Transfer Mode for more information.

2. Data Read--In order to read the data from the disk, the DMA must be programmed to read 516 bytes, including the header and data bytes. Error checks assure that the complete transmission of data was accurate.

# Memory-to-Memory Data Transfer Mode

In the Memory-to-Memory Data Transfer Mode, the DMA is programmed to the transfer mode, allowing transfer of data from one location to another in system main memory using the DMA as a temporary data storage location. This mode begins operating immediately after the DMA is programmed. The DMA outputs a bus request (BUSRQ\*) signal to the system CPU. The CPU acknowledges the bus request with a bus acknowledge (BUSAK\*) signal and turns control over to the DMA. Control is retained until the data transfer is completed. For more information on DMA programming in this mode, refer to the microcircuit programming information in this chapter.

#### Extended Address Function

The Extended Address Function requires no initial programming of WDI-II circuits. Refer to Chapters 3 and 5 for more information.

#### MICROCIRCUIT PROGRAMMING

The following paragraphs provide a brief overview of programming the WDI-II microcircuits. For a more detailed discussion, refer to the Zilog Microcomputer Components Data Book.

# DMA (Direct Memory Access) Controller Programming

The DMA microcircuit contains seven groups of write registers programmed to control the various operating functions. Each group includes a base or control register and usually several subservient registers controlling individual DMA functions. The write registers are:

- WRO Port A Base (1 byte), Starting Address (2 bytes), and data Block Length (2 bytes) Registers.

- WR1 Port A Base and Variable Timing Registers (1 byte each).

- WR2 Port B Base and Variable Timing Registers (1 byte each).

- WR3 Byte Match Base, Mask and Match Registers (1 byte each).

- WR4 Port B Base (1 byte), Starting Address (2 bytes), and the Interrupt, Pulse, and Interrupt Vector Registers (1 byte each).

- WR5 DMA Control (1 byte).

- WR6 DMA Control and DMA Read Mask (status control) Registers (1 byte each).

The read registers output the status of the DMA and the various internal registers controlled by the Read Mask Register. The read registers are:

RRO DMA Status

RR1/RR2 Byte Counter Status

RR3/RR4 Port A Address Counter Status RR5/RR6 Port B Address Counter Status

The write registers are programmed from left to right in sequence, as shown in Figure 4-1. The starting address counters may either count up, down, or they may be fixed. They are multiplexed to the WDI-II Address Bus in a sequence dependent on the operation being performed.

Pigure 4-1: DNA SIMPLIFIED BLOCK DIAGRAM

The DMA has two programmable operations pertinent to WDI-II operation.

DMA Search--Enter the WDI-II Disk Data Transfer mode by selecting address E8h. Program the DMA as follows:

- 1. Select the data byte search mode.

- 2. Mask all bits of the Mask Byte so no search match can be made. (This makes the search continuous.)

- 3. Select the continuous data transfer mode. This allows hardware control of the DMA, assuring orderly data transfer during simultaneous operation with other WDI-II circuits.

- 4. Program the DMA with main memory address locations as follows:

- a. the beginning address.

- b. the block length of data to be transferred.

NOTE: This programming list for the DMA is by no means exhaustive. Refer to the Zilog Data Book for more information.

In operation, the following events occur:

- The DMA asks for and receives control of the S-100 Bus from the system CPU.

- The Formatter halts DMA operation until the first data byte is ready to be transferred. The DMA is then released.

- 3. The DMA outputs the beginning address and tries to match the first data byte. Hardware control circuits hold the address until the data transfer is completed.

- 4. The Formatter indicates to the DMA that the next byte is ready. Steps 1 through 4 are repeated until all the bytes are transferred.

- 5. The DMA relinquishes bus control to the CPU and the data transfer ends.

4. Programming and Program Control Information

DMA Transfer--To enter the WDI-II Memory-to-Memory Data Transfer Mode, program the DMA in the following manner:

- 1. Select the data transfer operation.

- 2. Select the continuous data transfer mode.

- Select the DMA ready input inhibit.

- 4. Program the DMA with main memory data byte address locations as follows:

- a. the beginning address.

- b. the number of data bytes to be transferred.

NOTE: This list of DMA programming steps is by no means exhaustive. Refer to the Zilog Data Book for more information.

In operation, the following events take place:

- The DMA asks for and receives control of the S-100 Bus from the system CPU.

- 2. The DMA outputs the beginning source address. The data byte from main memory is temporarily stored in an internal DMA data register.

- 3. The DMA outputs the beginning destination address and the data byte is transferred to that main memory location.

- 4. Steps 2 and 3 are repeated for each subsequent data byte until all are transferred.

- 5. Data transfer ends and the DMA relinquishes S-100 Bus control to the CPU.

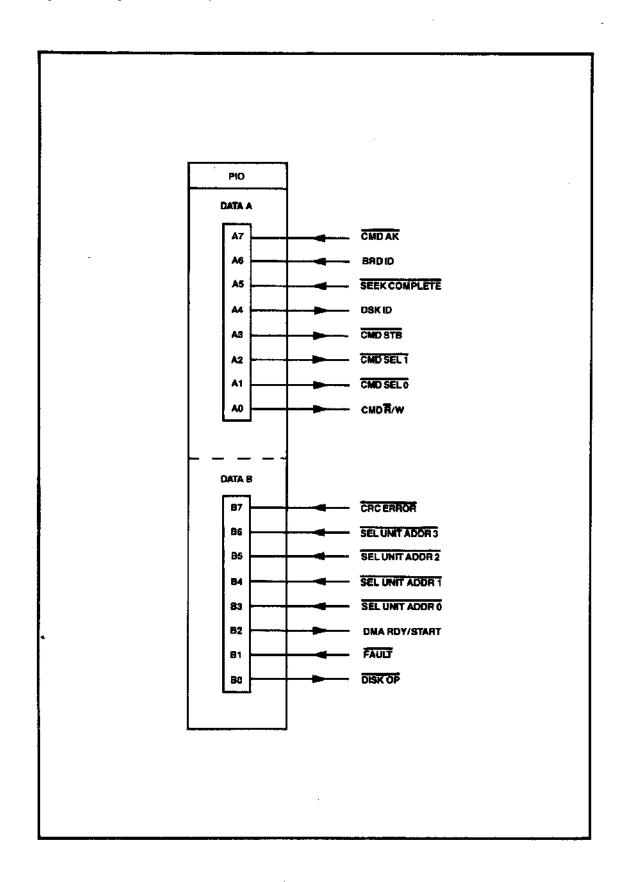

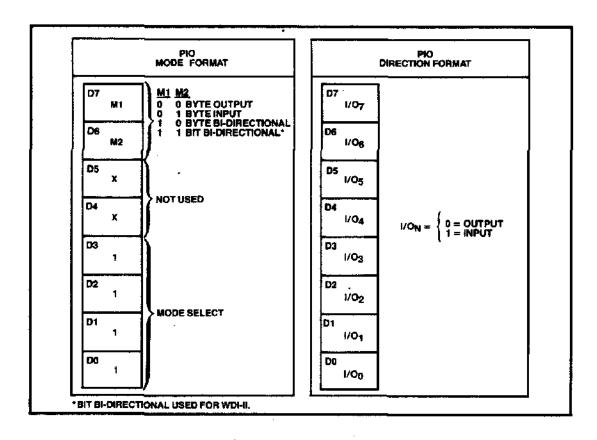

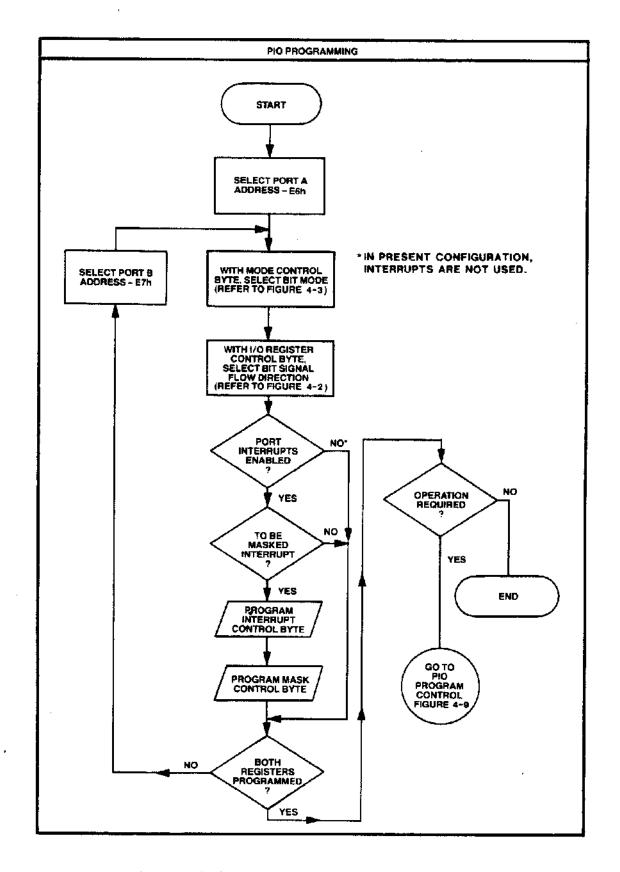

# PIO (Parallel Input/Output) Controller Programming

The PIO is a programmable, dual port, parallel I/O device. The PIO input and output lines may be programmed to operate individually or as a group. Preselected logical combinations of line transitions may optionally generate interrupts. Once the PIO mode and I/O operation have been defined, the PIO interfaces the operating system to the hardware on the WDI-II board. Since the PIO is hardware committed to the WDI-II board, the data flow of each line must conform to that shown in Figure 4-2.

Figure 4-2: PIO I/O SIGNAL FLOW DEFINITION

In the case of the WDI-II circuits, PIO Ports A and B (selected by addresses E6h and E7h respectively) are programmed to the Bit Input/Output mode. Control bytes select the mode and the bit input and output definition. The format of these control bytes are shown in Figure 4-3.

Although the PIO Interrupts are not used in the present WDI-II configuration, the potential does exist. Refer to Figure 4-4 for a generalized sequence of programming steps.

Figure 4-3: PROGRAMMED PIO CONTROL BYTE FORMAT

## 4. Programming and Program Control Information

Figure 4-4: PIO PROGRAMMING SEQUENCE

An interrupt byte selects the logic conditions and levels which generate the interrupt. The logic function may be an AND or an OR. In the former case, all inputs must be active to generate the interrupt. In the latter, only one input must be active. The active levels must be either all highs or lows. Any or all of the input bits may be masked by programming the Mask Control Byte.

## CTC (Counter/Timer Circuit) Programming

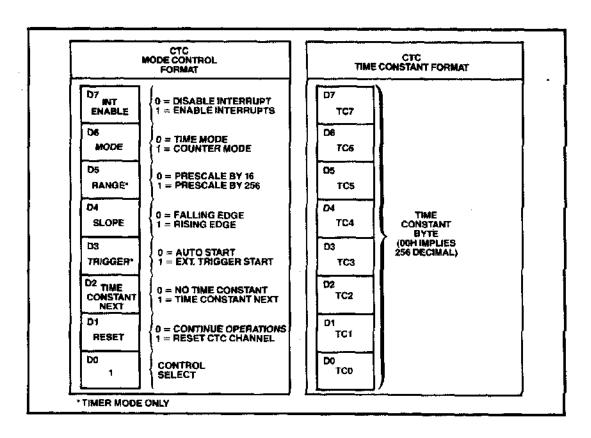

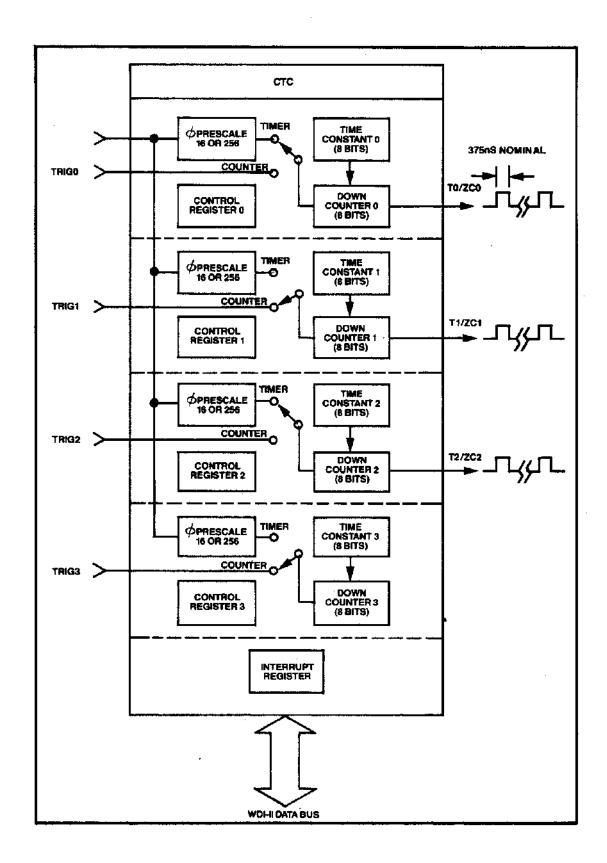

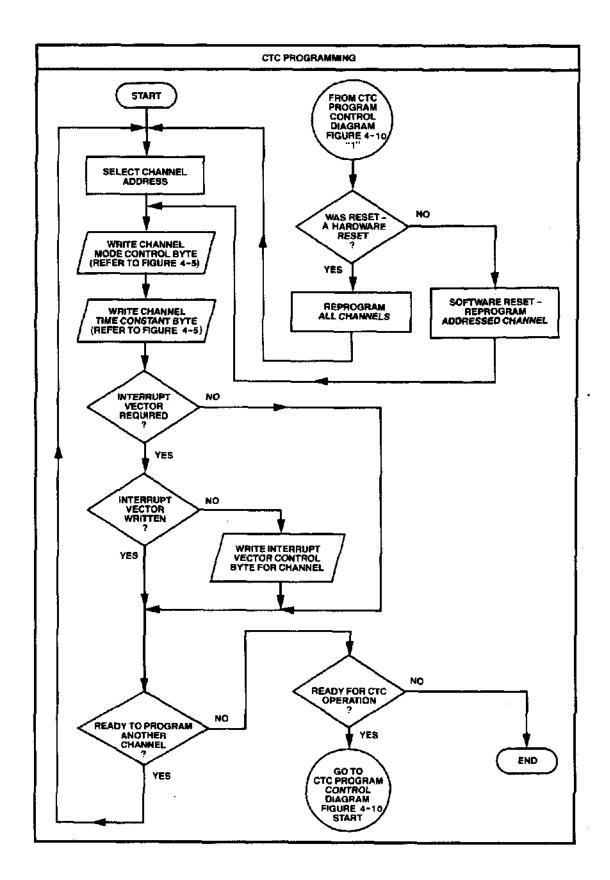

The CTC is used in both the counter and timer modes for controlling the operation of a disk drive during the Disk Data Transfer Mode. The four channels are mapped into the WDI-II I/O Port Assignments shown in Table 3-1. The mode of operation, counting rate, and interrupt behavior of each channel are programmed by outputting control bytes to the addressed channel (port). Each channel is initialized by writing a mode control byte and a time constant byte to each port as shown in Figure 4-5. A simplified representation of the CTC is shown in Figure 4-6. Refer to Figure 4-7 for a simplified diagram of CTC programming.

Figure 4-5: PROGRAMMED CTC CONTROL BYTE FORMATS

Figure 4-6: SIMPLIFIED CTC INTERNAL STRUCTURE

## 4. Programming and Program Control Information

Figure 4-7: CTC PROGRAMMING SEQUENCE

The timing element of each CTC channel is an 8-bit down counter. Three of the four channels have a hardware time out or zero count output. A counter is preloaded with the programmed 8-bit time constant from which it counts down to zero. Upon reaching zero, a 375ns positive-going pulse is output from the Zero Count pin. The time constant is automatically reloaded and the counting continues uninterrupted.

Bit 6 of the mode control byte programs the addressed CTC channel to the timer or count mode. In the timer mode, the clock input  $\phi 2$  (a 4 MHz signal) is connected in parallel with each channel.  $\phi 2$  is prescaled by 16 if bit D5 is reset, or by 256 if D5 is set. Bit 4 causes the counter to decrement on the clock falling or rising edge. In the timer mode, the time constant and prescaler are both preloaded in determining the total count time. This is expressed as follows:

t=(p\*K)/4

where t=time in us

p=prescaled value (programmed to 16 or 256)

k=time constant (programmed from 1 to 256; 256

is programmed as 00h)

4=4 MHz φ2 Clock Frequency

For example:

If t=8 us, then p=16, and K=2.

Each of the three CTC channels, when used as a counter, is driven by a control signal from the disk drive. In Channels 0 and 1 it is a servo control signal. For more information refer to the sections on the individual signals, SEEK COMPLETE\*, INDEX\* and SECTOR\*.

## PROGRAMMING CONTROL THROUGH WDI-II MICROCIRCUITS, REGISTERS AND COUNTERS

The following paragraphs explain how the operating system controls the WDI-II board functions and subsequently the hard disk drives. Operating system control is discussed in terms of WDI-II microcircuits, registers and counters. Figure 4-8 shows the connections between the WDI-II and disk drive. Table 3-2 provides information on disk drive signals and interfacing. For more detailed information on the disk

drives, including disk data transfer timing diagrams, refer to the appropriate disk drive manual. For more information on error messages, refer to the appropriate disk drive manual or the system manual.

Figure 4-8: WDI-II/DISK DRIVE INTERFACE BUS

### Command/Status Bus

Selecting address E0h enables the Command/Status Bus. One-of-eight command or status bytes may be selected. Four are disk drive command bytes while the remaining four bytes transmit disk drive status information. As shown in Table 4-1, one byte addresses several functions. Refer to PIO bits AO, Al, A2, A3 and A7 for Command/Status Bus control signal information.

NOTE: All signals on the Command/Status Bus are active low. Refer to Table 4-1 for more information.

Table 4-1: HARD DISK DRIVE COMMAND/STATUS **BUS SIGNALS**

|                | COMMAND/STATUS BUS<br>CONTROL SIGNALS |       |       | COMMAND/STATUS BUS SIGNALS |                            |                            |              |                    |                 |         |                |                |

|----------------|---------------------------------------|-------|-------|----------------------------|----------------------------|----------------------------|--------------|--------------------|-----------------|---------|----------------|----------------|

|                | R/W                                   | SEL 1 | SEL 0 | BYTE                       | 8/7 7                      | BIT 6                      | BAT 5        | B#T 4              | BIT 3           | BIT 2   | BIT 1          | BITO           |

| DRIVE COMMANDS | 0                                     | ō     | 0     | 0                          | UAS31                      | UASP                       | UAST         | UASO               | HAS13           | HAS0    | C≜S9           | CAS8           |

|                | Q.                                    | 0     | 1     | 1                          | CA972                      | CAS6                       | CA95         | CAS4               | CASS            | CAS2    | CAS1           | CAS0           |

|                | 0                                     | 1     | 0     | 2                          | SERVO<br>OFFSET<br>PEVERSE | SERVO<br>OFFSET<br>FORWARD |              |                    | DIAGNOSTIC      |         | READ<br>GATE   | WRITE<br>GATE  |

|                | 0                                     | 1     | 1     | 3                          |                            |                            |              |                    |                 |         | RE-ZERO        | FAULT<br>CLEAR |

| DRIVE STATIJS  | 1                                     | Đ.    |       | 4                          | SPEED<br>EAROR             | ILLEGAL<br>ADDRESS         | P/W<br>FAULT | SERVO<br>ERROR     | AE-<br>ZETICING | SEEKING | ON<br>CYLINDER | UNIT<br>RÉADY  |

|                | 1                                     | Q     | Ť,    | 5                          | GUARD<br>BAND              |                            |              | WRITE<br>PROTECTED | PLÓ<br>ERROR    | POR     |                | R/W<br>UNSAFE  |

|                | 1                                     | 1     | ٥     | 6                          | CAV75                      | CAVE                       | CAV5         | CAV4               | CAV3            | CAV2    | CAV1           | CAV0           |

|                | 1                                     | 1     | -     | 7                          | ∪ <b>4</b> ₩36             | UAV2                       | UAV1         | UAVO               | HAV14           | HAVO    | CAV9           | CAV8           |

NOTE:

1. UASING = UNIT ADDRESS SELECT

1. DASING = UMEN ADDRESS SELECT

2. CASO-9 = CYLINDER ADDRESS SELECT

3. MASO-1 = MEAD ADDRESS SELECT

4. MAVO-1 = MEAD ADDRESS VERIFY

5. CAVO-9 = CYLINDER ADDRESS VERIFY

6. UAVO-3 = UNIT ADDRESS VERIFY 7. SPACE = UNUSED BIT (NORMALLY AT LOGICAL ZERO)

8. NEGATIVE TRUE LOGIC:

LOGICAL 0 = 2.4 TO 5.0V

Disk Drive Unit Address Select/Verify and Related Commands--Unit Address Select (UAS) 0-3 byte 0 bits 4-7 are used to address a specific disk drive. Unit Address Verify (UAV) 0-3 byte 7 bits 4-7 may be used to verify that the correct drive has been selected. ILLEGAL ADDRESS byte 4 bit 6 indicates that an illegal or nonexistent address for the hard disk drive has been issued. When a unit address is issued, all disk drives will check the address but only one should respond.

#### CAUTION

Cromemco recommends that no more than seven drives be connected to the WDI-II/Disk Drive Interface Bus at one time.

Head Address Select/Verify--Head Address Select (HASO and HASI) byte 0 bits 2 and 3 are used to address a specific head in the addressed disk drive. Head Address Verify HAVO and HAVI byte 7 bits 2 and 3 are used to verify that the disk drive has received the correct head address. Depending on the disk drive, either 1 or up to 3 separate heads may be selected for the data transfer. The fourth head accesses disk location information in a read only mode. The signals accessed are the INDEX\* and SECTOR\* that have been prerecorded on the disk servo surface as reference signals for controlling disk drive operation.

Cylinder Address Select/Verify and Related Commands—Cylinder Address Select CASO-9, byte 1 in its entirety and byte 0 bit 0 and bit 1, are used to address a specific cylinder (track location) on the disk. Cylinder Address Verify CAVO-9, all of byte 6 and byte 7 bit 0 and bit 1, may be used to verify that the disk drive unit has received the correct cylinder address. SEEKING byte 4 bit 2 is active while the head is being moved to the correct track. The ON CYLINDER signal, byte 4 bit 1, indicates that the head has arrived at the correct track (cylinder).

Servo Command and Status Signals--SERVO ERROR byte 4 bit 4 indicates that the selected drive has detected a seek error condition. This may be due to the following:

- The SEEKING (cylinder) process has not been completed.

- 2. REZERO is incomplete.

- An invalid address (UAS, CAS, or HAS) has been selected.

- 4. The head is over a GUARD BAND.

For SEEK and REZERO, the REZERO or POR (Power On Reset) command must be reissued to enable disk drive operation. Issuing FAULT CLEAR will clear SERVO ERROR.

SERVO OFFSET FORWARD and SERVO OFFSET REVERSE byte 2 bit 6 and bit 7 cause the head to move forward (toward) or reverse (away from) the disk drive spindle. The head

moves in 400 micro inch increments. A new command must be reissued for each subsequent movement. ON CYLINDER goes false until the offset position is reached.

#### NOTES:

- Servo offset commands may be used in an error recovery mode.

- 2. Servo offset commands will affect disk drive operation immediately. This means that only the CMD STB is needed. CMD AK has no effect. (This occurs only in Command/Status Bus byte 2.)

**Diagnostic--**DIAGNOSTIC byte 2 bit 3 causes the disk drive to ignore a R/W UNSAFE signal while other byte 2 drive commands are active.

Write (to disk) and Read (from disk) Control Signals—The commands WRITE GATE byte 2 bit 0 and READ GATE byte 2 bit 1 are normally inactive until the final phases of the disk data transfer operation when one or the other is programmed for the active state. At this time, the WDI-II circuits allow the READ or WRITE GATE signal to pass to the disk drive, enabling the disk drive for the forthcoming data transfer. Other WDI-II circuits begin the actual data transfer when the proper disk sector location is reached. The command mode is held while waiting for the WRITE or READ GATE command to be sent to the disk drive by holding the CMD STB signal true. When the WRITE or READ GATE signal is passed to the disk drive, the drive responds immediately without waiting to output the CMD AK signal.

R/W (Read/Write) FAULT byte 4 bit 5 indicates that multiple head selection, write current is flowing but either no write data exists, or the WRITE GATE has not been enabled.

R/W UNSAFE byte 5 bit 0 indicates that the FAULT signal is true.

WRITE PROTECT byte 5 bit 4 indicates that writing to the disk is not allowed. This may be because a FAULT signal is active or the disk drive is set to the write protect mode. Refer to the appropriate disk drive instruction manual for more information.

Cromemco WDI-II Instruction Manual

4. Programming and Program Control Information

Rezero/Rezeroing—REZERO byte 3 bit 2 causes the head to move to track 000; the head and cylinder registers are reset to zero while ON CYLINDER, SERVO ERROR and R/W FAULT are cleared. A SEEK COMPLETE pulse is generated at the end of REZERO. REZEROING byte 4 bit 3 is active during the REZERO operation.

Fault Clear--FAULT CLEAR byte 3 bit 0 resets the FAULT status flip-flop.

Guard Band--GUARD BAND byte 5 bit 7 indicates the read/write head is outside the data track area.

PLO (Phase Locked Oscillator) Error--PLO ERROR byte 5 bit 3 indicates that the disk drive phase locked oscillator is not synchronized with the clock pulses from the servo control surface.

**POR (Power-On Reset)**—POR byte 5 bit 2 indicates a 12 to 15s delay. This allows the disk drive motor to reach proper operating speed. The disk drive logic circuits are reset by POR during this time.

Speed Error--SPEED ERROR byte 4 bit 7 indicates that the disk speed is not within tolerance. Refer to the disk drive instruction manual for more information.

Unit Ready--UNIT READY byte 4 bit 0 indicates that no FAULT exists. The disk drive unit is ready to read, write or seek.

Extended Address Function—The system program enables this function by using address Elh. Data inputs DOO through DO7 from the S-100 Bus are enabled. The RD\* signal from the S-100 Bus clocks data from the WDI-II Data Bus, through the Extended Address Latch and onto the S-100 Bus Extended Address Lines (A16-A23). Addresses E2 and E3 are not used.

## PIO (Parallel Input/Output Controller) Control

Addresses E4h through E7h are used in programming and controlling the operation of the PIO. E4h and E5h are used to select the PIO data (operational) modes while E6h and E7h select the command (programming) modes. In

the command modes, the I/O functions of the registers are selected by the system program. In the data modes, the programmed functions are enabled, in effect becoming part of the WDI-II circuit board hardware. The command modes should be programmed at the beginning of WDI-II board operation. The data modes are then selected, as required, during the execution of the Disk Data Transfer mode. Refer to Figure 4-9 for a simplified program control sequence for the PIO.

Port A Data Mode—Address E4h selects the Data Mode for Port A of the PIO. The port I/O is 8 bits wide and interfaces the operating system to the hard disk drive(s) through the Command/Status Bus. Each individual bit and its purpose follow. For more information about bits A0, A1, A2, A3 and A7, refer to the section entitled Command/Status Bus in this chapter. Refer also to Table 4-1, Table 3-2, and the Z-2H and HDD manual.

AO Command Read/Write--CMD R\*/W provides operating system control of the Command or Status mode. The Command mode is selected with a logical true, the Status mode with a logical false.

Al and A2, Command Select 0 and 1--CMD SEL 1\* and CMD SEL 2\* provide operating system selection of one-of-eight Command/Status Bus bytes in conjunction with A0. Four bytes may be selected in the command mode and four bytes in the status mode.

A3 Command Strobe--CMD STB\* is used in conjunction with A7 to provide handshaking between the S-100 Bus and the disk drive unit. In the command mode, A3 is issued by the operating system at least 200ns after the command byte is placed on the Command/Status Bus. A3 signals the disk drive that the Command/Status Bus information is valid. In the status mode, A3 signals the disk drive that the operating system is ready to receive status information.

A4 Drive Identifier--Under program control, DRV ID indicates the disk size of the addressed disk drive. In conjunction with A6, this signal also indicates the model of the WDI Winchester Disk Interface board (WDI or WDI-II). A logic true output from A4 indicates that a 5" disk drive is being used; a logic false indicates an 8" disk drive.

•

Ĵ

Figure 4-9: PIO PROGRAM CONTROL

A5 Seek Complete-SEEK COMPLETE\* pulses at the completion of the head carriage movement. This signal is input to the CTC and PIO microcircuits, and this can trigger a counter and/or be polled immediately by the operating system.

A6 Board Identifier--BRD ID will always be the same state as A4 if the WDI-II is the interface board.

A7 Command Acknowledge--CMD AK\* is used in conjunction with A3 to provide handshaking between the S-100 bus and the hard disk drive. In the command mode, this signal indicates that the disk drive has received and latched the command byte. The operating system can now have the WDI-II release A3. In the status mode, the disk drive indicates that the status byte is valid; that is, the operating system should read this byte and then release the command strobe. Note that A7 is issued by the selected drive only.

Port B Data Mode--Address E5h selects the Port B Data Mode of the PIO. The port I/O is made up of 8 bits of data interfacing the operating system to the WDI-II circuits and a disk drive. Each individual bit and its purpose follow.

BO Disk Operation--DISK OP\* has two primary purposes that relate to disk data transfer.

- It provides the "first byte" trigger which initializes the appropriate WDI-II circuits for the coming data transfer.

- It controls the pulse synchronized READ or WRITE GATE signals issued to the disk drive units.

Bl Fault--FAULT\* indicates to the system that at least one of several possible problems exist in the disk drive unit. These are:

- multiple heads selected,

- 2. write current with no write data,

- write current without WRITE GATE enabled,

- 4. WRITE GATE active with no ON CYLINDER signal,

- 5. disk drive phase locked oscillator synchronization error indicated by PLO ERROR,

- 6. head forced off track, or

- 7. disk drive internal SEEK or REZERO time out.

FAULT\* inhibits the write-to-disk mode when active. The Command/Status Bus may be polled to determine the fault. REZERO clears FAULT\*.

B2 DMA Ready/Start--DMA RDY/START is issued by the system to the Disk Data Transfer Synchronizer which generates the DMA RDY signal. The bus request (BUSRQ\*) is output by the DMA to the system CPU when DMA RDY is received.

B3-B6 Select Unit Address 0 through 3--SEL UNIT ADDR 0\* through SEL UNIT ADDR 3\* indicate which disk drive has been selected. The same information can be obtained on the Command/Status Bus using UASO through UAS3, and it is recommended that UASO through 3 be used rather than these signals. Refer to the Z-2H and HDD manual for information pertaining to selection of disk drive addresses.

B7 CRC Error--An active CRC ERROR signal indicates to the system program that an error has occurred in transferring data to or from the disk.

Port A Programming Mode—Address E6h selects the Port A programming mode. PIO Port A is programmed for operation as stated under Port A Data Mode. Programming is received from the S-100 Bus under the control of the operating system drivers. Refer to Figure 4-4 for a simplified diagram of PIO programming requirements.

Port B Programming Mode--Address E7h selects the Port B programming mode. PIO Port B is programmed for operation as stated under Port B Data Mode. Programming is received from the S-100 Bus under the control of operating system drivers. Refer to Figure 4-4 for a simplified diagram of PIO programming requirements.

#### DMA Control

Address E8h selects the DMA microcircuit. The DMA is programmed for one of two operations. During disk data transfer, the DMA is programmed for the search continuous mode, and for memory-to-memory transfer, it is programmed for the transfer mode. The DMA is placed in the Command (programming) or Data (operating) modes under software control. Refer to the section entitled Microcircuit Programming for more information.

Addresses E9h through EBh will also select the DMA microcircuit but it is recommended that E8h be used exclusively for this purpose. E9h through EBh are then reserved for future operating mode expansion. Using E8h for DMA Control will ensure software compatibility with future hardware configurations.

#### CTC Control

Each of these addresses, ECh through EFh, enables one-of-four counters that is part of the CTC microcircuit. In the present configuration, only Channels 0-2 are used. Each is used in the disk data transfer operation. Refer to Figure 4-10 for a simplified CTC program control sequence.

Channel 0 is addressed by ECh and is used in the counter mode only. It is programmed to a value of 1. When the INDEX pulse from the disk drive servo control surface is received by the TRIGI input, the operating system learns of this event by monitoring the CTC data lines. For more information, refer to the paragraphs under CTC Programming in this chapter. Note that the INDEX\* pulse is also connected to A5 of the PIO. This counter, in the timer mode, could be used to check the rotational speed of the disk.

Channel 1 is addressed by EDh and is used in both the counter and timer modes. In the counter mode, the channel is programmed to count sectors, determining when disk data transfer is to start. The counter is then immediately programmed for the timer mode with a predetermined time period. The timer ensures a specific passage of time before the beginning of the next event in the disk data transfer. When time is up, the time out TO1 signal from the CTC triggers the next event.

## Cromemco WDI-II Instruction Manual 4. Programming and Program Control Information

Channel 2 is addressed by EEh and is used in the counter mode only. It is used exactly like the counter of Channel 0. The signal input is the SEEK COMPLETE\* signal from the disk drive, which indicates that the cylinder seeking process has been completed.

EF Counter 3 is not used in the operation of the WDI-II circuit board.

Figure 4-10: CTC PROGRAM CONTROL

## Chapter 5

#### PRINCIPLES OF OPERATION

#### INTRODUCTION

This chapter explains the operating principles of the WDI-II.

#### PRINCIPLES OF OPERATION

The primary purpose of the WDI-II is to provide an interface between the S-100 Bus and a hard disk drive. This facilitates the exchange of data between the system main memory and the hard disk surface media. A secondary purpose that is often very important, is to transfer data rapidly between main memory locations. The board may also be used to place "extended addresses" onto the appropriate S-100 Bus signal lines.

## Operating Modes

The operating system causes control, status, address, and data information to be exchanged with the WDI-II or to be passed on to the hard disk drive. The operations and functions that the WDI-II performs are selected under operating system control by programming and selectively enabling the operation of the registers contained within the WDI-II microcircuits. These operations and functions are explained in greater detail in the following paragraphs.

#### Disk Data Transfer Mode