# MAXIMIZER

**Board Manual**

December 1984

CROMEMCO, Inc. P.O. Box 7400 280 Bernardo Avenue Mountain View, CA 94039 023-2034 Rev. B

Copyright © 1984 CROMEMCO, Inc. All Rights Reserved This manual was produced using a Cromemco System Three computer running under the Cromemco Cromix Operating System. The text was edited with the Cromemco Cromix Screen Editor. The edited text was proofread by the Cromemco SpellMaster Program and formatted by the Cromemco Word Processing System Formatter II. Camera-ready copy was printed on a Cromemco 3355B printer.

The following are registered trademarks of Cromemco, Inc.

C-Net®

Cromemco®

Cromix®

FontMaster®

SlideMaster®

SpellMaster®

System Zero®

System Two®

System Three®

WriteMaster®

The following are trademarks of Cromemco, Inc.

C-10<sup>TM</sup>

CalcMaster<sup>TM</sup>

DiskMaster<sup>TM</sup>

Maximizer<sup>TM</sup>

System One<sup>TM</sup>

TeleMaster<sup>TM</sup>

#### TABLE OF CONTENTS

| Chapter 1: INTRODUCTION                                | 1                                     |

|--------------------------------------------------------|---------------------------------------|

| Hardware Specifications Software Specifications        | $\begin{array}{c} 1 \\ 2 \end{array}$ |

| Applications                                           | 3                                     |

| Chapter 2: INSTALLATION                                | 5                                     |

| Jumpers                                                | 6                                     |

| Cabling                                                | 6                                     |

| Installation Procedure                                 | 7                                     |

| In Case of Difficulty                                  | 8                                     |

| Chapter 3: THEORY OF OPERATION                         | 9                                     |

| Introduction                                           | 9                                     |

| Data Paths                                             | 11                                    |

| Address Paths                                          | 11                                    |

| Microcode RAM and ROM (Max-C)                          | 11                                    |

| Instruction Sequencer (Max-C)                          | 12                                    |

| Arithmetic Logic Unit (Max-C)                          | 12                                    |

| Shift, Carry, Loop and Test Logic (Max-C)              | 12                                    |

| Data RAM (Max-I)                                       | 13<br>13                              |

| Multiplier (Max-I) Flag and Squirrel Registers (Max-C) | 13                                    |

| S-100 Interface and State Circuits (Max-I)             | 13                                    |

| I/O Register Control (MAX-I)                           | 14                                    |

| C-Bus Interface and State Circuits (Max-I)             | 14                                    |

| Clock (Max-C)                                          | 14                                    |

| Power Supply                                           | 14                                    |

| Microcode Word Description                             | 15                                    |

| Auxiliary Control Field                                | 15                                    |

| I/O Control Field                                      | 15                                    |

| 2901C Control Field                                    | 15                                    |

| A Address Field                                        | 16                                    |

| B Address Field                                        | 16                                    |

| Branch, Immediate, and Data RAM Field                  | 16                                    |

| Conditional Sequence/Test, Implicit Branch, and        | 4.0                                   |

| Processor Control Point                                | 16                                    |

| Cycle Time Period                                      | 16                                    |

| Conditional Sequence/Test Modes                        | 17<br>18                              |

| Carry-In Bit (Inverted)<br>Shift Modes                 | 18                                    |

| Immediate To/From Yout                                 | 19                                    |

| . Output Clock Enables                                 | 19                                    |

| Using Bit-Number as Argument                           | 21                                    |

| External Bus Input Clock Enables                       | 24                                    |

| Input Enables                                          | 25                                    |

| Alternate Test for Implicit Branch Determination Implicit Branch Field Test Type Polarity Bit Processor Control Points Field Polarity Bit                                                                                                                                                                                                                                                                                                                               |                                                  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

| LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  |  |  |  |

| Figure 2-1: Maximizer Coprocessor (Max-C) Board Figure 2-2: Maximizer I/O Coprocessor (Max-I) Board Figure 3-1: Maximizer Block Diagram Figure 3-2: Basic Fields and Bit Positions Figure 3-3: Auxiliary Control Field Figure 3-4: Input/Output Field Figure 3-5: 2901C Control Field Figure 3-6: Test and Processor Control Points Field of Conseq/Test Modes Figure 3-7: Conditional Sequencer Field Figure 3-8: Test and Implicit Branch Field of Condseq/Test Modes | 5<br>6<br>10<br>15<br>16<br>19<br>25<br>28<br>28 |  |  |  |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                  |  |  |  |

| Table 2-1: Connector J1 Pin Assignments and Signals Table 2-2: S-100 Bus Connector Pin Assignments and Signals Table 3-1: ALU Destination and Shift Control Table 3-2: Carry Bit/Flag and OVR Flag for Various ALU Functions Table 3-3: Source Operand and ALU Function Matrix                                                                                                                                                                                          | 7<br>8<br>26<br>26<br>27                         |  |  |  |

| LIST OF APPENDICES                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |  |  |  |

| Appendix A: Parts List Max-C                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                               |  |  |  |

| Appendix B: Parts List Max-I                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |  |  |  |

SCHEMATICS

LIMITED WARRANTY

#### Chapter 1

#### INTRODUCTION

Many scientific and engineering applications, particularly those involving complex video imaging, require large amounts of RAM and high-speed number-processing capability. The two-board Maximizer, consisting of the Maximizer Coprocessor (Max-C) and Maximizer I/O Coprocessor (Max-I), when used with Cromemco's DPU, provides an ideal solution to these applications requirements.

The Maximizer is a general-purpose, microprogrammable array coprocessor, capable of performing many functions in a fraction of the time required by the 68000 microprocessor.

#### HARDWARE SPECIFICATIONS

#### Microprocessor:

- 2901C microprocessor, using bit-slice internal ECL logic.

- Separate program and data paths.

- 16 general-purpose 2-port registers.

- 60 nsec, 16-bit multiplier.

- Double pipelined architecture.

#### Instruction Time:

62.5 to 125 nsec in four microcode-controllable steps; most instructions execute in 62.5 nsec.

#### Microcode Control Store:

- 4.096 x 48 bits of read/write RAM.

- 512 x 48 bits of PROM.

#### Data Storage:

16 Kbits x 8 bits of 55 nsec read/write storage.

1. Introduction

#### Clock:

48 MHz system clock, phase-locked to the S-100 bus clock, variable from 32 to 60 MHz under microcode control.

#### Input/Output:

- I/O port addresses: F4h through F7h.

- S-100 DMA rate of 4 Mbytes/sec over full 16-Mbyte address space.

- S-100 and C bus DMA-controlled by I/O state machines.

#### Hardware:

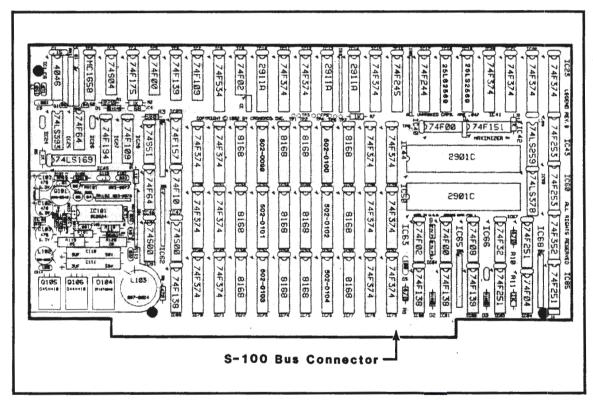

- Two S-100 bus boards, with about 150 IC's.

- Two high-efficiency, switching, regulated 5-VDC power supplies, operating at 6 A.

#### SOFTWARE SPECIFICATIONS

The Maximizer operates with Cromemco's Cromix Operating System, and Cromemco's 256KZ and MCU (Rev K and up) boards. The Maximizer supports FORTRAN 77, Pascal, and C compilers to generate in-line code for the Maximizer with no changes to the source code. The operating environment allows multiple users to share the Maximizer's resources. Multi-tasking is supported without changes to the Cromix Operating System.

#### Microcode:

- Control Structures:

- Microcode subroutines up to four levels.

- Single-instruction looping.

- Override for exiting multi-instruction loops.

- 16 conditional tests.

- Ability to flush microcode pipeline.

- Constant and computed addresses may be used for data storage and jump targets.

- Parallel control of input and output.

- Instruction time controllable by microcode.

- Multi-word shifting and arithmetic.

#### Development Software:

- Microcode assembler (written in C language) presents uniform register-transfer syntax.

- Microcode linker and loader.

- Microcode debugger is modeled after 68000 debugger.

#### APPLICATIONS

The Maximizer performs all basic arithmetic functions. In addition, it performs format conversions, square roots, logarithmic, and trigonometric functions. All floating-point arithmetic is handled according to the IEEE Standard, in single-precision (32-bit) or double-precision (64-bit) format, with dramatic speed improvements over normal DPU machines. The Maximizer also handles 16-bit and 32-bit integer operations.

Cromemco's Fast FORTRAN-77, Fast Pascal, and Fast C provide compiler support for the Maximizer. No knowledge of the Maximizer hardware or software is required to use the Maximizer with these languages. In addition, by recompiling and linking with the Fast software listed above, existing programs in 68000 FORTRAN, 68000 Pascal, and 68000 C can be used without modification.

Because of its high-speed number-processing and rapid DMA-accessing capabilities, many video graphics applications can also be run on the Maximizer.

Cromemco recommends that, because of the Maximizer's cooling requirements, this board set should only be installed in systems with adequate, positive fan cooling.

Cromemco Maximizer Board Manual

#### Chapter 2

#### **INSTALLATION**

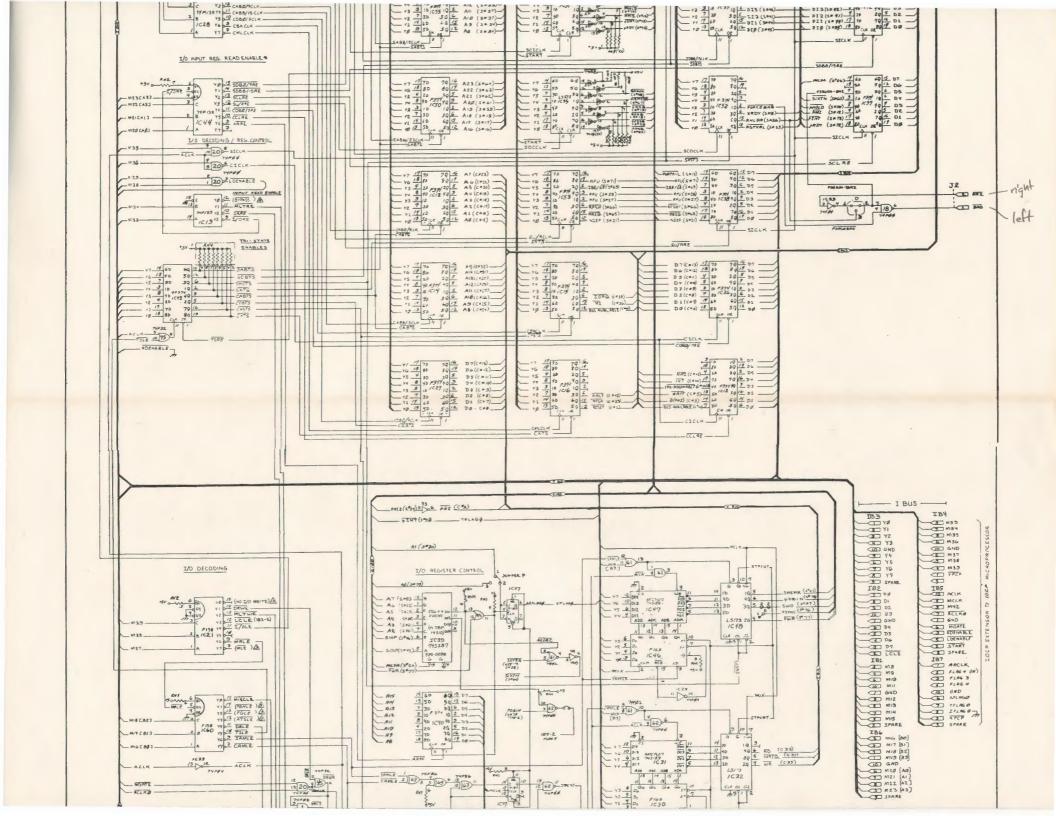

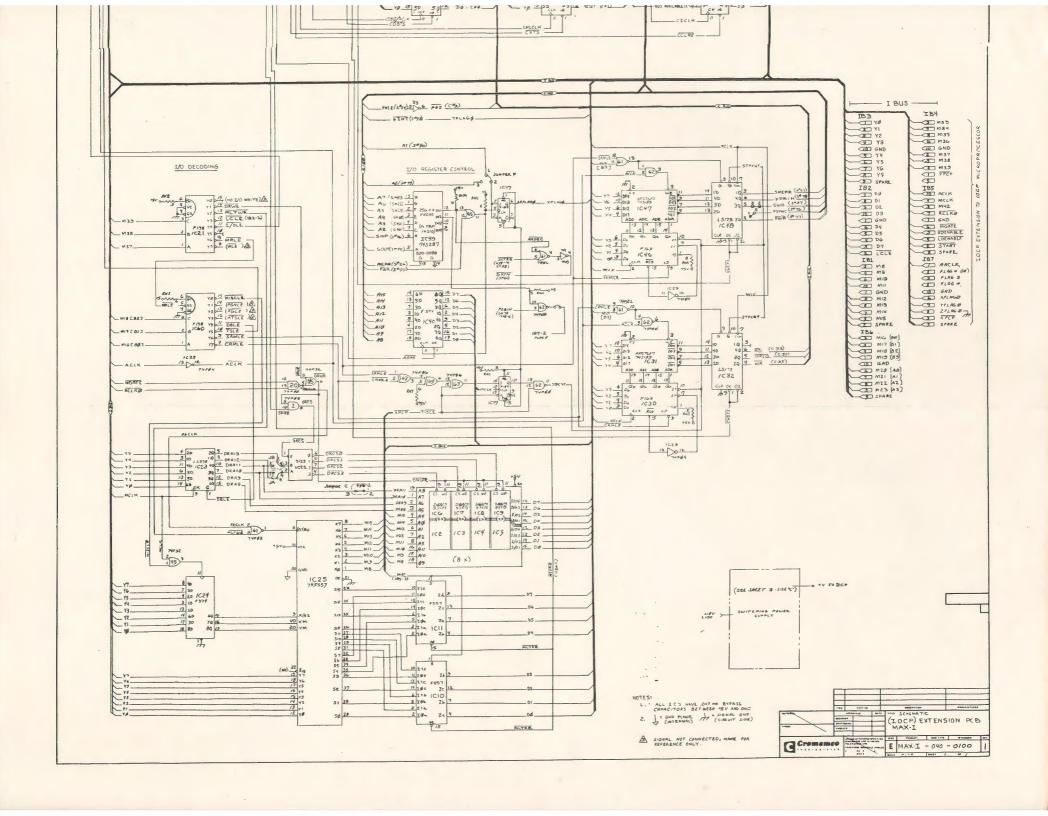

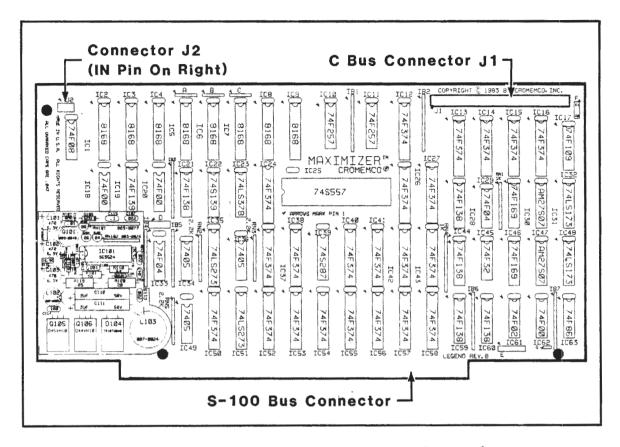

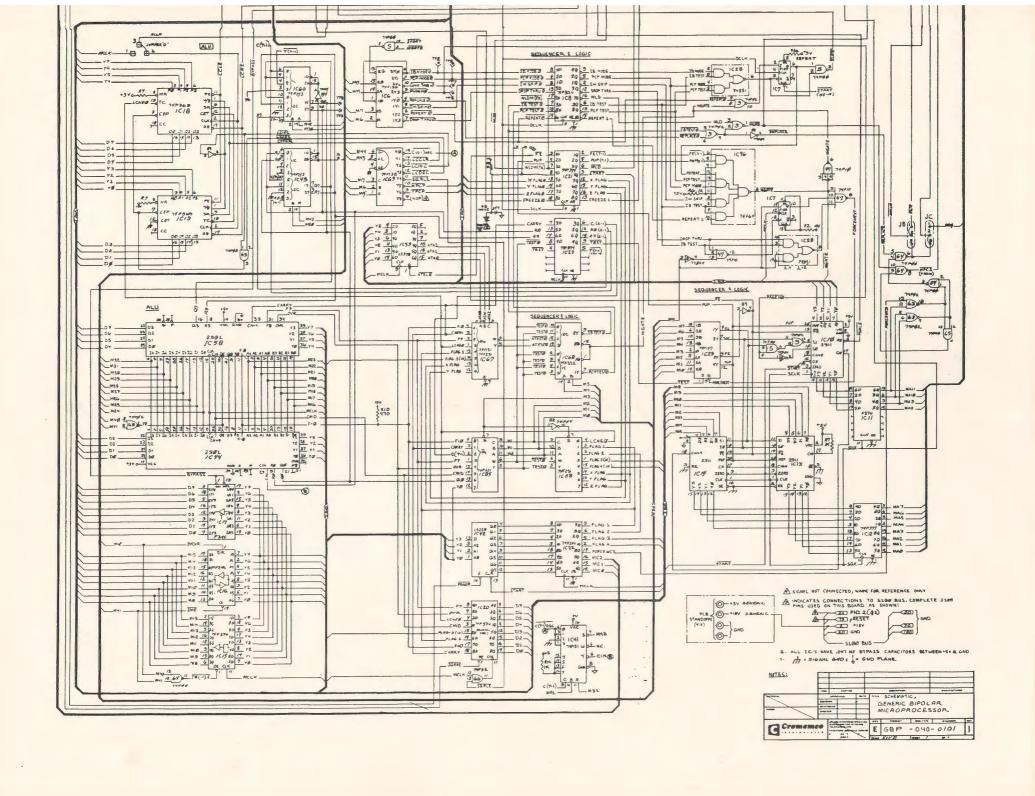

The Maximizer boards are shown in Figures 2-1 and 2-2.

Figure 2-1: MAXIMIZER COPROCESSOR (MAX-C) BOARD

Figure 2-2: MAXIMIZER I/O COPROCESSOR (MAX-I) BOARD

#### **JUMPERS**

There are no user-configurable jumpers on either of the Maximizer boards. Do not change any of the jumpers on these boards.

#### CABLING

Two cables attach to the Maximizer—the DMA priority cable and the optional C bus cable. The DMA priority cable connects the IN pin (right pin) of connector J2 on the Max-I board to the OUT pin (right pin) of connector J2 on the STDC board (or to the OUT pin (right pin) of connector J3 on the WDI-II board). The pin assignments and signals for the C bus connector, J1, are listed in table 2-1. The pin assignments and signals for the S-100 bus connector are listed in table 2-2.

Table 2-1: CONNECTOR J1 PIN ASSIGNMENTS AND SIGNALS

| Pin No.       | Signal   | Input | Output | Pin No. | Signal                | Input | Output |

|---------------|----------|-------|--------|---------|-----------------------|-------|--------|

| 1             | GND      | -     | _      | 26      | A10                   | -     | х      |

| $\frac{1}{2}$ | RESET    | -     | x      | 27      | A11                   | -     | x      |

| 3             | Not Used | -     | -      | 28      | GND                   | -     | -      |

| 4             | GND      | -     | -      | 29      | A12                   | -     | x      |

| 5             | WAIT     | х     | -      | 30      | A13                   | ~     | х      |

| 6             | D0       | x     | x      | 31      | A14                   | -     | х      |

| 7             | D1       | х     | x      | 32      | <u>A1</u> 5           | -     | x      |

| 8             | D2       | x     | x      | 33      | $\overline{	ext{RD}}$ | -     | x      |

| 9             | D3       | x     | x      | 34      | <u>GN</u> D           | -     | ~      |

| 10            | D4       | х     | х      | 35      | WR                    | - ,   | х      |

| 11            | D5       | x     | х      | 36      | M1                    | -     | x      |

| 12            | D6       | x     | x      | 37      | MREQ                  | -     | x      |

| 13            | D7       | x     | x      | 38      | IORQ                  | -     | X      |

| 14            | GND      | -     | -      | 39      | RFSH                  | -     | X      |

| 15            | A0       | _     | x      | 40      | CPU DISCONNECT        | Х     | -      |

| 16            | A1       | -     | х      | 41      | BUS AVAILABLE         | х     | x      |

| 17            | A2       | -     | x      | 42      | HALT                  | -     | x      |

| 18            | A3       | -     | x      | 43      | GND                   | -     | -      |

| 19            | A4       | -     | X      | 44      | INT                   | Х     | -      |

| 20            | A5       | -     | x      | 45      | NMI                   | Х     | -      |

| 21            | GND      | -     | -      | 46      | Not Used              | -     | -      |

| 22            | A6       | -     | x      | 47      | Not Used              | -     | -      |

| 23            | A7       | -     | x ·    | 48      | PRI 3                 | -     | -      |

| 24            | A8       |       | х      | 49      | Not Used              | -     | -      |

| 25            | A9       | -     | х      | 50      | GND                   | -     | -      |

#### INSTALLATION PROCEDURE

Use the following procedure to install the Maximizer board set in your system:

- 1. Turn off the system power.

- 2. Insert the Maximizer board set into any adjacent pair of S-100 slots available.

- 3. Install the DMA priority cable between connector J2 on the Max-I board and connector J2 on the STDC (or connector J3 on the WDI-II board).

- 4. If your system has a C bus, install the C bus cable to connector J1 on the Max-I board.

- 5. Turn on the system power.

- 6. Boot the Cromix Operating System.

- 7. Perform the software installation procedures described in the manual accompanying the software you intend to run on the Maximizer.

#### IN CASE OF DIFFICULTY

The Maximizer adds a significant electrical load on the system power supply which may affect the selection of the proper line-voltage tap. Refer to the manual provided with your system should you need to change the line-voltage tap to accommodate the Maximizer.

Table 2-2: S-100 BUS CONNECTOR PIN ASSIGNMENTS AND SIGNALS

| Pin No.  | Signal               | Input | Output | Pin No.  | Signal               | Input  | Output |

|----------|----------------------|-------|--------|----------|----------------------|--------|--------|

| 1        | +8 VDC               | -     |        | 51       | +8 VDC               | -      | _      |

| 2        | +18 VDC              | -     | -      | 52       | -18 VDC              | -      | -      |

| 3        | XRDY                 | -     | x      | 53       | Not Used             |        |        |

| 4<br>5   | Not Used<br>Not Used |       |        | 54       | SLVCLR*              | -      | х      |

| 6        | Not Used             |       |        | 55       | Not Used             |        |        |

| 7        | Not Used             |       |        | 56<br>57 | Not Used<br>Not Used |        |        |

| 8        | Not Used             |       |        | 58       |                      | .,     | l      |

| 9        | Not Used             |       |        | 59       | sXTRQ*<br>A19        | X -    | X      |

| 10       | Not Used             |       |        | 60       | SIXTN*               | x      | X<br>X |

| 11       | Not Used             |       |        | 61       | A20                  |        | x      |

| 12       | NMI*                 | х     | x      | 62       | A21                  | -      | x      |

| 13       | PWRFAIL*             | X     | _      | 63       | A22                  | _      | x      |

| 14       | DMA3                 | -     | x      | 64       | A23                  | _      | . x    |

| 15       | A18                  | _     | x      | 65       | MREQ*                | х .    | x      |

| 16       | A16                  | -     | x      | 66       | RFSH*                | x      | X      |

| 17       | A17                  | -     | x      | 67       | MEMDSB*              | _      | x      |

| 18       | SDSB*                | -     | x      | 68       | MWRT                 | _      | -      |

| 19       | CDSB*                | -     | x      | 69       | Not Used             |        |        |

| 20       | GND                  | -     | _      | 70       | GND                  | _      | _      |

| 21       | Undefined            | x     | x      | 71       | Z80/68*              | x      | x      |

| 22       | ADSB*                | _     | x      | 72       | pRDY                 | x      |        |

| 23       | DODS B*              | -     | x      | 73       | pINT*                | x      | x      |

| 24       | phi 2                | x     | -      | 74       | pHOLD*               | x      | x      |

| 25       | pSTVAL*              | -     | x      | 75       | RESET*               | -      | -      |

| 26       | pH LDA               | х     | x      | 76       | pSYNC                | -      | x      |

| 27       | EXTAD*               | х     | x      | 77       | pWR*                 | x      | x      |

| 28       | Undefined            | х     | x      | 78       | pDB <b>i</b> N       | x      | -      |

| 29       | A5                   | -     | x      | 79       | A0                   | -      | x      |

| 30       | A4                   | -     | x      | 80       | A1                   | -      | x      |

| 31       | A3                   | -     | х      | 81       | A2                   | -      | x      |

| 32       | A15                  | -     | х      | 82       | A6                   | -      | х      |

| 33       | A12                  | -     | х      | 83       | A7                   | -      | х      |

| 34<br>35 | A9                   | -     | X      | 84       | A8                   | -      | х      |

| 36       | DO1/D9<br>DO0/D8     | X     | X      | 85<br>86 | A13                  | -      | X      |

| 37       | A10                  | X -   | X<br>X | 87       | A14<br>A11           | -      | X      |

| 38       | DO4/D12              | x     | X      | 88       | DO2/D10              | x      | X      |

| 39       | DO5/D13              | x     | X<br>X | 89       | DO3/D11              | x<br>x | X<br>X |

| 40       | DO6/D14              | x     | X      | 90       | DO7/D15              | x<br>x | X<br>X |

| 41       | DI2/D2               | x     | x      | 91       | DI4/D4               | x      | x      |

| 42       | DI3/D3               | X     | X      | 92       | DI5/D5               | X      | x      |

| 43       | DI7/D7               | X     | X      | 93       | DI6/D6               | x      | X      |

| 44       | sM1                  | -     | x      | 94       | DI1/D1               | X      | x      |

| 45       | sOUT                 | x     | x      | 95       | DIO/DO               | x      | x      |

| 46       | sINP                 | X     | x      | 96       | sINTA                | _      | x      |

| 47       | sMEMR                | -     | x      | 97       | sWO                  | _      | x      |

| 48       | sH LTA               | -     | x      | 98       | ERROR*               | -      | х      |

| 49       | CLOCK                | -     | -      | 99       | POC*                 | -      | _      |

| 50       | GND                  | -     | -      | 100      | GND                  | -      | _      |

|          |                      |       |        |          |                      |        |        |

#### Chapter 3

#### THEORY OF OPERATION

#### INTRODUCTION

The architecture of a traditional central processing unit is a trade-off between speed and flexibility. Most computers store data and instructions in the same memory space, and use a bi-directional bus to transfer information in and out of the central processing unit. This method provides a flexible, but slower than optimum, computer.

The Maximizer, on the other hand, is a computer designed to optimize memory-cycle time. Instructions and data are stored in separate memory locations. Separate buses into and out of the ALU are also provided for instructions and data. Separate memories and buses permit multiple data transfers to occur simultaneously.

Conventional microprocessor MOS logic has been replaced by pipelined bipolar logic, with a resulting speed improvement of 20 to 1 compared to the 68000.

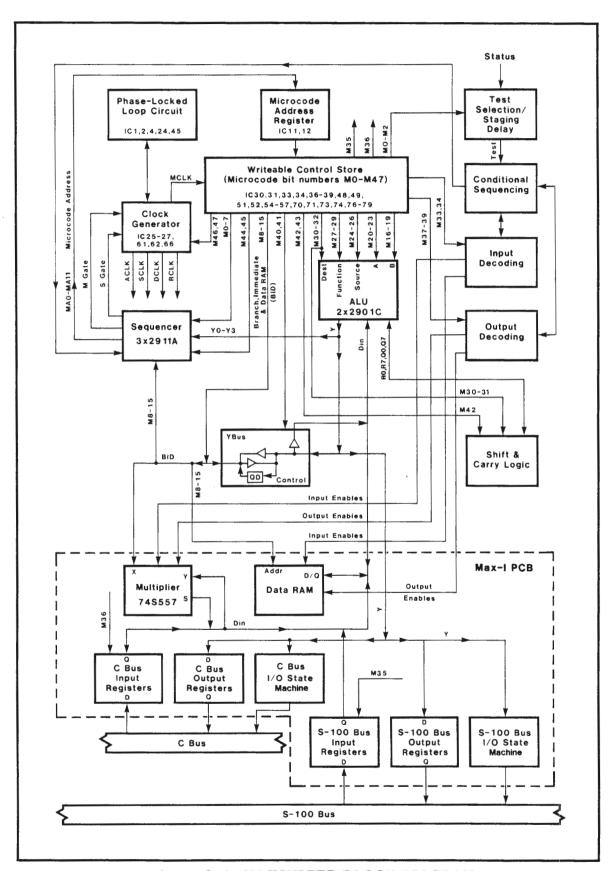

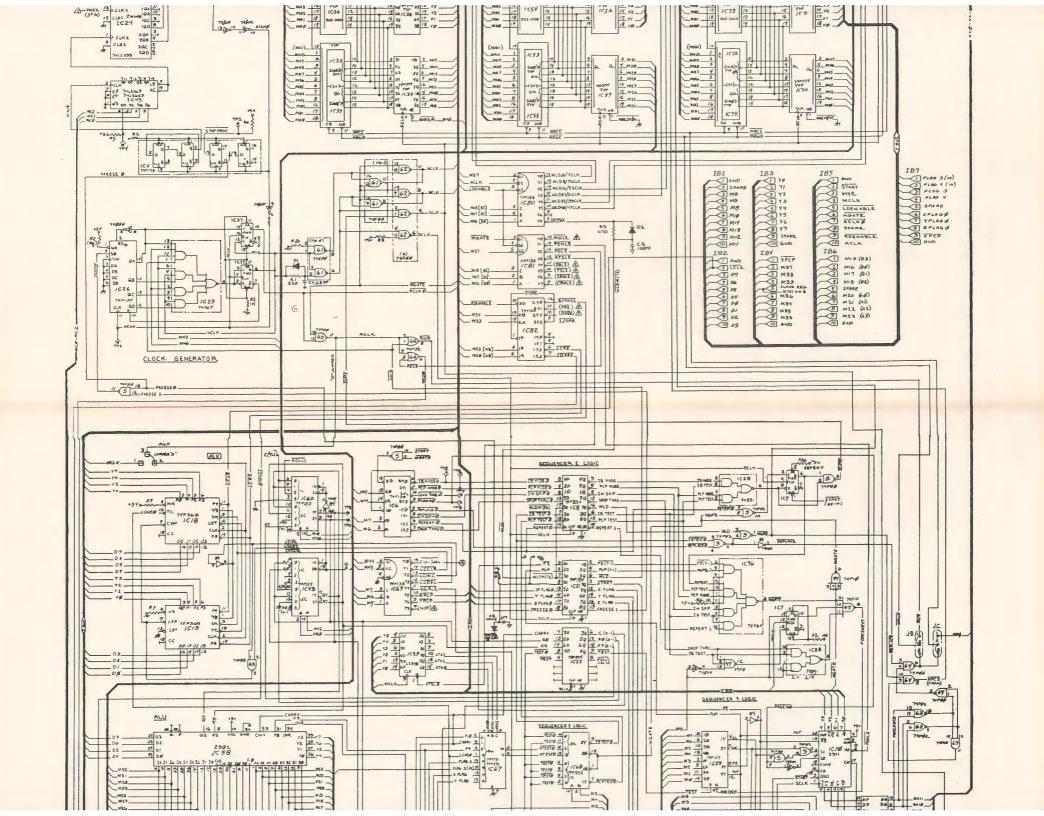

The Maximizer circuits are placed on two circuit boards, interconnected by pin and socket connectors. A basic block diagram of the Maximizer is shown in figure 3-1. The processors and support circuits occupy the first board, called the Max-C. The companion board, called the Max-I, comprises the multiplier, data RAM, and bus interface registers. The architecture of the Maximizer and the functions of each section are discussed below. Where integrated circuit (IC) numbers are given, the heading of the section indicates on which board the circuit is located.

Figure 3-1: MAXIMIZER BLOCK DIAGRAM

#### DATA PATHS

The primary flow of data is along the D bus, which feeds the data input lines of the two 2901C bit-slice ALU's (Arithmetic Logic Unit). The output of the 74S557 multiplier drives the D bus, as do the outputs of the bus-interface registers. Both input and output circuits of the data RAM are connected to the D bus.

Another important path for data is the Y bus, which is driven by the data output from the 2901C ALU's. The Y bus supplies one operand to the multiplier, and provides data to the inputs of the bus-interface registers. It is also possible for the Y bus to drive the D bus, allowing the ALU to supply data to the data RAM or the BID bus to supply immediate values to the ALU. Also, the Y bus can be linked to the BID bus, described below.

The BID bus carries branch, immediate, and data RAM address information, supplied by one of the microcode fields in the WCS (Writeable Control Store). A bi-directional bus driver links the BID and Y buses. A temporary holding register, the Y register, can be used to gate a delayed sample of the Y bus information onto the BID bus.

#### ADDRESS PATHS

The Maximizer has separate paths for program addresses and data addresses. Program addressing is done by the 2911A instruction sequencer, described below, which provides information to the microcode address register. The output of this register is then applied to the microcode control store.

Data addressing is done by the ALU or the microcode control store; the information is passed along the BID bus, as described in the preceding section.

#### MICROCODE RAM AND ROM (MAX-C)

The microcode control store issues the 48-bit microinstructions required for operation of the Maximizer. The store is divided into a writeable section (IC's 32, 34, 35, 39, 50, 51, 53, 55, 72, 74, 75, and 77), which holds 4,096 entries in RAM, and a non-writeable section (IC's 33, 36, 51, 54, 73, and 76), which holds 512 entries in ROM. Registers are used at the input (IC's 11 and 12) and output (IC's 30, 39, 48, 57, 70, and 79) to store the microcode address and data, respectively. Microcode is loaded through registers (IC's 31, 38, 49, 56, 71, and 78) that connect to the Y bus. Microcode words are assembled one byte at a time, then written to the RAM during a load cycle.

#### INSTRUCTION SEQUENCER (MAX-C)

The instruction sequencer generates the microcode addresses that are supplied to the input register of the microcode control store. The sequencer uses three 2911A chips (IC's 10, 13, and 14) to obtain twelve bits of address. These chips provide a basic set of addressing modes, including sequential, skip-on-condition, loop, branch, and call-return along with a four-level stack for subroutine return and looping addresses. All branch, repeat, and skip operations use the test logic circuits to provide conditional sequencing. The branch instruction provides two fields, each of which can select one of sixteen branch options. The drop-through instruction, when combined with a branch instruction, makes it possible to execute a three-way branch. Control and input signals to the sequencer are latched by IC's 8, 21, and 23.

#### ARITHMETIC LOGIC UNIT (MAX-C)

The ALU is built from two 2901C bit-slice microprocessors (IC's 44 and 58). Together, these chips provide a 16-word by 8-bit two-port RAM, a high-speed ALU with eight functions, and associated shifting, decoding, and multiplexing circuitry. Seventeen bits of microcode control (M16-M32) are used to specify the ALU operation, ALU source and destination data, and two-port RAM addresses.

#### SHIFT, CARRY, LOOP AND TEST LOGIC (MAX-C)

Two four-input multiplexers (IC's 60 and 43) are used to complete the shift carry/borrow path around the ALU. The nature of the shift is determined by three microcode bits, M30, M31, and M42.

The carry-in bit to the ALU is supplied by a data selector, IC 41, which is controlled by microcode bits M32 and M42. Although the carry-in bit is normally the inverted microcode bit M43, the delayed carry-out from the preceding operation can be asserted when necessary.

Loop control is assisted by an eight-bit counter, IC's 18 and 19, which signals the ALU when the microcode has performed a specified number of instructions. The counter is loaded from the Y bus data when specified by microcode bits M39 through M37; the counter may be incremented, decremented, or cleared as specified by bits M7 through M5 of the microcode. The output of the counter (count-not-equal-zero) is sampled by the test logic.

The test logic works in conjunction with the sequencer to control the flow of the microprogram. Maximizer flags are sampled by IC's 83, 85, 87, and 68, and the selected test value is then sent to the sequencing logic.

#### DATA RAM (MAX-I)

Eight 4K x 4 static RAM's are used as a 16K x 8-bit data memory on the Maximizer. The array (IC's 2 through 9) is addressed by eight bits from the BID bus and six bits from address latch IC 23. The address latch is controlled by microcode bits M39 through M37, M16 through M18, and the Y bus. Chip selects are generated by decoder IC 22 operating on the outputs of address latch IC23.

The data lines are connected to the D bus. A write line from the ALU requires a by pass (IC 17 on Max-C) to gate data from the Y bus to the D bus. Data from other input devices can be written into the data RAM without involving the ALU or the Y bus.

#### MULTIPLIER (MAX-I)

In less than 60 nanoseconds, a high-speed multiplier, IC 25, multiplies two 8-bit unsigned or two's-complement signed numbers to form a 16-bit unsigned or signed product. The chip internally develops proper rounding for either signed or unsigned numbers, as specified by control register IC 24. The arguments for multiplier and multiplicand are supplied from the BID and Y buses; the product, latched when the multiplier is activated using microcode bits M37 through M39, is sent to the D bus through two data selectors, IC's 10 and 11.

#### FLAG AND SQUIRREL REGISTERS (MAX-C)

An addressable latch, IC 42, and flip-flop, IC 22, are used to generate control flags; selection of microcode RAM or ROM is done in this manner.

Eight selected status bits are latched by the squirrel register, IC 20, allowing momentary states of the Maximizer to be captured and examined at the proper time.

#### S-100 INTERFACE AND STATE CIRCUITS (MAX-I)

The interface between the Maximizer and the S-100 bus comprises input registers, output registers, and an I/O state machine. The input registers are used to read the state of the S-100 bus, including data signals (IC's 41 and 42) and handshake signals (IC's 37 and 38). The output registers are used to drive the bus signals when the Maximizer becomes a bus master. The data lines are driven by IC's 56 and 57; the address lines by IC's 50, 54, and 55; and the status/control lines are driven by IC's 35, 51, 52, and 58.

Some of the interface lines on the bus are driven directly from the I/O state machine, which uses a counter (IC 46) to drive a RAM (IC 47). The outputs of the RAM are latched and applied to the bus by IC 48. The contents of the RAM are loaded by the ALU, as specified by microcode bits M39 through M37. The counter is enabled and disabled by microcode bits M7 through M5.

#### I/O REGISTER CONTROL (MAX-I)

The I/O register control circuits make the Maximizer seem like an output port on the S-100 bus. A decoder PROM, IC 39, detects every I/O cycle in which the Maximizer is referenced, and generates a signal, ARCLK, which may be sampled by the microprogram. This signal clocks the middle byte of the S-100 address bus into input port IC 40, and bit A1 into flip flop IC 17 as another test condition.

#### C-BUS INTERFACE AND STATE CIRCUITS (MAX-I)

The interface between the Maximizer and the C bus comprises input registers, output registers, and an I/O state machine. The input registers are used to read the state of the C bus, including data signals (IC 26) and handshake signals (IC 12). The output registers are used to drive the bus signals when the Maximizer becomes a bus master. The data lines are driven by IC 27; the address lines by IC's 13 and 14; and the status/control lines are driven by IC's 15 and 16.

Some of the interface lines on the bus are driven directly from the I/O state machine, which uses a counter (IC 30) to drive a RAM (IC 31). The outputs of the RAM are latched and applied to the bus by IC 32. The contents of the RAM are loaded by the ALU, as specified by microcode bits M39 through M37. The counter is enabled and disabled by microcode bits M16 through M19.

#### CLOCK (MAX-C)

A phase-locked loop (IC's 1, 2, 4, 24, 45, and Q1 and Q2) generates the master clock, HCLK, for the Max-C using an ECL voltage-controlled oscillator and a CMOS phase detector. The signal ranges from 32 MHz to 60 MHz in eight microcode-controlled steps, and is locked to the S-100 bus clock signal, PHI2.

Several clock signals are derived from the master clock by IC's 25 through 27, 61, and 62. A field in each instruction chooses one of four cycle periods, lasting from three to six ticks of HCLK. MCLK is sent to the ALU; SCLK to the sequencer, RCLK to the data RAM, and ACLK to certain status decoders. These clocks may be gated off to allow control of the instruction pipeline. In addition, there is a DCLK clock which runs continuously.

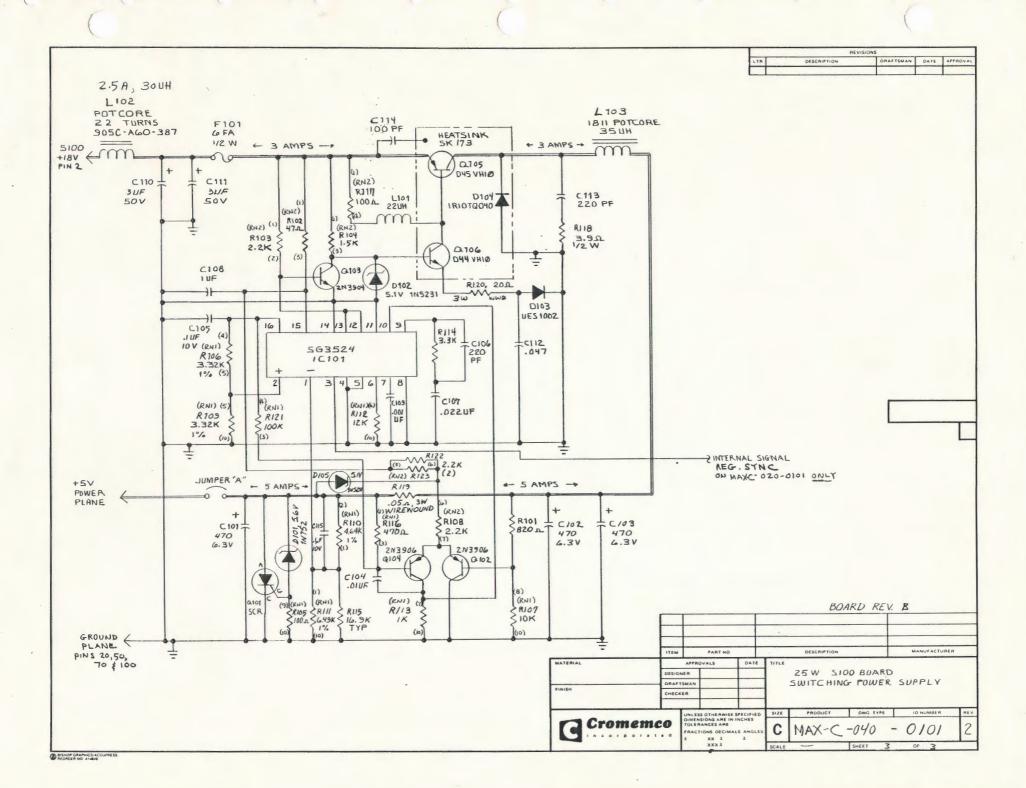

#### POWER SUPPLY

Each board of the Maximizer uses a switching power supply to provide regulated 5-volt power at a maximum of 5 amperes. This supply draws its input power from the +18 volt bus line rather than the traditional +8 volt line; this reduces the input current requirement to a level that can be safely passed through the PC board edge connector. A 100-KHz, fixed-frequency, variable-duty-cycle waveform is generated by IC 101 and used to control the charging and discharging interval of L103 through Q103, Q105, Q106, D102, and D103. The flyback pulse is caught by Shottky diode D104.

The supply includes short-circuit protection (Q104 and Q102) and a crowbar circuit for overvoltage protection (D101 and Q101).

#### MICROCODE WORD DESCRIPTION

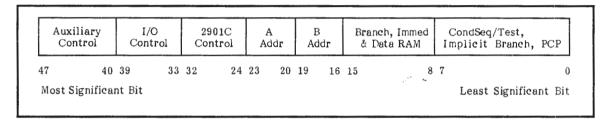

The Maximizer uses 48-bit words. These words are divided into seven basic fields. The bit positions of the fields are shown in figure 3-2. Each of the major basic fields and bit positions shown in figure 3-2 are summarized below. Additional detailed descriptions of each basic field follows the summaries.

Figure 3-2: BASIC FIELDS AND BIT POSITIONS

#### Bits 40-47: Auxiliary Control Field

These eight bits are used to make up five small auxiliary fields that deal with instruction cycle-time selection, conditional sequencing and test modes, carry-in bit, shift modes, and immediate-field-to/from-Yout manipulations.

#### Bits 33-39: I/O Control Field

These seven bits provide fields for selectively storing input information from external buses, reading from various external registers into the 2901C microprocessor, and many other functions.

#### Bits 24-32: 2901C Control Field

These nine bits are sent to I0-I8 on the 2901C as source, function, and destination controls. Their effects include selection of shift types (along with the auxiliary shift mode field).

#### Bits 20-23: A Address Field

These four bits go to both the A address field on the 2901C and to selected input devices and decodes.

#### Bits 16-19: B Address Field

These four bits go to both the B address field on the 2901C and to selected output devices and decodes.

#### Bits 8-15: Branch, Immediate, and Data RAM Field

These eight bits always load into the D and R inputs of the 2911A and are clocked into the least significant byte of the microcode address register at the end of each instruction period. The bits can also load onto the Yout bus of the 2901C (YBUS) for particular instructions or can be replaced by the Yout field (as determined by the auxiliary control field).

In addition, these bits go to the least significant byte of the data RAM address, which, along with the 4-6 data RAM bank selection bits, determines the actual address used when the I/O control field calls for data RAM read or write.

## Bits 0-7: Conditional Sequence/Test, Implicit Branch, and Processor Control Point

These eight bits are used to determine microprogram flow. They operate in three different modes, depending on the conditional sequence/test mode. In one mode, the bits select a test condition and provide for limited program redirection. In the second mode, the bits select a test condition to be used in the next instruction and provide special-purpose input and output functions. In the third mode, the bits provide two alternative control fields for the 2911A, thus allowing elaborate sequencing capabilities to be selected, depending on the outcome of a test of the previous instruction.

| Cycle Time | CondSeq/Test | Carry-In | Shift | Immediate   |

|------------|--------------|----------|-------|-------------|

| Period     | Modes        | bit*     | Modes | to/from You |

| 47 46      | 45 44        | 43       | 42    | 41 40       |

Figure 3-3: AUXILIARY CONTROL FIELD

#### Bits 46-47: Cycle Time Period

These two bits select the total time period allotted for the current cycle, using the following choices of bits 47 and 46:

| Bit # |                   |         |

|-------|-------------------|---------|

| 47 46 |                   |         |

| 0-0   | 125.0 nanoseconds | {TICK6} |

| 0-1   | 104.2 nanoseconds | {TICK5} |

| 1-0   | 83.3 nanoseconds  | {TICK4} |

| 1-1   | 62.5 nanoseconds  | {TICK3} |

#### Bits 44-45: Conditional Sequence/Test Modes

CondSeq/test modes, indexed by bits 45 and 44:

#### If = 0

The present instruction is one of the test mode instructions, in particular the test/implicit branch mode. In this mode, Bits 0-7 are divided into a test selection field (Bits 0-3) and an implicit branch field (Bits 4-7). The next instruction to be executed is determined by these two fields, and is limited to three possibilities: the next instruction in the pipeline, the instruction one later than the one in the pipeline, or the instruction in the writeable control store ("Replace") register. Refer to the section on Conditional Sequence/Test for additional information.

#### If = 1

The present instruction is also one of the test mode instructions, in this case the test/processor control point (PCP) mode. In this mode, bits 0-7 are divided into a test selection field (bits 0-3), a repeat-exit polarity field (bit 4), and a processor control point field (bits 5-7). The next instruction to be executed will be the next instruction in the pipeline (i.e., no effect on program sequencing). For further information, refer to the section on Test/Processor Control Points.

#### If = 2

The present instruction is a conditional sequencer mode instruction, which uses bits 0-7 to provide two alternate 4-bit choices of 2911A controls (depending on the value of the test flipflop, as set at the end of the last instruction) with:

```

Bits 0-3 used if TEST = 1

Bits 4-7 used if TEST = 0.

```

For further information, refer to the section on the Conditional Sequencer Field.

#### If = 3

The present instruction is also a conditional sequencer mode instruction, and is identical to the previous case, except that the microcode page (Bank) in two instruction-times is changed to that of the pageN register. The pageN register is located in the third 2911A (most significant nibble of microcode address), and is set by an I/O write. For further information, refer to the section on the Conditional Sequencer Field.

#### 3. Theory of Operation

Note that four extra states are available for each of the 2911A control fields. These indicate Flush/NOP versions of four 2911A control choices (i.e., the next instruction in the pipe is effectively NOPied, by gating all clocks except those needed for the sequencer). The sequence state fed to the 2911A during this NOP is that of continue (i.e., the instruction executed two after the NOP will be taken from a microcode address one later than the address of the instruction immediately after the NOP). See details of conditional sequencer field.

#### Bit 43: Carry-In Bit (Inverted)

This bit is the inverted carry-in bit, unless a PCP (Processor Control Point) operation forces in an alternate one (using a logical OR).

#### Bit 42: Shift Modes

This bit selects the external carry structure for ALU shifts, with a great deal of influence from bits 30 and 31 (actually, bit 42 doubles the shift options for each direction already made possible by the 2901).

#### If bit 31 = 0

Right shift/rotates are done, with the following results for particular choices of bits 30 and 42 (with R0d meaning a one-clock-delayed R0):

| Bit | #           |         |                   |       |

|-----|-------------|---------|-------------------|-------|

| 42  | 30          |         |                   |       |

| 0-0 | R7 = C[t-1] | Q7 = R0 | [Double RShift]   | {DRS} |

| 0-1 | R7 = R0     | Q7 = Q0 | [Dual RRotate]    | {DRR} |

| 1-0 | R7 = 0      | Q7 = X  | [Logical RShift]  | {LRS} |

| 1-1 | R7 = R0d    | Q7 = X  | [Multprec RShift] | {MRS} |

#### If bit 31 = 1

Left shift/rotates are done, with the following results for particular choices of bits 30 and 42 (with R7d meaning a one-clock-delayed R7):

| Bit   | #         |             |                   |       |

|-------|-----------|-------------|-------------------|-------|

| 42    | <u>30</u> |             |                   |       |

| 0-0   | R0 = Q7   | Q0 = C[t-1] | [Double LShift]   | {DLS} |

| 0 - 1 | R0 = R7   | Q0 = Q7     | [Dual LRotate]    | {DLR} |

| 1-0   | R0 = 0    | Q0 = X      | [Logical LShift]  | {LLS} |

| 1-1   | R0 = R7d  | Q0 = X      | [Multprec LShift] | {MLS} |

#### Bits 40-41: Immediate To/From Yout

These two bits determine whether bits 8-15 will replace the normal output of the 2901 (i.e., Y bus) for its various loading activities, whether the Y bus bits will replace the normal output of microcode bits 8-15 (for loading the branch address into the 2911A and for addressing the data RAM), whether a delayed version of Y bus (Y register) will replace bits 8-15, or whether bits 8-15 and the Y bus are left uncoupled. These actions are for the following choices of bits 41 and 40:

# Bit # 41 40 0-0 Bits 8-15 drive Y bus 0-1 Y bus drives lines from bits 8-15 1-0 Normal (uncoupled) 1-1 Y register drives lines from bits 8-15

| Out | put En<br>Field | able |    | s Input<br>k Field | Input<br>Fi | Enable<br>eld |

|-----|-----------------|------|----|--------------------|-------------|---------------|

| 39  | 38              | 37   | 36 | 35                 | 34          | 33            |

Figure 3-4: INPUT/OUTPUT FIELD

#### Bits 37-39: Output Clock Enables

The following are loaded from the Yout Bus at the end of the current cycle:

|     | Bit #           |                        |                          |

|-----|-----------------|------------------------|--------------------------|

|     | <u>39 38 37</u> |                        |                          |

|     | 0 - 0 - 0       | No load operation      | (no address bits)        |

|     | 0-0-1           | Load data RAM          | (M8-M15 as address bits) |

|     | 0 - 1 - 0       | Load/update multiplier | (no address bits)        |

|     | 0-1-1           | Load loop counter      | (no address bits)        |

| (1) | 1-0-0           | Load I/O bus registers | (B0-B3 as address bits)  |

|     | 1-0-1           |                        |                          |

| (2) | 1-1-0           | Load misc registers    | (B0-B3 as address bits)  |

| (3) | 1-1-1           | Load WCS registers     | (B0-B2 as addr bits)     |

### (1) Load I/O Bus Registers for both S-100 & C bus

| ####################################### |                                                                                                     | Load S-100 address bus bits 0-7 Load S-100 address bus bits 8-15 Load S-100 address bus bits 16-23 Load S-100 data bus bits 0-7 Load S-100 data bus bits 8-15 Load S-100 status lines Load S-100 control output lines Load S-100 control input lines Load S-100 DMA control lines Load S-100 utility/reserved/non-defined  Load C bus address bus bits 0-7 Load C bus data bus bits 0-7 Load C bus data bus bits 0-7 Load C bus mimic lines  Product (Bit 42) | {SADDR0 = } {SADDR1 = } {SADDR2 = } {SDATA0 = } {SDATA1 = } {SCTRLO = } {SCTRLI = } {SCTRLI = } {SDMA = } {SUTIL = } {CADDR1 = } {CADDR1 = } {CACCS = } {CMIMIC = } |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | 0<br>1                                                                                              | Read LS byte of product Read MS byte of product                                                                                                                                                                                                                                                                                                                                                                                                               | {= PRODUCT0} {= PRODUCT1}                                                                                                                                           |

|                                         |                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (= INODOCII)                                                                                                                                                        |

|                                         | (2) Load Misc                                                                                       | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                     |

| # # # # #                               | B3 B2 B1 B0<br>X-0-0-0<br>X-0-0-1<br>X-0-1-0<br>X-0-1-1<br>X-1-0-0<br>X-1-0-1<br>0-1-1-0<br>0-1-1-1 | Load misc register (8 bits) Load pageN (Bank) register (4 bits) Load flag register (4 bits, address latch) Load ATEST selection reg. (3-6 bits) Load data RAM bank register (6 bits) Load S-100 & C bus tri-state enable Reg. Load S-100 RAM-mapped I/O Control & RAM Load C bus RAM-mapped I/O Control & RAM                                                                                                                                                 | {MISC =}<br>{PAGEN =}<br>{FLAGS =}<br>{ATEST =}<br>{DBANK =}<br>{SCTRE =}<br>{SIORAM =}<br>{CIORAM =}                                                               |

| #                                       | 1-1-1-0                                                                                             | Load S-100 RAM-mapped I/O Control                                                                                                                                                                                                                                                                                                                                                                                                                             | ${SIOCTR =}$                                                                                                                                                        |

| #                                       | 1-1-1-1                                                                                             | Load C bus RAM-mapped I/O Control                                                                                                                                                                                                                                                                                                                                                                                                                             | {CIOCTR =}                                                                                                                                                          |

|                                         | (3) Load WCS                                                                                        | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                     |

|                                         | Bit #<br>B3 B2 B1 B0<br>X-0-0-0<br>X-0-0-1<br>X-0-1-0<br>X-0-1-1<br>X-1-0-0                         | Load WCS data bits 0-7 Load WCS data bits 8-15 Load WCS data bits 16-23 Load WCS data bits 24-31 Load WCS data bits 32-39                                                                                                                                                                                                                                                                                                                                     | {WCS0 =}<br>{WCS1 =}<br>{WCS2 =}<br>{WCS3 =}<br>{WCS4 =}                                                                                                            |

|                                         | X-1-0-1                                                                                             | Load WCS data bits 40-47                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\{WCS5 = \}$                                                                                                                                                       |

|                                         | X-1-1-0<br>X-1-1-1                                                                                  | Generate a load cycle (Next instruction)                                                                                                                                                                                                                                                                                                                                                                                                                      | {WCSLD =}                                                                                                                                                           |

#### Read Misc Input Registers

```

Bit #

3 2 1 0

Read S-100 data bus bits 0-7

0-0-0-0

{= SDATA0}

0-0-0-1

Read S-100 data bus bits 8-15

{= SDATA1}

Read S-100 control lines

{= SCTRL }

0-0-1-0

Read S-100 utility/reserved/non-defined

{= SUTIL }

0-0-1-1

Read C bus data bus bits 0-7

{= CDATA }

0-1-0-0

Read C bus control lines

{= CCTRL }

0-1-0-1

Read Z80/68000 attention register

{= ATTREG}

0-1-1-0

0-1-1-1

Read loop Control

{= LC

1-X-X-0

{= SQREG }

1-X-X-1

Read squirrel register

```

#### USING BIT-NUMBER AS ARGUMENT (unless otherwise stated):

Load Flag Register (Y3 = bit value and Y0-Y2 = bit-state address)

(addressable latch--only one bit at a time)

```

0

Flag1 (same processor)

1

Flag2 (same processor)

^2

Flag3 (to other processor)

3

Flag4 (to other processor)

4

ForceWCS (1 = no microcode ROM)

5

MC2

| Main clock phase-locked loop control

6

MC1

7

MC0

```

#### Load S-100 and C bus tri-state enable register {SCTRE =}

```

0

CXTS*

(C bus extra lines enable)

1

(C bus heavy-signals enable)

CHSTS*

2

(C bus data bus enable)

CDBTS*

3

(C bus address bus enable)

CABTS*

4

SXTS*

(S-100 extra lines enable)

5

(S-100 heavy-signals enable)

SHSTS*

(S-100 data bus enable)

6

SDBTS*

(S-100 address bus enable)

SABTS*

```

#### Load S-100 RAM-mapped I/O Control & RAM {SIORAM =, SIOCTR =}

```

0

Bit 0 of Control

Bit 1 of Control

1

2

Bit 2 of Control

3

Bit 3 of Control

4

pWR* bit of RAM

(S-100 pin 77)

5

sWO* bit of RAM

(S-100 pin 97)

6

pDBIN bit of RAM

(S-100 pin 78)

sMEMR bit of RAM

(S-100 pin 47)

```

```

Load C bus RAM-mapped I/O Control & RAM {CIORAM =, CIOCTR =}

0

Bit 0 of Control

1

Bit 1 of Control

Bit 2 of Control

Bit 3 of Control

3

WR* bit of RAM

(C bus pin 35)

4

5

MREQ* bit of RAM

(C bus pin 37)

RD* bit of RAM

(C bus pin 33)

6

[Not used]

Load S-100 status lines {SSTAT =}

0

[Not used]

(S-100 pin 44)

1

sM1

2

sINP

(S-100 pin 46)

3

sOUT =

(S-100 pin 45)

4

[Not used]

5

sINTA

(S-100 pin 96)

(S-100 pin 48)

6

sHLTA

(S-100 pin 58)

7

sXTRQ*

Load S-100 control output lines {SCTRLO =}

0

pSTVAL*

(S-100 pin 25)

(S-100 pin 26)

1

pH LDA

2

xRDY

(S-100 pin 3)

3

[Not used]

4

[Not used]

5

[Not used]

6

[Not used]

7

[Not used]

Load S-100 control input lines {SCTRLI =}

0

O.C.

pRDY*

(S-100 pin 72)

(S-100 pin 73)

O.C.

[68000 interrupt]

1

pINT**

[68000 interrupt]

2

NMI**

(S-100 pin 12)

O.C.

3

pHOLD**

(S-100 pin 74)

O.C.

[new RAM boards]

4

(S-100 pin 60)

o.c.

SIXTN**

(S-100 pin 14)

[undefined]

5

DMA3**

O.C.

(S-100 pin 54)

6

SLVCLR**

O.C.

ForceBAO* (DMA priority pin 1)

```

3. Theory of Operation

```

Load S-100 DMA control lines and miscellaneous lines (SDMA =)

0

ADSB**

(S-100 pin 22)

O.C.

(S-100 pin 23)

1

DODSB**

O.C.

2

SDSB**

(S-100 pin 18)

oc.

(S-100 pin 19)

3

CDSB**

O.C.

[PHANTOM* by Standard ]

4

MEMDSB**

(S-100 pin 67)

O.C.

(S-100 pin 98)

5

[68000 bus error mode]

ERROR**

O.C.

6

[Not used]

TSRE (Tri-state register enable)

Load S-100 utility/reserved/non-defined lines {SUTIL =}

(S-100 pin 21)

0

NDEF

MREQ*

(S-100 pin 65)

[NDEF by Standard ]

1

2

(S-100 pin 66)

[NDEF by Standard ]

RFSH*

3

EXTAD*

(S-100 pin 27)

[RFU by Standard]

(S-100 pin 28)

4

RFU

(S-100 pin 69)

5

RFU

6

Z80/68*

(S-100 pin 71)

[RFU by Standard ]

7

[Not used]

Load C bus Access lines {CACCS =}

0

(C bus pin 41)

BUS-AVAILABLE*

M1*

(C bus pin 36)

1

2

IORQ*

(C bus pin 38)

3

[Not used]

4

[Not used]

5

[Not used]

6

[Not used]

7

[Not used]

Load C bus mimic lines {CMIMIC =}

0

RESET*

(C bus pin 2)

(C bus pin 39)

1

RFSH*

(C bus pin 42)

2

HA LT*

3

[Not used]

4

[Not used]

5

[Not used]

[Not used]

6

[Not used]

```

#### Read S-100 control lines {= SCTRL}

```

0

pRDY

(S-100 pin 72)

0.C.

1

*TNIq

(S-100 pin 73)

O.C.

[68000 interrupt]

2

NMI*

(S-100 pin 12)

O.C.

[68000 interrupt]

3

pHOLD*

(S-100 pin 74)

O.C.

4

SIXTN*

(S-100 pin 60)

O.C. [new RAM boards]

5

(DMA priority pin 2)

PseudoBAI

6

pH LDA

(S-100 pin 26)

7

[Not used]

```

#### Read S-100 utility/reserved/non-defined lines {= SUTIL}

```

0

NDEF

(S-100 pin 21)

1

MREQ*

(S-100 pin 65)

[NDEF by Standard]

2

RFSH*

(S-100 pin 66)

[NDEF by Standard]

3

EXTAD*

(S-100 pin 27)

[RFU by Standard]

4

RFU

(S-100 pin 28)*

5

RFU

(S-100 pin 69)

(S-100 pin 71)

6

Z80/68*

[RFU by Standard]

7

PWRFAIL*

(S-100 pin 13)

```

#### Read C bus control lines {= CCTRL}

| 0 | BUS-AVAILABLE*  | (C bus pin 41) |

|---|-----------------|----------------|

| 1 | PHI*            | (C bus pin 3)  |

| 2 | WAIT*           | (C bus pin 5)  |

| 3 | CPU-DISCONNECT* | (C bus pin 40) |

| 4 | INT*            | (C bus pin 44) |

| 5 | NMI*            | (C bus pin 45) |

| 6 | [Not used]      | -              |

| 7 | [Not used]      |                |

#### Bits 35-36: External Bus Input Clock Enables

Bit 35 causes all of the S-100 input information to be stored at the end of the current cycle, while bit 36 does the same for the C bus inputs. The following operations occur for bits 36 and 35:

| Bit #        |                                              |

|--------------|----------------------------------------------|

| <u>36 35</u> |                                              |

| 0-0          | Clock in neither S-100 nor C bus information |

| 0-1          | Clock in S-100 input information             |

| 1-0          | Clock in C bus input information             |

| 1-1          | Clock in both S-100 and C bus information    |

#### Bits 33-34: Input Enables

These two bits decode into input enables for loading onto the Din bus. The following are allowed to drive the bus using these values of bits 34 and 33 (address bits An mean the 2901 An bits, Bn mean the 2901 Bn bits, and Mn mean microcode bits 8-15, whether generated by the microcode address store, by Yout, or by Yreg):

|   | Bit #        |                           |                          |

|---|--------------|---------------------------|--------------------------|

|   | <u>34 33</u> |                           |                          |

|   | 0 - 0        | Enable Yout-Din by pass   | (no address bits)        |

| * | 0-1          | Read multiplier product   | (M42 as address bit)     |

| • | 1-0          | Read data RAM             | (M8-M15 as address bits) |

| * | 1-1          | Read misc input registers | (A0-A3 as address bits)  |

|    | Destinat<br>Control | ion |    |    | Function on trol | ion |    | ALU Source<br>Control |

|----|---------------------|-----|----|----|------------------|-----|----|-----------------------|

| 32 | 31                  | 30  | 29 | 28 | 27               | 26  | 25 | 24                    |

Figure 3-5: 2901C CONTROL FIELD

Tables 3-1, 3-2, and 3-3 list ALU destination and shift control, ALU function control, and ALU source control, respectively.

Table 3-1: ALU DESTINATION AND SHIFT CONTROL

| Microcode Bits | RAM   | FCT            | Q-re  | g FCT  | Y      | RAM SH        | IFTER         | Q SHI         | FTER          |

|----------------|-------|----------------|-------|--------|--------|---------------|---------------|---------------|---------------|

| 32,31,30       | shift | load           | shift | load   | OUTPUT | RAMO          | RAM7          | Q0            | Q7            |

| 000 [0]        | Х     | none           | none  | F->Q   | F      | Х             | Х             | Х             | Х             |

| 001 [1]        | Х     | none           | . Х   | none   | F      | Х             | Х             | Х             | Х             |

| 010 [2]        | none  | F->B           | Х     | none   | A      | Х             | Х             | Х             | Х             |

| 011 [3]        | none  | F->B           | Х     | none   | F      | Х             | Х             | Х             | Х             |

| 100 [4]        | down  | F/2->B         | down  | Q/2->Q | F      | F0            | IN7<br>In(R7) | Q0            | IN7<br>In(Q7) |

| 101 [5]        | down  | F/2->B         | Х     | none   | F      | F0            | IN7<br>In(R7) | QO            | Х             |

| 110 [6]        | ир    | 2F <b>-</b> >B | . up  | 2Q->Q  | F      | INO<br>In(RO) | F7            | INO<br>In(QO) | Q7            |

| 111 [7]        | up    | 2F->B          | Х     | none   | F      | INO<br>In(RO) | F7            | Х             | Q7            |

Table 3-2: CARRY BIT/FLAG AND OVR FLAG FOR VARIOUS ALU FUNCTIONS

| Microcode Bits<br>29,28,27 | ALU Function | Carry                                                      | OVR              |

|----------------------------|--------------|------------------------------------------------------------|------------------|

| 000 [0]                    | R + S        | C8 [ALU]                                                   | C7 XOR C8        |

| 001 [1]                    | S - R        | same as for "R + S", using                                 | g R* in defns    |

| 010 [2]                    | R - S        | same as for "R + S", using                                 | g S* in defns    |

| 011 [3]                    | R OR S       | AnyZero[(R OR S)] v Cn                                     | same as Carry    |

| 100 [4]                    | R AND S      | AnyOne[(R AND S) v Cn]                                     | same as Carry    |

| 101 [5]                    | R* AND S     | AnyOne[(R* AND S) v Cn]                                    | same as Carry    |

| 110 [6]                    | R XORS       | same as for "R XNOR S", us                                 | sing R* in defns |

| 111 [7]                    | R XNOR S     | see 2901 specifications fo                                 | or logic eqns    |

|                            |              | f any bit of X == 0 or if C<br>f any bit of X == 1 or if C |                  |

Table 3-3: SOURCE OPERAND AND ALU FUNCTION MATRIX

|          |            |               |       |            | Bits 2     | 26, 27,    | and 24       | Source     |            |            |

|----------|------------|---------------|-------|------------|------------|------------|--------------|------------|------------|------------|

|          |            |               | 000   | 001<br>[1] | 010<br>[2] | 011        | 100<br>[4]   | 101<br>[5] | 110<br>[6] | 111<br>[7] |

|          |            |               | A,Q   | A,B        | 0,Q        | О,В        | 0 <b>,</b> A | D,A        | D,Q        | D,0        |

|          | 000        | Cn=0<br>R + S | A+Q   | A+B        | Q          | В          | А            | D+A        | D+Q        | D          |

|          | [0]        | Cn=1          | A+Q+1 | A+B+1      | Q+1        | B+1        | A+1          | D+A+1      | D+Q+1      | D+1        |

| Function | 001<br>[1] | Cn=0<br>S - R | Q-A-1 | B-A-1      | Q-1        | B-1        | A-1          | A-D-1      | Q-D-1      | -D-1       |

|          |            | Cn=1          | Q-A   | B-A        | Q          | В          | A            | A-D        | Q-D        | <b>-</b> D |

| nuc      | 010<br>[2] | Cn=0<br>R - S | A-Q-1 | A-B-1      | -Q-1       | -B-1       | - A - 1      | D-A-1      | D-Q-1      | D-1        |

| 1 1      | [ - ]      | Cn=1          | A – Q | A-B        | -Q         | <b>-</b> B | ' A          | D-A        | D-Q        | D          |

| 27 ALU   | 011<br>[3] | R OR S        | AvQ   | AvB        | Q          | В          | A            | Dv A       | DvQ        | D          |

| 28, and  | 100<br>[4] | R AND S       | A.Q   | A.B        | 0          | 0          | 0            | D.A        | D.Q        | 0          |

| 29,      | 101<br>[5] | R AND S       | Ā.Q   | Ā.B        | Q          | В          | A            | D. A       | D.Q        | 0          |

| Bits     | 110<br>[6] | R XOR S       | AxQ   | AxB        | Q          | В          | A            | DxA        | DxQ        | D          |

|          | 111<br>[7] | R XNOR S      | ĀxQ   | AxB        | Q          | _<br>B     | Ā            | DxA        | DxQ        | D          |

| I |   | or Contro<br>CCP) Fiel | ol Points<br>ld | Polarity<br>bit | Condi |   | Seque<br>Field |   |

|---|---|------------------------|-----------------|-----------------|-------|---|----------------|---|

|   | 7 | 6                      | 5               | 4               | 3     | 2 | 1              | 0 |

Figure 3-6: TEST AND PROCESSOR CONTROL POINTS FIELD OF CONSEQ/TEST MODES

Note: The following modes are only available when the CondSeq/Test field = 1. When this test mode is used, a Continue instruction is forced upon the 2911A, and these eight bits are available for other than 2911A control alternatives.

| Condi | tional Se<br>for Tes | - | Field | Condi | tional Se<br>for Tes |   | Field |

|-------|----------------------|---|-------|-------|----------------------|---|-------|

| 7     | 6                    | 5 | 4     | 3     | 2                    | 1 | 0     |

Figure 3-7: CONDITIONAL SEQUENCER FIELD

Note: The following modes are available when the Cond/Seq/Test field (bits 44 and 45) equals 2 or 3.

The following 16 conditional sequencing states are primarily the standard states from the 2911A, with bits 1 and 5 inverted with respect to the normal 2911A (i.e., S1, S0, FE\*, and PUP); the four previously unused states are implemented, using NOP/FLUSH Mode options for Continue (i.e., SKIP) and Jump (i.e., JMP AR, JMP STK0, and JMP D). In the following list, the references are bits 3, 2, 1, and 0 and/or 7, 6, 5, and 4 and represent (approximately) S1, S0, FE, and PUP:

| Microcode<br>Bit #                                                                                                                          | 2909/11                                                                                                                                     | Mnemonic                                                                                            | Flush?                                         | Action                                                                                                                                                                                         | Main Use                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 2 1 0<br>0-0-0-0<br>0-0-0-1<br>0-0-1-0<br>0-0-1-1<br>0-1-0-0<br>0-1-1-1<br>1-0-0-0<br>1-0-1-1<br>1-0-1-0<br>1-0-1-1<br>1-1-0-0<br>1-1-0-1 | 0 0 1 X<br>0 0 1 X<br>0 0 0 0<br>0 0 0 1<br>0 1 1 X<br>0 1 1 X<br>0 1 0 0<br>0 1 0 1<br>1 0 1 X<br>1 0 1 X<br>1 0 0 0<br>1 0 0 1<br>1 1 1 X | CONT SKIP POP PUSH JMP AR JMPF AR RET AR CALL AR JMP STKO JMPF STKO RET CALL STKO JMP addr JMP addr | No Yes No No Yes No No Yes No No Yes No No Yes | Continue Continue, Flush Cont, Pop Stack Cont, Push uPC Jump to AR JMP AR, Flush JMP AR, Pop Stk JMP AR, Push uPC Jump to STK0 LOOP, Flush LOOP, Pop Stk LOOP, Push uPC Jump to D JMP D, Flush | Continue Skip next Instr End Loop Setup Loop Branch using AR Branch,NOP End Subr Jump Subr Loop Branch Loop,NOP Ret from Subr Branch using D Branch,NOP |

| 1-1-1-0<br>1-1-1-1                                                                                                                          | $\begin{matrix}1&1&0&0\\1&1&0&1\end{matrix}$                                                                                                | RET addr<br>CALL addr                                                                               | No<br>No                                       | JMP D,Pop Stk<br>JMP D,Push uPC                                                                                                                                                                | End Subr<br>Jump Subr                                                                                                                                   |

#### Bits 0-3: Conditional Sequencer Test Field

The following tests may affect the generation of the instruction 1, 2, or 3 time-slots later. The actual effect depends on the CondSeq/Test mode and the value of Test. The following selections use these choices of bits 3, 2, 1, and 0:

| Bit #          |        | •                                   |             |

|----------------|--------|-------------------------------------|-------------|

| <u>3 2 1 0</u> |        |                                     |             |

| 0-0-0-0        | F=0    | (set if 2901C ALU result = 0)       | {ZERO}      |

| 0-0-0-1        | CARRY  | (carry out of 2901C)                | {CARRY}     |

| 0-0-1-0        | C[t-1] | (carry out delayed 1 clock)         | $\{CDEL\}$  |

| 0-0-1-1        | F7     | (MS bit from 2901C ALU result)      | $\{F7\}$    |

| 0-1-0-0        | OVR    | (arithmetic overflow)               | {OVFL}      |

| 0-1-0-1        | Cmid   | (internal bit 3-to-4 carry)         | {CMID}      |

| 0-1-1-0        | Q0     | (LS bit of Qreg, Rshifting          | {Q0}        |

|                |        | Y6, Lshifting                       | <b>{Y6}</b> |

|                |        | TEST[t-1], not shifting)            | $\{TDEL\}$  |

| 0-1-1-1        | Y 0    | (LS bit of Y bus)                   | {Y0}        |

| 1-0-0-0        | LCNE0  | (Loop counter != 0)                 | {LCNE0}     |

| 1-0-0-1        | FLAG1  | (from flag register)                | {FLAG1}     |

| 1-0-1-0        | FLAG2  | (from flag register)                | $\{FLAG2\}$ |

| 1-0-1-1        | ARCLK  | (Attention register clock)          | {ARCLK}     |

| 1-1-0-0        | INPCLK | (68000 input request clock)         | {INPCLK}    |

| 1-1-0-1        | ARFLAG | (Attention register A1 address bit) | {ARFLAG}    |

| 1-1-1-0        | INT*   | (Interrupt line)                    | {INTBAR}    |

| 1-1-1-1        | FALSE  | •                                   | {FALSE}     |

|                |        |                                     |             |

These flags are tested at the end of the current cycle, using results from the present instruction.

#### Alternate Tests for Implicit Branch Determination

Alternate Test Selections.

. . .

If the Atest mode is chosen, one of the following tests is used, in conjunction with the polarity bit, to determine whether an implicit branch is to be taken. The three selections bits are preset by loading into the Atest register prior to calling for the results of the test. The following selections are common to both the I/O and arithmetic coprocessors, and use these choices of bits 2, 1, and 0 of the Atest register:

| Bit #                     |        |                                     |

|---------------------------|--------|-------------------------------------|

| $\frac{2}{1} \frac{1}{0}$ |        |                                     |

| 0 - 0 - 0                 | F=0    | (set if 2901C ALU result = 0)       |

| 0 - 0 - 1                 | CARRY  | (carry out of 2901C)                |

| 0 - 1 - 0                 | F7     | (MS bit from 2901C ALU result)      |

| 0 - 1 - 1                 | LCne0  | (Loop counter != 0, or != 0FFh)     |

| 1-0-0                     | FLAG1  | (from flag register)                |

| 1-0-1                     | FLAG3  | (spare input)                       |

| 1-1-0                     | ARFLAG | (Attention register A1 address bit) |

| 1-1-1                     | INT*   | (Interrupt line)                    |

|                           |        |                                     |

These flags are tested at the end of the current cycle, using results from the present instruction.

| • | t Branch<br>Tield | Test<br>Type | Polarity<br>bit | Condi |   | Sequ<br>Field |   |  |

|---|-------------------|--------------|-----------------|-------|---|---------------|---|--|

| 7 | 6                 | 5            | 4               | 3     | 2 | 1             | 0 |  |

Figure 3-8: TEST & IMPLICIT BRANCH FIELD OF CONDSEQ/TEST MODES

Note: The following modes are only available when the CondSeq/Test field = 0. When this Test mode is used, a Continue instruction is forced upon the 2911A, and these eight bits are available for other than 2911A control alternatives.

#### Bits 6-7: Implicit Branch Field