# Cromemco 4 Port I/ Interface

Instruction Manual

# **Cromemco**™ 4PIO

**INSTRUCTION MANUAL**

CROMEMCO, Inc. 280 Bernardo Avenue Mountain View, CA 94040

Part no. 023-0079

July 1979

Copyright © 1979

By CROMEMCO, Inc.

ALL RIGHTS RESERVED

# TABLE OF CONTENTS

| Section | 1:  | INTRODUCTION                               | 3  |

|---------|-----|--------------------------------------------|----|

|         |     | TECHNICAL SPECIFICATIONS                   | 9  |

| Section | 2:  | OPERATING INSTRUCTIONS                     | (  |

|         | 2.1 | ASSIGNING A 4PIO BASE ADDRESS              | e  |

|         | 2.2 | 4PIO PIN-OUTS AND INTERFACE CABLING        | 9  |

|         | 2.3 | MCT-66 OPTO-ISOLATOR INTERFACING           | 13 |

|         | 2.4 | OUT 0 & OUT 1 ; OPTO PARALLEL OUT DATA     | 19 |

|         | 2.5 | OUT 2 ; RELAY PARALLEL OUT DATA            | 22 |

|         | 2.6 | OUT 3 ; OUT PORT ENABLE/DISABLE CONTROL    | 24 |

|         | 2.7 | IN Ø, IN 1 & IN 2; OPTO PARALLEL IN DATA   | 27 |

|         | 2.8 | IN 3 ; 4PIO STATUS                         | 29 |

|         | 2.9 | RESET/NON-MASKABLE INTERRUPT JUMPER OPTION | 31 |

| Section | 3:  | ASSEMBLY INSTRUCTIONS                      | 33 |

|         |     | 4PIO PARTS LIST                            | 39 |

|         |     | 4PIO PARTS LOCATION DIAGRAM                | 42 |

|         |     | 4PIO SCHEMATIC DIAGRAM                     | 44 |

# Section 1

# INTRODUCTION

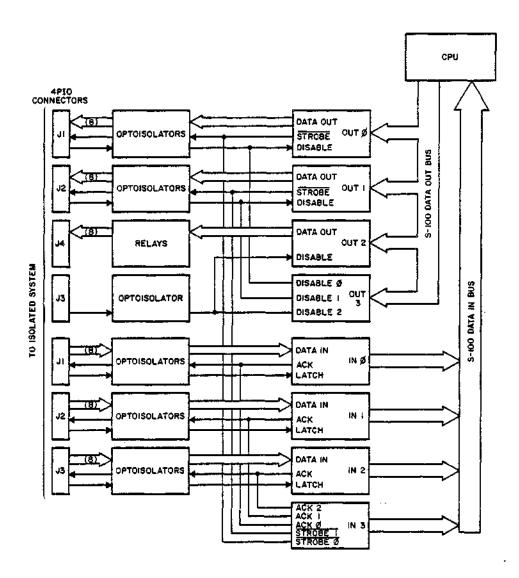

The Cromemco 4PIO is an S-100 bus compatible, four isolated I/O port printed circuit board (see Simplified Block Diagram, Figure 1). The 4PIO is designed to operate reliably in high noise industrial control environments where computer system to terminal device electrical isolation is necessary. In summary, the 4PIO features:

- \* Complete computer system to terminal device electrical isolation.

- \* Three optically isolated, 8-bit parallel input ports.

- \* One input port dedicated to 4PIO software status polling.

- \* Two optically isolated, 8-bit parallel output ports.

- \* One magnetic relay isolated, 8-bit parallel output port.

- \* One output port dedicated to software enabling/disabling the other three output ports.

- \* Optically isolated handshake lines on all three input ports; optically isolated output strobes on the two opto output ports.

- \* A 5 Kbytes/second opto-isolated parallel data transfer rate.

- \* Slide switch assigned I/O port address assignments.

- \* Optically isolated system RESET/NMI (jumper selectable).

Figure 1: 4PIO BLOCK DIAGRAM

This manual is organized in two basic sections. Section 2, Operating Instructions, supplies all the essential information needed to effectively use and tailor the 4PIO to your specific system requirements. Please read this section carefully and completely to get maximum performance from your 4PIO interface board. Section 3, Assembly Instructions, provides step-by-step assembly and initial board check-out procedures.

#### 4PIO TECHNICAL SPECIFICATIONS

Number of I/O Ports: 4

I/O Port Addresses: The six high-order port address bits

> are switch selectable; the two loworder port address bits select one-

of-four 4PIO ports

Input Port Functions:

IN Ø Inputs opto-isloated 8-bit, parallel

data

IN 1 Inputs opto-isolated 8-bit, parallel

data

IN 2 Inputs opto-isolated 8-bit, parallel

data

IN 3 Polls status of IN 0, IN 1, IN 2,

OUT Ø and OUT 1

Opto-Input Drive: 5 VDC @ 20 mA (typ)

Input Handshake Lines: LATCH INPUT and INPUT ACK

Input Data Set-up Time: 200 uSec (min) before LATCH INPUT 10 uSec (min) after LATCH INPUT Input Data Hold Time:

Output Port Functions:

OUT Ø Outputs opto-isolated 8-bit,

parallel data

OUT 1 Outputs opto-isolated 8-bit,

parallel data

OUT 2 Parallel controls eight SPDT relays

OUT 3 Enable/disable controls OUT 0, OUT

1. OUT 2

Opto-output Drive:  $\emptyset$  mA/1.2 mA (min)  $\emptyset$  V(ce) = 5 VDC

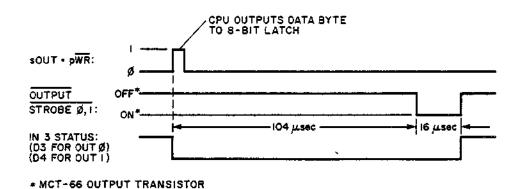

Strobes provided on OUT Ø and OUT 1; Output Strobe Timing: PW = 16 uSec; delay = 104 uSec after

data output by CPU

SPDT Relay Type:

Relay Contact Ratings: 1 Ampere @ 32 VDC or VAC

Bus Compatibility: S-100

Power Requirements: +8 VDC unregulated @ 2.3 A (max)

Ø - 55 degrees Celsius Operating Environment:

# Section 2

#### OPERATING INSTRUCTIONS

To operate the 4PIO card in your S-100 bus computer system, you must assign the card a Base Address, install interface cabling between the 4PIO and your isolated terminal devices, then write and execute software to control the parallel data transfers between the CPU and the system terminal devices.

# 2.1 ASSIGNING A 4PIO BASE ADDRESS

The system CPU transfers data between its accumulator (Reg. A) and an I/O port by placing the port address on S-100 bus address lines A0 - A7, and then asserting sOUT true and driving the Data Out lines (DO0 - DO7) if outputting data, or by asserting sINP true and reading the Data In lines (DI0 - DI7) if inputting data. The output sequence is initiated by executing an OUT [port], A instruction, and the input sequence is initiated by executing an IN A, [port] instruction, where "port" is the port address.

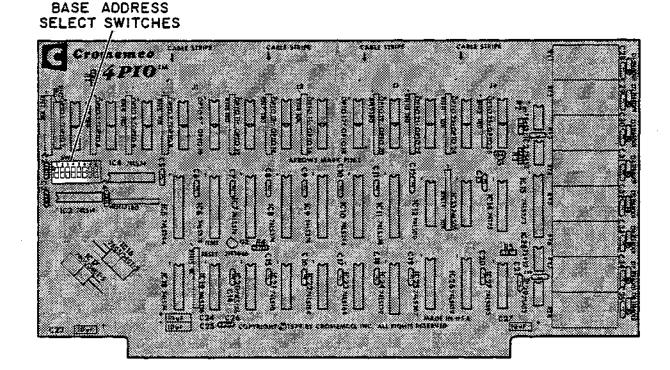

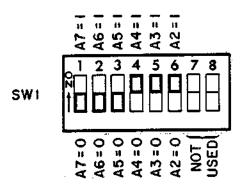

The 4PIO is conditioned to respond to four specific port addresses by positioning the six slide switches illustrated in Figure 2. The six switch settings are hardware compared to S-100 bus address lines A7, A6, A5, A4, A3 and A2, thereby defining the 4PIO Base Address. Positioning a Base Address

switch ON causes the 4PIO to respond to a logic 1 level on its corresponding address line; an OFF switch responds to logic 0 (see Figure 3).

Figure 2: 4PIO BASE ADDRESS SWITCHES

A 4PIO Board Select condition is generated when the CPU asserts either sINP or sOUT, and the Base Address switch settings match the S-100 bus address lines A7 - A2. In this case, the low-order address lines A1 and A0 then select one-of-four 4PIO ports. The two bit number formed by lines A1 and A0 define the port offset from the Base Address. Throughout the remainder of this manual, 4PIO ports will be referenced by their offset. For example, IN 0 and OUT 0 have zero offset from the Base Address, IN 1 and OUT 1 have an

offset of +1 from the Base Address, and so on. An actual 4PIO address is computed by adding the offset to the Base Address.

#### BASE ADDRESS SWITCHES

Figure 3: BASE ADDRESS LOGIC LEVELS

# EXAMPLE 1

- Setting Base Address switches A7 thru A2 OFF (logic 0) maps the 4PIO into port addresses 00H (port 0) thru 03H (port 3).

- Setting Base Address switches A7 thru A2 ON (logic 1) maps the 4PIO into port addresses  $\emptyset$ FCH (port  $\emptyset$ ) thru  $\emptyset$ FFH (port 3).

- Setting Base Address switches A7 thru A5 OFF and A4 thru A2 ON (as in Figure 3) maps the 4PIO into port addresses lCH (port  $\emptyset$ ) thru 1FH (port 3).

If two or more 4PIO cards are installed in the same S-100 bus system, the boards must be assigned distinct and non-overlapping Base Addresses, otherwise a data bus conflict will result when inputting I/O data to the CPU. Also note: Base Addresses 00H and 30H are already used by Cromemco's 4FDC Floppy Disc Controller; 40H is used by Cromemco memory boards with BANK SELECT; and 50H is used by Cromemco's PRI printer interface. Do not assign the 4PIO a conflicting Base

Address if your system contains any of these Cromemco parts.

After a Base Address has been assigned, the 4PIO may be installed in any empty S-100 bus slot. Always verify that the system power if OFF before inserting or removing the 4PIO from the S-100 bus. Interfacing cables may then be installed connecting 4PIO terminal strips J1 thru J4 to the isolated system terminal devices. After installing interface cabling, parallel data may be transferred between the CPU and your terminal devices under software control.

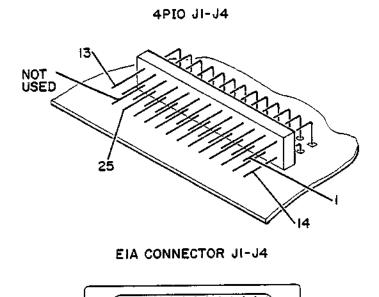

# 2.2 4PIO PIN-OUTS & INTERFACE CABLING

Cromemco provides two interface cables which are plug compatible with 4PIO connectors J1 - J4; Part No. 519-0017 (62 cm, \$15) and Part No. 519-0018 (110 cm, \$15). Each of these cable assemblies consists of a 26-pin female connector which mates with one 4PIO terminal strip connector J1 - J4, a 25-conductor flat ribbon cable of length 62 cm/110 cm, and a 25-pin female DB-25S EIA terminating connector. Your I/O terminal devices should be equipped with a mating 25-pin male DB-25P EIA connector when using either of these Cromemco supplied cables.

All J1 - J4 pin numbers referenced in this manual and in the 4PIO schematic correspond to DB-25S EIA pin numbers. Figure 4 illustrates the EIA numbering convention, and also

shows the pin-outs of the 4PIO terminal strips.

Figure 4: 4PIO PIN NUMBERING

Cromemco supplied cables must be installed by aligning the arrow head near each connector strip on the printed circuit board with the ribbon cable stripe (the colored edge of the ribbon cable. With the cable stripe properly aligned, the pin-outs of EIA connectors Jl thru J4 are shown in Table l.

Table 1

EIA CONNECTOR J1 THRU J4 PIN-OUTS

|     |                |                | •              |                     |

|-----|----------------|----------------|----------------|---------------------|

| Pin | Connector Jl   | Connector J2   | Connector J3   | Connector J4        |

| 1   | -IN Ø BIT DØ   | -IN 1 BIT DØ   | -IN 2 BIT DØ   | OUT 2 BIT DØ (NC)   |

| 2   | -IN Ø BIT D2   | -IN 1 BIT D2   | -IN 2 BIT D2   | OUT 2 BIT DØ (NO)   |

| 3   | -IN Ø BIT D4   | -IN 1 BIT D4   | -IN 2 BIT D4   | OUT 2 BIT D1 (POLE) |

| 4   | -IN Ø BIT D6   | -IN 1 BIT D6   | -IN 2 BIT D6   | OUT 2 BIT D2 (NC)   |

| 5   | +IN Ø COMMON   | +IN 1 COMMON   | +IN 2 COMMON   | OUT 2 BIT D2 (NO)   |

| 6   | +OUT Ø BIT DØ  | +OUT 1 BIT DØ  | NOT USED       | OUT 2 BIT D3 (POLE) |

| 7   | +OUT Ø BIT D2  | +OUT 1 BIT D2  | NOT USED       | OUT 2 BIT D4 (NC)   |

| 8   | +OUT Ø BIT D4  | +OUT 1 BIT D4  | NOT USED       | OUT 2 BIT D4 (NO)   |

| 9   | +OUT Ø BIT D6  | +OUT 1 BIT D6  | +RESET/NMI     | OUT 2 BIT D5 (POLE) |

| 10  | +OUT Ø DISABLE | +OUT 1 DISABLE | +OUT 2 DISABLE | OUT 2 BIT D6 (NC)   |

| 11  | +LATCH IN Ø    | +LATCH IN 1    | +LATCH IN 2    | OUT 2 BIT D6 (NO)   |

| 12  | +IN Ø ACK      | +IN 1 ACK      | +IN 2 ACK      | OUT 2 BIT D7 (POLE) |

| 13  | +OUT Ø STROBE  | +OUT 1 STROBE  | NOT USED       | NOT USED            |

| 14  | -IN Ø BIT Dl   | -IN 1 BIT D1   | -IN 2 BIT D1   | OUT 2 BIT DØ (POLE) |

| 15  | -IN Ø BIT D3   | -IN 1 BIT D3   | -IN 2 BIT D3   | OUT 2 BIT D1 (NC)   |

| 16  | -IN Ø BIT D5   | -IN 1 BIT D5   | -IN 2 BIT D5   | OUT 2 BIT D1 (NO)   |

| 17  | -IN Ø BIT D7   | -IN 1 BIT D7   | -IN 2 BIT D7   | OUT 2 BIT D2 (POLE) |

| 18  | -OUT Ø COMMON  | -OUT 1 COMMON  | NOT USED       | OUT 2 BIT D3 (NC)   |

| 19  | +OUT Ø BIT Dl  | +OUT 1 BIT D1  | NOT USED       | OUT 2 BIT D3 (NO)   |

| 20  | +OUT Ø BIT D3  | +OUT 1 BIT D3  | NOT USED       | OUT 2 BIT D4 (POLE) |

| 21  | +OUT Ø BIT D5  | +OUT 1 BIT D5  | NOT USED       | OUT 2 BIT D5 (NC)   |

| 22  | +OUT Ø BIT D7  | +OUT 1 BIT D7  | -RESET/NMI     | OUT 2 BIT D5 (NO)   |

| 23  | -OUT Ø DISABLE | -OUT 1 DISABLE | -OUT 2 DISABLE | OUT 2 BIT D6 (POLE) |

| 24  | -LATCH IN Ø    | -LATCH IN 1    | -LATCH IN 2    | OUT 2 BIT D7 (NC)   |

| 25  | -IN Ø ACK/     | -IN 1 ACK/     | -IN 2 ACK      | OUT 2 BIT D7 (NO)   |

|     | -OUT Ø STROBE  | -OUT 1 STROBE  |                |                     |

These signal lines are functionally grouped and briefly described below. More complete functional descriptions may be found in the manual sections enclosed by parentheses.

# INPUT DATA LINES (Section 2.3 & 2.7)

+IN X COMMON: Common positive terminal, IN port

Х.

-IN X BIT DZ: Negative terminal, IN port X, data

bit Z. Source current 20 mA = logic 0; source current 0 mA =

logic 1.

# INPUT HANDSHAKE (Section 2.7 & 2.8)

+/-LATCH IN X:  $\emptyset$  mA to  $2\emptyset$  mA transition latches IN

port X data.

+/-IN X ACK: Sink current 1.2 mA [min] when data latched in IN X; sink current 0 mA

after CPU reads data from IN X.

# OUTPUT DATA LINES (Section 2.3, 2.4 & 2.5)

+OUT X BIT DZ: Positive terminal, OUT port X, data

bit Z. Sink current 1.2 mA (min) = logic 0: sink current 0 mA = logic

1.

OUT 2 BIT DZ (POLE): Relay data bit Z, relay pole.

Output logic 1 to latch relay in energized state; output logic 0 to latch relay in "normal" unenergized

state.

OUT 2 BIT DZ (NO): Relay data bit Z, normally open.

(NO) NORMALLY OPEN: This contact is not connected to the

pole while the relay is off (de

energized).

OUT 2 BIT DZ (NC): Relay data bit Z, normally closed.

(NC) NORMALLY CLOSED: This contact is connected to the

pole while the relay is off (de

energized).

#### OUTPUT CONTROL/HANDSHAKE (Section 2.6 & 2.8)

+/-OUT X DISABLE: Source current 20 mA unconditionally

disables OUT port X; source current Ø mA returns OUT port X to software

enable/disable control.

+/-OUT X STROBE: 16 uSec active (sink current = 1.2

mA [min]) pulse, delayed 104 uSec

after data is output to OUT port X by CPU.

# CPU CONTROL (Section 2.9)

+/-RESET/NMI:

Source current 20 mA generates an S-100 bus pRESET (factory shipped condition) or NMI (jumper wire inserted).

# 2.3 OPTO-ISOLATOR INTERFACING

Excepting the relays, all data and control is exchanged between the 4PIO and the isolated terminal devices over MCT-66 opto-isolators. This section discusses MCT-66 electrical characteristics and interfacing techniques.

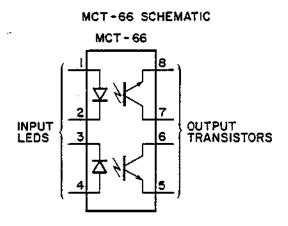

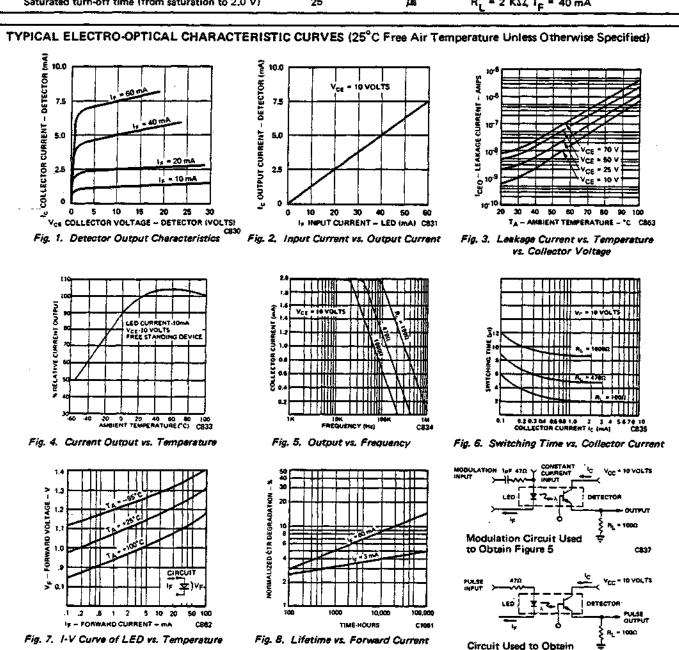

The MCT-66 is a dual optically coupled phototransistor isolator. Each phototransistor consists of an input LED and an optically coupled detector output transistor (see Figure 5 and the MST-66 data sheet, pages 40 and 41). Driving current thru the input LED causes photons to bombard the base region of the output transistor, bringing it into its conduction region. When no current flows thru the input LED, the output transistor receives no base drive, and thus it conducts no collector current.

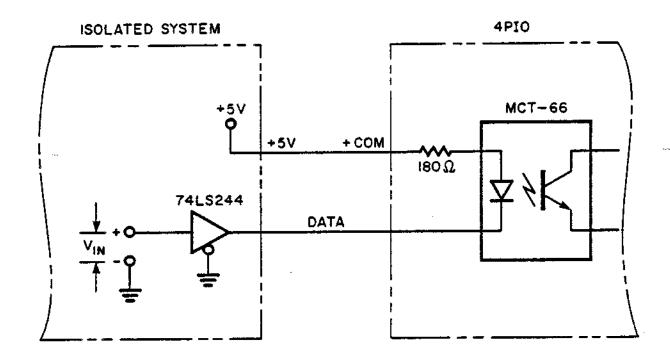

Figure 5: MCT-66 SCHEMATIC

The 4PIO drives the input LEDs when an MCT-66 is used as an output device. In such cases, the LED drive current is either 0 mA (LED OFF) or 20 mA (LED ON). When an MCT-66 is used as an input channel, the isolated system must drive the input LED with 0 mA and 20 mA (min) - 60 mA (max) levels (Cromemco recommends a 20 mA ON current for device longevity and maximum switching speed). All 4PIO opto-isolated input channels incorporate a 180 ohm series current limiting resistor which anticipates 0 volt and +5 volt drive levels. A typical IN port interface is shown in Figure 6.

Figure 6: A TYPICAL INPUT MCT-66 INTERFACE

Non-inverting 74LS244 drivers, capable of sinking 24 mA @ +.5 volts, are used in the example interface. Inputting logic Ø to the 74LS244 results in 20 mA of LED current, an ON output phototransistor, and thus logic Ø data to the CPU. A logic l data bit results in no LED current, an OFF output phototransistor, and thus logic l data to the CPU.

Since there are a total of 31 opto-input channels, the isolated system power supply must be capable of sourcing 31 x 20 mA = 620 mA of forward LED current when fully loaded.

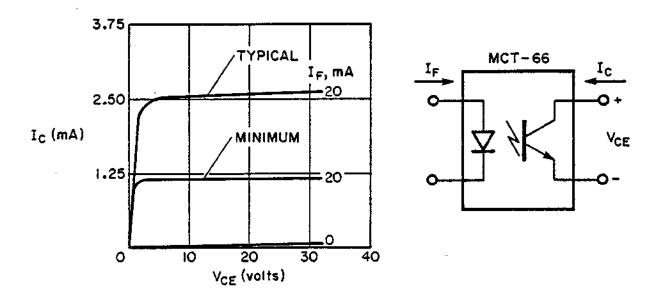

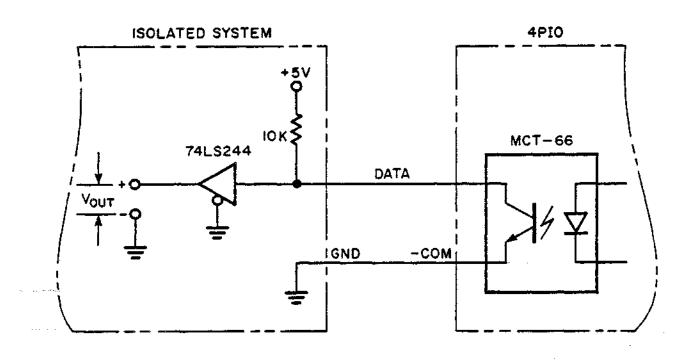

As stated above, the 4PIO supplies either 0 mA or 20 mA of LED drive current when outputting opto status and data. The MCT-66 specifications guarantee a 6%(min) input-to-output current transfer ratio which results in 0 mA and 1.2 mA (min) output collector currents. Representative output transistor characteristic curves are shown in Figure 7 for the 0 mA and 20 mA LED current conditions.

Figure 7: OPTO OUTPUT CHARACTERISTIC CURVES

These characteristic curves suggest a representative OUT port interface illustrated in Figure 8. Notice the MCT-66 output transistors drive low power Schottkey parts with I(IN-LOW) = -0.4 mA (max). Since the MCT-66 outputs can sink only 1.2 mA (min), interfacing to standard TTL (-1.6 mA) or Schottkey (+2 mA) is not recommended. The 74LS244 driver inputs are pulled up thru 10K resistors to +5 volts to speed up the output transistor turn off time. The pull up resistor value should be small to speed up the RC rise time, but large

enough to limit the MCT-66 sink current to 1.2 mA or less. In general, the pull up resistor value must satisfy:

$$R > [V(max) - V(IL)]/[1.2 mA - I(IL)]$$

where V(max) is the maximum pull up voltage, V(IL) is the maximum input low voltage (+0.8 volts for typical 'LS parts), and I(IL) is the maximum input low current (0.4 mA for typical 'LS parts).

Figure 8: A TYPICAL OUTPUT MCT-66 INTERFACE

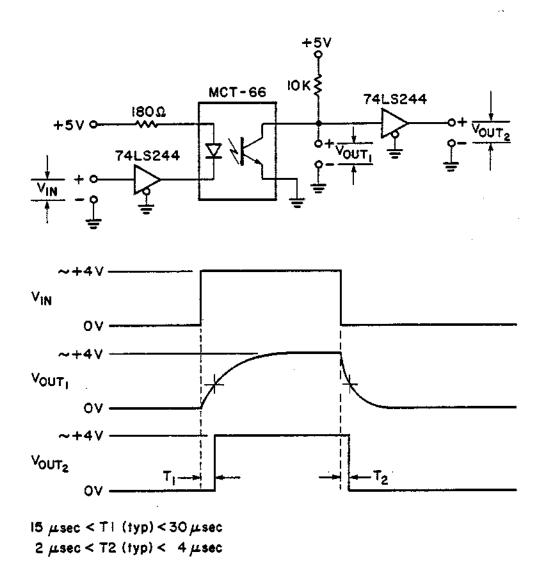

The MCT-66 switching times are heavily dependent on the detector output transistor loading. A representative MCT-66 interface and corresponding switching curves are shown in Figure 9.

Figure 9: MCT-66 SWITCHING WAVEFORMS

The exponentially rising output transistor turn-off voltage gives rise to T1, the turn-off delay, and the exponentially falling waveform results in T2, the turn-on delay. T1 typically lies between 15 uSec and 30 uSec, while T2 typically lies between 2 uSec and 4 uSec, although infrequently variations of two to three times these typical ranges may be observed.

# 2.4 OUTPUTTING OPTO-ISOLATED DATA

4PIO ports OUT Ø and OUT 1 output optically isolated, 8-bit parallel data to connectors J1 and J2 respectively. The typical sequence of events when outputting data to either of these ports follows:

- (A) The data byte is loaded into CPU register A under program control. A logic 1 data bit results in a high OUT Ø/OUT 1 output voltage (an OFF output transistor); a logic Ø data bit results in a low OUT Ø/OUT 1 output voltage (an ON output transistor).

- (B) An OUT [BASE], A instruction is then executed to output the data byte to 4PIO OUT 0; or an OUT [BASE+1], A is executed to output the data byte to 4PIO OUT 1.

- (C) Executing the OUT instruction causes the data byte to be loaded into a 4PIO 8-bit latch (IC7 for OUT 0; IC9 for OUT 1) during the last clock cycle of the OUT instruction.

- (D) The OUT instruction also triggers OUTPUT STROBE circuitry which generates a 16 uSec wide, 104 uSec delayed strobe pulse which indicates to the isolated system that an output data byte is available at the OUT 0/OUT 1 opto-isolator outputs. The OUTPUT STROBE 0/1

timing is illustrated below in Figure 10.

Figure 10: OUT 0 AND OUT 1 STROBE TIMING

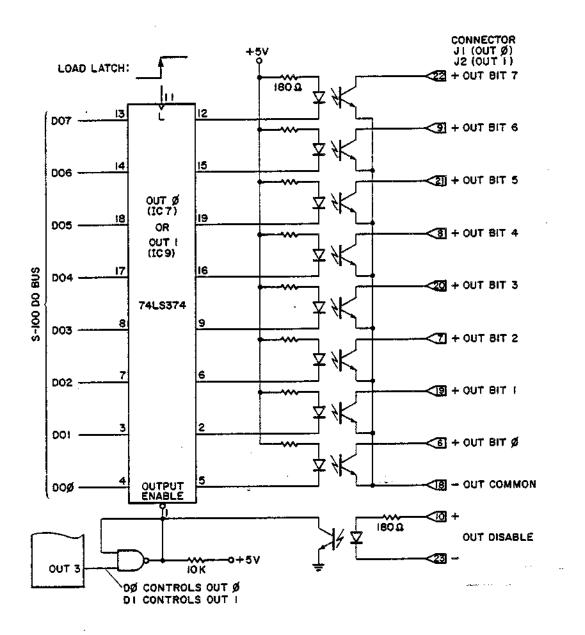

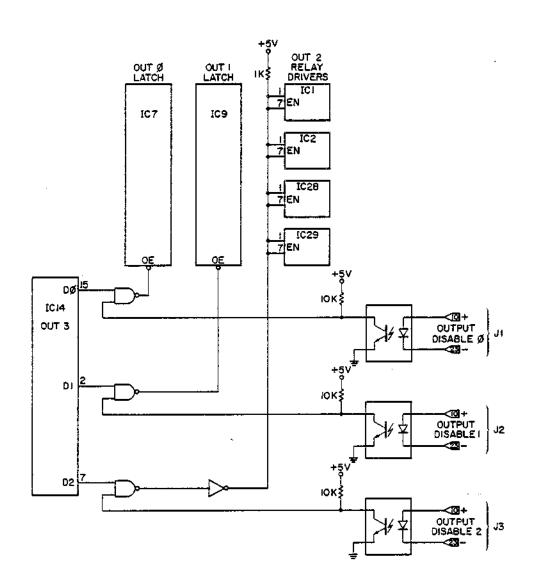

(E) The 8-bit latch (IC7 or IC9) drives the opto-isolator inputs as shown in Figure 11. The latch must be brought out of its tri-stated outputs condition by applying an active low level to the OUTPUT ENABLE line, pin 1. is accomplished by sourcing  $\emptyset$  mA of current to the OUTPUT DISABLE 0/1 input LED, and by making bit D0/D1 of 4PIO control port OUT 3 logic 1. See Section 2.6 for a full discussion of control port OUT 3. When the latch outputs are tri-stated, all OUT Ø/OUT 1 MCT-66 output When the latch outputs are made transistors are OFF. active, the data byte bits drive the opto-isolator inputs (logic Ø bits turn MCT-66 output transistors ON; logic 1 bits turn MCT-66 output transistors OFF). The MCT-66 outputs are then coupled to the isolated system as discussed in Section 2.3.

Figure 11: OUT Ø & OUT 1 CIRCUITRY

(F) The isolated system uses handshake line  $\overline{\text{OUTPUT}}$   $\overline{\text{STROBE X}}$  (X=0,1) as a signal that parallel data is valid at the opto-isolated outputs. Caution: Do not assume output data is valid until  $\overline{\text{OUTPUT STROBE X}}$  is active. Either edge of  $\overline{\text{OUTPUT STROBE X}}$ , or its active low level

may be used to unload the output data to isolated system circuitry.

(G) The CPU monitors bits D3 and D4 of 4PIO status port IN 3 to determine when port OUT Ø or OUT 1 is available to accept new output data (see Figure 10). The 4PIO handshake circuitry anticipates the isolated system will unload the output data during OUTPUT STROBE X, thus the CPU may output new data when OUTPUT STROBE X goes inactive.

# 2.5 OUT 2 ; RELAY PARALLEL DATA

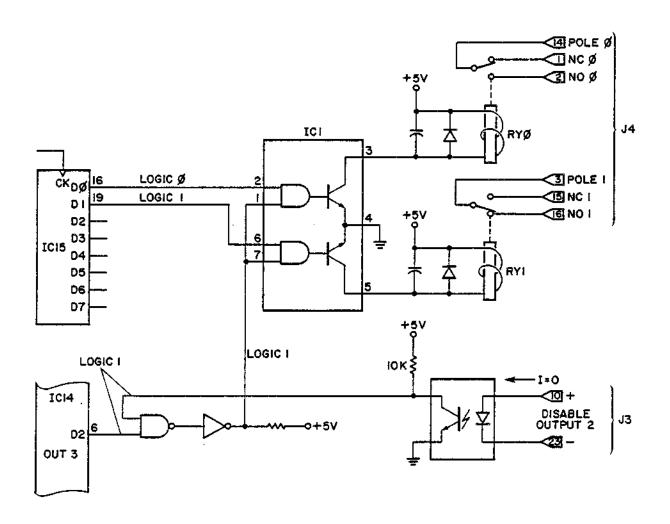

4PIO port OUT 2 outputs relay isolated, 8-bit parallel data to connector J4. The typical sequence of events to output data to the eight parallel SPDT relays follows: the relay data byte is loaded into CPU register A under program control (a logic 1 data bit energizes its relay, a logic Ø data bit leaves its relay in the "normal" un-energized position); an OUT [BASE+2], A instruction is then executed, where BASE = 4PIO BASE ADDRESS; the OUT instruction loads an 8-bit latch (IC15) with the data byte; the latch contents are then made to actively parallel control four relay drivers (IC1, IC2, IC28 & IC29) only when bit D2 of OUT 3 = logic 1 and OUTPUT DISABLE 2 is inactive (no source current).

Note that the relays may be disabled to their normal, un-energized positions by making bit D2 of OUT 3 = logic  $\emptyset$

or by making OUTPUT DISABLE 2 active (sourcing 20 mA of current to the input LED). See Section 2.6 for a further discussion of 4PIO control port OUT 3.

# EXAMPLE 2

Suppose you have a system with a 4PIO board assigned to Base Address 80H. Further assume the state of your relays is kept as a data byte in memory location RELAYS, and you now want to de-energize RYO, energize RYI and leave all other relays in their previous state. Executing the program segment below will then accomplish this task:

```

; SAMPLE PROGRAM TO DE-ENERGIZE RYØ,

; ENERGIZE RY1, AND LEAVE RY2 - RY7

; IN THEIR PREVIOUS STATES.

;4PIO BASE ADDRESS

BASE:

EQU

8ØH

(ØØ8Ø)

OFMASK: EQU

111111110B ;TURN OFF RYØ

(ØØFE)

ONMASK: EQU ØØØØØØIØB ; TURN ON RY1

(0002)

A, (RELAYS) ; GET RELAY DATA

SAMPLE: LD

8000

3AØD8Ø

;RYØ OFF

AND A, OFMASK

8003

C6FE

F602

;RY1 ON

OR

A,ONMASK

8005

(RELAYS), A ; RESTORE RELAY DATA

32ØD8Ø

LD

8007

OUT (BASE+2), A ; DATA TO 4PIO

800A

D382

HALT

8ØØC

76

; ALL OFF INITIALLY

RELAYS: DB Ø

ØØ

8ØØD

END SAMPLE

```

The essential 4PIO logic circuitry effected by this example is shown below in Figure 12. Note that D2 of OUT 3 is assumed at logic 1, and OUTPUT DISABLE 2 source current is assumed Ø mA. Only RYØ and RY1 are shown in their states after program execution.

-----

Figure 12: RELAY CONTROL EXAMPLE

# 2.6 OUT 3 ; OUTPUT PORT ENABLE/DISABLE

4PIO output ports OUT 0, OUT 1 and OUT 2 are enabled and disabled under a combination of hardware and software control. The 4PIO output states corresponding to the enabled

and disabled conditions are summarized in Table 2 below:

| TABL | Ē | 2 |

|------|---|---|

|------|---|---|

| PORT                    | CONDITION                        | 4PIO OUTPUT STATE                                                                                                    |

|-------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| out ø                   | ENABLED                          | LOGIC Ø DATA BIT -> ON MCT-66 TRANSISTOR LOGIC 1 DATA BIT -> OFF MCT-66 TRANSISTOR                                   |

| OUT 1                   | ENABLED                          | LOGIC Ø DATA BIT -> ON MCT-66 TRANSISTOR                                                                             |

| OUT 2                   | ENABLED                          | LOGIC 1 DATA BIT -> OFF MCT-66 TRANSISTOR LOGIC Ø DATA BIT -> UN-ENERGIZED RELAY LOGIC 1 DATA BIT -> ENERGIZED RELAY |

| OUT Ø<br>OUT 1<br>OUT 2 | DISABLED<br>DISABLED<br>DISABLED | UNCONDITIONAL OFF MCT-66 TRANSISTORS UNCONDITIONAL OFF MCT-66 TRANSISTORS UNCONDITIONAL UN-ENERGIZED RELAYS (NORMAL) |

4PIO port OUT 3, bits DØ, Dl and D2, provide software enable/disable control over OUT Ø, OUT l and OUT 2 respectively, while opto-isolated input lines OUTPUT DISABLE Ø, OUTPUT DISABLE l and OUTPUT DISABLE 2 provide the corresponding hardware control. These control lines are arranged so that a disable from either source disables the corresponding OUT port. Table 3 below summarizes this behavior.

TABLE 3

OUT Port Enable/Disable Control

| OUT 3 BIT DX     | OUTPUT DISABLE X<br>CURRENT    | OUT X STATE                                 |

|------------------|--------------------------------|---------------------------------------------|

| Ø<br>Ø<br>1<br>1 | 0 MA<br>20 MA<br>0 MA<br>20 MA | DISABLED<br>DISABLED<br>ENABLED<br>DISABLED |

|                  | WHERE $X = \emptyset$ , 1 OR 2 |                                             |

Note that only when OUT 3 bit DX is 1 and when OUTPUT DISABLE X current =  $\emptyset$  mA is port OUT X enabled. The corresponding 4PIO enable/disable logic circuitry is shown in Figure 13.

Figure 13: OUT ENABLE/DISABLE LOGIC CIRCUITRY

# 2.7 IN Ø, IN 1 & IN 2; OPTO PARALLEL IN DATA

4PIO ports IN 0, IN 1 and IN 2 input optically isolated, 8-bit parallel data from connectors J1, J2 and J3, respectively. The typical sequence of events when inputting parallel data from any of these three ports follows:

- (A) The isolated system input device drives eight MCT-66 input LEDs with the parallel data byte (see Section 2.3). An LED drive current of Ø mA inputs a logic 1; a 20 mA LED drive current inputs a logic Ø.

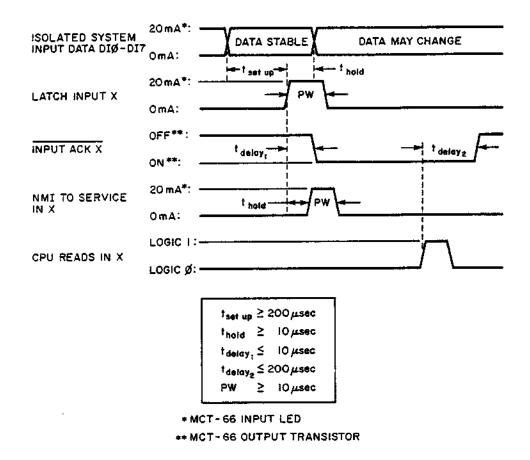

- (B) After observing a 200 uSec (min) set-up time, the parallel data is loaded into an 8-bit latch (IC6 for IN 0; IC8 for IN 1; IC11 for IN 2) by sourcing 20 mA to control line LATCH INPUT X (X=0,1,2) for at least 10 uSec. The input data must also observe a 10 uSec (min) hold time after LATCH INPUT X goes active (see Figure 14).

Figure 14: INPUT DATA TIMING REQUIREMENTS

(C) Sourcing 20 mA to line LATCH INPUT X activates handshake line INPUT ACK X. These three lines are available to the isolated system in inverted form at INPUT ACK X (an ON MCT-66 output transistor acknowledges input data), and to the system CPU in non-inverted form thru port IN 3 (a logic 1 bit acknowledges input data). These lines are reset to their inactive states when the CPU inputs the parallel data from the 8-bit latch. Thus, the isolated system monitors INPUT ACK X to determine when the CPU is ready to accept new input data (see Section 2.8 for full details on staus port IN 3).

- (D) The CPU is alerted that input data is available via the Non-Maskable Interrupt (NMI) 4PIO input lines (see Section 2.9), and/or thru polling 4PIO status port IN 3. The NMI input is optically coupled to S-100 bus line 12, and anticipates a Z80 CPU. When this line goes active low, the Z80 does a restart to a user created service routine starting at memory address 0066H (see Z80 specifications for complete details). Caution: Do not assert NMI active until the input data has satisfied its 10 usec hold time after LATCH INPUT, otherwise the NMI service routine may read unreliable input data.

- (E) The CPU inputs the data byte to register A from port X by executing an IN A, [BASE+X] instruction.

- (F) Inputting the data byte clears handshake signal INPUT ACK X, thereby alerting the isolated system that new data may be input, and also clearing the corresponding status bit of port IN 3 (see Section 2.8).

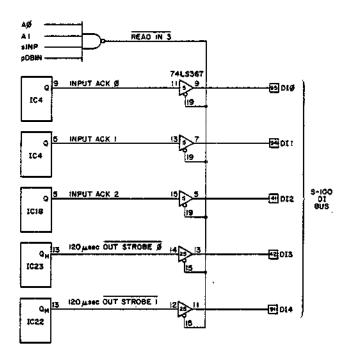

# 2.8 IN 3 ; 4PIO STATUS PORT

4PIO port IN 3 is used to software monitor the ready status of ports IN 0, IN 1, IN 2, OUT 0 and OUT 1 (notice that the relay port, OUT 2, is not monitored by IN 3). The port, implemented in 74LS367 tri-state drivers, connects 4PIO status lines INPUT ACK 0, INPUT ACK 1, INPUT ACK 2, and two shift register output lines from which OUT STROBE 0 and OUT STROBE 1 are derived, to the S-100 data in (DI) bus as shown

in Figure 15.

Figure 15: STATUS PORT IN 3

The CPU reads the port contents by executing an IN A,[BASE+3] instruction, and the bits of the read status byte are interpreted as follows:

Table 4

4PIO Status Port IN 3

| IN 3 STATUS              | BIT | 4PIO STATUS                                                   |

|--------------------------|-----|---------------------------------------------------------------|

| DØ = LOGIC<br>DØ = LOGIC |     | PORT IN Ø EMPTY<br>PORT IN Ø DATA AVAILABLE                   |

| D1 = LOGIC<br>D1 = LOGIC | _   | PORT IN 1 EMPTY PORT IN 1 DATA AVAILABLE                      |

| D2 = LOGIC<br>D2 = LOGIC |     | PORT IN 2 EMPTY<br>PORT IN 2 DATA AVAILABLE                   |

| D3 = LOGIC<br>D3 = LOGIC | ~   | PORT OUT Ø BUSY OUTPUTTING DATA PORT OUT Ø READY FOR NEW DATA |

| D4 = LOGIC<br>D4 = LOGIC | - T | PORT OUT 1 BUSY OUTPUTTING DATA PORT OUT 1 READY FOR NEW DATA |

| D5, D6, D7               |     | NOT USED                                                      |

After the system CPU reads port IN Ø, IN 1 or IN 2, its corresponding status bit is reset to indicate empty, although the previous input data remains latched and available for rereading until over-written by a new input data byte.

# 2.9 4PIO RESET, POWER-UP & NMI

The 4PIO responds to a system RESET (when S-100 bus line 75 pRESET goes active low) by: clearing any active OUT STROBE 0 or OUT STROBE 1; clearing any active INPUT ACK 0, INPUT ACK 1, INPUT ACK 2; tri-stating both OUT 0 and OUT 1 8-bit latches thereby forcing all OUT 0 and OUT 1 opto-output transistors OFF; and returning all SPDT relays to their normal, un-energized positions. Since many systems automatically generate a RESET upon power-up or after an

intermittent power failure, the post-RESET 4PIO state should then correspond to a "safe", "non-runaway" condition, especially in sensitive control applications.

After system RESET, initialization, or power failure, recovery software would typically configure 4PIO output ports OUT 0, OUT 1 and OUT 2 by outputting an appropriate control word to OUT 3 (see Section 2.6).

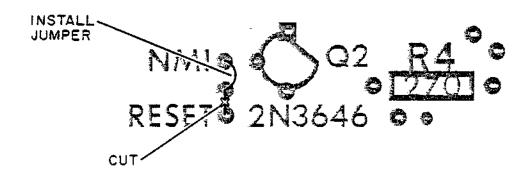

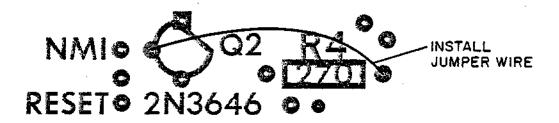

The 4PIO provides an opto-isolated input channel which may be wired to produce either a system RESET, or a Non-Maskable Interrupt (NMI). In its factory wired condition, sourcing 20 mA to input lines J3 pins 9 & 22 generates a system pRESET by forcing S-100 bus line 75 active low. Alternately, J3 pins 9 & 22 may be defined as NMI control lines by cutting a trace and installing a jumper wire as illustrated in Figure 16. With the cut trace and the jumper inserted, sourcing 20 mA to J3 pins 9 & 22 then generates a NMI by forcing S-100 bus line 12 active low.

Figure 16: RESET/NMI JUMPER OPTION

#### Section 3

# ASSEMBLY INSTRUCTIONS

If you purchased a 4PIO kit, you will find assembly to be straight forward provided you follow the instructions below. Before beginning assembly, verify you have all kit parts by referring to the 4PIO PARTS LIST near the end of this manual. Please fill out and return the included Missing Parts Form to your authorized Cromemco dealer if any parts are damaged or missing.

#### 3.1 ASSEMBLY STEPS

The following tools will be needed to assemble your 4PIO kit: small needle nosed pliers; small diagonal cutters (dikes); small phillips head screw driver; a fine tipped low-wattage soldering iron (25 W or less); a supply of fine, high quality multi-core rosin solder--DO NOT USE ACID CORE SOLDER; an ohmmeter; flurocarbon cleaning solution; and a desoldering tool (optional).

All 4PIO parts are inserted from the board component side (with the white printed legend); all soldering is done from the opposite side (the board solder side). For professional looking results, bend component leads at right angles to match the solder pad span before component insertion and soldering. After soldering, trim away excess lead length by cutting as close to the board as possible.

The printed legend on the component side shows the exact location and orientation of each component. You may also find the PARTS LOCATION DIAGRAM helpful when components overlay the printed legend. Follow the steps below in order, checking off each instruction step when completed.

( ) On the board component right side is the relay mounting area. The relays are plugged into female spring sockets which must be soldered to the 40 large feed-thru holes. Using one of the relays as an assembly jig, mount five spring sockets on the relay legs, then push the relay into place until properly seated from the component side. Solder the five sockets in place from the solder side. Unplug the relay and solder the remaining thirty-five sockets in place in a similar fashion.

( ) Solder in position four 1/4 watt resistors:

| 180 | brown-grey-brown |

|-----|------------------|

| lK  | brown-black-red  |

| 270 | red-violet-brown |

|     | Not used         |

| 1K  | brown-black-red  |

|     | 1K<br>27Ø        |

- ( ) Install eight diodes D1 D8. Align diode banded ends with the arrow symbol (anode end) printed legends, and the square pad in the PC foil.

- ( ) Install four 10 uF polarized tantalum capacitors C23 C25 and C27. Align the "+" symbol on each capacitor with the "+" legend symbol, and the square pad in the PC foil.

- ( ) Install three .001 uF ceramic disc capacitors C2 C4, and one 220 pF capacitor C26.

- ( ) Install twenty-seven Ø.1 uF capacitors Cl, C5 C22 and C28 C35.

- ( ) Install transistor Q1 (2N39Ø4). Note that transistor Q2, labeled a 2N3646 on the board legend, is <u>not</u> used. Align the transistor flat side with outline drawing. The square pad in the PC foil marks the emitter lead.

- ( ) Install a short piece of insulated jumper wire between the right unused R4 solder pad, and the unused collector solder pad of Q2 (see Figure 17).

Figure 17: R4 - Q2 JUMPER WIRE PLACEMENT

- ( ) Install resistor SIP network RN15 (lK, lØ pin). The legend arrow symbol points to SIP pin 1 which is marked on the package with either a numeral "l" or a dot, pin 1 is inserted in the square pad in the PC foil.

- ( ) Likewise, install 8 pin 180 ohm SIPs RN2, RN12, RN13; then 10 pin 10K SIPs RN1, RN5, RN8, RN11, RN14; then 10 pin 180 ohm SIPs RN3, RN4, RN6, RN7, RN9 and RN10.

- ( ) Install the eight position DIP switch package SWl. Orient the package so that the ON position in towards the top of the board.

- ( ) Install four 26-pin cable connector strips J1 J4. Position each strip so that the right angle bent legs are soldered to the p.c. board, and the straight legs point towards the top of the board.

- ( ) Mount the large heatsink assembly in the board lower left corner. Insert the phillips head screws from the solder side mating with hex nuts on the component side. Finger tighten.

- ( ) Install two 7805 +5 volt regulators on the heatsink. Pre-bend the regulator leads to match solder pad spacing, loosely install securing screw (from solder side) and hex nut to each regulator, then solder regulator leads. Make sure the regulator leads do not contact the metallic heat sink assembly. Take care that the triangular holes in the heat sink do not touch any of the pads in the PC foil. Tighten all four screws.

- ( ) Install four 8-pin IC sockets in positions ICl, IC2, IC28 and IC29.

- ( ) Install the remaining thirty-six IC sockets.

- ( ) Connect an ohmmeter, set on the RX1 or lowest range, across C23, then C24, then C25. Verify a near full-scale

reading (several hundered ohms or greater) in each case. If not, a short circuit between +8 volts and ground (C23), or between +5 volts and ground (C24, C25) is indicated. Locate and remove the short circuit, then re-test as above before proceeding.

# IMPORTANT NOTE

The most common assembly fault is bent-under IC legs. To avoid this problem, first bend the IC legs to closely match the IC socket span. Then, "rock" the IC into its socket with a gentle end-to-end pressure. Visually inspect the legs after insertion by looking beneath the device.

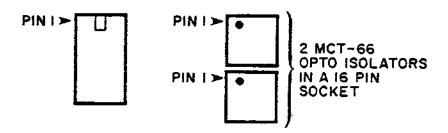

( ) Install twenty-six MCT-66 opto-isolators in positions OPTO1 - OPTO26. Note that two MCT-66s occupy one 16-pin IC socket. In each case, the legend arrow tip symbol points to IC pin 1 (see Figure 18 below).

Figure 18:IC PIN 1

( ) Install the remaining thirty-six ICs. Again, the legend arrow tip symbol points to IC pin 1.

( ) Plug eight relays RY1 - RY8 into the female spring sockets soldered in place at the first assembly step.

This completes assembly of your Cromemco 4PIO board. Clean the board solder side with the fluorocarbon solution to remove any fine metallic particles which may be imbedded in the rosin residue. Carefully inspect the solder side for unsoldered pads, or solder bridges between adjacent pads.

If further testing indicates a board failure, the first corrective measure should be the removal of all board ICs to check for bent under IC legs. If none are found, re-insert all ICs paying close attention to correct IC placement, orientation, and insertion. If problems persist, return the board to Cromemco, Inc. for servicing (see WARRANTY at the end of this manual).

# 4PIO PARTS LIST

|                     |          |               | <del></del>          |                      |

|---------------------|----------|---------------|----------------------|----------------------|

| Part Desc           | ription  | Part No.      | Part Description     | Part No.             |

| Integrated Circuits |          | Resistors     |                      |                      |

| IC1-2               | 75452    | Ø1Ø-Ø147      | R1 18Ø               | 001-0009             |

| IC3                 | 74LS14   | 010-0061      |                      |                      |

| IC4                 |          |               |                      | 001-0030             |

|                     | 74LS74   | 010-0055      | R3 1K                | 001-0018             |

|                     | 74LS244  | 010-0100      | R4                   | NOT USED             |

|                     | 74LS374  | Ø1Ø-Ø133      | R5 4.7K              | 001-0024             |

|                     | 74LS244  | 010-0100      | R6 27Ø               | 001-0011             |

| ICll                | 74LSØØ   | 010-0069      | R7 10K               | 001-0030             |

|                     | 74LS374  | 010-0133      | R8 27Ø               | 001-0011             |

| IC13                | 74LSØ5   | Ø1Ø-ØØ65      | R9 1K                | 001-0018             |

| IC14                | 74175    | Ø10-ØØØ6      |                      |                      |

| IC15                | 74LS273  | 010-0107      | Capacitors           |                      |

| IC16-17             | 78Ø5     | 012-0001      | •                    |                      |

| IC18                | 74LS74   | 010-0055      | ci .1 UF @ 10V       | 004-0030             |

|                     | 74LS136  | 010-0050      | C2-4 .001 UF DISC    | 004-0022             |

| IC21                | 74LS10   | 010-0063      | C5-22 .1 UF @ 1ØV    | 004-0030             |

|                     | 74LS164  | 010-0043      | C23-25 10 UF @ 20V   | · ·                  |

|                     | 74LS139  | 010-0043      | •                    | 004-0032             |

|                     | 74LS367  |               | C26 220 PF DISC      | 004-0013             |

|                     |          | Ø10-Ø108      | C27 10 UF @ 20V      | 004-0032             |

|                     | 74LS139  | 010-0118      | C28-35 .1 UF @ 10V   | 004-0030             |

|                     | 74LS393  | 010-0141      |                      |                      |

| IC28-29             | 75452    | 010-0147      | Resistor Networks    |                      |

| Optical Is          | olators  |               | RN1 10K, 10 PIN      | 003-0024             |

| -                   |          |               | RN2 180, 8 PIN       | 003-0002             |

| OPT01-26            | MCT-66   | 012-0010      | RN3-4 180, 10 PIN    | 003-0028             |

| *****               |          | 012 0010      | RN5 10K, 10 PIN      | ØØ3-ØØ24             |

| Transistor          | e/Diodes |               | RN6-7 180, 10 PIN    |                      |

| 114.1515001         | 3/210463 |               |                      | 003-0028             |

| D1-8                | 1N4001   | ØØ8-ØØØ9      |                      | 003-0024             |

|                     |          |               | RN9 180, 10 PIN      | ØØ3-ØØ28             |

| Q1                  | 2N39Ø4   | 003-0001      | RN10 180, 10 PIN     | 003-0028             |

| Q2                  |          | NOT USED      | RN11 10K, 10 PIN     | ØØ3-ØØ24             |

|                     |          |               | RN12-13 180, 8 PIN   | 003-0002             |

| Relays              |          |               | RN14 10K, 10 PIN     | ØØ3-ØØ24             |

|                     |          |               | RN15 1K, 10 PIN      | 003-0011             |

| RY1-8 SIGM          | IA 5VDC  | 013-0019      |                      |                      |

| IC Sockets          | <b>;</b> |               | Miscellaneous        |                      |

|                     |          |               | 8 POS. DIP SWITCH    | 013-0002             |

| 4 EA. 8             | PIN      | Ø17-ØØØØ      | 4 EA. 6-32X3/8 SCREW |                      |

| 10 EA. 14           |          | 017-0001      | 4 EA. 6-32 HEX NUT   |                      |

| 16 EA. 16           | PIN      |               | WAKEFIELD HEATSINK   |                      |

| 8 EA. 20            |          |               |                      | 020-001/<br>020-0036 |

| 0 DM. 20            |          | 2 1 - 0 2 0 4 |                      |                      |

| Documentat          | ion      |               | 4 EA. CABLE CONNECT. | 01/-0012             |

| 4========           |          |               |                      |                      |

| 4PIO INSTR          | UCTION   |               |                      |                      |

|                     |          |               |                      |                      |

023-0079

MANUAL

# Monsanto

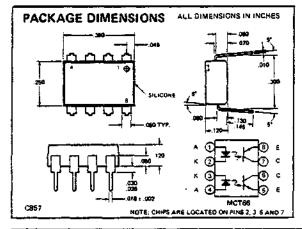

# DUAL PHOTOTRANSISTOR OPTO-ISOLATOR

**MCT66**

#### PRODUCT DESCRIPTION

The MCT66 opto-isolator has two channels for high density applications. For four channel applications, two-packages fit into a standard 16-pin DIP socket.

At the input, a GaAsLITE emitting diode generates infrared light proportional to current passing through the diode in the forward direction. At the output, a silicon phototransistor detects and amplifies the photocurrent generated in its photosensitive base region. Light coupling electrically isolates the input from the output.

#### **FEATURES**

- Two isolated channels per package

- Two packages fit into a 16 lead DIP socket

- Same basic electrical characteristics as MCT26

- 1500 volt isolation from non-repetitive surges

- 15% typical current transfer ratio

#### **APPLICATIONS**

| ■ AC Line/Digital Logic                         | Isolate high voltage transients         |

|-------------------------------------------------|-----------------------------------------|

| Digital Logic/Digital Logic                     | Eliminate spurious ground loops         |

| ■ Digital Logic/AC Triac Control                | Isolate high voltage transients         |

| ■ Twisted pair line receiver                    | Eliminate ground loop pick-up           |

| ■ Telephone/Telegraph line receiver             | Isolate high voltage transients         |

| <ul> <li>High Frequency Power Supply</li> </ul> |                                         |

| Feedback Control                                | Maintain floating ground                |

| Relay contact monitor                           | Isolate floating grounds and transients |

| ■ Power Supply Monitor                          | Isolate transients and ground systems   |

| ABSOLUTE MAXIMUM RATINGS                                                                  | Storage Temperature<br>Operating Temperatur | e −55°C to 100°C                                                                                                                                   |

|-------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                           | Lead Temperature (solde                     | ring, 10 sec.) 250°C                                                                                                                               |

| INPUT DIODE (each channel) Rated forward current, DC Peak reverse current Reverse voitage | 10 μΑ                                       | OUTPUT TRANSISTOR (each channel)  Power dissipation @ 25°C ambient                                                                                 |

| Peak forward current (1 µs pulse, 300 pps) Power dissipation at 25°C ambient              | 3 A 100 mW                                  | COUPLED Input to output breakdown voltage 1500 volts DC Total package power dissipation @ 25°C ambient 400 mW Derate linearly from 25°C 5.33 mW/°C |

| ELECTRO-OPTICAL CHARACTERISTICS (25°C Free Air Temperature Unless Otherwise Specified) |             |                  |      |       |                                                                   |  |

|----------------------------------------------------------------------------------------|-------------|------------------|------|-------|-------------------------------------------------------------------|--|

| CHARACTERISTICS                                                                        | MIN.        | TYP.             | MAX. | UNITS | TEST CONDITIONS                                                   |  |

| INPUT DIODE                                                                            |             |                  |      |       | •                                                                 |  |

| Rated forward voltage V <sub>F</sub>                                                   | _           | 1.25             | 1.50 | V     | I <sub>p</sub> = 20 mA ·                                          |  |

| Reverse voltage V <sub>B</sub>                                                         | 3.0         | 25               | -    | V     | l <sub>p</sub> = 10 μA                                            |  |

| Reverse current I R                                                                    | _           | .001             | 10   | μΑ    | √ <sub>R</sub> = 3.0 ∨                                            |  |

| Junction capacitance C <sub>J</sub>                                                    | <del></del> | 50               | _    | ρF    | V <sub>F</sub> = 0 ∨                                              |  |

| OUTPUT TRANSISTOR (I= = 0)                                                             |             |                  |      |       |                                                                   |  |

| Breakdown voltage,                                                                     |             |                  |      |       |                                                                   |  |

| collector to emitter BV <sub>CEO</sub>                                                 | 30          | 85               | -    | V     | l <sub>c</sub> = 1.0 mA                                           |  |

| Breakdown voltage,                                                                     |             |                  |      |       | •                                                                 |  |

| emitter to collector BV <sub>ECO</sub>                                                 | 6           | 13               | _    | V     | I <sub>C</sub> = 100 μA                                           |  |

| Leakage current, collector to emitter I CEO                                            | _           | 5                | 100  | пА    | V <sub>CF</sub> = 10 V                                            |  |

| Capacitance collector to emitter C <sub>CE</sub>                                       |             | 8                |      | pf    | V <sub>CE</sub> = 0 V                                             |  |

| COUPLED                                                                                |             |                  |      |       | •                                                                 |  |

| DC current transfer ratio (I <sub>C</sub> /I <sub>F</sub> ) = CTR                      | 6           | 15               | -    | %     | V <sub>CE</sub> = 10 V, I <sub>F</sub> = 10 mA                    |  |

| Isolation voltage BV <sub>(1-0)</sub>                                                  | 1500        | 2500             | _    | VDC   | Peak from non-repetitive surges                                   |  |

| Isolation resistance R <sub>(I-O)</sub>                                                | 1011        | 10 <sup>12</sup> | _    | Ω     | V <sub>I-O</sub> = 500 VDC                                        |  |

| Isolation capacitance C <sub>(1-O)</sub>                                               | _           | 0.5              | _    | pF    | f = 1 MHz                                                         |  |

| Breakdown voltage — channel-to-channel                                                 | _           | 1500             | _    | VDC   | Relative humidity = 40%                                           |  |

| Capacitance between channels                                                           |             | 0.4              | _    | pF    | f = 1 MHz                                                         |  |

| Saturation voltage —                                                                   |             |                  |      |       |                                                                   |  |

| collector to emitter V <sub>CE</sub> (SAT)                                             | -           | 0.2              | 0.4  | V     | 1 <sub>C</sub> = 2 mA, 1 <sub>F</sub> = 40 mA                     |  |

| Bandwidth B <sub>W</sub>                                                               |             | 150              | _    | kHz   | $I_{C} = 2 \text{ mA}, V_{CC} = 10 \text{ V}, R_{L} = 100 \Omega$ |  |

#### ELECTRO-OPTICAL CHARACTERISTICS (Con't) CHARACTERISTICS UNITS TEST CONDITIONS MIN. TYP. MAX. SWITCHING TIMES, OUTPUT TRANSISTOR Non-saturated rise time, fall time (Note 3) 2.4 = 2 mA, V<sub>CE</sub> = 10 V, R<sub>L</sub> = 100 Ω = 2 mA, V<sub>CE</sub> = 10 V, R<sub>L</sub> = 1 kΩ Non-saturated rise time, fall time (Note 3) 15 Saturated turn-on time (from 5.0 V to 0.8 V) = 2 KΩ, I<sub>F</sub> = 40 mA 5 = 2 K $\Omega$ , $i_{\rm p}$ = 40 mA Saturated turn-off time (from saturation to 2.0 V) 25

#### **NOTES**

- 1. The current transfer ratio (IC/IF) is the ratio of the detector collector current to the LED input current with VCE at 10 volts.

- 2. The frequency at which  $i_{\rm C}$  is 3 dB down from the 1 kHz value.

- Rise time (t<sub>r</sub>) is the time required for the collector current to increase from 10% of its final value to 90%.

Fall time (t<sub>r</sub>) is the time required for the collector current to decrease from 90% of its initial value to 10%.

Figure 6

C836

| DI IN4001 DZ IN4 | DC 35 (= )                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |

| RY1 RY2 RY3 RY4 RY5 RY6 RY7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RY8 +                                                         |

| R2 R3 IC 15 74L5273 IC 2875452 E IC 15 74L5273 IC 2875452 E IC 277                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2975452                                                       |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 774L5393                                                      |

| OPTO 23-OPTO 24  Details of the second of th |                                                               |

| RN11 10K RN14 10K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               |

| - RN10 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 74LS367 ES                                                  |

| орто 19- ОРТО 20 СП Ф IC 11 74L5374 СП8 СТ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4 74LS139 P                                                   |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2274LS164 WADE  \$ 1979 BY CROMEMCO, INC. ALL RIGHTS RESERVED |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3274LS164 \(\frac{3}{2}\)                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |

| OPIO 13 - OPIO 14 C8 - IC8 74L5374 C15 - C | 31 74LS10 H                                                   |