# 16KTP 16KTP Two Port Memory

Instruction Manual

|  | <br> |  |

|--|------|--|

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

# **Cromemco**® 16KTP TWO PORT MEMORY

Instruction Manual

# THIS BOARD IS NOT INTENDED FOR USE AS A SYSTEM MEMORY BOARD.

CROMEMCO, Inc. 280 Bernardo Avenue Mountain View, CA. 94043

Part No. 023-2003

**April 1982**

Copyright © 1982 CROMEMCO, Inc. All Rights Reserved This manual was produced on a Cromemco System Three computer utilizing a Cromemco HDD-22 Hard Disk Storage System running under the Cromemco Cromix<sup>TM</sup> Operating System. The text was edited with the Cromemco Cromix Screen Editor. The edited text was proofread using the Cromemco SpellMaster<sup>TM</sup> Program and then formatted using the Cromemco Word Processing System Formatter II. Final camera-ready copy was printed on a Cromemco 3355A printer.

# TABLE OF CONTENTS

| Chapter 1: INTRODUCTION                                         | 1              |

|-----------------------------------------------------------------|----------------|

| Chapter 2: BOARD DESCRIPTION                                    | 3              |

| Chapter 3: STANDARD SYSTEM CONFIGURATION                        | 5              |

| 3.1 Installation Of The 16KTP                                   | 7              |

| Chapter 4: SWITCH SETTINGS                                      | 11             |

| 4.1 Switch Group SW-1 4.2 Switch Group S-2 4.3 Switch Group S-3 | 11<br>13<br>14 |

| Chapter 5: CONNECTIONS BETWEEN THE 16KTP AND THE SDI            | 17             |

| PARTS LIST                                                      | 21             |

| LIMITED WARRANTY                                                | 25             |

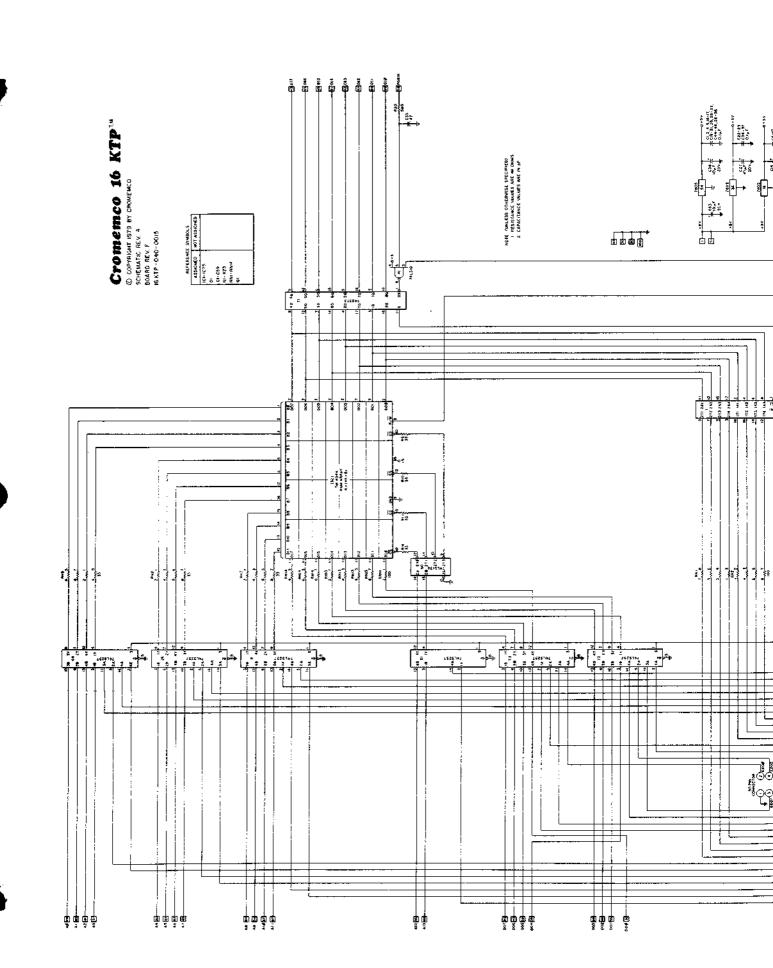

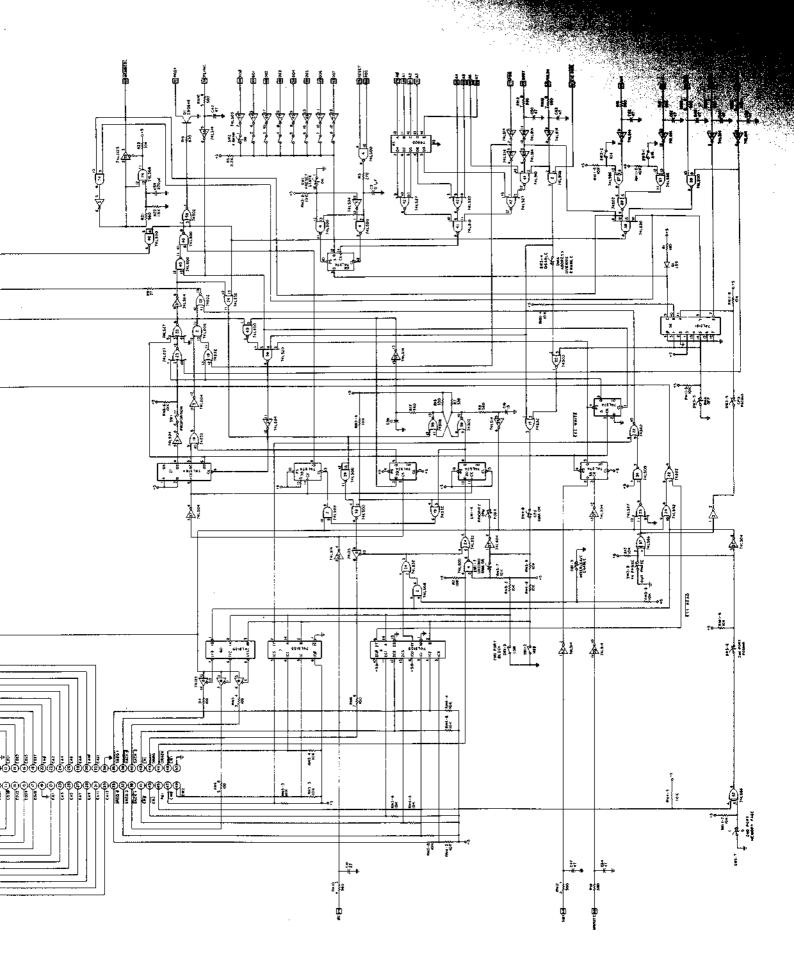

| SCHEMATIC                                                       | 27             |

# FIGURES

rome. In

| Figure 1: | THE BASIC SDI SYSTEM                                    | 1  |

|-----------|---------------------------------------------------------|----|

| Figure 2: | AN SDI SYSTEM WITH 1-6 KTP BOARDS                       | 2  |

| Figure 3: | CDOS SYSTEM WITH SIX 16KTPs                             | 6  |

| Figure 4: | STANDARD SWITCH SETTINGS FOR THE 16KTPs AND HOST MEMORY | 9  |

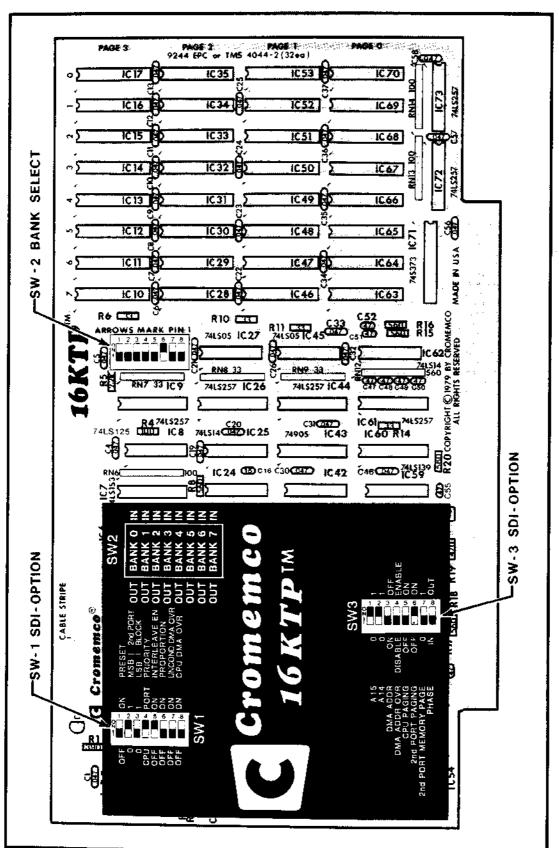

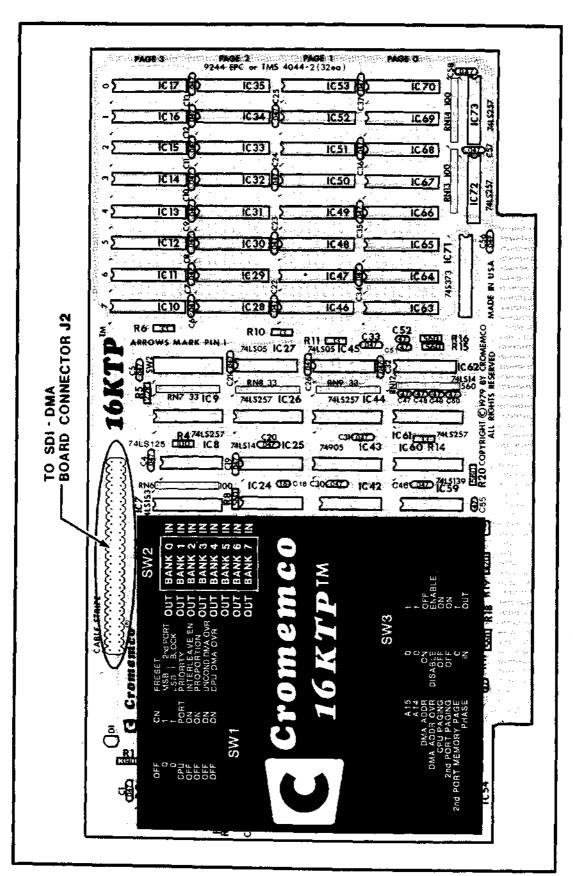

| Figure 5: | 16KTP SWITCH LOCATIONS                                  | 12 |

| Figure 6: | CABLE CONNECTIONS TO THE 16KTP                          | 20 |

|           | TABLES                                                  |    |

| Table 1:  | STANDARD SYSTEM CONFIGURATION WITH TWO 16KTPs           | 7  |

| Table 2:  | BANK SWITCH CORRESPONDENCE                              | 14 |

| Table 3:  | HOST DMA OPTIONS                                        | 15 |

# Chapter 1

# INTRODUCTION

The Cromemco 16KTP Two Port Memory board is designed to be used with Cromemco systems that use a Cromemco SDI graphics interface. Together with a high resolution RGB color monitor such as the Cromemco RGB-13, these boards turn a Cromemco microcomputer into a highly sophisticated graphics system.

One to six 16KTP RAM boards can be added to each SDI system as a means of storing picture information. Each 16KTP is capable of storing an entire 12K nybble-mapped or bit-mapped image. Alternatively, 3 16KTPs may be used to store an entire 48K image.

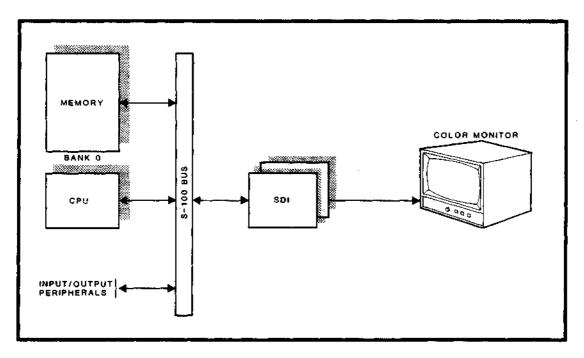

The basic SDI system configuration without the 16KTP RAM boards is shown in Figure 1.

Figure 1: THE BASIC SDI SYSTEM

rome Bo

In this configuration the SDI scans main memory for a digitized image. When reading the picture information from main memory, the SDI must disable the ZPU up to 92% of the time. This greatly reduces execution efficiency because the ZPU must share the S-100 address and data bus lines with the SDI.

This situation is remedied with the 16KTP. The 16KTP has two sets of address and data lines (two ports) which give it the ability to process the SDI's memory refresh requests while the ZPU simultaneously and independently executes a user program. The second port of the 16KTP is a 50 pin connector on the top edge of the card. This allows a direct connection of the SDI with the 16KTP which bypasses the S-100 bus. The ZPU accesses the 16KTP through the S-100 bus (the main port) as though the SDI were not present.

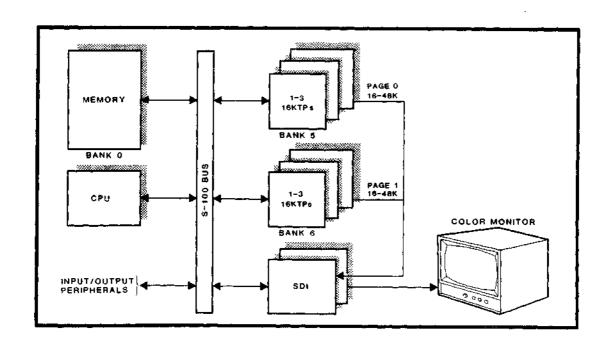

One to six 16KTP boards can be employed in a single SDI system. The system configuration with six 16KTPs is shown in Figure 2.

Figure 2: AN SDI SYSTEM WITH 1-16 KTP BOARDS

# Chapter 2

# BOARD DESCRIPTION

The 16KTP is a two port static memory board. It incorporates 200ns (4K x 1) static RAM chips in its 16K block of user memory. Also on board is all the logic necessary to service read and write requests from the host (S-100 bus) and read and write requests from the SDI (second port).

The 16KTP contains an external connector on the edge opposite the S-100 plug. This connector, a 50 pin connector, allows a top edge interface to the SDI. By connecting the 16KTP to the SDI-D with 50 conductor ribbon cable, data and timing information can be communicated between the two boards. The address requests to the 16KTP as well as the picture data to the SDI are passed through the 50 conductor cable.

There are 3 switch groups on board the 16KTP. SW-2 indicates to the host which banks the 16KTP appears in. Switches SW-1 and SW-3 establish information regarding the relationship between the 16KTP and the SDI as well as address information and other features. These switches, for example, determine which page of image memory the 16KTP occupies with respect to the SDI and what 16K block of memory the board is addressed as. The SDI can support two 48K pages, page 0 and page 1. The selection of frame buffer page is independent of bank selection.

Cromemco 16KTP Two Port Memory

ome St womemco l6KTP Two Port Memory

i Standard System Configuration

# Chapter 3

# STANDARD SYSTEM CONFIGURATION

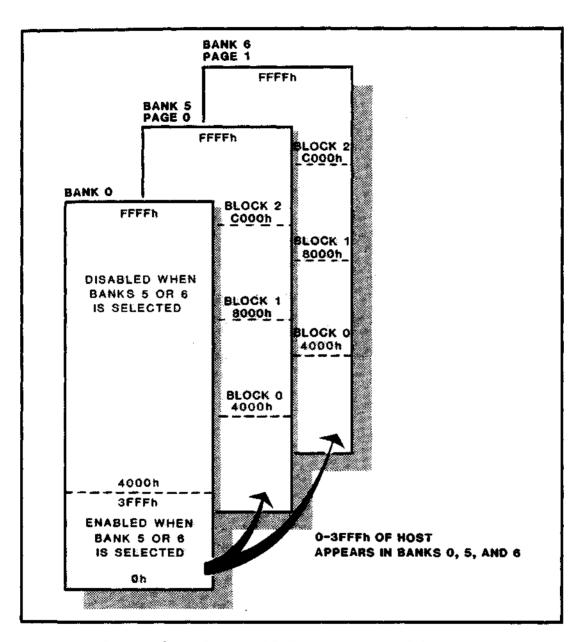

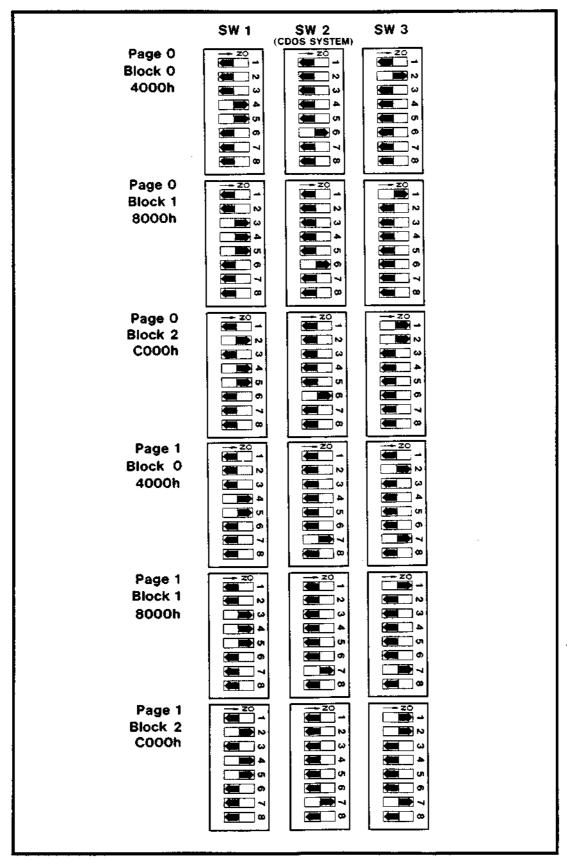

For most CDOS applications (and in particular when using Cromemco CDOS software) a standard system configuration with regard to bank placement and switch settings should be observed. In this configuration, the main user bank (hereafter referred to as host memory) appears in bank 0. If one page of memory (consisting of 3 16KTPs) is used, it should appear in bank 5 and from the point of view of the SDI appear as page 0. If a second page of memory is used, these boards should be set to bank 6 and appear to the SDI as page 1. Both 48K pages (if two are present) should be addressed from 4000h to FFFFh, i.e., the upper 48K of memory. This means that when 3 16KTPs are used to comprise a single page, their base addresses should be 4000h, 8000h and C000h respectively. Finally, because of the 16KTPs special memory disable feature, the host memory, bank 0, should be set to also appear in bank 5, if SDI page 0 is present, or banks 5 and 6, if both SDI pages (0 and 1) are present. This apparent memory overlap is allowed because the 16KTP disables all memory which lies in its bank and memory area while the 16KTP is being written into or read from. This system configuration is summarized in Figure 3 and Table 1. The switch settings for this configuration are shown in Figure 4.

For the Cromix Operating System, the only switch settings which change are those that set the Host address. Instead of the cards appearing in banks 5 and 6 at addresses 4000 (Block 0), 8000 (Block 1) and C000 (Block 2); for Cromix they must be at addresses 0000 (Block 0), 4000 (Block 1) and 8000 (Block 2). The switch changes affect SW-3, 1 and 2 only.

rome

St

Figure 3: CDOS SYSTEM WITH SIX 16KTPs

Table 1

STANDARD SYSTEM CONFIGURATION WITH TWO 16KTPs

|                                                                                           | Size                                          | Appears<br>in banks:            | Addressed<br>as:                                                                                  | Appears to SDI as:                                                                        |

|-------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Host memory<br>1st 16KTP<br>2nd 16KTP<br>3rd 16KTP<br>4th 16KTP<br>5th 16KTP<br>6th 16KTP | 64K<br>16K<br>16K<br>16K<br>16K<br>16K<br>16K | 0,5,6<br>5,5<br>5,5<br>6,6<br>6 | 0-FFFFh<br>4000h-7FFFh<br>8000h-BFFFh<br>C000h-FFFFh<br>4000h-7FFFh<br>8000h-BFFFh<br>C000h-FFFFh | page 0 block 0 page 0 block 1 page 0 block 2 page 1 block 0 page 1 block 1 page 1 block 2 |

From the point of view of the graphics programmer, the host memory from 4000h to FFFFh will appear only in bank 0. Thus, when it is necessary to switch to bank 5 or bank 6 in order to manipulate the image memory, that portion of the program which handles the bank select and subsequent image manipulation must be located in host memory below 4000h. This is because host addresses 0-3FFFh appear in banks 5 and 6; when these banks are selected any program segment which appears in this address range will continue to operate. A typical organization of software for the SDI/16KTP system is shown in Figure 3.

# INSTALLATION OF THE 16KTP

1.1

- Verify that the SDI board set is properly installed in the system (refer to the SDI manual for switch settings and installation instructions).

- Copy the switch settings of Figure 4 onto all of the 16KTPs and also onto the bank select switch of the host memory card(s).

- 3. Connect 1 plug of a 50 pin ribbon cable to connector J-1 of the 16KTP, leaving the other plugs free. If more than one 16KTP is present, use a single cable/multi plug ribbon connector and plug this cable into each 16KTP leaving at least one plug free.

- 4. Insert all 16KTPs into the system in the vacant slots adjacent the SDI-D board, with the free cable ends toward the SDI-D.

- 5. Plug the 50 conductor cable free end into connector J-2 of the SDI-D.

The 16KTP boards are now installed in the system.

Figure 4: STANDARD SWITCH SETTINGS FOR THE 16KTPs

AND HOST MEMORY

Cromemco 16KTP Two Port Memory

nco 16KT itch Set

This deta sta emp loc 5.

SWI

Bit

Bit

В

# Chapter 4

## SWITCH SETTINGS

This section describes the use of each 16KTP switch in detail. Reference is made to the previous section if a standard Cromemco graphics system configuration is employed. An outline of the 16KTP board showing the location of the three switch groups is shown in Figure 5.

# SWITCH GROUP SW-1

# Bit 1 (preset)

1

If this switch is on, the 16KTP will be active after reset. If off, the board will be off (unselected). Off is the standard position.

# Bits 2 and 3 (second port block)

These bits determine which of the 4 16K blocks the 16KTP will reside in from the second port point of view.

| Bit 2 (MSB)      | Bit 3<br>(LSB)   | Block                       |

|------------------|------------------|-----------------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1<br>2<br>3 (not used) |

| A                | - h Noppell      |                             |

# 0 = switch "OFF' 1 = switch "ON"

# Bit 4 (memory access priority)

This bit, in conjunction with SWI-8, determines the circumstances under which the ORRQ (override request) signal of the second port will be asserted by the 16KTP. If the second port controlling device chooses to ignore the ORRQ signal, then the Host cannot gain access to the 16KTP and must wait (PRDY will become not ready, or low).

Pigure 5: 16KTP SWITCH LOCATIONS

, 2

omemco 16KTP Two Port Memory

Switch Settings

| SW1 | BIT |                         |

|-----|-----|-------------------------|

| 8   | 4   | ORRQ Asserted On        |

| OFF | OFF | All Host accesses.      |

| OFF | ON  | Nothing. ORRQ disabled. |

| ON  | OFF | All Host accesses.      |

| ON  | ON  | Host DMA accesses only. |

# Bit 5 (interleave enable)

When on, this bit allows the interleaving of picture data from the second port. That is, when used with the SDI, data may be read from this board, or another board which is identically addressed but occupying a different page. Usually in the on position, this bit enables the SDI to perform its windowing function.

# Bit 6 (proportion)

For 8080 systems. Leave "OFF".

# Bit 7 (unconditional DMA override)

If SW-1 bit 8 (see below) is "ON", then this switch when "ON" disables the second port during Host DMA into or out of the 16KTP. Applies to Host DMA accesses only.

# Bit 8 (CPU or DMA override)

The bit (switch) when "ON", enables the functioning of SW1-4 and SW1-7. If "OFF", SW1-7 is effectively "OFF".

# .2 SWITCH GROUP S-2

This switch group determines the bank(s) in which the 16KTP resides. Normally the 16KTP designated page 0 will be in bank 5, and the 16KTP designated page 1 will be in bank 6. The bank-switch correspondence is shown in Table 2.

Table 2: BANK-SWITCH CORRESPONDENCE

| Switch Number | Bank |

|---------------|------|

| 1             | 0    |

| 2             | 1 1  |

| 3             | 2    |

| 4             | ] 3  |

| 5             | 4    |

| <u>6</u>      | 5    |

| 7             | 6    |

| 8             | , 7  |

# 4.3 SWITCH GROUP S-3

Bits 1 and 2 (AlS and Al4)

These bits determine the base address of the 16KTP as viewed from the host. The options are:

| Bit 1 (A15) | Bit 2<br>(A14) | Base Addr.    |

|-------------|----------------|---------------|

| 0           | 0              | 0000h         |

| 0           | 1              | 4000h         |

| 1           | 0              | <b>8000</b> h |

| 1           | 1              | C000h         |

|             |                |               |

0 = switch "OFF"

1 = switch "ON"

# Bits 3 and 4 (host DMA controls)

The standard operation of the 16KTP is with both of these bits in the off (0) position. In this case the 16KTP responds to a host DMA request if it is in the selected bank, otherwise it will not respond.

Two alternative situations are:

- 1. 16KTP ignores all host DMA requests regardless of bank (bit 3 = off, bit 4 = on).

- 2. 16KTP responds to all host DMA requests regardless of bank (bit 3 = on, bit 4 = on).

# comemco 16KTP Two Port Memory Switch Settings

| SW1<br>8   | BIT<br>4          | ORRQ Asserted On                              |

|------------|-------------------|-----------------------------------------------|

| OFF<br>OFF | OFF<br>ON         | All Host accesses.<br>Nothing. ORRQ disabled. |

| ON<br>ON   | O <b>FF</b><br>ON | All Host accesses. Host DMA accesses only.    |

# Bit 5 (interleave enable)

When on, this bit allows the interleaving of picture data from the second port. That is, when used with the SDI, data may be read from this board, or another board which is identically addressed but occupying a different page. Usually in the on position, this bit enables the SDI to perform its windowing function.

# Bit 6 (proportion)

For 8080 systems. Leave "OFF".

# Bit 7 (unconditional DMA override)

If SW-l bit 8 (see below) is "ON", then this switch when "ON" disables the second port during Host DMA into or out of the 16KTP. Applies to Host DMA accesses only.

# Bit & (CPU or DMA override)

The bit (switch) when "ON", enables the functioning of SWl-4 and SWl-7. If "OFF", SWl-7 is effectively "OFF".

# SWITCH GROUP S-2

This switch group determines the bank(s) in which the 16KTP resides. Normally the 16KTP designated page 0 will be in bank 5, and the 16KTP designated page 1 will be in bank 6. The bank-switch correspondence is shown in Table 2.

Table 2: BANK-SWITCH CORRESPONDENCE

| Switch Number | Bank |

|---------------|------|

| 1             | 0    |

| 2             | 1 1  |

| 3 4           | 2    |

| 5             | 4    |

| 6             | 5    |

| 7             | 6    |

| 8             | /    |

# 4.3 SWITCH GROUP S-3

Bits 1 and 2 (Al5 and Al4)

These bits determine the base address of the 16KTP as viewed from the host. The options are:

| Bit 1<br>(A15) | Bit 2<br>(A14) | Base Addr     |

|----------------|----------------|---------------|

| 0              | 0              | 0000h         |

| 0              | 1              | <b>4000</b> h |

| 1              | 0              | <b>8000</b> h |

| 1              | 1              | C000h         |

|                |                |               |

0 = switch "OFF"

1 = switch "ON"

# Bits 3 and 4 (host DMA controls)

The standard operation of the 16KTP is with both of these bits in the off (0) position. In this case the 16KTP responds to a host DMA request if it is in the selected bank, otherwise it will not respond.

Two alternative situations are:

- 1. 16KTP ignores all host DMA requests regardless

of bank (bit 3 = off, bit 4 = on).

- 2. 16KTP responds to all host DMA requests regardless of bank (bit 3 = on, bit 4 = on).

These possibilities are summarized in Table 3.

Table 3: HOST DMA OPTIONS

| Bit 4<br>DMA override<br>enable | Bit 3<br>DMA on/off | Effect                                     |

|---------------------------------|---------------------|--------------------------------------------|

| Off                             | No<br>Effect        | 16KTP behaves like<br>"normal" host memory |

| On                              | Off                 | l6KTP ignores all<br>host DMA requests     |

| On                              | On                  | 16KTP responds to<br>all host DMA requests |

Bit 5 (CPU paging)

In order to have the 16KTP respond to a particular page request from the SDI, bit 6, page enable, must be in the "on" position. If bit 6 is in the "off" position, the 16KTP will not differentiate between page 0 and page 1 requests and thus will respond to all accesses from the second port when of the correct block.

When bit 7 is in the "on" position the 16KTP will respond to either page 0 access or page 1 access from the second port (SDI). The determination of which page the RAM responds to is fixed by bit 7 - page 0 or 1. Page 0 is selected by bit 8 in the OFF position. Page 1 is selected by bit 8 in the ON position.

# Bit 8 (Phase)

Don't wonder, leave "OFF".

Cromemco 16KTP Two Port Memory

omem Con

# Chapter 5

# CONNECTIONS BETWEEN THE 16KTP AND THE SDI

The 16KTP contains provisions for a separate cable connection to the SDI. The pin group on the card edge, labelled J-1, is shown in Figure 6.

The connector J-1 is the main data and address transmission line to the SDI. The SDI sends address requests to the 16KTP through this connection, and the 16KTP responds by sending data back to the SDI, also through J-1. The details are shown below.

| 1.  | GND    | 2.  | EDO0*   |

|-----|--------|-----|---------|

| 3.  | EDO1*  | 4.  | ED02*   |

| 5.  | EDO3*  | 6.  | EDO 4 * |

| 7.  | EDO5*  | 8.  |         |

| 9.  | EDO7*  | 10. | GND     |

| 11. | EDIO   | 12. | EDI1    |

| 13. | EDI2   | 14. | EDI3    |

| 15. | EDI4   | 16. | EDI5    |

| 17. | EDI6   | 18. | EDI7    |

| 19. | GND    | 20. | EA0     |

| 21. | EAl    | 22. | EA2     |

| 23. | EA3    | 24. | EA4     |

| 25. | EA5    | 26. | EA6     |

| 27. | EA7    | 28. | EA8     |

| 29. | EA9    | 30. | EA10    |

| 31. | EA11   | 32. | EAl2    |

| 33. | EA13   | 34. | GND     |

| 35. | SREQ0  | 36. | SREQ1   |

| 37. | SREQ2  | 38. | SACK 0  |

| 39. | SACK 1 | 40. | SACK 2  |

| 41. | ER0    | 42. | ER1     |

| 43. | ER2    | 44. | ORRQ    |

|     | PG1    | 46. |         |

| 47. | EW0*   | 48. | EW1*    |

| 49. | EW2*   | 50. | GND     |

|     |        |     |         |

<sup>\*</sup> SDI-D not connected to these lines.

# SECOND PORT CONNECTOR J-1 PIN FUNCTION DESCRIPTIONS

# Pin Functions 2-9 ED00-7

The second port write data bus.

- 11-18 EDIO-7 Second port read data bus

- 20-33 EA0-13

Second port address bus. These lines are the same as address lines A0-A13. The memory block (i.e., the 16KTP being accessed) is determined through pins 35-37.

- 35-37 SREQ0-2

These low active lines select the 16KTP being accessed. They are decoded so that only one is active at any given time.

- 38-40 SACK 0-2

This signal is generated by the second port memory device after receiving a SREQ0-2 signal with ORACK high. The SACK signal states that the selected two port memory device (in this case, a 16KTP) has switched over to its second port and that the second port memory cycle can start immediately. From the reception of this signal, it is 220ns minimum until the end of the memory cycle.

- 41-43 ER0-2

These low active lines enable second port read data onto the second port bus from the selected Two Port RAM. They enable the data buffer.

- This line selects either the first 48K of second port memory when low (PAGEO) or the second 48K of memory (PAGEI) when high.

- 44,46 ORRQ, ORACK

These lines work in conjunction with SW-l on the DMA board of the SDI board set. If the override enable switch of SDI-D SW-l is on, then an override request on pin ORRQ generated by the 16KTP will cause the SDI to temporarily stop driving the Two Port RAM.

The second port signal ORRQ, is generated in accordance with the setting of switch 1 bits 4 and 8 (see Section 4.1, SW1). The ORACK line

is used by the controlling second port device to signal that an override is O.K. This is done by driving the line low. If ORACK is not taken low, then the HOST DMA device must WAIT because the HOST WAIT line will become active (low), or the DMA device will not read or write its data correctly. The ORRQ line should be pulled up to 5v through a 10K ohm resistor on the second port controlling device.

# 47-49 EW0-2

These low active lines allow the second port device to write a byte into the addressed RAM location of the selected block (0, 1 or 2). The EWO-2 signal must not go low before the respective SACKO-2 signal has been received from the 16KTP.

Figure 6: CABLE CONNECTIONS TO THE 16KTP

PARTS LIST

| Designation     | Description          | Cromemco<br>Part No. |

|-----------------|----------------------|----------------------|

| Integrated      | DESCRIPTION          | FAIL NO.             |

| Circuits        |                      |                      |

| IC1<br>IC2      | 745241               | 010-0088             |

| IC3             | 74LS08<br>74S04      | 010-0064<br>010-0123 |

| IC4             | 74LS00               | 010-0069             |

| IC5             | 74LS74               | 010-0055             |

| IC6-7           | 74LS153              | 010-0048             |

| IC8<br>IC9      | 74LS125              | 010-0127             |

| IC10-17         | 74LS257<br>9244/9044 | 010-0124<br>011-0013 |

| IC18            | 7805/340T-5          | 012-0001             |

| IC19            | 74832                | 010-0090             |

| IC20            | 74LS74               | 010-0055             |

| IC21<br>IC22    | 74LS164<br>74S02     | 010-0043             |

| IC22<br>IC23    | 74502<br>74LS27      | 010-0122<br>010-0112 |

| IC24            | 74LS32               | 010-0058             |

| IC25            | 74LS14               | 010-0061             |

| IC26<br>IC27    | 74LS257              | 010-0124             |

| IC28-35         | 74LS05<br>9244/9044  | 010-0065<br>011-0013 |

| 1C36            | 7805/340T-5          | 012-0001             |

| IC37            | NON TI 74LS04        | 010-0066             |

| IC38            | 74LS74               | 010-0055             |

| IC39-40<br>IC41 | 74LS00<br>74LS10     | 010-0069<br>010-0063 |

| IC42            | 74LS27               | 010-0112             |

| IC43            | 16 pin shunt         | 017-0069             |

| IC44            | 74LS257              | 010-0124             |

| IC45            | 74LS05               | 010-0065             |

| IC46-53         | 9244/9044            | 011-0013             |

| IC54            | 7805/340T-5          | 012-0001             |

| IC55<br>IC56    | 74LS14               | 010-0061             |

| IC56            | 74LS151<br>74S86     | 010-0049<br>010-0125 |

| IC58            | 74LS20               | 010-0095             |

| 6                                               |                                                                         |                                                                      |

|-------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|

| <u>Designation</u>                              | Description                                                             | Cromemco<br>Part No.                                                 |

| IC59<br>IC60<br>IC61<br>IC62<br>IC63-70         | 74S02<br>74LS139<br>74LS257<br>74LS14<br>9244/9044                      | 010-0122<br>010-0118<br>010-0124<br>010-0061<br>011-0013             |

| IC71<br>IC72-73<br>IC74<br>IC75                 | 74S373<br>74LS257<br>74S08<br>74125                                     | 010-0085<br>010-0124<br>010-0166<br>010-0011                         |

| Transistors/<br>Diodes                          |                                                                         |                                                                      |

| Q1<br>D1                                        | 2N3646<br>led til-211                                                   | 009-0000<br>008-0020                                                 |

| Capacitators                                    |                                                                         |                                                                      |

| C1-13<br>C14<br>C15-17<br>C18<br>C19-26         | .047 uf axial 10 uf tant .047 uf axial 15 pf mono .047 uf axial         | 004-0061<br>004-0032<br>004-0061<br>004-0044<br>004-0061             |

| C27<br>C28-37<br>C38<br>C39<br>C40-43           | 10 uf tant .047 uf axial 10 uf tant 15 pf mono 47 pf mono               | 004-0032<br>004-0061<br>004-0032<br>004-0044<br>004-0000             |

| C44-46<br>C47-52<br>C53<br>C54<br>C55<br>C56-58 | .047 uf axial 47 pf mono 10 uf tant 22 pf mono 47 pf mono .047 uf axial | 004-0061<br>004-0000<br>004-0032<br>004-0041<br>004-0000<br>004-0061 |

| Resistors                                       |                                                                         |                                                                      |

| R1<br>R2<br>R3<br>R4<br>R5                      | 390<br>10 K<br>270<br>100<br>2.2 K                                      | 001-0013<br>001-0030<br>001-0011<br>001-0007<br>001-0021             |

|                                           | <u> </u>                                                                                                              |                                                                                  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Designation                               | Description                                                                                                           | Cromemco<br>Part No.                                                             |

| R6<br>R7<br>R8<br>R9<br>R10-11            | 33<br>330<br>560<br>27<br>33                                                                                          | 001-0071<br>001-0012<br>001-0015<br>001-0047<br>001-0071                         |

| R12<br>R13<br>R14<br>R15-16<br>R17        | 560<br>330<br>33<br>560<br>10 K                                                                                       | 001-0015<br>001-0012<br>001-0071<br>001-0015<br>001-0030                         |

| R18<br>R19<br>R20-21<br>R22<br>R23<br>R24 | 560<br>470<br>560<br>1.5 K<br>10 K<br>390                                                                             | 001-0015<br>001-0014<br>001-0015<br>001-0020<br>001-0030<br>001-0013             |

| Resistor<br>Networks                      |                                                                                                                       | -                                                                                |

| RN1-2<br>RN3-5<br>RN6<br>RN7-9            | 100, 8 pin<br>10K, 8 pin<br>100, 8 pin<br>33, 8 pin                                                                   | 003-0001<br>003-0025<br>003-0001<br>003-0000                                     |

| RN10<br>RN11<br>RN12<br>RN13-14           | 560, 8 pin<br>10K, 8 pin<br>560, 8 pin<br>100, 8 pin                                                                  | 003-0006<br>003-0025<br>003-0006<br>003-0001                                     |

| Miscellaneous                             |                                                                                                                       |                                                                                  |

|                                           | 1 connector, 50 pin<br>2 sockets, 20 pin<br>32 sockets, 18 pin<br>11 sockets, 16 pin<br>27 sockets, 14 pin            | 017-0033<br>017-0004<br>017-0003<br>017-0002<br>017-0001                         |

|                                           | 1 heat sink 3 silicon pads 2 2-56x5/8 screws 3 6-32x7/16 screws 3 6-32 hex nuts 2 3/8x3/16 spacers 2 #2 nylon washers | 016-0060<br>021-0109<br>015-0113<br>015-0129<br>015-0074<br>015-0114<br>015-0115 |

# Cromemco 16KTP Two Port Memory

# LIMITED WARRANTY

Cromemoo, Inc. ("Cromemoo") warrants this product against defects in material and workmanship to the original purchaser for ninety (90) days from the date of purchase, subject to the following terms and conditions.

### What Is Covered By This Warranty:

During the ninety (90) day warranty period Cromemoo will, at its option, repair or replace this Cromemoo product or repair or replace with new or used parts any parts or components, manufactured by Cromemoo, which prove to be defective, provided the product is returned to an Authorized Cromemoo Dealer as set forth below.

# How To Obtain Warranty Service:

You should immediately notify IN WRITING your Authorized Cromemoo Dealer or Cromemoo of problems encountered during the warranty period. In order to obtain warranty service, first obtain a return authorization number by contacting the Authorized Cromemoo Dealer from whom you purchased the product. Then attach to the product:

- 1. Your name, address and telephone number,

- 2. the return authorization number,

- 3. a description of the problem, and

- proof of the date of retail purchase.

Ship or otherwise return the product, transportation and insurance costs prepaid, to the Authorized Cromemco Dealer. If you are unable to receive warranty repair from the Authorized Cromemco Dealer from whom you purchased the product, you should contact Cromemco Customer Support at: Cromemco, Inc., 280 Bernardo Ave., Mountain View, Ca. 94043.

### What Is Not Covered By This Warranty:

Cromemoo does not warrant any products, components or parts not manufactured by Cromemoo.

This warranty does not apply if the product has been damaged by accident, abuse, misuse, modification or misapplication; by damage during shipment; or by improper service. This product is not warranted to operate satisfactorily with peripherals or products not manufactured by Cromemco. Transportation and insurance charges incurred in transporting the product to and from the Authorized Cromemco Dealer or Cromemco are not covered by this Warranty.

# Exclusion of Liability, Damages, and Other Warranties:

THIS WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, WHETHER ORAL OR WRITTEN, EXPRESS OR IMPLIED. ANY IMPLIED WARRANTIES, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINE-TY (90) DAYS FROM THE DATE OF PURCHASE OF THIS PRODUCT. IF THIS PRODUCT IS NOT IN GOOD WORKING ORDER AS WARRANTED ABOVE, YOUR SOLE REMEDY SHALL BE REPAIR OR REPLACEMENT AS PROVIDED ABOVE. CROMEMCO SHALL NOT BE LIABLE FOR INCIDENTAL AND/OR CONSEQUENTIAL DAMAGES FOR THE BREACH OF ANY EXPRESS OR IMPLIED WARRANTY, INCLUDING DAMAGE TO PROPERTY AND, TO THE EXTENT PERMITTED BY LAW, DAMAGES FOR PERSONAL INJURY, EVEN IF CROMEMCO HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE AGENTS, DEALERS, AND EMPLOYEES OF CROMEMCO ARE NOT AUTHORIZED TO MAKE MODIFICATIONS TO THIS WARRANTY, OR ADDITIONAL WARRANTIES BINDING ON CROMEMCO ABOUT OR FOR PRODUCTS SOLD OR LICENSED BY CROMEMCO. ACCORDINGLY, ADDITIONAL STATEMENTS WHETHER ORAL OR WRITTEN EXCEPT SIGNED WRITTEN STATEMENTS FROM AN OFFICER OF CROMEMCO DO NOT CONSTITUTE WARRANTIES AND SHOULD NOT BE RELIED UPON. SOFTWARE, TECHNICAL INFORMATION AND FIRMWARE ARE LICENSED ONLY BY A SEPARATE AGREEMENT ON AN "AS IS" BASIS.

## Limitation on Statute of Limitation and Transferability:

This warranty and the statute of limitations shall run concurrently with any acceptance period. This warranty is not transferable. No suit, itigation, or action shall be brought based on the alleged breach of this warranty or implied warranties more than one year after the date of purchase in those jurisdictions allowing such a limitation, otherwise no such action shall be brought more than one year after the expiration of this warranty.

# Other Important Provisions:

Some states do not allow the exclusion or limitation of incidental or consequential damages or limitations on how long an implied warranty lasts, so the above limitation or exclusion may not apply to you. This warranty shall not be applicable to the extent that any provision of this warranty is prohibited by any federal, state or municipal law which cannot be preempted. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.