# CPU-Z TECHNICAL MANUAL

A206 \$20.00

## CPU-Z Technical Manual

IEEE 696/S-100 2-6 MHz CPU (SWITCH SELECTABLE) WITH ON-BOARD RAM/ROM AND INTERRUPT CONTROL CPU-Z Technical Manual Copyright 1982, 1984 CompuPro Hayward, CA 94545

Document No: 11608

File Name: CPUZ.MAN

Board No: 160K

First Edition: 1982

Second Edition: February 1984

Latest Printing: August, 1984

DISCLAIMER - CompuPro makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, CompuPro reserves the right to revise this publication and to make any changes from time to time in the content hereof without obligation of CompuPro to notify any person of such revision or changes.

CPU-Z is a trademark of CompuPro. Z80 is a trademark of the Zilog Corporation. TRI-STATE is a trademark of National Semiconductor Corp.

All rights reserved. No part of this publication may be reproduced or transmitted in any form, or by any means, without the written permission of CompuPro. Printed and assembled in the United States of America.

# CONTENTS

| How to Get Your CPU-Z Up and Running  |           |

|---------------------------------------|-----------|

| Without Reading the Manual            | 1         |

| Technical overview                    | 2         |

| Using vectored interrupts             | 2         |

| Using nonmaskable interrupts          | 3         |

| Extended addressing                   | 3         |

| Wait states                           | 4         |

| On-board-memory sockets               | 4         |

| Clock                                 | - 5       |

| Power-on-jump/jump-on-reset           | . 5       |

| MWRITE generation                     | 6         |

| IMSAI front panel usage               | 6         |

|                                       | 7         |

| Circuit description                   | 7         |

| Vectored interrupts and mask          | 7         |

| Extended addressing                   | 7         |

| CPU status lines                      | 7         |

| Status signals                        | -         |

| System clock                          | 8         |

| Power-on-jump(POJ)/jump-on-reset(JOR) | 8         |

| Wait states                           | 9         |

| Switch summary                        | 9         |

| Typical switch settings               | 10        |

|                                       | 10        |

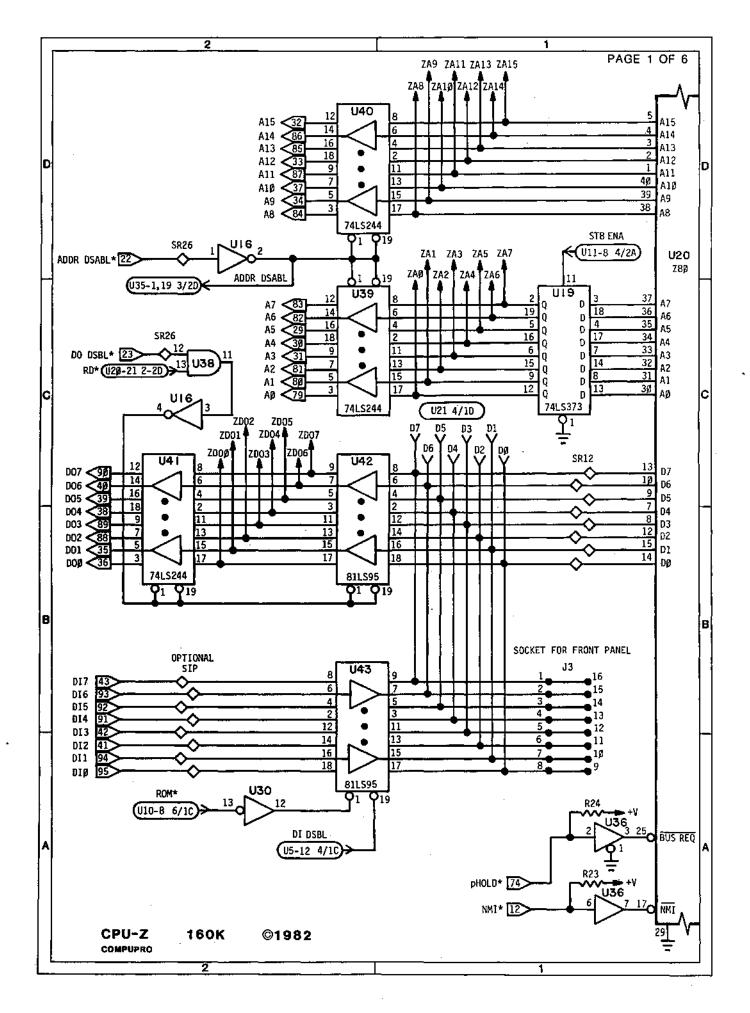

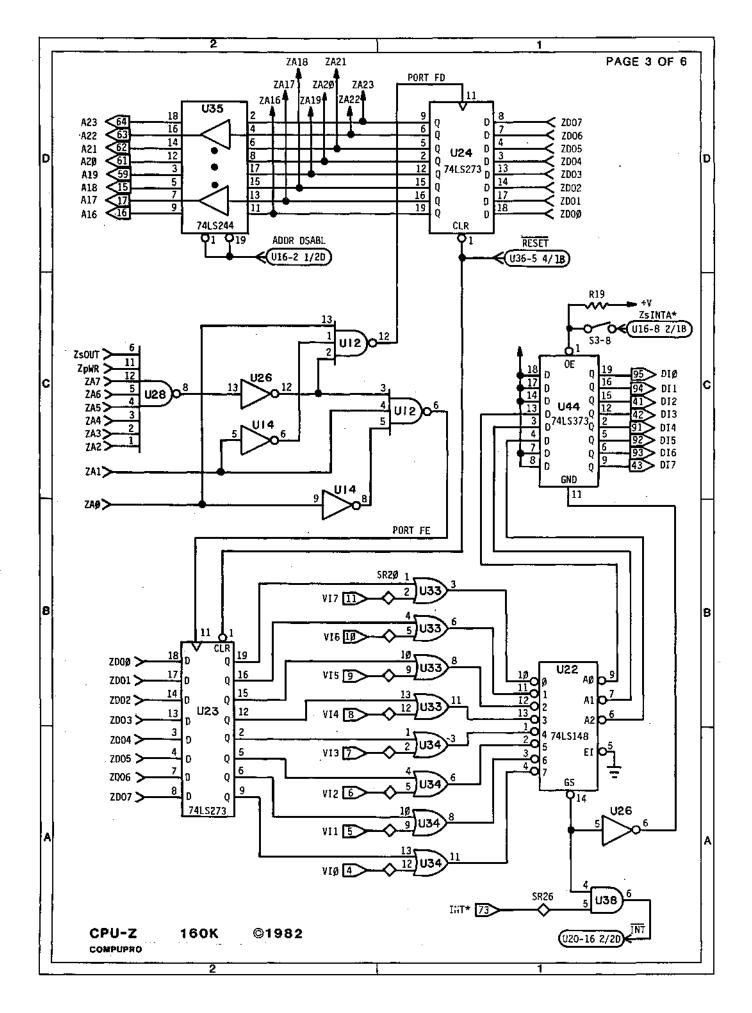

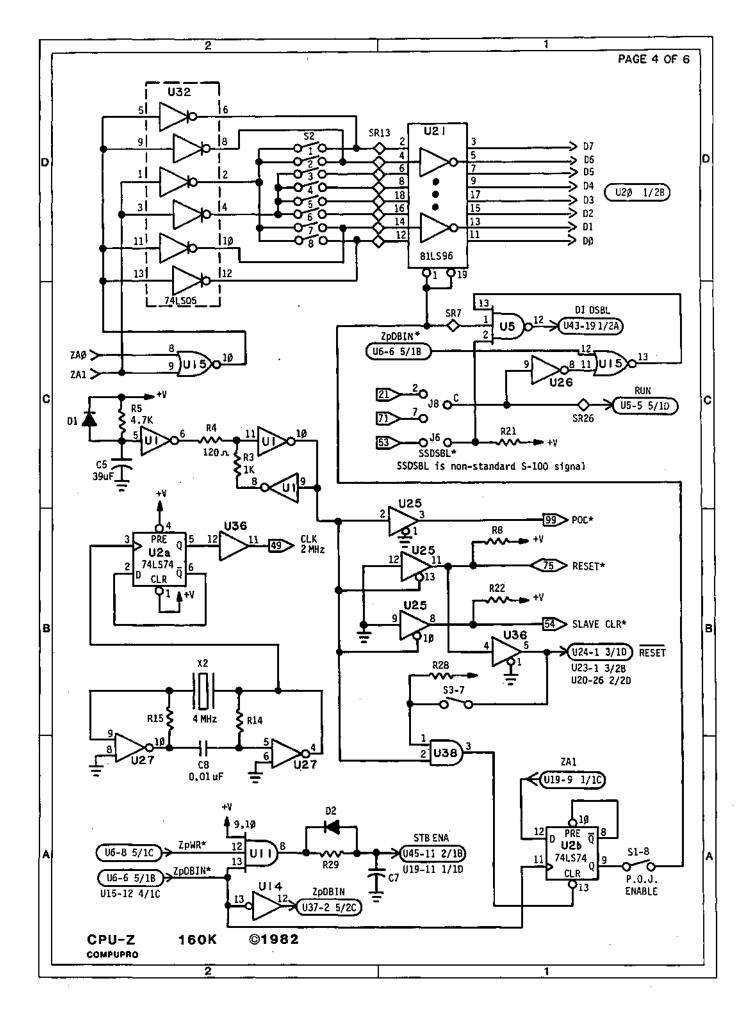

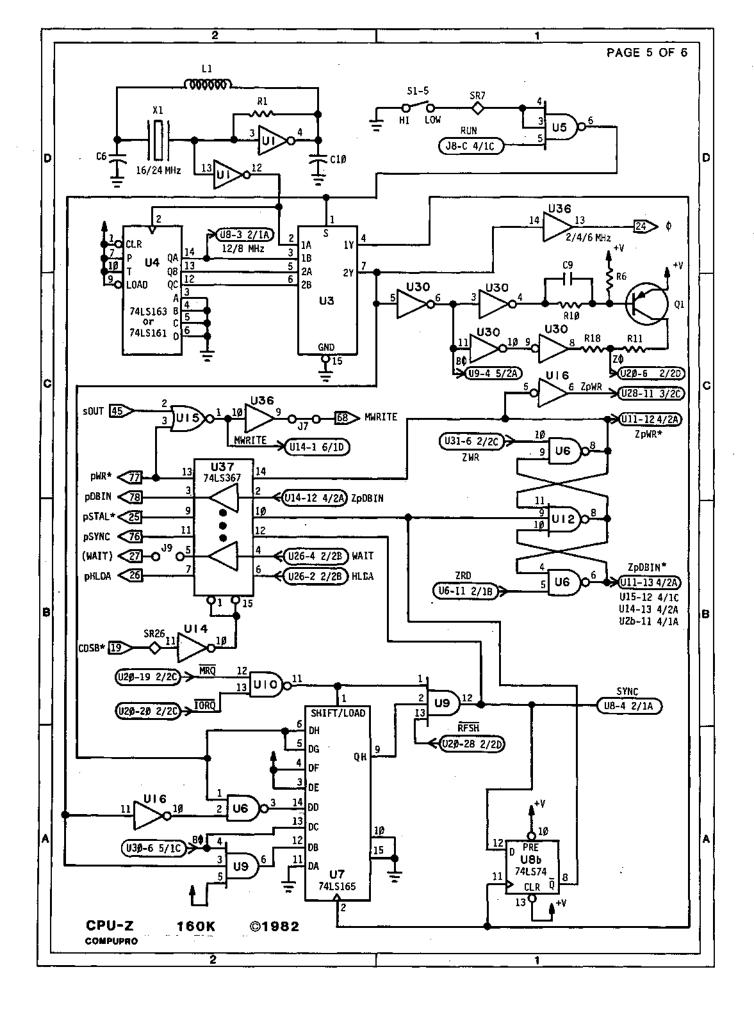

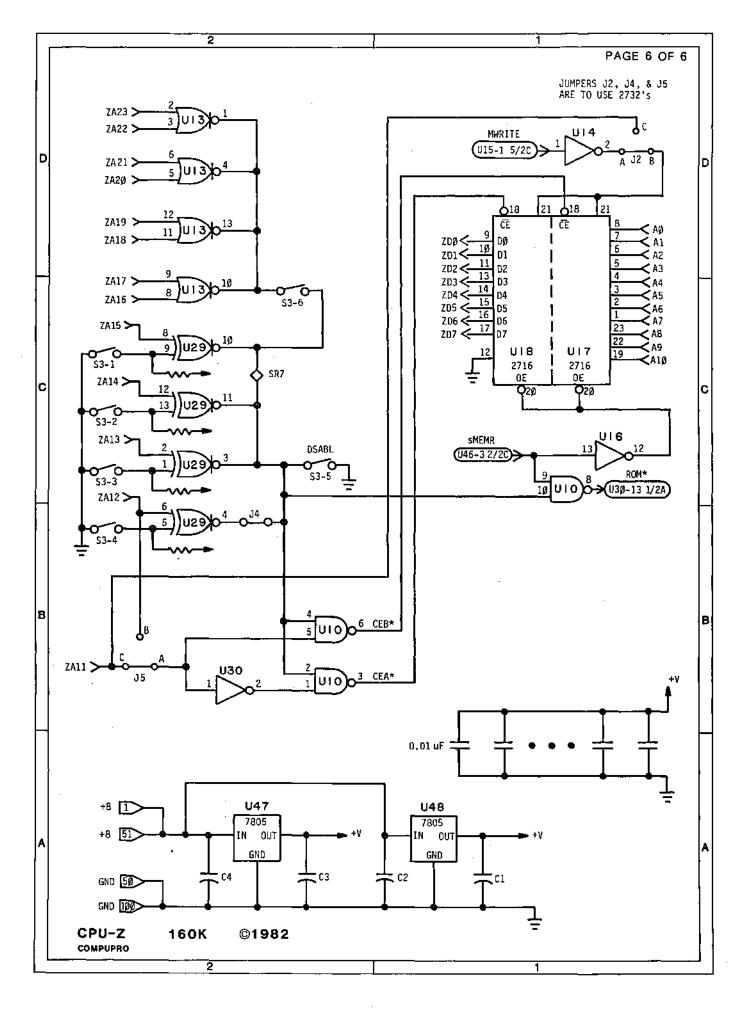

| Logic diagram                         | <b>17</b> |

|                                       | 18        |

|                                       | 19        |

# HOW TO GET YOUR CPU-Z UP AND RUNNING WITHOUT READING THE MANUAL

This section is for those of you who are anxious to see your new CPU board working without having to read the entire manual. By setting all the switches off except for switch 3, position 5, which should be switched on, the board will be set up for the standard CompuPro configuration. This assumes that you are not planning to run at the slow CPU-Z speed and that you do not require wait states generated on the CPU.

After you install the board and attach the cables, your board should work. If it doesn't, do not panic. Relax, read the rest of the manual and proceed with patience.

### TECHNICAL OVERVIEW

The CPU-Z with a Z80 CPU, features on-board memory sockets, a power-on-jump circuit to any 256 byte boundary, a Memory Manager to extend the addressing range of the system from 64 Kbytes to a maximum of 16 Mbytes of system RAM, fully maskable vectored interrupts to speed up system throughput by eliminating polling loops, and wait state generation circuitry for all machine cycles.

Other features standard to all CompuPro boards include thorough bypassing of all supply lines to suppress transients, on board regulators, and low power Schottky TTL and MOS technology integrated circuits for reliable, cool operation. All this and sockets for all ICs go into a double sided, solder masked printed circuit board with a complete component legend.

### USING VECTORED INTERRUPTS

The CPU chip recognizes 8 instructions as Restart0 - Restart7. These instructions will cause the program counter to jump to one of eight locations depending on the Restart instruction.

| RESTA | R7 | [  |   |   |    |   | Pr | og  | ra | <u>m C</u> | ounter(HEX) |

|-------|----|----|---|---|----|---|----|-----|----|------------|-------------|

| 0     | •  | ٠. | • |   | ٠  | • | •  | •   | •  | _ <u>o</u> |             |

| 1     |    |    |   |   | ٠  | ٠ |    | •   | •  | 8          |             |

| 2     | •  |    | ٠ |   |    | • |    | •   |    | 10         |             |

| 3     |    |    |   |   |    | • |    | ٠   | ٠  | 18         |             |

| 4     |    |    |   |   | ٠. |   |    | •   | •  | 20         |             |

| 5     |    |    | • | • | ٠  | ٠ | ٠  | • . | •  | 28         |             |

| 6     | •  | ٠  | ٠ | • | •  |   | •  | •   |    | 30         |             |

| 7     | ٠  | ٠  | • |   | •  |   |    |     | •  | 38         |             |

At these locations, jumps to interrupt driver routines can be placed into either RAM or PROM. Then when one of the VIO - VI7 lines goes low, the specific routine can instantly be started to service the interrupting device. Upon Power-on-Clear or reset (pRESET\*) the interrupt mask is cleared, enabling all eight interrupt lines (NOTE: This does NOT mean that the Z8O has interrupts enabled.) Then (with the VI switch [SW3-8] turned ON) when any of the VI inputs goes low the Restart will be generated if the CPU has previously received an Enable Interrupts (FB[H]) command. To disable an individual interrupt line, or a group of lines, the mask must be set up by an output to Port FE(H) with the desired mask in the Accumulator. A "1" in the mask will disable the interrupt line, and a "0" will enable the interrupt line.

If it is desired to use this CPU-Z board with the Z80 mode 2 interrupts, the on-board vector generation circuitry must be disabled. To do this switch SW3-8 should be turned OFF, and all ls should be output to the interrupt mask port (Port FE[H]). This will prevent the CPU-Z from responding to the VI lines, but it will still respond to the bus interrupt signal (bus pin 73).

| EXAMPLE            | (HEX) | (BINARY)   |

|--------------------|-------|------------|

| to disable VI5-VI7 | 03    | (00000111) |

| to disable VI2     | 20    | (00100000) |

| to disable all     | FF    | (11111111) |

Note that the VI lines are all open collector and more than one device can be connected to each VI line by using open collector gates.

It is recommended to put a "DEAD MEMORY" error recovery routine at location 38 (H), since this location will be jumped to in case the CPU encounters an FF (H) instruction, which corresponds to a restart 7. This is the instruction that will be read from a memory location for which there is no system memory. Location 38 is the most common launching pad for CPU flights into never-never land.

### USING THE NONMASKABLE INTERRUPT

The S-100 bus has a NMI\* pin (bus pin 12) which is implemented on the CPU card for any function that the user desires. NMI\* is primarily used for a catastrophic system failure, such as loss of primary power. This interrupt enables the processor to execute a short program to save current system parameters on either a disk or some other nonvolatile memory before total power is lost (which usually takes milliseconds, lots of time for a computer). The NMI\* causes the CPU to jump to address 66(H), which should be initialized with a routine to control the interrupt.

### EXTENDED ADDRESSING

Address lines A16-A23 are driven through output port FD(H) and can be changed with a simple output instruction. Upon Power-on-Clear or reset (pRESET\*) the extended address lines will be reset to 0, bringing the system up in base page. To access memory in other than base page requires an output to Port FD(H) with the desired page address in the Accumulator in order to set the extended address lines A16-A23. These address lines are pin numbers 16, 17, 15, 59, 61, 62, 63, & 64, for address lines A16-A23 respectively.

### Example:

| ACCUMULATOR DATA | TO ACCESS | PAGE  |

|------------------|-----------|-------|

| (HEX)            | (BINARY)  | (HEX) |

| 40               | 01000000  | 40    |

| 2                | 00000010  | 2     |

| FO               | 11110000  | FO    |

Of course, to take advantage of this extended addressing feature requires memory boards which respond to extended address lines. If a board does not monitor the S-100 extended address lines, then only the normal 16 address lines will be decoded.

### WAIT STATES

A single wait state may be added to any processor cycle by closing the corresponding dip switch on SWL. A wait may be added to:

| CYCLE           | SWITCH POSITION |

|-----------------|-----------------|

| ON-BOARD MEMORY | 1               |

| 1/0             | 2               |

| MEMORY          | 3               |

| INSTRUCTION     | 4               |

Due to critical timing requirements of the Z80 during an instruction fetch (M1), extra time may be required for marginally slow memory chips. When running at 4 MHz or 6 MHz some RAM chips may also need more time for each memory operation than is normally allowed. The on-board-memory sockets may be used for many different speed parts, and when running at 4 MHz or 6 MHz a wait state may be needed for a fetch there also. In addition, since the internal architecture of the RAM 16 and RAM 21 are optimized for 16 bit CPUs, a memory request wait state (S1-3) may be required when running either of these memory boards with the 6 MHz CPU-Z.

### **ON-BOARD-MEMORY SOCKETS**

The MEMORY sockets on this board are set up to take INTEL 2716, T.I. 2516 2Kx8 EPROMS, or any of the new 2Kx8 RAM chips which are pin compatible (Hitachi HM6116 or equivalent). By cutting J2(A-B) on the solder side above U17, J4 on the solder side to the left of U29, an J5(A-C) on the solder side to the left of U29 and installing jumpers J2(A-C) and J5(A-B) the sockets can now be used for 2732 4Kx8 EPROMS. (NOTE: Extreme care must be used when soldering in the jumpers so as not to damage the board or any of the traces. A soldering iron of no more than 25 watts should be used.) With 2732s SW3-4 is no longer used to address the sockets. The on-board sockets will be totally disabled when switch SW3-5 is ON. With SW3-6 ON, the sockets are addressable anywhere in base page (A16-A23 are all 0) on a 4K boundary (8K for the 2732s). This feature allows the user to have on-board-memory in base page only. With SW3-6 OFF, the sockets ignores address lines A16 - A23 and occupies every page of memory. A prime example of how to use the

sockets in this "shadow" mode would be to use them with SW3-6 turned ON and the Power-on-jump set to the start of the PROM address, then when the system is initially turned on the program in the PROM will start and either initialize the system by booting in a disk program, or some other type of routine. Then the last thing the PROM will do is jump to the RAM address where the initialization routine was loaded. The first thing that program will do is an output to port FD(H) of anything except 0. This will set the extended page address to the page that was in the Accumulator, and the sockets will be disabled. RAM which was overlapped with the PROM can now be used and a complete memory map is available to the user. SW3 positions 1-4 are used for address lines A15-A12. The socket closest to the Z-80 chip is the low address half and the left socket the high half.

|           |   | SWITCH | <b>S</b> 3 |   | DESIRED START | ADDRESS (HEX) |

|-----------|---|--------|------------|---|---------------|---------------|

|           | 1 | 2      | 3          | 4 | 2716          | 2732          |

|           | 0 | 0      | 0          | 0 | 0000-0FFF     | 0000-1FFF     |

|           | 0 | 0      | 0          | 1 | 1000-1FFF     |               |

| 0N = "0"  | 0 | 0      | 1          | 0 | 2000-2FFF     | 2000-3FFF     |

| OFF = "1" | 0 | 0      | 1          | 1 | 3000-3FFF     |               |

|           | : | :      | :          | : | : :           | : :           |

|           | : | :      | :          | : | : :           | : :           |

|           | 1 | 0      | 1          | 0 | A000-AFFF     | A000-BFFF     |

|           | : | :      | ;          | : | : :           |               |

|           | 1 | 1      | 1          | 1 | FOOO-FFFF     | •             |

To disable sockets completely, turn ON SW3-5

### CLOCK

The clock for this system can be set to allow the CPU to run at either 3 MHz or 6 MHz. SW1-5 is used to select between these two speeds. When SW1-5 is ON the CPU will run at 3 MHz and bus pin 24 (\$\phi\$) will have a 3 MHz square wave on it. When SW1-5 is OFF, the system will run at 6 MHz and bus pin 24 will have a 6 MHz square wave on it. With a 16 MHz crystal used for X1 the speed switch SW1-5 will select between processor speeds of 4 MHz (when OFF) and 2 MHz (when ON). Bus pin 49 (CLK) will always have a 2 MHz signal on it.

### POWER-ON-JUMP/JUMP-ON-RESET

Provisions have been made on this board to allow the processor to jump to any memory location on a 256 byte boundary on either a power-on only, or every reset also. To enable this feature, JMP ENABLE (SW1-8) should be turned ON and the jump address should be set on switch S2 according to the following table. To enable the jump on every reset also, SW3-7 should also be turned ON.

| SWITCH PO | SI | TI | ON |   |   |   | FUNCTION  | ĺ      |       |

|-----------|----|----|----|---|---|---|-----------|--------|-------|

| 1 .       |    |    | ↴  |   | • |   | ADDRESS A | 15     |       |

| 2.        |    |    |    |   |   |   | ADDRESS A | 14     |       |

| 3.        |    |    |    |   |   |   | ADDRESS A | .13    |       |

| ٠ 4 .     |    |    |    | ٠ |   | ٠ | ADDRESS A | 12 ON  | = "1" |

| 5.        |    |    |    |   |   |   | ADDRESS A | 11 OFF | = "0" |

| 6.        |    |    |    |   |   |   | ADDRESS A | .10    |       |

| 7.        |    |    |    |   |   |   | ADDRESS A | .9     |       |

| 8.        |    |    |    |   |   |   | ADDRESS A | .8     |       |

EXAMPLE: To jump to E900 for a North Star floppy disk system, S2 positions 1-3,5, and 8 should be ON and S2 positions 4,6,and 7 should be OFF. JMP ENABLE (SW1-8) should be ON to enable this feature. NOTE: Since the jump circuitry disables the input buffer, it is unnecessary to use the phantom line (S-100 pin 67) for proper operation.

### **MWRITE GENERATION**

The CPU-Z has circuitry on board for generating the MWRITE signal (bus pin 68) and a positive going strobe will be generated for each memory write operation. This circuitry looks at the bus and whenever the south signal is low, and the pWR\* signal strobes low, an MWRITE strobe will be generated. This signal must be generated at only one source in each system. If there is a front panel in your system it also may be generating the MWRITE signal, and the signal from the CPU-Z must be disabled. There are two ways to disable this signal:

- A) Cut jumper J7 on the solder side below U36 and R21; or

- B) Remove pin 9 of U36 from its socket and let the pin hang out.

This makes it easier to reconnect the pin should you ever want MWRITE to be generated from the CPU-Z board in the future. If MWRITE is generated in more than one place, memory boards that rely on MWRITE as their write strobe may not work properly.

### IMSAI FRONT PANEL USAGE

If you have an IMSAI type front panel this CPU will require minor modifications to work properly. The problems arise from the fact that the IMSAI front panel (which does not conform to the IEEE standard) requires some signals that are not on the S-100 bus. Jumper pads are provided to allow these lines to be used. J6, and J8 should be installed to connect bus pins 53, and 21 (J8 connect C to 2) respectively to control the CPU from the front panel. If the system is set to run at 4 MHz or 6 MHz, the front panel will force the CPU to run at 2 MHz or 3 MHz when the RUN/STOP signal is in the STOP mode. This will allow for proper front panel operation which is speed dependent. Socket J3 in the upper right corner is for the front panel connector. Jumper J9 can be installed to have the CPU drive bus pin 27 (which was the WAIT

line). Pin 13 of U38 must also be removed from the socket and tied to +5 volts. This can be done by connecting the free hanging pin 13 to pin 14 and keeping pin 14 in the socket. This will allow the DATA OUT bus to reflect the DATA IN bus information which the front panel reQuires. The MWRITE circuitry will also have to be disabled if the front panel is going to generate MWRITE (bus pin 68).

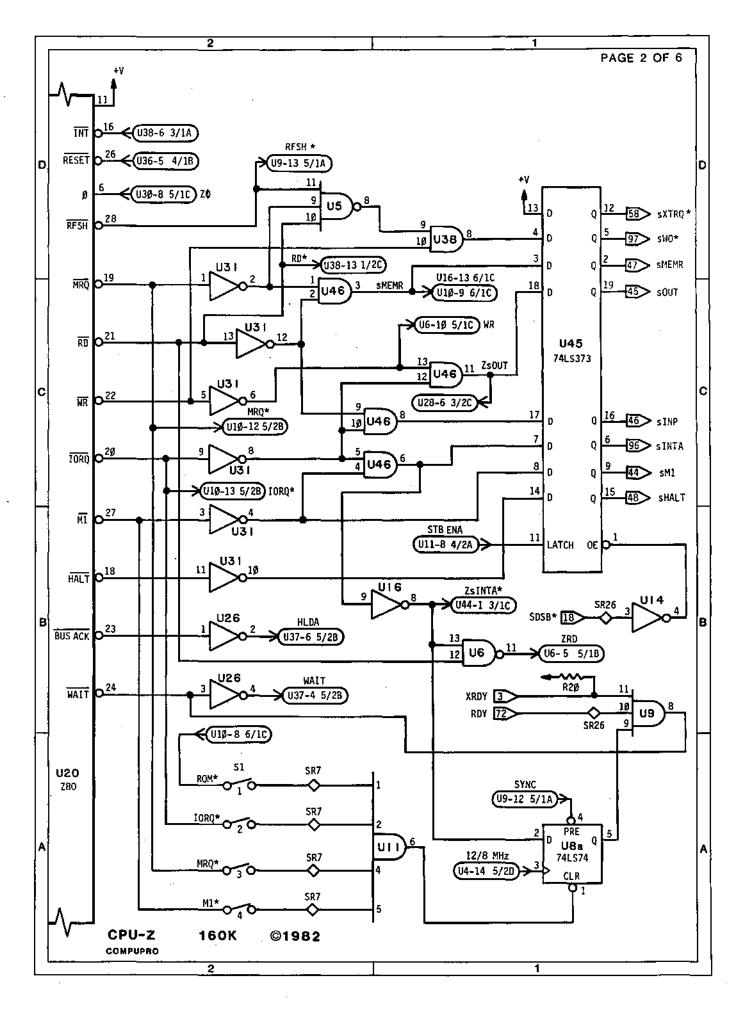

### CIRCUIT DESCRIPTION

### **VECTORED INTERRUPTS AND MASK**

Upon reset (pRESET\*) U23 is cleared, and will output all lows to the OR gates (U33 & U34). The VIO - VI7 inputs normally sit at a high level, and hence all inputs on U22 are high. This resting state makes the GS output high. Upon receiving a vectored interrupt when one of the VIO - VI7 inputs goes low, U22 will output a value corresponding to the highest priority interrupt on the lines. This value will go to U44 and when the CPU acknowledges the interrupt, the proper Restart command will go to the CPU. When a 1 has been written into the mask port FE(H), U23 will output a high to the associated OR gate (U33 & U34). Then when an interrupt pulls the input low, U22 will still have a high input and will never detect interrupts that are being masked out.

### EXTENDED ADDRESSING

When an OUT FD(H) instruction is executed, the data bits in the Accumulator are latched into U24 and output on bus lines A16-A23. These address lines will be TRI-STATEd<sup>tm</sup> along with the other 16 address lines when ADDR-DSABL (bus pin 22) is driven low by an external device requesting control of the bus.

### CPU STATUS LINES

The S-100 bus has eight status signals that all bus masters must provide, these signals come from U45. During either a read cycle or a write cycle these status signals are latched on the bus. A short time after the read or write signal goes away the status signals are allowed to toggle. The S-100 status signals are shown below, along with their associated bus pins. (A \* suffix means active low signal.)

| SIGNAL | BUS PIN |

|--------|---------|

| sWO*   | 97      |

| sMEMR  | 47      |

| sINTA  | 96      |

| sMl    | 44      |

| sINP   | 46      |

| sOUT   | 45      |

| sHLTA  | 48      |

| sXTRQ* | 58      |

These status bits are decoded from the seven control signals coming from the Z80 as shown (a \* suffix means active low signal):

### STATUS SIGNALS

| CONTROL SIGNAL | *WO          | sMEMR          | sINTA | sM1 | sINP | sOUT     | sHLTA      |

|----------------|--------------|----------------|-------|-----|------|----------|------------|

|                | (a) or (l    | o)             |       |     |      | <u> </u> |            |

| RFSH*          | 1 7          | <del>X</del> X | Х     | X   | X    | X        | X          |

| MRQ*           | 0 2          | ζ 0            | X     | X   | X    | X        | X          |

| RD*            | 1 2          | K 0            | X     | X   | 0    | X        | x          |

| wr*            | X, C         | X              | X     | X   | X    | 0        | X          |

| IORQ*          | X X          | Х              | 0     | X   | 0    | 0        | X          |

| M1*            | X Y          | X X            | 0     | 0   | X    | X        | . <b>X</b> |

| HALT*          | , <b>X</b> 2 | х х            | X     | X   | X    | X        | 0          |

An X means a don't care condition. The sXTRQ\* signal is permanently high since this is an 8 bit processor.

### SYSTEM CLOCK

The system clock circuitry consists mainly of U1, U3, and U4. The 16 or 24 MHz square wave is fed into U4 which divides it down to the desired system clock speed. The multiplexer U3 will feed either 16 and 24 MHz or 8 and 12 MHz to the pSYNC and pSTVAL\* generation circuitry and 2 and 3 MHz or 4 and 6 MHz to the Z80 and bus for the system clock. If jumper J8 (C-2) is used, then when the SINGLE STEP LINE (bus pin 21) is low the input to U5 will be low and cause the system to run at 2 MHz. This is the same circuitry that switch SW1-5 uses to determine the system speed. X2 & U27 generate a 4 MHz clock which is divided down to 2 MHz by U2 and then through a buffer to bus pin 49, which is the clock signal.

### POWER-ON-JUMP(POJ)/JUMP-ON-RESET(JOR)

The jump circuitry consists of octal inverter U21 (81LS96), DIP switch SW2, SIP resistor R13, hex o.c. inverter U32 (74LSO5), a "D" flip flop U2, the POJ enable switch SWI-8, and JOR enable switch SW3-7. With the POJ enable switch ON, upon receiving a power-onclear, the "D" flip flop is cleared which disables input buffer U43, and enables jump buffer U21. This action starts a three byte sequence which will cause the CPU to jump to the proper starting The CPU is reset to address 0, and from the jump buffer a jump (C3H) instruction is put on the data bus. At address 1 the low order address of zero is then put on the data bus, then at address 2 the high order address coming from the jump switch setting is placed on the data bus. When address 2 is in the address buffer the "D" flip flop will then be clocked to the set state and disable the jump buffer while enabling the data input The "D" flip flop will not get cleared again until the next Power-On-Clear (POC). This complete sequence also occurs for

every RESET\*, if switch SW3-7 is turned ON. This option will allow the CPU to come up with a known jump on power-on and then later when a reset is recognized the CPU can either start again at O(H) or jump to the address in switch SW2.

### WAIT STATES

The CPU wait line (Z80 pin 24) is driven by three main sources, causing the processor to give more time for certain devices or system states. The three sources are:

- The RDY (pin 72) bus signal, which will be driven by an external device which must have more time to respond to the CPU,

- b) The XRDY (pin 3) bus signal which is driven by the front panel (if the system has one), and

- c) On board selector to generate a wait state for four different states.

The on-board wait state will come from the settings of SWl positions 1-4. Ml (SW1-4) will generate a wait state for every instruction cycle. The MRQ (SW1-3) will generate a wait state for every memory fetch cycle. The IORQ (SW1-2) will generate a wait state during every I/O operation. Finally, the ROM switch (SW1-1) will generate a wait state for every access of the on-board MEMORY. U8 will remain in the set mode with Q high unless one of these switches (SWl positions 1-4) is turned ON. Then when one of the selected inputs go low, U8 will be cleared and cause the wait input (on the CPU) to go low. These wait states can only start when pSYNC is high. When pSYNC goes low U8 will be set and end the wait. A wait will also be generated for each interrupt acknowledge cycle to allow external interrupt controllers to respond.

### SWITCH SUMMARY

| S1 POSITION | FUNCTION                         |

|-------------|----------------------------------|

| 1           | WAIT STATE FOR ON-BOARD MEMORY   |

| 2           | WAIT STATE FOR I/O               |

| 3           | WAIT STATE FOR MEMORY            |

| . 4         | WAIT STATE FOR INSTRUCTION FETCH |

| 5           | SPEED SWITCH (OFF = HIGH SPEED)  |

| 6           | NOT USED                         |

| 7           | NOT USED                         |

| 8           | POWER-ON-JUMP ENABLE             |

| S2 POSITION | FUNCTION                         |

|-------------|----------------------------------|

| 1           | JUMP ADDRESS BIT A15             |

| 2           | JUMP ADDRESS BIT A14             |

| 3           | JUMP ADDRESS BIT A13 ON = "1"    |

| 4           | JUMP ADDRESS BIT Al2 OFF = "0"   |

| 5           | JUMP ADDRESS BIT All             |

| 6           | JUMP ADDRESS BIT A10             |

| 7           | JUMP ADDRESS BIT A9              |

| 8           | JUMP ADDRESS BIT A8              |

| S3 POSITION | FUNCTION                         |

| 1           | SOCKET ADDRESS BIT A15           |

| 2           | SOCKET ADDRESS BIT A14 ON = "0"  |

| 3           | SOCKET ADDRESS BIT A13 OFF = "1" |

| 4           | SOCKET ADDRESS BIT A12           |

| 5           | SOCKET DISABLE (WHEN ON)         |

| 6           | SOCKET BASE PAGE ONLY (WHEN ON)  |

| 7           | JUMP-ON-RESET ENABLE             |

INTERRUPT ENABLE FOR VECTORED INTERRUPTS

### TYPICAL SWITCH SETTING

8

For a typical CompuPro system with a CompuPro DISK 1 floppy disk controller board, all switch positions should be OFF except SW3-5. This will have the CPU-Z running at the high speed, no wait states, no power-on-jump, no vectored interrupts, and no on-board memory.

### JUMPER SUMMARY

- J2 Used with J4, J5, to convert memory sockets for 2732 use

- J3 Front panel data socket

- J4 See J2

- J5 See J2

- J6 SSDSBL for IMSAI type systems

- J7 MWRITE brought to Bus pin 68

- J8 Run or single step for IMSAI type systems

- J9 WAIT brought to Bus pin 27

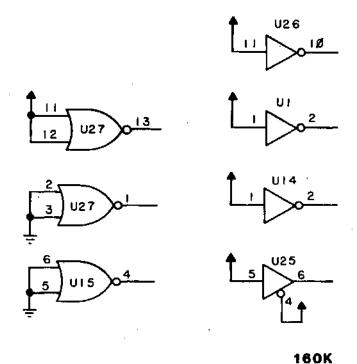

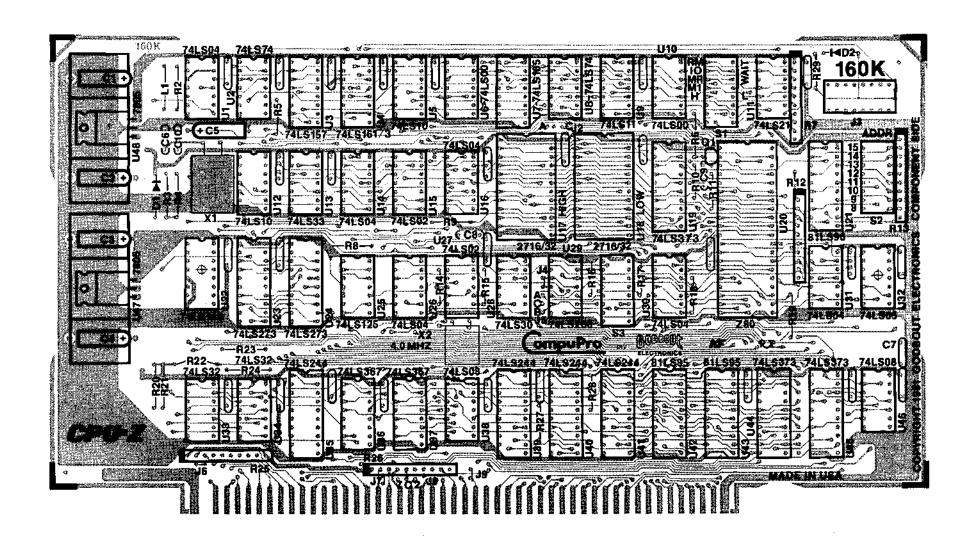

### LOGIC DIAGRAM

The numbers inside the ovals on the logic diagram indicate where a signal comes from or goes to, for example:

U20-21 2/2D = [IC # 20] - [Pin # 21] [Page # 2] / [Coordinates 2D]

### UNUSED GATES

COMPUPRO ©1982

# PARTS LIST

| SEMIC      | CONDUCTOR | RESISTOR    | VALUE           |

|------------|-----------|-------------|-----------------|

| Ų1         | 74LS04    | R1          |                 |

| U2         | 74LS74    | R2          | 1K ohm          |

| บ3         | 74LS157   | R3          | 1K ohm          |

| U4         | 74LS161/3 | R4          | 120 ohm         |

| U5         | 74LS10    | R5          | 4.7K ohm        |

| U6         | 74LS00    | R6          | 150 ohm         |

| บ7         | 74LS165   | R7          | 5.1K ohm SIP    |

| U8         | 74LS74    | R8          | 1.5K ohm        |

| บ9         | 74LS11    | R9          | 4.7K ohm        |

| U10        | 74LS00    | R10         | 910 ohm         |

| <b>V11</b> | 74LS21    | R11         | 33 ohm          |

| U12        | 74LS10    | R12         | 5.1K ohm SIP    |

| บ13        | 74LS33    | R13         | 5.1K ohm SIP    |

| บ14        | 74LS04    | R14         | 1K ohm          |

| U15        | 74LS02    | R15         | 1K ohm          |

| U16        | 74LS04    | R16         | 4.7K ohm        |

| บ17        | 2716-32   | R17         | 4.7K ohm        |

| U18        | 2716-32   | R18         | 33 ohm          |

| V19        | 81LS95    | R19         | 4.7K ohm        |

| U20        | Z80B      | R20-24      | 1.5K ohm        |

| U21        | 81LS96/98 | R25         | 1.5K ohm SIP    |

| U22        | 74LS148   | R26         | 1.5K ohm SIP    |

| Ծ23        | 74LS273   | R27         | 4.7K ohm        |

| Ծ24        | 74LS273   | R28         | 4.7K ohm        |

| ช25        | 74LS125   | R29         | 390 ohm         |

| บ26        | 74LS04    |             |                 |

| บ27        | 74LS02    | · CAPACITOR | VALUE           |

| U28        | 74LS30    | C1-5        | Tantalum Bypass |

| U29        | 74LS266   | C6          | 62 pF           |

| บ30        | 74LS04    | C7          | 390 pF          |

| U31        | 74LS04    | C8          | 0.01 uF         |

| บ32        | 74LS05    | C9          | 43 pF           |

| บ33        | 74LS32    | UNMARKED    | 0.01 uF         |

| <b>U34</b> | 74LS32    |             |                 |

| ช35        | 74LS244   | INDUCTOR    |                 |

| บ36        | 74LS367   | L1          | 1.0 uH          |

| <b>V37</b> | 74LS367   |             |                 |

| บ38        | 74LS08    | CRYSTAL     | VALUE           |

| บ39        | 74LS244   | <b>X1</b>   | 24 MHz          |

| U40        | 74LS244   | X2          | 4 MHz           |

| U41        | 74LS244   |             |                 |

| U42        | 81LS95    | DIODE       |                 |

| Ծ43        | 81LS95    | D1-2        | Signal Diode    |

| U44        | 74LS373   |             |                 |

| U45        | 74LS373   | TRANSISTO   |                 |

| U46        | 74LS08    | Q1          | 2N3906          |

| V47<br>V48 | 7805      |             |                 |

|            | 7805 l    | I           |                 |

COMPONENT LAYOUT

### LIMITED WARRANTY

COMPUPRO warrants this computer product to be in good working order for a period of one (1) year, (two [2] years CSC and six [6] months for disk drives) from the date of purchase by the original end user. Should this product fail to be in good working order at any time during this warranty period, COMPUPRO will, at its option, repair or replace the product at no additional charge except as set forth below. Repair parts and replacement products will be furnished on an exchange basis and will be either reconditioned or new. All replaced parts and products become the property of COMPUPRO. This limited warranty does not include service to repair damage to the product resulting from accident, disaster, misuse, abuse, or unauthorized modification of the product.

If you need assistance, or suspect an equipment failure, always contact your COMPUPRO System Center or dealer first. COMPUPRO System Center technicians are factory trained to provide prompt diagnosis and repair of equipment failures. If you prefer, or if you are not satisfied by the actions taken by your System Center/dealer, you may return the product to COMPUPRO for warranty service. Please call COMPUPRO at (415) 786-0909 to obtain a Return Material Authorization (RMA) number, or, write to COMPUPRO at 3481 Arden Road, Hayward, California 94545, Attn.: RMA. Be sure to include a copy of the original bill of sale to establish purchase date. If the product is delivered by mail or common carrier, you agree to insure the product or assume the risk of loss or damage in transit, to prepay shipping charges to the warranty service location (System Center or COMPUPRO) and to use the original shipping container or equivalent. Contact your COMPUPRO System Center/dealer or write to COMPUPRO at the above address for further information.

ALL EXPRESS AND IMPLIED WARRANTIES FOR THIS PRODUCT, INCLUDING THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO A PERIOD OF ONE (1) YEAR FROM THE DATE OF PURCHASE, AND NO WARRANTIES, WHETHER EXPRESS OR IMPLIED, WILL APPLY AFTER THIS PERIOD. SOME STATES DO NOT ALLOW LIMITATIONS ON HOW LONG AN IMPLIED WARRANTY LASTS, SO THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

IF THIS PRODUCT IS NOT IN GOOD WORKING ORDER AS WARRANTED ABOVE, YOUR SOLE REMEDY SHALL BE REPAIR OR REPLACEMENT AS PROVIDED ABOVE. IN NO EVENT WILL COMPUPRO BE LIABLE TO YOU FOR ANY DAMAGES, INCLUDING ANY LOST PROFITS, LOST SAVINGS OR OTHER INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OF OR INABILITY TO USE SUCH PRODUCT, EVEN IF COMPUPRO OR A COMPUPRO FULL SERVICE SYSTEM CENTER HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, OR FOR ANY CLAIM BY ANY OTHER PARTY.

SOME STATES DO NOT ALLOW THE EXCLUSION OR LIMITATION OF INCIDENTAL OR CONSEQUENTIAL DAMAGES FOR CONSUMER PRODUCTS, SO THE ABOVE LIMITATIONS OR EXCLUSIONS MAY NOT APPLY TO YOU.

THIS WARRANTY GIVES YOU SPECIFIC LEGAL RIGHTS, AND YOU MAY ALSO HAVE OTHER RIGHTS WHICH MAY VARY FROM STATE TO STATE.

COMPUPRO 3481 Arden Road Hayward, CA 94545 (415) 786-0909

Note: This warranty supersedes all previous warranties, and all other warranties are now obsolete.