# CCS 200, 300 & 400 Z-80 Family

# **PROGRAMMING GUIDE**

| 7    |

|------|

| 31 ° |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| 1    |

|      |

| 4    |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| 14   |

| 541  |

|      |

| 14   |

| 14   |

| 14   |

|      |

|      |

|      |

# CCS SYSTEMS 200, 300, and 400

# Z-80™ FAMILY

# PROGRAMMING REFERENCE MANUAL

MANUAL 89000-23400 REV. A COPYRIGHT 1981

CALIFORNIA COMPUTER SYSTEMS 250 CARIBBEAN DRIVE SUNNYVALE CA 94086

Copyright 1981 by California Computer Systems.

All rights reserved. No part of this publication may be reproduced in any form or by any means without express permission of California Computer Systems.

The information contained in this manual is believed to be correct at the time of publication. However, CCS assumes no liability resulting from the use of this publication.

Publication history:

Revision A printed March 1981

Z-80™ is a trademark of Zilog, inc.

## INTRODUCTION

This manual is divided into sections corresponding to the six Z-80 devices used in the CCS 200, 300, and 400 systems: the CPU, the SIO, the DART, the PIO, the CTC, and the DMA. Each section provides a complete discussion of how to program the device in question, though the implementation of the devices in CCS systems may often limit the programming possibilities. Such limitations are noted in the Programming Information chapters of the individual board manuals.

In order to minimize the number of ports occupied by a device, the Z-80 peripherals have been designed so that a number of registers may occupy a single address. In some cases part of the base register for a certain address is used to point to the register to be accessed on the next read or write. In other cases certain bits determine the register being accessed by the current operation. The result is that programming of the Z-80 family can become somewhat complicated. It is the aim of this manual to simplify the procedure as much as possible. This manual is not a Z-80 programming tutorial, however. It is designed to be used as a reference by programmers experienced with similar kinds of programming, if not with programming the Z-80 itself. For those who desire a tutorial approach, a number of good books are available.

# TABLE OF CONTENTS

| CHAPT                                                                       | TER 1              | PROGR                                                                                                       | AM                                        | II    | NG  | 7                                       | H     | E    | CI                                      | PU                                    |      |       |      |     |   |                                         |     |      |   |                                         |     |     |            |                                                    |   |

|-----------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------|-----|-----------------------------------------|-------|------|-----------------------------------------|---------------------------------------|------|-------|------|-----|---|-----------------------------------------|-----|------|---|-----------------------------------------|-----|-----|------------|----------------------------------------------------|---|

| 1.1<br>1.2<br>1.3                                                           | CPU INTE           | REGISTER<br>ERRUPT MO<br>STRUCTION                                                                          | DES                                       | 5     |     |                                         |       |      |                                         |                                       |      |       |      |     | • |                                         |     |      |   |                                         |     |     | 1          | -3                                                 |   |

| CHAPT                                                                       | TER 2              | PROGR                                                                                                       | AMI                                       | IIN   | NG  | 7                                       | ΡН    | E    | S                                       | 10                                    | )    |       |      |     |   |                                         |     |      |   |                                         |     |     |            |                                                    |   |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11 | STATUS             | REGISTER | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>Ø<br>1 | •     |     | • • • • • • • • • • • • • • • • • • • • |       |      | • • • • • • • • • • • • • • • • • • • • | · · · · · · · · · · · · · · · · · · · |      |       |      |     |   | • • • • • • • • • • • • • • • • • • • • |     |      |   | • • • • • • • • • • • • • • • • • • • • |     |     | 2-2-2-2-2- | -2<br>-6<br>-6<br>-7<br>-9<br>10<br>11<br>11<br>13 |   |

| CHAP                                                                        | rer 3              | PROGR                                                                                                       | AMI                                       | MII   | NG  | 7                                       | гн    | E    | D.                                      | AR                                    | т    |       |      |     |   |                                         |     |      |   |                                         |     |     |            |                                                    |   |

| 3.1<br>3.2                                                                  | COMMAND<br>COMMAND | REGISTER<br>REGISTER                                                                                        | 1                                         |       |     |                                         | 77.5  |      |                                         |                                       |      |       |      |     |   |                                         | -   |      |   |                                         | -   |     | - 35       | 3-1<br>3-3                                         |   |

| 3.3                                                                         | COMMAND            | REGISTER                                                                                                    |                                           | -     |     | _                                       | -     |      | _                                       | -                                     |      | -     |      | -   | - | _                                       |     | _    | - | -                                       | -   |     | _          | -5                                                 |   |

| 3.4                                                                         | COMMAND            | REGISTER                                                                                                    | _                                         | -     | -   | -                                       | -     | -5   |                                         |                                       |      |       |      | -   |   | -                                       |     | _    |   |                                         | -   | -   |            | -5                                                 |   |

| 3.5                                                                         | COMMAND            | REGISTER                                                                                                    |                                           |       | ٠.  |                                         |       |      |                                         |                                       |      | 7/2/3 |      |     |   |                                         |     |      |   |                                         |     |     |            | 8-6                                                |   |

| 3.6                                                                         | COMMAND            | REGISTER                                                                                                    |                                           |       | ٠.  |                                         | 10:50 | 10 3 | - 53                                    | 700                                   | 0.00 | 100   | . 60 | E 6 |   | 11.2                                    | -   |      | - |                                         |     | 100 | 15         | 3-7                                                |   |

| 3.7                                                                         |                    | REGISTER                                                                                                    | -                                         | S (5) | 7   | 0.70                                    | 5050  |      |                                         | 70.7                                  |      | 7007  |      | - T | - |                                         |     | 27.0 |   | -                                       | 700 | -   | - 3        | 8-8                                                |   |

| 3.8                                                                         |                    | REGISTER                                                                                                    |                                           | • •   | • • | •                                       | • •   |      | •                                       | • •                                   | •    |       | •    |     | • | •                                       | • • | •    | • | •                                       | •   | • • | 175        | -9                                                 |   |

| 3.9                                                                         | STATUS 1           | REGISTER                                                                                                    | 2                                         |       |     |                                         |       |      |                                         |                                       |      |       |      |     |   |                                         |     |      |   |                                         |     |     | - 3        | 3-1                                                | ſ |

| CHAPT                                  | ER 4                                                            | PROGRA                                                   | AMMING THE DMA                                                                                                               |                                 |

|----------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | COMMAND<br>COMMAND<br>COMMAND<br>COMMAND<br>COMMAND<br>STATUS I | REGISTER<br>REGISTER<br>REGISTER<br>REGISTER<br>REGISTER | Ø       4         1       4         2       4         3       4         5       4         6       4         EGISTERS       4 | 1-3<br>1-5<br>1-6<br>1-9<br>1-9 |

|                                        |                                                                 |                                                          | AMMING THE CTC                                                                                                               |                                 |

|                                        |                                                                 |                                                          | REGISTER 5                                                                                                                   |                                 |

| 5.2                                    |                                                                 |                                                          | REGISTERS 5                                                                                                                  |                                 |

|                                        |                                                                 |                                                          | GISTERS 5                                                                                                                    |                                 |

| 5.4                                    | PROGRAM                                                         | MING BAUD                                                | RATES 5                                                                                                                      | -4                              |

| СНАРТ                                  | ER 6                                                            | PROGRA                                                   | AMMING THE PIO                                                                                                               |                                 |

| 6.1                                    | INTERRU                                                         | T VECTOR                                                 | REGISTER                                                                                                                     | 5-2                             |

| 6.2                                    |                                                                 |                                                          | Ø 6                                                                                                                          |                                 |

| 6.3                                    |                                                                 |                                                          | 1 6                                                                                                                          |                                 |

| 6.4                                    |                                                                 |                                                          | 2 6                                                                                                                          |                                 |

## CHAPTER 1

# PROGRAMMING THE CPU

significantly The Z-8Ø differs from microprocessors in its register configuration, instruction set, and interrupt response. Advantages of the Z-80 include a duplicate set of accumulator, flag, and general purpose registers, a large instruction set including the 78 8080 instructions, and a powerful daisy-chain interrupt mode supported by the Z-80 family peripherals. The essential information for CPU programming is provided in this section; for supplementary information see any of the numerous with Z-8Ø readily-available publications dealing programming.

#### 1.1 THE CPU REGISTERS

The Z-80 CPU has four 16-bit and eighteen 8-bit program-accessible registers, as indicated in Figure 1.1. Descriptions of the registers follow.

#### 1.1.1 Accumulator (A) and Flag (F) Registers

The two 8-bit accumulators A and A' hold the result of arithmetic and logical operations while their associated flag registers indicate the special results of such operations. A single exchange instruction allows the programmer to work with either pair of registers.

|                       |                      | A                 | F          | MAIN SET      |            |

|-----------------------|----------------------|-------------------|------------|---------------|------------|

|                       |                      | ACCUMULATOR<br>A' | FLAG<br>F' | ALTERNATE S   | ET         |

|                       |                      |                   | <b>^</b> [ | В             | С          |

| INTERRUPT<br>VECTOR I | MEMORY<br>REFRESH MR |                   | MAIN SET   | D             | E          |

| PROGRAM (             | COUNTER PC           |                   | <b>\</b> [ | н             | L          |

| STACK P               | OINTER SP            |                   |            | В'            | c,         |

| INDEX RE              | GISTER IX            | ALTE              | ERNATE SET | D'            | E'         |

| INDEX RE              | GISTER IY            |                   | Li         | н′            | Ľ          |

| DECIAL BURD           | OSE REGISTERS        | _                 |            | GENERAL PURPO | SE REGISTI |

FLAG

ACCUMULATOR

FIGURE 1.1. Z-80 REGISTERS

#### 1.1.2 Special Purpose Registers

Program Counter (PC)--This 16-bit register holds the memory address of the current instruction. The PC is automatically incremented after its contents have been transferred to the address lines. A program jump overrides the incrementer and places a new value in the PC.

Stack Pointer (SP)--This 16-bit register holds the address of the current top of a stack located anywhere in external RAM memory. The PUSH and POP instructions push data from specific registers onto the stack or pop the data off the stack into specific registers.

Index Registers (IX and IY) -- These two independent 16-bit registers hold a base address that is used in indexed addressing modes. This base address is used in conjunction with a displacement byte (a two's complement integer) in an indexed instruction to specify a location in memory.

Interrupt Page Address Register (I) -- This register is used in interrupt response mode 2. The register stores the high order 8-bits of the indirect address; the interrupting device provides the lower 8-bits.

Memory Refresh Register (R)--This register is the counter register for dynamic memory refresh. It holds the refresh address placed on the address bus during the last two clock cycles of every Ml cycle. The address is automatically incremented. You would not normally access this register, but can load it for testing purposes.

#### 1.1.3 General Purpose Registers

The general purpose registers consist of primary and alternate sets of six 8-bit registers. They can be used as individual 8-bit registers or as 16-bit register pairs. The primary pairs are BC, DE, and HL; the alternate pairs are BC', DE', and HL'. A single exchange command allows the programmer to switch from one set to the other.

#### 1.2 CPU INTERRUPT MODES

The Z-80 CPU is capable of three modes of maskable interrupt response; the mode in which the CPU operates at a given time is determined by software. The three modes are as follows:

Mode Ø--This mode is identical to the 8080A interrupt response mode. Data put onto the bus by the interrupting device is interpreted as an instruction by the CPU and immediately executed. The CPU will be in this mode after any system reset.

Mode 1--In this mode the CPU responds to an interrupt by executing a restart to location 0038h.

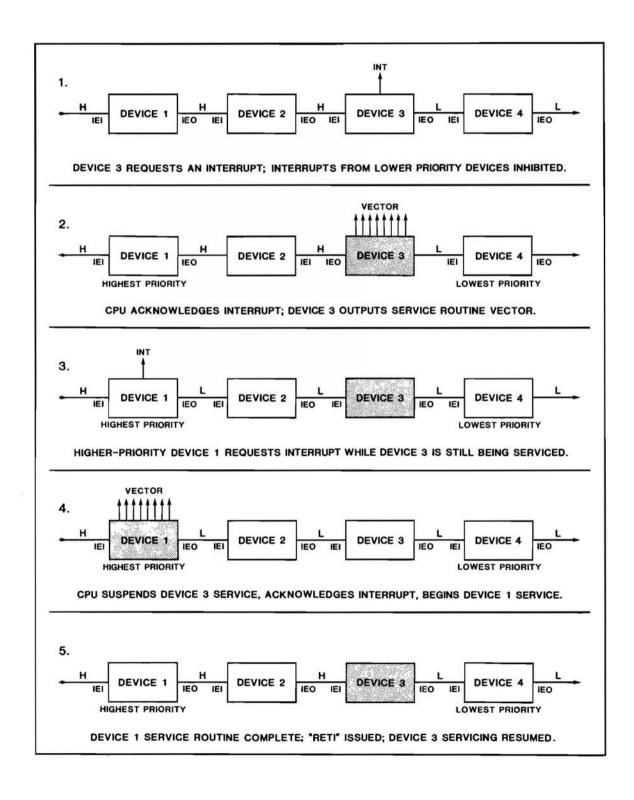

Mode 2--This powerful mode takes advantage of the Z-80 family interrupt daisy chain capabilities. If a Z-80 device has requested an interrupt (and

no higher-priority device has also requested an interrupt), it puts an 8-bit interrupt vector on the bus when the CPU acknowledges the interrupt. The CPU then reads the next instruction from the two contiguous locations specified by the register (high byte) and the byte put on the data bus by the interrupting device (low byte; bit  $\emptyset$  = The I register is programmable, allowing the programmer to dedicate any page of memory for an interrupt service routine table. The interrupt vectors for the various devices are programmable; in addition, some devices modify the interrupt vector according to the cause of the interrupt. In order to allow time for interrupt daisy chain to implement its priority control, two wait states are inserted in all interrupt acknowledge cycles.

Figure 1.2 illustrates Mode 2 Interrupt operation.

The Z-80 responds to non-maskable interrupts by saving the current contents of the PC register on the stack, ignoring the data bus, and executing a call to location 0066h.

#### 1.3 Z-8Ø INSTRUCTION SET

The Z-80 instruction set includes the 78 8080 instructions plus 80 additional instructions. The 8080-compatible instructions use the same object codes, but different mnemonics. Programs written in 8080 code can be duplicated in Z-80 code, but because of the 80 additional instructions Z-80 can often perform the same functions using fewer bytes than the 8080.

FIGURE 1.2. Z-80 MODE 2 INTERRUPT DAISY CHAIN OPERATION

#### 1.3.1 ABBREVIATIONS USED IN THE INSTRUCTION SET TABLE

addr A 16-bit memory address.

label A 16-bit memory address represented by a

mnemonic.

port An 8-bit port address.

data Single-byte data.

data 16 Double-byte data.

req One of the eight-bit registers A, B, C, D,

E, H, L.

regd, regs Destination register, source register.

One of the register pairs AF, BC, DE, HL. pr

One of the register pairs BC, DE, HL, SP. rp

One of the register pairs specified in the rr

operation description.

Denotes an alternate register or register

pair: e.g., AF'.

A The Accumulator.

F The Program Status Register

R The Refresh Register.

IV The Interrupt Vector Register.

IX, IY The 16-bit Index Registers.

PC The Program Counter.

SP The Stack Pointer.

B7, BØ, etc. Individual bits of an eight-bit register.

() The operand is the contents of the memory

location addressed by the contents of

the enclosed location.

#### Flags:

C Carry status

Z Zero status

S Sign status

P/O Parity/Overflow status

AC Auxiliary Carry status

N Subtract status

#### Symbols Used in Flag Columns:

(blank) Flag not affected by operation

X Flag affected by operation

1 Flag set by operation

Ø Flag reset by operation

? Flag unknown after operation

P Flag shows parity status

O Flag shows overflow status

I Flag shows interrupt enable status

#### Conditions:

Zero flag = 1  $\mathbf{z}$ NZ Zero flag = Ø C Carry flag = 1 NC Carry flag =  $\emptyset$ PO Parity flag =  $\emptyset$  (Odd) Parity flag = 1 (Even) PE P Sign flag =  $\emptyset$  (Positive) M Sign flag = 1 (Minus)

The format of the Program Status Word is shown below. Blank bits are not used.

| 7 | 6 | 5 | 4  | 3 | 2   | 1 | Ø |

|---|---|---|----|---|-----|---|---|

| S | Z |   | AC |   | P/0 | N | C |

# 1.3.2 INSTRUCTION SET TABLE

| I/O INST | I/O INSTRUCTIONS |       |       |             |     |            |     |          |   |                                                                                                                                           |

|----------|------------------|-------|-------|-------------|-----|------------|-----|----------|---|-------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC | OPERAND(S)       | BYTES | OBJEC | OBJECT CODE | 2 2 | S          | P/0 | AC       | z | OPERATION                                                                                                                                 |

| NI       | A, port          | 2     | DB yy |             |     |            |     |          |   | Input to A from I/O port addressed by A7-A0.                                                                                              |

| NI       | reg,(C)          | 7     | ED    |             | ×   | ×          | Δ,  | ×        | 0 | Input to register from port addressed by C.                                                                                               |

| INIR     |                  | 2     | ED B2 |             | -   | <b>C</b> - | ~   | <b>~</b> | - | Block transfer from port addressed by C to memory addressed by incrementing HL. Stop when B, which decrements after each byte, reaches 0. |

| INDR     |                  | 7     | ED BA | _           | H   | ~          | ~   | ~        | - | Block transfer from port addressed by C to memory addressed by decrementing HL. Stop when B, which decrements after each byte, reaches 0. |

| INI      |                  | 7     | ED A2 |             | ×   | ~          | ~   | ~        | п | Transfer byte from port addressed by C to memory addressed by HL. Increment HL, decrement B.                                              |

| IND      |                  | 7     | ED AA |             | ×   | ~          | ~   | ~        | - | Transfer byte from port addressed by C to memory addressed by HL. Decrement HL, decrement B.                                              |

| TUO      | port, A          | 7     | D3 yy |             |     |            |     |          |   | Output from A to I/O port addressed by A7-A0.                                                                                             |

| TUO      | (C), reg         | 2     | ED 01 | 01888001    |     |            |     |          |   | Output from register to port addressed by C.                                                                                              |

| OTIR     |                  | 2     | ED B3 |             | -   | ~          | ~   | ~        | - | Block transfer to port addressed by C from memory addressed by incrementing HL. Stop when B, which decrements after each byte, reaches 0. |

| OTDR     |                  | 7     | ED BB |             | 1   | ~          | ~   | ~        | - | Block transfer to port addressed by C from memory addressed by decrementing HL. Stop when B, which decrements after each byte, reaches 0. |

| OUTI     |                  | 2     | ED A3 |             | ×   | <b>~</b>   | ~   | <b>~</b> | г | Transfer byte to port addressed by C from memory addressed by HL. Increment HL, decrement B.                                              |

| OUTD     |                  | 7     | ED AB |             | ×   | ~          | ~   | <b>~</b> | - | Transfer byte to port addressed by C from memory addressed by HL. Decrement HL, decrement B.                                              |

|          |                  |       |       |             |     |            |     |          |   |                                                                                                                                           |

|          |                  |       |       |             |     |            |     |          |   |                                                                                                                                           |

|          |                  |       |       |             |     |            |     |          |   |                                                                                                                                           |

|          |                  |       |       |             |     |            |     |          | 7 |                                                                                                                                           |

| IMMEDIA        | IMMEDIATE LOAD INSTRU                                                            | STRUC  | CTIONS                                                                           |     |    | ŝ   |     |                                          |                                                                             |

|----------------|----------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------|-----|----|-----|-----|------------------------------------------|-----------------------------------------------------------------------------|

| MNEMONIC       | OPERAND(S)                                                                       | BYTES  | OBJECT CODE                                                                      | C   | ß  | P/0 | AC. | N                                        | OPERATION                                                                   |

| ED             | reg, data                                                                        | 8      | 00dddll0 yy                                                                      |     |    |     |     | 3                                        | Load data into specified register.                                          |

| 9              | rp,data 16                                                                       | Э      | 68xx6881 yyyy                                                                    |     |    |     |     | 3                                        | Load two data bytes into specified register pair.                           |

| 99             | IX,data 16<br>IY,data 16                                                         | 44     | DD 21 yyyy<br>FD 21 yyyy                                                         |     |    |     |     | 3                                        | Load two data bytes into specified index.                                   |

| 3              | (HL), data                                                                       | 7      | 36 yy                                                                            |     |    |     |     | St                                       | Store data in memory addressed by HL.                                       |

| LD             | (IX+disp), data<br>(IX+disp), data                                               | 4 4    | DD 36 yy yy<br>PD 36 yy yy                                                       | 9   | 3  |     |     | St                                       | Store data in memory addressed relative to index.                           |

| REGISTER,      | REGISTER/MEMORY LOAD                                                             |        | NSTRUCTIONS                                                                      |     |    |     |     |                                          |                                                                             |

| MNEMONIC       | OPERAND(S)                                                                       | BYTES  | OBJECT CODE                                                                      | 2 2 | S  | P/0 | AC  | N OP                                     | OPERATION                                                                   |

| T.D            | A, (addr)                                                                        | 3      | 3A ppqq                                                                          |     |    |     |     | 2                                        | Load A from directly addressed memory.                                      |

| CJ.            | BC, (addr) DE, (addr) HL, (addr) SP, (addr) IX, (addr) IY, (addr)                | 440444 | ED 01xx1011 ppqq ED 01xx1011 ppqq 2A ppqq ED 01xx1011 ppqq DD 2A ppqq FD 2A ppqq |     |    |     |     | or o | Load specified pair of registers from directly addressed memory.            |

| r <sub>D</sub> | (addr), A                                                                        | e      | 32 ppqq                                                                          |     |    |     |     | St                                       | Store A contents in directly addressed memory.                              |

| <b>G</b>       | (addr), BC<br>(addr), DE<br>(addr), HL<br>(addr), SP<br>(addr), IX<br>(addr), IX | 444444 | ED 43 ppqq<br>ED 53 ppqq<br>22 ppqq<br>ED 73 ppqq<br>DD 22 ppqq<br>FD 22 ppqq    |     |    |     |     | St q1                                    | Store contents of specified register pair in directly addressed memory.     |

| CD.            | A, (BC)<br>A, (DE)                                                               |        | 0A<br>1A                                                                         |     |    |     |     | J &                                      | Load A with contents of memory addressed by specified register pair.        |

| 9              | reg, (HL)                                                                        | -      | Ø1ddd110                                                                         |     | 39 |     |     | J E                                      | Load specified register with contents of memory addressed by HL.            |

| Э              | (BC),A<br>(DE),A                                                                 |        | 62<br>12                                                                         |     |    |     |     | s t                                      | Store contents of A in memory addressed by specified register pair.         |

| CD             | (HL),reg                                                                         | ,      | 01110sss                                                                         | -   |    | 12  |     | St.                                      | Store contents of specified register in memory addressed by contents of HL. |

| Store contents of memory addressed relative to index in specified register.  Store contents of specified register in memory addressed relative to index. | N OPERATION                 | Transfer block from memory addressed by HL to memory addressed by DE, incrementing both and decrementing BC with each byte. Stop when BC reaches 0. | Transfer block from memory addressed by HL to memory addressed by DE, decrementing both and decrementing BC with each byte. Stop when BC reaches 0. | Transfer byte from memory addressed by HL to memory addressed by DE, incrementing both and decrementing BC. | Transfer byte from memory addressed by HL to memory addressed by DE, decrementing both and decrementing BC. | Compare A contents with memory block addressed by incrementing HL. Decrement BC with each byte. Stop on match or BC contents 0. | Compare A contents with memory block addressed by decrementing HL. Decrement BC with each byte. Stop on match or BC contents Ø. | 1 Compare A contents with memory byte addressed by HL. Increment HL and decrement BC. | Compare A contents with memory byte addressed by HL. Decrement Hl and BC. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                                                                                                                                          | AC N                        | p                                                                                                                                                   |                                                                                                                                                     |                                                                                                             |                                                                                                             | -                                                                                                                               |                                                                                                                                 | ×                                                                                     | ×                                                                         |

| 1 1                                                                                                                                                      | P/0                         | 6                                                                                                                                                   | 6                                                                                                                                                   | 60                                                                                                          | 60                                                                                                          | ×                                                                                                                               | ×                                                                                                                               |                                                                                       |                                                                           |

|                                                                                                                                                          | S P/                        | ~                                                                                                                                                   | 6                                                                                                                                                   | ×                                                                                                           | ×                                                                                                           | ×                                                                                                                               | ×                                                                                                                               | ×                                                                                     | *                                                                         |

|                                                                                                                                                          | 8                           | ·                                                                                                                                                   |                                                                                                                                                     |                                                                                                             |                                                                                                             | ×                                                                                                                               | ×                                                                                                                               | ×                                                                                     | ×                                                                         |

|                                                                                                                                                          | υ                           |                                                                                                                                                     |                                                                                                                                                     |                                                                                                             |                                                                                                             |                                                                                                                                 |                                                                                                                                 | 5.70                                                                                  |                                                                           |

| DD @ldddll@ yy<br>FD @ldddll@ yy<br>DD @lll@sss                                                                                                          | NSTRUCTIONS S OBJECT CODE   | ED 86                                                                                                                                               | ED 88                                                                                                                                               | ED AØ                                                                                                       | ED A8                                                                                                       | ED B1                                                                                                                           | ED B9                                                                                                                           | ED A1                                                                                 | ED A9                                                                     |

| <b>ოო ოო</b>                                                                                                                                             | ER IN                       | 7                                                                                                                                                   | 7                                                                                                                                                   | 7                                                                                                           | 8                                                                                                           | 8                                                                                                                               | 7                                                                                                                               | 7                                                                                     | 8                                                                         |

| reg, (IX+disp) reg, (IX+disp) (IX+disp), reg (IX+disp), reg                                                                                              | SEARCH/TRANSF<br>OPERAND(S) |                                                                                                                                                     |                                                                                                                                                     |                                                                                                             |                                                                                                             |                                                                                                                                 |                                                                                                                                 |                                                                                       |                                                                           |

| 9 9                                                                                                                                                      | BLOCK                       | LDIR                                                                                                                                                | LDDR                                                                                                                                                | LDI                                                                                                         | CDD                                                                                                         | CPIR                                                                                                                            | CPDR                                                                                                                            | CPI                                                                                   | CPD                                                                       |

| REGISTER | REGISTER LO           | NAD IN | REGISTER/REGISTER LOAD INSTRUCTIONS |     |   |     |   |      |        |                                                                           |

|----------|-----------------------|--------|-------------------------------------|-----|---|-----|---|------|--------|---------------------------------------------------------------------------|

| MNEMONIC | OPERAND(S)            | BYTES  | OBJECT CODE                         | 2 2 | S | P/0 |   | AC N |        | OPERATION                                                                 |

| g        | regd, regs            | 1      | Øldddsss                            |     |   |     |   |      | æ *0   | Move contents of source register to destination register.                 |

| 23       | A, IV                 | 7      | ED 57                               | ×   | × | н   | 0 |      | Σ      | Move contents of Interrupt Vector register to A.                          |

| 3        | A, R                  | 7      | ED 5F                               | ×   | × | I   | 6 |      | Σ<br>Σ | Move contents of Refresh register to A.                                   |

| C.D      | IV, A                 | 7      | ED 47                               |     |   |     |   |      | 1      | Load Interrupt Vector register with A contents.                           |

| 3        | R,A                   | 8      | ED 4F                               |     |   |     |   |      | П      | Load Refresh register with contents of A.                                 |

| 3        | SP, HL                | -      | P.9                                 |     |   |     |   |      | Σ      | Move contents of HL to Stack Pointer.                                     |

| Э        | SP, IX<br>SP, IY      | 0.0    | DD F9<br>FD F9                      |     |   |     |   |      | E      | Move contents of index register to Stack Pointer.                         |

| EX       | DE, HL                | 1      | EB                                  |     |   |     |   |      | E      | Move contents of HL to DE.                                                |

| EX       | AF, AF                | ٦      | 80                                  |     |   |     |   |      | ы      | Exchange primary and alternate program statuses.                          |

| EXX      |                       | 1      | D9                                  |     |   |     |   |      | ыm     | Exchange primary and alternate register pairs BC, DE, and HL.             |

| STACK 1  | STACK INSTRUCTIONS    | S      |                                     |     |   |     |   |      |        |                                                                           |

| MNEMONIC | OPERAND(S)            | BYTES  | OBJECT CODE                         | 2 2 | S | P/0 |   | AC N |        | OPERATION                                                                 |

| PUSH     | pr                    | 7      | 11xx010                             |     |   |     |   |      | 0.0    | Put contents of specified register pair on top of stack and decrement SP. |

| PUSH     | IX                    | 88.    | DD E5<br>FD E5                      |     |   |     |   |      | Δ. 6   | Put contents of index on top of stack and decrement SP.                   |

| POP      | þr                    | ı      | 11xx0001                            |     |   |     |   |      | ΩĤ     | Put contents of top of stack in specified register pair and increment SP. |

| POP      | XX                    | 7 7    | DD E1<br>DD E1                      |     |   |     |   |      | ₽.4    | Put contents of top of stack in index and increment SP.                   |

| EX       | (SP),HL               | -      | E3                                  |     |   |     |   |      | ы      | Exchange contents of SP and HL.                                           |

| EX       | XI,(SP),IX<br>(SP),IX | 77     | DD E3<br>FD E3                      |     |   |     |   |      | ш      | Exchange contents of SP and index.                                        |

|          |                       |        |                                     |     |   |     |   |      |        |                                                                           |

| IMMEDIATE OPERATE INSTRU     | UCTIONS<br>OBJECT CODE | υ | ы. | S P | P/0 | AC. | z   | OPERAND(S) OPERATION                                                                  |

|------------------------------|------------------------|---|----|-----|-----|-----|-----|---------------------------------------------------------------------------------------|

| 5                            | C6 yy                  | × | ×  | ×   | 0   | ×   | 6   | data Add data to A. No Carry.                                                         |

| 70                           | CE yy                  | × | ×  | ×   | 0   | ×   | 0   | data Add data to A. Carry.                                                            |

| _                            | D6 yy                  | × | ×  | ×   | 0   | ×   | 69  | data Subtract data from A. No Carry.                                                  |

| 2                            | DE YY                  | × | ×  | ×   | 0   | ×   | 0   | data Subtract data from A. Carry.                                                     |

| 170                          | E6 yy                  | 0 | ×  | ×   | Δ,  | -   | 100 | data And data with A.                                                                 |

| 2                            | F6 yy                  | 8 | ×  | ×   | Δ,  | 7   | 0   | data OR data with A.                                                                  |

| -                            | EE yy                  | 0 | ×  | ×   | Δ,  | н   | -   | data Exclusive-OR data with A.                                                        |

| 20                           | FE yy                  | × | ×  | ×   | 0   | ×   | _   | data Compare data with A. Only flags are affected.                                    |

| REGISTER OPERATE INSTRUCTION | IONS                   |   |    |     |     |     |     |                                                                                       |

| BYTES                        | OBJECT CODE            | υ | 2  | S   | P/0 | AC  | z   | OPERATION                                                                             |

|                              | 27                     | × | ×  | ×   | Q.  | ×   |     | Decimal adjust A, assuming that A contents are the sum or difference of BCD operands. |

|                              | 2F                     |   |    |     |     | 1   | 7   | Complement Accumulator (ones complement).                                             |

|                              | ED 44                  | × | ×  | ×   | 0   | ×   | 7   | Negate Accumulator (twos complement).                                                 |

| _                            | 00xxx100               |   | ×  | ×   | 0   | ×   | 0   | Increment contents of specified register.                                             |

| _                            | 00xx0011               |   |    |     |     |     |     | Increment contents of specified register pair.                                        |

|                              | DD 23<br>FD 23         |   |    |     |     |     |     | Increment contents of index register.                                                 |

|                              | 00xxx101               |   | ×  | ×   | 0   | ×   | -   | Decrement contents of specified register.                                             |

| _                            | 00xx1011               |   |    |     |     |     |     | Decrement contents of specified register pair.                                        |

|                              | DD 2B<br>FD 2B         |   |    |     |     |     |     | Decrement contents of index register.                                                 |

|                              |                        |   |    |     |     |     |     |                                                                                       |

|                           | OPERATION   | Add contents of specified register to A. No carry. | Add contents of specified register to A. Carry. | Subtract contents of specified register from A. No Carry. | Subtract contents of specified register from A. Carry. | AND A with contents of specified register. | OR A with contents of specified register. | Exclusive-OR A with contents of specified register. | Compare contents of A and of specified register. Only flags are affected. | Add contents of specified register pair to contents of HL. No Carry. | Add contents of specified register pair to contents of HL. Carry. | Subtract contents of specified register pair from contents of HL. Carry. | Add contents of specified register pair (BC, DE, SP, other index) to contents of index. No Carry. |                         | OPERATION   | Add to A the contents of memory addressed by HL. No Carpy. | Add to A the contents of memory addressed relative to index. No Carry. | Add to A the contents of memory addressed by HL. Carry. |

|---------------------------|-------------|----------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------|--------------------------------------------|-------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------|-------------|------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------|

|                           | N           | 0                                                  | 0                                               | г                                                         | 1                                                      | 0                                          | 0                                         | 0                                                   | н                                                                         | 0                                                                    | 0                                                                 | 1                                                                        | 0                                                                                                 |                         | z           | 0                                                          | 0                                                                      | 0                                                       |

|                           | AC          | ×                                                  | ×                                               | ×                                                         | ×                                                      | 7                                          | 7                                         | 1                                                   | ×                                                                         | ~                                                                    | ~                                                                 | 2                                                                        | ~                                                                                                 |                         | AC          | ×                                                          | ×                                                                      | ×                                                       |

| ĺ                         | P/0         | 0                                                  | 0                                               | 0                                                         | 0                                                      | Q.                                         | Q,                                        | ď                                                   | 0                                                                         |                                                                      | 0                                                                 | 0                                                                        |                                                                                                   |                         | P/0         | 0                                                          | 0                                                                      | 0                                                       |

|                           | ဖ           | ×                                                  | ×                                               | ×                                                         | ×                                                      | ×                                          | ×                                         | ×                                                   | ×                                                                         |                                                                      | ×                                                                 | ×                                                                        |                                                                                                   |                         | w           | ×                                                          | ×                                                                      | ×                                                       |

|                           | Ŋ           | ×                                                  | ×                                               | ×                                                         | ×                                                      | ×                                          | ×                                         | ×                                                   | ×                                                                         |                                                                      | ×                                                                 | ×                                                                        |                                                                                                   |                         | 12          | ×                                                          | ×                                                                      | ×                                                       |

|                           | υ           | ×                                                  | ×                                               | ×                                                         | ×                                                      | Ø                                          | Ø                                         | 60                                                  | ×                                                                         | ×                                                                    | ×                                                                 | ×                                                                        | ×                                                                                                 |                         | υ           | ×                                                          | ×                                                                      | ×                                                       |

| INSTRUCTIONS              | OBJECT CODE | 10000xx                                            | 10001xxx                                        | 10010xxx                                                  | 10011xxx                                               | 10100xxx                                   | 10110xxx                                  | 10101xxx                                            | 10111xxx                                                                  | 00xx1001                                                             | ED Ølxx1010                                                       | ED ØlxxØØlØ                                                              | DD 00xx1001<br>FD 00xx1001                                                                        | INSTRUCTIONS            | OBJECT CODE | 98                                                         | DD 86 yy<br>FD 86 yy                                                   | 8.5                                                     |

| PERATE                    | BYTES       | 1                                                  | 1                                               | 1                                                         | 1                                                      | 1                                          | 1                                         | 1                                                   | -                                                                         | 1                                                                    | 7                                                                 | 7                                                                        | 2 2                                                                                               | PERATE                  | BYTES       | 1                                                          | ოო                                                                     | 1                                                       |

| REGISTER/REGISTER OPERATE | OPERAND(S)  | reg                                                | reg                                             | reg                                                       | reg                                                    | reg                                        | reg                                       | reg                                                 | reg                                                                       | HL, rp                                                               | HL, rp                                                            | HL, rp                                                                   | IX, rr<br>IY, rr                                                                                  | REGISTER/MEMORY OPERATE | OPERAND(S)  | (нг)                                                       | (IX+disp)                                                              | (HL)                                                    |

| REGISTER                  | MNEMONIC    | ADD                                                | ADC                                             | SUB                                                       | SBC                                                    | AND                                        | OR                                        | XOR                                                 | 8                                                                         | ADD                                                                  | ADC                                                               | SBC                                                                      | ADD                                                                                               | REGISTER                | MNEMONIC    | ADD                                                        | ADD                                                                    | ADC                                                     |

| MNEMONIC | OPERAND(S)             | BYTES | OBJ       | OBJECT CODE    | ODE        | υ           | 2 | S | P/0 | AC  | z   | OPERATION                                                                               |

|----------|------------------------|-------|-----------|----------------|------------|-------------|---|---|-----|-----|-----|-----------------------------------------------------------------------------------------|

| ADC      | (IX+disp)<br>(IY+disp) | ee    | 50 E      | 8E yy<br>8E yy | Tigos too  | ×           | × | × | 0   | ×   | 60  | Add to A the contents of memory addressed relative to index. Carry.                     |

| SUB      | (нг)                   | -     | 96        |                |            | ×           | × | × | 0   | ×   | н   | Subtract from A the contents of memory addressed by HL. No Carry.                       |

| SUB      | (IX+disp)<br>(IY+disp) | ოო    | 95        | 96<br>96<br>77 | 25 44      | ×           | × | × | 0   | ×   | -   | Subtract from A the contents of memory addressed relative to index. No Carry.           |

| SBC      | (HF)                   | -     | 9E        |                |            | ×           | × | × | 0   | ×   | -   | Subtract from A the contents of memory addressed by HL. Carry.                          |

| SBC      | (IX+disp)<br>(IY+disp) | ოო    | 50 G      | 9E YY<br>9E YY | g, be      | ×           | × | × | 0   | × · | г   | Subtract from A the contents of memory addressed relative to index. Carry.              |

| AND      | (HL)                   | τ     | A6        |                |            | Ø           | × | × | O.  | ı   | 8   | AND A with the contents of memory addressed by HL.                                      |

| AND      | (IX+disp)<br>(IX+disp) | ოო    | 98        | A6 yy<br>A6 yy | SECURE     | <b>6</b> 0, | × | × | ď   | ч   | 0   | AND A with the contents of memory addressed relative to index.                          |

| OR       | (HL)                   | 1     | 96        |                |            | 0           | × | × | Д   | 1   | 0   | OR A with the contents of memory addressed by HL.                                       |

| OR       | (IX+disp)<br>(IX+disp) | ოო    | 85        | B6 yy<br>B6 yy | 11-2-160   | 6           | × | × | O.  | -   | 0   | OR A with the contents of memory addressed relative to index.                           |

| XOR      | (HL)                   | 1     | AE        |                |            | 0           | × | × | Δ.  | ٠,  | 100 | Exclusive-OR A with memory addressed by HL.                                             |

| XOX      | (IX+disp)              | ოო    | 96        | AE YY          | 92.06      | 20          | × | × | Q.  | -   | 20  | Exclusive-OR A with the contents of memory addressed relative to index.                 |

| G.       | (HF)                   | н     | BE        |                |            | ×           | × | × | 0   | ×   | -   | Compare A with contents of memory addressed by HL. Only flags are affected.             |

| CP       | (IX+disp)<br>(IY+disp) | ოო    | 00<br>101 | BE YY<br>BE YY | *          | ×           | × | × | c   | ×   | ٦   | Compare A with contents of memory addressed relative to index. Only flags are affected. |

| INC      | (HL)                   | 1     | 34        |                |            |             | × | × | 0   | ×   | Ø   | Increment contents of memory addressed by HL.                                           |

| INC      | (IX+disp)<br>(IY+disp) | mе    | 55        | 34 yy<br>34 yy | t geologer |             | × | × | 0   | ×   | 8   | Increment contents of memory addressed relative to index.                               |

| DEC      | (HL)                   | 1     | 35        |                |            |             | × | × | 0   | ×   | 7   | Decrement contents of memory addressed by HL.                                           |

| DEC      | (IX+disp)<br>(IY+disp) | ოო    | 85        | 35 YY<br>35 YY | 31663-84   |             | × | × | 0   | ×   | п   | Decrement contents of memory addressed relative to index.                               |

|          |                        |       |           |                |            |             |   |   |     |     | 1   |                                                                                         |

|                           | P/O AC N OPERATION | 8 8 Rotate A left: B7 to B8 and Carry. | 8 8 Rotate A left: B7 to Carry, Carry to B8. | 8 8 Rotate A right: BØ to B7 and Carry. | 8 8 Rotate A right: BØ to Carry, Carry to B7. | P 0 0 Rotate contents of specified register left: B7 to B0 and Carry. | P 0 0 Rotate contents of specified register left:<br>B7 to Carry, Carry to B0. | P Ø Ø Rotate contents of specified register right: BØ to B7 and Carry. | P Ø Ø Rotate contents of specified register right: BØ to Carry, Carry to B7. | P 0 0 Shift contents of specified register left and clear B0. | p 0 0 Shift contents of specified register right: B7 to B7 and B6. | P 8 8 Shift contents of specified register right and clear B7. | P 6 B Rotate BCD digit left between A and memory addressed by HL: low nibble A to low nibble of memory, low nibble of memory to high nibble of memory to low nibble of High nibble of A unaffected. | Rotate BCD digit right between A and memory addressed by HL: low nibble A to high nibble of memory, high nibble of memory to low nibble of memory, low nibble of memory to low nibble of High nibble of A unaffected. |    |

|---------------------------|--------------------|----------------------------------------|----------------------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                           | S                  |                                        |                                              |                                         |                                               | ×                                                                     | ×                                                                              | ×                                                                      | ×                                                                            | ×                                                             | ×                                                                  | ×                                                              | ×                                                                                                                                                                                                   | ×                                                                                                                                                                                                                     |    |

|                           | 2                  |                                        |                                              |                                         |                                               | ×                                                                     | ×                                                                              | ×                                                                      | ×                                                                            | ×                                                             | ×                                                                  | ×                                                              | ×                                                                                                                                                                                                   | ×                                                                                                                                                                                                                     |    |

|                           | υ                  | ×                                      | ×                                            | ×                                       | ×                                             | ×                                                                     | ×                                                                              | ×                                                                      | ×                                                                            | ×                                                             | ×                                                                  | ×                                                              | ×                                                                                                                                                                                                   | ×                                                                                                                                                                                                                     |    |