# Model 2830 6 CHANNEL SERIAL I/O

# Reference Manual

MODIFIED TO USE PIN 25 (\$2) RATHER THAN PIN 24 (\$1) DUE TO 2810 CLOCK PHASE. AZSO MODIFIED TO PICK UP BAND RATE CLOCK FROM BUS PIN 70 SUPPLIED BY 2719 CTC CHANNEL Z

CCS MODEL 2830

SIX CHANNEL SERIAL I/O

Reference Manual

Copyright 1981

California Computer Systems

250 Caribbean Drive

Sunnyvale CA 94086

Copyright 1981 by California Computer Systems.

All rights reserved. No part of this publication may be reproduced in any form or by any means without express permission of California Computer Systems.

The information contained in this manual is believed to be correct at the time of publication. However, CCS assumes no liability resulting from the use of this publication.

Publication History:

Revision A printed August 1981 Revision B printed November 1981

Z-80™ is a trademark of Zilog, Inc.

# TABLE OF CONTENTS

| CHAP                                   | TER 1                                                                 | INTRODUCTION                                                                                                                                             |         |                                 |

|----------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4               | USING THIS SPECIFICAT:                                                | SCRIPTION MANUAL IONS DIAGRAM                                                                                                                            | • • • • | 1-1<br>1-2                      |

| CHAP                                   | TER 2                                                                 | CONFIGURING THE 2830                                                                                                                                     |         |                                 |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | THE PORT AI THE INTERRI 2.3.1 STAN 2.3.2 RECO SERIAL PORT THE CLOCK S | THE 2830 IN A SYSTEM 200/300/400 DDRESS SELECT JUMPERS UPT DAISY CHAIN HEADER NDARD CONFIGURATION ONFIGURATION T INTERFACE JUMPERS SELECT JUMPERS GROUND |         | 2-2<br>2-4<br>2-4<br>2-5<br>2-6 |

| CHAP'                                  | TER 3                                                                 | PROGRAMMING INFORMATION                                                                                                                                  |         |                                 |

| 3.1<br>3.2<br>3.3<br>3.4               | CTC 2830-UN PROGRAMMING                                               | UNIQUE PROGRAMMING CHARACTERISTICS NIQUE PROGRAMMING CHARACTERISTICS BAUD RATES                                                                          |         | 3-2<br>3-3                      |

| CHAP'                                  | rer 4                                                                 | HARDWARE DESIGN                                                                                                                                          |         |                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | ADDRESS DEC                                                           | CODING                                                                                                                                                   | • • •   | 4-2<br>4-5<br>4-5               |

| APPEI                                  | NDIX A                                                                | TECHNICAL INFORMATION                                                                                                                                    |         |                                 |

| A.5                                    | DART AND CT<br>ON-BOARD IN<br>RS-232-C CO<br>BUS CONNECT              | CEABLE PARTS  TO PINOUTS  TERFACE CONNECTOR PINOUTS  ONNECTOR PINOUTS  TOR PINOUTS                                                                       | • • •   | A-3<br>A-3<br>A-4               |

## CHAPTER 1

# INTRODUCTION

## 1.1 GENERAL DESCRIPTION

The CCS Model 2830 Six Channel Serial I/O Board employs three Z-80 DARTs (Dual Asynchronous Receiver/Transmitters) and a Z-30 CTC to provide six programmable serial ports with programmable baud rates. Designed to conform to the 696/D2 specifications for the S-100 bus, the 2830 also features a unique Z-80 Mode 2 Interrupt Daisv look-ahead scheme which significantly reduces the ripple time for long daisy chains, alleviating the need for states during Interrupt Acknowledge cycles. The base address οf the CTC and the three DARTS hardware-selectable at any multiple of 16 between Ø and 255. port interfaces, configured for DCE but easily reconfigured for DTE, meet EIA RS-232-C specifications.

### 1.2 USING THIS MANUAL

This manual is intended to provide information required by a variety of users in a variety of situations; most users will not find it necessary to read the entire manual. Chapter 2 deals with board configuration, and all users should consult this chapter. Chapter 3 discusses the 2830-unique programming requirements of the DARTs and CTC. Chapter 4 is a detailed discussion of the hardware design of the 2830, and is intended to be read in conjunction with frequent references to the Schematic/Logic Diagram in Appendix A. Various technical illustrations and tables are provided in Appendix A.

### 1.3 SPECIFICATIONS

## I/O INTERFACES:

Three Z-80 DARTs Provide Six

Asynchronous Serial Ports

Meets EIA RS-232-C Specifications,

Full or Partial Primary Channel

DARTs Replaceable with SIO/0s for

Synchronous Operation

Jumper-Enabled Handshake Options:

RS-232-C Lines 8, 11, 19

Easy DCE-to-DTE Reconfiguration

Programmable Baud Rates (Z-80 CTC)

#### SYSTEM INTERFACE:

S-100: Complies with IEEE Task 696.1/D2,

SLAVE AI F6 T300

Supports Z-80 Mode 0, 1, & 2 Interrupts

Supports IEEE/696 Use of VI\* Lines in

CCS-Unique Fast Interrupt Daisy Chain

Look-Ahead Scheme

Jumper-Selectable Board Base Address

Full Buffering of Bus-Driving Outputs,

Schmitt-Trigger Bus Receiver Inputs

### POWER:

+8 Volts Regulated On-Board to +5 Volts +16 Volts Regulated On-Board to +12 Volts -16 Volts Regulated On-Board to -12 Volts

Consumption: .50 Amps at +8 Volts

.05 Amps at +16 Volts .05 Amps at -16 Volts

Heat Burden: 81 gram-calories/minute

.34 BTU/minute

## **ENVIRONMENTAL REQUIREMENTS:**

Temperature: Ø to +7Ø C. (32 to 155 F.)

Humidity: Up to 90% Non-Condensing

INTRODUCTION 1-3

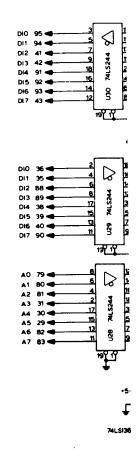

## 1.4 2830 BLOCK DIAGRAM

## **CHAPTER 2**

# **CONFIGURING THE 2830**

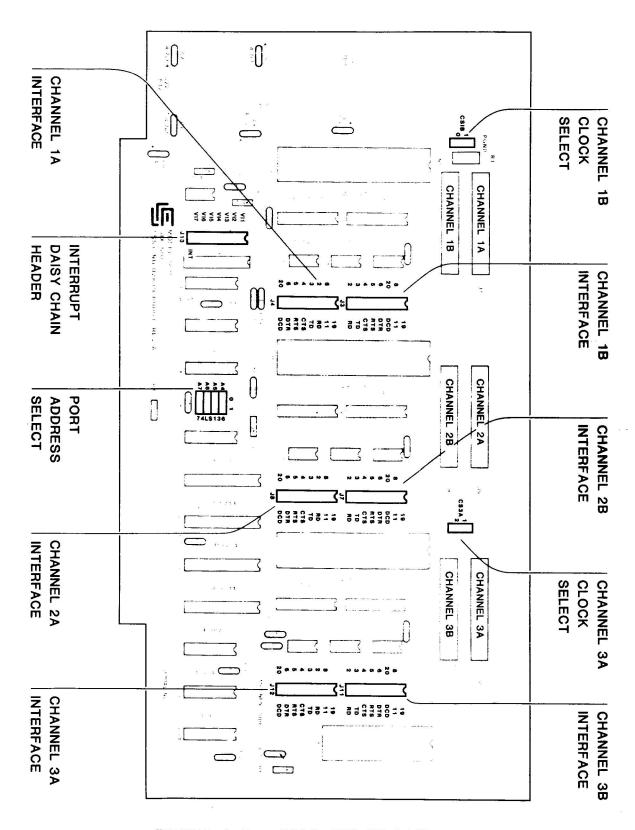

Several user-configurable options exist on the 2830: base address, port interface configuration, baud rate interrupt priority level, and interface protective ground. Protective ground for the port interfaces requires user-implementation in all systems in which terminals are to be connected to a different power source than the mainframe (including different wall outlets in the same building). used in the System 200/300/400 in standard configuration, only the protective ground option need be configured. However, in customized systems reconfiguration may be necessary. Instructions are provided in this chapter. Locations of the jumpers and headers on the 2830 are shown in Figure 2-1.

## 2.1 INSTALLING THE 2830 IN A SYSTEM 200/300/400

To install the 2830 in a CCS System 200/300/400, follow these step-by-step instructions:

- 1. Ensure that the Port Address Select Jumpers are set to 20H.

- 2. If you desire an interrupt priority level other than level 2, reconfigure the Interrupt Priority Header as described in Section 2.3.

- 3. Six I/O cables are supplied with the board. Connect one for each port you plan to bring up, making sure that the triangular pin 1 marks on the board and cable connectors match. See Figure 2-1 for port/connector correspondences.

- 4. Configure the Protective Ground, if required, as described in Section 2.6.

- 5. Install the board in the mainframe. For optimum performance, install the boards in adjacent slots in the following order: System Processor, Memory, Fast I/O (Disk Controllers), Slow I/O (including 2830), Termination. ALWAYS POWER DOWN THE SYSTEM BEFORE INSTALLING OR REMOVING BOARDS.

- 6. Fasten the I/O cable RS-232-C connectors to the back of the mainframe.

- 7. Install the appropriate cables between the mainframe and your peripherals. For instructions on setting up your peripheral, see your System User's Guide.

## 2.2 THE PORT ADDRESS SELECT JUMPERS

The settings of these jumpers select the base address of the CTC and I/O ports at any multiple of 16 (10H). These jumpers are set at the factory for a base address of 20H, which is the base address required by the CCS system software packages; thus the first 2830 used in a CCS System 300 or 400 should be left in the factory configuration. When the 2830 is used in other situations, however, a different base address may be desired. (Be sure that any other port address selected does not conflict with other port assignments in the system.) Consult Table 2-1 for the jumper settings for all possible base addresses.

Table 3-3 shows the relative addresses of the CTC Channels and DART data and command/status ports.

FIGURE 2-1. 2830 JUMPER LOCATIONS

TABLE 2-1. PORT BASE ADDRESSES

| JUMPER SETTINGS |    |             |    | BASE |      |  |

|-----------------|----|-------------|----|------|------|--|

| A7              | A6 | <b>A</b> 5  | A4 | HEX. | DEC. |  |

| 0               | 0  | 0           | 0  | 00   | 00   |  |

| 0               | 0  | 0           | 1  | 10   | 16   |  |

| 0               |    |             | 0  | 20   | 32   |  |

| 0 0             | 0  | 1           | 1  | 30   | 48   |  |

| 0               | 1  | 0           | 0  | 40   | 64   |  |

| 0               | 1  | 0           | 1  | 50   | 80   |  |

| 0               | 1  | 1           | 0  | 60   | 96   |  |

| 0               | 1  | 1           | 1  | 70   | 112  |  |

| 1               | 0  | 0           | 0  | 80   | 128  |  |

| 1               |    |             | 1  | 90   | 144  |  |

| 1               | 0  | 0<br>1<br>1 | 0  | AO   | 160  |  |

| 1               | 0  | 1           | 1  | B0   | 176  |  |

| 1               | 1  | 0           | 0  | CO   | 192  |  |

| 1               | 1  | 0<br>0<br>1 | 1  | DO   | 208  |  |

| 1               | 1  |             | 0  | EO   | 224  |  |

| 1               | 1  | 1           | 1  | FO   | 240  |  |

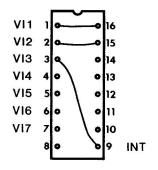

FIGURE 2-2. INTERRUPT HEATER

FIGURE 2-3. INTERFACE JUMPERS

## 2.3 THE INTERRUPT DAISY CHAIN HEADER

## 2.3.1 STANDARD CONFIGURATION

System 200/300/400 interrupt priorities may be determined at the system implementer's discretion, depending on system components and application. However, the priority scheme shown below is followed in the factory configuration of the interrupt priority headers for each system board, and should be appropriate for the majority of systems. The System Processor is hardwired for Level 0; it is the only board whose priority is fixed.

Level 0: 2820 System Processor

Level 1: 2805 Clock/ROM/Terminator

Level 2: 2830 Six-Channel Serial I/O

Level 3: 2 Parallel/2 Serial I/O

Level 4: 2831 Arithmetic Processor

Level 5: GPIB Interface

Level 6: 2832 Hard Disk Controller

Level 7: 2822 Floppy Disk Controller

Note that gaps are allowed in the priority structure; thus, it is not necessary to reconfigure a level 3 board to level 2 if there is no level 2 board in the system. However, no priority level may be occupied by more than one board. Header reconfiguration will be required if two of the same board are installed in a system. Priority swapping can be accomplished by swapping header plugs, except in the case of the 2832, which has a slightly different header configuration. For example, to put the 2830 at level 3 and the 2818 at level 2, simply exchange the header plugs supplied with the boards.

#### 2.3.2 RECONFIGURATION

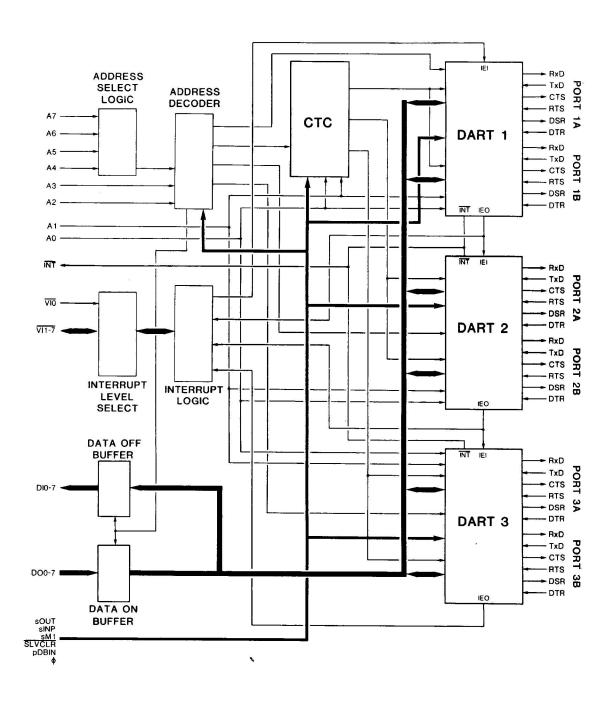

A Z-80 Mode 2 Interrupt Daisy Chain, when extended beyond four peripheral devices, requires look-ahead logic to devices are properly informed of that all higher-priority interrupts within the allotted time. Systems 200, 300, and 400 implement a unique look-ahead scheme in which: 1) each board participating in the daisy chain asserts its interrupt priority by forcing a given Vectored Interrupt bus line low; and 2) a board is prevented from interrupting when a lower-numbered VI\* line is low. there are nine interrupt priority levels, Ø-8; the priority Ø board controls VIØ\* and senses no lines, while the priority 8 board senses all VI\* lines and controls none. The Interrupt Daisy Chain Header, illustrated in Figure 2-2, allows the user to select the interrupt priority level (1-8) of the 2830 by selecting which VI\* line(s) the board will be sensitive to and which VI\* line it will pull low when an on-board device requests an interrupt.

To configure the header:

- 1. Tie the pins corresponding to higher-priority (lower-numbered) VI\* lines straight across (pin 1 to pin 16, pin 2 to pin 15, etc);

- 2. Tie the pin corresponding to the 2830's priority-assertion line to the INT pin (pin 9);

- 3. Leave unconnected all lower-priority VI pins.

Note that the highest priority level to which the 2830 may be assigned is 1. The board is hardwired to sense the VIO\* line, which is reserved as the 2820 System Processor's priority-assertion line. Figure 2-2 shows the header configured for interrupt priority level 3.

## 2.4 SERIAL PORT INTERFACE JUMPERS

The Serial Port Interfaces are hardwired for the DCE configuration (board emulates a modem), but may be reconfigured for DTE (board emulates a terminal). To re-configure, first cut the existing traces which connect the pads straight across (on the component side of the board). Jumper wires may be soldered directly to the jumper pads, but we recommend that you install a 16-pin DIP header with cover. On the header plug, install jumper wires so that pins 3-14 are connected crosswise, as illustrated in Figure 2-3.

Some terminal devices, notably printers, use lines other than RTS, CTS, DTR, and DSR for handshaking. To ensure compatibility with these devices, we have provided pins allowing RS-232-C lines 8 (RLSD), 11 (Unassigned), and 19 (SRTS) to be jumpered to replace other handshake lines as required. Consult your peripheral manual to determine handshaking requirements.

### 2.5 THE CLOCK SELECT JUMPERS

In the standard configuration, baud rates for DARTS 1, 2, and 3 are determined by CTC Channels 0, 1, and 2 respectively. The Clock Select 1B and 3A jumper pads allow the user to select CTC Channel 1 as the baud rate source for DART Channel 1B and/or DART Channel 3A. This frees DART Channels 1A and 3B for independent or variable baud rate applications (e.g., use with a modem requiring 110, 300, and 1200 baud at different times). To select Channel 1 as the baud rate source for either DART Channel 1B or DART Channel 3A, cut the trace between the pair of pads labeled 0 (jumper CS1B) or 2 (jumper CS3A) and install a jumper wire between the pair of pads labeled 1.

#### 2.6 PROTECTIVE GROUND

Protective Ground is defined as the supply current return path, not a signal current return path. It is intended to equalize the voltage potential of the terminal and the mainframe, and should be implemented whenever the terminal and the mainframe are connected to different power sources which may have different ground potentials. If all terminals interfaced through the 2830 are to be connected to the same outlet as the mainframe, the protective ground feature need not be implemented.

Next to the CS1B jumper pads are two jumper pads labeled PGND and SGND. These allow the user to select of two implementations of the RS-232-C interface Protective Ground signals for all ports. The recommended implementation is to run a green wire from the PGND pad to the mainframe chassis, with an alligator clip or other convenient method for connection. This conforms to the RS-232 design specifications, ensuring that terminal mainframe have the same potentials. Use this method with CCS-supplied terminals. Some terminals, however, Protective Ground and Signal Ground together or use the protective ground as the signal ground. If you are using such a terminal with the 2830, you will need to install a 100 ohm, 1/4 Watt resistor (as per EIA standard RS-422-A) between the PGND and SGND pads.

# CHAPTER 3

# PROGRAMMING INFORMATION

Programming options for the Z-80 DART and CTC are quite Complete instructions are given in the Z-80Family Programming Guide included in CCS documentation packages. Users of the 2830 who do not own a copy of the CCS Programming Guide may order a copy or find programming instructions in a variety of equivalent publications, a few of which are listed below. This chapter deals with programming limitations and requirements stemming from the implementation of the Z-80 DART and CTC on 2830.

AN INTRODUCTION TO MICROCOMPUTERS, Osborne and Associates, Inc. (Berkeley, CA: 1978).

ZILOG MICRCOMPUTER COMPONENTS DATA BOOK, Zilog, Inc. (Cupertino, CA: 1980).

MOSTEK MICROCOMPUTER DATA BOOK, Mostek Corporation (Carollton, TX: 1979).

SGS Z-80 MICROCOMPUTER SYSTEM, SGS-ATES Componenti Elettronici SpA (Agrate Brianza, Italy: 1981).

## 3.1 DART 2830-UNIQUE PROGRAMMING CHARACTERISTICS

Table 3-1 shows which DART pins are connected to which RS-232-C lines. The programmer should keep in mind that command and status bits in the programming guide are named for the DART pin and not the RS-232-C interface line--for example, the RTS command bit actually controls the CTS interface line when the board is in the standard DCE configuration.

| DAI   | RT                | `RS- | -232-0 | 2    |

|-------|-------------------|------|--------|------|

| PIN   | SIGNAL            | PIN  | SIGNAL |      |

| 15/26 | TxD               | 3    | RD     | (BB) |

| 12/28 | $R_{\mathbf{X}}D$ | 2    | TD     | (BA) |

| 17/24 | RTS               | 5    | CTS    | (CB) |

| 18/23 | CTS               | 4    | RTS    | (CA) |

| 16/25 | DTR               | 6    | DSR    | (CC) |

| 19/22 | DCD               | 20   | DTR    | (CD) |

TABLE 3-1. DART/RS-232-C INTERFACING

Programming limitations of the DARTs are few and stem from the fact that some inputs and outputs are not connected: specifically, W/RDYA\*, W/RDYB\*, RIA\*, and RIB\*. The specific limitations are listed below.

- 1. Bit 7 of Command Register 1 (Wait/Ready Enable) should be  $\emptyset$ . Bits 6 and 5 are don't-care bits.

- 2. Bit 4 of Status Register Ø will always be low. This will not affect External Status Interrupts.

- 3. Bits 7-6 of Command Register 4 should be programmed as required for the desired baud rate, as indicated in Table 3-2.

## 3.2 CTC 2830-UNIQUE PROGRAMMING CHARACTERISTICS

The CTC on the 2830 provides programmable clock signals for the DARTs. In the factory configuration, Channel 0 provides the clocks for Ports 1A and 1B, Channel 1 provides the clocks for Ports 2A and 2B, and Channel 2 provides the clocks for Ports 3A and 3B. Channel 3, which has no output, can be used only as a readable real-time clock, the contents of a channel's downcounter being available to the CPU at the channel address. In the factory configuration the address of CTC Channel 3 is 23H.

The specific programming requirements for the CTC on the 2830 are listed below.

1. The CTC INT\*, IEI, and IEO pins are unconnected. Therefore, the Interrupt Vector Register need never be programmed. Command

Register Bit 7 should be Ø to disable interrupts.

2. Channels  $\emptyset$ -2 may be programmed in either the counter mode (2 MHz clock) or the timer mode (4 MHz clock and prescaler of 16 or 64). See Table 3-2 for the programming options for common baud rates. In the CCS System 300 and 400 software, the CTC is programmed in the counter mode.

### 3.3 PROGRAMMING BAUD RATES

Because of the counter/timer and prescaler options of the CTC and the data rate option of the DART, the CTC/DART combination allows for a wide range of possible baud rates. In some cases there are two or more ways to program the CTC and DART for a given baud rate. Table 3-2 shows all of the programming options for commonly used baud rates.

| TARIF 2 2  | PROGRAMMING   | CTC AND  | STO/DART | FOR | SEI ECTED | BAIID | BATES |

|------------|---------------|----------|----------|-----|-----------|-------|-------|

| INDUC SAZA | PROGRAMMITING | CIC MIND | DIO/DANI | run | SCHELLED  | DAUD  | THIT  |

|                                                                                                                        |                                                |                                                  | TIM                                        | E CONST                                  | ANTS                       |                                            |                 |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------|--------------------------------------------|-----------------|

| BAUD<br>RATE                                                                                                           | P=1<br>DR=16*                                  | P=16<br>DR=1                                     | P=16<br>DR=16*                             | P=16<br>DR=32*                           | P=16<br>DR=64*             | P=256<br>DR=1                              | P=256<br>DR=16* |

| 50<br>75<br>110<br>134.5<br>150<br>300<br>600<br>1200<br>1800<br>2000<br>2400<br>3600<br>4800<br>7200<br>9600<br>19200 | 208<br>104<br>69<br>62<br>52<br>35<br>26<br>17 | 208<br>139<br>125<br>104<br>69<br>52<br>35<br>26 | 208<br>142<br>116<br>104<br>52<br>26<br>13 | 156<br>104<br>71<br>58<br>52<br>26<br>13 | 78<br>52<br>29<br>26<br>13 | 208<br>142<br>116<br>104<br>52<br>26<br>13 | 13              |

P Prescaler programmed for CTC. If P=1, then the CTC is in the counter mode, clocked by the 2 MHz signal.

DR Data Rate programmed for SIO or DART.

<sup>\*</sup> Fvailable in Async Mode only.

## 3.4 PORT RELATIVE ADDRESSES

The base address of the 16 ports occupied by the 2830 is selected by the user as described in Chapter 2, but within the 16-port block the relative addresses of the ports are fixed. Table 3-3 shows the relative addresses of the CTC channels and the DART data and command/status ports. The port addresses for the standard configuration of the board when used in a CCS System 300/400 are given in parentheses.

TABLE 3-3. PORT RELATIVE ADDRESSES

|        |               |               | THE RESERVE THE PROPERTY OF TH | 27 27 27 27 27 27 27 27 27 27 27 27 27 2 |

|--------|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| CTC    | CHANNEL 0     | CHANNEL 1     | CHANNEL 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CHANNEL 3                                |

|        | Base (20H)    | Base+1 (21H)  | Base+2 (22H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Base+3 (23H)                             |

| DART 1 | A DATA        | A COMMAND     | B DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B COMMAND                                |

|        | Base+4 (24H)  | Base+5 (25H)  | Base+6 (26H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Base+7 (27H)                             |

| DART 2 | A DATA        | A COMMAND     | B DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B COMMAND                                |

|        | Base+8 (28H)  | Base+9 (29H)  | Base+10 (2AH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Base+11 (2BH)                            |

| DART 3 | A DATA        | A COMMAND     | B DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B COMMAND                                |

|        | Base+12 (2CH) | Base+13 (2DH) | Base+14 (2EH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Base+15 (2FH)                            |

## CHAPTER 4

## HARDWARE DESIGN

The 2830 is a software-intensive board. A wide range capabilities are provided with relatively simple οf Three DARTs and a CTC form the heart of the hardware. I/O ports with board, providing six asynchronous serial semi-independent programmable baud rates. Additional hardware performs three basic functions: address decoding, bus and interface line buffering, and interrupt daisy chain The DARTs, the CTC, and the three basic implementation. support functions are discussed individually below.

This chapter is intended to be read in conjunction with frequent references to the Schematic/Logic Diagram in Appendix A.

#### 4.1 THE DART

Each Z-80 Dual Asynchronous Receiver/Transmitter provides two extensively programmable asynchronous serial ports capable of serial-to-parallel and parallel-to-serial data conversions in a variety of formats. Such options as word length, parity type or inhibition, interrupt conditions and vector, clock divisor, and stop bit length are under program control. Details of the programming capabilities of the DART are given in the System 200, 300, and 400 Z-80 Family Programming Reference Manual.

DART interfaces are configured for the DART as DCE (Data Communications Equipment), but may be reconfigured for the DART as DTE at the user's discretion; instructions are given in Chapter 2. RS-232-C lines supported by each port include Protective and Signal Grounds, TxD, RxD, CTS, RTS,

DSR, and DTR. Because the DART pins are named assuming that the DART is used as DTE, the RS-232-C lines and the DART pins are oppositely labeled when the DART is used as DCE; see Table 3-1.

Table 4-1 identifies the DART inputs and outputs. RIA\*, RIB\*, W/RDYA\*, and W/RDYB\* are unconnected.

#### 4.2 THE CTC

The Z80 Counter/Timer Circuit consists separately-programmed channels, each of which can operate in either the timer or the counter mode. In either mode a value programmed into a channel's Time Constant Register is loaded into a downcounter which decrements until it reaches zero, at which point the channel's ZC/TO output pulses high (Channels  $\emptyset$ -2 only), an interrupt is generated (this capability is not supported by the 2830 hardware), and downcounter is reloaded with the Time Constant. difference between timer mode and counter mode is in method of decrementing the downcounter. In the timer mode, the downcounter decrements with every 16 or 64 cycles of the system clock (depending on the prescaler selected). In the counter mode, the downcounter decrements with every cycle of the CLK/TRG input, which on the 2830 is controlled by the 2 MHz clock.

The CTC is implemented on the 2830 as a baud rate generator. Channels 0-2 provide 512 different clock rates for each DART in a range wide enough to allow the programming of all common baud rates. Channel 3 is not used and is accessible to the programmer only as a polled-access real-time clock; there is no output from Channel 3 and the CTC's interrupt request output is not connected. Table 3-2 shows how the prescaler and time constant can be programmed to produce common baud rates.

CTC inputs and outputs are described in Table 4-2. ZC/TO outputs  $\emptyset$ -3 control all transmitter and receiver clock inputs for DARTs 1, 2, and 3 respectively unless jumper options are implemented (see Section 2.4). All CLK/TRG inputs are controlled by the 2 MHz clock.

TABLE 4-1. DART SIGNALS

| SIGNAL                 | FUNCTION                                                                                                                                  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| CE* DØ-7 IORQ* M1* RD* | See Table 4-2 for definitions of these signals.                                                                                           |

| в/а*                   | This input, controlled by AØ, determines whether Channel A or Channel B is selected.                                                      |

| C/D*                   | This input, controlled by Al, determines whether a control or data transfer will occur.                                                   |

| TxDA<br>TxDB           | Serial data at TTL levels is output to interface lines RxD.                                                                               |

| RxDA<br>RxDB           | Serial data at TTL levels is input at these pins via the TxD interface lines.                                                             |

| CTSA*<br>CTSB*         | The Clear To Send inputs, connected to the RTS RS-232-C lines, may be programmed as transmitter auto-enable or general-purpose signals.   |

| RTSA*<br>RTSB*         | The Request to Send handshaking outputs are connected to the CTS RS-232-C lines.                                                          |

| DCDA*<br>DCDB*         | The Data Carrier Detect inputs, connected to the DTR RS-232-C lines, may be programmed as receiver auto-enable or general purpose inputs. |

| DTRA*<br>DTRB*         | The Data Terminal Ready handshaking outputs are connected to the DSR RS-232-C lines.                                                      |

| RIA*<br>RIB*           | These pins are not connected on the 2830.                                                                                                 |

| RxCA<br>TxCA<br>RxTxCB | The Channel A and Channel B clocks are controlled by one CTC channel unless jumpered otherwise.                                           |

| RESET*                 | A low at this pin resets both DART channels.                                                                                              |

| CLK                    | This is the DART's system clock input.                                                                                                    |

| INT*<br>IEI<br>IEO     | See Section 4.4 for a discussion of these interrupt daisy chain signals.                                                                  |

TABLE 4-2. CTC SIGNALS

| 1                      |                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL                 | FUNCTION                                                                                                                        |

| CE*                    | Chip Enable is controlled by the address decode circuitry.                                                                      |

| RD*                    | The Read input determines the direction of data transfer.                                                                       |

| IORQ*                  | The I/O Request input enables data transfer.                                                                                    |

| M1*                    | Both Ml* and IORQ* low indicates an Interrupt Acknowledge cycle.                                                                |

| CSØ,CS1                | The Channel Select inputs select one of four CTC channels. They are controlled by AØ-Al.                                        |

| CLK/TRG<br>  Ø-3       | The Clock/Trigger inputs control downcounter decrementing in counter mode. All are controlled by the 2 MHz clock (bus pin 49).  |

| ZC/TO<br>  Ø-2         | The Zero Count/Timeout pins pulse high when the downcounters reach zero. They control the DART receiver and transmitter clocks. |

| DØ-7                   | The bi-directional data pins connect directly to the 2719 internal data bus.                                                    |

| RESET*                 | Reset low terminates downcounting, disables interrupts, and tri-states DØ-D7.                                                   |

| CLK                    | This is the CTC's system clock input.                                                                                           |

| INT*<br>  IEI<br>  IEO | See Section 4.4 for a discussion of these interrupt daisy chain signals.                                                        |

### 4.3 ADDRESS DECODING

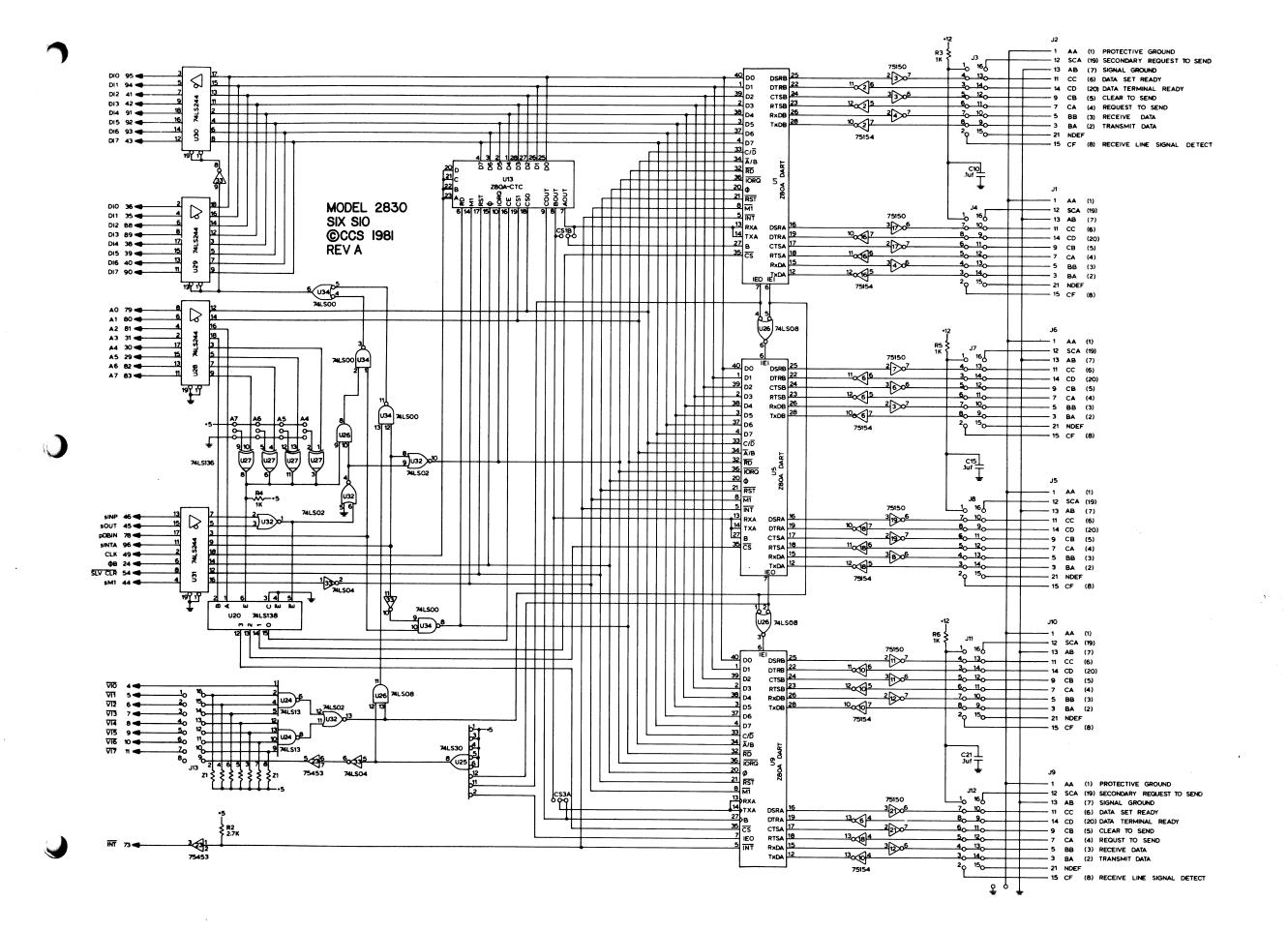

The four Z-80 peripheral devices on board the occupy a block of 16 port addresses whose base is a multiple The base address is selected by the user with four jumper plugs. These plugs determine whether a high or a low signal is Ex-ORed with each of the bus lines A7-A4. A7-A4 is in the state opposite of that selected by the corresponding jumper, the outputs οf the open-collector Ex-OR gates are all high. The Ex-OR outputs are tied together to control the E (Enable) input of the The decoder has two other 3-to-8 Device Select Decoder. Enable inputs, both active low; the conditions of all three enable inputs must be met for the decoder to be enabled. One of the E\* inputs is tied to ground. The other is active when either sINP or sOUT is active -- i.e., during I/O read or Thus, when A7-A4 address I/O write cycles. jumper-selected 16-port block during an I/O cycle the Device Select Decoder is enabled.

Each Z-80 device on board--CTC or DART--occupies four port addresses. The Device Select Decoder, used as a 2-to-4 decoder, decodes bus lines A3 and A2 to force one of four outputs low. Each of the four outputs is tied to the CE (Chip Enable) input of one of the Z-80 devices, so that whenever the Device Select Decoder is enabled one of the Z-80 devices is enabled. The enabled device then decodes A1 and A0 to determine which channel or port is addressed.

### 4.4 INTERRUPT DAISY CHAIN LOGIC

The 2830 supports the Z-80 Mode 2 Interrupt Daisy Chain as implemented by CCS Systems 200, 300, and 400. (Mode 2 interrupts are discussed in detail in the 2820 Reference Manual and in the Z-80 Family Programming Reference Manual.) The Vectored Interrupt bus lines are used to prioritize the boards participating in the chain. Each board must include look-ahead logic that guarantees that an interrupt request by an on-board device or by a device on a higher-priority board will be passed on to lower-priority boards rapidly enough to be recognized by lower-priority devices before the interrupt is acknowledged; otherwise, two devices might put their interrupt vectors on the bus at the same time.

If an on-board interrupt occurs, the DART(s) having lower priority than the interrupting DART are prevented from interrupting by the normal chip-to-chip IEI-IEO daisy chain,

the interrupt-disable message rippling through the individual chips (input IEI low forcing output IEO low) from high priority to low. An interrupt by a higher-priority board does not ripple through the DARTs, however; each DART's interrupt request logic is immediately disabled when the 2830 interrupt logic senses any higher-priority VI\* line going low, thereby significantly reducing response time. In addition, whenever an on-board DART interrupts or the 2830 senses a higher-priority VI\* line low, the 2830 forces its priority-assertion VI\* line low.

The particular VI\* lines the 2830 senses and the VI\* line it asserts are determined by the configuration of the Interrupt Daisy Chain Header; see Section 2.2. The 2820 System Processor is always the highest priority (0), but the 2830 can be configured for any other priority from 1 to 8. As shipped from the factory, it is configured for priority level 1.

#### 4.5 BUFFERING

All system bus inputs and outputs are fully buffered, as are the RS-232-C interface lines. Hysteresis drivers and receivers are used for system bus interfacing, ensuring minimum noise on the bus. No load of more than one Low-Power Schottky TTL level is placed on any system bus input. INT\* and lower-priority VI\* line drivers are open-collector. Port interface drivers and receivers meet EIA RS-232-C specifications.

Except for the Data In and Data Out Buffers, all buffers are permanently enabled. The Data In and Data Out Buffers are alternately tri-stated. Basically, the Data In Buffer is tri-stated and the Data Out Buffer enabled: 1) when the board is addressed during an I/O Read cycle; or 2) during an Interrupt Acknowledge cycle when the 2830 is the highest-priority board requesting an interrupt. At all other times the Data Out Buffer is tri-stated and the Data In Buffer is enabled.

When a device's interrupt has been blocked by the interrupt of a higher-priority device, the lower-priority device monitors the data bus during all instruction fetches, looking for the RETI instruction which signals that servicing of the higher-priority interrupt has been completed and that lower-priority interrupts may now be asserted. To ensure proper monitoring of the CPU instruction fetches by the 2830, the CPU must internally

HARDWARE DESIGN 4-7

connect the DI and DO buses. This is necessary because, while the RETI instruction is input to the CPU on the DI lines, the 2830 looks for RETI on the DO lines. The CCS 2820 System Processor Board meets this requirement as long as no peripheral or memory board asserts DODSB during instruction fetch cycles.

# APPENDIX A

# TECHNICAL INFORMATION

# A.1 USER-REPLACEABLE PARTS

| QTY                                       | REF                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                             |                                                                                                                                                                                   |

|-------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inte                                      | grated Circuits                                                                            | `                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                   |

| 3<br>5<br>9                               | U1,5,9<br>U2,6,10,16,18<br>U3,4,7,8,11,12,<br>17,19,21                                     | Z-8Ø DART<br>75154 line receiver<br>7515Ø line driver                                                                                                                                                                                                                                   | 48200119-01<br>48200056-01<br>48200055-01                                                                                                                                         |

| 1<br>1<br>1<br>1<br>1<br>1<br>1<br>4<br>1 | U13<br>U14<br>U15<br>U2Ø<br>U22<br>U23<br>U24<br>U25<br>U26<br>U27<br>U28-31<br>U32<br>U33 | Z-80 CTC 7805 +5 V regulator 7912 -12 V regulator 74LS138 3-to-8 decoder 7812 +12 V regulator 75453 dual OR driver 74LS13 dual 4-in NAND 74LS30 8-in NAND 74LS08 quad 2-in AND 74LS136 quad EX-OR 74LS244 octal buffers 74LS02 quad 2-in NOR 74LS04 hex inverters 74LS00 quad 2-in NAND | 48200084-01<br>48200109-01<br>48200115-01<br>48200022-01<br>48200113-01<br>48200059-01<br>482000120-01<br>48200012-01<br>48200001-01<br>48200002-01<br>48200004-01<br>48200001-01 |

| Capa                                      | citors                                                                                     | •                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                   |

| 16<br>6                                   | C1-3,10-22<br>C4-9                                                                         | .luf Mono, 50VDC, 20%<br>4.7uf Tant, 35VDC, 20%                                                                                                                                                                                                                                         | 15900001-01<br>15500003-01                                                                                                                                                        |

| Resi                                      | stors                                                                                      |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                   |

| 1<br>4<br>1                               | R2<br>R3-6<br>RP1                                                                          | 2.7K ohm, 1/4 Watt, 5% 1K ohm, 1/4 Watt, 5% SIP Network, 2.7K x 7                                                                                                                                                                                                                       | 47000003-01                                                                                                                                                                       |

| Sock                                      | ets                                                                                        |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                   |

| 1<br>1<br>3                               | XJ13<br>XU13<br>XU1,5,9                                                                    | 16 pin DIP<br>28 pin DIP<br>40 pin DIP                                                                                                                                                                                                                                                  | 21400015-01<br>21400019-01<br>21400020-01                                                                                                                                         |

| Misc                                      | ellaneous                                                                                  |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                   |

| 6<br>1<br>1<br>4<br>4                     | J1,2,5,6,9,10<br>J13                                                                       | Conn, 2 x 13 rt angle Header, 2 x 8 Header cover, 2 x 8 Header, 2 x 4 Header, 1 x 4 Jumper shorting plugs                                                                                                                                                                               | 21000005-01<br>21600001-01<br>14100001-01<br>21000023-01<br>21000009-01<br>21300021-01                                                                                            |

| 3<br>3<br>2<br>2<br>6                     | XU14,15,22<br>XU14,15,22                                                                   | Heatsink, TO-220<br>Screw, 6-32 x 3/8<br>Nut, 6-32 KEP<br>Board extractor<br>Roll pin<br>Cable, RS-232-C                                                                                                                                                                                | 76000001-01<br>28000006-01<br>28100004-01<br>74000001-01<br>28300001-01<br>60900007-01                                                                                            |

## A.2 DART AND CTC PINOUTS

| 1      |    | <del></del> |    |         | 4      | ,           |   |    |          |

|--------|----|-------------|----|---------|--------|-------------|---|----|----------|

| D1     | 1  |             | 40 | DO      | D4     | 1           |   | 28 | D3       |

| D3     | 2  |             | 39 | D2      | · D5   | 2           |   | 27 | D2       |

| D5     | 3  |             | 38 | D4      | D6     | 3           |   | 26 | D1       |

| D7     | 4  |             | 37 | D6      | D7     | 4           | 0 | 25 | DO       |

| INT*   | 5  |             | 36 | IORQ*   | GND    | 5           | C | 24 | +5 V     |

| IEI    | 6  | n           | 35 | CE*     | RD     | 6           | T | 23 | CLK/TRGO |

| IEO    | 7  | Ď           | 34 | B/A*    | ZC/TOO | 7           | 1 | 22 | CLK/TRG1 |

| M1*    | 8  | A           | 33 | C/D*    | ZC/TO1 | 8           | C | 21 | CLK/TRG2 |

| +5 V   | 9  |             | 32 | RD*     | ZC/TO2 | 9           | U | 20 | CLK/TRG3 |

| WRDYA* | 10 | R           | 31 | GND     | IORQ*  | 10          |   | 19 | CS1      |

| RIA*   | 11 | Ŧ           | 30 | WRDYB*  | IEO    | 11          |   | 18 | CS0      |

| RxDA   | 12 | l           | 29 | RIB#    | INT*   | 12          |   | 17 | RESET*   |

| Rx CA* | 13 |             | 28 | RxDB    | IEI    | 13          |   | 16 | CE#      |

| Tx CA* | 14 |             | 27 | RxTxCB* | M1*    | 14          |   | 15 | CLK      |

| TxDA   | 15 |             | 26 | TxDB    |        | <del></del> |   |    |          |

| DTRA*  | 16 |             | 25 | DTRB*   |        |             |   |    |          |

| RTSA*  | 17 |             | 24 | RTSB*   |        |             |   |    |          |

| CTSA*  | 18 |             | 23 | CTSB#   |        |             |   |    |          |

| DCDA*  | 19 |             | 22 | DCDB*   |        |             |   |    |          |

| CLK    | 20 |             | 21 | RESET*  |        |             |   |    |          |

|        |    |             |    |         |        |             |   |    |          |

## A.3 ON-BOARD INTERFACE CONNECTOR PINOUTS

| PROTECTIVE GROUND      |   | 1 •  | • 2  |                     |

|------------------------|---|------|------|---------------------|

| TRANSMITTER DATA       |   | 3 •  | • 4  |                     |

| RECEIVER DATA          |   | 5 •  | • 6  |                     |

| REQUEST TO SEND        |   | 7 •  | • 8  |                     |

| CLEAR TO SEND          |   | 9 •  | • 10 |                     |

| DATA SET READY         |   | 11 • | • 12 | SEC REQUEST TO SEND |

| SIGNAL GROUND          |   | 13.  | • 14 | DATA TERMINAL READY |

| REC LINE SIGNAL DETECT |   | 15 ● | • 16 |                     |

|                        |   | 17 • | • 18 |                     |

| SIGNAL QUALITY DETECT  |   | 19 • | • 20 |                     |

| <u>-</u>               |   | 21 • | • 22 |                     |

|                        |   | 23 ● | • 24 |                     |

|                        | × | 25 ● | • 26 |                     |

|                        |   |      |      |                     |

## A.4 RS-232-C CONNECTOR PINOUTS

#### FRONT VIEW

| PROTECTIVE GROUND     | AA   | 1  | (  |          |    |              |                            |

|-----------------------|------|----|----|----------|----|--------------|----------------------------|

| PROTECTIVE GROUND     | ^^   |    | 0  | (        | 14 | SBA          | SEC TRANSMIT DATA          |

| TRANSMIT DATA         | BA   | 2  | 0  |          |    | <del>-</del> | *                          |

|                       | 1.50 |    |    | 0        | 15 | DB           | TRANSMIT SIG ELE CLK (DCE) |

| RECEIVE DATA          | BB   | 3  | 0  |          | 16 | epp.         | SEC RECEIVE DATA           |

| REQUEST TO SEND       | CA   | 4  | 0  | 0        | 10 | SBB          | SEC RECEIVE DAIA           |

|                       | -    |    |    | 0        | 17 | DD           | RECEIVE SIG ELE CLK (DCE)  |

| CLEAR TO SEND         | CB   | 5  | 0  |          |    |              |                            |

| SATI ALT DEADY        |      | _  |    | 0        | 18 | _            | UNASSIGNED                 |

| DATA SET READY        | cc   | 6  | 0  | 0        | 19 | SCA          | SEC REQUEST TO SEND        |

| SIGNAL GROUND         | AB   | 7  | 0  |          |    | <del>4</del> | SEG REGUES! TO SEND        |

| 10                    |      |    |    | 0        | 20 | CD           | DATA TERMINAL READY        |

| REC LINE SIG DET      | CF   | 8  | 0  |          |    |              |                            |

| RESERVED              | _    | 9  |    | 0        | 21 | CG           | SIGNAL QUALITY DETECTOR    |

| HESERVED              |      | ð  | 0  | 0        | 22 | CE           | RING INDICATOR             |

| RESERVED              | _    | 10 | 0  |          |    |              |                            |

|                       |      |    |    | 0        | 23 | CH/CI        | DATA RATE SELECT           |

| UNASSIGNED            | -    | 11 | 0  |          |    |              |                            |

| SEC REC LINE SIG DET  | SCF  | 12 | 0  | <b>@</b> | 24 | DA           | TRANSMIT SIG ELE CLK (DTE) |

| OLO FILO LINE OIG DET | 4    | 12 | ۱۳ | 0        | 25 | _            | UNASSIGNED                 |

| SEC CLEAR TO SEND     | SCB  | 13 | 0  | رگر      |    |              | 1                          |

|                       |      |    |    |          |    |              |                            |

DB-25S (FEMALE)

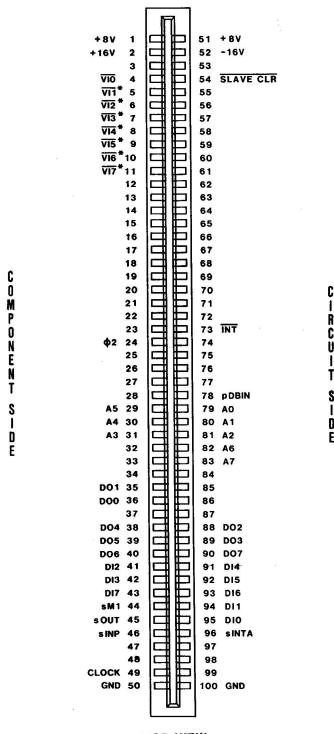

## A.5 BUS CONNECTOR PINOUTS

**TOP VIEW**

<sup>\*</sup>Jumper-enabled signals

## TECHNICAL INFORMATION

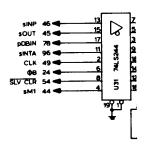

## A.6 SCHEMATIC/LOGIC DIAGRAM