# ME32K RAM/ROM/Bootstrap Module

1 February 2025

# **PREFACE**

This manual provides the information needed to install, operate, maintain, and troubleshoot the ME32K Rev D RAM/ROM/Bootstrap Module by Martin Eberhard

The reader is assumed to have a basic knowledge of digital computer theory and an understanding of the PDP11/20 computer in which the ME32K is used.

|  | ——— Page 2 |  |  |

|--|------------|--|--|

|  |            |  |  |

|  |            |  |  |

|  |            |  |  |

|  |            |  |  |

|  |            |  |  |

|  |            |  |  |

|  |            |  |  |

|  |            |  |  |

# **TABLE OF CONTENTS**

| Preface                                                       | 1  |

|---------------------------------------------------------------|----|

| 1 General Information                                         | 5  |

| 1.1 Introduction                                              | 5  |

| 1.2 General Description                                       | 5  |

| 1.2.1 RAM Capacity and Address                                | 5  |

| 1.2.2 ROM Capacity and Addresses                              | 5  |

| 1.2.3 Bootstrap Vector                                        | 6  |

| 1.2.4 Access and Cycle times                                  | 6  |

| 1.3 Unibus Interface                                          | 6  |

| 1.3.1 Access Modes                                            | 6  |

| 1.3.2 Writing to ROM Addresses                                | 6  |

| 1.3.3 Interface Signals                                       | 7  |

| 1.3.4 Power Supply                                            | 7  |

| 1.4 Physical Specifications                                   | 7  |

| 1.4.1 Power Requirements                                      | 7  |

| 2 Configuration and Installation                              | 8  |

| 2.1 Assembly Options                                          | 8  |

| 2.1.1 EPROMs                                                  | 8  |

| 2.1.2 Delete Battery Backup                                   | 9  |

| 2.1.3 Battery Type for Backup                                 | 9  |

| 2.1.4 Grounding Options                                       | 9  |

| 2.1.5 NPG                                                     | 9  |

| 2.2 Switch-Selectable Options                                 | 10 |

| 2.2.1 DIP Switch SW1                                          | 10 |

| 2.2.2 Bootstrap Vector Switch Bank (DIP Switches SW2 and SW3) | 10 |

| 2.2.3 DIP Switch SW4                                          | 10 |

| 2.3 Installation                                              | 11 |

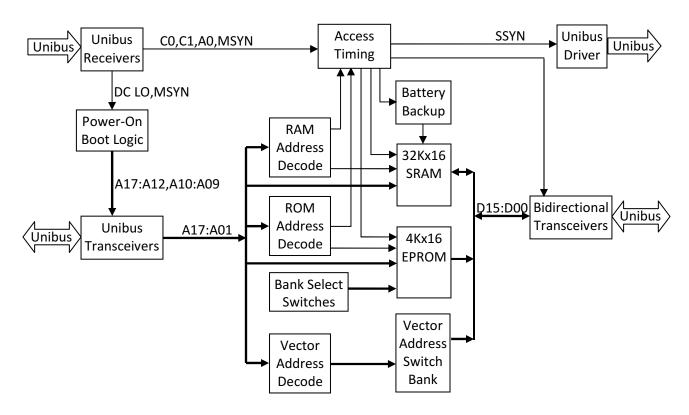

| 3 Theory of Operation                                         | 12 |

| 3.1 Block Diagram                                             | 12 |

| 3.2 Circuit Descriptions                                      | 12 |

| 3.2.1 Unibus Receivers, Drivers, and Transceivers             | 12 |

| 3.2.2 RAM Address Decode                                      | 12 |

| 3.2.3 ROM Address Decode                                      | 13 |

| 3.2.4 Bootstrap Vector Address                                | 13 |

| 3.2.5 Power-On Boot                                  | 13 |

|------------------------------------------------------|----|

| 3.2.6 Access Timing                                  | 13 |

| 3.2.5 256x16 ROM                                     | 15 |

| 3.2.6 32Kx16 RAM                                     | 16 |

| 3.2.7 Battery Backup                                 | 16 |

| Appendix                                             | 17 |

| A.1 Bill of Materials                                | 17 |

| A.2 Component Specifications                         | 17 |

| A.2.1 HM62246ALP-100 SRAM                            | 18 |

| A.2.2 NM26C32B EPROM                                 | 29 |

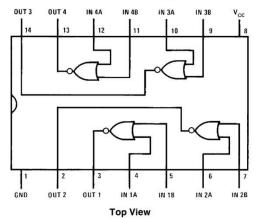

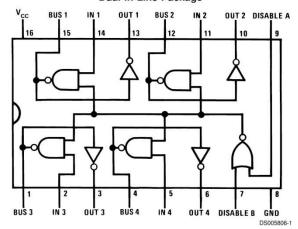

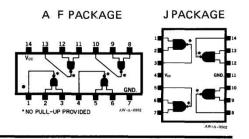

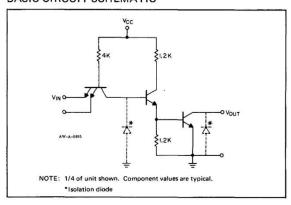

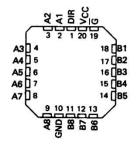

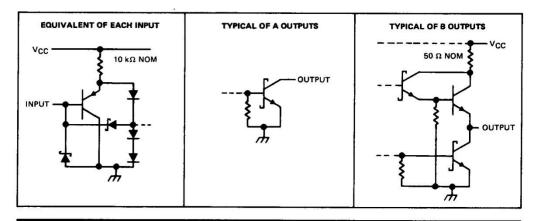

| A.2.3 DS8640 Unibus Receiver                         | 33 |

| A.2.4 DS8641 Unibus Transceiver                      | 35 |

| A.2.5 8881 Unibus Driver                             | 39 |

| A.2.6 74LS639 Bus Transceiver                        | 40 |

| A.2.7 MAX693 Microprocessor Supervisory Circuit      | 43 |

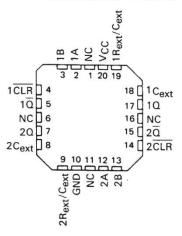

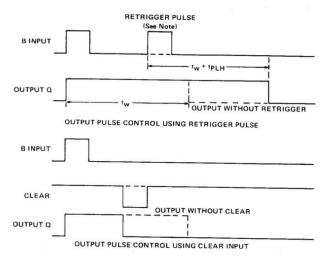

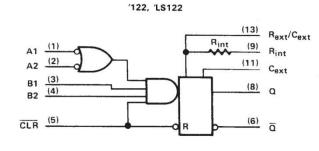

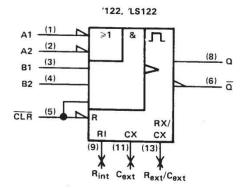

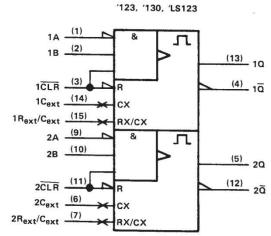

| A.2.8 74LS123 Retriggerable Monostable Multivibrator | 58 |

### 1 GENERAL INFORMATION

### 1.1 Introduction

This manual provides the information needed to install, operate, maintain and troubleshoot the ME32K Rev C memory, designed by Martin Eberhard

The material is arranged into five sections as follows:

Section 1 - GENERAL INFORMATION contains a brief functional description and specifications of the ME32K.

Section 2 - INSTALLATION explains the requirements and procedures for equipment installation. Address selection and other options are described.

Section 3 - THEORY OF OPERATION. contains a detailed functional description of the ME32K

<u>APPENDIX</u> - The appendix contains the parts list, logic diagrams, and assembly drawing required for a complete understanding of the unit.

# 1.2 General Description

The ME32K provides Random-Access Memory (RAM), Read-Only Memory (ROM), and Bootstrap capability for Digital Equipment Corporation (DEC) PDP11 computers that have Unibus interfaces - especially the PDP11/20. It is designed to plug into any Small Peripheral Option slot on the Unibus, such as those on a DD-11A System Unit or in slots 13 and 14 of the PDP11/20 (which are also for small peripheral options).

### 1.2.1 RAM Capacity and Address

RAM on the ME32K is fully-static memory, comprising 32,768 words, 16 bits each. (This is the maximum memory in a basic PDP11/20.) Switches on the ME32K allow you to select one of four address ranges for the ME32K, for systems that can address 128K words of memory.

Memory on the ME32K between  $760000_8$  and  $777777_8$  is disabled because this region is reserved by PDP11/20 convention for device registers, I/O devices and ROMs. Note that in its standard configuration (without a KT11-B Paging Option), the PDP11/20 CPU will map addresses between  $160000_8$  and  $177777_8$  into this I/O region between  $760000_8$  and  $777777_8$ .

The ME32K RAM can be battery-backed so that it retains its data when the PDP11's power is off, similar to core memory.

The ME32K RAM can be disabled with a DIP switch setting.

### 1.2.2 ROM Capacity and Addresses

The ME32K supports ROM in two regions. Low ROM is between  $765000_8$  and  $765777_8$ . High ROM is between  $773000_8$  and  $773777_8$ . Each ROM bank can be disabled with a DIP switch setting, (The PDP11 normally has its "console emulator" and diagnostics firmware in Low ROM, and a selection of boot loader programs in High ROM.)

The ME32K supports up to 8 separate pairs of Low ROM and High ROM data, selectable with a DIP switch setting.

### 1.2.3 Bootstrap Vector

The ME32K supports a bootstrap vector similar to that on the DEC M9312 Bootstrap-Terminator board.

Immediately following power-on, the bootstrap vector hardware forces the PDP11's program counter (PC) and status register to be read from addresses  $773024_8$  and  $773026_8$ , instead of the PDP11/20's normal addresses,  $000024_8$  and  $000026_8$ . This feature can be disabled with a DIP switch.

$773024_8$  is the address of the Bootstrap Vector Switch Bank, which is only available if high ROM is also enabled. This 16-bit switch bank specifies the initial PC value. (Though bit 0 should always 0.) The Bootstrap Vector Switch Bank can be disabled with a DIP switch. When disabled, reading from address  $773024_8$  will read from high ROM instead, assuming high ROM is enabled.

### 1.2.4 Access and Cycle times

Access time is the time from when MSYN initiates a bus cycle to when the ME32K ends the cycle with SSYN. Unlike core memory, reading is nondestructive and writes do not require memory to be cleared first. This means that cycle time for the ME32K is the same as its access time.

| Item                                          | Nominal | Maximum |

|-----------------------------------------------|---------|---------|

| RAM Read Access Time                          | 200 ns  | 350 nS  |

| RAM Write Access Time                         | 200 nS  | 350 nS  |

| RAM Read Access Time, Battery Backup Deleted  | 140 nS  | 160 nS  |

| RAM Write Access Time, Battery Backup Deleted | 140 nS  | 160 nS  |

| ROM Read Access Time                          | 140 nS  | 160 nS  |

# 1.3 Unibus Interface

### 1.3.1 Access Modes

The ME32K operates in several different modes, as determined by the state of address Bit A00 and control lines C0 and Cl. The modes of operation are as follows. (0 means "inactive," 1 means "active", and X means "any state." These signals on the Unibus are negative signals, meaning that active signals are below 0.8V and inactive signals are above 2.4V.)

| C0 | <b>C1</b> | A00 | Mode            | Description            |

|----|-----------|-----|-----------------|------------------------|

| 0  | Х         | Χ   | Read            | 16-bit read operation  |

| 1  | 0         | Χ   | Word Write      | 16-bit write operation |

| 1  | 1         | 0   | Low-Byte Write  | 8-bit write to D<7:0>  |

| 1  | 1         | 1   | High-Byte Write | 8-bit write to D<15:8> |

# **1.3.2 Writing to ROM Addresses**

Attempts to write to ROM are ignored by the ME32K, which will cause a Unibus timeout, invoking a TRAP operation by the PDP11. You can modify the ME32K to respond (with the SSYN signal) to writes in the ROM address spaces, though no actual writes will occur.

| Operation | Side   | Location                                                 |  |  |

|-----------|--------|----------------------------------------------------------|--|--|

| Cut       | Solder | Trace between E14 pin 6 and E15 pin 10                   |  |  |

| Cut       | Solder | Trace between E19 pin 20 and via to GND, near E19 pin 14 |  |  |

| Jumper    | Solder | From E14 pin 6 and E14 pin 16                            |  |  |

| Jumper    | Solder | From E19 pin 20 and E1 pin 1                             |  |  |

# 1.3.3 Interface Signals

The following signals of the Unibus Small Peripheral Interface are used by the ME32K:

| Name | Dir | Pin | Function    | Name | Dir | Pin | Function    | Name  | Dir | Pin | Function   |

|------|-----|-----|-------------|------|-----|-----|-------------|-------|-----|-----|------------|

| A00  | IN  | EH2 | Byte Select | A13  | IN  | EK2 | Address 13  | D05   | 1/0 | CP2 | Data 5     |

| A01  | IN  | EH1 | Address 1   | A14  | IN  | EK1 | Address 14  | D06   | 1/0 | CV2 | Data 6     |

| A02  | IN  | EF1 | Address 2   | A15  | IN  | ED2 | Address 15  | D07   | 1/0 | CM2 | Data 7     |

| A03  | IN  | EV2 | Address 3   | A16  | IN  | EE2 | Address 16  | D08   | 1/0 | CL2 | Data 8     |

| A04  | IN  | EU2 | Address 4   | A17  | IN  | ED1 | Address 17  | D09   | 1/0 | CK2 | Data 9     |

| A05  | IN  | EV1 | Address 5   | MSYN | IN  | EE1 | Master Sync | D10   | 1/0 | CJ2 | Data 10    |

| A06  | IN  | EU1 | Address 6   | CO   | IN  | EJ2 | Mode 0      | D11   | 1/0 | CH1 | Data 11    |

| A07  | IN  | EP2 | Address 7   | C1   | IN  | EF2 | Mode 1      | D12   | 1/0 | CH2 | Data 12    |

| A08  | IN  | EN2 | Address 8   | D00  | 1/0 | CS2 | Data 0      | D13   | 1/0 | CF2 | Data 13    |

| A09  | IN  | ER1 | Address 9   | D01  | 1/0 | CR2 | Data 1      | D14   | 1/0 | CE2 | Data 14    |

| A10  | IN  | EP1 | Address 10  | D02  | 1/0 | CU2 | Data 2      | D15   | 1/0 | CD2 | Data 15    |

| A11  | IN  | EL1 | Address 11  | D03  | 1/0 | CT2 | Data 3      | SSYN  | OUT | EJ1 | Slave Sync |

| A12  | IN  | EC1 | Address 12  | D04  | 1/0 | CN2 | Data 4      | DC LO | IN  | CN1 | Power fail |

# 1.3.4 Power Supply

Power is supplied to the ME32K with the following Unibus Small Peripheral Interface pins:

| Supply | Pins     | Function                                             |  |  |

|--------|----------|------------------------------------------------------|--|--|

| GND    | CC2, CT1 | Ground, used for data bus transceivers               |  |  |

| GND    | DC2, DT1 | Ground, used for onboard logic and memory components |  |  |

| GND    | EC2, ET1 | Ground, used for address and control bus receivers   |  |  |

| +5V    | CA2      | +5 Volts, used for data bus transceivers             |  |  |

| +5V    | DA2      | +5V, used for onboard logic and memory components    |  |  |

| +5V    | EA2      | +5V, used for address and control bus receivers      |  |  |

# 1.4 Physical Specifications

The ME32K consists of a single 3-high circuit board that occupies connectors C,D, and E of one Small Peripheral Option interface slot on the Unibus. Note that the AAA batteries are positions so as not to interfere with an adjacent board, despite their height.

| Characteristic                             | Specification                      |

|--------------------------------------------|------------------------------------|

| Interface Signal Levels: High (inactive)   | 2.4V                               |

| Low (active)                               | 0.8V                               |

| Mechanical Dimensions: Width               | 7.7 inches                         |

| Height                                     | 8.5 inches, not including handles  |

| Max Component Height Without AAA batteries | 0.33 inches, not including handles |

| With AAA batteries                         | 0.50 inches                        |

# **1.4.1 Power Requirements**

|         |                 | Operating | Current    |

|---------|-----------------|-----------|------------|

| Voltage | Standby Current | Typical   | Worst Case |

| +5V     |                 | 350 mA    | 650 mA     |

# 2 CONFIGURATION AND INSTALLATION

# 2.1 Assembly Options

The ME16K can be assembled a few different ways, trading off speed, cost, and functionality.

### **2.1.1 EPROMs**

The ME2732 supports the following EPROM types: 2732, 2764, 27128, 27256, and 27512. If EPROMs are used, then both EPROMs must be installed. The EPROM at E18 contains the even bytes, and the EPROM at E17 contains the odd bytes of every word.

Note that data in the EPROMs must be inverted when the EPROMs are programmed.

Only 4K-bytes from each EPROM are used, with the EPROM at E18 contains the even bytes, and the EPROM at E17 contains the odd bytes of every word in the 4K-word EPROM space.

For EPROMs larger than 2732's, address pin A12 is tied low, and all higher address lines are tied high. (This is represented by the "(E)" in the table below.)

The 4K-word EPROM space is subdivided into eight 512-word banks, which are selectable by DIP switch SW1. (See below.)

Each 512-word bank is further subdivided into a 256-word Low-ROM region and a 256-word high-ROM region The EPROM data is mapped into the PDP11 address space as follows. (This table shows the EPROM address for both the low-byte EPROM and the high-byte EPROM.)

| EPROM Address | ROM  | ROM      | PDP11 Address |

|---------------|------|----------|---------------|

| Range (Hex)   | Bank | Region   | Range (Octal) |

| (E)000-(E)0FF | 0    | Low ROM  | 765000-765777 |

| (E)100-(E)1FF | 0    | High ROM | 773000-773777 |

| (E)200-(E)2FF | 1    | Low ROM  | 765000-765777 |

| (E)300-(E)3FF | 1    | High ROM | 773000-773777 |

| (E)400-(E)4FF | 2    | Low ROM  | 765000-765777 |

| (E)500-(E)5FF | 2    | High ROM | 773000-773777 |

| (E)600-(E)6FF | 3    | Low ROM  | 765000-765777 |

| (E)700-(E)7FF | 3    | High ROM | 773000-773777 |

| (E)800-(E)8FF | 4    | Low ROM  | 765000-765777 |

| (E)900-(E)9FF | 4    | High ROM | 773000-773777 |

| (E)A00-(E)AFF | 5    | Low ROM  | 765000-765777 |

| (E)B00-(E)BFF | 5    | High ROM | 773000-773777 |

| (E)COO-(E)CFF | 6    | Low ROM  | 765000-765777 |

| (E)D00-(E)DFF | 6    | High ROM | 773000-773777 |

| (E)E00-(E)EFF | 7    | Low ROM  | 765000-765777 |

| (E)F00-(E)FFF | 7    | High ROM | 773000-773777 |

A typical EPROM configuration would put DEC's Console/Diagnostic PROM data in the low ROM region and four different boot ROMs' data in the high ROM region. The ROM bank select switches allow you to have up to eight different configurations, supporting alternative Console/Diagnostic programs and alternative boot ROM data.

# 2.1.2 Delete Battery Backup

Battery backup for the static RAM's can be deleted, which has the effect of speeding up SRAM accesses by as much as 200 nS per cycle. To delete battery backup:

- 1. Do not install either battery holder (B1 or B2)

- 2. Do not install an IC in location E21 (the MAX693)

- 3. Install a jumper from pin 2 to 3 at IC location E21

- 4. Install a jumper from pin 12 to pin 13 at IC location E22

- 5. Optionally, delete transistor Q1. (Leaving it in is harmless but also useless.)

- 6. Optionally, delete diode D1 and replace it with a jumper wire. You can then delete resistor R6.

# 2.1.3 Battery Type for Backup

The ME32K can be assembled to use either a 20 mm (CR2032) lithium "coin-cell" or two AAA batteries, to power the static RAM chips when the PDP11 power is off. The coin cells are (obviously) much smaller and less prone to chemical leakage. The AAA batteries have much higher capacity.

For a coin cell, the battery holder is part number 122-2620-GR, manufactured by Eagle Plastic Devices. For AAA batteries, the battery holder is part number 12BH425P-GR, manufactured by Eagle Plastic Devices.

It is strongly recommended that lithium-type batteries be used for the AAA battery option (as opposed to alkaline or "standard" AAA batteries), to reduce the chance of chemical leakage as the batteries age.

# 2.1.4 Grounding Options

Per the recommendations on page 4-6 of *PDP-11 Unibus(tm) Design Description* published by Digital Equipment Corporation, the backplane power and ground pins used for the ME32K's onboard logic are completely separate from those used to power the bus transceiver ICs.

Should you wish to connect the separate ground signals on the ME32K, install jumpers at J1 and J2. (Normally, these should not be jumpered.)

### 2.1.5 NPG

The ME32K does not do Active Data Transmission (DMA), and therefore does to use the Unibus NPG signal. You can pass this signal on through the ME32K by installing a jumper wire at J3.

# 2.2 Switch-Selectable Options

There are four DIP switches on the ME32K, which allow you to control various options.

### 2.2.1 DIP Switch SW1

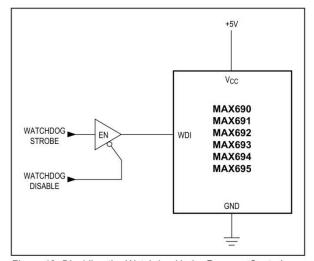

Switch 1 of SW1 disables Power-On Boot when closed.

The two EPROMs contains 8 separate 512-word EPROM banks, Only one bank is available to the PDP11 at any time, selectable with SW1 switches 2 through 4:

| SW  | 1 Swi | tch |                   |

|-----|-------|-----|-------------------|

| 4   | 3     | 2   | <b>EPROM Bank</b> |

| on  | on    | on  | Bank 0            |

| on  | on    | off | Bank 1            |

| on  | off   | on  | Bank 2            |

| on  | off   | off | Bank 3            |

| off | on    | on  | Bank 4            |

| off | on    | off | Bank 5            |

| off | off   | on  | Bank 6            |

| off | off   | off | Bank 7            |

# 2.2.2 Bootstrap Vector Switch Bank (DIP Switches SW2 and SW3)

SW2 switch 6 disables the Bootstrap Vector when closed. When this switch is open, reading from address 173024<sub>8</sub> will always read from the Bootstrap Vector Switch Bank (BVSB).

SW2 and SW3 together specify the 16-bit Bootstrap Vector. For these switches, closed represents a logical 1 and open represents a logical 0. SW3 switch 8 is the most-significant bit (bit 15), and SW2 switch 1 is the least-significant bit (bit 0). Bit 0 should always be set to 0.

### 2.2.3 DIP Switch SW4

The 6-positionDIP Switch at location SW4 provides the following options:

| SW2 Switch | Off                    | On                  |  |  |

|------------|------------------------|---------------------|--|--|

| 1          | RAM is disabled        | RAM is enabled      |  |  |

| 2          | Unibus A16 must be low | Unibus A16 must be  |  |  |

| 2          | to address RAM         | high to address RAM |  |  |

| 3          | Unibus A17 must be low | Unibus A17 must be  |  |  |

| 3          | to address RAM         | high to address RAM |  |  |

| 4          | High ROM is disabled   | High ROM is enabled |  |  |

| 5          | Low ROM is disabled    | Low ROM is enabled  |  |  |

| 6          | BVSB is disabled       | BVSB is enabled     |  |  |

For a basic PDP11/20 (without a KT11-B Paging Option) set both switches 2 and 3 to the Off position.

RAM between  $760000_8$  and  $777777_8$  is disabled on the ME32K because this region is for I/O devices and ROMs. Note that in its standard configuration, the PDP11/20 will map addresses between  $160000_8$  and  $177777_8$  into this I/O region between  $760000_8$  and  $777777_8$ .

# 2.3 Installation

Once the ME32K is configured correctly, it can be installed in any PDP-11 Unibus Small Peripheral Option slot, such as those on a DD-11A System Unit or in slots 13 and 14 of the PDP11/20's CPU system unit (which are also for small peripheral options).

The ME32K occupies one Small Peripheral Option interface slot on the Unibus. It plugs into connectors C, D, and E, leaving connectors A, B (on the right) and slot F (on the left) unused.

A wire may be needed to connect the Unibus DC LO L signal to pin CxN1, where x is the slot number for the ME32K.

# 3 THEORY OF OPERATION

# 3.1 Block Diagram

# 3.2 Circuit Descriptions

# 3.2.1 Unibus Receivers, Drivers, and Transceivers

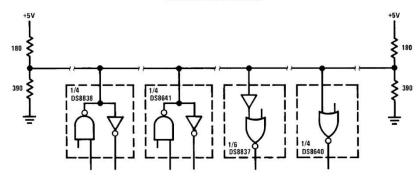

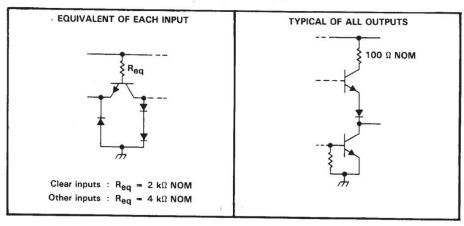

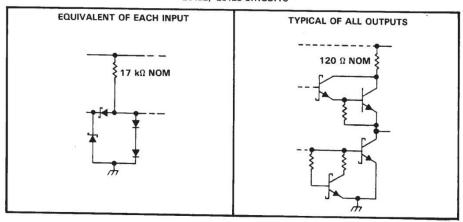

The single-direction Unibus receivers are the DS8640, which is equivalent to the DEC8640, as specified on page 4-1 of *PDP-11 Unibus(tm) Design Description* published by Digital Equipment Corporation.

The single-direction Unibus driver is the DEC8881, also as specified by DEC.

The eight address lines (A09, A10, and A12 through A17) that are driven by the ME32K during power-on boot are buffered using the bidirectional DS8641 transceiver, equivalent to the DEC 8641 as specified by DEC.

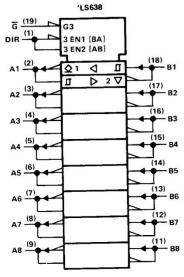

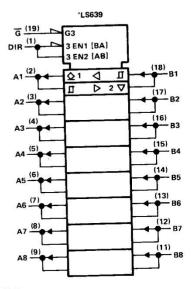

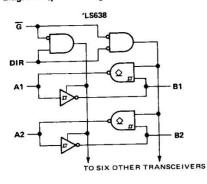

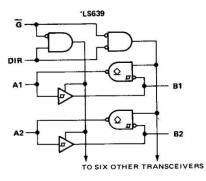

DEC did not specify a bus transceiver with a bidirectional bus on the both sides. The ME32K uses a 74LS639 for this purpose. The two 74LS639s are enabled whenever either RAMSEL or ROMSEL is true. Its direction is controlled by CO, which is low for read transactions and high for write transactions.

Data sheets for these ICs may be found in the Appendix.

### 3.2.2 RAM Address Decode

RAM address decode is shown in the upper-left corner of the schematic, comprising ICs E16, half of E23, and related gates, and 2 switches in SW4.

The two exclusive -OR gates in E23 (E23a and E23b) compare the DIP switch setting to Unibus address bits A16 and A17. If the Unibus address matches the DIP switch setting, then the outputs of both exclusive-OR gates will be high (true).

E16b and related gates detect addresses in the range that is reserved for PDP-11 I/O and ROM accesses. If the Unibus address is in this range then the output of E16b will be low (false), which will block RAM accesses.

E16a's output will be low (true) if the Unibus address matches the DIP switch selections, and the address does not match the I/O/ROM address range, and the Unibus MSYN signal is true. This output is SRAMSEL L, where low (true) means the cycle on the bus is accessing the ME32K's RAM.

### 3.2.3 ROM Address Decode

ROM address decode is directly below the RAM address decode on the schematic, comprising E14, E16b, three gates from E24, and two switches in SW4.

E14, E16b, and related gates decode ROM accesses for both the Low ROM address region and the High ROM address region. SW4 switches 4 and 5 independently enable/disable either ROM region.

E24a logically OR's the two region selects to produce the ROMSEL signal, which enables the EPROM outputs. The active-low Low ROM select signal drives EPROM address bit 8, so that the low half of every 512-word bank is Low ROM, and the high half is High ROM.

EPROM address signals A<11:A9> are connected to SW1 switches 2 through 4, selecting one of the eight possible ROM banks.

If the Vector Vector Address Switch Bank is enabled (via SW4 switch 6), then the EPROMs are disabled for the single 16-bit word at address 173024<sub>8</sub>.

# 3.2.4 Bootstrap Vector Address

The ME32K can provide a bootstrap vector address via the Vector Address Bank. The Vector Address Switch Bank is available only if High ROM is also enabled (by closing SW3 switch 4). When enabled (by closing SW4 switch 6), reading from address 173024<sub>8</sub> will read from the Vector Address Switch Bank (SW2 and SW3. This address is decoded by E17, E18, and related gates.

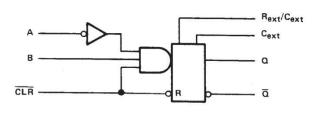

### 3.2.5 Power-On Boot

When enabled (by opening SW1 switch 1), the ME32K will force address bits 9-10 and 12-17 high during the first two Unibus transactions after the Unibus DC LO signal goes false. During these Unibus transactions, the PDP11/20's CPU will attempt to read from address  $000024_8$  for its initial Program Counter value, and from  $000026_8$  for its initial Status Register value. The Power-On Boot logic changes these addresses to  $173024_8$  and  $173026_8$ .

When Power-On Boot is enabled, E12 holds the VECTOR signal true until the end of the second MSYNC pulse. While VECTOR is true, E4 and E8 drive the required address line to their "1" state. (Note that signals on the Unibus are active-low.)

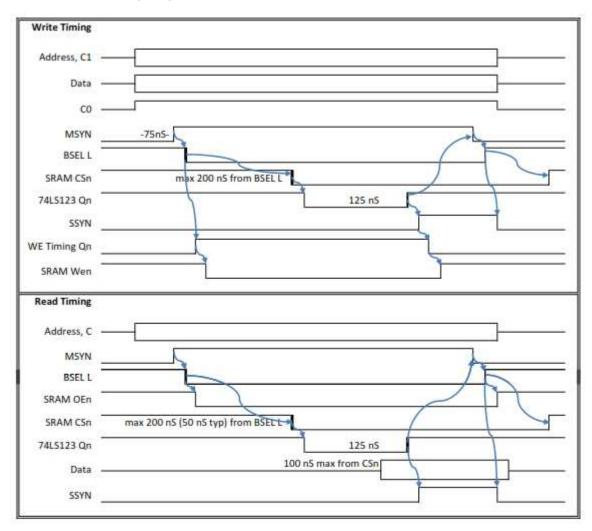

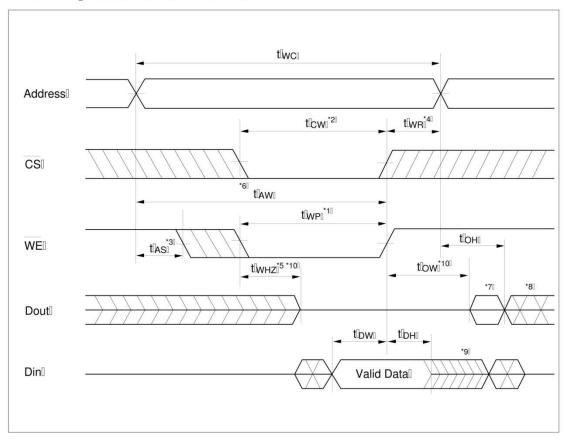

### 3.2.6 Access Timing

### Unibus

Unibus timing is completely asynchronous. When the current bus master wants to access memory, it puts the desired address on the Unibus address signals, sets the two Unibus control signals, CO and C1, appropriately for the type of transaction it needs, for a write cycle, puts the write data on the Unibus data signals, and then waits 150 nS to account for propagation delays, skew, and setup times. At this

point, the bus master sets MSYNC true to indicate the start of the transaction. The bus master will then wait until it gets a response from the bus slave (in this case the ME32K).

For a write cycle, the slave sets SSYN true once it has latched the data from the Unibus. For a read cycle, the slave sets SSYN true when the requested data is on the Unibus data signals.

When the bus master sees SSYN true, it waits 150 nS, then (in the case of a read cycle) latches the data from the Unibus. It then sets MSYN low, indicating the end of the cycle.

### **SRAM Accesses**

When the slave sees MSYN become false, it sets SSYN false, indicating that it is ready for another cycle.

The SRAM on the ME32K has 100 nS access time, meaning that data is stable on its data pins 100 nS from when Chip Select goes low (true).

The Chip Select signal is SRAMSEL L, after it passes through the MAX693 (discussed later). The propagation through the MAX693 is specified as 50 nS nominal, 200 nS maximum. Because of this long and loosely-specified propagation delay, the ME32K starts its SRAM cycle based on the the output of the MAX693.

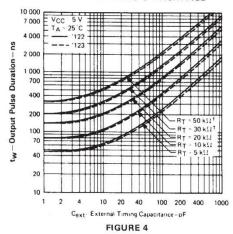

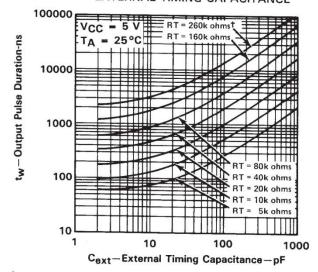

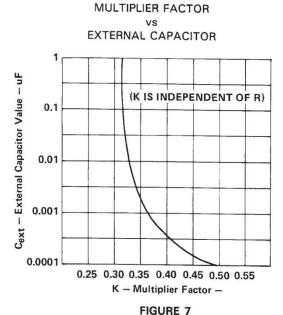

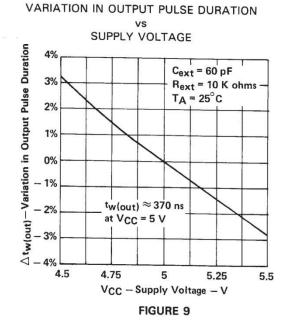

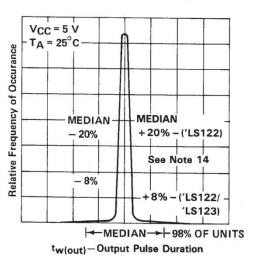

The low-going leading edge of the SRAM Chip Select signal triggers one-shot E26, whose output is configured to generate a negative pulse starting at the trigger and ending 125 nS later. The trailing edge of this pulse clocks a 1 into flip-flop E25b, which set the SSYN signal true on the Unibus SSYN remains true until the end of the MSYN pulse, as controlled by the bus master.

If CO indicates a write cycle, then flip-flop E25a's output goes high (true) when the output of E25b is true. E25a's output, combined with Unibus signals A0 and C1, generate the active-low write enable signals to the two SRAM chips. (See the table in section 1.3.) The Write Enable signals end when SSYN ends.

Gate E15A delays the start of the SSYN pulse until the SRAM write Enable signal is low (true), to guarantee stable data when the SRAM chips latch data at the leading edge of the Write Enable signal.

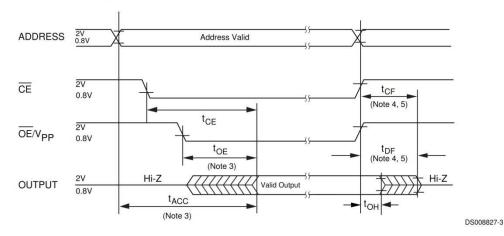

### **ROM Accesses**

The ME32K ROMs are specified to be 150 nS EPROMs, such as the Fairchild NMC27C32B. This means that their data signals will be stable no more that 150 nS after their address pins are stable and their Chip Enables pins are low (true).

Because the Chip Enable signals of the EPROMs are tied low (true), they will begin decoding their address as soon as it is stable, which will be long before ROMSEL is true. When ROMSEL becomes true (after MSYN becomes true), then the EPROM's outputs are enabled via their Output Enable signals. The access time for these EPROMs from Output Enable to stable data is specified as 60 nS maximum. This means that the 125 nS delay of the one-shot at E24 is adequate time for EPROM accesses.

During a ROM read cycle, the SSYN signal is started 125 nS after ROMSEL is high (true). This implies that the Unibus address signals must be stable 25 nS before MSYN becomes active.

### **RAM and ROM Timing Diagrams**

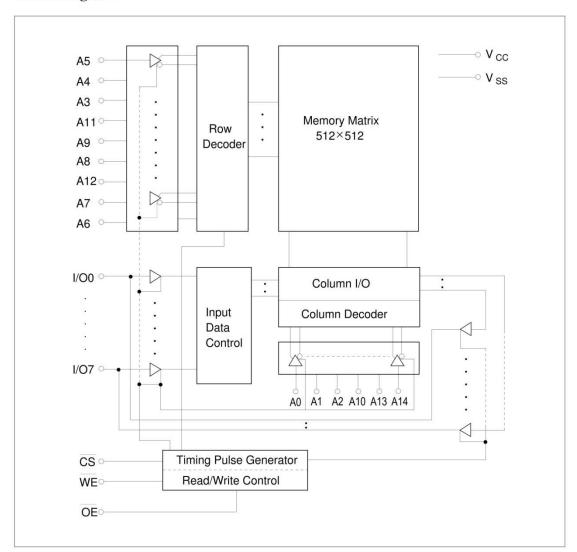

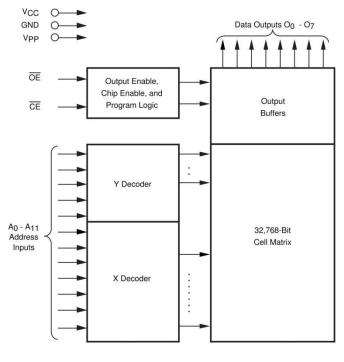

### 3.2.5 256x16 ROM

The ME32K's ROM comprises two 150 nS (or faster) 2732-type 4Kx8 EPROMs.. See the Fairchild NM27C32B data sheet in the Appendix for details.

Note that the data in the EPROMs are inverted if the two data buffer chips are 74LS639's. (74LS638s would allow for non-inverted EPROM data, but these seem to be unavailable.)

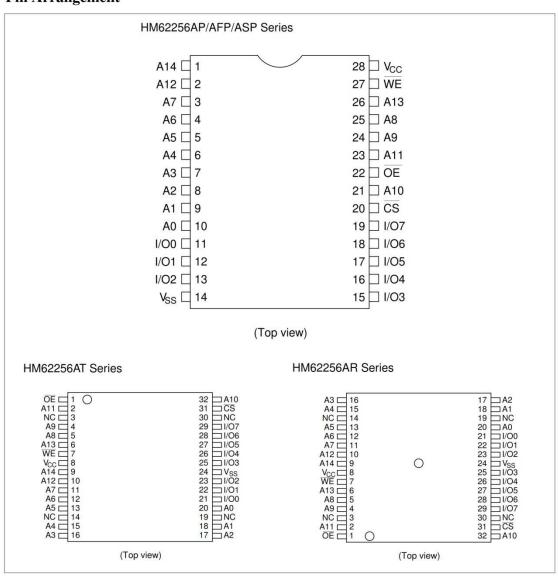

### 3.2.6 32Kx16 RAM

The ME32K's RAM comprises two 100 nS (or faster) 32Kx8 fully-static RAM chips, such as the Hitachi HM62256APL-100. See the Hitachi data sheet in the Appendix for details.

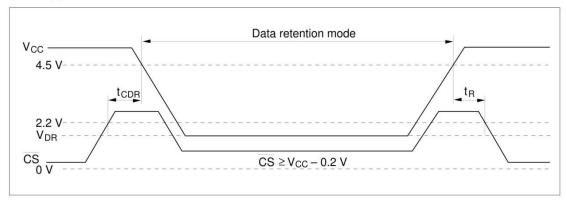

# 3.2.7 Battery Backup

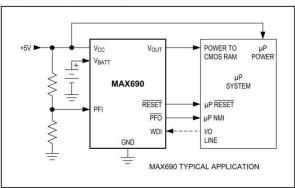

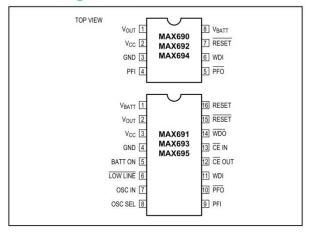

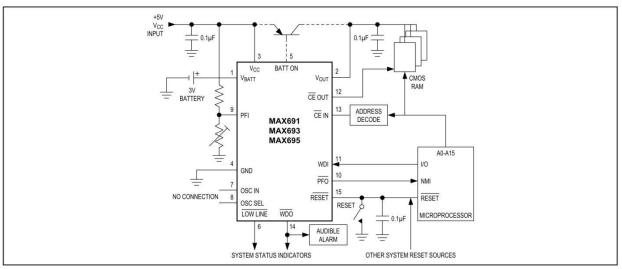

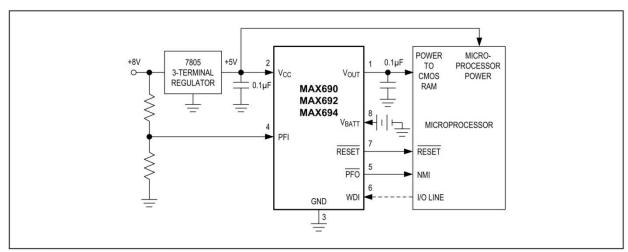

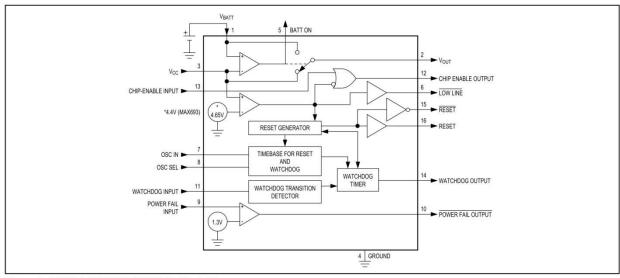

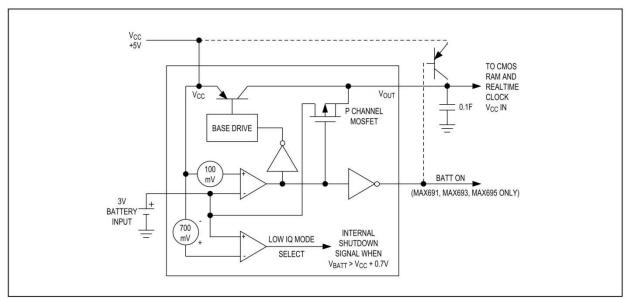

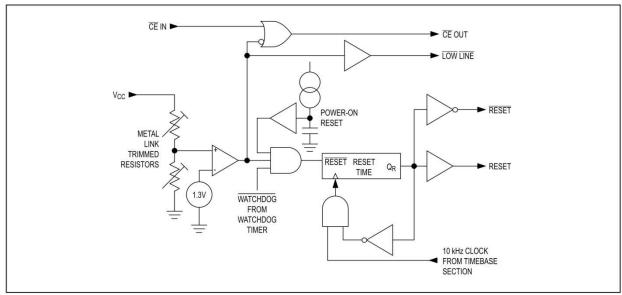

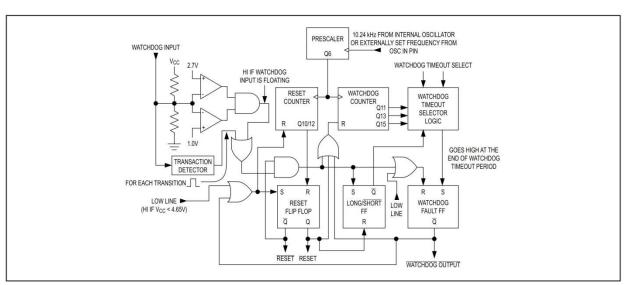

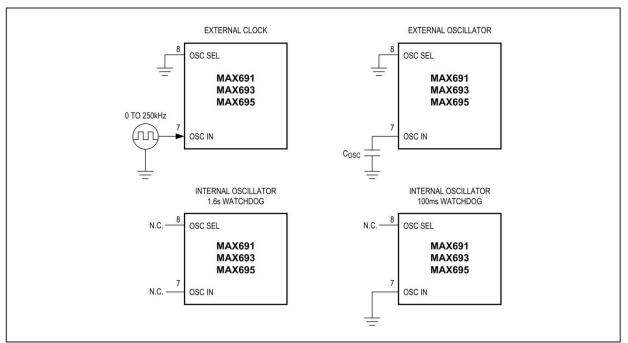

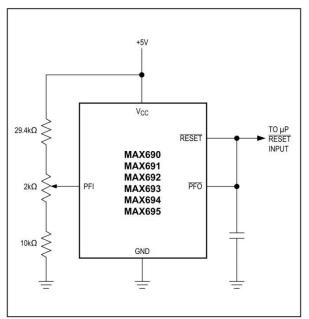

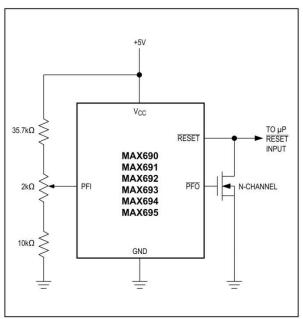

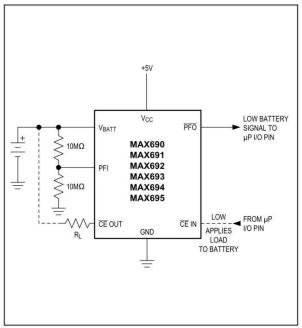

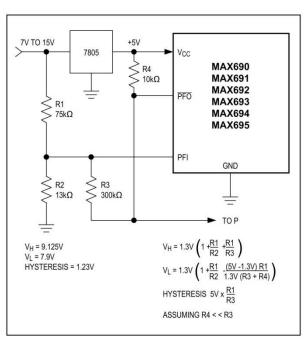

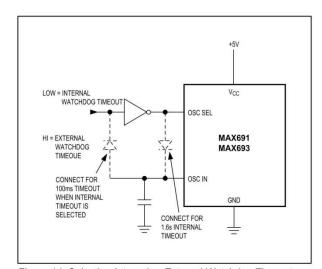

The SRAM chips are backed up with a nominally 3-volt battery. Backup is managed by a MAX693 Microprocessor Supervisory Circuit at location E21.

The MAX693 maintains the integrity of the data in SRAM. The ME32K's 5-volt supply drops below 4.4 volts, the MAX693 de-asserts the SRAM Chip Select signal (to prevent unintended writes), and switches over to the battery to power the SRAM chips. (Transistor Q1 boosts the current capability of the MAX693, so that most SRAM chips can be powered by this circuit.)

As discussed above, the propagation of the Chip Select signal through the MAX693 is surprisingly slow, with a maximum propagation delay of 200 nS. For this reason, the ME32K does not start timing SRAM accesses until the Chip Enable signal has made it through the MAX693.

Since the Chip Enable output of the MAX693 is driving a chip (E23c) that is not battery-backed, this signal is buffered by Schottkey diode D1, with resistor R6 acting as a pullup. This prevents the MAX693 from supplying any current to an unpowered IC at E23.

With the "L" version of the Hitachi SRAM chip, power consumption during standby is typically 0.3 uA, but could be as high as 100 uA for each of the two SRAM chips.

A CR2032 lithium coin cell battery has a capacity of 225 mAh. We can calculate how long this battery will last when powering the ME32K's SRAMs:

225,000 / (2\* 0.3) =375,000 hours, or 42 years, typical case.

225,000 / (2\*100) = 1125 hours, or 46 days, worst case.

An Energizer L92 lithium AAA battery has a capacity of 1250 mAh, We can calculate how long a pair of these batteries will last when powering the ME32K's SRAMs:

1,250,000 / (2\*0.3) = about 2,000,000 hours, or 238 years, typical case.

1,250,000 / (2\*100) = 6250 hours, or 260 days, worst case.

Without data, we can assume that the SRAM chips will tend to behave more like the typical case cited in the datasheet.

# **APPENDIX**

# **A.1 Bill of Materials**

| Part No.        | Device                           | Qty | Locations     | Comment                 |

|-----------------|----------------------------------|-----|---------------|-------------------------|

| 74LS00          | Quad 2-Input NAND                | 2   | E13, E24      |                         |

| 74LS04          | Hex Inverter                     | 2   | E15,E22       |                         |

| 74LS20          | Dual 4-Input NAND                | 1   | E16           |                         |

| 74LS27          | Triple 3Input NOR                | 1   | E17           |                         |

| 74LS30          | 8-Input NAND                     | 1   | E18           |                         |

| 74LS74          | Dual D-Type Flip-flop            | 2   | E12,E25       |                         |

| 74LS86          | Quad XOR                         | 1   | E23           |                         |

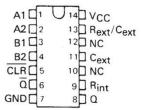

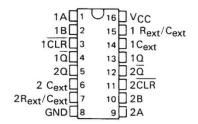

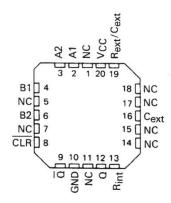

| 74LS123         | Dual One-Shot                    | 1   | E26           |                         |

| 74LS138         | 3:8 Decoder                      | 1   | E14           |                         |

| 74LS245         | 8-bit Bidirectional Buffer       | 2   | E28,E29       |                         |

| 74LS639         | 8-bit Bidirectional Buffer       | 2   | E1, E2        |                         |

| DS8640          | Quad Unibus Receiver             | 4   | E3,E4,E7,E9   | Equivalent: DEC8640     |

| DS8641          | Quad Unibus Transceiver          | 2   | E5,E8         | Equivalent: DEC8641     |

| 8881            | Quad Unibus Driver               | 1   | E6            |                         |

| NM27C32B        | 4K-byte EPROM                    | 2   | E18,E19       | Programmed              |

| HM62256ALP-10   | 100 nS 128K-byte SRAM            | 2   | E10,E11       | -10SL version is better |

| MAX693          | Microprocessor Supervisory Ckt   | 1   | E20           | Battery backup control  |

| IC Socket28     | 24-pin, 0.6" wide IC socket      | 2   | E18,E19       |                         |

| DIPSW, 4 Pos    | 4-position DIP Switch            | 1   | SW1           |                         |

| DIPSW, 6 Pos    | 6-position DIP Switch            | 1   | SW4           |                         |

| DIPSW, 8 Pos    | 8-position DIP Switch            | 2   | SW2,SW3       |                         |

| BAT46           | Schottkey Diode                  | 1   | D1            |                         |

| Cap, 0.1 uF     | 0.1 uF Ceramic Capacitor         | 29  | C1-C29        |                         |

| Cap, 100 pF, 5% | 100 pF±5% Ceramic Capacitor      | 1   | C30           |                         |

| Cap, 10uF 10V   | 10 uF 10V Electrolytic Capacitor | 3   | C31-C33       |                         |

| Res, 1K         | 1KΩ±5% Resistor                  | 2   | R4,R5         |                         |

| Res, 4.7K       | 4.7KΩ±5% Resistor                | 10  | R1-R3, R6-R12 |                         |

| Res, 1.74K, 1%  | 1.74KΩ±1% Resistor               | 1   | R13           |                         |

| 2N6520          | NPN Transistor                   | 1   | Q1            |                         |

| 122-2620-GR     | 20mm Coin Cell Battery Holder    | 1   | B1            | Option: either B1 or B2 |

| 12BH425P-GR     | Double AAA battery holder        | 0   | B2            | Option: either B1 or B2 |

# **A.2 Component Specifications**

Following are data sheets for some of the less-common components used on the ME32K

# Maintenance only

### 32,768-word × 8-bit High Speed CMOS Static RAM

The Hitachi HM62256A is a CMOS static RAM organized 32-kword  $\times$  8-bit. It realizes higher performance and low power consumption by employing 0.8  $\mu$ m Hi-CMOS process technology. The device, packaged in a 8  $\times$  14 mm TSOP with thickness of 1.2 mm, 450-mil SOP (foot print pitch width), 600-mil plastic DIP, or 300-mil plastic DIP, is available for high density mounting. TSOP package is suitable for cards, and reverse type TSOP is also provided. It offers low power standby power dissipation; therefore, it is suitable for battery back up system.

### **Features**

- High speed: Fast Access time 85/100/120/150 ns (max)

- Low Power

Standby: 5 μW (typ) (L/L-SL version)

Operation: 40 mW (typ) (f = 1 MHz)

- Single 5 V supply

- Completely static memory No clock or timing strobe required

- · Equal access and cycle times

- Common data input and output: Three state output

- · Directly TTL compatible: All inputs and outputs

- Capability of battery back up operation

# **Ordering Information**

| Type No.          | Access time | Package     |

|-------------------|-------------|-------------|

| HM62256AP-8       | 85 ns       | 600-mil     |

| HM62256AP-10      | 100 ns      | 28-pin      |

| HM62256AP-12      | 120 ns      | plastic DIP |

| HM62256AP-15      | 150 ns      | (DP-28)     |

| HM62256ALP-8      | 85 ns       |             |

| HM62256ALP-10     | 100 ns      |             |

| HM62256ALP-12     | 120 ns      |             |

| HM62256ALP-15     | 150 ns      |             |

| HM62256ALP-8SL    | 85 ns       |             |

| HM62256ALP-10SL   | 100 ns      |             |

| HM62256ALP-12SL   | 120 ns      |             |

| HM62256ALP-15SL   | 150 ns      |             |

| HM62256ASP-8      | 85 ns       | 300-mil     |

| HM62256ASP-10     | 100 ns      | 28-pin      |

| HM62256ASP-12     | 120 ns      | plastic DIP |

| HM62256ASP-15     | 150 ns      | (DP-28NA)   |

| HM62256ALSP-8     | 85 ns       |             |

| HM62256ALSP-10    | 100 ns      |             |

| HM62256ALSP-12    | 120 ns      |             |

| HM62256ALSP-15    | 150 ns      |             |

| HM62256ALSP-8SL   | 85 ns       |             |

| HM62256ALSP-10SL  | 100 ns      |             |

| HM62256ALSP-12SL  | 120 ns      |             |

| HM62256ALSP-15SL  | 150 ns      |             |

| HM62256AFP-8T     | 85 ns       | 450-mil     |

| HM62256AFP-10T    | 100 ns      | 28-pin      |

| HM62256AFP-12T    | 120 ns      | plastic SOP |

| HM62256AFP-15T    | 150 ns      | (FP-28DA)   |

| HM62256ALFP-8T    | 85 ns       |             |

| HM62256ALFP-10T   | 100 ns      |             |

| HM62256ALFP-12T   | 120 ns      |             |

| HM62256ALFP-15T   | 150 ns      |             |

| HM62256ALFP-8SLT  | 85 ns       |             |

| HM62256ALFP-10SLT | 100 ns      |             |

| HM62256ALFP-12SLT | 120 ns      |             |

| HM62256ALFP-15SLT | 150 ns      |             |

|                   |             |             |

Note: This device is not available for new application.

# HM62256A Series

### **TSOP Series**

| Access time | Package                                                          | Type No.                                                                                     | Access time                                                                                                                                                                                                              | Package                                                                                                                                                                                                               |

|-------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 85 ns       | 8 mm × 14 mm                                                     | HM62256ALR-8                                                                                 | 85 ns                                                                                                                                                                                                                    | 8 mm × 14 mm                                                                                                                                                                                                          |

| 100 ns      | 32-pin TSOP                                                      | HM62256ALR-10                                                                                | 100 ns                                                                                                                                                                                                                   | 32-pin TSOP                                                                                                                                                                                                           |

| 120 ns      | (normal type)                                                    | HM62256ALR-12                                                                                | 120 ns                                                                                                                                                                                                                   | (reverse type)                                                                                                                                                                                                        |

| 150 ns      | (TFP-32DA)                                                       | HM62256ALR-15                                                                                | 150 ns                                                                                                                                                                                                                   | (TFP-32DAR)                                                                                                                                                                                                           |

| 85 ns       |                                                                  | HM62256ALR-8SL                                                                               | 85 ns                                                                                                                                                                                                                    |                                                                                                                                                                                                                       |

| 100 ns      |                                                                  | HM62256ALR-10SL                                                                              | 100 ns                                                                                                                                                                                                                   |                                                                                                                                                                                                                       |

| 120 ns      |                                                                  | HM62256ALR-12SL                                                                              | 120 ns                                                                                                                                                                                                                   |                                                                                                                                                                                                                       |

| 150 ns      |                                                                  | HM62256ALR-15SL                                                                              | 150 ns                                                                                                                                                                                                                   |                                                                                                                                                                                                                       |

|             | 85 ns<br>100 ns<br>120 ns<br>150 ns<br>85 ns<br>100 ns<br>120 ns | 100 ns 32-pin TSOP<br>120 ns (normal type)<br>150 ns (TFP-32DA)<br>85 ns<br>100 ns<br>120 ns | 85 ns 8 mm × 14 mm HM62256ALR-8<br>100 ns 32-pin TSOP HM62256ALR-10<br>120 ns (normal type) HM62256ALR-12<br>150 ns (TFP-32DA) HM62256ALR-15<br>85 ns HM62256ALR-8SL<br>100 ns HM62256ALR-10SL<br>120 ns HM62256ALR-12SL | 85 ns 8 mm × 14 mm 100 ns 32-pin TSOP HM62256ALR-10 100 ns 120 ns (normal type) HM62256ALR-12 120 ns 150 ns (TFP-32DA) HM62256ALR-15 150 ns HM62256ALR-8SL 85 ns 100 ns HM62256ALR-10SL 100 ns HM62256ALR-12SL 120 ns |

# **Pin Arrangement**

# HM62256A Series

# **Pin Description**

| Symbol      | Function     |  |  |  |  |  |

|-------------|--------------|--|--|--|--|--|

| A0 – A14    | Address      |  |  |  |  |  |

| I/O0 – I/O7 | Input/output |  |  |  |  |  |

| CS          | Chip select  |  |  |  |  |  |

| WE          | Write enable |  |  |  |  |  |

| Symbol          | Function      |   |  |  |  |  |

|-----------------|---------------|---|--|--|--|--|

| ŌĒ              | Output enable | - |  |  |  |  |

| NC              | No connection | _ |  |  |  |  |

| V <sub>CC</sub> | Power supply  | - |  |  |  |  |

| V <sub>SS</sub> | Ground        | _ |  |  |  |  |

# **Block Diagram**

# HM62256A Series

# **Function Table**

| WE | CS | ŌĒ | Mode           | V <sub>CC</sub> current            | I/O pin | Ref. cycle         |

|----|----|----|----------------|------------------------------------|---------|--------------------|

| X  | Н  | Х  | Not selected   | I <sub>SB</sub> , I <sub>SB1</sub> | High-Z  | —                  |

| Н  | L  | Н  | Output disable | Icc                                | High-Z  |                    |

| Н  | L  | L  | Read           | Icc                                | Dout    | Read cycle (1)–(3) |

| L  | L  | Н  | Write          | Icc                                | Din     | Write cycle (1)    |

| Ĺ  | L  | L  | Write          | Icc                                | Din     | Write cycle (2)    |

Note: X: H or L

# **Absolute Maximum Ratings**

| Parameter                                      | Symbol         | Value                      | Unit |  |

|------------------------------------------------|----------------|----------------------------|------|--|

| Voltage on any pin relative to V <sub>SS</sub> | V <sub>T</sub> | -0.5 <sup>*1</sup> to +7.0 | V    |  |

| Power dissipation                              | P <sub>T</sub> | 1.0                        | W    |  |

| Operating temperature                          | Topr           | 0 to +70                   | °C   |  |

| Storage temperature                            | Tstg           | -55 to +125                | °C   |  |

| Storage temperature under bias                 | Tbias          | -10 to +85                 | °C   |  |

Note: 1.  $V_T \min = -3.0 \text{ V for pulse half-width} \le 50 \text{ ns}$

# **Recommended DC Operating Conditions** (Ta = $0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter                    | Symbol          | Min                | Тур | Max | Unit |

|------------------------------|-----------------|--------------------|-----|-----|------|

| Supply voltage               | V <sub>CC</sub> | 4.5                | 5.0 | 5.5 | V    |

|                              | V <sub>SS</sub> | 0                  | 0   | 0   | V    |

| Input high (logic 1) voltage | V <sub>IH</sub> | 2.2                | _   | 6.0 | V    |

| Input low (logic 0) voltage  | V <sub>IL</sub> | -0.5 <sup>*1</sup> | -   | 0.8 | V    |

Note: 1.  $V_{IL} min = -3.0 V$  for pulse half-width  $\leq 50 ns$

# **HM62256A Series**

DC Characteristics (Ta = 0 to +70°C,  $V_{CC}$  = 5 V ± 10%,  $V_{SS}$  = 0 V)

| Parameter              |                                                         | Symbol           | Min                                 | Typ*1                | Max                  | Unit | Test conditions                                                                                                                                                                                                                        |

|------------------------|---------------------------------------------------------|------------------|-------------------------------------|----------------------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input leakaç           | ge current                                              | IILII            | ::::::::::::::::::::::::::::::::::: | -                    | 1                    | μΑ   | Vin = V <sub>SS</sub> to V <sub>CC</sub>                                                                                                                                                                                               |

| Output leakage current |                                                         | I <sub>LO</sub>  | à <del></del>                       | _                    | 1                    | μА   | $\overline{\text{CS}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{OE}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{WE}} = \text{V}_{\text{IL}},$ $\text{V}_{\text{I/O}} = \text{V}_{\text{SS}} \text{ to V}_{\text{CC}}$ |

| Operating V            | CC current                                              | I <sub>CC</sub>  | 37                                  | 6                    | 15                   | mA   | $\overline{\text{CS}} = \text{V}_{\text{IL}}, \text{ others} = \text{V}_{\text{IH}}/\text{V}_{\text{IL}}$ $\text{lout} = 0 \text{ mA}$                                                                                                 |

|                        | HM62256A-8<br>HM62256A-10<br>HM62256A-12<br>HM62256A-15 | I <sub>CC1</sub> |                                     | 33<br>30<br>27<br>24 | 50<br>50<br>45<br>40 | mA   | $\frac{\text{min cycle, duty} = 100\%, I_{I/O} = 0 \text{ mA}}{\overline{\text{CS}}} = V_{IL}, \text{ others} = V_{IH}/V_{IL}$                                                                                                         |

|                        |                                                         | I <sub>CC2</sub> | \$* <del></del> *                   | 5                    | 15                   | mA   | Cycle time = $1\mu$ s, $I_{I/O} = 0$ mA<br>$\overline{CS} = V_{IL}$ , $V_{IH} = V_{CC}$ , $V_{IL} = 0$                                                                                                                                 |

| Standby V <sub>C</sub> | C current                                               | I <sub>SB</sub>  |                                     | 0.3                  | 2                    | mA   | CS = V <sub>IH</sub>                                                                                                                                                                                                                   |

|                        |                                                         | I <sub>SB1</sub> | _                                   | 0.01                 | 1                    | mA   | $\frac{\text{Vin} \ge 0 \text{ V}}{\text{CS}} > \text{V} \qquad 0.2 \text{ V}$                                                                                                                                                         |

|                        |                                                         |                  | _                                   | 0.3*2                | 100*2                | μΑ   | - <del>CS</del> ≥ V <sub>CC</sub> – 0.2 V                                                                                                                                                                                              |

|                        |                                                         |                  |                                     | 0.3*3                | 50 <sup>*3</sup>     | μΑ   | -                                                                                                                                                                                                                                      |

| Output low             | voltage                                                 | V <sub>OL</sub>  | ×                                   | _                    | 0.4                  | ٧    | I <sub>OL</sub> = 2.1 mA                                                                                                                                                                                                               |

| Output high            | voltage                                                 | V <sub>OH</sub>  | 2.4                                 |                      |                      | V    | I <sub>OH</sub> = -1.0 mA                                                                                                                                                                                                              |

Typical values are at V<sub>CC</sub> = 5.0 V, Ta = +25°C and not guaranteed.

This characteristics is guaranteed only for L-version.

This characteristics is guaranteed only for L-SL version.

# Capacitance $(Ta = 25^{\circ}C, f = 1 \text{ MHz})^{*1}$

| Parameter                | Symbol           | Min | Тур         | Max | Unit | Test conditions        |

|--------------------------|------------------|-----|-------------|-----|------|------------------------|

| Input capacitance        | Cin              | _   | _           | 6   | pF   | Vin = 0 V              |

| Input/output capacitance | C <sub>I/O</sub> | =   | <del></del> | 8   | pF   | V <sub>I/O</sub> = 0 V |

Note: 1. This parameter is sampled and not 100% tested.

AC Characteristics (Ta = 0 to +70°C,  $V_{CC}$  = 5 V  $\pm$  10%, unless otherwise noted.)

# **Test Conditions**

• Input pulse levels: 0.8 V to 2.4 V

• Input and output timing refernce levels: 1.5 V

• Input rise and fall times: 5 ns

• Output load: 1 TTL Gate + C<sub>L</sub> (100 pF) (Including scope & jig)

# Read Cycle

|                                      |                  | HM622 | 256A-8 | HM62 | 256A-10 | HM622 | 256A-12 | HM622 | 256A-15 |      |      |

|--------------------------------------|------------------|-------|--------|------|---------|-------|---------|-------|---------|------|------|

| Parameter                            | Symbol           | Min   | Max    | Min  | Max     | Min   | Max     | Min   | Max     | Unit | Note |

| Read cycle time                      | t <sub>RC</sub>  | 85    | _      | 100  | _       | 120   | _       | 150   |         | ns   |      |

| Address access time                  | t <sub>AA</sub>  | -     | 85     | _    | 100     | F     | 120     | -     | 150     | ns   |      |

| Chip select access time              | t <sub>ACS</sub> | _     | 85     | _    | 100     | -     | 120     | _     | 150     | ns   |      |

| Output enable to output valid        | t <sub>OE</sub>  | _     | 45     | _    | 50      |       | 60      | a*    | 70      | ns   |      |

| Chip selection to output in low-Z    | <sup>t</sup> CLZ | 10    | N      | 10   | _       | 10    | _       | 10    | _       | ns   | 2    |

| Output enable to output in low-Z     | <sup>t</sup> OLZ | 5     | _      | 5    | _       | 5     | _       | 5     | _       | ns   | 2    |

| Chip deselection to output in high-Z | t <sub>CHZ</sub> | 0     | 30     | 0    | 35      | 0     | 40      | 0     | 50      | ns   | 1, 2 |

| Output disable to output in high-Z   | t <sub>OHZ</sub> | 0     | 30     | 0    | 35      | 0     | 40      | 0     | 50      | ns   | 1, 2 |

| Output hold from address change      | <sup>t</sup> OH  | 5     | -      | 10   | -       | 10    | _       | 10    | -       | ns   |      |

# HM62256A Series

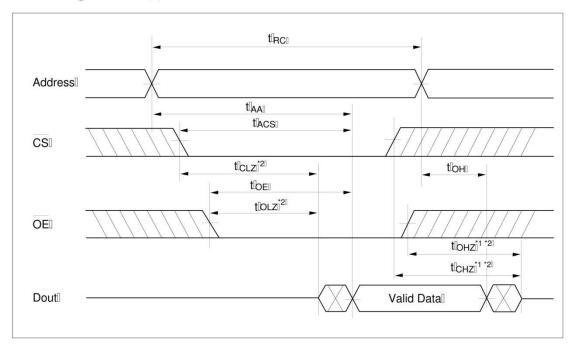

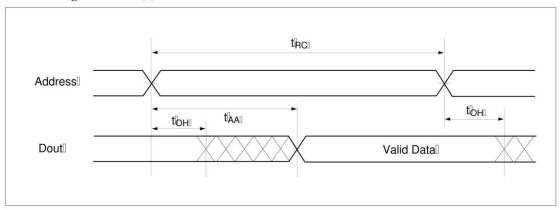

# Read Timing Waveform (1) \*3

# Read Timing Waveform (2) \*3 \*4 \*6

# HM62256A Series

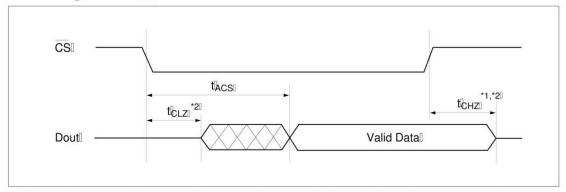

# Read Timing Waveform (3) \*3 \*5 \*6

- Notes: 1.  $t_{CHZ}$  and  $t_{OHZ}$  are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- 2. This parameter is sampled and not 100% tested.

- WE is high for read cycle.

Device is continuously selected, S = V<sub>IL</sub>.

Address Valid prior to or coincident with S transition Low.

- 6.  $\overline{OE} = V_{IL}$ .

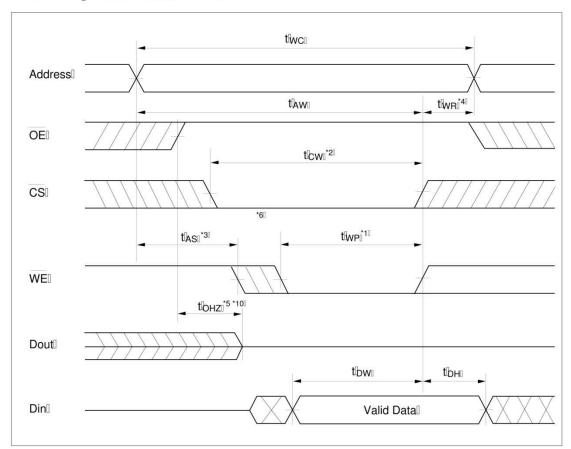

# Write Cycle

|                                    |                  | HM622 | 256A-8            | HM62 | 256A-10 | HM622 | 256A-12      | HM622 | 256A-15 |      |        |

|------------------------------------|------------------|-------|-------------------|------|---------|-------|--------------|-------|---------|------|--------|

| Parameter                          | Symbol           | Min   | Max               | Min  | Max     | Min   | Max          | Min   | Max     | Unit | Note   |

| Write cycle time                   | t <sub>WC</sub>  | 85    | ),                | 100  | _       | 120   |              | 150   | _       | ns   |        |

| Chip selection to end of write     | t <sub>CW</sub>  | 75    | 88                | 80   | _       | 85    | _            | 100   |         | ns   | 2      |

| Address setup time                 | t <sub>AS</sub>  | 0     | S:                | 0    | _       | 0     | _            | 0     | _       | ns   | 3      |

| Address valid to end of write      | t <sub>AW</sub>  | 75    | -                 | 80   | _       | 85    | -            | 100   | _       | ns   |        |

| Write pulse width                  | t <sub>WP</sub>  | 55    | (: <del></del> ): | 60   | _       | 70    | _            | 90    |         | ns   | 1      |

| Write recovery time                | t <sub>WR</sub>  | 0     | ),====            | 0    | _       | 0     | <del>-</del> | 0     | _       | ns   | 4      |

| WE to output in high-Z             | t <sub>WHZ</sub> | 0     | 30                | 0    | 35      | 0     | 40           | 0     | 50      | ns   | 10     |

| Data to write time overlap         | t <sub>DW</sub>  | 40    | B4 <del></del> 3  | 40   |         | 50    | _            | 60    | _       | ns   |        |

| Data hold from write time          | t <sub>DH</sub>  | 0     | _                 | 0    | -       | 0     | -            | 0     | -       | ns   |        |

| Output active from end of write    | t <sub>OW</sub>  | 5     | _                 | 5    | _       | 5     | -            | 5     |         | ns   | 10     |

| Output disable to output in high-Z | t <sub>OHZ</sub> | 0     | 30                | 0    | 35      | 0     | 40           | 0     | 50      | ns   | 10, 11 |

# Write Timing Waveform (1) $(\overline{OE} \text{ Clock})$

### Write Timing Waveform (2) (OE Low Fixed)

- Notes: 1. A write occurs during the overlap of a low  $\overline{CS}$  and a low  $\overline{WE}$ . A write begins at the later transition of  $\overline{CS}$  going low or  $\overline{WE}$  going low. A write ends at the earlier transition of  $\overline{CS}$  going high or  $\overline{WE}$  going high.  $t_{WP}$  is measured from the beginning of write to the end of write.

- 2.  $t_{CW}$  is measured from  $\overline{CS}$  going low to the end of write.

- 3.  $t_{AS}$  is measured from the address valid to the beginning of write.

- 4. twB is measured from the earlier of WE or CS going high to the end of write cycle.

- 5. During this period, I/O pins are in the output state so that the input signals of the opposite phase to the outputs must not be applied.

- 6. If the  $\overline{\text{CS}}$  low transition occurs simultaneously with the  $\overline{\text{WE}}$  low transition or after the  $\overline{\text{WE}}$  transition, the output remain in a high impedance state.

- 7. Dout is the same phase of the write data of this write cycle.

- 8. Dout is the read data of next address.

- 9. If  $\overline{\text{CS}}$  is low during this period, I/O pins are in the output state. Therefore, the input signals of the opposite phase to the output must not be applied to them.

- 10. This parameter is sampled and not 100% tested.

- 11.  $t_{OHZ}$  and  $t_{WHZ}$  are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

# Low $V_{CC}$ Data Retention Characteristics (Ta = 0 to +70°C)

This characteristics is guaranteed only for L/L-SL version.

| Parameter                            | Symbol           | Min                | Typ*1 | Max              | Unit | Test conditions                                                                      |

|--------------------------------------|------------------|--------------------|-------|------------------|------|--------------------------------------------------------------------------------------|

| V <sub>CC</sub> for data retention   | $V_{DR}$         | 2                  | _     | 19               | ٧    | $\overline{\text{CS}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V, Vin} \ge 0 \text{ V}$ |

| Data retention current               | ICCDR            | _                  | 0.2   | 30*2             | μΑ   | V <sub>CC</sub> = 3.0 V, Vin ≥ 0 V                                                   |

|                                      |                  | _                  | 0.2   | 10 <sup>*3</sup> | μΑ   | $\overline{\text{CS}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V}$                      |

| Chip deselect to data retention time | t <sub>CDR</sub> | 0                  | _     | ō— <u>-</u> s:   | ns   | See retention waveform                                                               |

| Operation recovery time              | t <sub>R</sub>   | t <sub>RC</sub> *4 |       | s                | ns   | _                                                                                    |

# Low V<sub>CC</sub> Data Retention Timing Waveform

- 1 Typical values are at  $V_{CC}=3.0$  V,  $T_{a}=+25$ °C and not guaranteed. 2. 20  $\mu$ A max at  $T_{a}=0$  to +40°C. (only for L-version) 3. 3  $\mu$ A max at  $T_{a}=0$  to +40°C. (only for L-SL version) Notes: 1

- 4. t<sub>RC</sub> = read cycle time.

5. CS controls address buffer, WE buffer, OE buffer, and Din buffer. If CS controls data retention mode, Vin levels (address,  $\overline{\text{WE}}$ ,  $\overline{\text{OE}}$ , I/O) can be in the high impedance state.

January 1999

# NMC27C32B 32,768-Bit (4096 x 8) CMOS EPROM

# **General Description**

The NMC27C32B is a 32k UV erasable and electrically reprogrammable CMOS EPROM, ideally suited for applications where fast turnaround, pattern experimentation and low power consumption are important requirements.

The NMC27C32B is designed to operate with a single +5V power supply with  $\pm 10\%$  tolerance.

The NMC27C32B is packaged in a 24-pin dual-in-line package with a quartz window. The quartz window allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written electrically into the device by following the programming procedure.

This EPROM is fabricated with Fairchild's proprietary, time proven CMOS double-poly silicon gate technology which combines high performance and high density with low power consumption and excellent reliability.

### **Features**

- Low CMOS power consumption

- Active Power: 55 mW Max

- Standby Power: 0.55 mW Max

- Industrial temperature range, -40°C to +85°C

- Fast and reliable programming

- TTL, CMOS compatible inputs/outputs

- TRI-STATE ® output

- Manufacturer's identification code for automatic programming

- High current CMOS level output drivers

- Compatible with NMOS 2732

# **Block Diagram**

DS008827-1

© 1998 Fairchild Semiconductor Corporation NMC27C32B Rev. C

1

www.fairchildsemi.com

# **Connection Diagram**

|                  | 27C16<br>2716  | 27C64<br>2764  | 27C128<br>27128 | 27C256<br>27256 |

|------------------|----------------|----------------|-----------------|-----------------|

| NN               |                | Vpp            | V <sub>PP</sub> | V <sub>PP</sub> |

| Dual-ii          |                | A12            | A12             | A12             |

| A7 1             | A7             | A7             | A7              | A7              |

| A6 2             | A <sub>6</sub> | A <sub>6</sub> | A <sub>6</sub>  | A <sub>6</sub>  |

| A5 3             | A <sub>5</sub> | A <sub>5</sub> | A5              | A5              |

| A4 4             | A <sub>4</sub> | A <sub>4</sub> | A <sub>4</sub>  | A <sub>4</sub>  |

| A3 5             | Аз             | Аз             | Аз              | Аз              |

| A2 6             | A <sub>2</sub> | A <sub>2</sub> | A <sub>2</sub>  | A <sub>2</sub>  |

| A1 🗆 7           | A <sub>1</sub> | A <sub>1</sub> | A <sub>1</sub>  | A <sub>1</sub>  |

| A0 8             | A <sub>0</sub> | A <sub>0</sub> | A <sub>0</sub>  | A <sub>0</sub>  |

| 00 9             | 00             | 00             | 00              | 00              |

| 01 🗆 1           | 01             | 01             | 01              | 01              |

| O <sub>2</sub> 1 | 02             | 02             | 02              | 02              |

| GND 1            | GND            | GND            | GND             | GND             |

|                | al-in-lin | J L | -      |

|----------------|-----------|-----|--------|

| A7             | 1         | 24  | VCC    |

| A6             | 2         | 23  | A8     |

| A5             | 3         | 22  | A9     |

| A <sub>4</sub> | 4         | 21  | A11    |

| Аз             | 5         | 20  | OE/VPF |

| A <sub>2</sub> | 6         | 19  | A10    |

| A <sub>1</sub> | 7         | 18  | CE     |

| A <sub>0</sub> | 8         | 17  | 07     |

| 00             | 9         | 16  | 06     |

| 01             | 10        | 15  | 05     |

| 02             | 11        | 14  | 04     |

| GND            | 12        | 13  | O3     |

| 27C16<br>2716 | 27C64<br>2764 | 27C128<br>27128 | 27C256<br>27256 |

|---------------|---------------|-----------------|-----------------|

|               | Vcc           | Vcc             | Vcc             |

|               | PGM           | PGM             | A14             |

| Vcc           | NC            | A13             | A13             |

| A8            | Ag            | A8              | A8              |

| A9            | A9            | A9              | A9              |

| VPP           | A11           | A11             | A11             |

| OE            | OE            | OE              | OE              |

| A10           | A10           | A10             | A10             |

| CE            | CE            | CE              | CE              |

| 07            | 07            | 07              | 07              |

| 06            | 06            | 06              | 06              |

| 05            | 05            | 05              | 05              |

| 04            | 04            | 04              | 04              |

| 03            | О3            | О3              | 03              |

Note: Socket compatible EPROM pin configurations are shown in the blocks adjacent to the NMC27C32B pin.

DS008827-2

# Order Number NMC27C32BQ See Package Number J24AQ

# **Pin Names**

| A0-A11          | Addresses           |

|-----------------|---------------------|

| CE              | Chip Enable         |

| ŌĒ              | Output Enable       |

| V <sub>PP</sub> | Programming Voltage |

| O0 -O7          | Outputs             |

| V <sub>CC</sub> | Power Supply        |

| GND             | Ground              |

# Commercial Temp Range (0°C to +70°C) $V_{CC}$ = 5V $\pm 10\%$

| Parameter/Order Number | Access Time (ns) |

|------------------------|------------------|

| NMC27C32BQ150          | 150              |

| NMC27C32BQ200          | 200              |

# Industrial Temp Range (-40°C to +85°C) $V_{CC}$ = 5V $\pm 10\%$

| Parameter/Order Number | Access Time (ns) |

|------------------------|------------------|

| NMC27C32BQE200         | 200              |

2

www.fairchildsemi.com

Absolute Maximum Ratings (Note 1)

Temperature Under Bias -40°C to +85°C

Storage Temperature -65°C to +150°C

V<sub>CC</sub> Supply Voltage with

Respect to Ground +7.0V to -0.6V

All Input Voltages except A9

and OE/V<sub>PP</sub> with

Respect to Ground (Note 9) +6.5V to -0.6V

All Output Voltages with

Respect to Ground (Note 9) V<sub>CC</sub> +1.0V to GND-0.6V

OE/V<sub>PP</sub> Supply and A9 Voltage with

Respect to Ground

+14.0V to -0.6V

Power Dissipation 1.0W

Lead Temperature (Soldering, 10 sec.) 300°C

**Operating Conditions** (Note 6)

Temperature Range

NMC27C32BQ150, 200 0°C to +70°C NMC27C32BQE 200 -40°C to +85°C

$V_{CC}$  Power Supply +5V  $\pm 10\%$

# **READ OPERATION**

# **DC Electrical Characteristics**

| Symbol             | Parameter                                        | Conditions                                                                                 | Min                   | Тур  | Max                | Units |

|--------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|------|--------------------|-------|

| ILI                | Input Load Current                               | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                   |                       | 0.01 | 1                  | μА    |

| I <sub>PP</sub>    | OE/V <sub>PP</sub> Load Current                  | OE/V <sub>PP</sub> = V <sub>CC</sub> or GND                                                |                       |      | 10                 | μА    |

| I <sub>LO</sub>    | Output Leakage Current                           | $V_{OUT} = V_{CC}$ or GND, $\overline{CE} = V_{IH}$                                        |                       | 0.01 | 1                  | μА    |

| I <sub>CC1</sub>   | V <sub>CC</sub> Current (Active)<br>TTL Inputs   | CE = V <sub>IL</sub> , f=5 MHz<br>Inputs = V <sub>IH</sub> or V <sub>IL</sub> , I/O = 0 mA |                       | 5    | 20                 | mA    |

| I <sub>CC2</sub>   | V <sub>CC</sub> Current (Active)<br>CMOS Inputs  | CE = GND, f = 5 MHz<br>Inputs = V <sub>CC</sub> or GND, I/O = 0 mA                         |                       | 3    | 10                 | mA    |

| I <sub>CCSB1</sub> | V <sub>CC</sub> Current (Standby)<br>TTL Inputs  | CE = V <sub>IH</sub>                                                                       |                       | 0.1  | 1                  | mA    |

| I <sub>CCSB2</sub> | V <sub>CC</sub> Current (Standby)<br>CMOS Inputs | CE = V <sub>CC</sub>                                                                       |                       | 0.5  | 100                | μА    |

| V <sub>IL</sub>    | Input Low Voltage                                |                                                                                            | -0.2                  |      | 8.0                | V     |

| V <sub>IH</sub>    | Input High Voltage                               |                                                                                            | 2.0                   |      | V <sub>CC</sub> +1 | V     |

| V <sub>OL1</sub>   | Output Low Voltage                               | I <sub>OL</sub> = 2.1 mA                                                                   |                       |      | 0.45               | V     |

| V <sub>OH1</sub>   | Output High Voltage                              | I <sub>OH</sub> = -400 μA                                                                  | 2.4                   |      |                    | V     |

| V <sub>OL2</sub>   | Output Low Voltage                               | I <sub>OL</sub> = 10 μA                                                                    |                       |      | 0.1                | V     |

| V <sub>OH2</sub>   | Output High Voltage                              | I <sub>OH</sub> = -10 μA                                                                   | V <sub>CC</sub> - 0.1 |      |                    | V     |

# **AC Electrical Characteristics**

| Symbol           |                                                                       |                                     |     | NMC27C32B |             |     |       |  |

|------------------|-----------------------------------------------------------------------|-------------------------------------|-----|-----------|-------------|-----|-------|--|

|                  | Parameter                                                             | Conditions                          | Q1  | 150       | Q200, QE200 |     | Units |  |

|                  |                                                                       |                                     | Min | Max       | Min         | Max |       |  |

| t <sub>ACC</sub> | Address to Output Delay                                               | CE = OE = V <sub>IL</sub>           |     | 150       |             | 200 | ns    |  |

| t <sub>CE</sub>  | CE to Output Delay                                                    | OE = V <sub>IL</sub>                |     | 150       |             | 200 | ns    |  |

| t <sub>OE</sub>  | OE to Output Delay                                                    | CE = V <sub>IL</sub>                |     | 60        |             | 60  | ns    |  |

| t <sub>DF</sub>  | OE High to Output Float                                               | CE = V <sub>IL</sub>                | 0   | 50        | 0           | 60  | ns    |  |

| t <sub>CF</sub>  | CE High to Output Float                                               | OE = V <sub>IL</sub>                | 0   | 50        | 0           | 60  | ns    |  |

| t <sub>OH</sub>  | Output Hold from Addresses,<br>CE or OE , Whichever<br>Occurred First | $\overline{CE} = \overline{OE} = V$ | 0   |           | 0           |     | ns    |  |

3

www.fairchildsemi.com

# Capacitance (Note 2) T<sub>A</sub> = +25°C, f = 1 MHz

| Symbol           | Parameter                                   | Conditions            | Тур | Max | Units |

|------------------|---------------------------------------------|-----------------------|-----|-----|-------|

| C <sub>IN1</sub> | Input Capacitance except OE/V <sub>PP</sub> | V <sub>IN</sub> = 0V  | 6   | 12  | pF    |

| C <sub>IN2</sub> | OE/V <sub>PP</sub> Input Capacitance        | V <sub>IN</sub> = 0V  | 16  | 20  | pF    |

| C <sub>OUT</sub> | Output Capacitance                          | V <sub>OUT</sub> = 0V | 9   | 12  | pF    |

# **AC Test Conditions**

1 TTL Gate and C<sub>L</sub> = 100 pF (Note 8) Output Load Input Rise and Fall Times ≤5 ns Input Pulse Levels 0.45V to 2.4V

Timing Measurement Reference Level

0.8V and 2V Outputs 0.8V and 2V

# AC Waveforms (Note 7)

Note 1: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: This parameter is only sampled and is not 100% tested.

$\textbf{Note 3:} \ \ \overline{\textbf{OE}} \ \, \text{may be delayed up to } t_{ACC} \text{--} t_{OE} \text{ after the falling edge of } \overline{\textbf{CE}} \text{ without impacting } t_{ACC}.$

Note 4: The  $t_{DF}$  and  $t_{CF}$  compare level is determined as follows: High to TRI-STATE, the measured  $V_{OH1}$  (DC) - 0.10V; Low to TRI-STATE, the measured  $V_{OL1}$  (DC) + 0.10V.

Note 5: TRI-STATE may be attained using  $\overline{\text{OE}}$  or  $\overline{\text{CE}}$

Note 6: The power switching characteristics of EPROMs require careful device decoupling. It is recommended that at least a 0.1  $\mu$ F ceramic capacitor be used on every device between  $V_{CC}$  and GND.

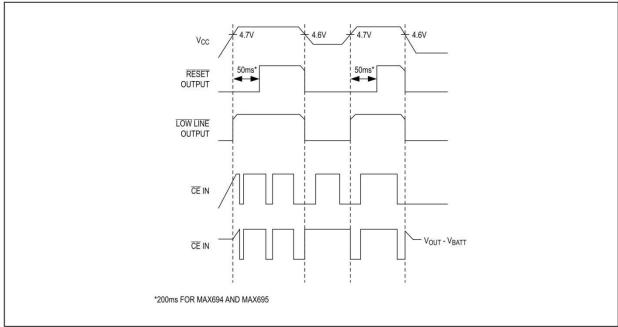

Note 7: The outputs must be restricted to  $V_{CC}$  + 1.0V to avoid latch-up and device damage.