# Alfair 88-MDS Minidisk Documentation Preliminary

#### Change Sheet 8800 Minidisk Documentation Preliminary

The following changes should be made in this document:

| Page                                              | Change                                                                                                            | Date    |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------|

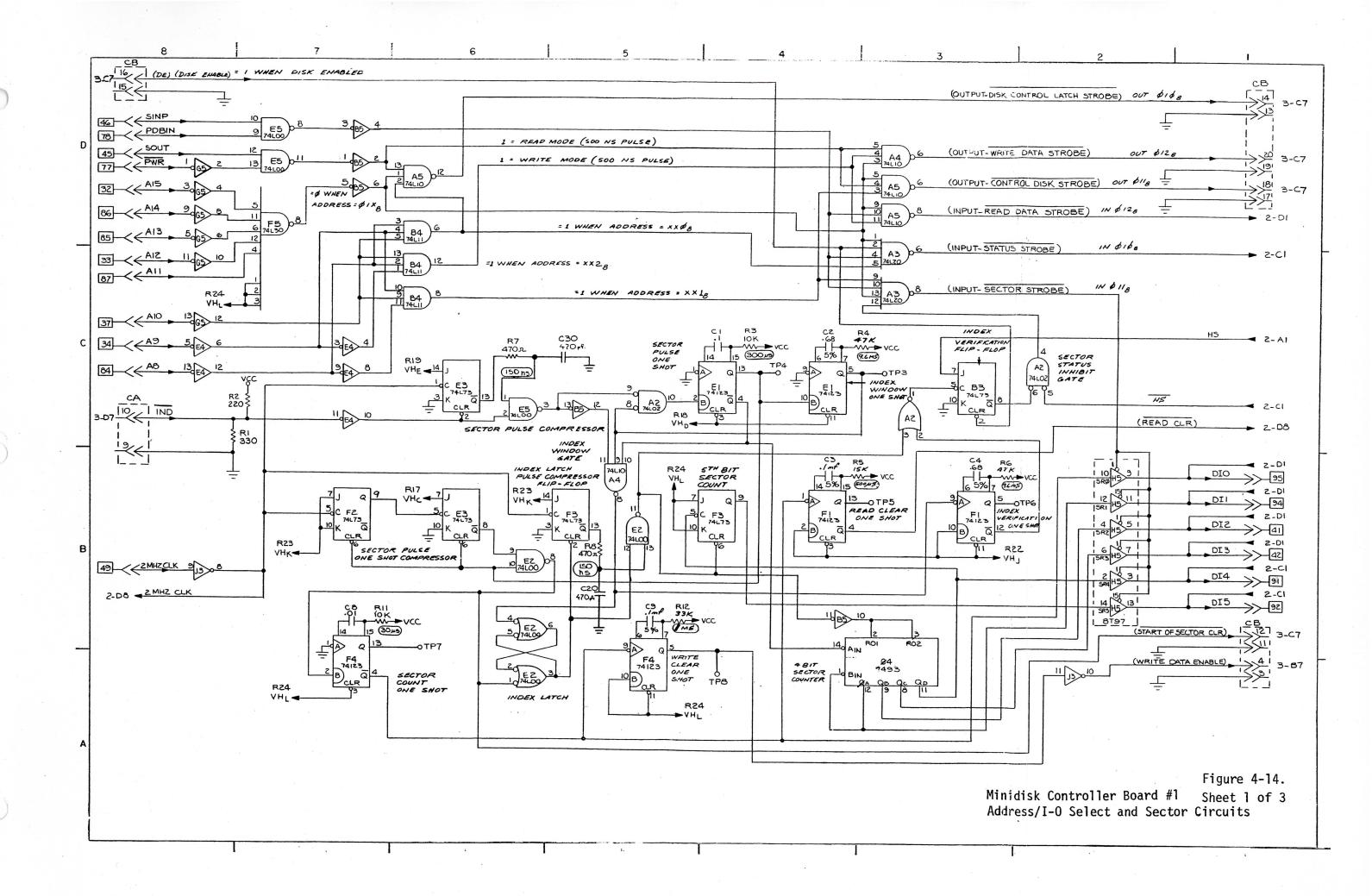

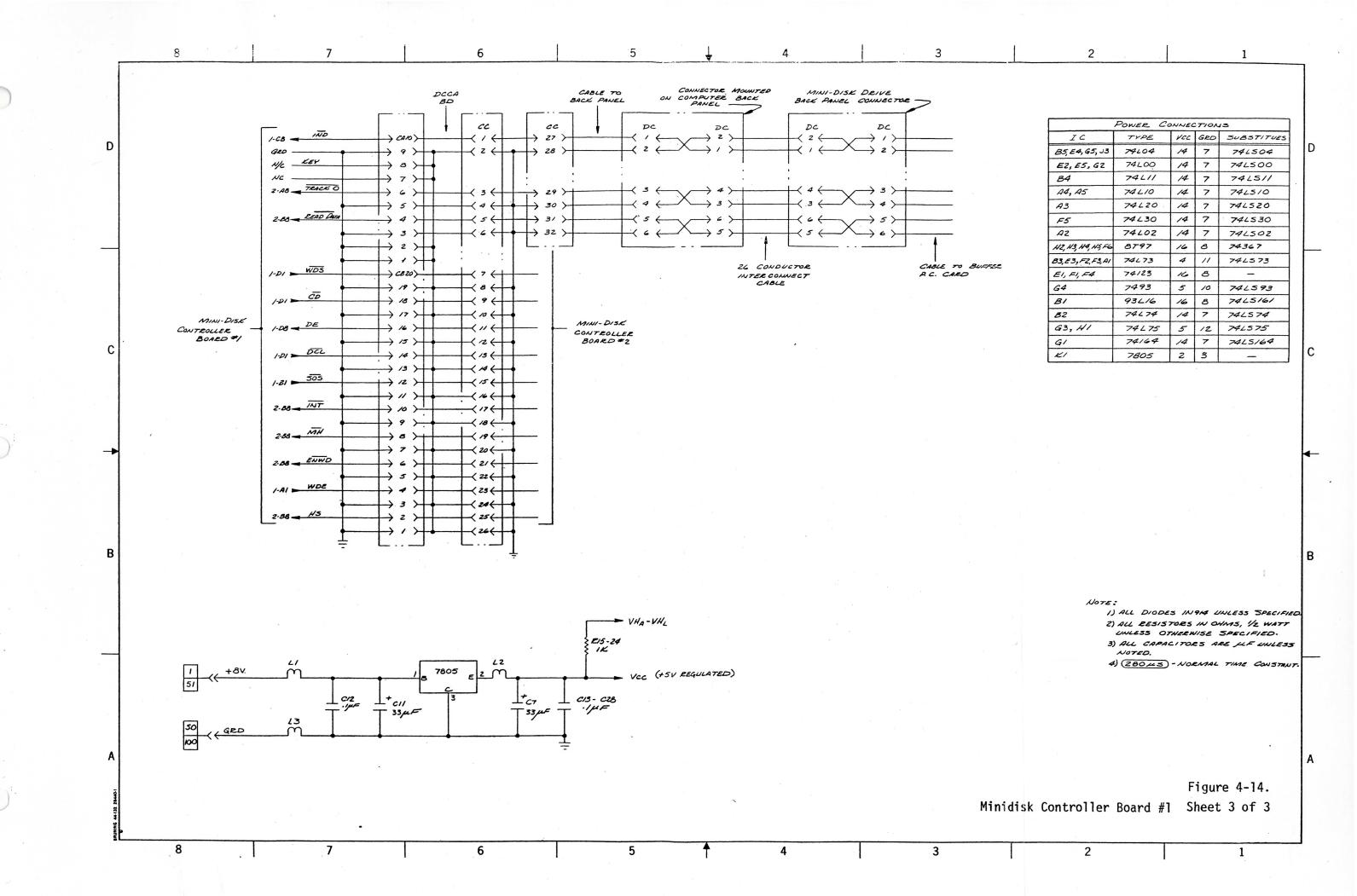

| Controller Board<br>#1 Schematic,<br>Sheet 1 of 3 | ICA2 (zone C2) from 74L02 to 74LS02<br>R5 (zone B3) from 15K to 7.32K, 1%<br>R12 (zone A5) from 33K to 14.7K, 1%  | 4/20/78 |

| Controller Board<br>#1 Schematic,<br>Sheet 2 of 3 | ICA2 (zone D5) from 74L02 to 74LS02<br>ICA4 (zone B4) from 74L10 to 74LS10<br>ICG2 (zone D4) from 74L00 to 74LS00 | 4/20/78 |

#### 88-DCDD Documentation

#### Erratum, December, 1977

#### Page 229:

#### CHANGE TO:

#### TABLE OF CONTENTS

| List of Tables                                                |

|---------------------------------------------------------------|

| List of Programs                                              |

| I. INTRODUCTION  1-1. MITS Altair Minidisk System Description |

| 1-1. MITS Altair Minidisk System Description                  |

| 1-2. Specifications                                           |

| A. 88-MDS Altair Minidisk System                              |

| B. 88-MDS Controller Specifications                           |

| C. 88-MDDR Drive Specifications                               |

| 1-3. Options/Accessories                                      |

| 1-3. Options/Accessories                                      |

| A. Software                                                   |

| B. MDBL PROM                                                  |

|                                                               |

|                                                               |

| D. Miscellaneous 5                                            |

| II. SYSTEM INSTALLATION                                       |

| 2-1. Minidisk Drive Inspection and Drive Address              |

| Selection                                                     |

| A. Inspection 9                                               |

| B. Drive Address Selection                                    |

| 2-2. Installing the Controller                                |

| A. Part Required 10                                           |

| B. Installation of 26-pin Bulkhead Connector 10               |

| C. PC Board and Cable Installation 10                         |

| 2-3. Connecting the Minidisk Drive                            |

| III. USING THE MINIDISK SYSTEM                                |

| 3-1. General Instructions                                     |

| A. Minidisk Drive                                             |

| B. Minidiskette                                               |

| C. Controller Boards                                          |

| 3-2. Loading Minidisk BASIC                                   |

| 3-3. Problems During Loading                                  |

|                                                               |

| 3-4. MDBL PROM Listing                                        |

| 3-6. Assembly Code to Read and Write a Section                |

| Sect | tion                                                | Page |

|------|-----------------------------------------------------|------|

|      | 3-7. Machine Language Operation                     | 29   |

|      | 3-8. Using Interrupts on the Altair Minidisk System | 35   |

| IV.  | THEORY OF OPERATION                                 |      |

|      | 4-1. General                                        | 39   |

|      | 4-2. Logic Circuits                                 | 39   |

|      | 4-3. Schematic Referencing                          | 39   |

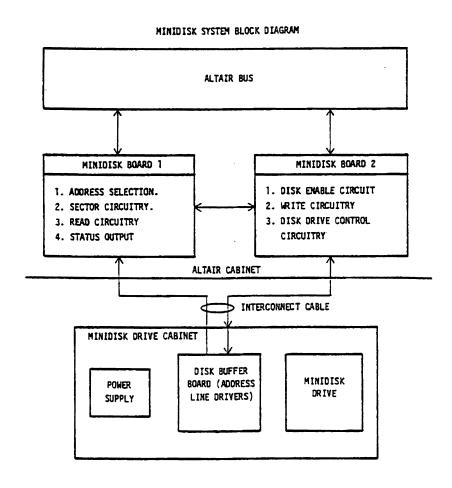

|      | 4-4. Minidisk System Block Diagram                  | 44   |

|      | 4-5. General System Operation                       | 45   |

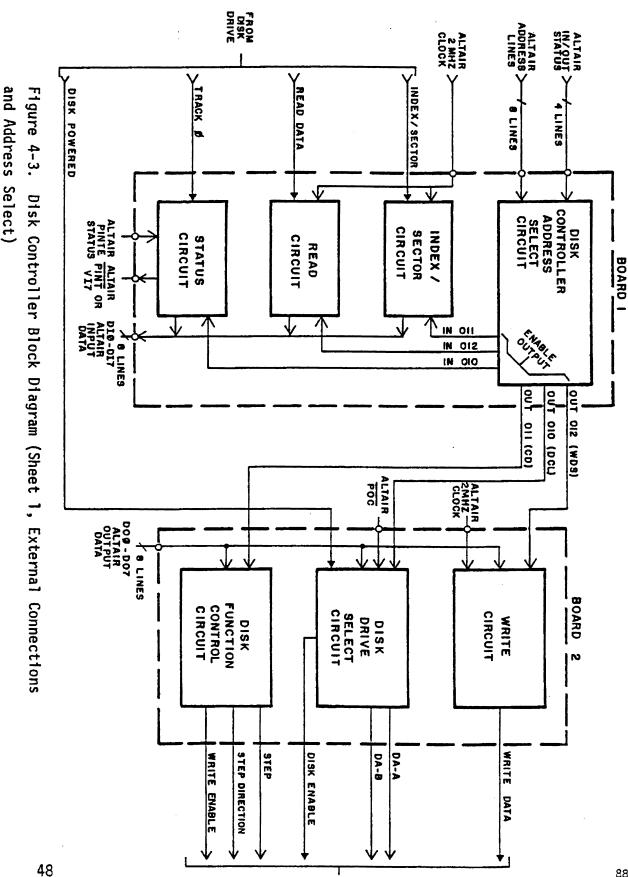

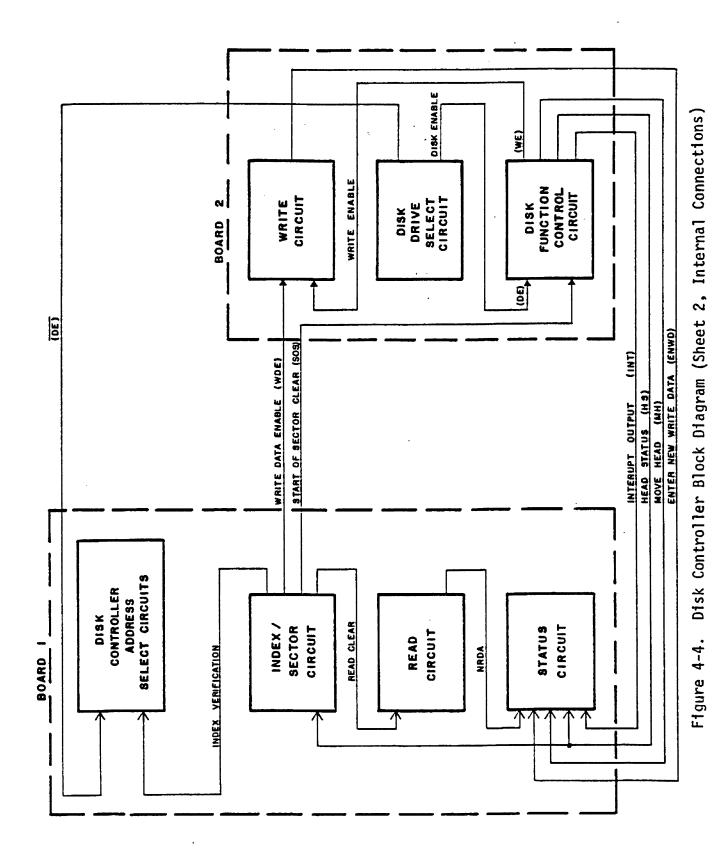

|      | 4-6. Minidisk Controller Block Diagram              | 46   |

|      | 4-7. Address Select Circuit                         | 51   |

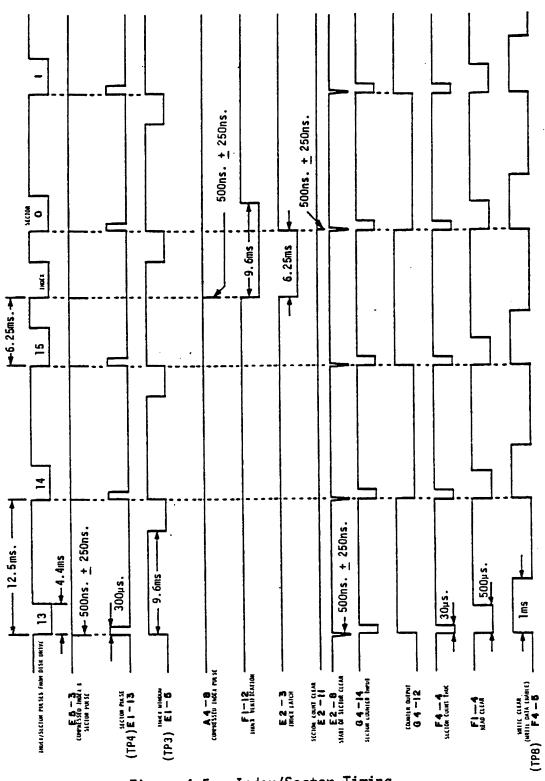

|      | 4-8. Index/Sector Circuits                          | 52   |

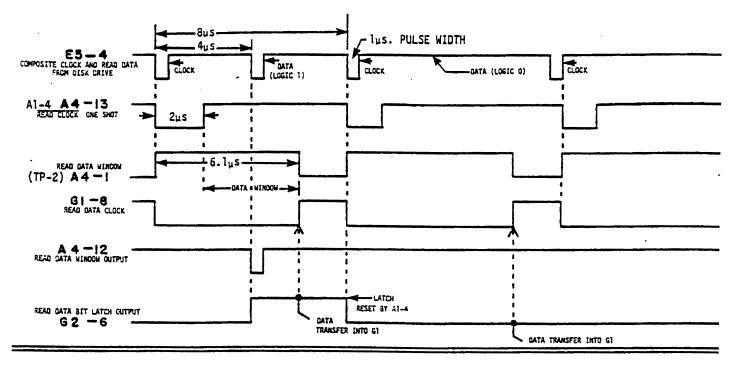

|      | 4-9. Read Circuit                                   | 55   |

|      | 4-10. Status Circuit                                | 58   |

|      | 4-11. Disk Enable Circuit                           | 58   |

|      | 4-12. Write Circuit                                 | 60   |

|      | 4-13. Disk Function Control Circuit                 | 65   |

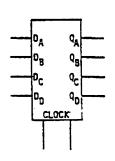

|      | 4-14. Head Stepping                                 | 67   |

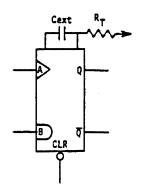

|      | 4-15. Disk Disable Timer                            | 68   |

|      | 4-16. Move Head Status                              | 68   |

|      | 4-17. Head Status                                   | 69   |

|      | 4-18. Enable Interrupts                             | 69   |

| ٧.   | MINIDISK SYSTEM PRELIMINARY CHECKOUT                | •    |

|      | 5-1. Disk Enable Test                               | 73   |

|      | 5-2. Altair Minidisk Controller Timing Test Points  | 74   |

|      | 5-3. Altair Minidisk Test Programs                  | 76   |

|      | 5-4. Disk Read/Write Test Program                   | 76   |

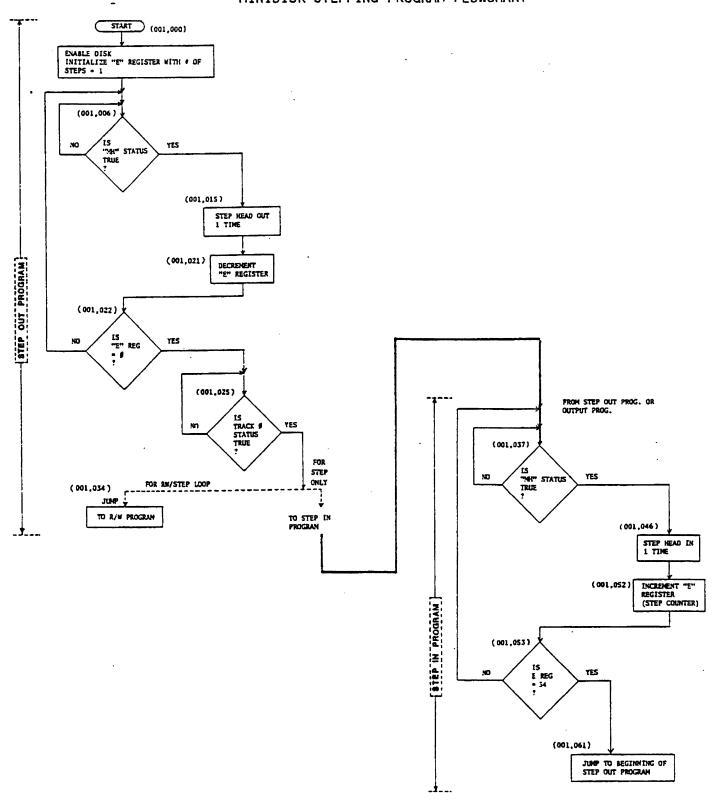

|      | 5-5. Stepping Program                               | 83   |

|      | 5-6. Looping with Stepping Program                  | 83   |

#### LIST OF TABLES

| Number        | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2-A.          | Drive Address Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 2 1           | Sonce Switch Sottings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|               | Sense Switch Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 3-B.          | Sector Position Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| A A           | Symbol Definitions 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 4-A.          | Symbol Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|               | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| Numbe         | Daniel Control of the | <u>.</u> |

| 4-1.          | Minidisk System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

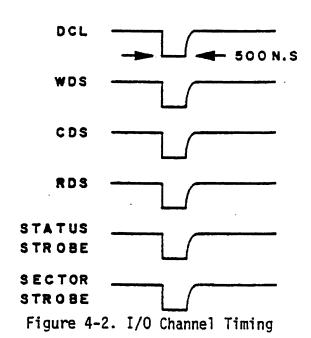

|               | 1,0 Glamer Finding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

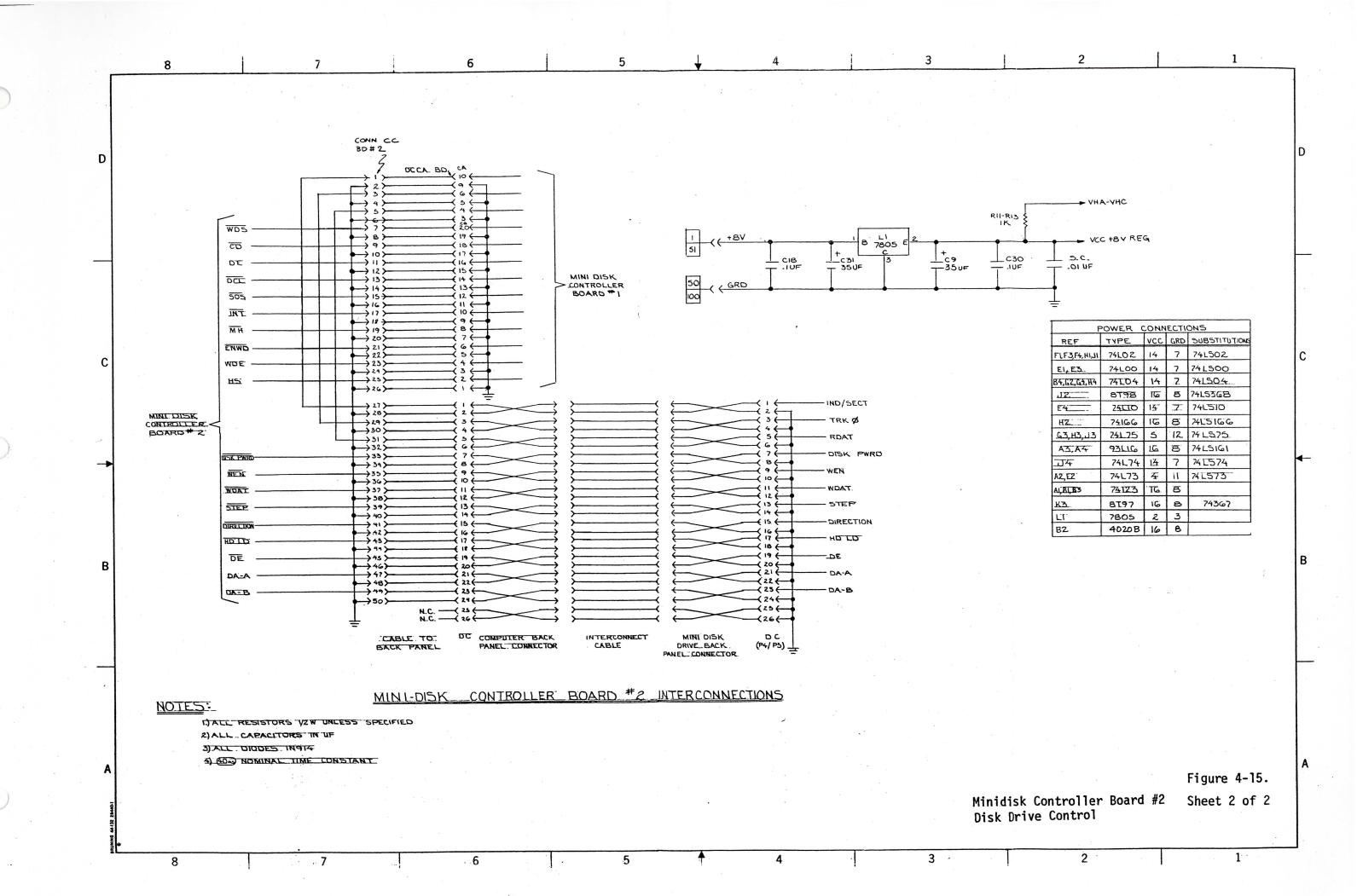

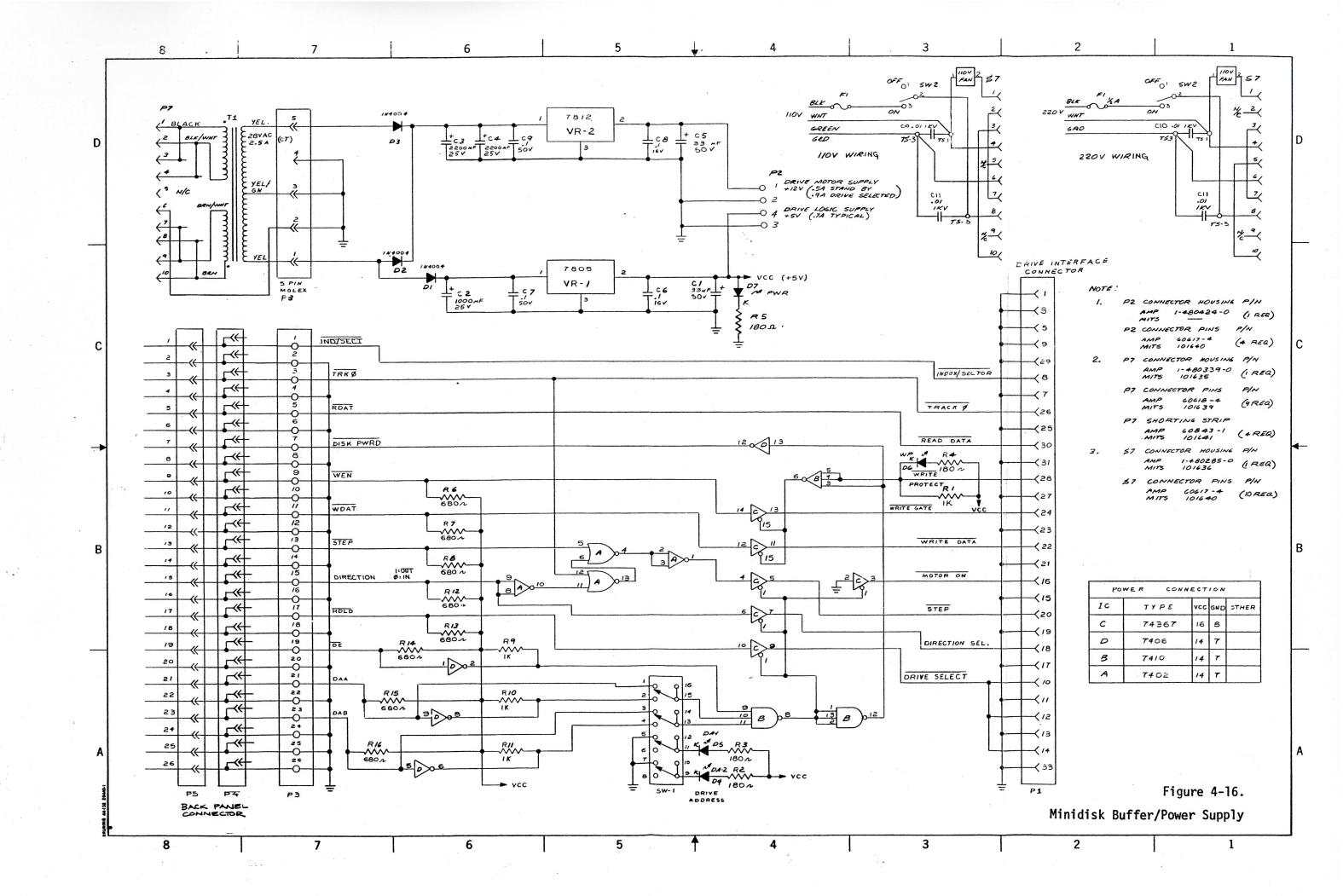

| 4-3.          | Disk Controller Block Diagram (External Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|               | and Address Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 4-4.          | Disk Controller Block Diagram (Internal Connections) 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 4-5.          | Index/Sector Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

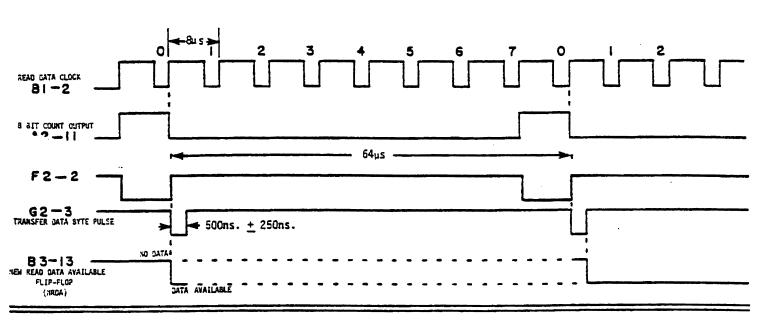

| 4-6.          | Read Circuit Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 4-7.          | Read Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

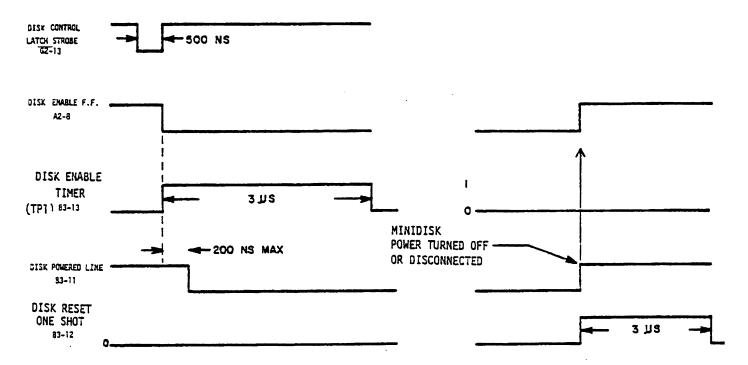

| 4-8.          | Disk Enable Timing With Valid Disk Address 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

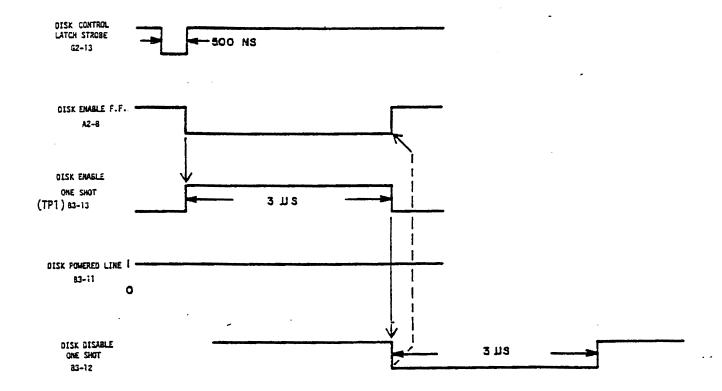

| 4-9.          | Disk Enable Timing With Invalid Disk Selection 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

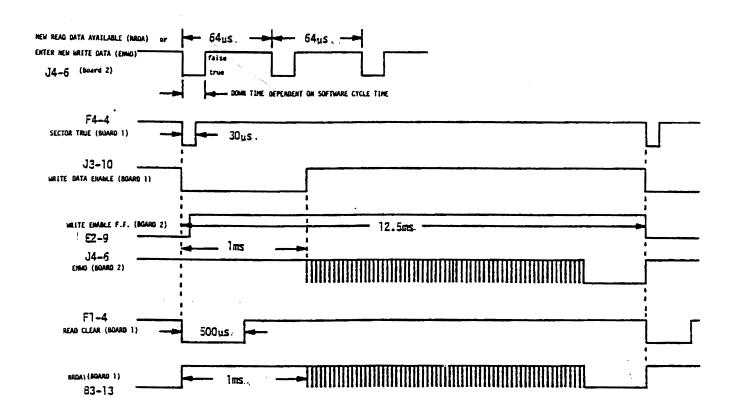

| 4-10.         | Minidisk Read/Write Timing 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

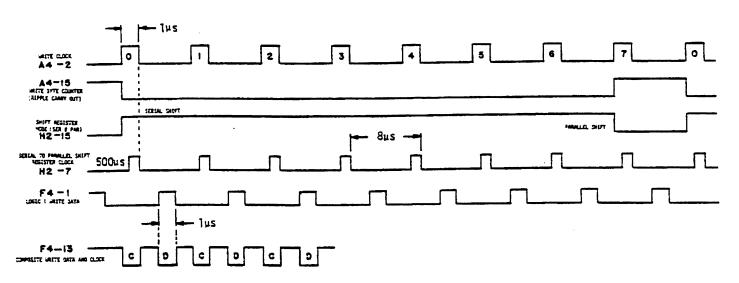

| 4-11.         | Write Circuit Timing 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

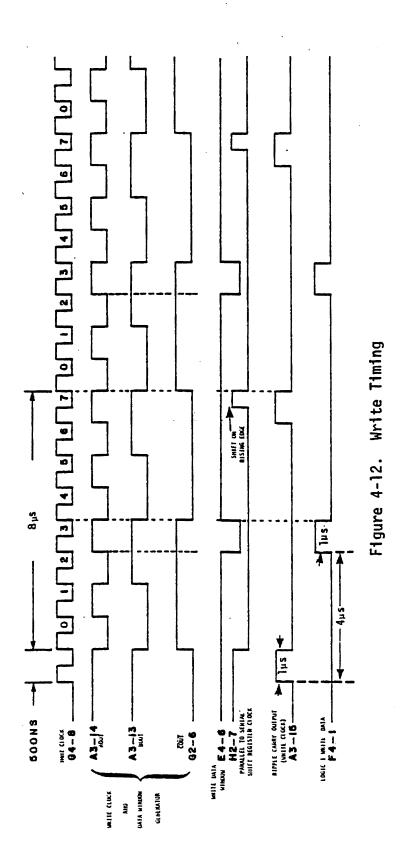

|               | Write Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

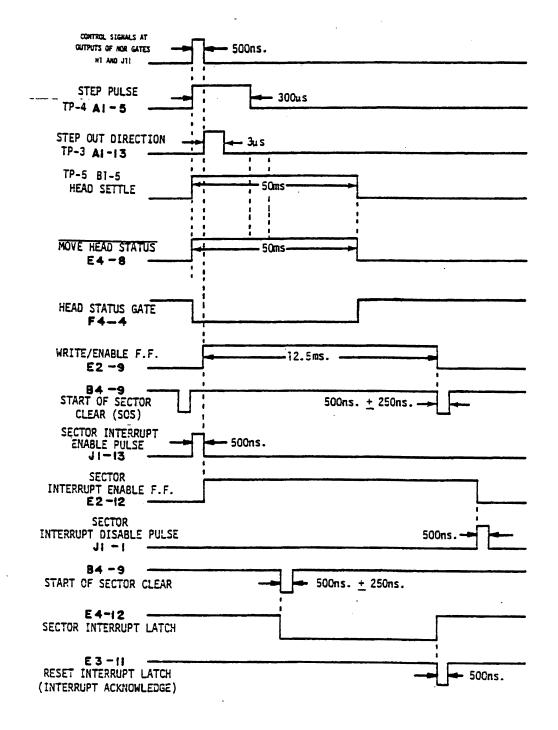

|               | Disk Function Control Timing 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|               | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|               | LIST OF PROGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| Numbe         | <u>Page</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>e</u> |

| 3 <b>-</b> I. | MDBL PROM Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 3-II.         | Assembly Code to Read and Write a Sector 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

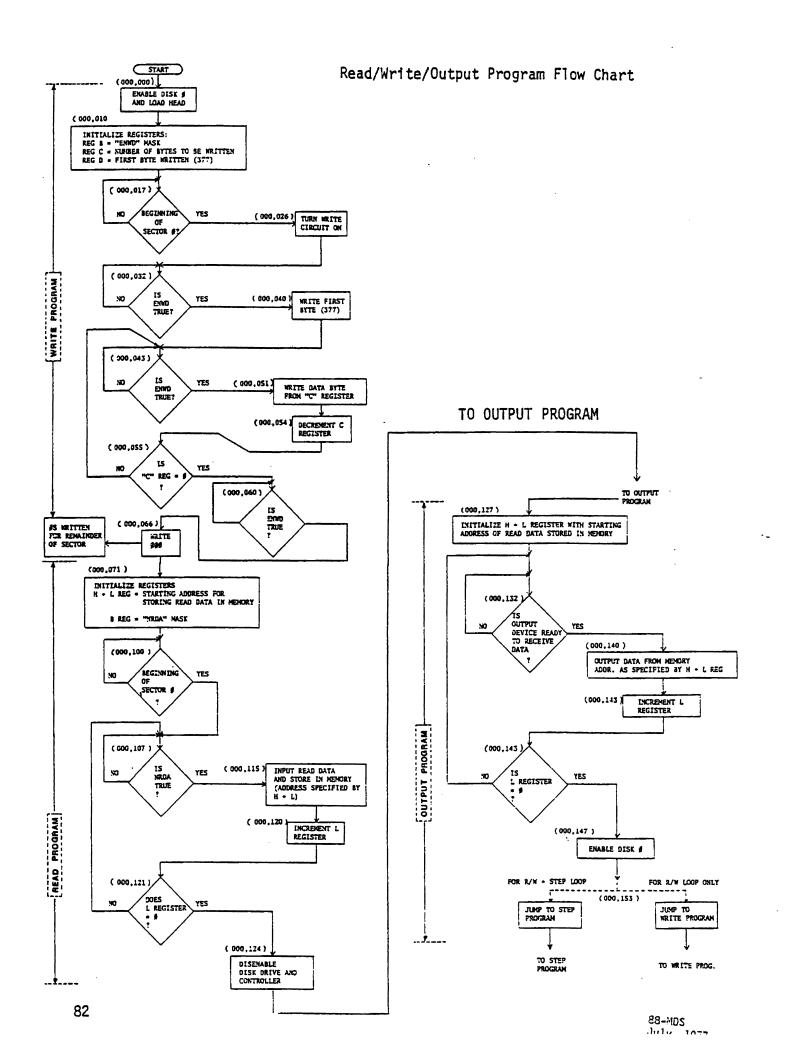

| 5-I.          | Minidisk Read/Write/Output Test Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 5-11.         | . Minidisk Stepping Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

- 3. Reliability Specifications of Minidisk Drive:

- a) Error Rates

- Soft (recoverable) errors -- 1 per 10<sup>8</sup> bits READ

- Hard (unrecoverable) errors -- 1 per 10<sup>11</sup> bits READ

- b) MTBF -- 8000 Hrs. (25% motor run time)

- c) Service Life -- 5 years

- d) Media Life -- 3.0 x 10<sup>6</sup> Passes/Track

- 4. Power Requirements:

- a) Minidisk Drive Cabinet

- Standby -- 25 watts, typical } 110V or 220V, 60HZ or 50HZ Operating -- 35 watts, typical }

- 5. Physical Specifications:

- a) Size: 5" high 11" wide 11" deep

- b) Weight: 10 lbs.

#### 1-3. OPTIONS/ACCESSORIES

#### A. Software:

Altair Minidisk Extended BASIC supplied with 88-MDS. Software on a Write Protected Minidiskette virtually identical to Altair Disk Extended BASIC in operation and features. Manual includes Bootstrap Listing and Read/Write Driver Code.

#### B. MDBL PROM:

Minidisk Bootstrap Loader on a Programmable Read Only Memory IC to be used with the 88-PMC PROM Memory Card at highest 256-byte block address.

#### C. DRWT PROM:

Floppy and Minidisk Read/Write Test PROM has the fundamental diagnostic tests for checking hardware operation. To be used with the 88-PMC at 3rd highest 256 byte block address.

#### D. Miscellaneous:

Number 102502

Minidiskette - Blank, Hard Sectored Diskette, MITS Part Number 102501 Minidisk Drive Service Manual, MITS Part Number 101597 Alignment Diskette (to be used with service manual), MITS Part

Altair Minidisk System Operators and Theory Manual, MITS Part Number 101571

5/(6 blank)

## Section 1 Introduction

#### 1-1. MITS ALTAIR MINIDISK SYSTEM DESCRIPTION

The Altair Minidisk System, used for mass storage of data for the Altair 8800 computer, has a capacity of 71,680 bytes (formatted) per Minidisk with a worst case access time of less than three seconds. A typical system using an Altair computer and Minidisk consists of an Altair 8800 Mainframe, CPU, 32K of memory, I/O Interface, a set of Minidisk Controller Cards and two Minidisk Drives.

The software most commonly used with the Altair Minidisk is Altair Minidisk BASIC, which resides in the lower 24K of memory. Altair Minidisk BASIC includes the standard features of BASIC, plus many extra functions that increase programming power significantly. The Software Driver for the Minidisk Read/Write functions is based on the Hard Sectoring technique, simplifying controller design.

The Altair computer interacts with the Minidisk Drives through two Minidisk Controller Cards that plug into the Altair bus. All Control, Status and Data I/O for the Minidisk System are handled through three I/O ports dedicated to the Minidisk Controller. To insure maximum life of the Drive Motor, a timer in the Controller turns the system off if the Minidisk is not accessed for six seconds.

Inside the Minidisk Drive cabinet is the Power Supply Drive, Line Buffers and Addressing Circuitry, allowing implementation of up to four Drives. The Drive Address is switch selectable, and the selected address is displayed on the front panel for easy identification. WRITE PROTECT is a standard feature in all Altair Minidisk Drives.

#### 1-2. SPECIFICATIONS

#### A. <u>88-MDS Altair Minidisk System</u>

The Altair Minidisk System contains a set of two Controller Boards and associated Interconnect Cables and one Minidisk Drive (88-MDDR). The Controller can control one to four Minidisk Drives. The Minidisk Drive case contains the Power Supply, Buffer and Address electronics. Included with the Minidisk Drive are interconnect cable and one blank Minidiskette.

#### B. 88-MDS Controller Specifications

- 1) Number of slots required in 8800 bus 2

- 2) Number of ICs

- TTL Logic -- 57

- CMOS -- 1

- Voltage Regulators 2

- 3) I/O Addresses (Octal) Ø1Ø, Ø11, Ø12

- Data Transfer Rate 1 byte every 64μs.

- 5) Data Format Hard Sectored (16 sectors)

- 6) Interrupt System Interrupt at beginning of Sector (Optional not used for Minidisk BASIC)

- 7) Power Requirements 1.4A @ 8V

#### C. 88-MDDR Drive Specifications

- 1. Performance Specifications:

- a) Data Capacity Hard Sectored Format

- Per Minidiskette -- 71,680 Data Bytes

- Per Track -- 2,048 Data Bytes

- Per Sector -- 128 Data Bytes

- b) Data Transfer Rate 125,000 Bits Per Second

- c) Access Time

- Disk Enable to READ or WRITE (Function of motor start-up time) -- 1 sec. (min)

- Track to Track -- 50 ms.

- Average Access Time (including motor start-up time) -- 1.85 sec.

- Worst Case Access Time -- 2.9 sec.

- Worst Case Latency -- 200 ms.

- 2. Functional Specifications:

- a) Rotational Speed -- 300 rpm (200 ms/rev.)

- b) Track Density -- 48 Tracks per inch

- c) Number of Tracks -- 35

- d) Number of Sectors -- 16

- e) Time Per Sector -- 12.5 ms.

### Section II System Installation

#### 2-1. MINIDISK DRIVE INSPECTION AND DRIVE ADDRESS SELECTION

#### A. Inspection