# DSD-440

# FLEXIBLE DISK MEMORY SYSTEM

User's Guide

Data Systems Design, Inc. • 3130 Coronado Drive • Santa Clara, CA 95051 408/249-9353 • TWX 910-338-0249 DSP SNTA

#### NOTE TO READER:

This is a preliminary copy of the DSD 440 USER'S MANUAL. Many of the illustrations are rough sketches, only intended to serve as a guide to the professional graphic artists. We would very much appreciate your comments and suggestions regarding improvements or any errors that you might find. Please feel free to write to DATA SYSTEMS, or phone us at: (408) 249-9353 EXT. 457.

THANK YOU

T. OLSEN

#### NOTICE

The information contained in this manual is subject to change without notice. Data Systems Design makes no commitment to update nor to keep current the information contained in this manual. Data Systems Design assumes no responsibility for any errors that may appear in this manual. Data Systems Design makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

BUMBS 1

4

## DSD440 USERS MANUAL

### CONTENTS

| )           | PREFACE |                                                                                                           | 보는 사용하는 사용하는 사용하는 것이 되었다. 그는 사용하는 사용하는 사용하는 것이 되는 것이다.<br>기계 보는 사용하는 사용하는 사용하는 사용하는 사용하는 사용하는 사용하는 사용하                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |         | 1<br>1-1<br>1-2<br>1-3<br>1-4<br>1-5                                                                      | GENERAL INFORMATION PRODUCT INTRODUCTION PURPOSE OF EQUIPMENT DISKETTE SYSTEM DESCRIPTION FEATURES SPECIFICATIONS                                                                                                                                                                                                                                                                                                                              |

|             |         | 2<br>2-1<br>2-2<br>2-2. 1<br>2-2. 2<br>2-2. 3<br>2-2. 4<br>2-2. 5<br>2-2. 6<br>2-2. 7<br>2-2. 8<br>2-2. 9 | OPERATING MODES AND SYSTEM CONFIGURATION OPERATIONAL MODES DSD 440 SYSTEM CONFIGURATION FLOPPY DISK DRIVES MASTER CONTROLLER PCB DC POWER SUPPLY POWER DISTRIBUTION PCB ASSEMBLY AC POWER SWITCH FAN CORCOM CONNECTOR AND FUSING INTERFACE CABLE INTERFACE MODULE                                                                                                                                                                              |

| , provident |         | 3<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12                  | SYSTEM INSTALLATION AND ACCEPTANCE ENVIRONMENTAL CONSIDERATIONS UNPACKING THE SYSTEM MOUNTING THE DSD 440 CHASSIS INSTALLING THE INTERFACE MODULE AND CABLE INPUT POWER CONSIDERATIONS CHANGING THE OPERATING MODE FINAL INSTALLATION POWERING UP INITIALIZATION RESPONSE CHECK SYSTEM BOOTSTRAP ACCEPTANCE TESTING ON PDP-11 AND LSI-11 ACCEPTANCE TESTING ON PDP-8                                                                           |

|             |         | 4<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11                          | MAINTENANCE FEATURES  OVERVIEW OF MAINTENANCE FEATURES  NORMAL VS. "HYPER-DIAGNOSTIC" MODE  INDICATOR LEDS, DRIVE LEDS, DIP-SWITCH  LED MEANINGS DURING "NORMAL" MODE  DIP-SWITCH SETTINGS DURING "NORMAL" MODE  HARDWARE SELF-TEST ROUTINES "HYPER-DIAGNOSTIC" MODE  DIP-SWITCH SETTINGS DURING "HYPER-DIAGNOSTIC" MODE  LED MEANINGS DURING "HYPER-DIAGNOSTIC" MODE  DESCRIPTION OF "HYPER-DIAGNOSTIC" TESTS  HOW TO READ THE INDICATOR LEDS |

| CHAPTER 5              | DSD 440 PROGRAMMING INFORMATION           |

|------------------------|-------------------------------------------|

| 5-1                    | DEC 11 FAMILY PROGRAMMERS' INTERFACE      |

| 5-1<br>5-1.1           | MODE 1 OPERATION                          |

|                        | PERIPHERAL DEVICE REGISTERS               |

| 5-1.1, 1. <u>1</u>     | COMMAND AND STATUS REGISTER               |

|                        | DATA REGISTER                             |

| MO2100ATEHI (5-1.1.1.3 |                                           |

| []                     | DATA BUFFER REGISTER                      |

| 5-1.1.1.4              | FLOPPY DISK TRACK ADDRESS                 |

| 5-1.1.1.5              | FLOPPY DISK SECTOR ADDRESS                |

| 5-1. 1. 1. 6           | SYSTEM ERROR AND STATUS REGISTER          |

| 5-1.1.2                | MODE 1 PROTOCOLS                          |

| 5-1. 1. 2. 1           | FILL SECTOR BUFFER                        |

| 5-1. 1. 2. 2           | EMPTY SECTOR BUFFER                       |

| 5-1, 1, 2, 3           | WRITE SECTOR                              |

|                        |                                           |

| J-1. 1. 2. 4           | READ SECTOR                               |

| 5-1. 1. 2. 5           | READ STATUS                               |

| 5-1. 1. 2. 6           | WRITE DELETED DATA SECTOR                 |

| 5-1. 1. 2. 7           | READ ERROR REGISTER                       |

| 5-1. 1. 2. 8           | POWER FAIL OR INIT COMMAND                |

| 5-1, 1, 2, 9           | DISKETTE FORMATTING                       |

| 5-1. 1. 3              | TYPICAL SEQUENCES OF OPERATIONS           |

| 5-1, 1, 3, 1           | READ/WRITE BUFFER                         |

| 5-1. 1. 3. 2           | READ/WRITE/WRITE D. D.                    |

|                        |                                           |

| 5-1. 1. 3. 3           | STATUS READ                               |

| 5-1. 1. 3. 4           | COMMON PROGRAMMING PITFALLS               |

| J-1. 1. 4              | INTERRUPTS                                |

| 5-1.2                  | MODE 2 OPERATION                          |

| 5-1. 2. 1              | PERIPHERAL DEVICE REGISTERS               |

| 5-1, 2, 1, 1           | COMMAND AND STATUS REGISTER               |

| 5-1. 2. 1. 2           | DATA REGISTER                             |

| 5-1. 2. 1. 3           | FLOPPY DISK TRACK ADDRESS                 |

| 5-1. 2. 1. 4           | FLOPPY DISK SECTOR ADDRESS                |

|                        |                                           |

| 5-1. 2. 1. 5           | WORD COUNT REGISTER                       |

| 5-1, 2, 1, 6           | BUS ADDRESS REGISTER                      |

| 5-1. 2. 1. 7           | SYSTEM ERROR AND STATUS REGISTER          |

| 5-1. 2. 2              | MODE 2 PROTOCOLS                          |

| 5-1. 2. 2. 1           | FILL SECTOR BUFFER                        |

| 5-1. 2. 2. 2           | EMPTY SECTOR BUFFER                       |

| 5-1. 2. 2. 3           | WRITE SECTOR                              |

| 5-1. 2. 2. 4           | READ SECTOR                               |

| 5-1. 2. 2. 5           | SET MEDIA DENSITY                         |

| 5-1. 2. 2. 6           | READ STATUS                               |

|                        |                                           |

| 5-1. 2. 2. 7           | WRITE DELETED DATA SECTOR                 |

| 5-1. 2. 2. 8           | READ EXTENDED STATUS                      |

| 5-1. 2. 2. 9           | POWER FAIL                                |

| 5-1. 2. 2. 10          | DISKETTE FORMATTING IN MULTIPLE DENSITIES |

| 5-1. 2. 3              | TYPICAL SEQUENCES OF OPERATIONS           |

| 5-1. 2. 3. 1           | READ/WRITE BUFFER                         |

| 5-1. 2. 3. 2           | READ/WRITE/WRITE D. D.                    |

| 5-1. 2. 3. 3           | STATUS READ                               |

| 5-1. 2. 3. 4           | COMMON PROGRAMMING PITFALLS               |

|                        |                                           |

| 5-1. 2. 4              | INTERRUPTS                                |

| 5-2.1.2 INSTRUCTION SET 5-2.1.2 THE TRANSFER DATA REGISTER (XDR) INSTRUCTI 5-2.1.3 THE SKIP ON TRANSFER REQUEST (STR) INSTRUC 5-2.1.4 THE SKIP ON ERROR (SER) INSTRUCTION 5-2.1.5 THE SKIP ON DONE (SDN) INSTRUCTION 5-2.1.6 THE INTERRUPT ENABLE/DISABLE (INTR) INSTRU 5-2.1.7 THE INITIALIZE (INIT) INSTRUCTION 5-2.2 REGISTER DESCRIPTIONS 5-2.2.1 COMMAND REGISTER 5-2.2.2 TRACK ADDRESS REGISTER 5-2.2.3 SECTOR ADDRESS REGISTER 5-2.2.4 DATA BUFFER REGISTER (MODE 1 OPERATIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-2        | DEC PDP-8 FAMILY PROGRAMMERS' INTERFACE AND AND AND ADDRESS OF THE PROGRAMMERS. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------|

| THE SKIP ON TRANSFER REQUEST (STR) INSTRUCT 5-2.1.4 THE SKIP ON ERROR (SER) INSTRUCTION 5-2.1.5 THE SKIP ON DONE (SDN) INSTRUCTION THE SKIP ON DONE (SDN) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCT 10 THE INITIALIZE (INIT) INSTRUCT 10 THE SECTOR ADDRESS REGISTER SECTOR ADDRESS REGISTER (MODE 1 OPERATIO 5-2.2.4 DATA BUFFER REGISTER (MODE 1 OPERATIO 5-2.3.1 FILL BUFFER (MODE 2 OPERATIO 5-2.3.1 FILL BUFFER EMPTY BUFFER SECTOR SET MEDIA DENSITY BUFFER SECTOR SET MEDIA DENSITY SECTOR SET MEDIA DENSITY READ SECTOR SET MEDIA DENSITY READ STATUS SECTOR READ SECTOR SECT | 5-2. 1     | INSTRUCTION SET                                                                 |

| 5-2. 1. 4 THE SKIP ON ERROR (SER) INSTRUCTION 5-2. 1. 5 THE SKIP ON DONE (SDN) INSTRUCTION 5-2. 1. 6 THE INTERRUPT ENABLE/DISABLE (INTR) INSTRU 5-2. 1. 7 THE INITIALIZE (INIT) INSTRUCTION 5-2. 2. 1 COMMAND REGISTER 5-2. 2. 2 TRACK ADDRESS REGISTER 5-2. 2. 3 SECTOR ADDRESS REGISTER 5-2. 2. 4 DATA BUFFER REGISTER 6-2. 2. 5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO 5-2. 3. 1 FUNCTION CODE DESCRIPTIONS 5-2. 3. 1 FILL BUFFER 5-2. 3. 2 EMPTY BUFFER 5-2. 3. 3 WRITE SECTOR 5-2. 3. 4 READ SECTOR 5-2. 3. 5 READ STATUS 6-2. 3. 7 WRITE DELETED DATA SECTOR 7-2. 3. 8 READ ERROR REGISTER 90WER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-2. 1. 2  | THE TRANSFER DATA REGISTER (XDR) INSTRUCTION                                    |

| THE SKIP ON DONE (SDN) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INITIALIZE (INIT) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INIT) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INIT) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INIT) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION THE INTERRUPT ENABLE/DISABLE (INIT) INSTRUCTION THE INTERPUPT ENABLE/DISABLE (INIT) INSTRUCTION THE INTERPUPT ENABLE/DISABLE (INIT) INSTRUCTOON THE INTERPUPT ENABLE/DISABLE (INIT) INSTRUCTION THE INTERPUPT ENABLE (INIT) INSTRUCTION THE INTERPUPT ENABLE (INIT) INSTRUCTOON THE INTERPUPT ENABLE (INIT) INSTRUCTION THE INTERPUPT ENABLE (INIT) INSTRUCTON THE INTERPU | 5-2. 1. 3  | THE SKIP ON TRANSFER REQUEST (STR) INSTRUCTION                                  |

| 5-2. 1. 6 THE INTERRUPT ENABLE/DISABLE (INTR) INSTRU 5-2. 1. 7 THE INITIALIZE (INIT) INSTRUCTION 5-2. 2 REGISTER DESCRIPTIONS 5-2. 2. 1 COMMAND REGISTER 5-2. 2. 2 TRACK ADDRESS REGISTER 5-2. 2. 3 SECTOR ADDRESS REGISTER 5-2. 2. 4 DATA BUFFER REGISTER 6-2. 2. 5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO ERROR AND STATUS REGISTER (MODE 2 OPERATIO 5-2. 3. 1 FUNCTION CODE DESCRIPTIONS 5-2. 3. 1 FILL BUFFER 5-2. 3. 2 EMPTY BUFFER 5-2. 3. 3 WRITE SECTOR 5-2. 3. 4 READ SECTOR 5-2. 3. 5 SET MEDIA DENSITY 5-2. 3. 6 READ STATUS 5-2. 3. 7 WRITE DELETED DATA SECTOR 5-2. 3. 9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-2. 1. 4  | THE SKIP ON ERROR (SER) INSTRUCTION                                             |

| 5-2.1.7 THE INITIALIZE (INIT) INSTRUCTION 5-2.2 REGISTER DESCRIPTIONS 5-2.2.1 COMMAND REGISTER 5-2.2.2 TRACK ADDRESS REGISTER 5-2.2.3 SECTOR ADDRESS REGISTER 5-2.2.4 DATA BUFFER REGISTER 5-2.2.5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO 5-2.2.6 ERROR AND STATUS REGISTER (MODE 2 OPERATIO 5-2.3.1 FUNCTION CODE DESCRIPTIONS 5-2.3.1 FILL BUFFER 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-2. 1. 5  | THE SKIP ON DONE (SDN) INSTRUCTION                                              |

| 5-2. 2 REGISTER DESCRIPTIONS 5-2. 2. 1 COMMAND REGISTER 5-2. 2. 2 TRACK ADDRESS REGISTER 5-2. 2. 3 SECTOR ADDRESS REGISTER 5-2. 2. 4 DATA BUFFER REGISTER 5-2. 2. 5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO 5-2. 2. 6 ERROR AND STATUS REGISTER (MODE 2 OPERATIO 5-2. 3 FUNCTION CODE DESCRIPTIONS 5-2. 3. 1 FILL BUFFER 5-2. 3. 2 EMPTY BUFFER 5-2. 3. 3 WRITE SECTOR 5-2. 3. 4 READ SECTOR 5-2. 3. 5 SET MEDIA DENSITY 5-2. 3. 6 READ STATUS 5-2. 3. 7 WRITE DELETED DATA SECTOR 5-2. 3. 8 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-2. 1. 6  | THE INTERRUPT ENABLE/DISABLE (INTR) INSTRUCTION                                 |

| 5-2.2.1 COMMAND REGISTER 5-2.2.2 TRACK ADDRESS REGISTER 5-2.2.3 SECTOR ADDRESS REGISTER 5-2.2.4 DATA BUFFER REGISTER 5-2.2.5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO) 5-2.2.6 ERROR AND STATUS REGISTER (MODE 2 OPERATIO) 5-2.3 FUNCTION CODE DESCRIPTIONS 5-2.3.1 FILL BUFFER 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-2.1.7    | THE INITIALIZE (INIT) INSTRUCTION                                               |

| TRACK ADDRESS REGISTER  5-2. 2. 3 SECTOR ADDRESS REGISTER  5-2. 2. 4 DATA BUFFER REGISTER  5-2. 2. 5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO  5-2. 2. 6 ERROR AND STATUS REGISTER (MODE 2 OPERATIO  5-2. 3 FUNCTION CODE DESCRIPTIONS  5-2. 3. 1 FILL BUFFER  5-2. 3. 2 EMPTY BUFFER  5-2. 3. 3 WRITE SECTOR  5-2. 3. 4 READ SECTOR  5-2. 3. 5 SET MEDIA DENSITY  5-2. 3. 6 READ STATUS  5-2. 3. 7 WRITE DELETED DATA SECTOR  5-2. 3. 8 READ ERROR REGISTER  5-2. 3. 9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-2. 2     | REGISTER DESCRIPTIONS                                                           |

| 5-2.2.3 SECTOR ADDRESS REGISTER 5-2.2.4 DATA BUFFER REGISTER 5-2.2.5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO 5-2.3.6 FUNCTION CODE DESCRIPTIONS 5-2.3.1 FILL BUFFER 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 WRITE DELETED DATA SECTOR 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2. 2. 1  | COMMAND REGISTER                                                                |

| 5-2. 2. 4 DATA BUFFER REGISTER 5-2. 2. 5 ERROR AND STATUS REGISTER (MODE 1 OPERATIO 5-2. 2. 6 ERROR AND STATUS REGISTER (MODE 2 OPERATIO 5-2. 3 FUNCTION CODE DESCRIPTIONS 5-2. 3. 1 FILL BUFFER 5-2. 3. 2 EMPTY BUFFER 5-2. 3. 3 WRITE SECTOR 5-2. 3. 4 READ SECTOR 5-2. 3. 5 SET MEDIA DENSITY 5-2. 3. 6 READ STATUS 5-2. 3. 7 WRITE DELETED DATA SECTOR 5-2. 3. 8 READ ERROR REGISTER 5-2. 3. 9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-2. 2. 2  | TRACK ADDRESS REGISTER                                                          |

| ERROR AND STATUS REGISTER (MODE 1 OPERATION STATUS REGISTER (MODE 2 OPERATION STATUS READ SECTION STATUS SET MEDIA DESCRIPTIONS SET MEDIA DESCRIPTION STATUS SET MEDIA DENSITY SET MEDIA DENSITY SET MEDIA DENSITY READ STATUS WRITE DELETED DATA SECTOR READ ERROR REGISTER SET SET SET MEDIA DENSITER SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-2. 2. 3  | SECTOR ADDRESS REGISTER                                                         |

| 5-2.2.6 ERROR AND STATUS REGISTER (MODE 2 OPERATIO 5-2.3 FUNCTION CODE DESCRIPTIONS 5-2.3.1 FILL BUFFER 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 75-2.3.4 READ SECTOR 75-2.3.6 READ STATUS 75-2.3.7 WRITE DELETED DATA SECTOR 75-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-2. 2. 4  | DATA BUFFER REGISTER                                                            |

| 5-2.3 FUNCTION CODE DESCRIPTIONS 5-2.3.1 FILL BUFFER 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2. 2. 5  | ERROR AND STATUS REGISTER (MODE 1 OPERATION)                                    |

| 5-2.3.1 FILL BUFFER 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-2. 2. 6  | ERROR AND STATUS REGISTER (MODE 2 OPERATION)                                    |

| 5-2.3.2 EMPTY BUFFER 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-2. 3     | FUNCTION CODE DESCRIPTIONS                                                      |

| 5-2.3.3 WRITE SECTOR 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-2. 3. 1  | FILL BUFFER                                                                     |

| 5-2.3.4 READ SECTOR 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-2. 3. 2  | EMPTY BUFFER                                                                    |

| 5-2.3.5 SET MEDIA DENSITY 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-2. 3. 3  | WRITE SECTOR                                                                    |

| 5-2.3.6 READ STATUS 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-2. 3. 4  | READ SECTOR                                                                     |

| 5-2.3.7 WRITE DELETED DATA SECTOR 5-2.3.8 READ ERROR REGISTER 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-2. 3. 5  | SET MEDIA DENSITY                                                               |

| 5-2.3.8 READ ERROR REGISTER<br>5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2. 3. 6  | READ STATUS                                                                     |

| 5-2.3.9 POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-2. 3. 7  | WRITE DELETED DATA SECTOR                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-2. 3. 8  | READ ERROR REGISTER                                                             |

| 5-2.3.10 DISKETTE FORMATTING IN MULTIPLE DENSITIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-2. 3. 9  | POWER FAIL                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-2. 3. 10 | DISKETTE FORMATTING IN MULTIPLE DENSITIES                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                                                 |

CHAPTER 6 6-1 6-2 6-3 6-3.1 6-3.2

6-3.3

HIGH LEVEL SOFTWARE AND THE DSD 440

GENERATING AN RT11 SYSTEM DISKETTE

GENERATING DOUBLE DENSITY DISKETTES

FRD440 SYSTEM DIAGNOSTIC PROGRAM

PROGRAM LOADING AND MONITOR PROTOCOL

FRD440 PROGRAM FUNCTIONAL MODES

PROGRAM STATUS AND ERROR PRINTOUTS

```

FIGURE 1-1

SYSTEM BLOCK DIAGRAM

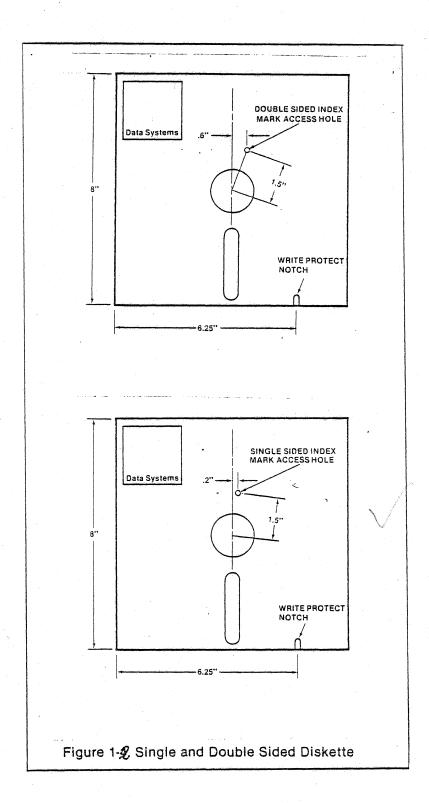

FIGURE 1-2

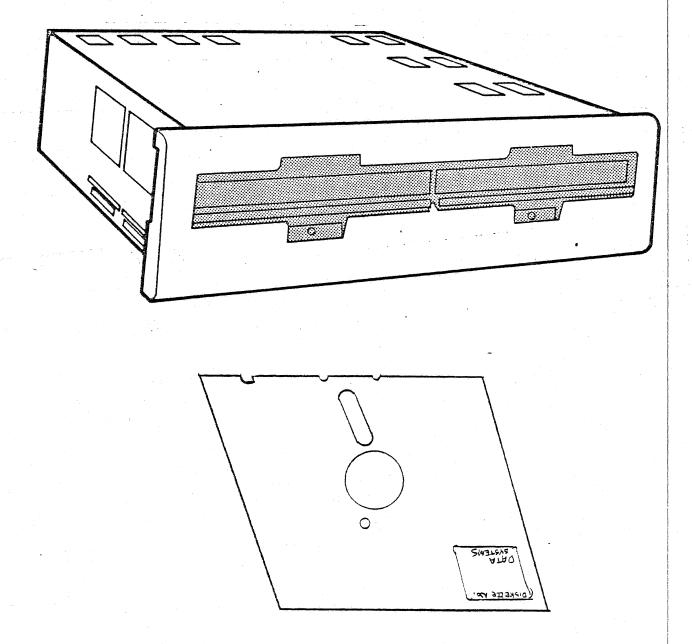

SINGLE AND DOUBLE SIDED DISKETTE

FIGURE 1-3

SINGLE DENSITY TRACK FORMAT

FIGURE 1-4

DEC DOUBLE DENSITY TRACK FORMAT

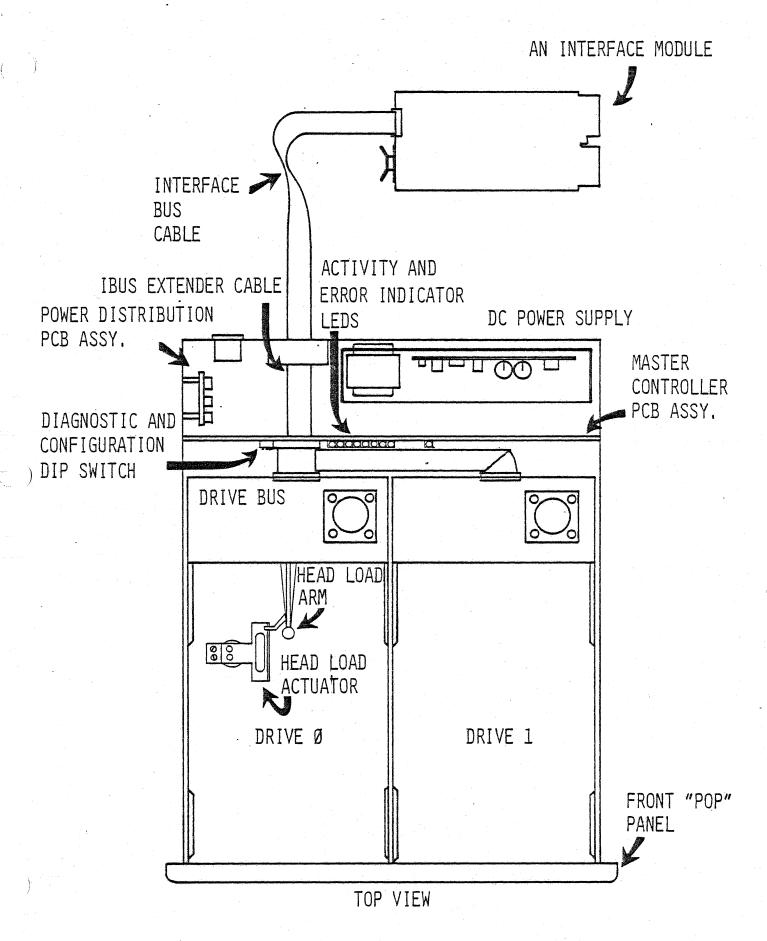

FIGURE 2-1

DSD 440 SYSTEM

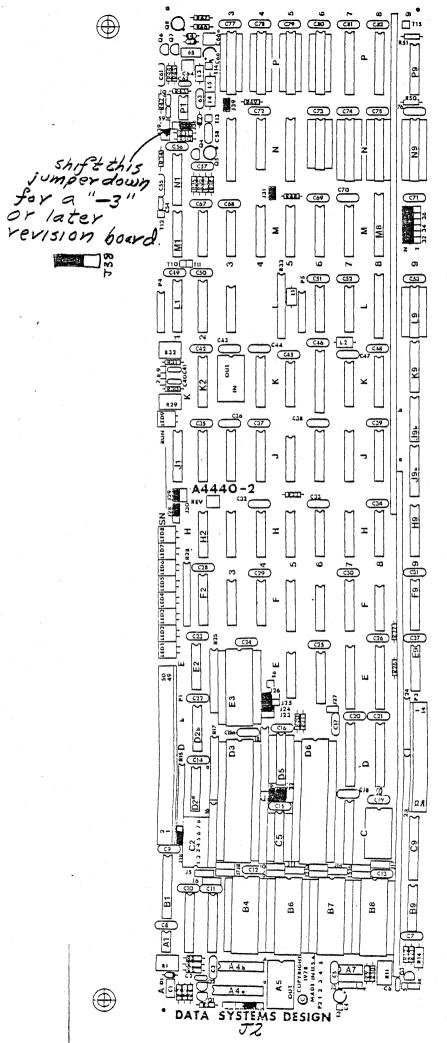

FIGURE 2-2

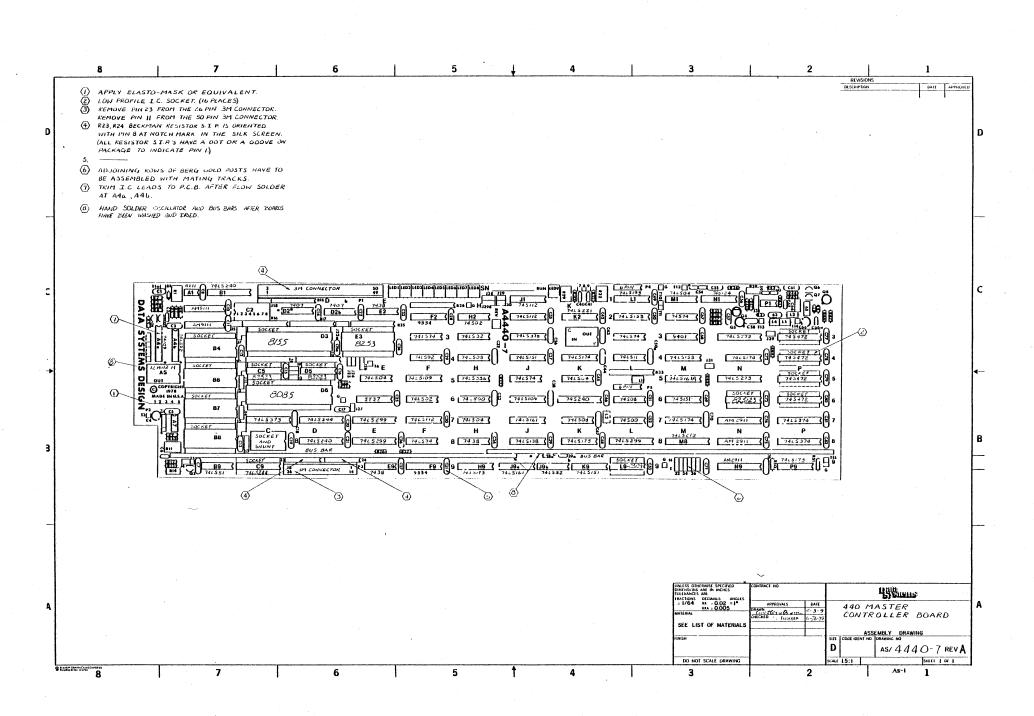

MASTER CONTROLLER PCB

FIGURE 2-3

DC POWER SUPPLY

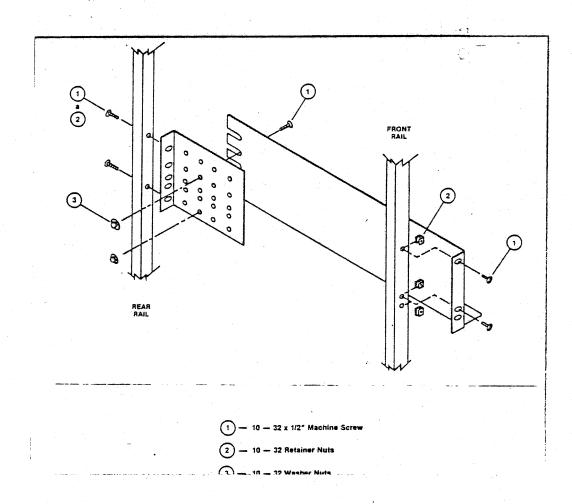

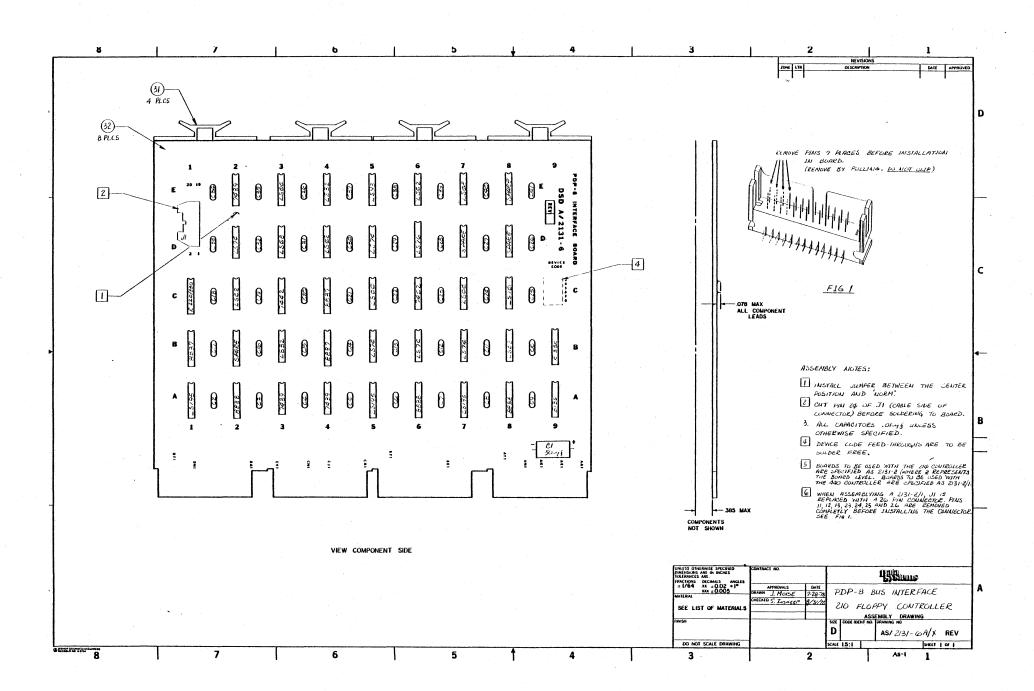

FIGURE 3-1

CHASSIS SLIDES MOUNTING

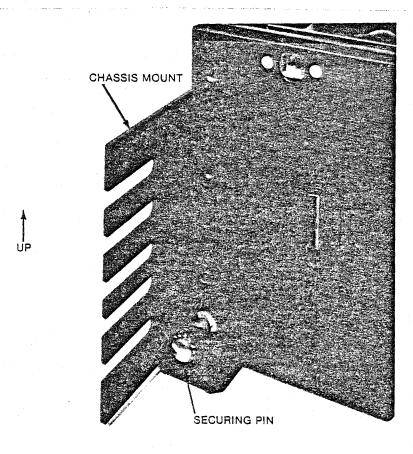

FIGURE 3-2

BULLET ENTERING HOLE IN REAR OF UNIT

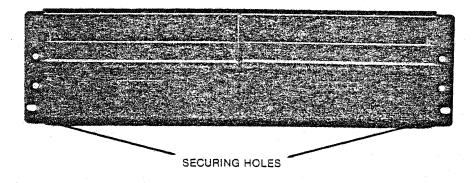

FIGURE 3-3

FRONT VIEW OF CHASSIS WITH FRONT PANEL REMOVED

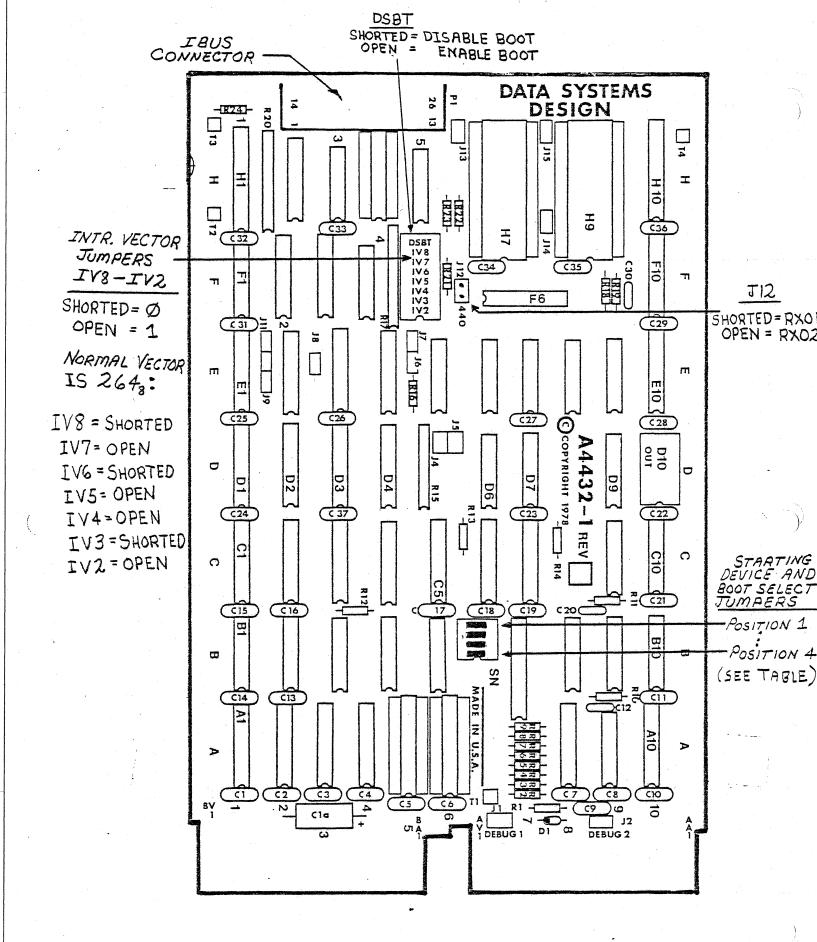

FIGURE 3-4

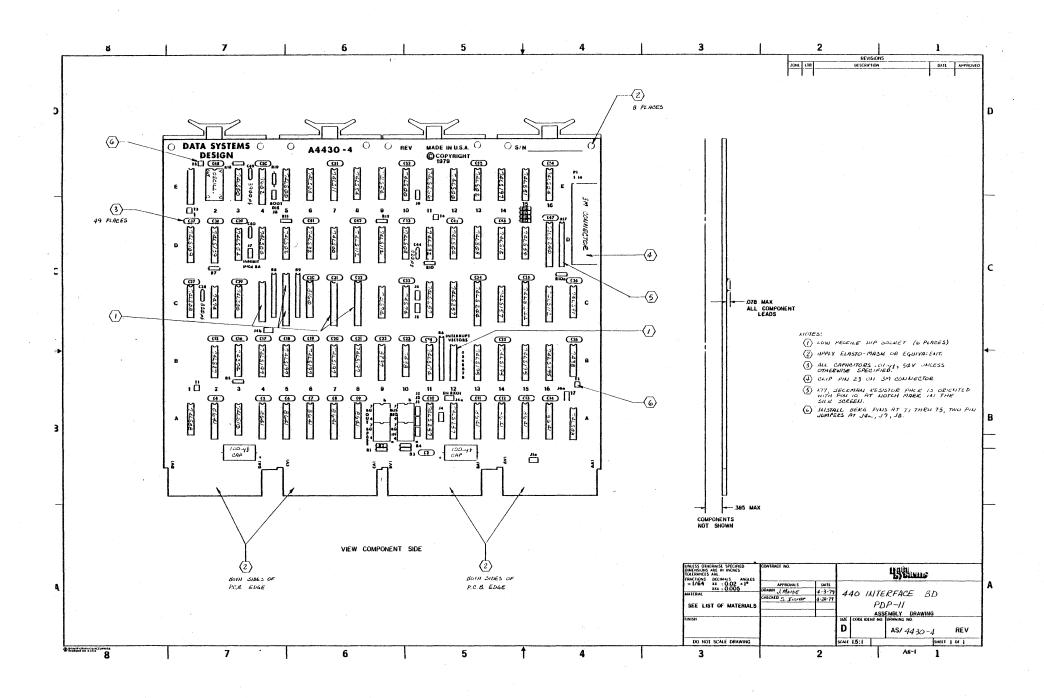

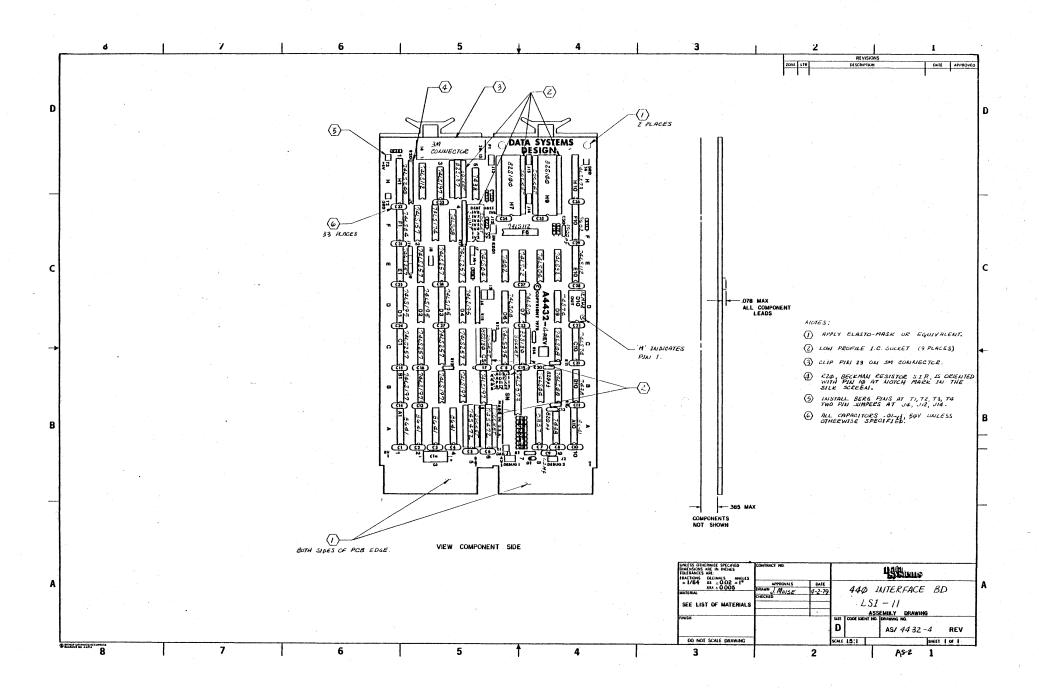

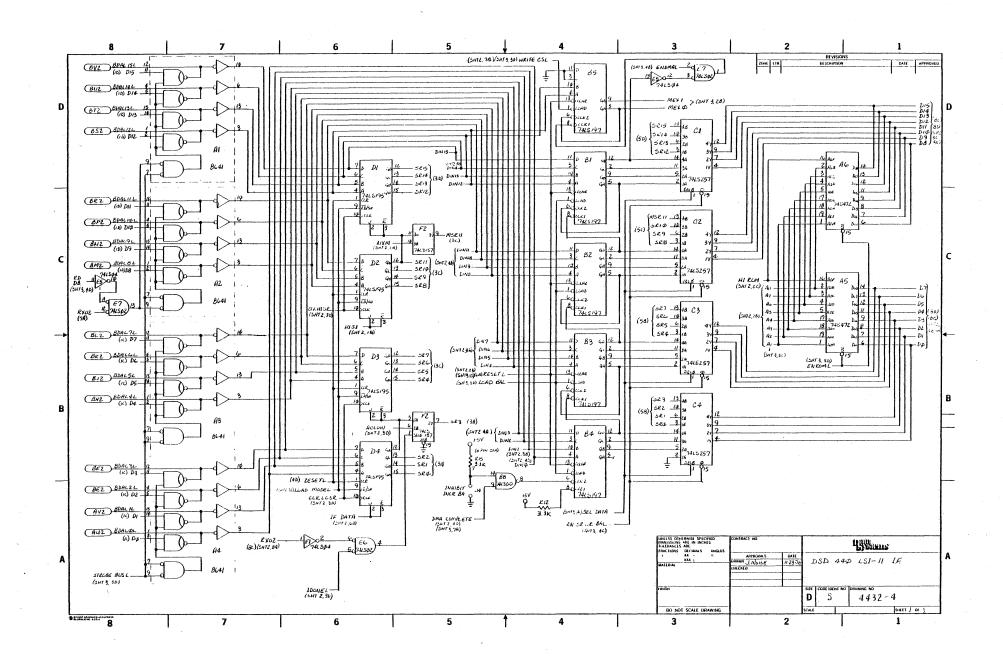

LSI-11 INTERFACE MODULE

FIGURE 3-5

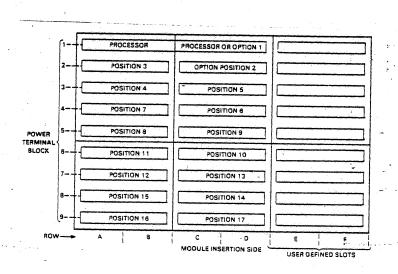

OPTION PRIORITY IN DEC BACKPLANES FOR LSI-11

FIGURE 3-6

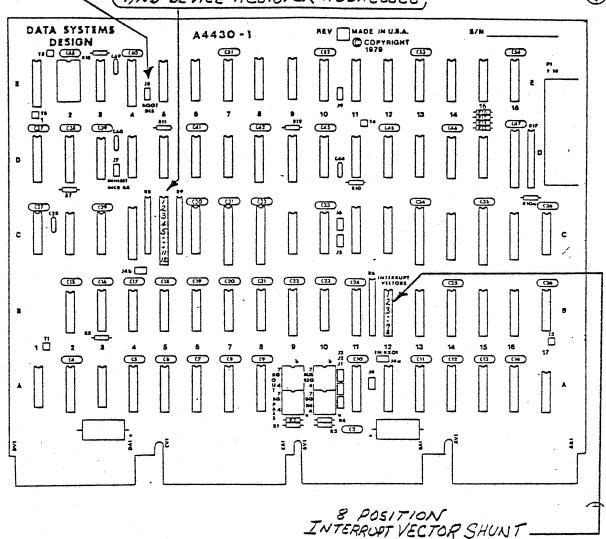

PDP-11 INTERFACE MODULE

FIGURE 3-7

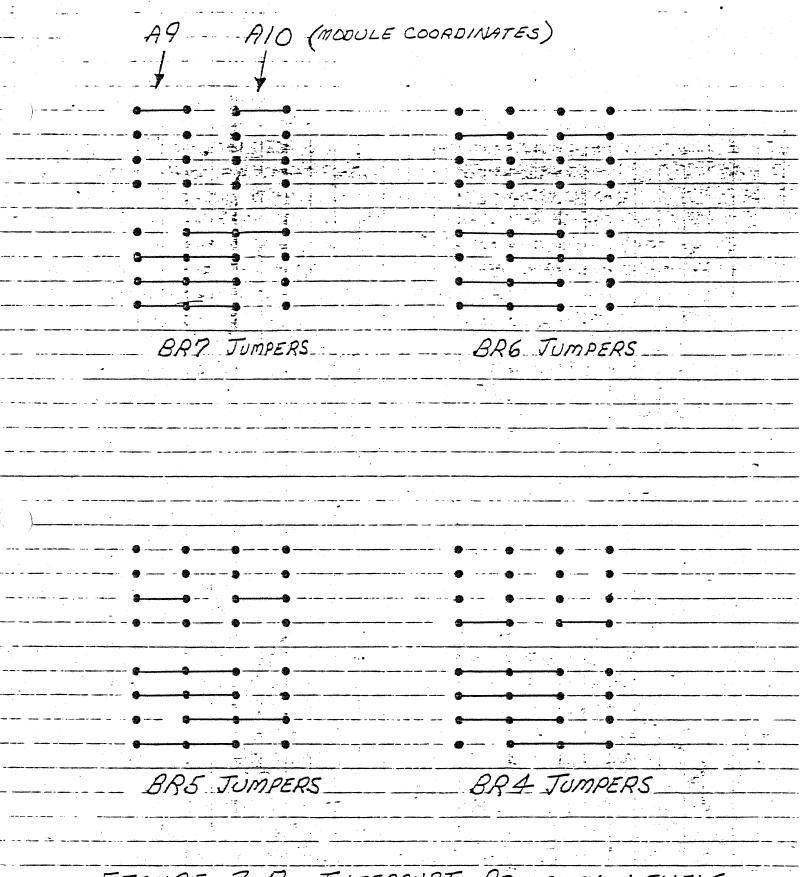

INTERRUPT PRIORITY LEVELS

FIGURE 3-8

PDP-8 INTERFACE MODULE

FIGURE 3-9

FIGURE 3-10

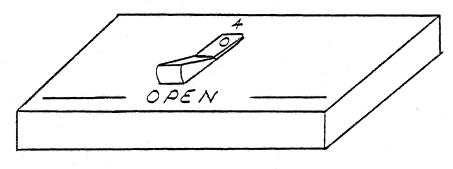

MASTER CONTROLLER BOARD DIP-SWITCH

INSERTING A DISKETTE INTO A DRIVE

FIGURE 4-1

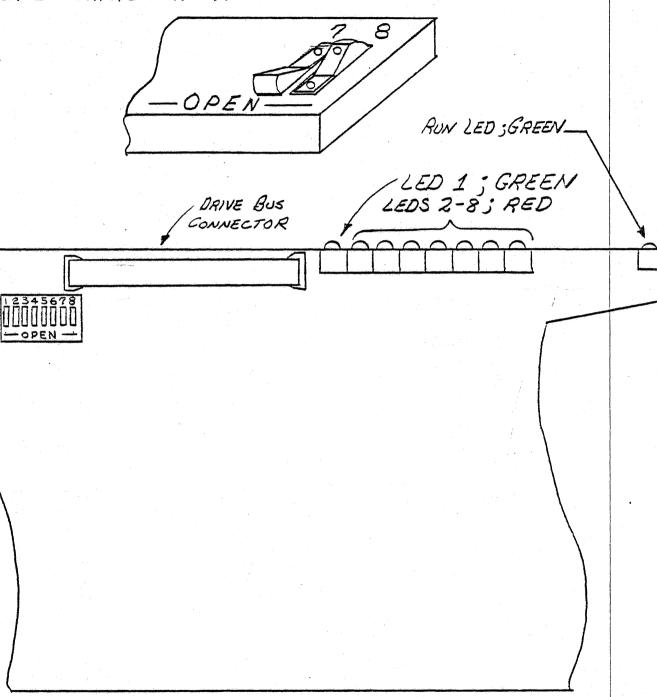

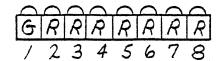

SWITCH AND LED ORIENTATION ON MASTER CONTROLLER CARD

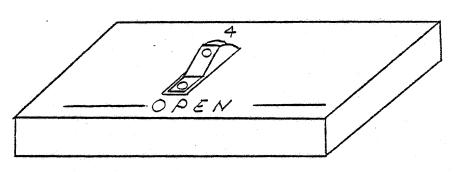

DIP-SWITCH SETTING WHEN PRODUCT IS SHIPPED

-FIGURE 4-2

FIGURE 4-3

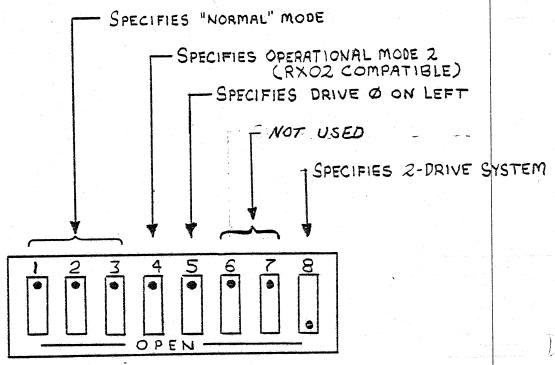

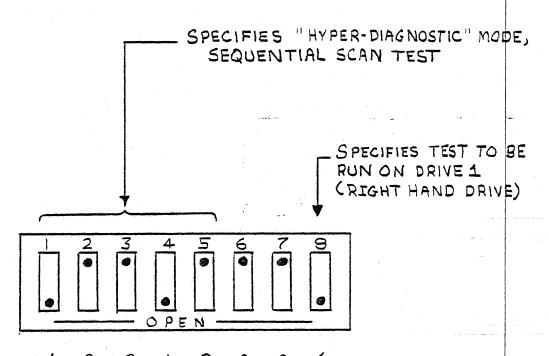

EXAMPLE "HYPER-DIAGNOSTIC" DIP-SWITCH CONFIGURATION

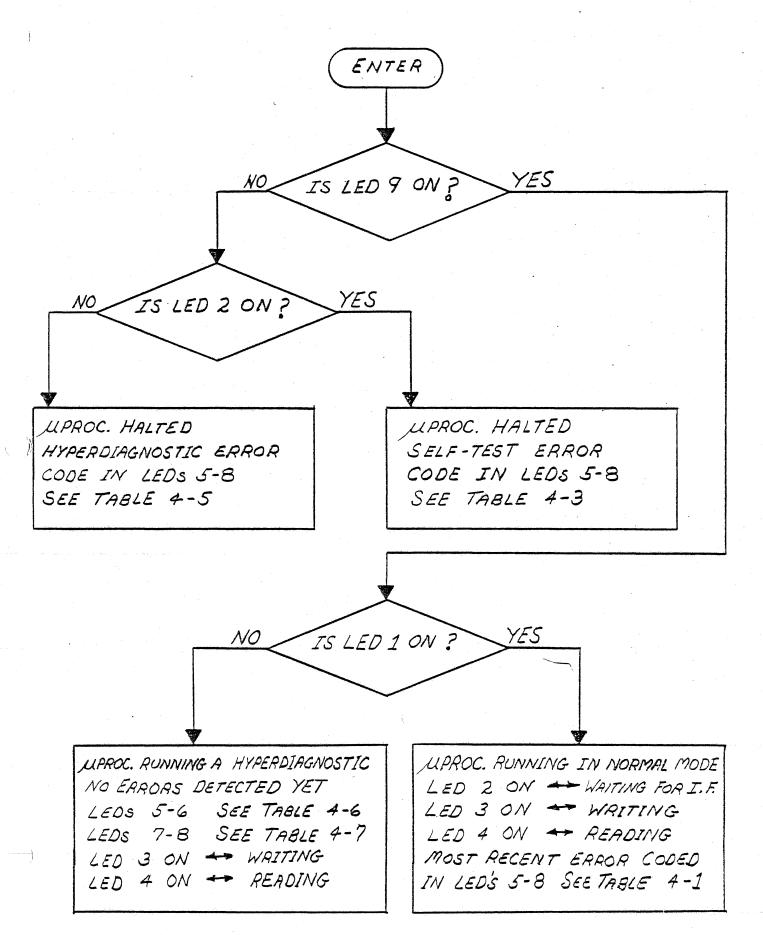

FIGURE 4-4 LED INTERPRETATION EXAMPLES

FIGURE 5-1

COMMAND AND STATUS REGISTER; MODE 1 (RX01 COMPATIBLE)

FIGURE 5-2

REGISTER FORMATS, 11 FAMILY; MODE 1 (RXO1 COMPATIBLE)

FIGURE 5-3

FIGURE 5-4

FILL / EMPTY BUFFER PROGRAM EXAMPLE; MODE 1

FIGURE 5-5

READ / WRITE SECTOR PROGRAM EXAMPLE; MODE 1

FIGURE 5-6

COMMAND AND STATUS REGISTER; MODE 2 (RXO2 COMPATIBLE)

FIGURE 5-7

FIGURE 5-8

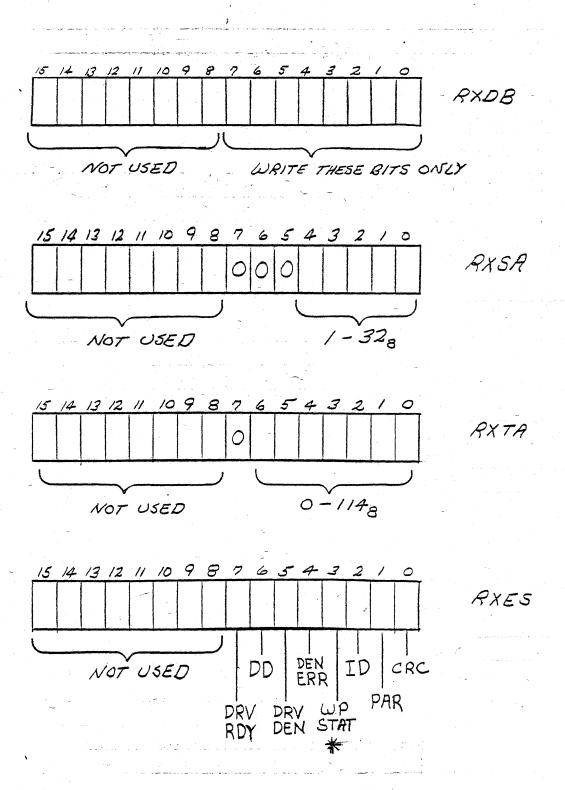

REGISTER FORMATS; 11 FAMILY; MODE 2 (RXO2 COMPATIBLE)

FILL / EMPTY BUFFER PROGRAM EXAMPLE; MODE 2

FIGURE 5-9

READ / WRITE SECTOR PROGRAM EXAMPLE; MODE 2

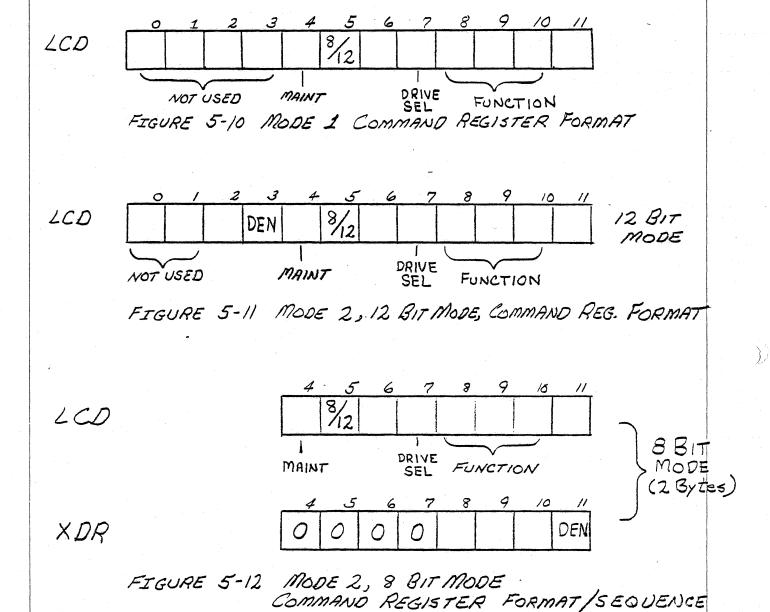

FIGURE 5-10

COMMAND REGISTER FORMAT; PDP-8; MODE 1

FIGURE 5-11

COMMAND REGISTER FORMAT; PDP-8; MODE 2; 12 BIT WORD

FIGURE 5-12

COMMAND REGISTER FORMAT; PDP-8; MODE 2; 8 BIT WORD

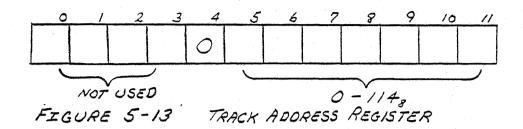

FIGURE 5-13

TRACK ADDRESS REGISTER; PDP-8

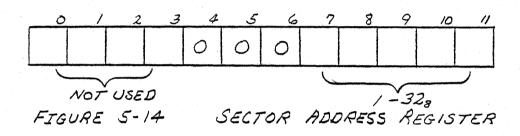

FIGURE 5-14

SECTOR ADDRESS REGISTER; PDP-8

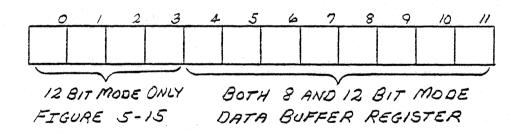

FIGURE 5-15

DATA BUFFER REGISTER; PDP-8

FIGURE 5-16

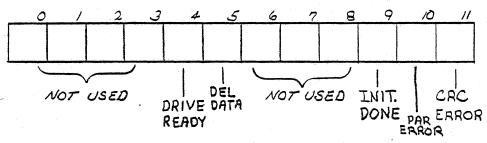

ERROR/STATUS REGISTER; PDP-8; MODE 1

FIGURE 5-17

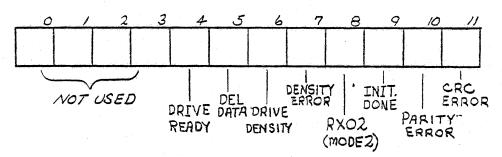

ERROR/STATUS REGISTER; PDP-8; MODE 2

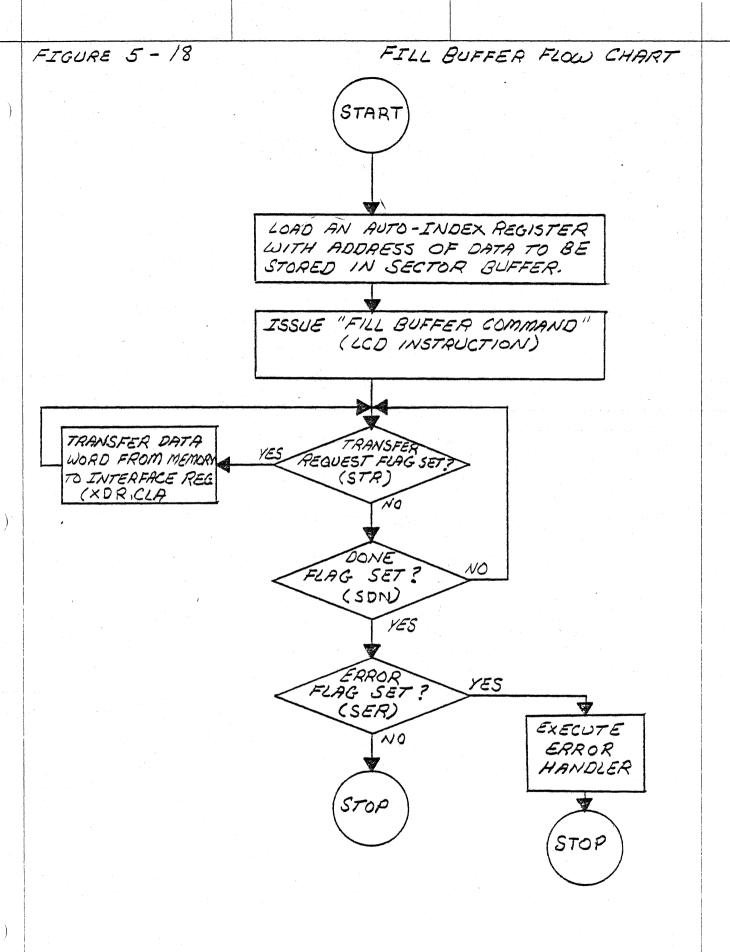

FIGURE 5-18

FILL BUFFER FLOW CHART; PDP-8

FIGURE 5-19 EMPTY BUFFER FLOW CHART; PDP-8

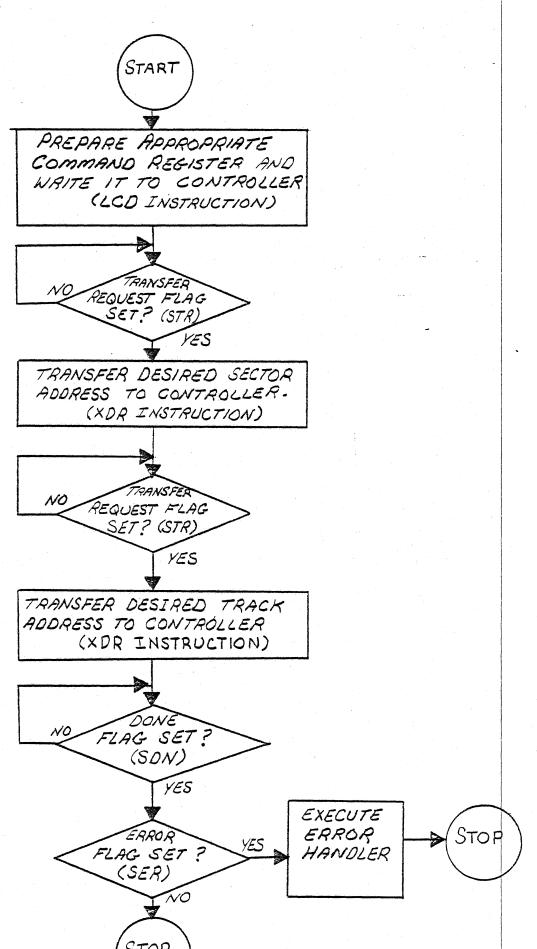

FIGURE 5-20 WRITE/READ/WRITE DEL. DATA FLOW CHART; PDP-8

```

#### LIST OF TABLES

| TABLE 4-4<br>TABLE 4-5<br>TABLE 4-6<br>TABLE 4-7                            | ERROR CLASS CODES IN "NORMAL" MODE  SELF-TEST ERROR CODES  "HYPER-DIAGNOSTIC" ERROR CODE INTERPRETATIONS INTERPRETATION OF LEDS 5-6 DURING A "HYPER-DIAGNOSTIC" INTERPRETATION OF LEDS 7-8 DURING A "HYPER-DIAGNOSTIC"                                                                                                                   |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE 4-8  TABLE 5-1  TABLE 5-2  TABLE 5-3  TABLE 5-4  TABLE 5-5  TABLE 5-6 | DIP-SWITCH CODES FOR "HYPER-DIAGNOSTIC" ROUTINES  ERROR REGISTER CODES; PDP-11; MODE 1  ERROR REGISTER CODES; PDP-11; MODE 2  PDP-8 IOT INSTRUCTIONS USED TO PROGRAM THE DSD 440  PDP-8 FUNCTION CODES, BOTH MODE 1 AND MODE 2  NUMBER OF PROGRAMMED I/O CYCLES VS. MODE AND WORD LENGTH  ERROR REGISTER CODES; PDP-8; MODE 1 AND MODE 2 |

#### LIST OF APPENDICES

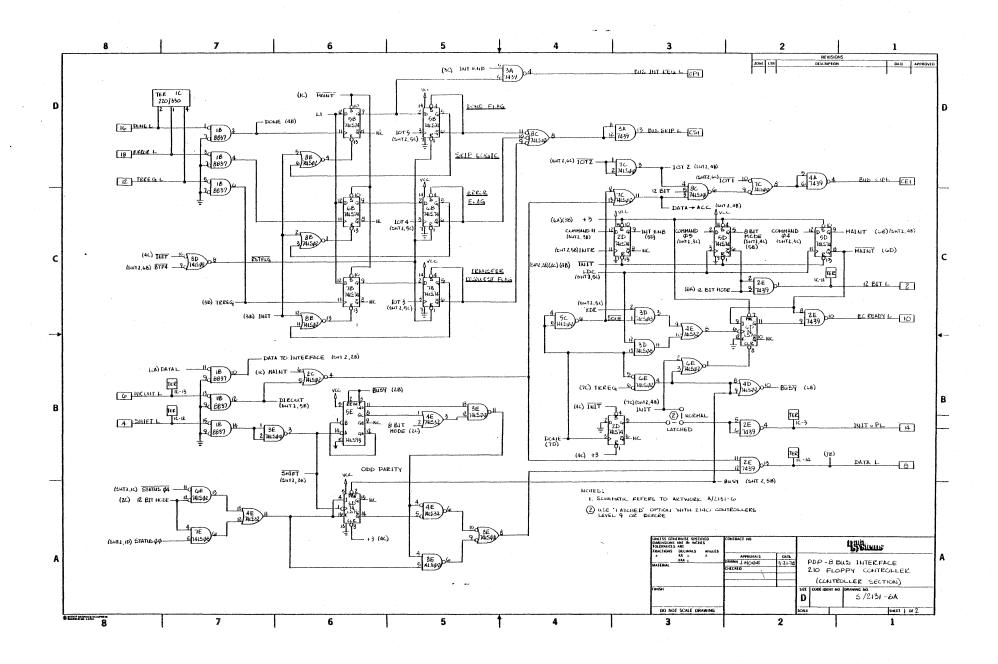

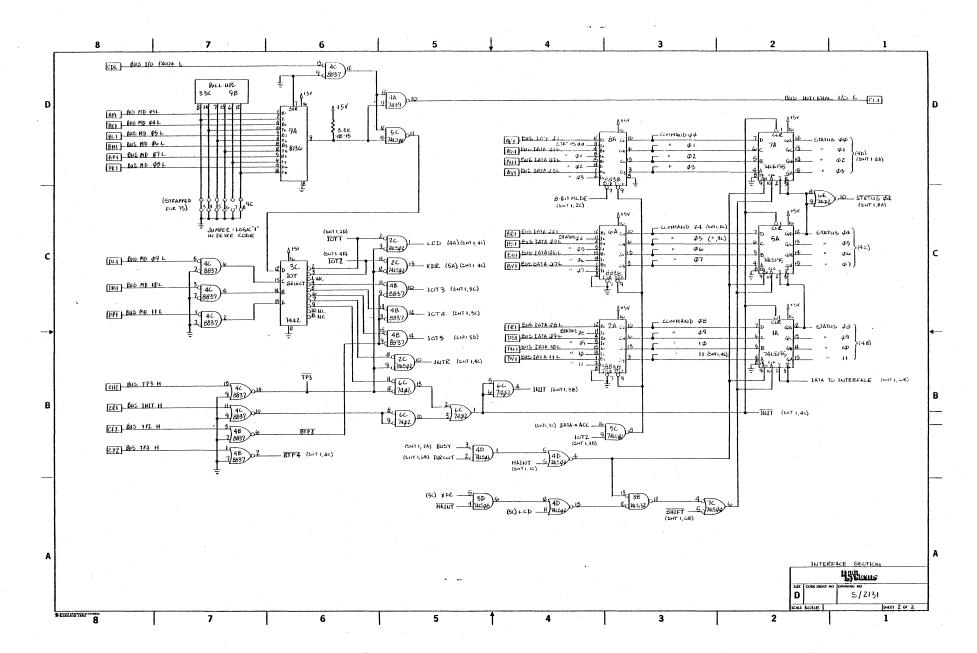

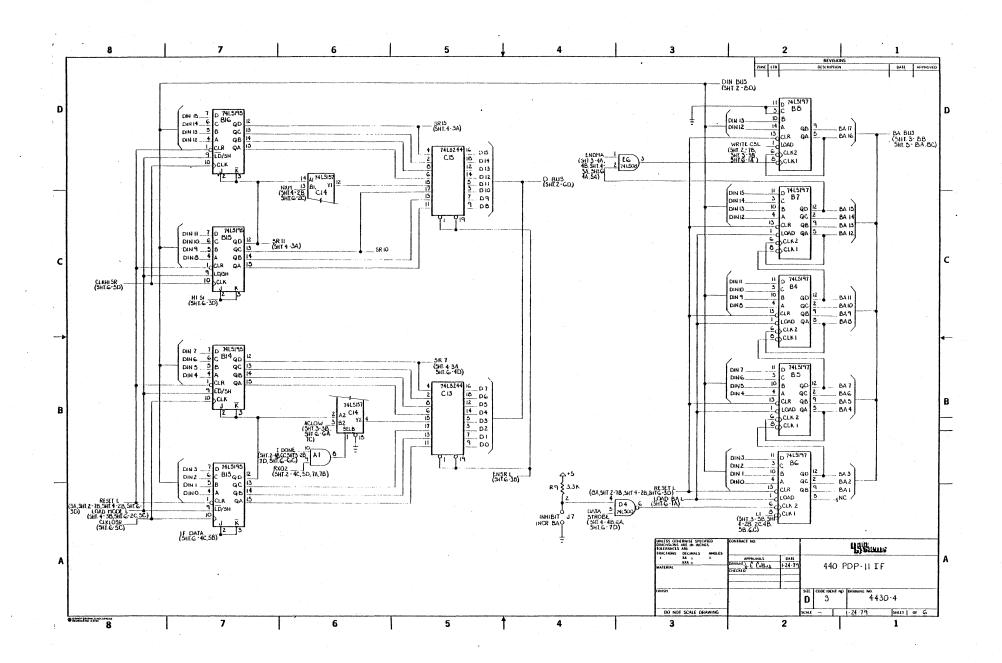

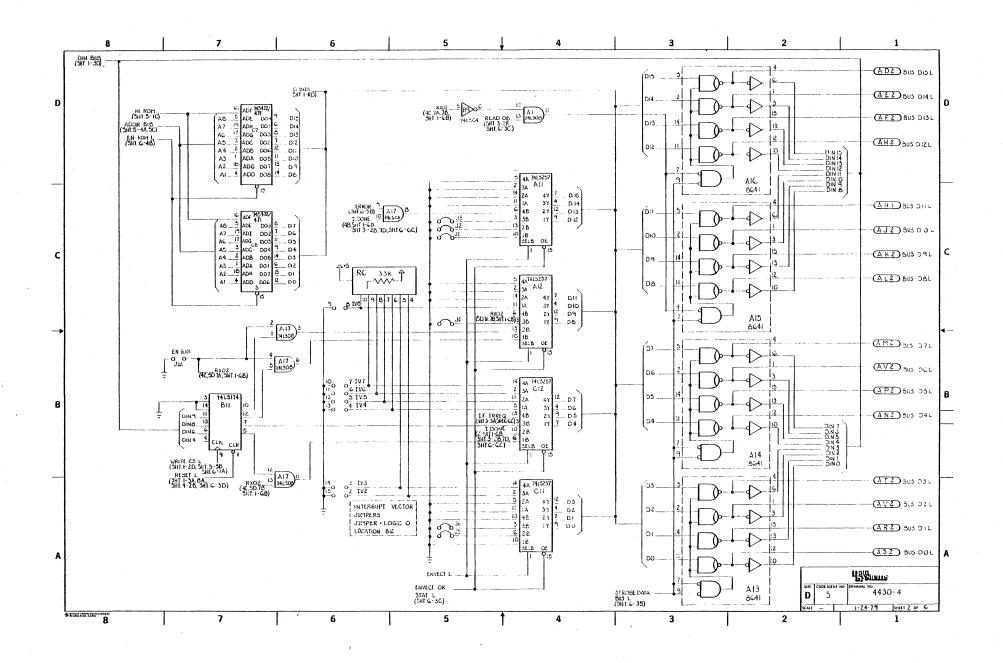

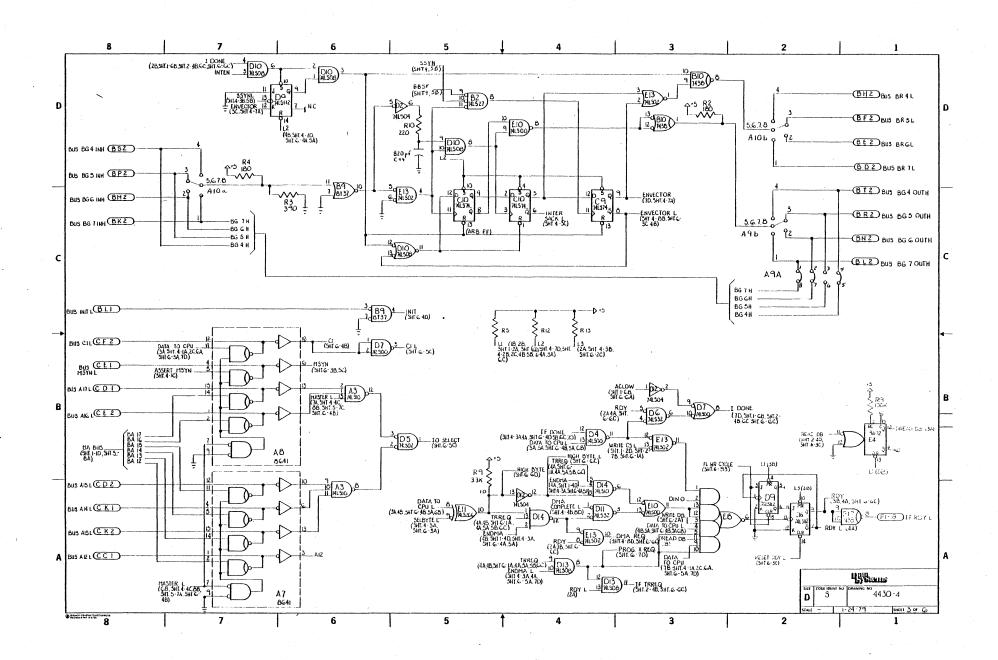

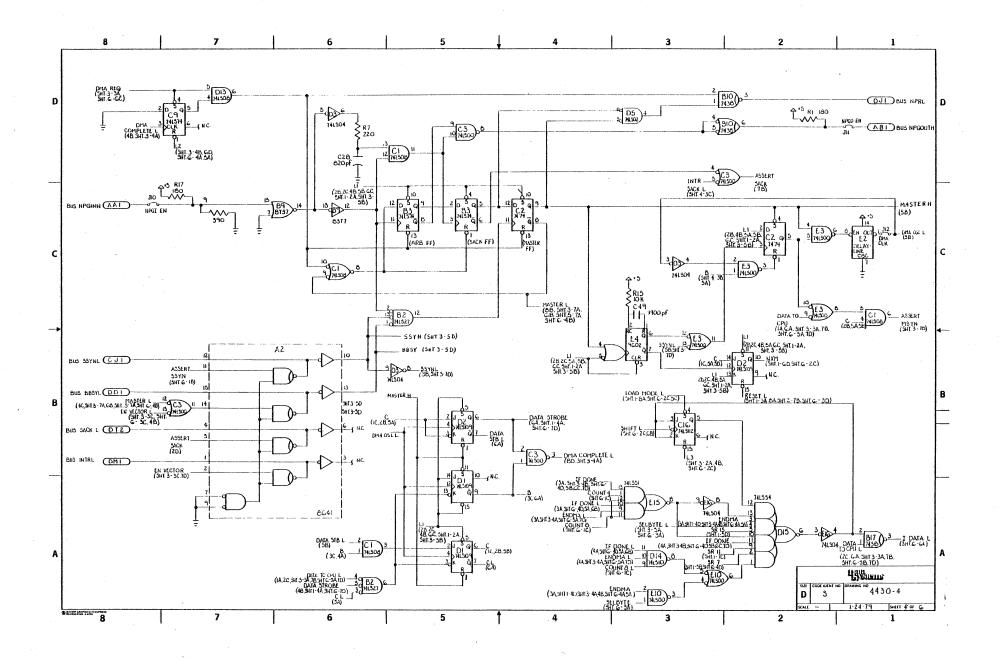

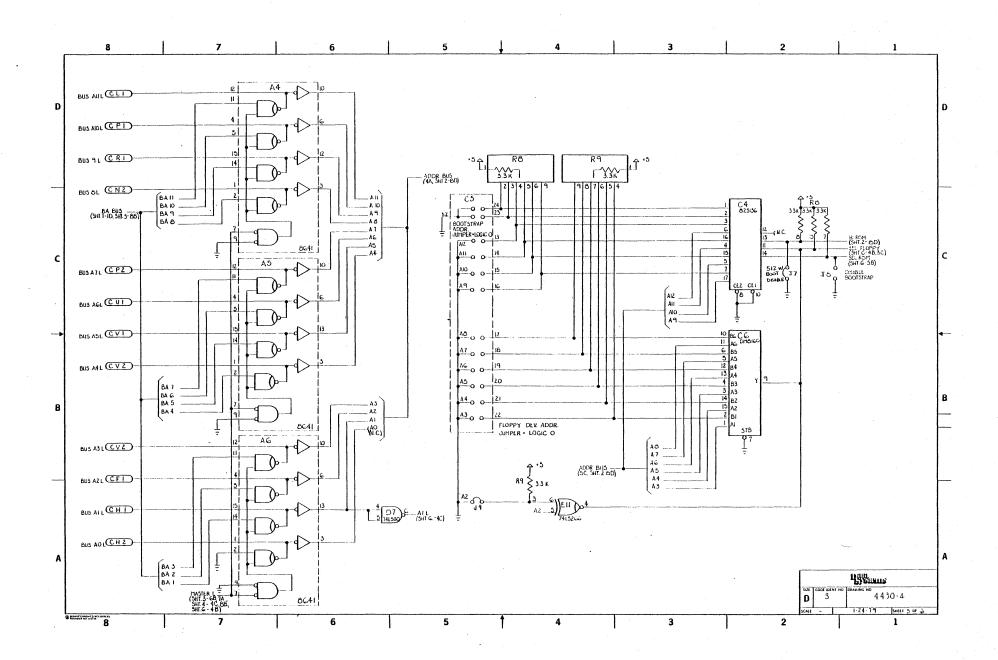

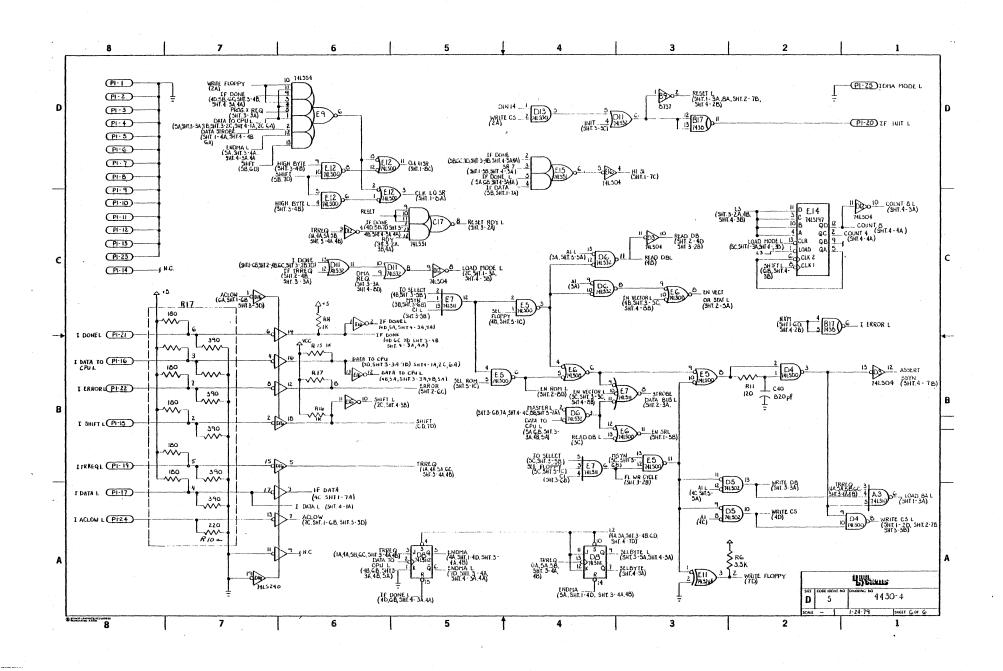

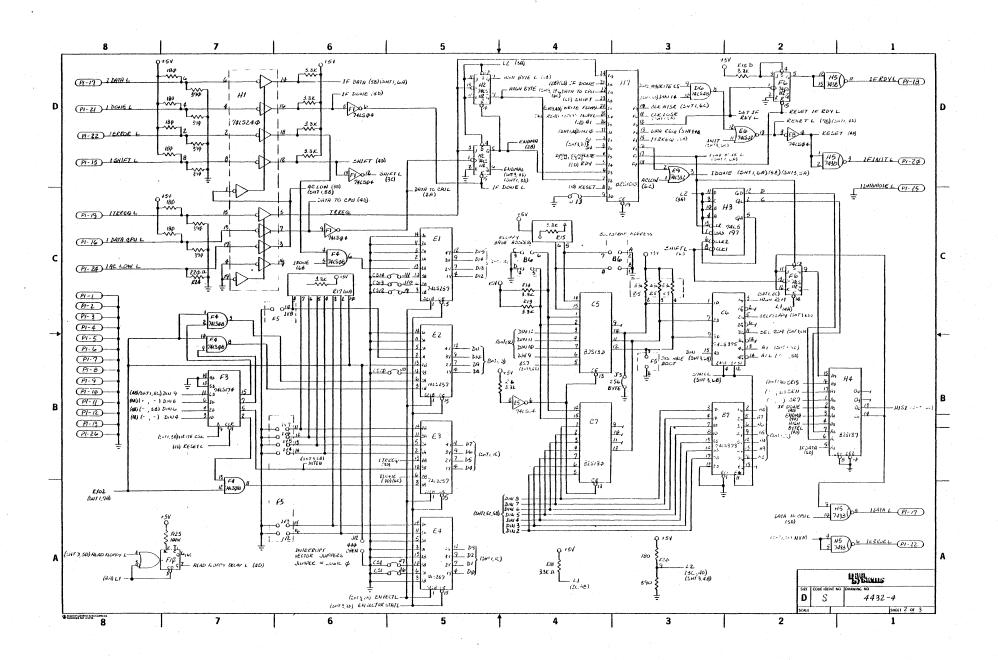

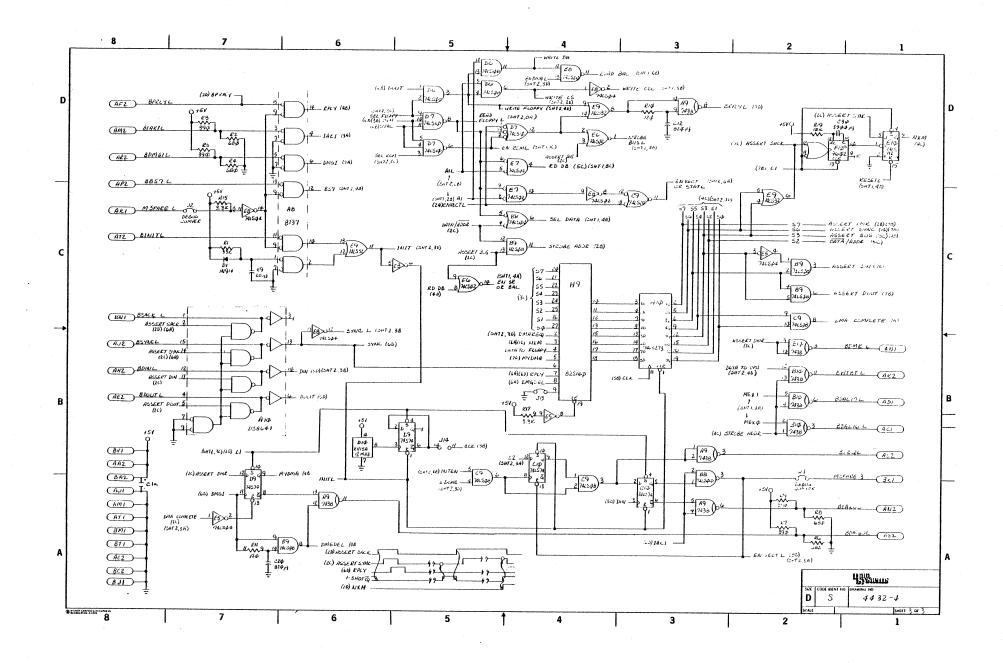

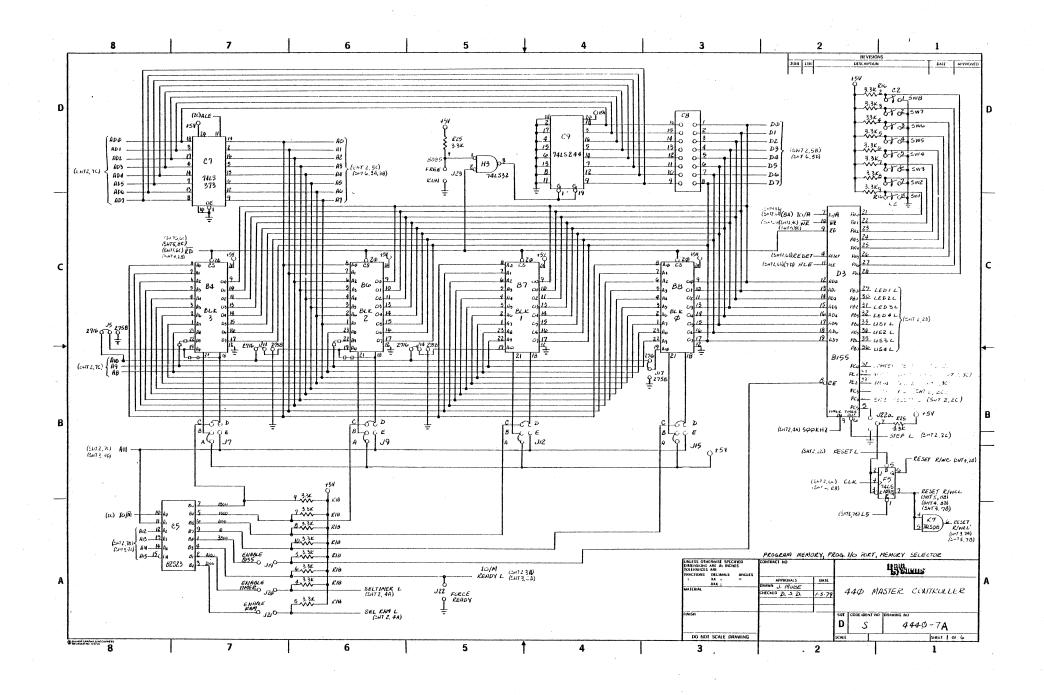

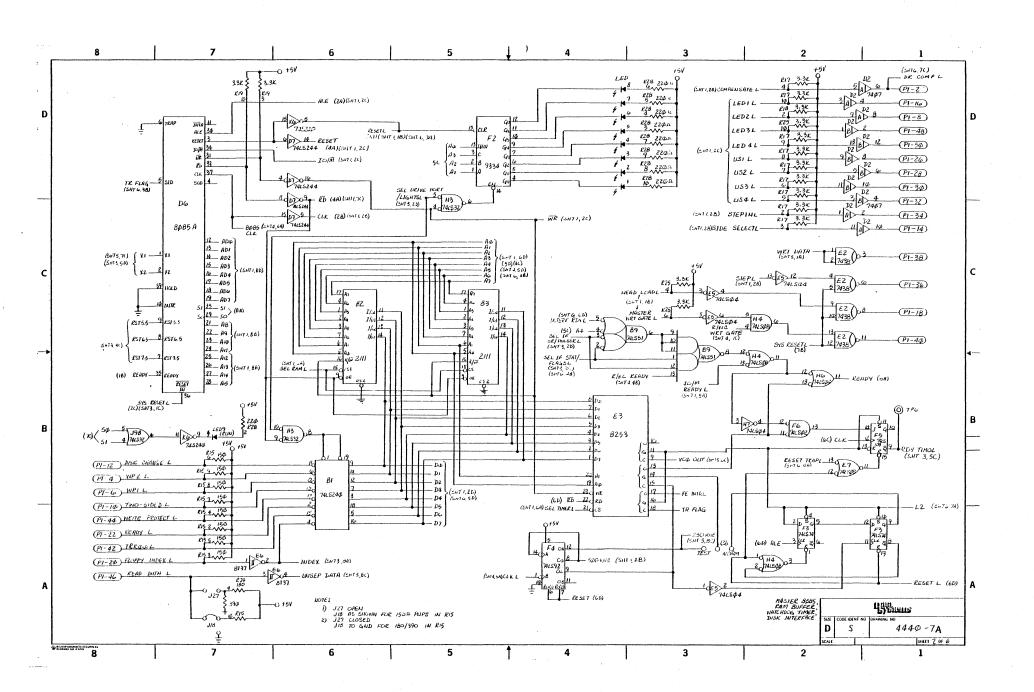

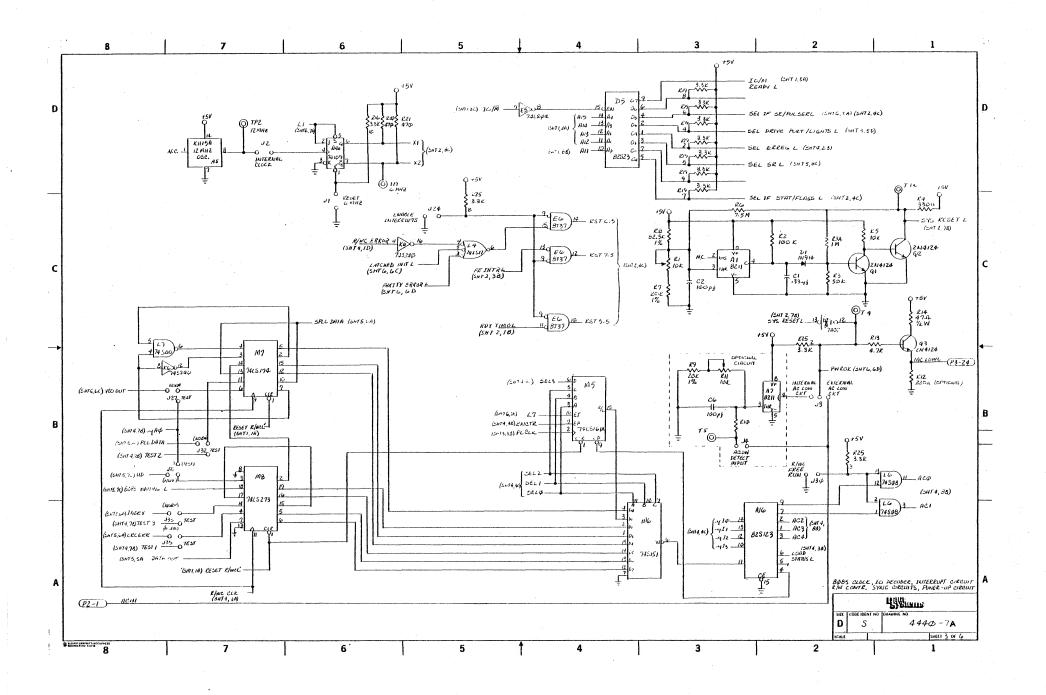

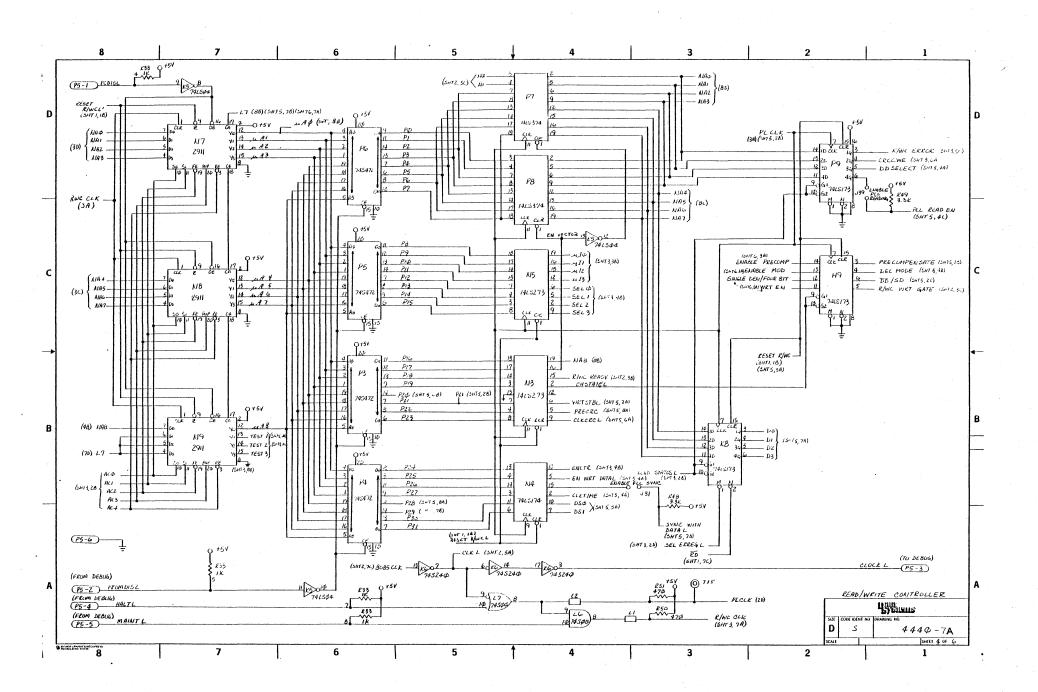

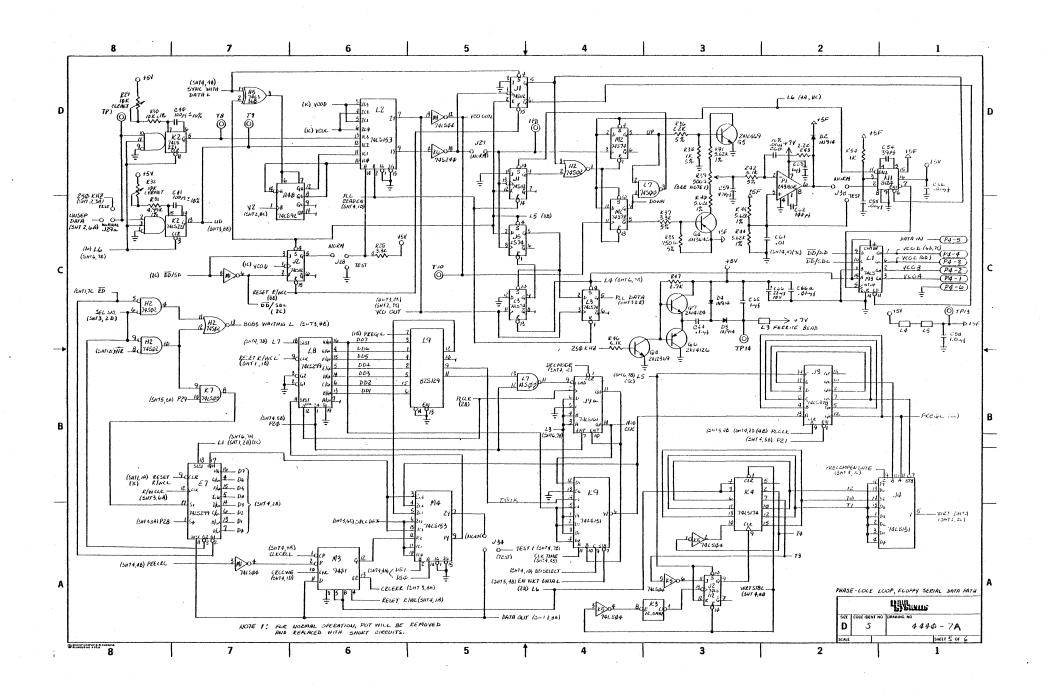

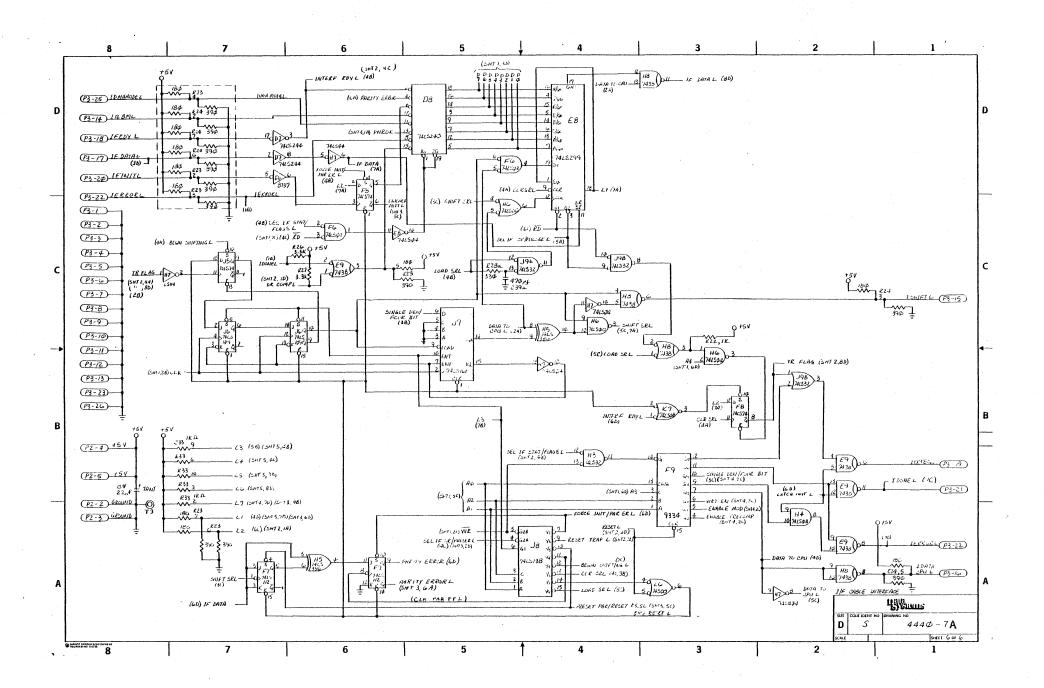

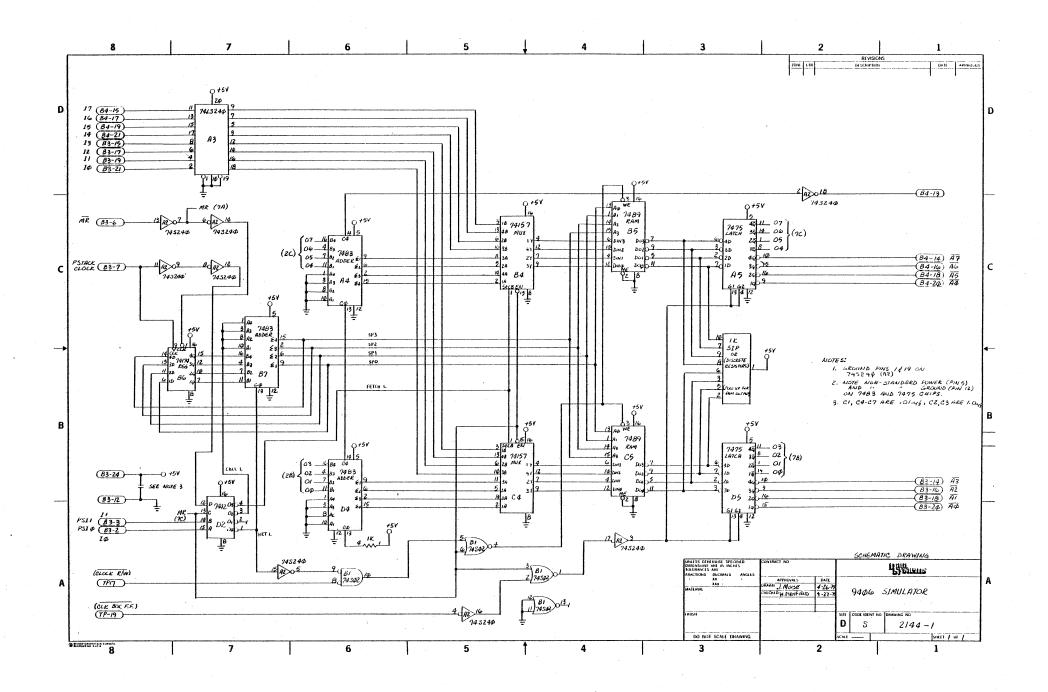

DSD 440 CONTROLLER AND INTERFACE SCHEMATICS

ASSEMBLY LISTING OF PDP-11, LSI-11 BOOTSTRAP PROGRAM

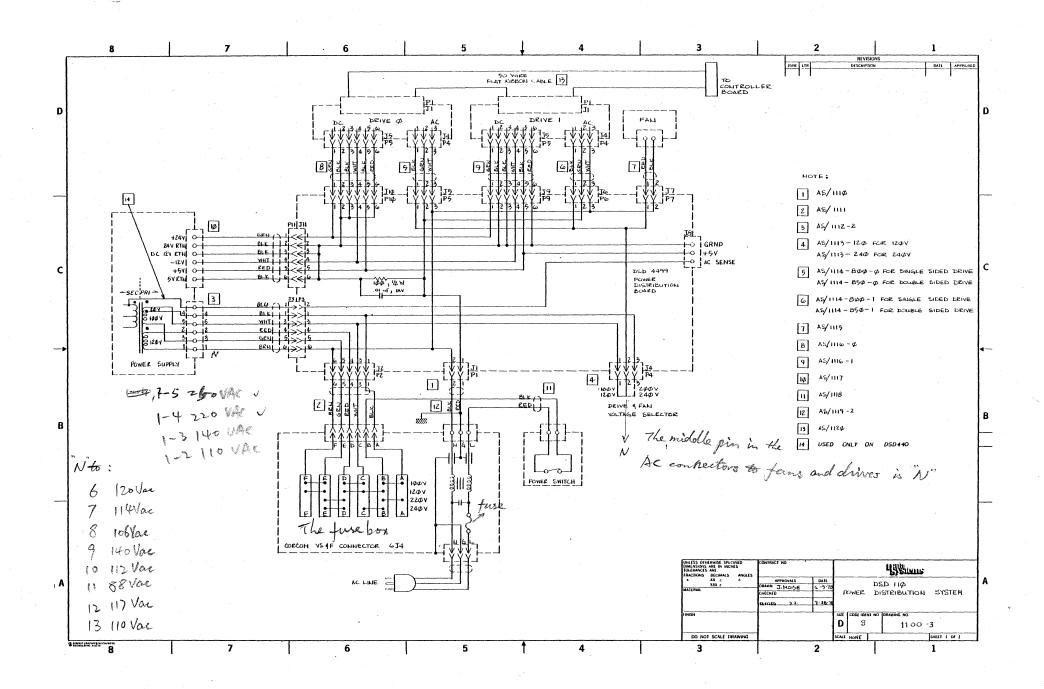

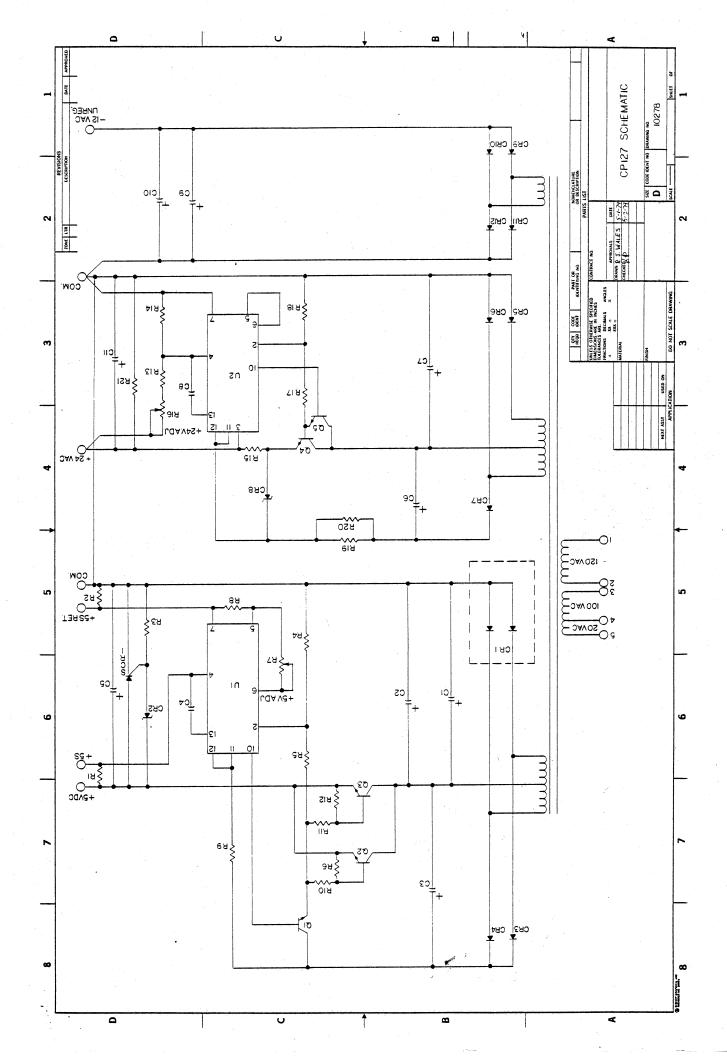

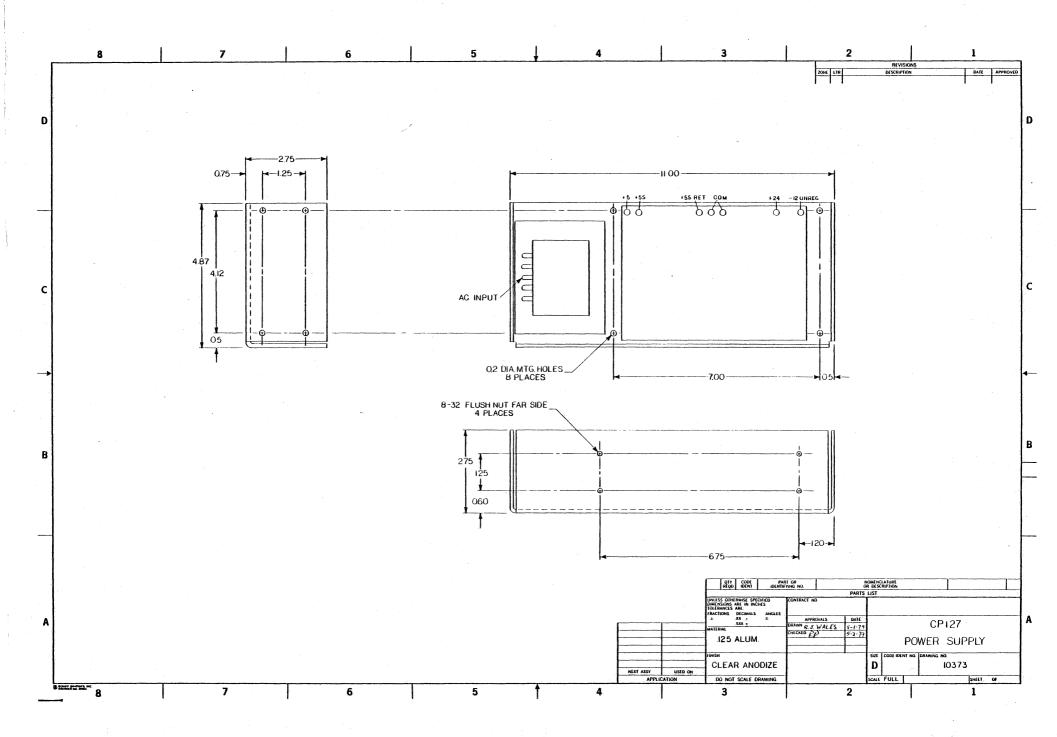

DC POWER SUPPLY SCHEMATIC, SPECIFICATIONS, ETC.

SHUGART SA800/801 DRIVE MAINTENANCE MANUAL

#### PREFACE

The purpose of this manual is to provide the user with sufficient information to correctly set up and operate the DSD 440 Double Density Floppy Disk Memory System. Included is a detailed description of what the product is, how to install it, how to program it, and how to maintain it. A familiarity with basic data processing terminology and the DEC PDP-11, LSI-11, and PDP-8\* is assumed in some sections.

\* DEC, PDP, UNIBUS, and OMNIBUS are registered trademarks of Digital Equipment Corporation.

#### 1-1 PRODUCT INTRODUCTION

The DSD 440 Floppy Disk Memory System is a random access data storage subsystem. Data is stored in fixed-length blocks on preformatted industry standard 8 inch diameter flexible disks. Each flexible disk, or "diskette" can store up to 512 kilobytes (8 bits per byte) of data. The average access time to this data is 296 milliseconds and the average sustainable data transfer rate is 16 kilobytes per second. A complete data storage system consists of a rack-mountable controller/drive subsystem, a computer interface module, and an interconnecting cable.

The DSD 440 can be used with the DIGITAL EQUIPMENT CORPORATION PDP-11, PDP-8, or LSI-11 computers using interface modules supplied by DATA SYSTEMS DESIGN. When used with the appropriate interface module, the DSD 440 is hardware, software, diagnostic, and media compatible with the DEC RXO2 double density flexible disk system. In addition, the DSD 440 has many features not found in the DEC RXO2 system including:

- \* HARDWARE BOOTSTRAP

- \* SELF-CONTAINED DIAGNOSTICS AND UTILITY PROGRAMS

- \* DISKETTE FORMATTING

The DSD 440 can be used with other types of computers if a user designs an interface module that conforms to the DSD 440 Interface Bus Specification.

#### 1-2 PURPOSE OF EQUIPMENT

A Floppy Disk Memory System consists of a set of mechanical and electronic components arranged for the purpose of passing data between a host computer and a flexible disk or, as IBM calls it, a "diskette". Due to their low cost and convenient packaging, flexible disks have become a very popular transportable data storage media for many applications. This popularity will be further increased by flexible disk systems such as the DSD 440 which provide increased capacity and performance over first generation flexible disk systems at only a slight increase in cost.

The DSD 440 was designed to provide a highly reliable, low cost and compact flexible disk system that is totally compatible with the DEC RXO2. While satisfying these design goals, advances in LSI circuitry and microprocessors have made possible the incorporation of a number of "BONUS" features. Important among these features are:

- \* The ability to execute test and utility programs on the controller/drive subsystem even when the controller and drives are not connected to a host computer.

- \* The ability to write-format diskettes in two industry standard formats.

High reliability is attained by using LSI circuits, by burning—in and pretesting all components, and by using field—proven Shugart Associates flexible disk drives. Low cost is attained by a design which minimizes parts count and assemblies. Compactness is provided by packaging two disk drives horizontally in a 5 1/4" high rack—mountable chassis. Figure 1-1 shows the System Block Diagram.

FIGURE 1-1 SYSTEM BLOCK DIAGRAM

42.381 SO SHEETS 5 SQUARE 12.382 100 SHEETS 5 SQUARE 12.382 200 SHEETS 5 SQUARE 142.382 200 SHEETS 5 SQUARE

14

#### 1-3 DISKETTE SYSTEM DESCRIPTION

A flexible disk is an oxide-coated mular disk, 7.8 inches in diameter, and .005 inches thick. It is permanently housed in an 8-inch-square flexible envelope. The flexible disk rotates inside the envelope at 360 RPM whenever the diskette is inserted into an operating drive and the drive door is closed. In standard IBM single density format, a diskette can store up to 256,256 bytes of data. In DEC double density format, a diskette can store 512,512 bytes of data. It is important to realize that there is no physical difference between a diskette which contains single density data and one which contains DEC format double density data. The only difference is the data encoding method that is used to record the user data bytes on the diskette. Single density data is using a technique known as "double frequency recording" while double density data is encoded using a technique known as "modified frequency modulation" or MFM, for short. The very same floppy disk drive can write data jusing both of these data encoding techniques with no problem. Diskettes can commonly differ in the following ways:

- 1) Intended for double or single sided drives

- 2) Hard sectored or soft sectored

- 3) Write protect notch available?

Initially, the DSD 440 will be shipped with the single-sided Shugart model 800 flexible disk drive. It is important to use only diskettes intended for single-sided drives, such as the one shown in the lower half of Figure 1-2. If a diskette intended for a double-sided drive is accidentally loaded into a single sided drive, the photo-sensor will not line up with the index access hole. As a result, the controller will never see an index pulse and will conclude that the drive is simply not ready. Be careful not to try and use an IBM Diskette 2D, Part No. 1766872. These diskettes are explicitly intended for use on double-sided drives. In addition, the format of the recorded data on these diskettes in not compatible with the DEC double density format used on the DSD 440.

The DSD 440 requires the use of soft sectored diskettes. To determine if you have a soft or hard sectored diskette, simply rotate the mylar disk inside the envelope while looking through the index access hole. If you observed more than one hole punched in the mylar disk in the course of a single revolution (maybe 27 holes) you have a hard sectored diskette. Soft sectored diskettes should have only one index hole punched in them.

The need for a write protect notch is completely up to the user. If you have diskettes with this notch, as shown in Figure 1-2, you must cover the notch with an opaque adhesive tab when you want to write on the diskette.

Flexible disk systems are ideal for applications that require a low cost, medium speed, random access memory device. Flexible disk systems provide faster access times than magnetic tapes, and cost less than the bigger rigid disk systems. They can replace paper tape or punch card storage methods. Because the diskettes can be quickly removed, the amount of data that is immediately accessible with a flexible disk system is far greater than the capacity of a single diskette. Diskettes can be exchanged in a drive within seconds, the limiting factor being the dexterity of the user.