# RSO4 DECdisk SERVICE MANUAL

# RSO4 DECdisk SERVICE MANUAL

DEC-00-HRS4A-A-D

Copyright © 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

COMPUTER LAB

**MASSBUS**

### CONTENTS

|           | Page                                                  |

|-----------|-------------------------------------------------------|

| SECTION 1 | INTRODUCTION                                          |

| 1.1       | GENERAL                                               |

| 1.1.1     | Characteristics                                       |

| 1.1.2     | Typical System Configuration                          |

| 1.1.3     | RS04 Recording Technique                              |

| 1.1.4     | Data Format                                           |

| 1.2       | SPECIFICATIONS                                        |

| 1.3       | MAJOR SUBASSEMBLIES                                   |

| 1.3.1     | Head/Disk Subassembly                                 |

| 1.3.2     | Logic Subassembly                                     |

| 1.3.3     | Power Supply/Control Subassembly                      |

| 1.4       | RS04 CONTROLS AND INDICATORS                          |

| 1.5       | OPTIONS                                               |

| 1.5       | OPTIONS1-14                                           |

| SECTION 2 | THEORY OF OPERATION                                   |

| 2.1       | GENERAL                                               |

| 2.2       | ELECTRICAL PRINCIPLES OF OPERATION                    |

| 2.2.1     | MASSBUS Interface                                     |

| 2.2.2     | RS04 Logical Block Diagram                            |

| 2.2.3     | Drive Operations                                      |

| 2.2.4     | Maintenance Mode                                      |

| 2.2.5     | Power Distribution and Control                        |

| 2.2.6     | Power Fail                                            |

| 2.3       | MECHANICAL PRINCIPLES OF OPERATION                    |

| 2.3.1     | Motor                                                 |

| 2.3.2     | Disk                                                  |

| 2.3.3     |                                                       |

| 2.3.4     | Heads       2-31         Air Filter System       2-31 |

|           |                                                       |

| 2.4       | MAGNETIC PRINCIPLES OF OPERATION                      |

| SECTION 3 | ELECTRICAL SERVICING                                  |

| 3.1       | GENERAL                                               |

| 3.2       | DIAGNOSTIC TESTING                                    |

| 3.2.1     | DECsystem-10 Diagnostics                              |

| 3.2.2     | Troubleshooting in DECsystem-10 Systems               |

| 3.2.3     | PDP-11 Diagnostics                                    |

| 3.2.4     | Troubleshooting in PDP-11 Systems                     |

| 3.2.5     | Problem Identification (Head/Disk Assembly)           |

| 3.3       | LOGIC MODULES                                         |

| 3.3.1     | Address Module M7754                                  |

| 3.3.2     | Command Decode Module M7759                           |

| 3.3.3     | Control Module M7755                                  |

| 3.3.4     | Data Register Module M7753                            |

| 3.3.5     | Deskew Module M7752                                   |

| 3.3.6     | Encode/Decode Module M7751                            |

| 3.3.7     | Format Module M7771                                   |

|           |                                                       |

| 3.3.8     |                                                       |

| 3.3.9     | Timing Amp Module G092                                |

## **CONTENTS (Cont)**

|                  | Page                                            |  |

|------------------|-------------------------------------------------|--|

| 3.4              | ANALOG MODULES                                  |  |

| 3.4.1            | Read/Write and Detection Module G182            |  |

| 3.4.2            | Head Matrix Module M7758                        |  |

| 3.4.3            |                                                 |  |

| 3.4.4            | Alternate Track Option M7756                    |  |

| 3.5              | 8                                               |  |

| 3.6              |                                                 |  |

| 3.0              | POWER CONTROL                                   |  |

| <b>SECTION 4</b> | MECHANICAL SERVICING                            |  |

| 4.1              | GENERAL                                         |  |

| 4.2              | FILTERS 4-1                                     |  |

| 4.2.1            | Pre-Filter                                      |  |

| 4.2.2            | Absolute (Disk Assembly) Filter                 |  |

| 4.2.3            | Blower Pre-Filter                               |  |

| 4.3              | STATUS INDICATOR LAMPS                          |  |

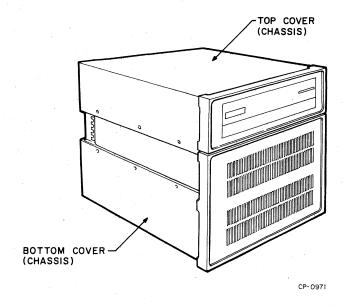

| 4.4              | COVER (CHASSIS)                                 |  |

| 4.5              | POWER/CONTROL ASSEMBLY                          |  |

| 4.6              | FAN 4-6                                         |  |

| 4.7              | BLOWER ASSEMBLY                                 |  |

| 4.8              | READ/WRITE HEADS                                |  |

| 4.9              | DISK                                            |  |

| 4.10             | DISK DRIVE MOTOR                                |  |

|                  |                                                 |  |

| <b>SECTION 5</b> | INSTALLATION                                    |  |

| 5.1              | GENERAL                                         |  |

| 5.2              | DRIVE SHIPPED SEPARATELY                        |  |

| 5.3              | DRIVE MOUNTED IN A RACK                         |  |

| 3.3              | DRIVE MOONTED IN A RACK 5-2                     |  |

| APPENDIX A       | DETAILED TIMING DIAGRAMS                        |  |

| APPENDIX B       | LOGIC DICTIONARY (SIGNAL GLOSSARY)              |  |

|                  |                                                 |  |

| APPENDIX C       | MASSBUS TRANSCEIVERS PIN MAP                    |  |

| APPENDIX D       | IC DESCRIPTIONS                                 |  |

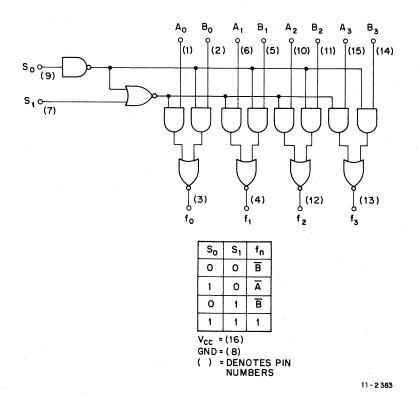

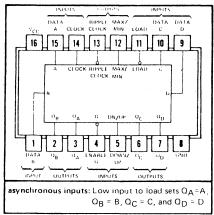

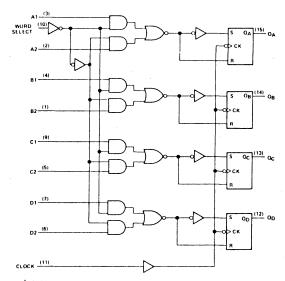

| 8234             | 2-Input 4-Bit Digital Multiplexer               |  |

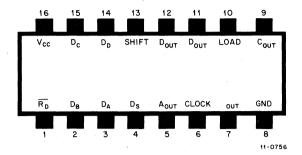

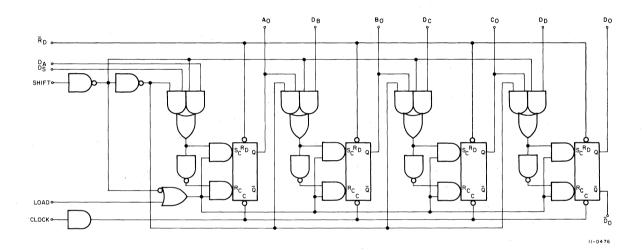

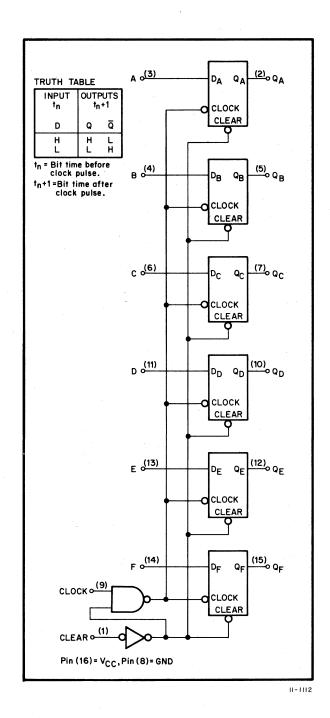

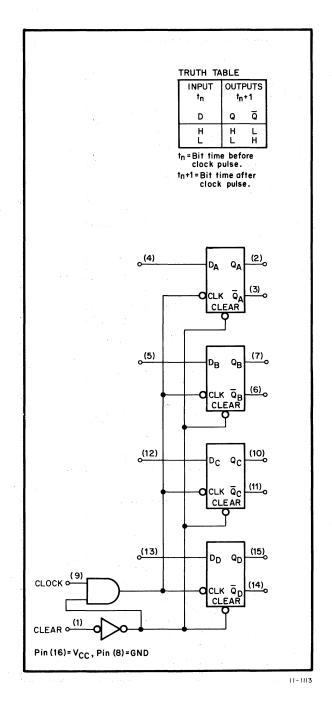

| 8271             | 4-Bit Shift Register                            |  |

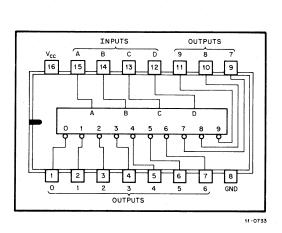

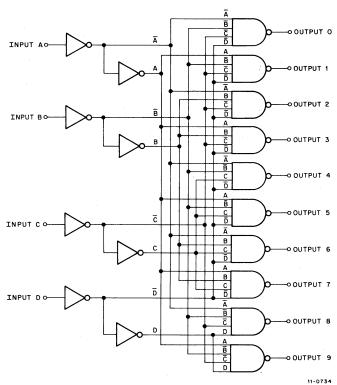

| 7442             | 4-Line-To-10-Line Decoder                       |  |

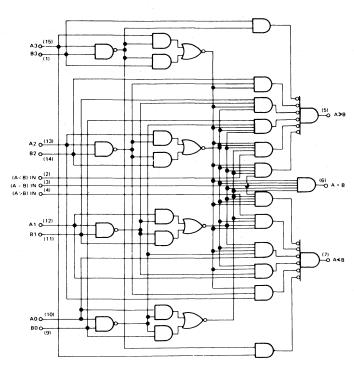

| 7485             | 4-Bit Magnitude Comparator                      |  |

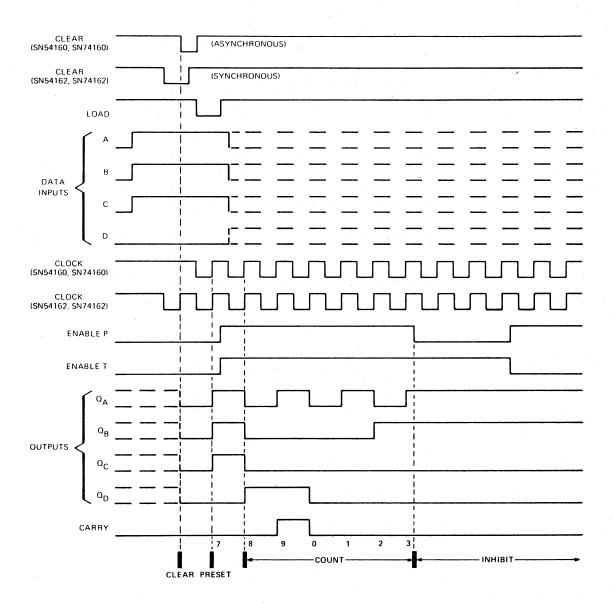

| 7490             | Decade Counter                                  |  |

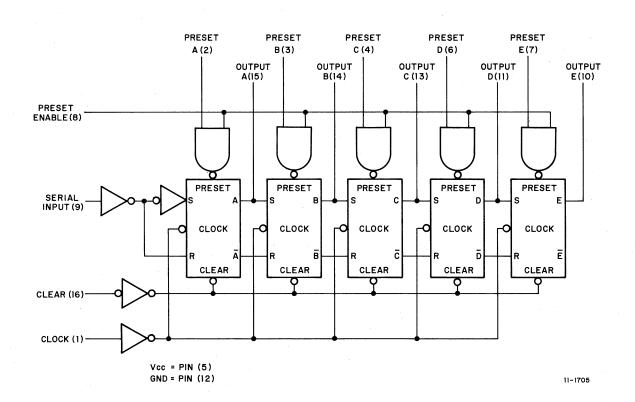

| 7496             | 5-Bit Shift Register                            |  |

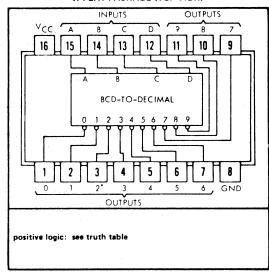

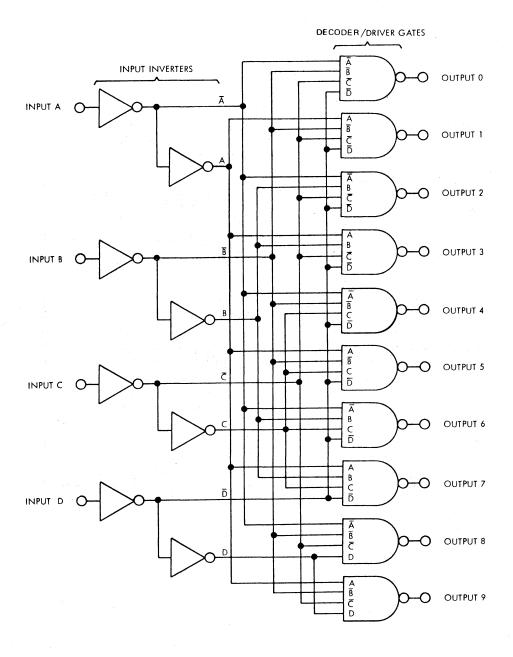

| 74145            | BCD-To-Decimal Decoder/Driver                   |  |

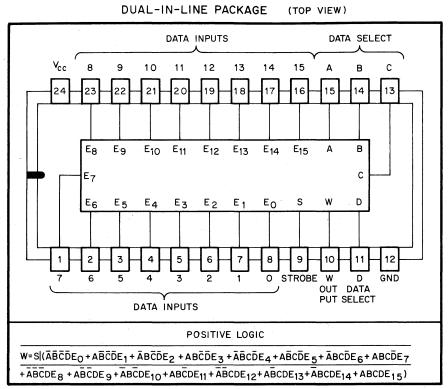

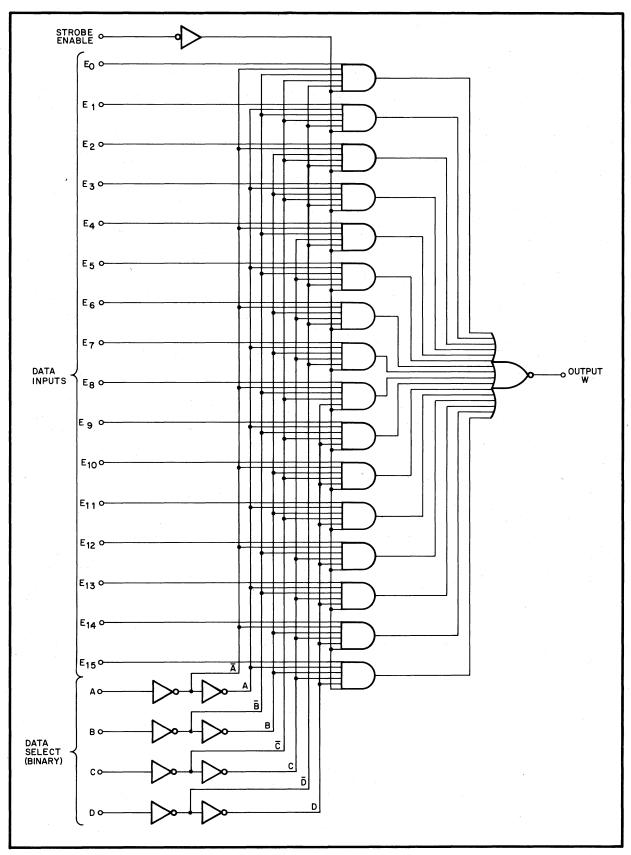

| 74150            | Data Selector/Multiplexer                       |  |

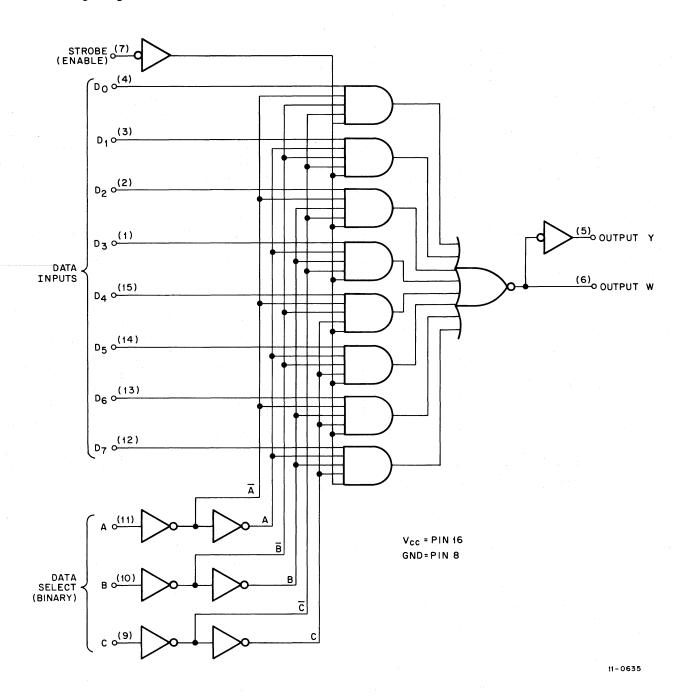

| 74151            | Data Selector/Multiplexer                       |  |

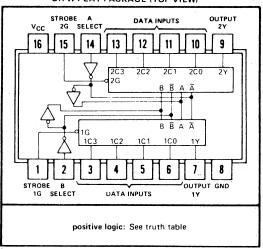

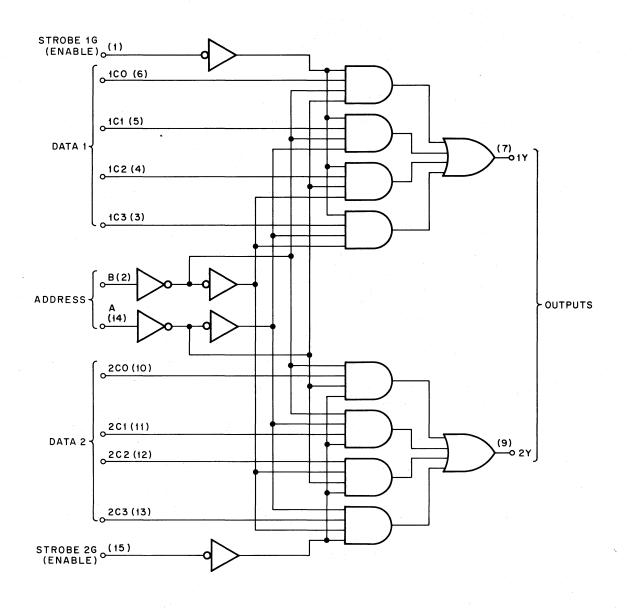

| 74153            | Dual 4-Line-To-1-Line Data Selector/Multiplexer |  |

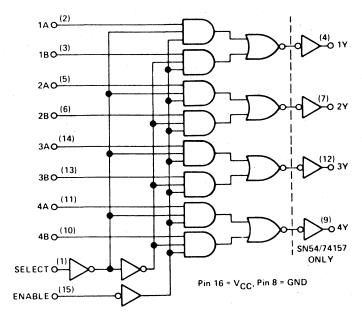

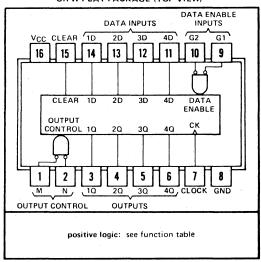

| 74157            | Quadruple 2-Line-To-1-Line Multiplexer          |  |

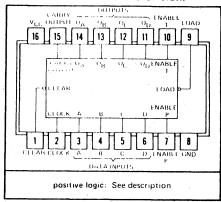

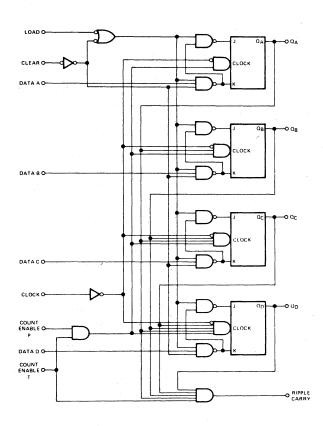

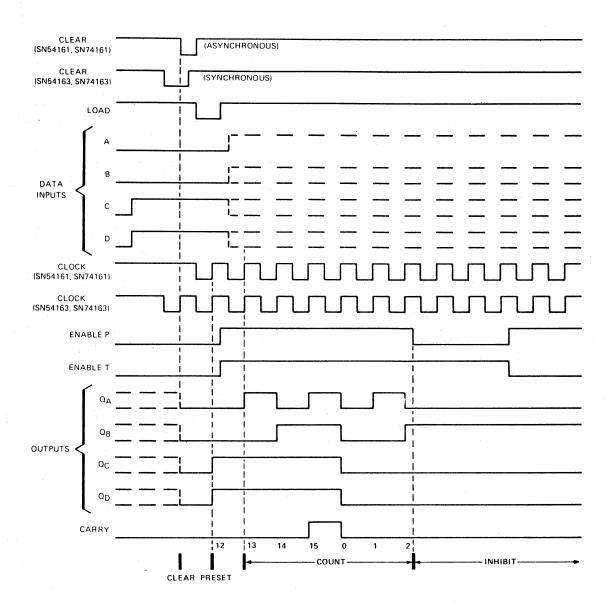

| 74161            | Synchronous 4-Bit Counter                       |  |

| 74173            | 4-Bit D-Type Register with Tri-State Output     |  |

### **CONTENTS (Cont)**

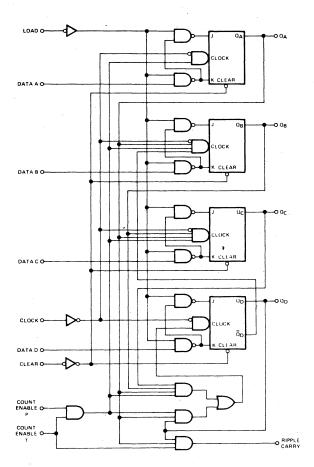

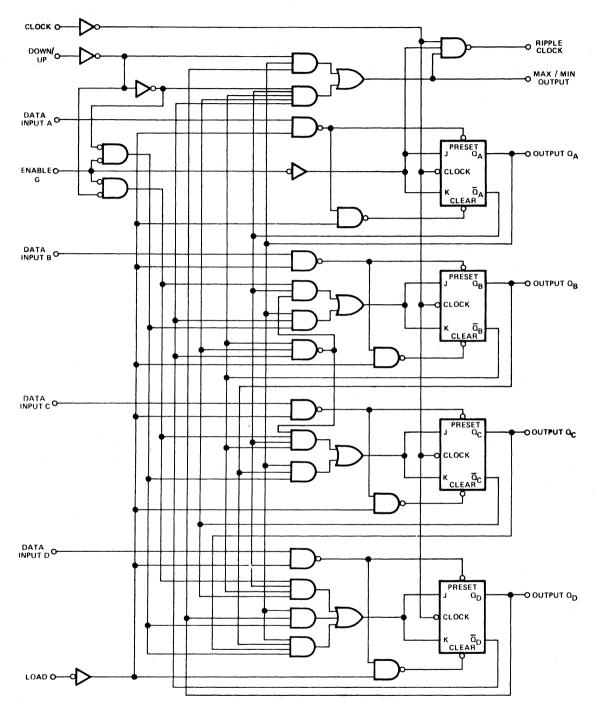

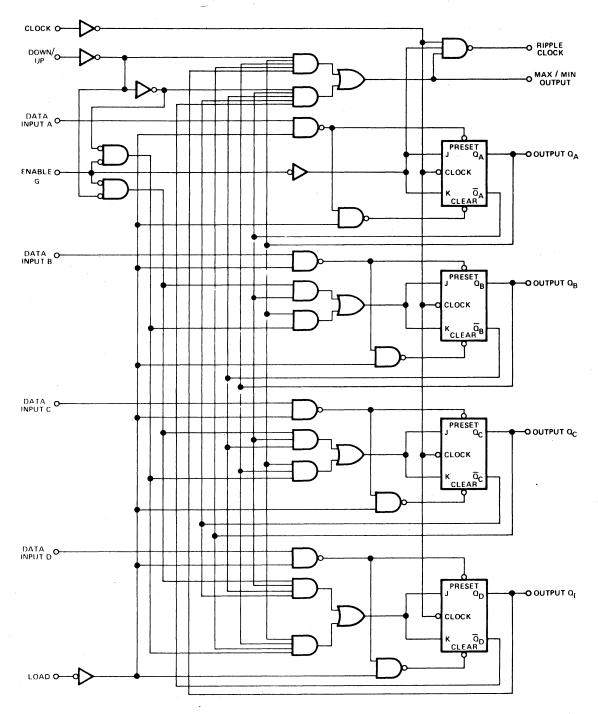

Synchronous Up/Down Counter with Down/Up Mode Control

Synchronous Up/Down Counter with Down/Up Mode Control

74174

74175

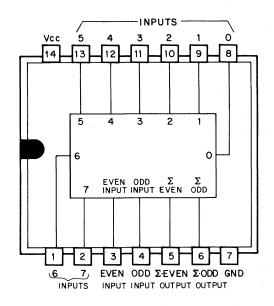

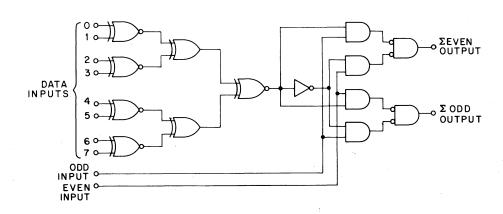

74180

74190 74191

74298

Hex D-Type Flip-Flops

Quad D-Type Flip-Flops

Parity Control Generator/Checker

Quadruple 2-Input Multiplexer with Storage

Page

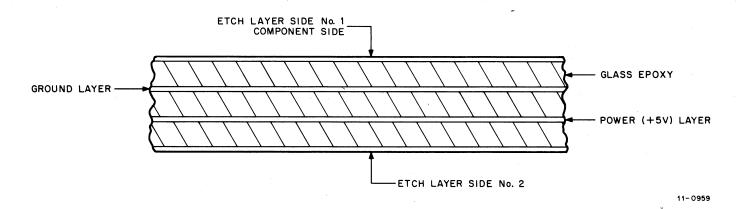

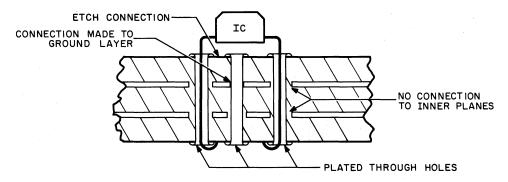

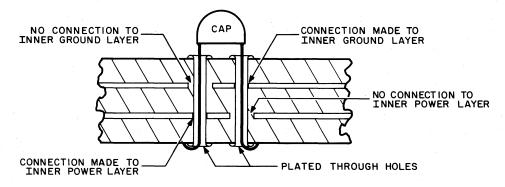

| APPENDIX E | MULTILAYER BOARD TECHNIQUES                                |        |

|------------|------------------------------------------------------------|--------|

| APPENDIX F | TIMING TRACK WRITING PROCEDURE                             |        |

| APPENDIX G | RECOMMENDED FILTER MAINTENANCE                             |        |

| APPENDIX H | RS04 DECDISK PREVENTIVE MAINTENANCE                        |        |

|            | ILLUSTRATIONS                                              |        |

| Figure No. | Title                                                      | Page   |

| 1-1        | RS04 Typical System Configuration                          | . 1-2  |

| 1-2        | RS04 Data Track Format Schematic Diagram                   |        |

| 1-3        | Major Subassembly Locations                                |        |

| 1-4        | Power Controls and Indicators                              |        |

| 1-5        | Front Panel Indicators                                     | . 1-10 |

| 1-6        | Error Indicators                                           |        |

| 1-7        | RS04 Write Lock Protect Address Switches                   |        |

| 1-8        | RS04 Unit Select Switches                                  |        |

| 1-9        | Effect of Sector Interleaving On RS04 Transfer Rate        | . 1-14 |

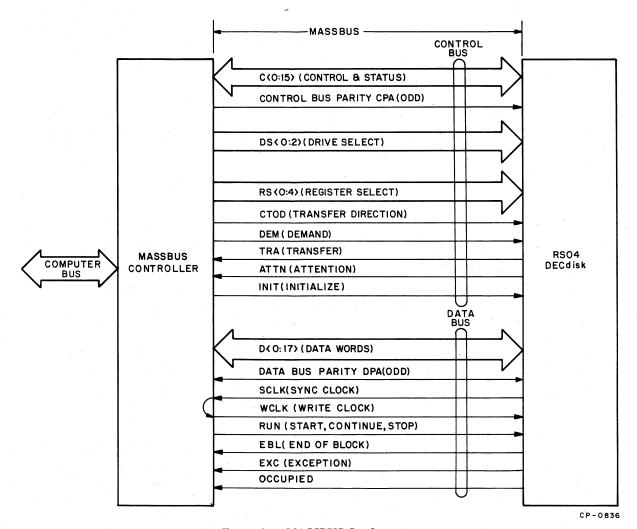

| 2-1        | MASSBUS Configuration                                      | . 2-2  |

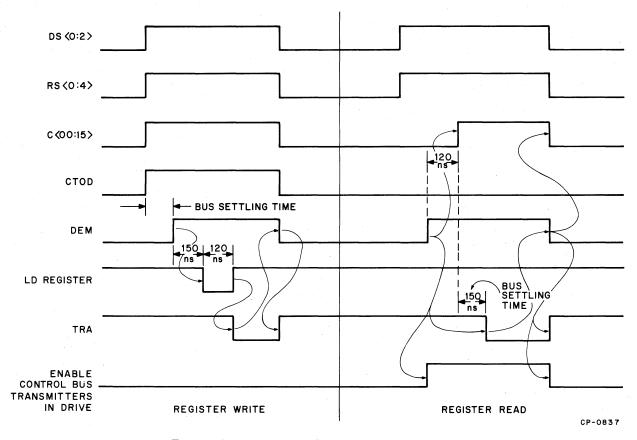

| 2-2        | Typical RS04 Control Bus Transfer Timing                   | . 2-3  |

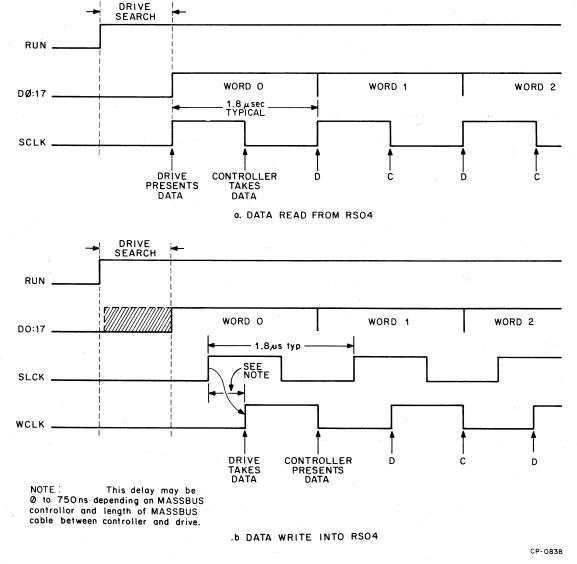

| 2-3        | Data Bus Transfer Timing                                   | . 2-4  |

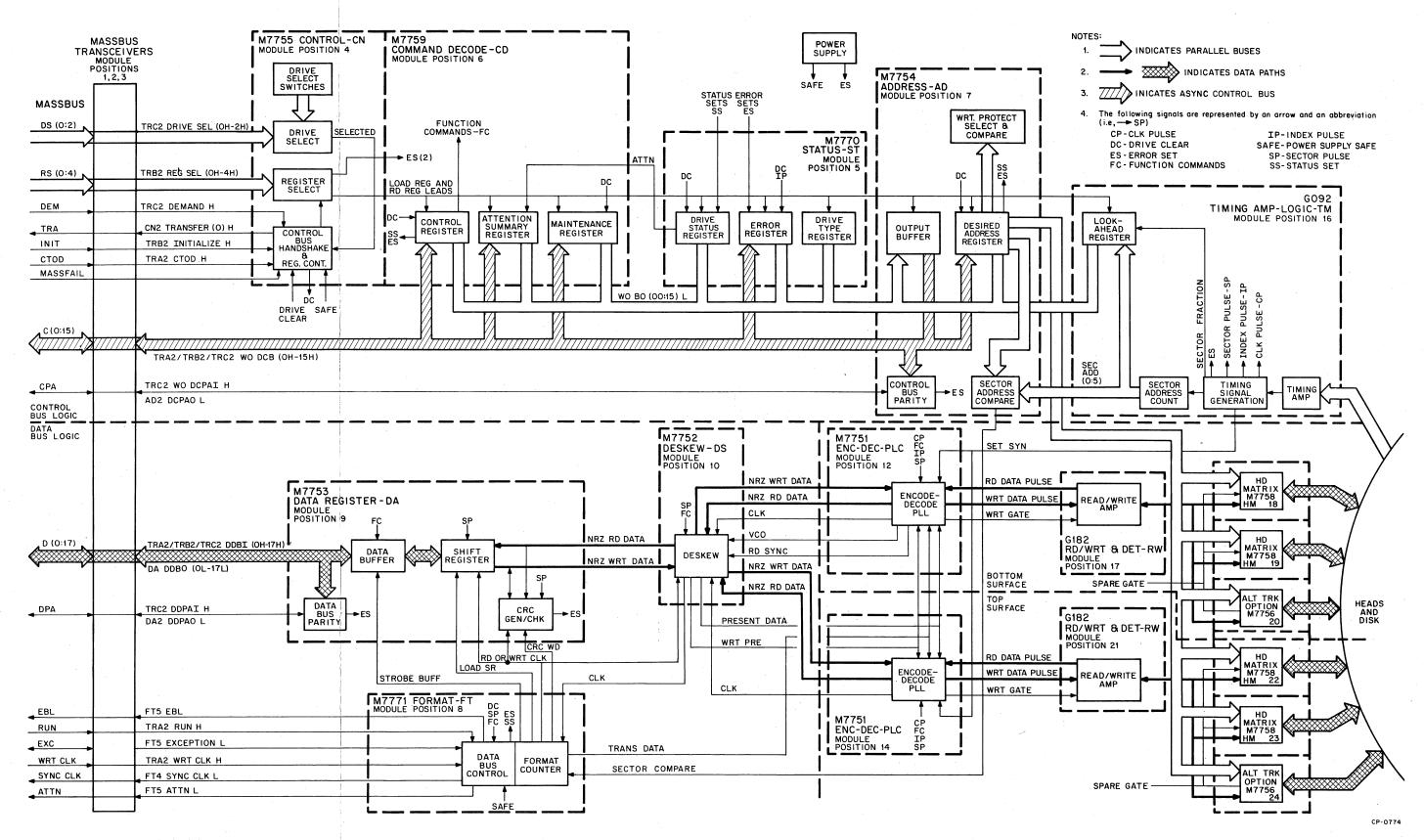

| 2-4        | RS04 Logical Block Diagram                                 | . 2-6  |

| 2-5        | Functional Representation of Register Data Paths (One Bit) | . 2-7  |

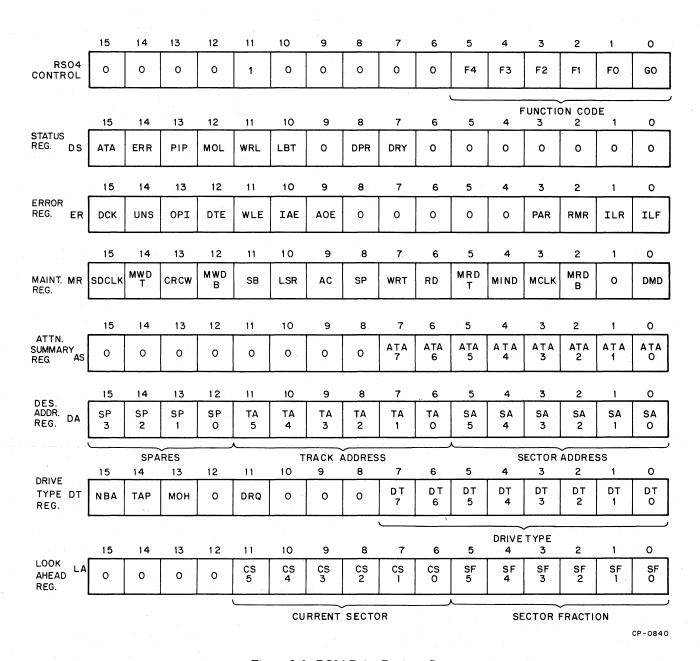

| 2-6        | RS04 Drive Register Summary                                | . 2-10 |

| 2-7        | RS04 Control Register Format                               | . 2-11 |

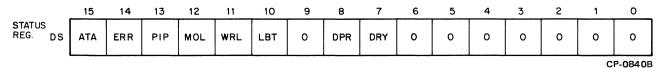

| 2-8        | Status Register Format                                     |        |

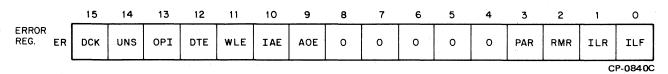

| 2-9        | Error Register Format                                      | . 2-13 |

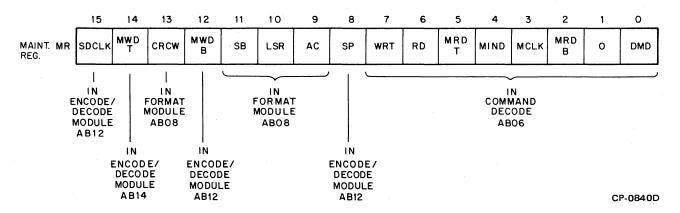

| 2-10       | Maintenance Register Format                                |        |

| 2-11       | Attention Summary Register Format and Sources              |        |

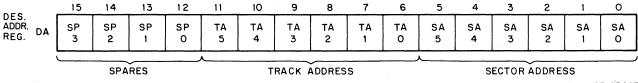

| 2-12       | Desired Address Register Format                            |        |

| 2-13       | Drive Type Register Format                                 |        |

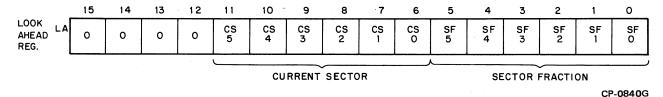

| 2-14       | Look Ahead Register Format                                 |        |

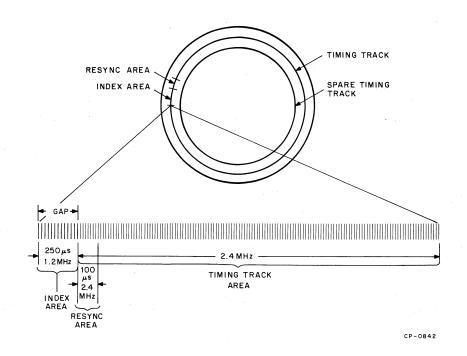

| 2-15       | RS04 Timing Track Format                                   |        |

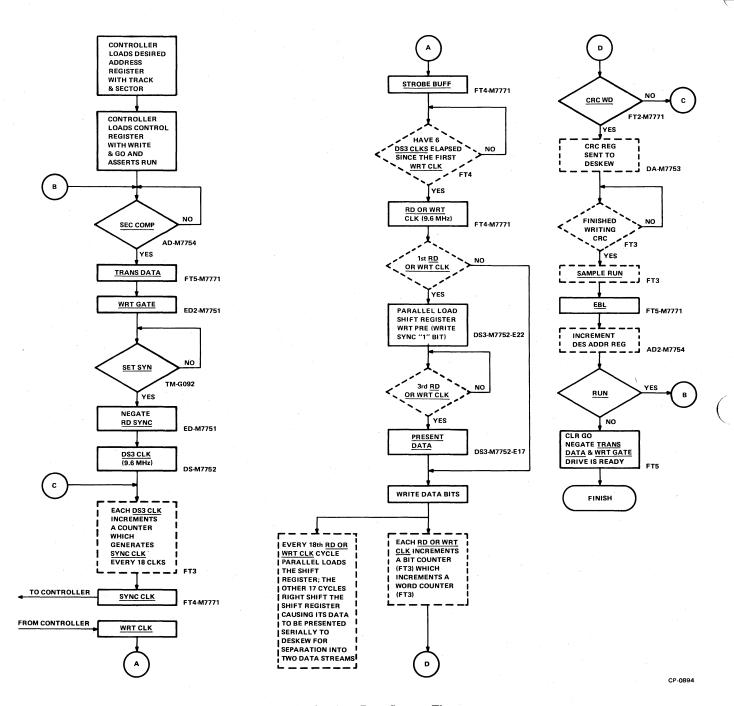

| 2-16       | Write Data System Flow                                     |        |

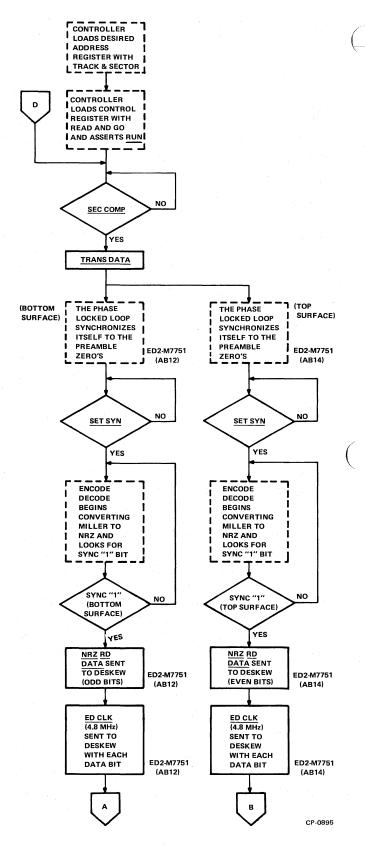

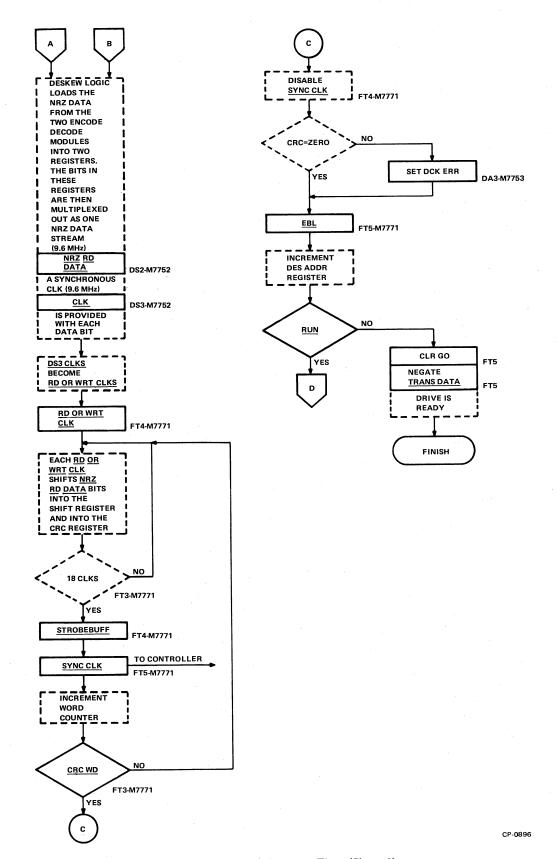

| 2-17       | Read Function Flow                                         | . 2-22 |

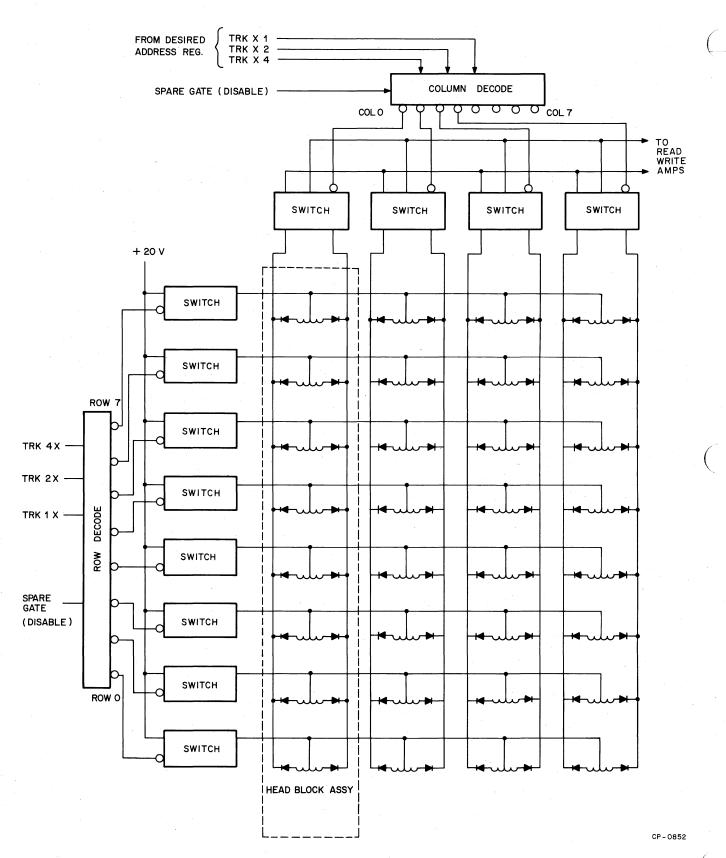

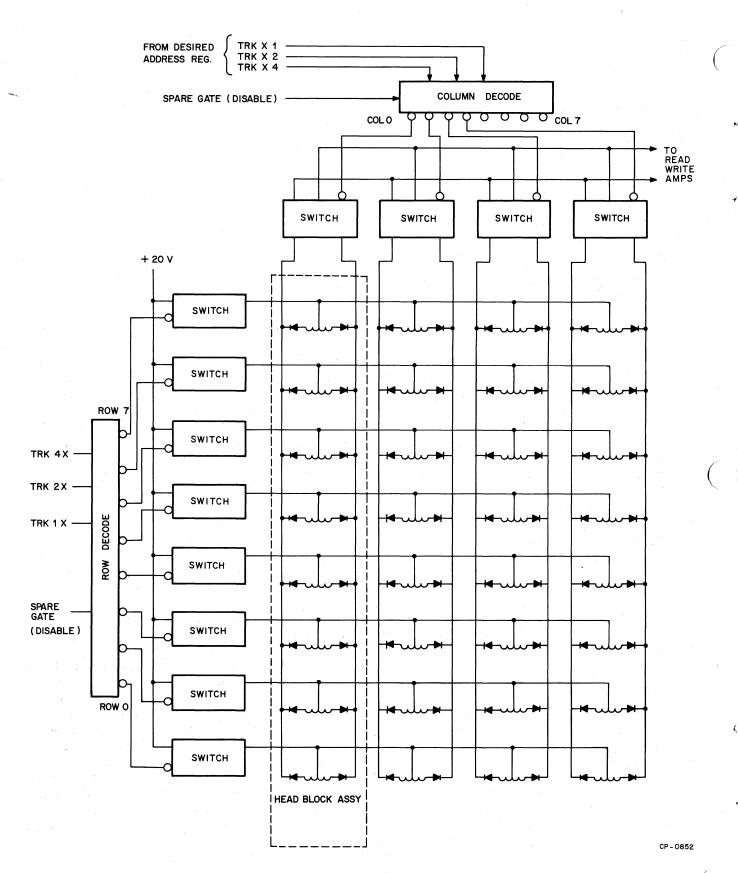

| 2-18       | Head Matrix Module (M7758) Simplified Diagram              | . 2-24 |

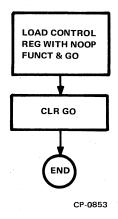

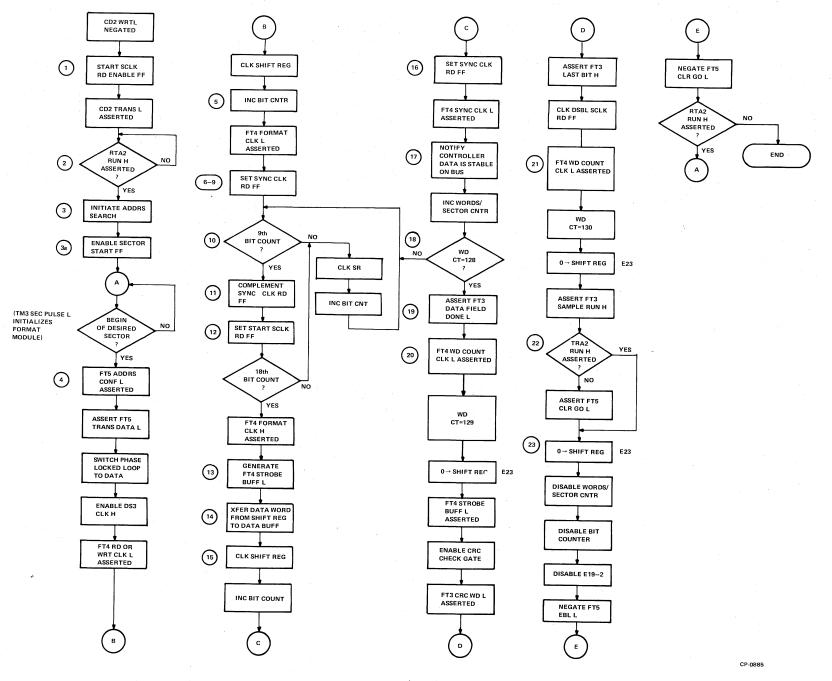

| 2-19       | No-op Flow Chart                                           | . 2-26 |

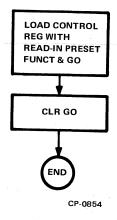

| 2-20       | Read-in Preset Flow Chart                                  | . 2-26 |

|            |                                                            |        |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                               | Page   |

|------------|---------------------------------------------------------------------|--------|

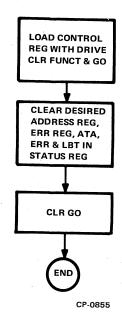

| 2-21       | Drive Clear Flow Chart                                              | . 2-26 |

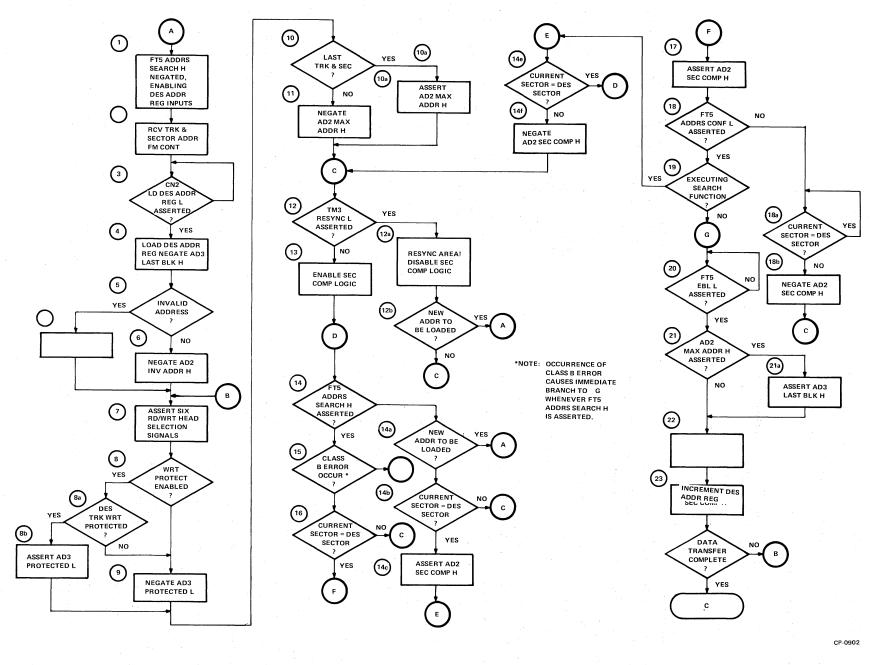

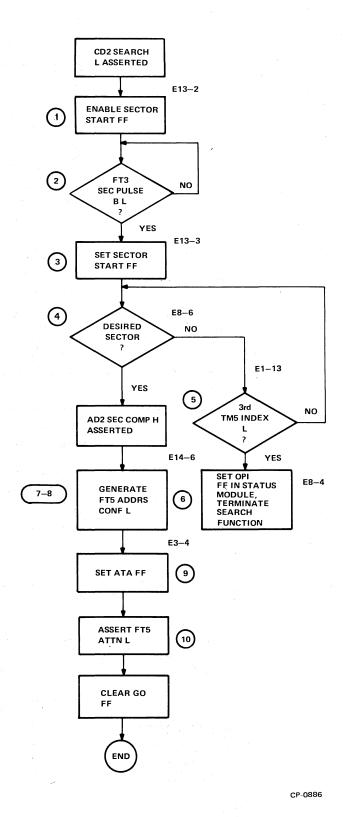

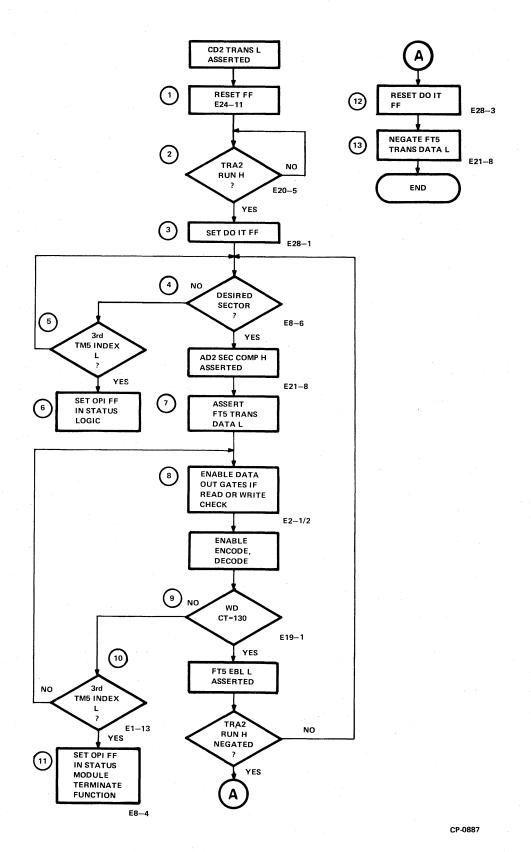

| 2-22       | Search Flow Chart                                                   |        |

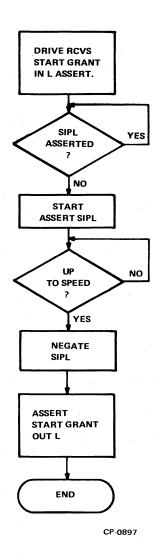

| 2-23       | Flow Chart for RS04 Power Sequencing Bus with Drive (SW1) in REMOTE |        |

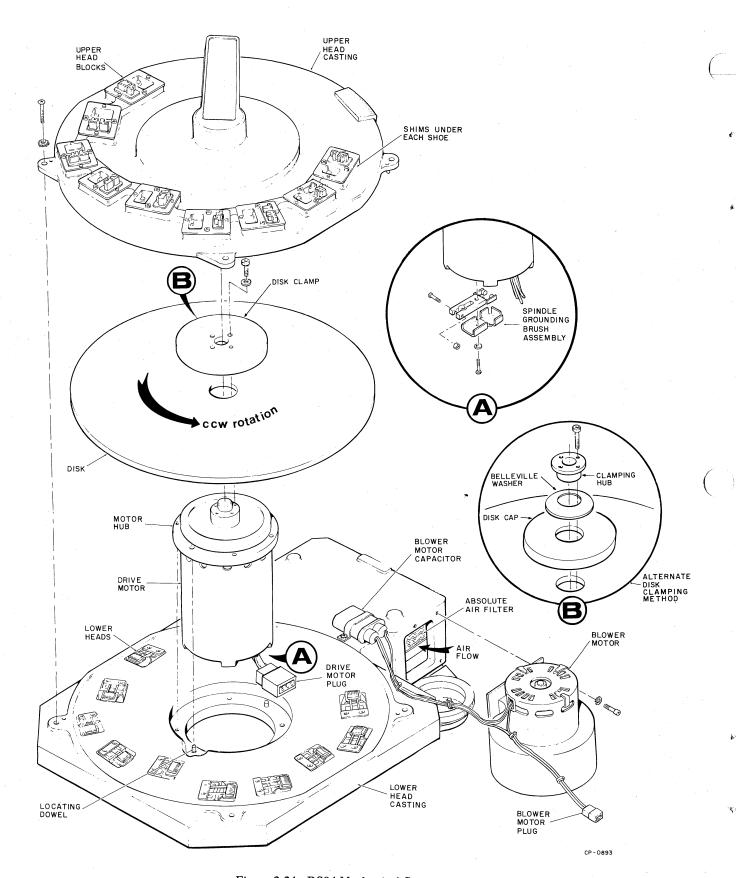

| 2-24       | RS04 Mechanical Components                                          |        |

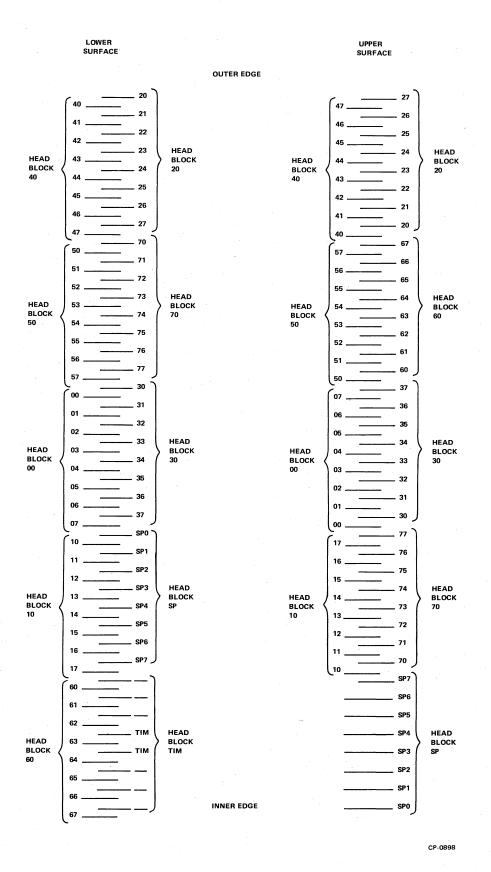

| 2-25       | Physical Track Locations on Disk                                    |        |

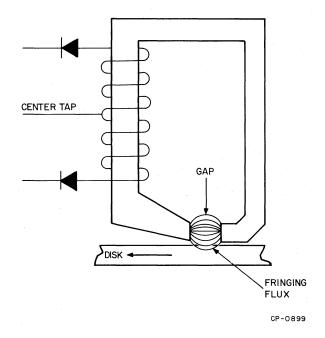

| 2-26       | Ferrite and Coil Assembly                                           |        |

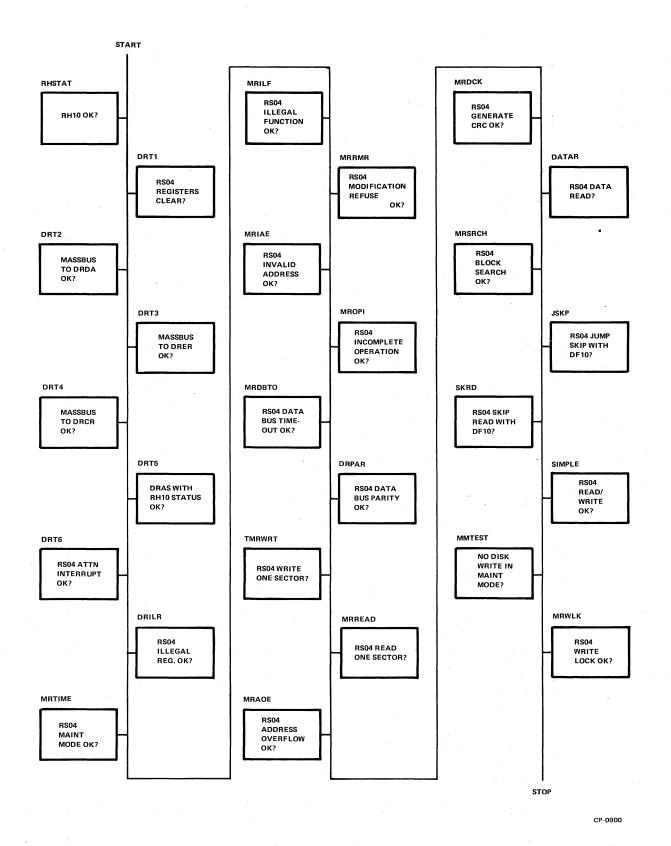

| 3-1        | PDP-10 Diagnostic Tree                                              |        |

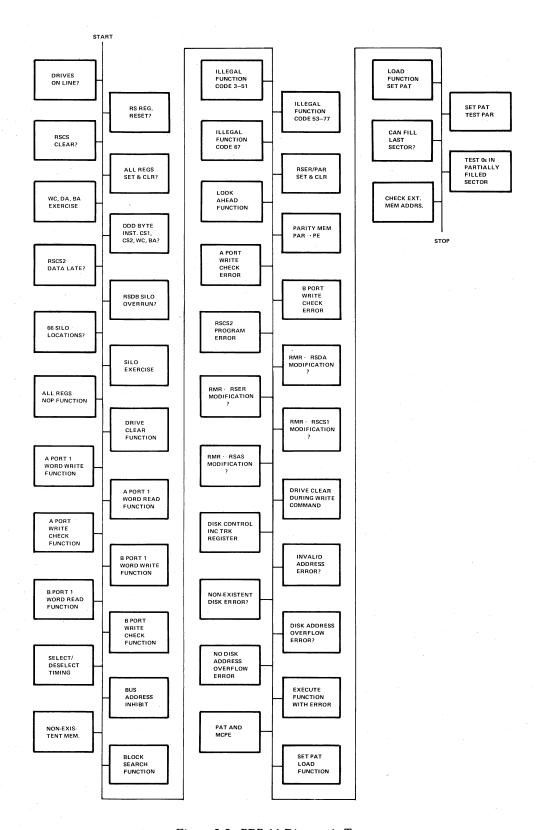

| 3-2        | PDP-11 Diagnostic Tree                                              |        |

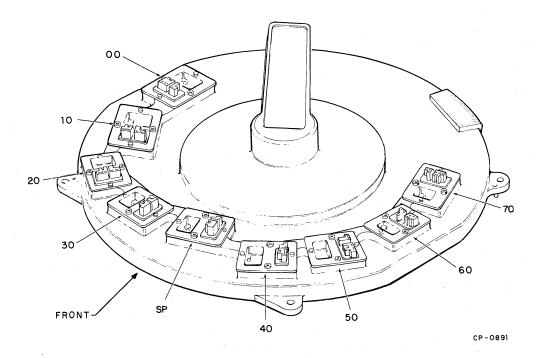

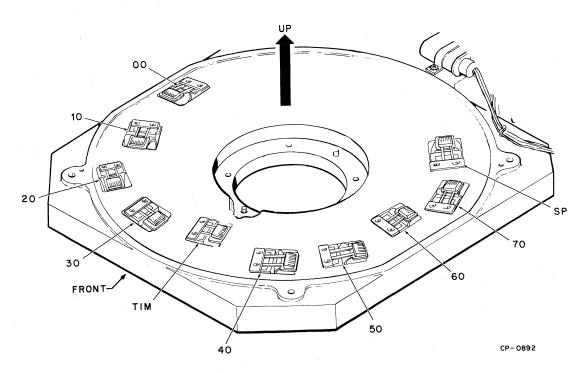

| 3-3        | Top View of Upper Casting Showing Head Locations                    |        |

| 3-4        | Top View of Lower Casting Showing Head Locations                    |        |

| 3-5        | Address Register Troubleshooting Flow Chart                         |        |

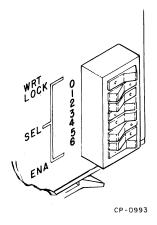

| 3-6        | Write Protect Switches Showing Write Protect Logic Enabled and Set  |        |

|            | to Protect Tracks 00 <sub>8</sub> -31 <sub>8</sub>                  | . 3-36 |

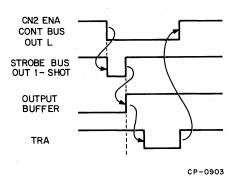

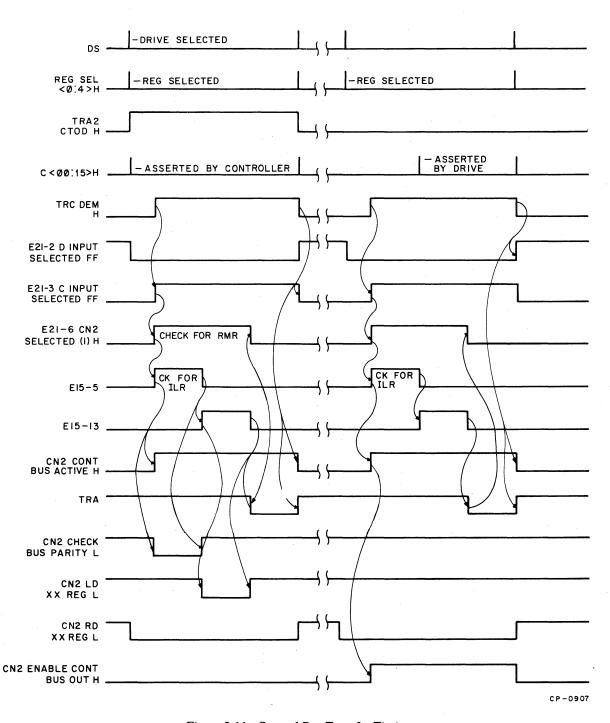

| 3-7        | Control Bus Output Buffer Timing Diagram                            | . 3-36 |

| 3-8        | Command Decode Troubleshooting Flow Chart                           | . 3-38 |

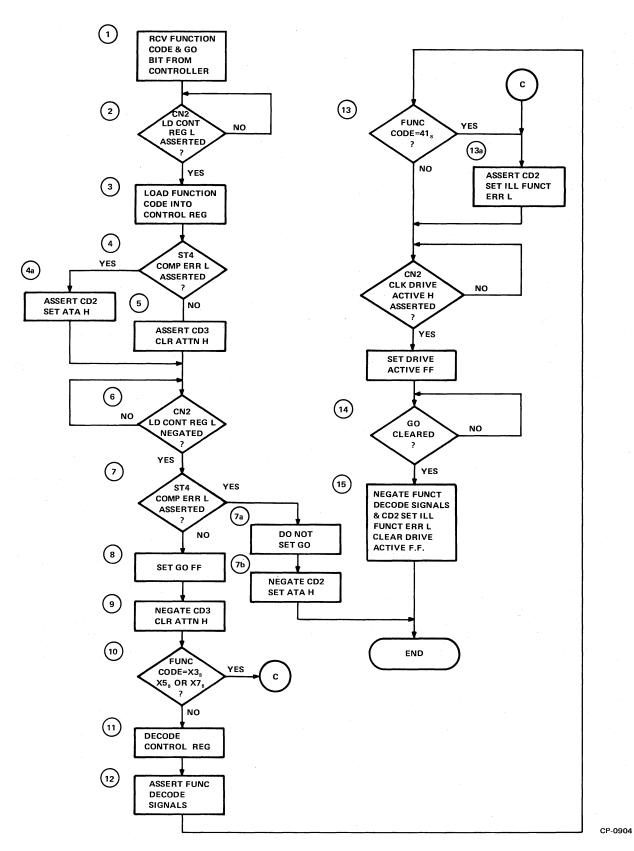

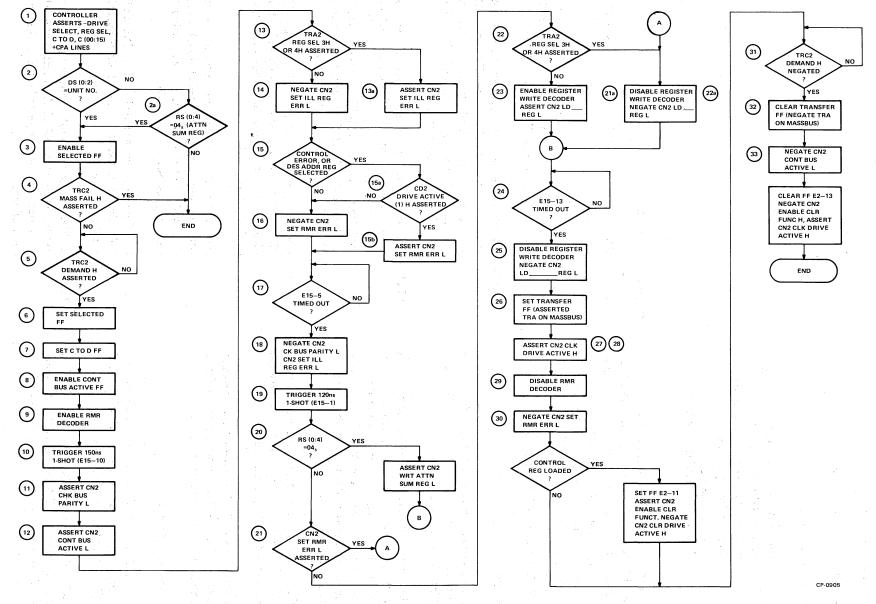

| 3-9        | Control Module Register Write Troubleshooting Flow Chart            |        |

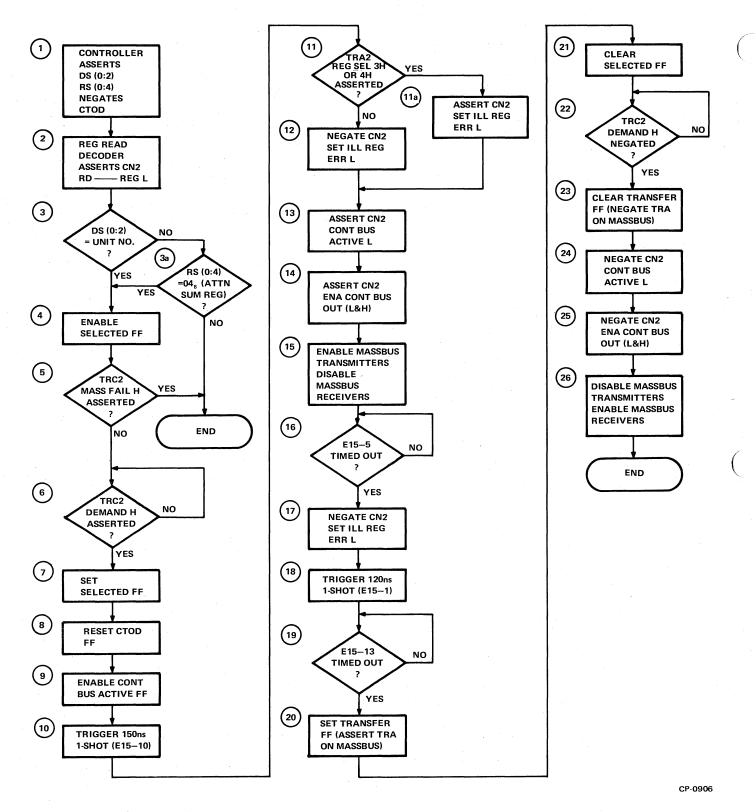

| 3-10       | Control Module Register Read Troubleshooting Flow Chart             |        |

| 3-11       | Control Bus Transfer Timing                                         |        |

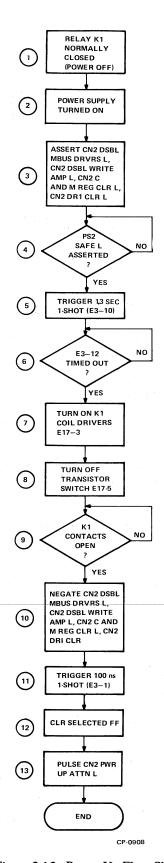

| 3-12       | Power Up Flow Chart                                                 |        |

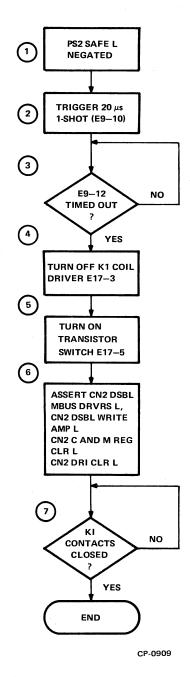

| 3-13       | Power Down Flow Chart                                               |        |

| 3-14       | Unit Number 5 Switch Setting                                        |        |

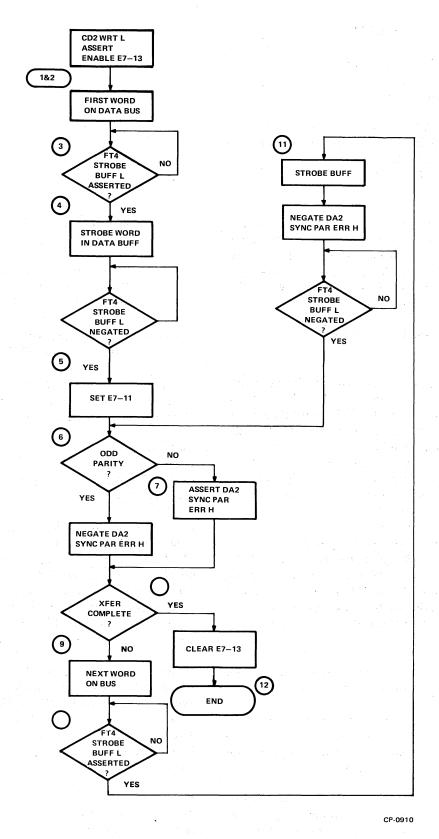

| 3-15       | Parity Check Troubleshooting Flow Chart                             |        |

| 3-16       | CRC Troubleshooting Flow Chart                                      |        |

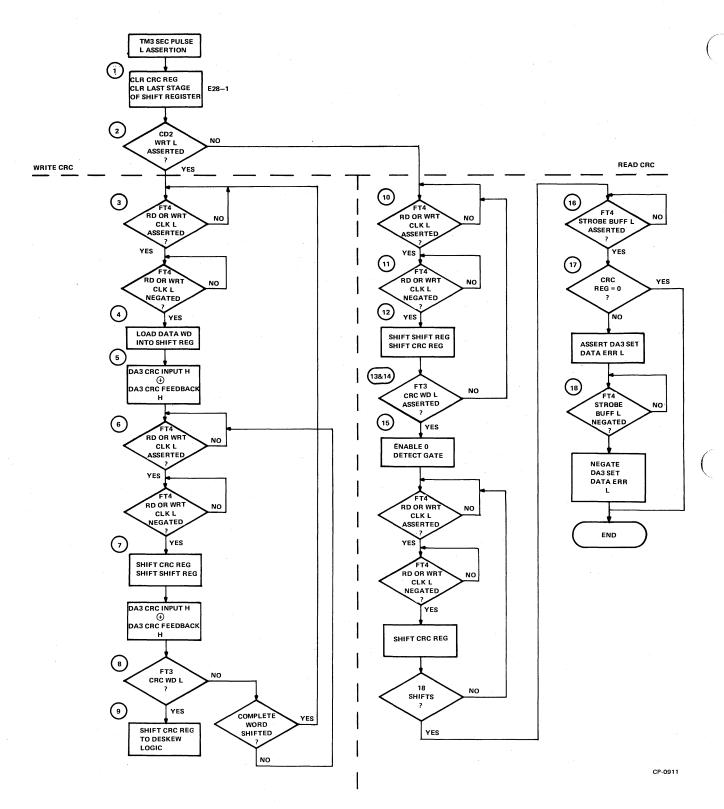

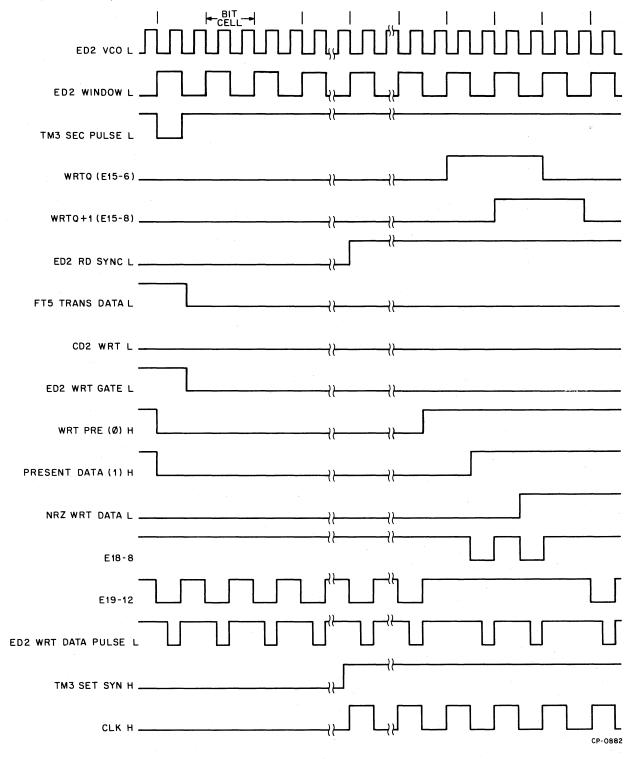

| 3-17       | Write Data Separator Timing                                         |        |

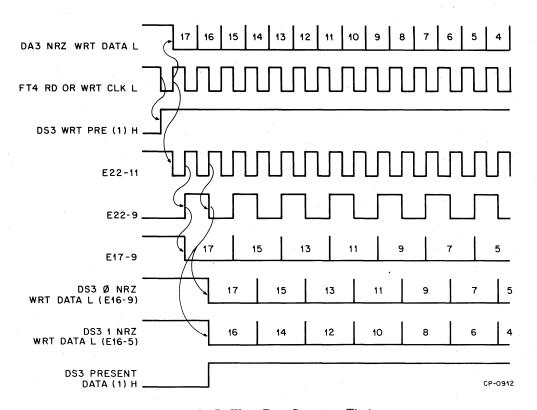

| 3-18       | Read Deskew Logic Timing                                            |        |

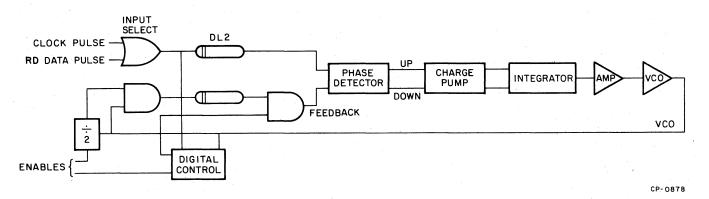

| 3-19       | Phase Locked Loop Block Diagram                                     |        |

| 3-20       | Loop Signals (Ready or Write)                                       |        |

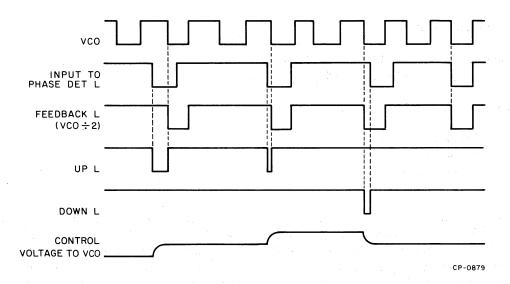

| 3-21       | Loop Lock on Data Timing Diagram                                    |        |

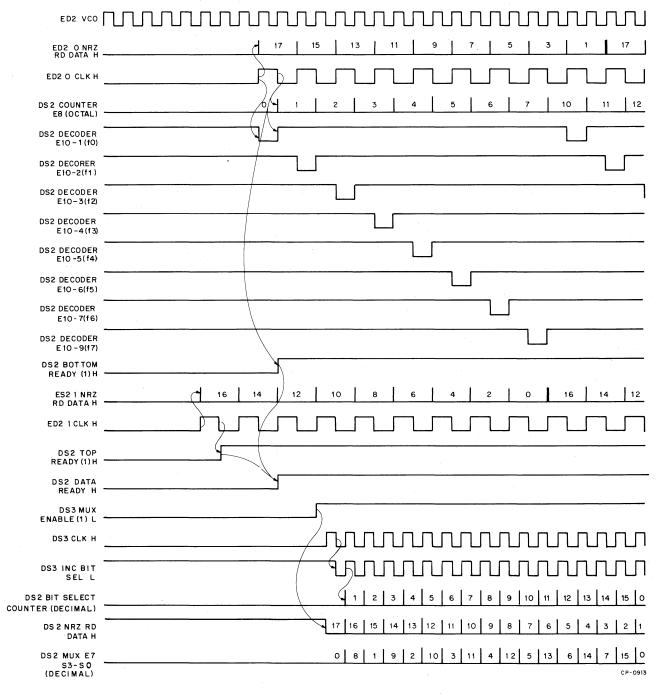

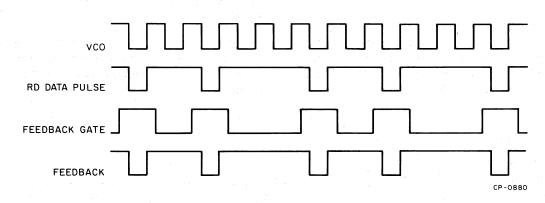

| 3-22       | Encode Logic Flow Chart                                             |        |

| 3-23       | Encode Timing                                                       |        |

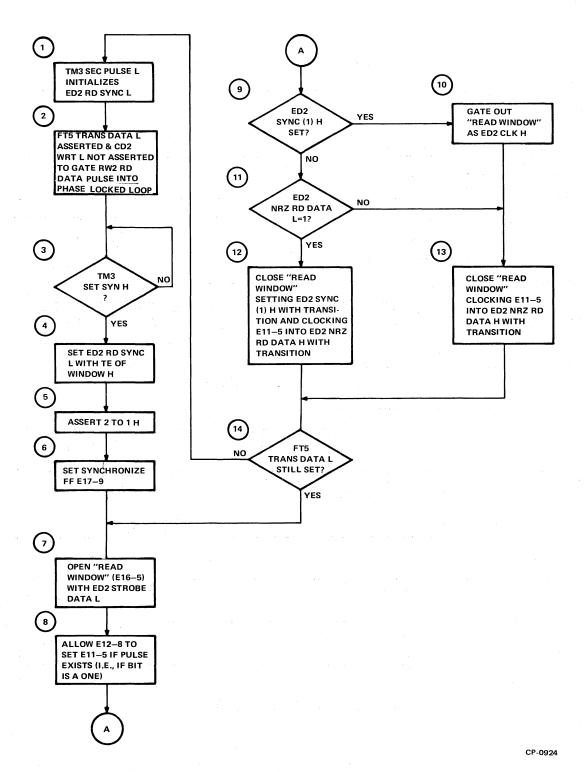

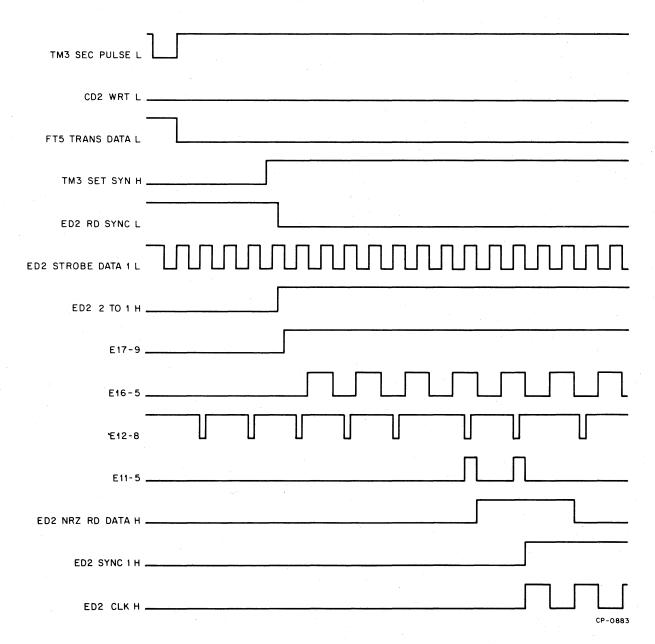

| 3-24       | Decode Logic Flow Chart                                             |        |

| 3-25       | Decode Timing Diagram                                               |        |

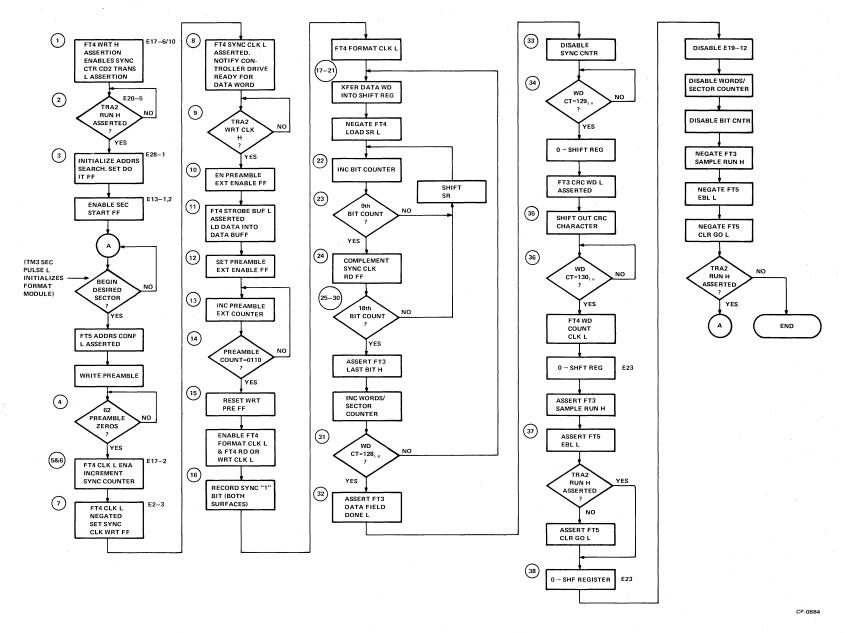

| 3-26       | Format Logic Data Write Troubleshooting Flow Chart                  |        |

| 3-27       | Format Logic Data Read Troubleshooting Flow Chart                   |        |

| 3-28       | Search (Initiation/Termination) Troubleshooting Flow Chart          |        |

| 3-29       | Data Transfer (Initiation/Termination) Troubleshooting Flow Chart   |        |

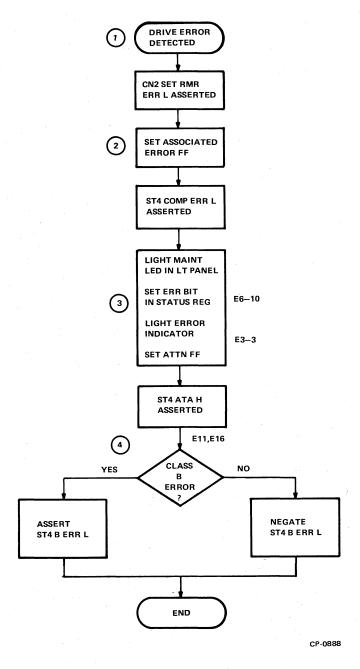

| 3-30       | Error Troubleshooting Flow Chart                                    |        |

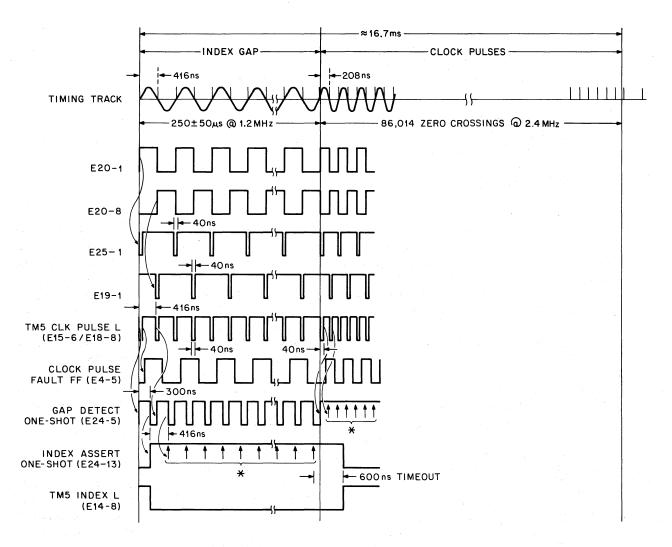

| 3-31       | Index and Clock Pulse Timing                                        |        |

| 3-32       | Clock Pulse Error Timing Example                                    |        |

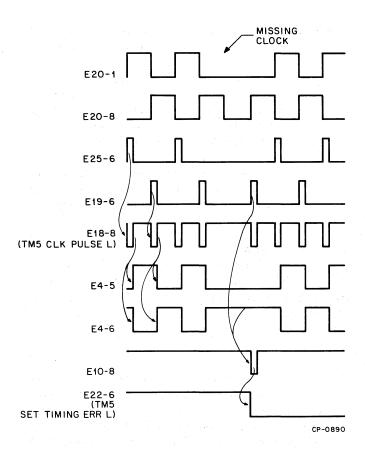

| 3-33       | Resync & Sector Pulse Generation Troubleshooting Flow Chart         |        |

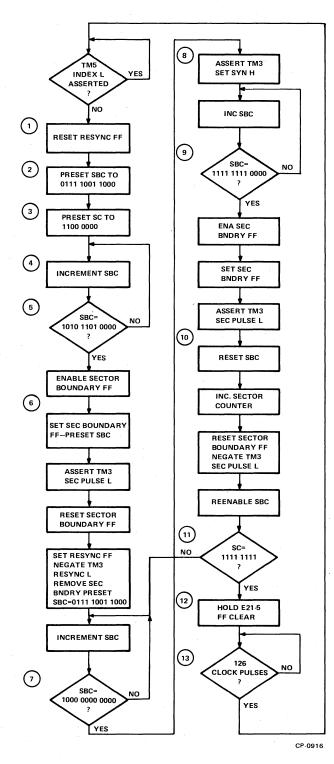

| 3-34       | Resync and Sector Pulse Timing                                      |        |

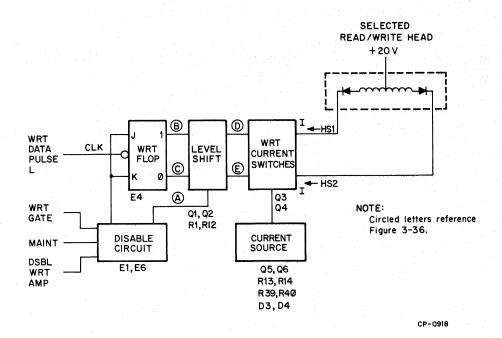

| 3-35       | Write Amplifier (G182) Elements, Simplified Block Diagram           |        |

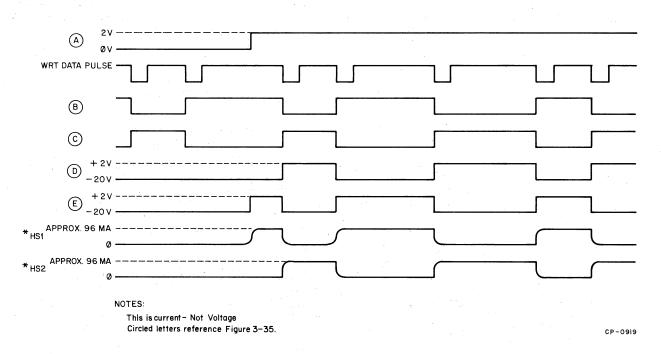

| 3-36       | Write Sequence Timing Diagram                                       |        |

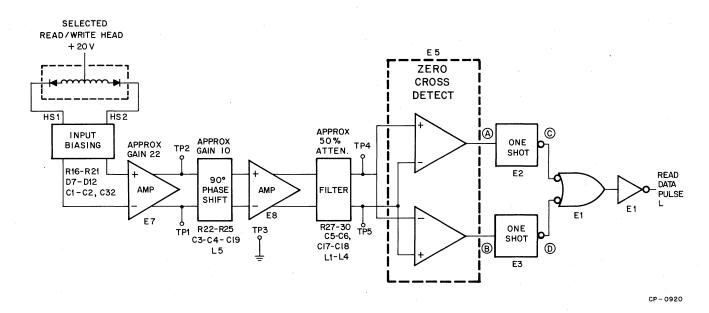

| 3-37       | Read Amplifier (G182) Peak Detection, Simplified Diagram            |        |

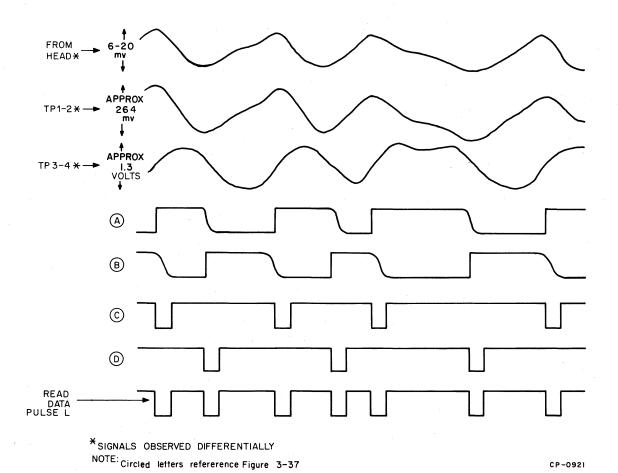

| 3-38       | Read Sequence Timing Diagram                                        |        |

| 3-39       | Head Matrix Module (M7758) Simplified Diagram                       |        |

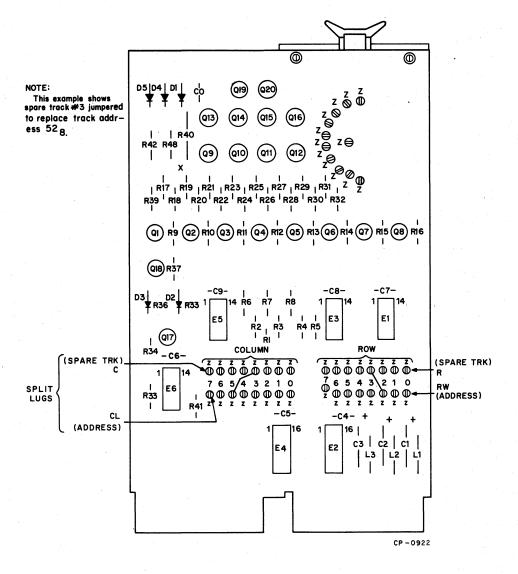

| 3-40       | Alternate Track Wiring Example                                      |        |

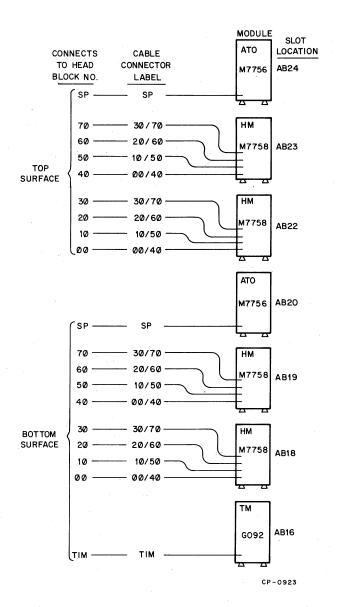

| 3-41       | Module to Connector Relationship                                    |        |

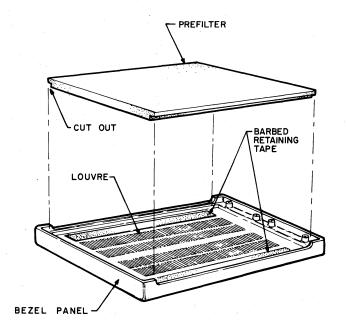

| 4-1        | Pre-Filter Removal and Replacement                                  |        |

## ILLUSTRATIONS (Cont)

| Figure No.   | Title                                                     | Page   |

|--------------|-----------------------------------------------------------|--------|

| 4-2          | Pre-Filter Installation                                   | 4-2    |

| 4-3          | Status Indicator Lamp Access                              |        |

| 4-4          | Chassis Cover Removal                                     |        |

| 4-5          | Power/Control Assembly Removal and Replacement            | 4-5    |

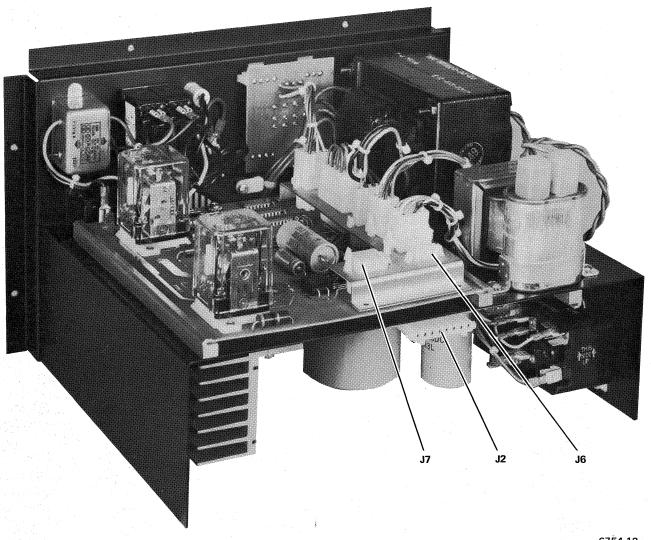

| 4-6          | Power/Control Assembly Connectors                         | 4-6    |

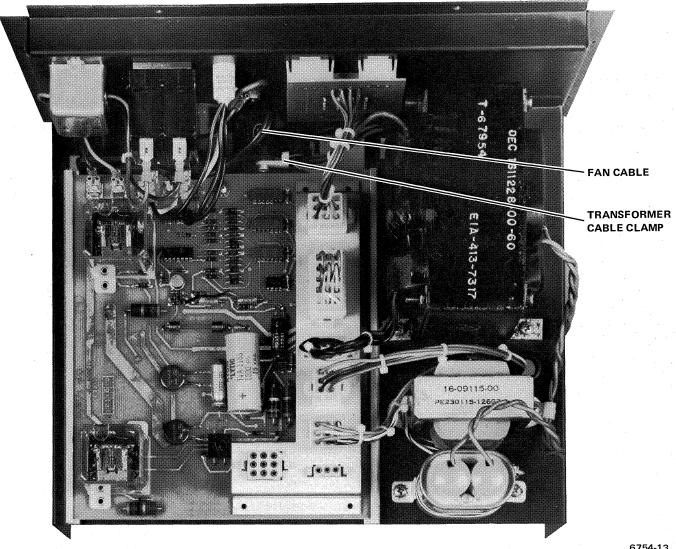

| 4-7          | Fan Cable Removal                                         |        |

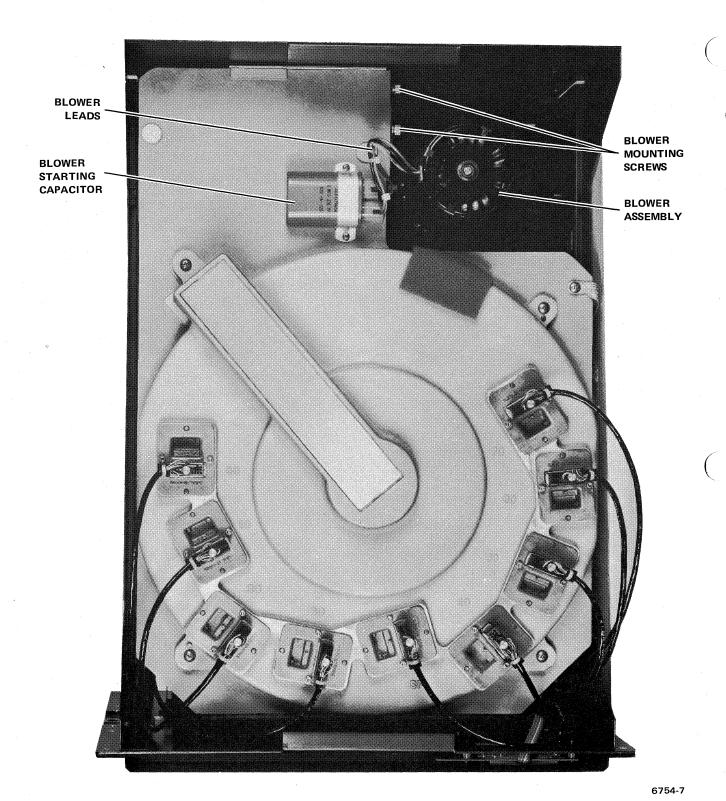

| 4-8          | Blower Motor Removal and Replacement                      |        |

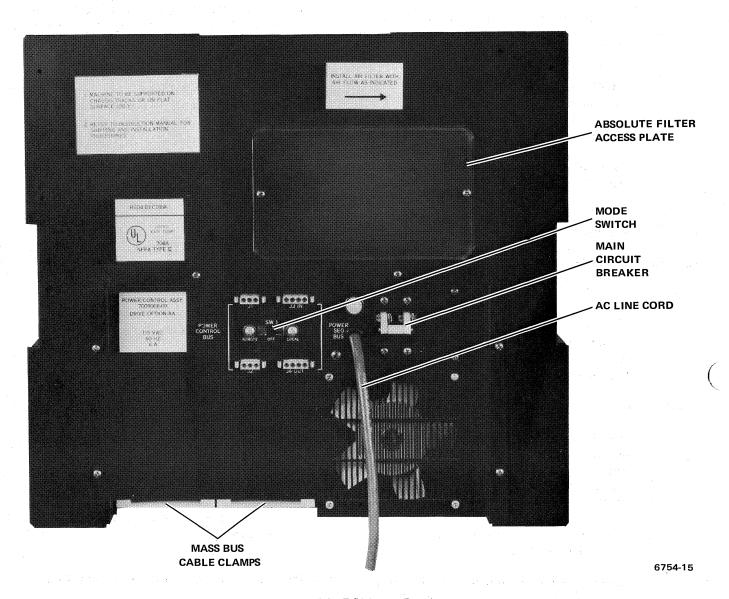

| 4-9          | RS04 Rear Panel                                           | 4-10   |

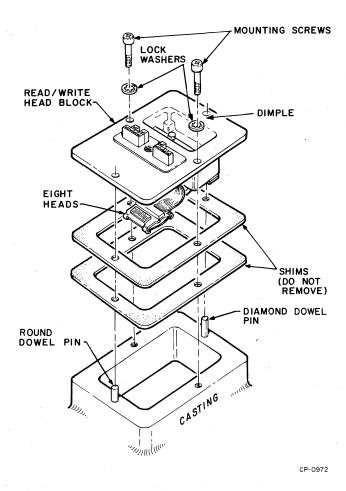

| 4-10         | Upper Head Casting Removal and Replacement                | 4-11   |

| 4-11         | Head Block Removal                                        | 4-12   |

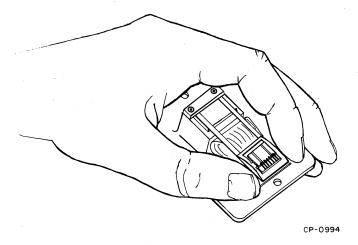

| 4-12         | Proper Head Holding During Cleaning                       | 4-12   |

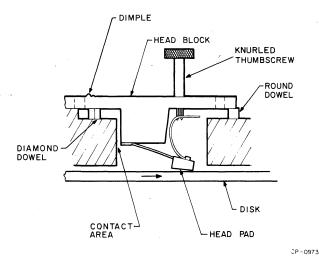

| 4-13         | Head Block Insertion                                      | 4-13   |

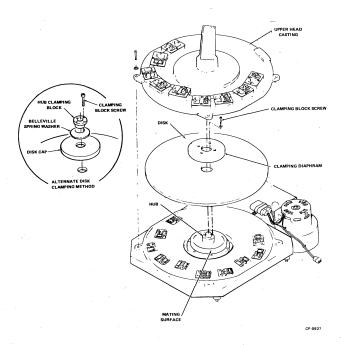

| 4-14         | Upper Casting and Recording Disk Removal and Replacement  | 4-14   |

| 4-15         | Disk Drive Motor Bottom View                              |        |

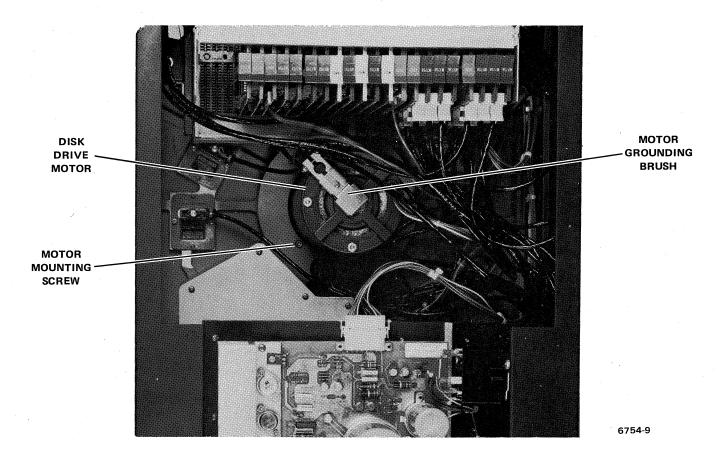

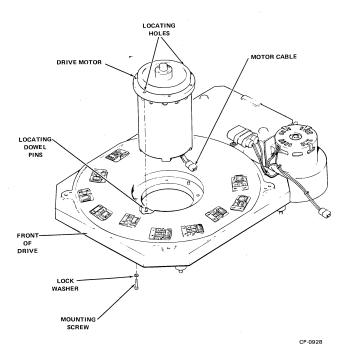

| 4-16         | Disk Drive Motor Removal and Replacement                  | 4-17   |

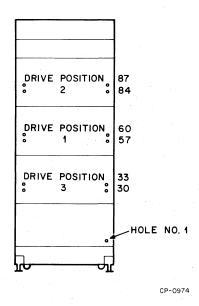

| 5-1          | Chassis Slide Mounting Hole Locations                     |        |

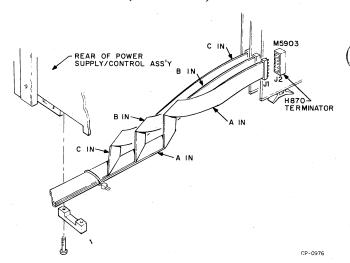

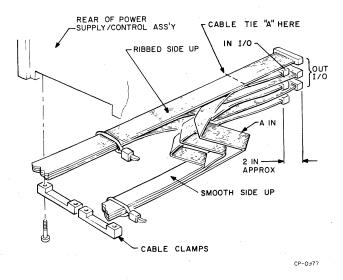

| 5-2          | MASSBUS Cable Installation (Middle of Bus)                |        |

| 5-3          | MASSBUS Cable Installation (Last or Only Drive)           | 5-2    |

| 5-4          | Cable Routing for Drives Located in the Middle of MASSBUS | 5-3    |

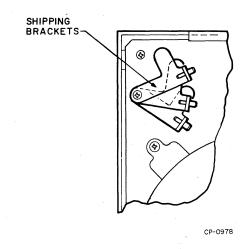

| 5-5          | Shipping Bracket Storage Location                         | 5-3    |

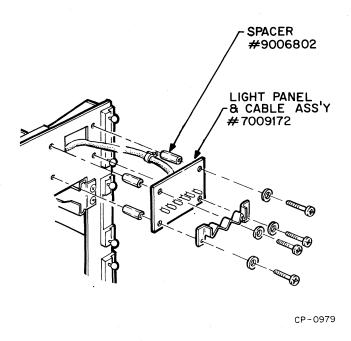

| 5-6          | Light Panel Assembly Procedure                            |        |

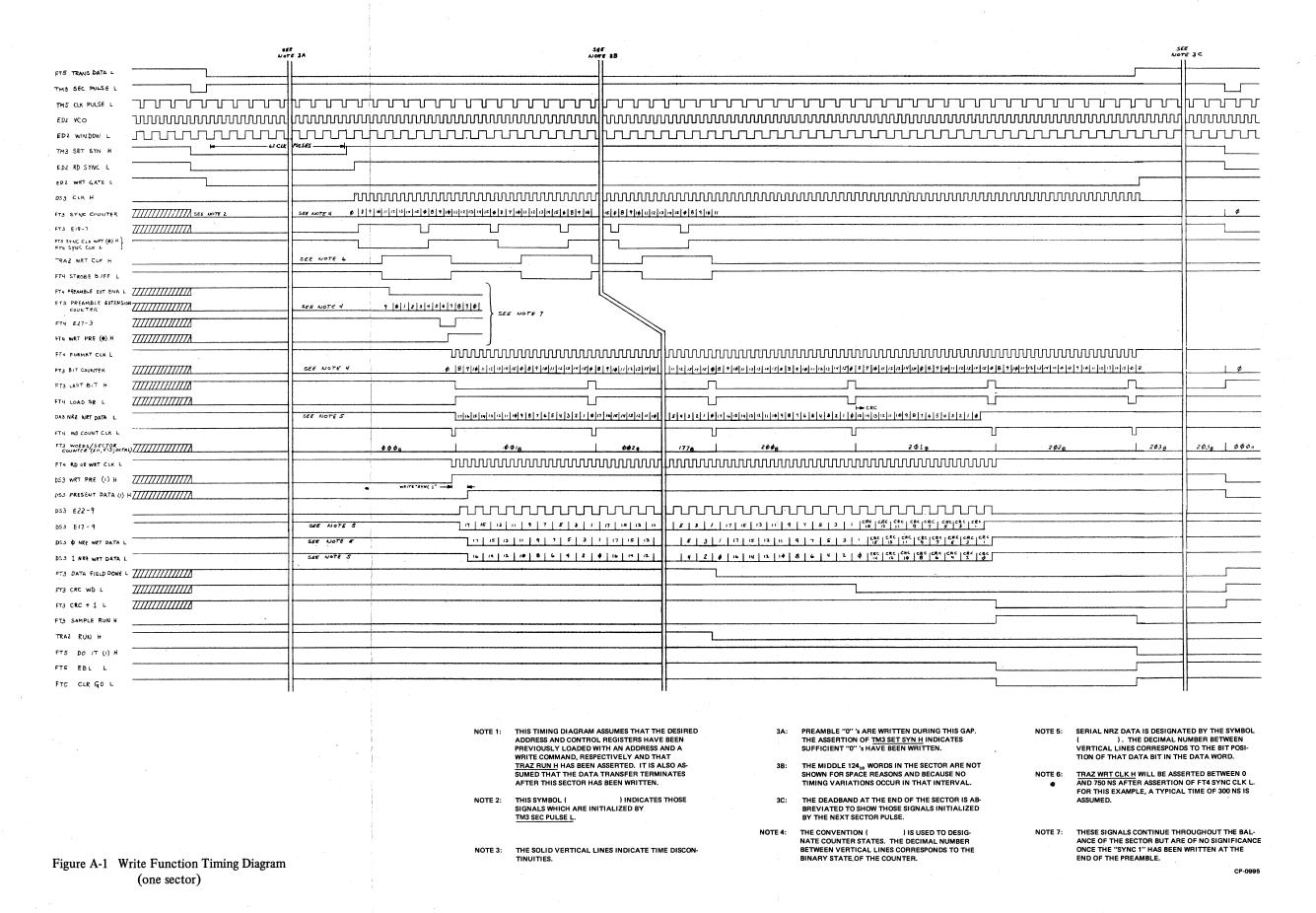

| A-1          | Write Function Timing Diagram (one sector)                |        |

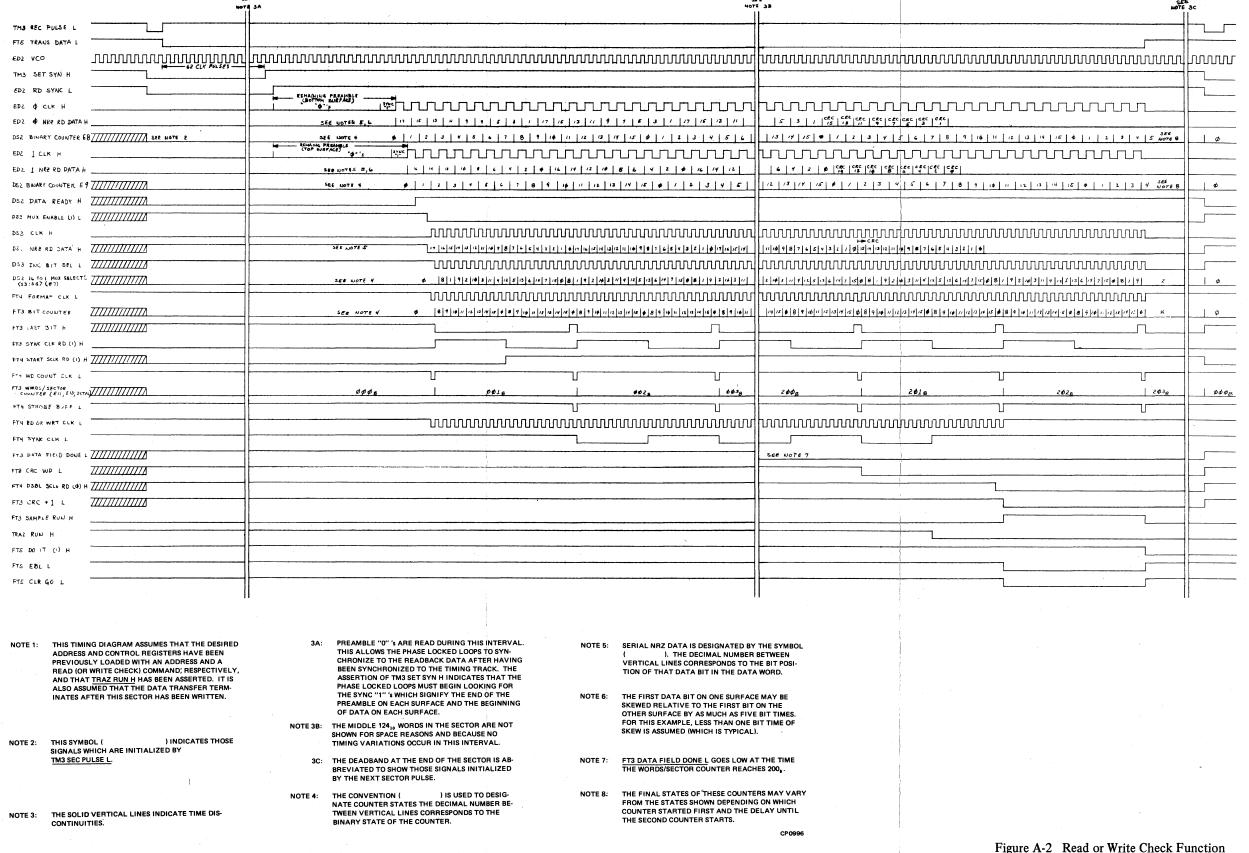

| A-2          | Read or Write Check Function Timing Diagram (one sector)  | A-2    |

| E-1          | Cross Section of Multilayer Board                         | A-3    |

| E-2          | Component Connections to Inner Layers                     | E-1    |

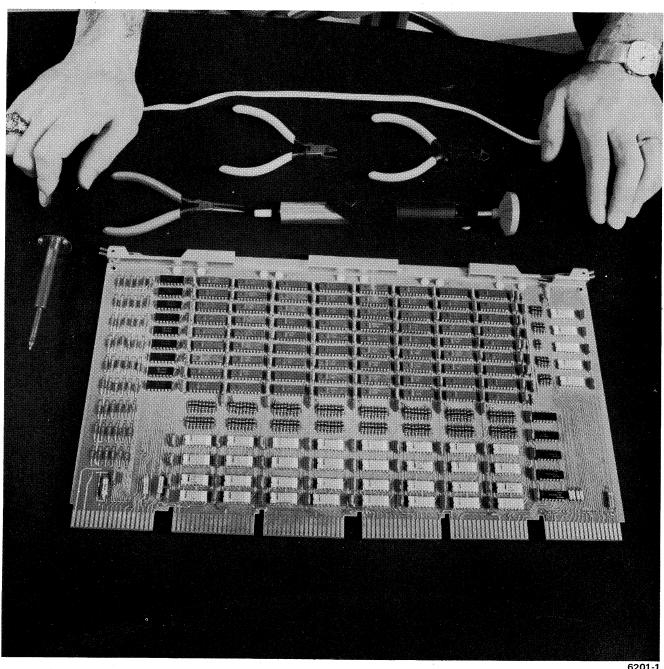

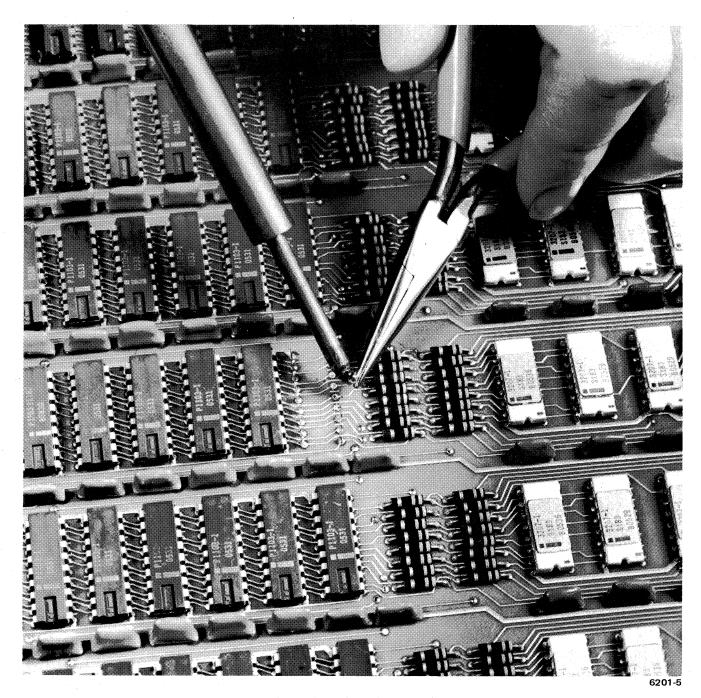

| E-3          | Module To Be Repaired and Tools Required                  | E-2    |

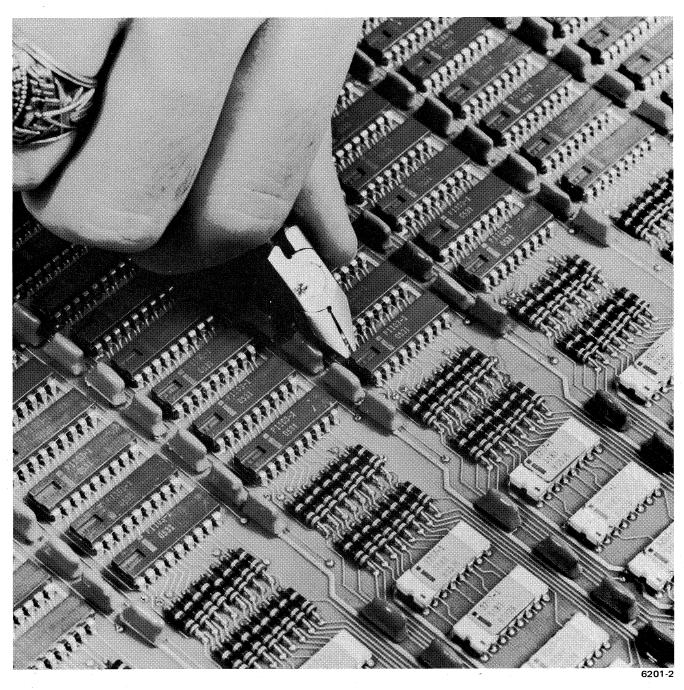

| E-4          | Clipping Leads of a Defective IC                          | E-4    |

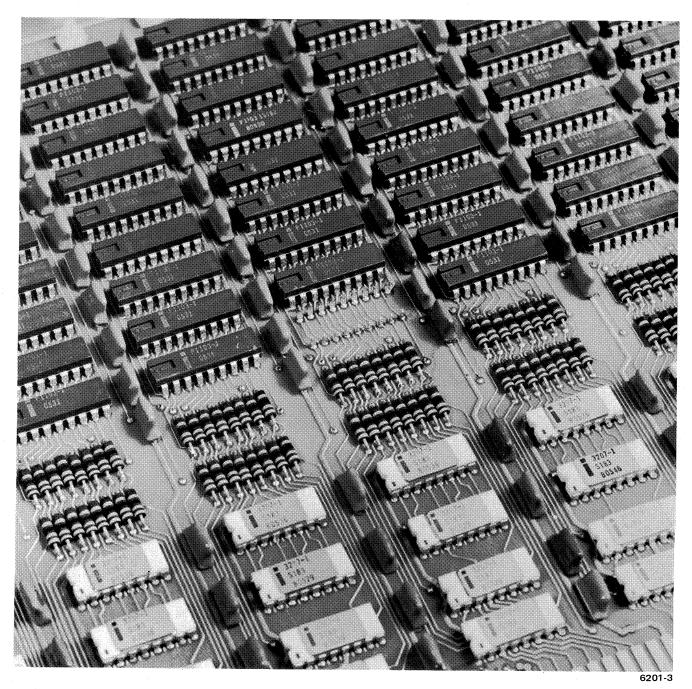

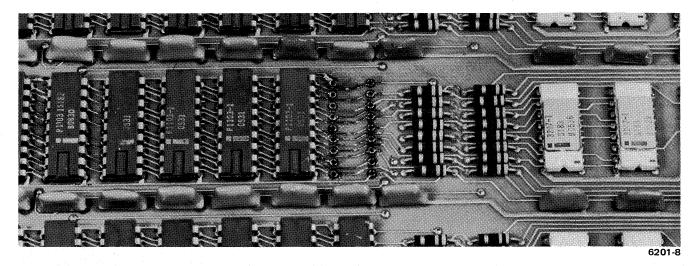

| E-5          | Defective IC Removed                                      | E-3    |

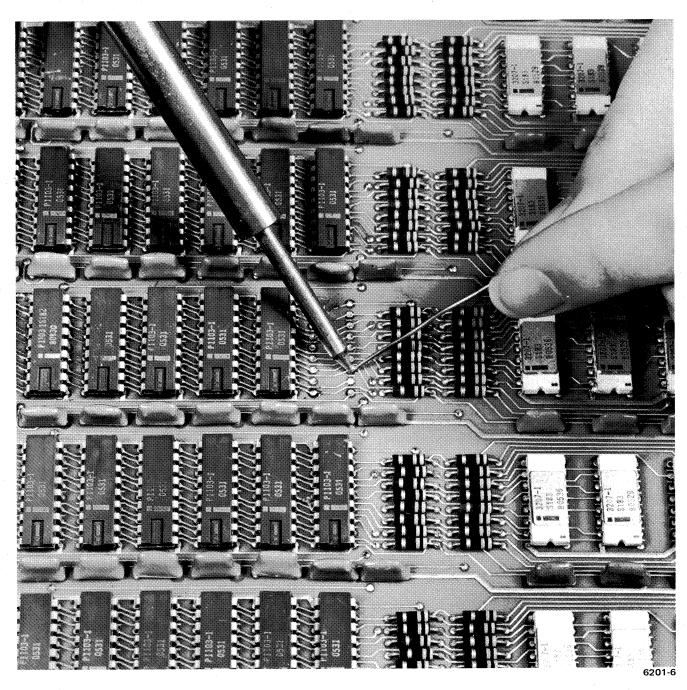

| E-6          | Removing IC Leads                                         | E-6    |

| E-7          | IC Lead Demoved                                           | E-7    |

| E-8          | IC Lead Removed                                           |        |

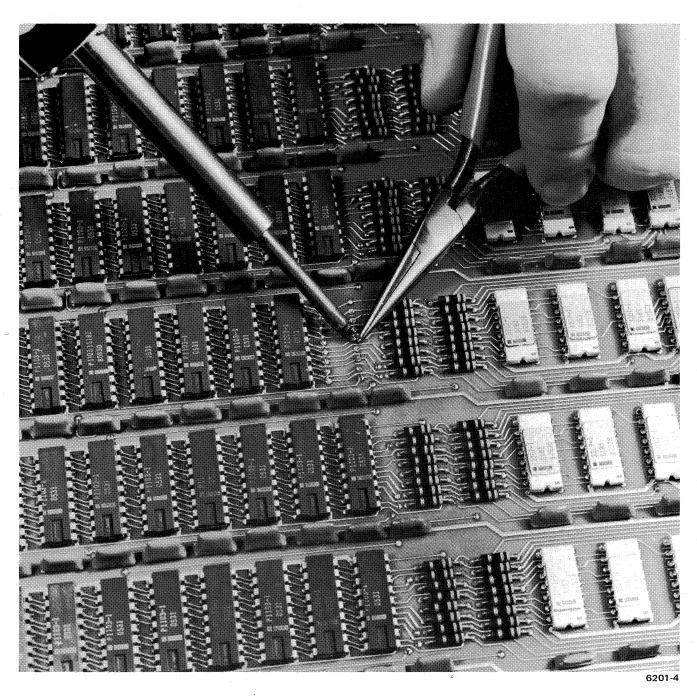

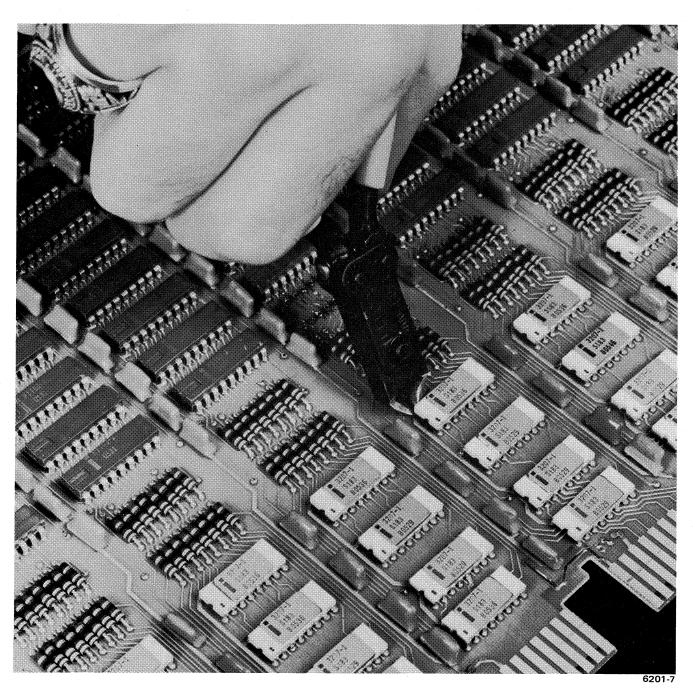

| E-9          | Applying Solder To Refill Eyelet                          |        |

| E-10         | Removing Excess Solder From Eyelet                        | . E-10 |

| E-10<br>E-11 | IC Location Ready for Insertion of New IC                 | . E-11 |

| E-11         | Special Tool and Method Used To Clip Ceramic IC Leads     | . E-12 |

|              |                                                           |        |

| V            | TABLES                                                    |        |

|              | TABLES                                                    |        |

| Table No.    | Title                                                     | Page   |

| 14010 1101   | THE                                                       | rage   |

| 1-1          | RS04 Performance Specifications                           | 1-4    |

| 1-2          | Power Controls and Indicators                             |        |

| 1-3          | Front Panel File Status Indicators                        |        |

| 1-4          | Error Indicators                                          |        |

| 2-1          | Drive Registers                                           |        |

| 2-2          | Command Function Codes                                    |        |

| 2-3          | Status Register Bit Assignments                           |        |

| 2-4          | Error Register Bit Assignments                            |        |

| 2-5          | Maintenance Register Rit Assignments                      | 2-14   |

| 2 3          | Maintenance Register Bit Assignments                      | 2-15   |

# TABLES (Cont)

| Table No. | Title                                                                        | Page |

|-----------|------------------------------------------------------------------------------|------|

| 2-6       | Drive Type Register Bit Assignments                                          | 2-17 |

| 3-1       | DECsystem-10 Static Diagnostic Tests Troubleshooting Chart                   | 3-3  |

| 3-2       | PDP-11 Static Diagnostic Tests Troubleshooting Chart                         | 3-11 |

| 3-3       | Sector Count/Sector Address in Interleaved and                               |      |

|           | Non-Interleaved Systems                                                      | 3-81 |

| 3-4       | Power Supply Checkpoints                                                     | 3-96 |

| B-1       | RS04 Signal Glossary                                                         |      |

| C-1       | M5904 Signal Table                                                           | C-2  |

| E-1       | Repair Tools Required                                                        | E-2  |

| G-1       | Recommended Filter Maintenance                                               |      |

| H-1       | RS04 Preventive Maintenance Schedule                                         | H-2  |

| H-2       | RS04 Preventive Maintenance Recommended Test Equipment and Replacement Parts | H-3  |

## **PREFACE**

#### SCOPE AND PURPOSE OF THIS MANUAL

This Service Manual has been devised to meet the needs of both Field Service and user personnel in servicing the RS04 DECdisk.

The bulk of the information may be found in Sections III and IV. Detailed theory, performance, and troubleshooting data is presented in modular elements, each devoted to a particular subassembly of the device, to minimize constant cross-checking through the document during troubleshooting. The modular elements are further separated into two categories: electrical and mechanical.

Section I of this Service Manual is devoted to introductory data. It includes an overall description of the equipment and defines the purpose of the equipment in a system. Both a physical and a functional description of the equipment is given with a brief list of technical characteristics.

Section II discusses the *Theory of Operation* of the RS04. It provides an overall functional description of the equipment, and its interface within a typical system. Only block diagrams are given here to describe series of events; timing diagrams are included whenever they are necessary to further delineate a concept.

Section III contains *Electrical Servicing* information. This section is headed by a diagnostic discussion for operation with both the DECsystem-10 and the PDP-11 computer systems. A table is included that describes each diagnostic test, its purpose, the probable malfunction indicated, and the probable mechanical and/or electrical area of the machine containing the fault. When an error is encountered in the testing of the RSO4, this table should be used first to locate the particular area of trouble, directing the serviceman to a particular subsection for more detailed information concerning the operation and troubleshooting procedures for the module at fault. Each subsequent subsection includes a brief reminder of the location of the module in the overall system, followed by a detailed theory discussion of the operation of that module. This is then

followed in each subsection by performance checks and troubleshooting information that applies to the individual module described.

Section IV contains Servicing Information for the mechanical portions of the RS04. This section describes, by subassemblies, the removal, replacement, inspection, and alignment of these subassemblies and cleaning procedures for critical items.

Section V is devoted to *Installation* of the RS04, with procedures for initially setting up the device in a system.

#### ORGANIZATION OF THE PRINT SET

The following conventions have been used on all RSO4 logic module prints. Each module has a two or three alphabetic character code name as listed in the Prefatory Table.

Each sheet of the module circuit schematic has a code name, composed of the module code name followed by the sheet number of the drawing. For example, the G092 module (Timing Amp Logic) contains five circuit schematic drawings, labelled TM1, TM2, TM3, TM4, and TM5.

All signal names contain a prefix which is the drawing sheet code name for the sheet which shows the source of the signal. Example: TM3 SEC PULSE L is sourced on sheet 3 of the Timing Amp Logic module print.

On all modules, each signal pin (finger connection) has its pin number written *each time* its signal name appears on any sheet. Each time the pin number appears, it is placed in parentheses and has a solid arrow (into) on the sheet if it is connected *only* to inputs (destination). If it is connected to *any* logical output or source, it is not in parentheses and has a solid arrow (out of) on the sheet.

Multiple source signals (wired ORs) have many sources with different source sheet names and are documented as being connected on the wire list. They are also denoted as wire ORed signals by a "WO" in the signal name.

Prefatory Table RS04 Signal/Drawing Number Prefixes

| Prefix | Module Name            | Module Designation | Logic Slot    |

|--------|------------------------|--------------------|---------------|

| TRA    | MASSBUS TRansceiver A  | M5903              | AB01          |

| TRB    | MASSBUS TRansceiver B  | M5903              | AB02          |

| TRC    | MASSBUS TRansceiver C  | M5903              | AB03          |

| CN     | CoNtrol                | M7755              | AB04          |

| ST     | STatus                 | M7770              | AB05          |

| CD     | Command Decode         | M7759              | AB06          |

| AD     | ADdress Register       | M7754              | AB07          |

| FT     | FormaT                 | M7771              | AB08          |

| DA     | DAta Register          | M7753              | AB09          |

| DS     | DeSkew                 | M7752              | AB10          |

| ED     | Encode/Decode          | M7751              | AB12,14       |

| TM     | TiMing Amp Logic       | G092               | AB16          |

| RW     | Read/Write & Det.      | G182               | AB17,21       |

| ATO    | Alternate Track Option | M7756              | AB20,24       |

| НМ     | Head Matrix            | M7758              | AB18,19,22,23 |

It is hoped that this new Service Manual format will more fully meet the needs of our customers and it is anticipated that it will more easily meet the needs of Training. Comments and suggestions from the field will be welcomed. A postage-paid form has been included at the back of the manual. Please use this tear-out page when communicating with the DEC Technical Documentation Department.

#### REFERENCE DOCUMENTS

In the preparation of this Service Manual, the following

documents have been referred to in whole, or in part, as a guide to its preparation:

| RS04 DECdisk Illustrated Parts     | DEC-RS04-IPB     |

|------------------------------------|------------------|

| Breakdown                          |                  |

| RJS04/RJS03 Fixed-Head Disk        | DEC-11-HRJSA-A-D |

| System Maintenance Manual          |                  |

| RH10/RS03-04 Disk Controller       | DEC-10-HRHMA-A-D |

| Maintenance Manual                 |                  |

| Digital Logic Handbook             | 058.00173.2505   |

| PDP-11 Peripherals and Interfacing | 112.01071.1854   |

| Handbook                           |                  |

RS04 DECdisk SERVICE MANUAL

RS04 DECdisk

# SECTION 1 INTRODUCTION

#### 1.1 GENERAL

This section contains the information necessary to familiarize the reader with the overall characteristics and purpose of the RS04 DECdisk. It contains a description of a typical system in which the RS04 is used. In addition, it delineates the various subassemblies of the equipment and describes them from a functional standpoint. The controls and indicators are shown with a tabular listing of their purposes and a table of drive specifications is included.

#### 1.1.1 Characteristics

The RS04 DEC disk (frontispiece) is a MASSBUS fixed-head disk subsystem that functions as a random-access mass storage device, possessing characteristics that are particularly applicable to swapping operations. The unit is designed to interface with any MASSBUS Controller. Maximum storage capacity is 524,288 18-bit words. The average transfer rate is  $2 \mu s$  per word. The device is completely self-contained, requires 15-3/4 in. of panel space in a standard 19 in. rack, and slides forward for servicing.

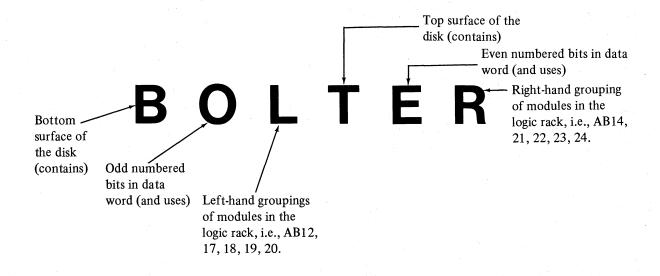

Data is stored in the RS04, on both surfaces of a single, nickel-cobalt plated disk that is driven by a unitized ac induction motor/spindle. Two data tracks, one on each surface, are always selected simultaneously. The written data stream is separated within the drive, enabling two bits to be written simultaneously, one on each surface. In this manner, every other bit in a data word is written on one surface and the remaining bits are written on the other surface. When read back, the separated data stream is recombined in proper sequence for presentation to the Controller. This parallel-track read/write scheme effectively increases data throughput since only nine data bit time intervals are required to record an 18-bit data word.

Internal drive timing and addressing information is derived from a single prerecorded timing track. This includes index (once per revolution) and sector marks, as well as individual bit cell boundaries (when writing). Recording on the disk is by the Three Frequency or Modified Frequency Modulation method, commonly referred to as the *Miller Encoded Recording Technique*. When writing, the data is synchronized to the timing track; when reading back however, the data is self-clocking and therefore need not be synchronized to the timing track.

Spare data tracks, which are jumper-selectable, are provided to replace any tracks which may fail over the life of the drive. In addition, one spare pre-recorded timing track is provided.

Write Protect logic is included in the RS04. When enabled, complete tracks starting with track 00 up to and including any switch-selectable track, are write protected (i.e., read-only).

#### 1.1.2 Typical System Configuration

Figure 1-1 illustrates a typical RS04 multi-drive system configuration. Drive selection logic, located within each RS04, allows each MASSBUS Controller to service up to eight fixed-head disk files. For information concerning the Controller itself, refer to the particular Controller maintenance manual.

#### 1.1.3 RS04 Recording Technique

The RS04 utilizes the Miller Encoded Recording Technique to magnetically record data on the disk surfaces. In the Miller encoding method, each logical one produces a flux reversal in the center of its bit cell. Two successive logical zeros produce a flux reversal at the bit cell boundary between them. There is no flux reversal in a bit cell containing a logical zero following a logical one. This method of recording has the advantage of putting at least one flux reversal on the disk for every two bit cells, thereby making it feasible to use phase-locked loop techniques to form a self-clocking data recovery system. This method has a maximum flux reversal density of one reversal per bit cell.

Figure 1-1 RS04 Typical System Configuration

In this method, clock pulses from the prerecorded timing track are used to establish the bit cell time interval during writing. When reading, the phase-locked loops are synchronized to the data stream and are used as data recovery clocks.

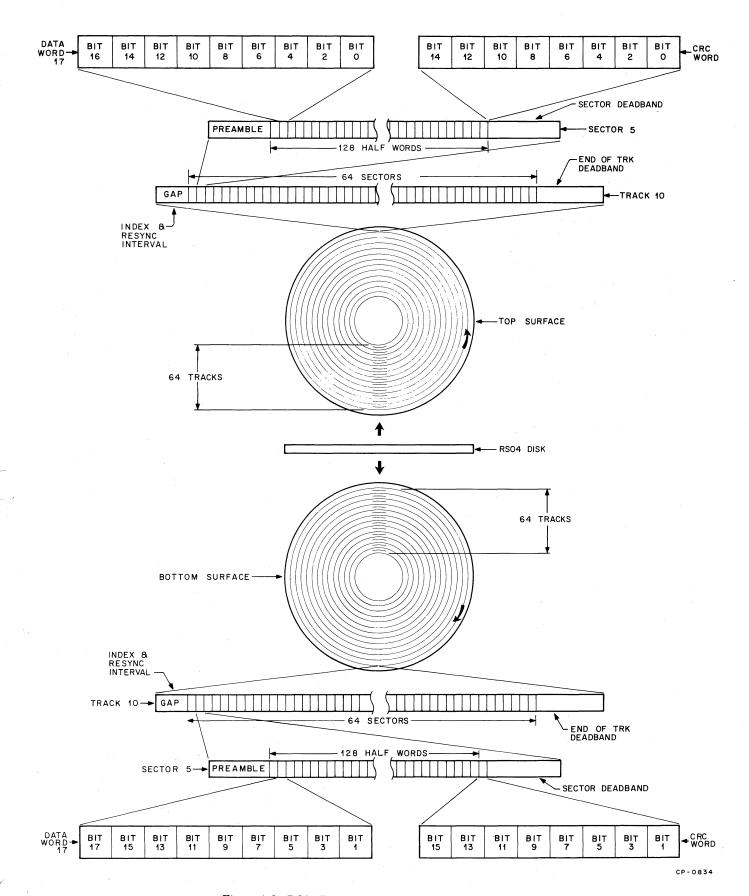

#### 1.1.4 Data Format

Both the top and bottom surfaces of the disk are utilized in the RS04. Nine head block assemblies (shoes) of 8 ferrites (heads) per assembly are permanently situated across the top surface, and 10 identical head block assemblies are fixed in position across the bottom surface. As the disk rotates, these ferrites describe 72 tracks on the top and 80 tracks on the bottom. Of these 152 available tracks, only 128 are utilized for data, 64 on each surface of the disk. One head block assembly on the top surface and one on the bottom surface are used as data track spares; the last one on the bottom surface is used for the timing tracks. The actual physical track locations on the disk are illustrated in Figure 2-25 in Section 2.3, Mechanical Principles of Operation.

The lowest level of addressing in the RS04 is the sector. Complete sectors are always transferred between Controller and drive. The detailed format of an RS04 disk is illustrated and described in later sections of this manual. Figure 1-2 is a schematic representation of format organization.

#### **NOTE**

In the following paragraph and throughout this manual, a distinction is made between *physical* data tracks and *logical* data tracks. The former refers to any individual discrete track on either surface of the disk. The latter refers to the combination of two physical data tracks, by the logic, to produce a single electrically-selectable data track. The distinction will become clear.

The logical data track consists of a  $250 \pm 50 \,\mu s$  index gap, followed by a resync interval, during which the phaselocked loops resynchronize to the timing track. The remaining data area is then sub-divided into 64 sectors with each sector containing a 128-word data block plus a 16-bit Cyclic Redundancy Check (CRC) word for error detection. At the beginning of each sector, a preamble is recorded, containing 67 - 70 zero bits and concluded by a Sync "1" bit. This is followed by 128 words of data. (If the number of data words to be written in any sector is less than 128, the remaining word positions of that sector are zero-filled by the Controller.) The CRC word is then written immediately after the data block of each sector. Finally, there are 103 to 106 bits of sector deadband. Note that although only 9 bits of each data word and 8 bits of the CRC word are written on each surface, the preamble described is written identically on both surfaces (i.e., 67-70 "0"s plus the sync "1" exist on each surface).

Figure 1-2 RS04 Data Track Format Schematic Diagram

### 1.2 SPECIFICATIONS

A list of RS04 characteristics is given in Table 1-1.

Table 1-1 RS04 Performance Specifications

| Characteristic          | Parameter                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------|

| Model Designation       |                                                                                                           |

| RS04-AA                 | 90–132 Vac @ 60 Hz                                                                                        |

| RS04-AB                 | 180–264 Vac @ 60 Hz                                                                                       |

| RS04-AC                 | 90–132 Vac @ 50 Hz                                                                                        |

| RS04-AD                 | 180–264 Vac @ 50 Hz                                                                                       |

| Power Requirements (ac) |                                                                                                           |

| Input Voltage           | 90–132 Vac @ 50/60 Hz<br>180–264 Vac @ 50/60 Hz                                                           |

| Starting Current        | 13 A @ 90–132 Vac<br>6 A @ 180–264 Vac                                                                    |

| Operating Current       | 6 A @ 90–132 Vac<br>3 A @ 180–264 Vac                                                                     |

| Dimensions and Weight   |                                                                                                           |

| Height                  | 15-3/4 in. (400 mm)                                                                                       |

| Width                   | 19 in. (482.6 mm)                                                                                         |

| Depth                   | 26-1/4 in. (665 mm)                                                                                       |

| Weight                  | 120 lbs (54.4 kg) (uncrated)                                                                              |

| Operating Environment   |                                                                                                           |

| Temperature             | 50° to 104° F (10° to 40° C)                                                                              |

| Humidity                | RH 10% to 90%; max wet bulb 82° F (22° C); min dewpoint 36° F (2° C).                                     |

| Vibration               | 5–50 Hz 0.004 in. DA                                                                                      |

| , 101 <b>2</b> 1012     | 50-500 Hz .5 g vertical.                                                                                  |

| Shock                   | 5 g, half sine, 10 ms duration, any plane.                                                                |

| Altitude                | 8000 ft (2438 m)                                                                                          |

| Storage Environment     |                                                                                                           |

| Temperature             | 150° F max                                                                                                |

| Humidity                | 85° F max wet bulb, 80% R.H.                                                                              |

| Vibration               | Vertical – 1.4 g, 10–300 Hz.                                                                              |

|                         | Acceleration spectral density .029 g <sup>2</sup> /Hz from 10-50 Hz with 8 db/oct rolloff from 50-300 Hz  |

|                         | <i>Horizontal</i> – 0.68 g, 10–200 Hz.                                                                    |

|                         | Acceleration spectral density .007 g <sup>2</sup> /Hz from 10-50 Hz with 8 db/oct rolloff from 50-200 Hz. |

|                         | $Shock - 20$ g, half sine, $30 \pm 10$ ms duration, vertical.                                             |

|                         | Altitude – 30,000 ft (9144 m)                                                                             |

Table 1-1 (Cont)

RS04 Performance Specifications

| Characteristic                                              | Parameter                                                                                                                                                                                       |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Medium                                              |                                                                                                                                                                                                 |

| Type Method Recording Technique Capacity (each disk) Format | 16 in., NiCo-plated, magnetic disk Two surfaces, fixed head, sector interleaving optional Miller Encoded (MFM) 524,288 words max. 18 bits/word 128 words/sector 64 sectors/track 64 tracks/disk |

|                                                             |                                                                                                                                                                                                 |

|                                                             | NOTE  These are <i>logical</i> tracks, since two physical tracks (one on each surface) are simultaneously addressed.                                                                            |

| Words/Logical Track                                         | 8192                                                                                                                                                                                            |

| Spare Tracks                                                | 16 data spares (8 per surface) 8 (4 per surface) guaranteed to customer 1 timing spare                                                                                                          |

| Error Detection                                             | 16-bit CRC per sector                                                                                                                                                                           |

| Bit Error Rate                                              |                                                                                                                                                                                                 |

| Recoverable Data Errors Unrecoverable Data Errors           | < 1 in 10 <sup>11</sup> bits transferred < 1 in 10 <sup>12</sup> bits transferred                                                                                                               |

| Access Times                                                | 60 Hz 50 Hz                                                                                                                                                                                     |

| Minimum<br>Typical<br>Maximum                               | 6.4 μs 7.7 μs<br>8.5 ms 10.2 ms<br>17.0 ms 20.4 ms                                                                                                                                              |

| Transfer Rates (average)                                    |                                                                                                                                                                                                 |

| Non-interleaved<br>Interleaved                              | 2 μs/18-bit word<br>4 μs/18-bit word (jumper removed)                                                                                                                                           |

| Interface Signals                                           |                                                                                                                                                                                                 |

| Logic Levels Input to MASSBUS transmitters                  | True = 0 V, False = +3 V                                                                                                                                                                        |

| Output from MASSBUS receivers                               | True = +3 V, False = 0 V                                                                                                                                                                        |

| Write Lock Out                                              | Selectable from track "0" to selected track.                                                                                                                                                    |

| MTBF (calculated)                                           | 4700 hours                                                                                                                                                                                      |

#### 1.3 MAJOR SUBASSEMBLIES

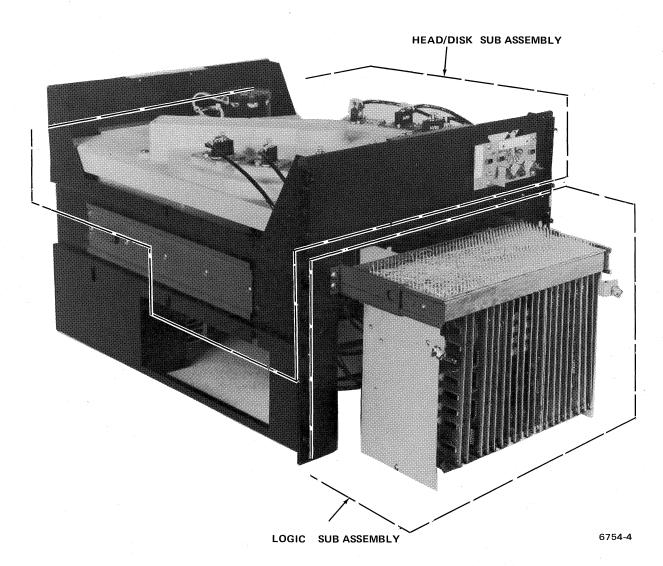

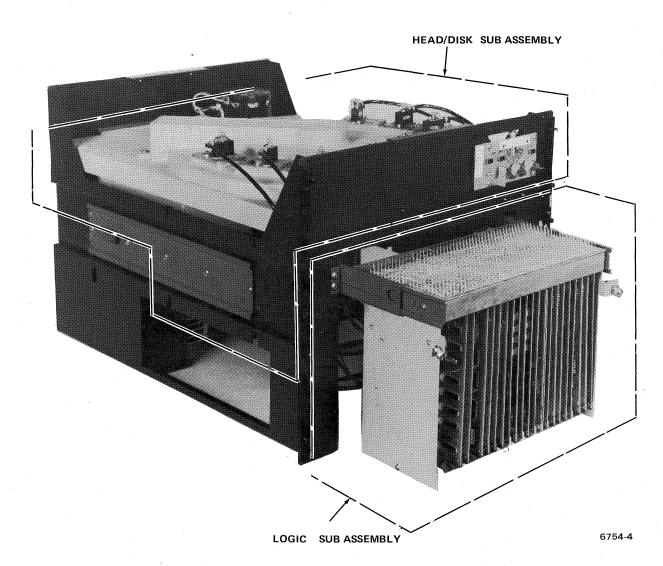

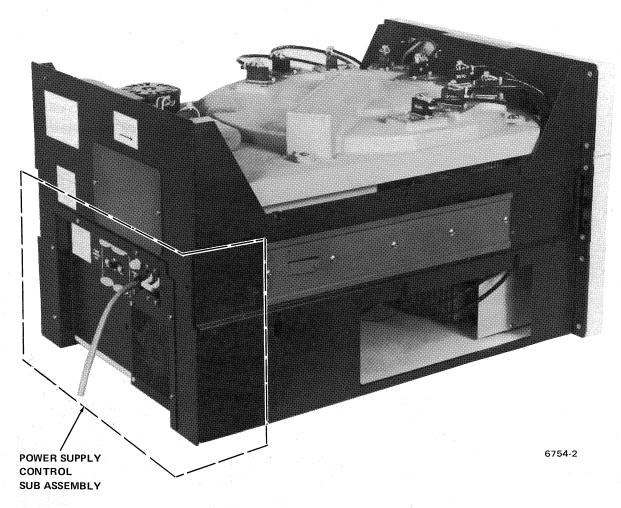

The RS04 can be subdivided into three major subassemblies: The Head/Disk Subassembly contains the heads, the disk, the spindle/motor, and the air filter system; the Logic Subassembly comprises all the analog and digital electronics necessary for drive control and data processing; and the Power Supply/Control Subassembly controls ac power to the disk and blower motors and supplies the dc voltages necessary to run the disk file (Figure 1-3).

#### 1.3.1 Head/Disk Subassembly

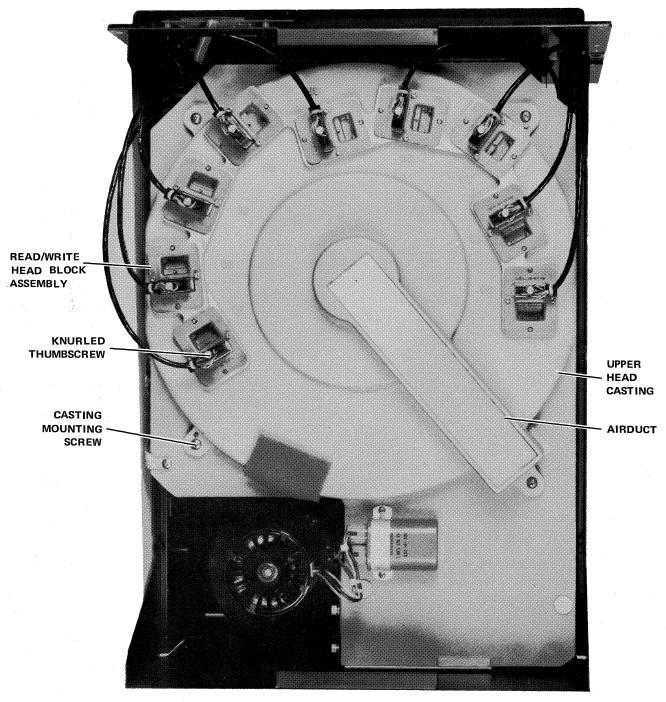

The Head/Disk Subassembly is composed of the upper and lower head castings, a 16-in. NiCo-plated recording disk, a

blower motor, the spindle/motor, an Absolute filter, and 19 head block assemblies (shoes). The upper head casting contains 9 head block assemblies; the lower casting contains the remaining 10. Each head block assembly contains 8 individual read/write heads (ferrites). All head blocks have been pre-adjusted such that when the disk is rotating, the heads will fly 55 microinches from the surface of the disk. When the disk is not rotating, the heads rest on the surfaces of the disk.

The disk is driven by a 50/60 Hz integral ac induction motor/spindle.

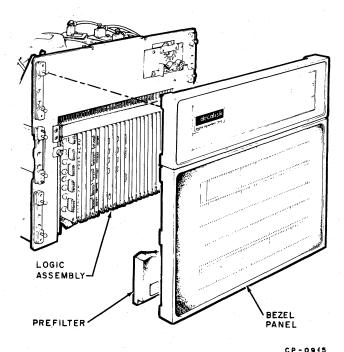

Figure 1-3a Major Subassembly Locations

<sup>\*</sup>Absolute is registered trademark of Cambridge Filter Corporation.

Table 1-1 (Cont)

RS04 Performance Specifications

| Characteristic                                              | Parameter                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Medium                                              |                                                                                                                                                                                                                                                                                                               |

| Type Method Recording Technique Capacity (each disk) Format | 16 in., NiCo-plated, magnetic disk Two surfaces, fixed head, sector interleaving optional Miller Encoded (MFM) 524,288 words max. 18 bits/word 128 words/sector 64 sectors/track 64 tracks/disk  NOTE These are logical tracks, since two physical tracks (one on each surface) are simultaneously addressed. |

| Words/Logical Track                                         | 8192                                                                                                                                                                                                                                                                                                          |

| Spare Tracks                                                | 16 data spares (8 per surface) 8 (4 per surface) guaranteed to customer 1 timing spare                                                                                                                                                                                                                        |

| Error Detection                                             | 16-bit CRC per sector                                                                                                                                                                                                                                                                                         |

| Bit Error Rate                                              |                                                                                                                                                                                                                                                                                                               |

| Recoverable Data Errors Unrecoverable Data Errors           | < 1 in 10 <sup>11</sup> bits transferred<br>< 1 in 10 <sup>12</sup> bits transferred                                                                                                                                                                                                                          |

| Access Times                                                | 60 Hz 50 Hz                                                                                                                                                                                                                                                                                                   |

| Minimum<br>Typical<br>Maximum                               | 6.4 μs 7.7 μs<br>8.5 ms 10.2 ms<br>17.0 ms 20.4 ms                                                                                                                                                                                                                                                            |

| Transfer Rates (average)                                    |                                                                                                                                                                                                                                                                                                               |

| Non-interleaved<br>Interleaved                              | 2 μs/18-bit word<br>4 μs/18-bit word (jumper removed)                                                                                                                                                                                                                                                         |

| Interface Signals                                           |                                                                                                                                                                                                                                                                                                               |

| Logic Levels Input to MASSBUS transmitters                  | True = 0 V, False = +3 V                                                                                                                                                                                                                                                                                      |

| Output from MASSBUS receivers                               | True = +3 V, False = 0 V                                                                                                                                                                                                                                                                                      |

| Write Lock Out                                              | Selectable from track "0" to selected track.                                                                                                                                                                                                                                                                  |

| MTBF (calculated)                                           | 4700 hours                                                                                                                                                                                                                                                                                                    |

#### 1.3 MAJOR SUBASSEMBLIES

The RS04 can be subdivided into three major subassemblies: The Head/Disk Subassembly contains the heads, the disk, the spindle/motor, and the air filter system; the Logic Subassembly comprises all the analog and digital electronics necessary for drive control and data processing; and the Power Supply/Control Subassembly controls ac power to the disk and blower motors and supplies the dc voltages necessary to run the disk file (Figure 1-3).

#### 1.3.1 Head/Disk Subassembly

The Head/Disk Subassembly is composed of the upper and lower head castings, a 16-in. NiCo-plated recording disk, a

blower motor, the spindle/motor, an Absolute (filter, and 19 head block assemblies (shoes). The upper head casting contains 9 head block assemblies; the lower casting contains the remaining 10. Each head block assembly contains 8 individual read/write heads (ferrites). All head blocks have been pre-adjusted such that when the disk is rotating, the heads will fly 55 microinches from the surface of the disk. When the disk is not rotating, the heads rest on the surfaces of the disk.

The disk is driven by a 50/60 Hz integral ac induction motor/spindle.

Figure 1-3a Major Subassembly Locations

<sup>\*</sup>Absolute is registered trademark of Cambridge Filter Corporation.

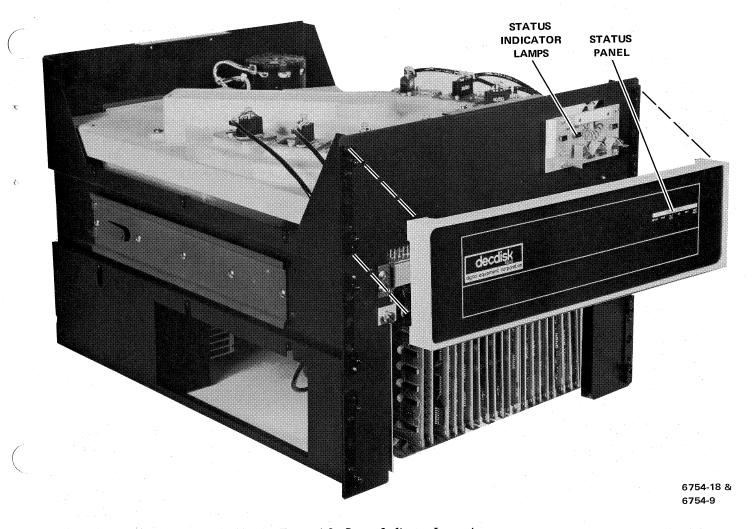

Figure 1-3b Major Subassembly Locations

#### 1.3.2 Logic Subassembly

The Logic Subassembly contains 24 printed circuit modules, located in the front of the drive cabinet. This subassembly is attached to slides which pull out from the drive cabinet as shown in Figure 1-3a.

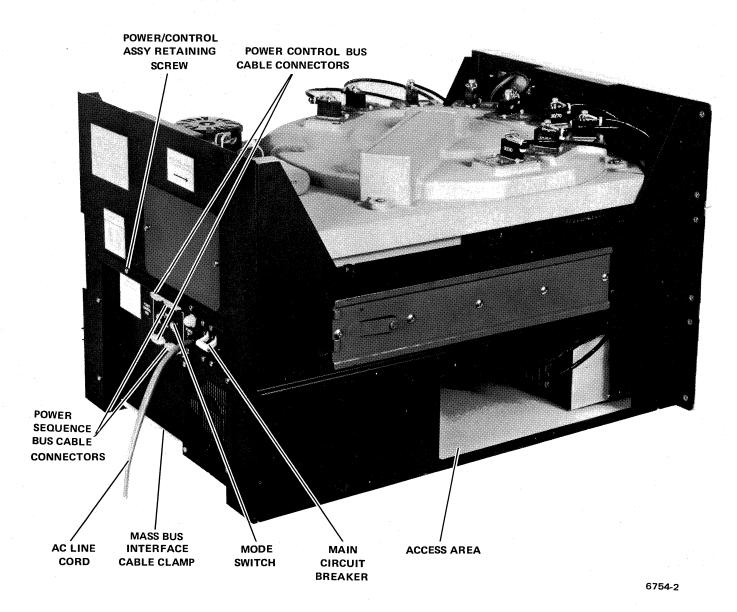

#### 1.3.3 Power Supply/Control Subassembly

The Power Supply/Control Subassembly is mounted in the lower-rear portion of the RS04 cabinet (Figure 1-3b) and is removable as a unit. It contains all of the electronic components necessary for generation of the operational voltages for the drive.

The linear type dc power supply regulator operates from a ferroresonant transformer to supply +5 Vdc @ 9 A, +20 Vdc @ 1 A, and -20 Vdc @ 1.5 A. All three of these output voltages are over-current protected; in addition, the +5 Vdc output is over-voltage protected.

The power control system distributes and controls all ac power within the drive. This system is controlled by the mode switch and can be operated in either REMOTE, LOCAL, or OFF mode.

In REMOTE mode, logic signals from two power buses are used to control individual drive power, as well as power sequencing along the daisy chain that connects all drives. In LOCAL mode, the individual drive power system is removed from power bus control and is operated directly by the MODE switch. In OFF mode, only the dc power supply is shut down. If the disk drive motor, blower motor, and fan are operating when this mode is selected, they will continue to operate and can only be stopped by manually tripping the main circuit breaker or by unplugging the ac line cord. If the disk drive motor, blower motor, and fan are not operating when this mode is selected, they cannot be started with logic signals on the power bus.

#### 1.4 RS04 CONTROLS AND INDICATORS

The RS04 controls and indicators are divided into five areas on the equipment.

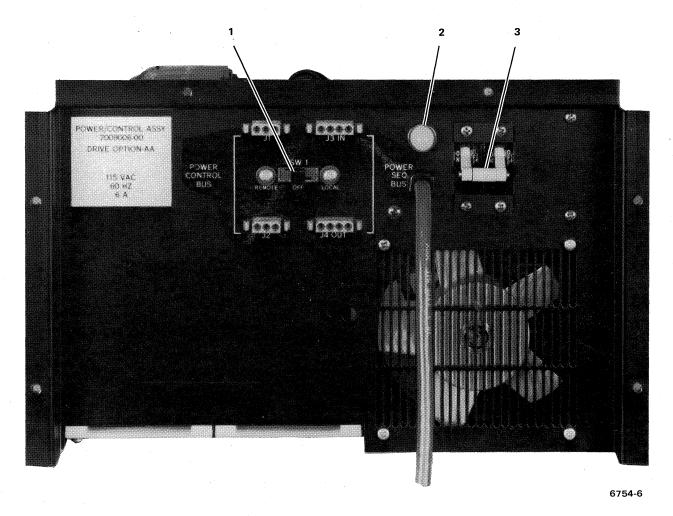

Figure 1-4 illustrates the power supply/control section controls and indicators located on the rear of the unit; Table 1-2 lists their functions.

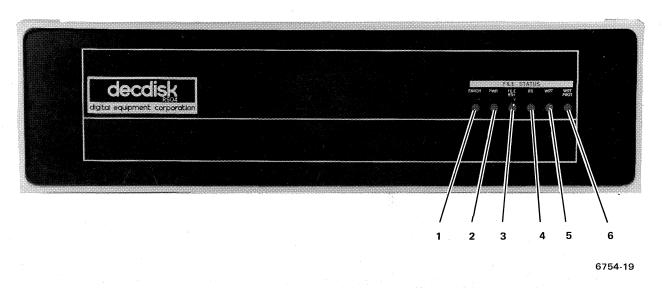

Figure 1-5 shows the front panel indicators that are described in Table 1-3.

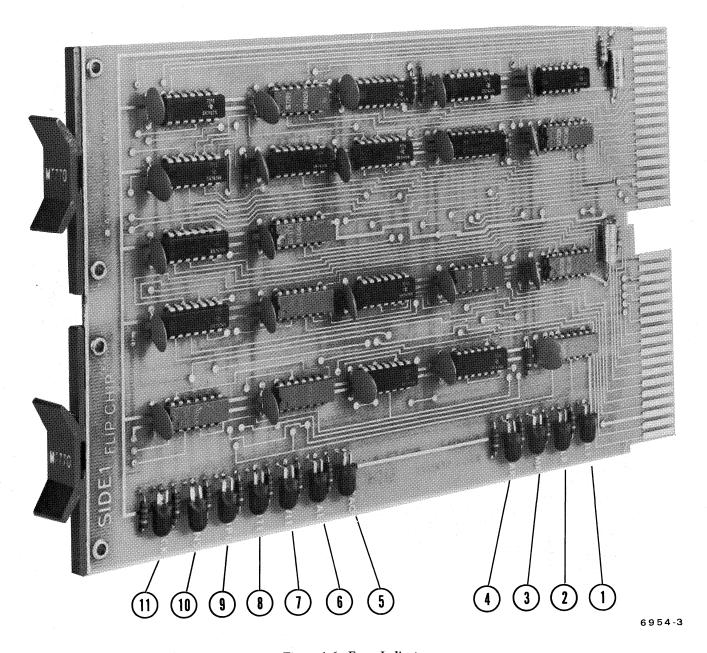

The error indicators are shown in Figure 1-6 and correspond to each of the bits in the Error register. Table 1-4 defines the 3-letter mnemonic associated with each LED indicator. These indicators are located on Module M7770 in slot AB05 of the logic subassembly. Access to these

indicators is gained by removing the lower-front panel from the unit; the LEDs are mounted on the front-edge of the module. The front panel ERROR indicator is the OR of all the error indicators.

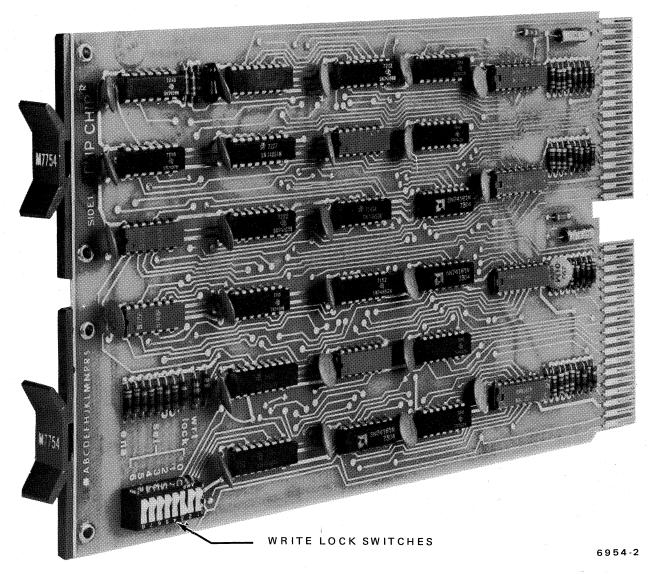

Figure 1-7 illustrates the Write Lock Address switches, located on Module M7754 in slot AB07 of the logic subassembly. One switch enables this feature; the others are set to the highest octal track address which will be locked out. All tracks, from zero up to and including the switch-set address, are write-protected.

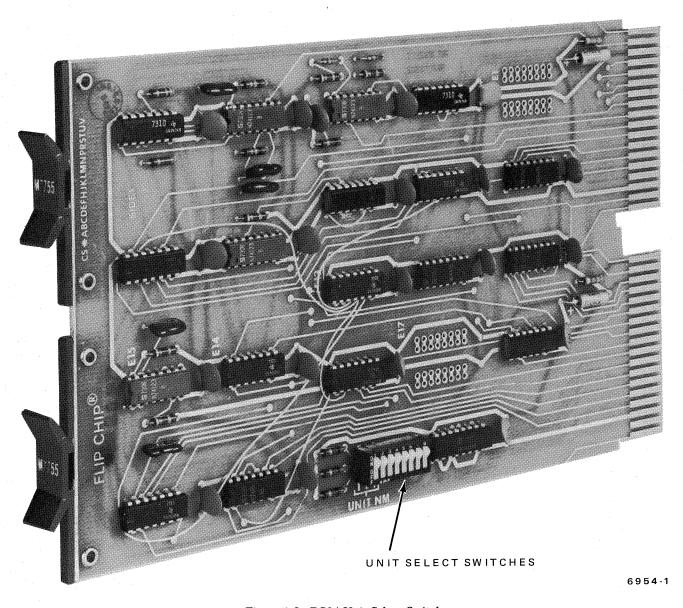

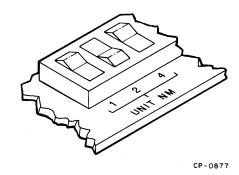

Figure 1-8 illustrates the Unit Number select switches, located on Module M7755 in slot AB04 of the logic subassembly. Numbers 1, 2, and 4 designate the binary weight of each switch in determining the desired unit number.

Figure 1-4 Power Controls and Indicators

Table 1-2 Power Controls and Indicators

| Index<br>No. | Panel<br>Marking | Function                                                                                                                                                                                                                                                                                                                                |  |

|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1            | SW1              | Power Control System Mode switch. In REMOTE position, allows the drive to be powered in accordance with the Power Sequence Bus and Power Control Bus requirements. In LOCAL position, allows the drive to be run independent of the Power Sequence and Control Buses. In OFF position, shuts off dc and inhibits starting of the drive. |  |

| 2            | (none)           | Power indicator. Lights whenever ac voltage is present anywhere in the drive.                                                                                                                                                                                                                                                           |  |

| 3            | (none)           | Main breaker. Controls all ac power in the drive and breaks both sides of the line in the event of malfunction.                                                                                                                                                                                                                         |  |

Table 1-3

Front Panel File Status Indicators

| Index<br>No. | Panel<br>Marking | Function                                                                                                                                                                                                  |  |

|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1            | ERROR            | Lights when any drive error is detected; specific error is indicated in Table 1-4. Remains lit until the Controller issues a Drive Clear or Initialize command, or writes all 0s into the Error register. |  |

| 2            | PWR              | Lights when operating power (ac and dc) is present; extinguishes when any operating power is not present.                                                                                                 |  |

| 3            | FILE RDY         | Lights when the disk is rotating at the correct speed and the drive is ready to perform a program-controlled operation; extinguishes while the drive is performing a program-controlled operation.        |  |

| 4            | RD               | Lights only when a Read or Write-Check command is being executed.                                                                                                                                         |  |

| 5            | WRT              | Lights only when a Write command is being executed.                                                                                                                                                       |  |

| 6            | WRT PROT         | Lights whenever the address in the Desired Address register is write-protected, regardless of the drive operation.                                                                                        |  |

Figure 1-5 Front Panel Indicators

Table 1-4

Error Indicators

| Index<br>No. | Module<br>Label | Function                            |  |  |

|--------------|-----------------|-------------------------------------|--|--|

| 1            | ILF             | ILlegal Function Error              |  |  |

| 2            | ILR             | ILlegal Register Error              |  |  |

| 3            | RMR             | Register Modification Refused Error |  |  |

| 4            | PAR             | MASSBUS PARity Error                |  |  |

| 5            | AOE             | Address Overflow Error              |  |  |

| 6            | IAE             | Invalid Address Error               |  |  |

| 7            | WLE             | Write Lock Error                    |  |  |

| 8            | DTE             | Drive Timing Error                  |  |  |

| 9            | OPI             | OPeration Incomplete Error          |  |  |

| 10           | UNS             | UNSafe Error                        |  |  |

| 11           | DCK             | Data ChecK Error                    |  |  |

Figure 1-6 Error Indicators

Figure 1-7 RS04 Write Lock Protect Address Switches

Figure 1-8 RS04 Unit Select Switches

#### 1.5 OPTIONS

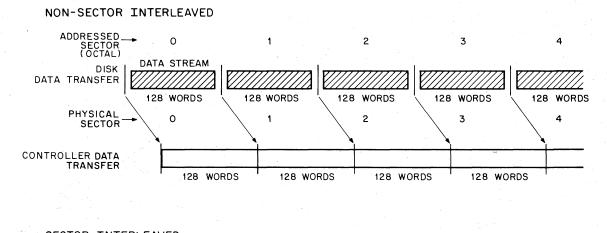

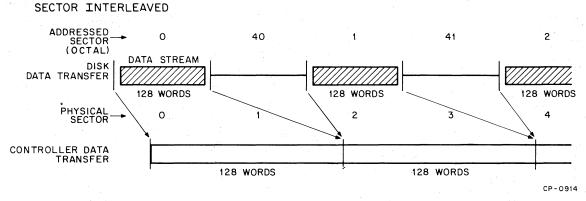

There is one jumper-selectable option on the RS04, the Sector Address Interleave option. By removing jumper W1 on the G092 module, sectors are addressed in an interleaved sequence, i.e., physically sequential sectors do *not* have numerically consecutive addresses. Instead, *alternate* physical sectors have consecutive addresses (Figure 1-9).

When this option is installed, a 250  $\mu$ s gap is provided between any two numerically consecutive sectors, effectively doubling the time available to transfer one sector. For example, two disk revolutions (33.3 ms) are required to consecutively transfer a complete data track (8192 words) resulting in a 4  $\mu$ s average word transfer rate.

Figure 1-9 Effect of Sector Interleaving On RS04 Transfer Rate

# SECTION 2 THEORY OF OPERATION

#### 2.1 GENERAL

This section contains a theoretical discussion of the RS04. It describes the three major areas of the disk drive, electrical, mechanical, and magnetic, on a functional block diagram level. Detailed logic descriptions of modules are found in Section III — Electrical Servicing; detailed mechanical servicing and maintenance discussions are found in Section IV — Mechanical Servicing.

#### 2.2 ELECTRICAL PRINCIPLES OF OPERATION

Subsection 2.2 discusses the electrical and electronic principles involved in the operation of the RS04.

#### 2.2.1 MASSBUS Interface

The RS04 is a MASSBUS peripheral and communicates with the MASSBUS Controller via the MASSBUS. The MASSBUS is composed of two separate, independent buses, capable of conducting two different types of communication simultaneously: the asynchronous Control Bus and the synchronous Data Bus (Figure 2-1).

The Control Bus communicates with the drive registers. Its signals are defined as follows:

Control and Status (C(00:15)) – These bidirectional lines transmit 16 parallel control or status bits to or from the drive.

Control Bus Parity (CPA) — This bidirectional line transmits an odd Control Bus parity bit to or from the drive. Control parity is simultaneously transmitted with the data on the Control Bus.

Drive Select (DS(0:2)) — These three lines transmit a 3-bit binary code from the Controller to select one drive from up to eight drives.

Register Select (RS(0:4)) — These five lines transmit a 5-bit binary code from the Controller to select one of the following eight drive registers:

00<sub>8</sub> – Control Register

01 8 - Status Register

028 - Error Register

03<sub>8</sub> – Maintenance Register

04<sub>8</sub> - Attention Summary Register

058 - Desired Address Register

06<sub>8</sub> - Drive Type Register

07<sub>8</sub> - Look-Ahead Register

#### **NOTE**

The two most significant bits (RS 3 and 4) are not used in the RS04. If either of these lines is asserted, an Illegal Register Error occurs.

Controller To Drive (CTOD) — This line transmits the signal from the Controller to indicate in which direction information is to be transferred on the Control Bus. For a Controller-to-drive transfer, the Controller asserts CTOD; for a drive-to-Controller transfer, the Controller negates CTOD.

Demand (DEM) – This line transmits the signal from the Controller to initiate a Control Bus transfer.

Transfer (TRA) — This line transmits the signal TRA from the drive in response to DEM. For a Controller-to-drive transfer, TRA is asserted after the data is strobed; for a drive-to-Controller transfer, TRA is asserted after the data is asserted on the Control Bus. TRA is negated when the Controller negates DEM.

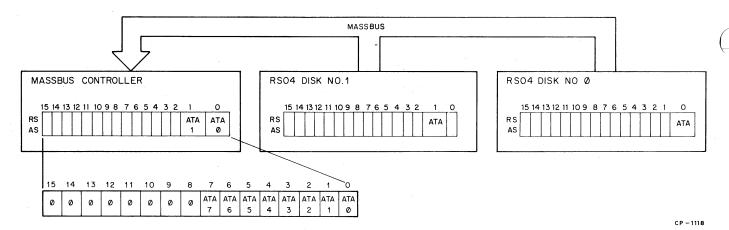

Figure 2-1 MASSBUS Configuration

Attention (ATTN) — The drive asserts this line to signal the Controller of any change in drive status. It is asserted any time a drive's ATA status bit is set. ATTN is common to all drives on the MASSBUS and may be asserted by more than one drive at a time.

Initialize (INIT) — This line transmits the signal INIT from the Controller to initialize all drives on the MASSBUS. This signal is transmitted at system start-up or whenever the Controller issues an Initialize command.

Mass Fail — This line transmits the signal MASS FAIL from the Controller whenever power fails in the Controller.

A typical Control Bus transmission is illustrated in Figure 2-2. In a Controller write operation into the RS04 registers. the Controller asserts the C lines with the register data to be transferred. The Controller also asserts the DS lines (to specify one drive), the RS lines (to specify the register to which the data must be transferred), and the CTOD line (to indicate that the direction of transfer is to the drive). After these signals have settled on the bus, the Controller asserts DEM to cause the drive to load the data on the C lines into the register addressed. When this is accomplished, the drive asserts TRA, informing the Controller that the register has been loaded. This causes the Controller to negate DEM. At the same time, the Controller negates the C, DS, RS, and CTOD lines. This is a typical transfer and illustrates what is referred to as a "handshake sequence" on the asynchronous Control Bus.

Figure 2-2 Typical RS04 Control Bus Transfer Timing

In a Controller read operation from the RS04 registers, the sequence is similar. The DS and RS lines are asserted by the Controller while the CTOD line is negated to indicate that the direction of transfer is from the drive. The Controller then asserts DEM, causing the drive to place the register data on the C lines. When the C lines have settled, the drive will assert TRA, causing the Controller to take the data from the C lines. The Controller then negates DEM, causing the RS04 to negate TRA and the C lines. This concludes the transfer operation.

The Data Bus lines are defined as follows:

Data Words (D(00:17)) – These bidirectional lines transmit 18 parallel data bits to or from the drive.

Data Bus Parity (DPA) — This bidirectional line transmits an odd Data Bus parity bit to or from the drive. Data parity is simultaneously transmitted with the bits on the Data Bus.

Sync Clock (SCLK) — During a read operation, this line transmits the signal SCLK from the drive to indicate when data on the Data Bus is to be strobed by the Controller. During a write operation, this line transmits SCLK to the Controller to indicate the rate at which data should be presented on the Data Bus.

Write Clock (WCLK) — This line transmits the signal WCLK from the Controller indicating when data to be written is to be strobed.

Run (RUN) — This line transmits the signal RUN from the Controller to initiate data transfer command execution. During a data transfer, the drive samples RUN at the end of each sector. If RUN is still asserted, the drive continues the data transfer into the next sector; if RUN is negated at this time, the drive terminates the data transfer.

End of Block (EBL) – This line normally transmits the signal EBL from the drive at the end of each sector during a data transfer. However, for certain abnormal conditions where it is necessary to terminate the data transfer immediately, EBL is asserted prior to the end of the sector.

Exception (EXC) — This bidirectional line transmits the signal EXC from the drive during a data transfer to indicate that an error has occurred. EXC can also be asserted by the Controller to abort an in-progress data transfer.

Occupied (OCC) – This line indicates to the Controller that the drive has accepted and recognized a valid data transfer command.

Figure 2-3 shows the typical timing of the Data Bus signals. To execute a Read command, the Controller first sets the address on the disk from which it wishes to read, and sets a read function. It then asserts the RUN line which causes the drive to search for the specified address. When the drive finds that address, transfer of data begins.

Synchronization of data transfer over the Data Bus originates in the drive, regardless of the direction of transfer. In this particular case, the drive places the first word on the D lines with the assertion of Sync Clock.

The Controller interprets the leading edge of the clock to signify that data has been put on D(00:17) and uses the trailing edge of that same clock to sample the data and place it into its data buffer. On the next leading edge of

Figure 2-3 Data Bus Transfer Timing

Sync Clock, the drive places the next data word on the bus, and on that trailing edge, the Controller takes it off. This continues for complete sectors as long as RUN is asserted. The drive samples the state of RUN at the end of each sector and continues transferring complete sectors until the negation of RUN is detected.

To execute a Write command, the sequence is similar. The desired address is set in the drive and then a write function is set. The assertion of RUN initiates an address search operation, and when the desired sector is found, the drive begins issuing SCLKs. These SCLKs are "echoed" back to the drive by the Controller as WCLKs. On the leading edge of WCLK, the drive strobes D(00:17) into its data buffer. On the trailing edge, the Controller will present another word on D(00:17). At the end of each sector the drive samples RUN, and if it is negated, terminates the data transfer.

EBL is normally asserted by the drive at the end of each sector transferred, for both reads and writes. It is asserted immediately after the last word of the sector is transferred and is typically one word-time or 1.8  $\mu$ s in duration. In this case, EBL indicates that a decision point has been reached — whether to continue or to terminate the current data transfer. The decision is based on the state of RUN at the trailing edge of EBL. Under certain conditions, EBL may be asserted prior to the end of a sector; these conditions will be discussed in the next paragraph and in the discussion of the Error register.

Under certain unusual circumstances, the Controller may need to terminate a data transfer prior to the end of the current sector. In such a case, the Controller asserts EXC, which is recognized only by the drive transferring data, causing that drive to assert EBL immediately and to terminate the data transfer.

EXC is asserted by the drive to indicate to the Controller that an error condition has occurred during a data transfer.

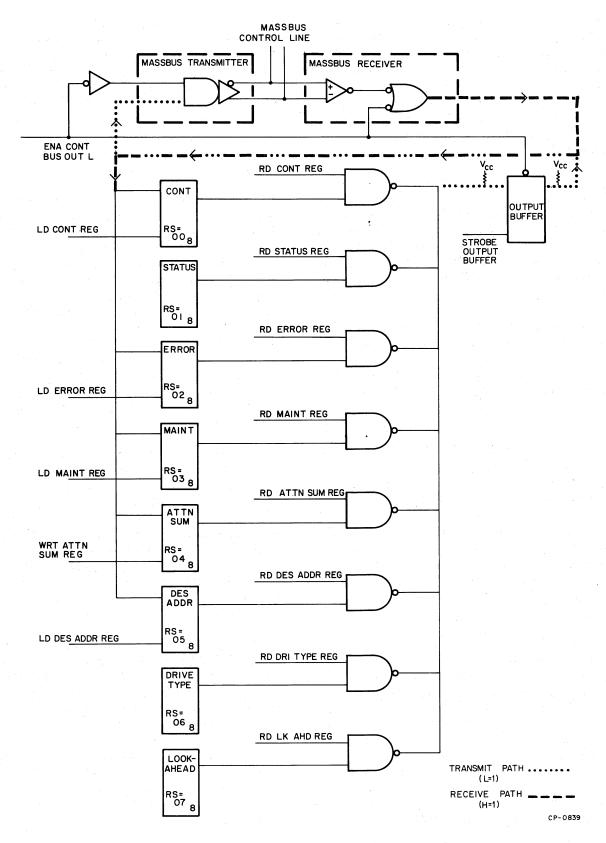

#### 2.2.2 RS04 Logical Block Diagram

Figure 2-4 is a functional block diagram of the RS04. The drawing can be divided in half, with the top half representing all the logic associated with the Control Bus, and the bottom half showing all the logic associated with the Data Bus. Note that the dashed blocks represent individual modules and that each individual module contains complete functional elements.

The MASSBUS Transceiver modules are represented by the block on the left-hand edge of Figure 2-4. All of the MASSBUS signals are distributed among the three M5903 modules, located in slots AB01, AB02, and AB03 of the logic subassembly. The purpose of the transceivers is to interface between the differential signal levels present on the MASSBUS and the TTL logic signal levels utilized within the RS04.

MASSBUS Control Bus lines (Figure 2-4, top-left) are brought into an M7755 Control module, located in slot AB04 of the Logic Subassembly. Here the Drive Select lines are compared to the locally-set Drive Select switches to yield the signal SELECTED. This signal is then used to enable the Control Bus Handshake and Register Control section of this logic. The Register Control section then enables the Register Select logic to decode the MASSBUS Register Select lines for the register to be addressed and uses CTOD to determine whether the register is to be written or read. Note that an error signal can be produced from the Register Select block (1) if a register write is decoded while the drive is performing a Search or data transfer function or (2) if a non-existent register is addressed.

As can be seen from the block diagram, the inputs to the Control, Attention Summary, Maintenance, Error, and Desired Address registers (as well as the Control Bus Parity Check logic), are the Control Bus lines (C(00:15)). Inside the drive, these signals are designated WO DCB(00:15) (Wired-OR Drive Control Bus). The Drive Control Bus is driven by either the MASSBUS transceivers or by the Output Buffer.

The purpose of the Output Buffer is to freeze the contents of a readable register while it is being read by the Controller.

The input to the Output Buffer is a wired-OR bus of all drive registers, designated WO BO(00:15) (Wired-OR Bus Out).

Figure 2-5 shows a functional representation of the register data paths. The MASSBUS transceivers, shown as a single block, are represented at the top of Figure 2-5, where they tie to the MASSBUS C lines. The transmitters have a TTL input and a differential output, while the receivers are differential in and TTL out. Either transmitters or receivers on the Control Bus are enabled at any one time, never both.

Figure 2-4 RS04 Logical Block Diagram

Figure 2-5 Functional Representation of Register Data Paths. (One Bit)

Normally, the receivers are enabled and data is received continuously, loading or writing any register that is selected; but when it is desired to read from some register, the ENA CONT BUS OUT signal is used to disable the receivers, and to enable both the transmitters and the Output Buffer. The contents of the selected register are gated to the input of the Output Buffer by the appropriate Register read control signal and transmitted to the MASSBUS C lines via the Output Buffer.

To perform any program-controlled drive operation, a drive must first be selected and then an operational command must be written into that drive's Control register. To accomplish this, the Controller places a 3-bit drive unit number code on the Drive Select lines, places the 5-bit Control register select code  $(00_8)$  on the Register Select lines, places the operational command on the Control Bus, and asserts CTOD.

After these signals have settled on the interface lines, the Controller asserts DEM to initiate the "handshake" operation. If the configuration of the drive's unit number switches corresponds to the Drive Select code received from the Controller, the drive control logic is enabled and the Control Bus is checked for correct parity.