# COMPUTER PERIPHERAL AND SIGNAL PROCESSING COMPONENTS

#### PROGRAMMABLE TRACKING FILTER

IMP42C455-13

### **General Description**

The IMP42C455-13 is a programmable continuous-time filter operating in the 2MHz to 13MHz cutoff frequency range. Its amplitude and phase response may be modified via a digital serial interface. This makes the 42C455-13 suitable for a variety of applications requiring modifiable responses such as disk drive read channels, telecom, video systems and other signal processing applications.

The filter consists of a 6<sup>th</sup> order Bessel lowpass filter and an asymmetrical pulse slimmer. The pulse slimmer zeros and the frequency scaling can be programmed through the serial interface. Matched normal and differentiated outputs are provided.

The general form of the filter transfer function is given by:

$$H_{NORM}(s) = A_{NORM} \left[ 1 + \frac{s}{\omega_{z_a}} \right] \left[ 1 - \frac{s}{\omega_{z_b}} \right] H_{Lowpass}(s)$$

$$H_{DIFF}(s) = A_{DIFF}[s] \left[1 + \frac{s}{\omega_{z_b}}\right] \left[1 - \frac{s}{\omega_{z_b}}\right] H_{Lowpess}(s)$$

where  $A_{NORM}$  &  $A_{DIFF}$  are used to set DC gains and  $\omega_{z_a}$  &  $\omega_{z_b}$  represent the slimmer zeros.

The IMP42C455-13 uses an external reference frequency and an internal Phase-Lock Loop to assure accuracy over process and environmental conditions. It also provides high accuracy pole and zero placement.

The IMP42C455-13 is based upon a transconductance-C filter technology and implemented in IMP's proprietary MxCMOS 1.2μm process.

#### **Features**

- 6<sup>th</sup> order Bessel Lowpass Filter

- Unboosted cutoff frequency programmable between 2MHz and 13MHz

- Programmable zeros for both symmetric and asymmetric pulse slimming

- Accurate (10%) pole placement using reference frequency and PLL tuning

- No external components required

- +5 volt operation

- Low-power mode

- Quadrature outputs

- Completely differential signal path

- 16 pin SOIC and DIP packages

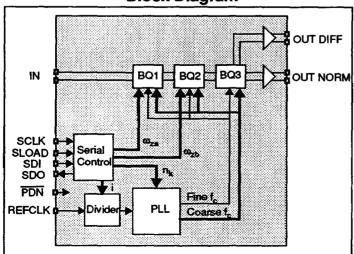

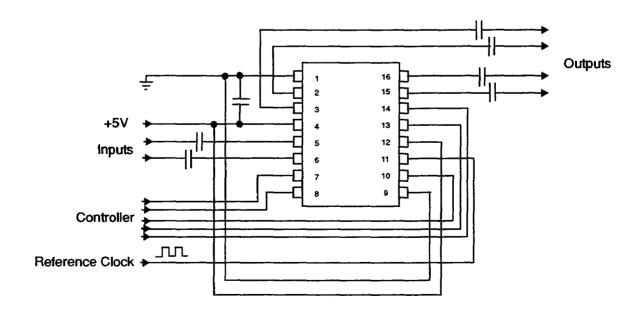

#### **Block Diagram**

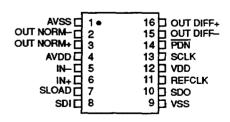

### **Pin Assignment**

# **Pin Descriptions**

| NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN+       | Filter positive differential input                                                                                                                                                                                                                                                                                                            |

| IN-       | Filter negative differential input                                                                                                                                                                                                                                                                                                            |

| OUT NORM+ | Filter normal positive differential output                                                                                                                                                                                                                                                                                                    |

| OUT NORM- | Filter normal negative differential output                                                                                                                                                                                                                                                                                                    |

| OUT DIFF+ | Filter differentiated positive differential output                                                                                                                                                                                                                                                                                            |

| OUT DIFF- | Filter differentiated negative differential output                                                                                                                                                                                                                                                                                            |

| SCLK      | Clock input for shifting in serial data for programming the filter characteristics. Input is TTL compatible                                                                                                                                                                                                                                   |

| SDI       | Input for shifting in serial data for setting the filter characteristics. A low level corresponds to a logical "0". Data is sampled on a high-to-low transition of SCLK. Input is TTL compatible.                                                                                                                                             |

| SLOAD     | Input used to latch serial data into internal registers. Data may be shifted in when SLOAD is low. Data is latched in when SLOAD transitions high. Input is TTL compatible.                                                                                                                                                                   |

| SDO       | Output for shifting out data stored in internal registers. Data changes on the high-to-low transition of SCLK. Output is high-impedance until the low-to-high transition of SLOAD after writing a readback address. The output returns to a high impedance state after the ninth high-to-low transition of SCLK after SLOAD transitions high. |

| REFCLK    | Clock reference for tuning the filter response. Input is TTL compatible.                                                                                                                                                                                                                                                                      |

| PDN       | A low level on this input causes the IC to go into a low power standby condition. Input is TTL compatible.                                                                                                                                                                                                                                    |

| AVDD      | Positive supply voltage - Analog                                                                                                                                                                                                                                                                                                              |

| AVSS      | Ground - Analog                                                                                                                                                                                                                                                                                                                               |

| VDD       | Positive supply voltage - Digital                                                                                                                                                                                                                                                                                                             |

| VSS       | Ground -Digital                                                                                                                                                                                                                                                                                                                               |

# **Electrical Specifications**

# **Absolute Maximum Ratings**

| Parameter            | Conditions          | Min  | Nom | Max  | Units     |  |

|----------------------|---------------------|------|-----|------|-----------|--|

| Supply Voltage       | VDD-VSS             | 0    |     | 8.0  | v         |  |

| Voltage on any input | min relative to VSS | -0.3 |     |      | V         |  |

|                      | max relative to VDD |      |     | +0.3 | ٧         |  |

| Storage temperature  |                     | 0    |     | 150  | degrees C |  |

# **Recommended Operating Conditions**

| Parameter                     | Conditions | Min | Nom | Max | Units     |

|-------------------------------|------------|-----|-----|-----|-----------|

| Supply Voltage                | VDD-VSS    | 4.5 | 5.0 | 5.5 | ٧         |

| Ambient operating temperature |            | 0   | 25  | 70  | degrees C |

### **DC Characteristics**

| Parameter                 | Conditions      | Min | Nom | Max  | Units |

|---------------------------|-----------------|-----|-----|------|-------|

| Power supply current      |                 |     |     | 85   | mA    |

| Powerdown supply current  | PDN=Low         |     | 250 | 1000 | μА    |

| High level input voltage  | TLL inputs only | 2.0 |     |      | ٧     |

| Low level input voltage   | TTL inputs only |     |     | 0.8  | ٧     |

| High level output voltage | SDO, IOH=2mA    | 2.4 |     |      | ٧     |

| Low level output voltage  | SDO, IOL=3.2mA  |     |     | 0.4  | ٧     |

## **AC Characteristics**

(unless otherwise specified:  $f_{refclk}$ =39MHz, No boost,  $f_c = f_{refclk}/3$ )

| Parameter                                | Conditions                                                    | Min  | Nom | Max        | Units    |

|------------------------------------------|---------------------------------------------------------------|------|-----|------------|----------|

| Filter cutoff frequency (fc) range       |                                                               | 2    |     | 13         | MHz      |

| Filter cutoff frequency accuracy         |                                                               |      |     | ±10        | %        |

| Vout norm differential gain              | f = 0.1f <sub>C</sub>                                         | -1.5 |     | +1.5       | dB       |

| Vout diff differential gain              | f = 0.67f <sub>C</sub>                                        | -1.5 |     | +1.5       | dB       |

| Phase shift between norm and diff        | f = 0.67f <sub>C</sub>                                        | 87   | 90  | 93         | degrees  |

| Programmable boost range at fc           |                                                               | 0    |     | 10.6       | dB       |

| Boost accuracy                           |                                                               | -1   |     | 1          | dB       |

| Differential group delay without boost   | f <sub>C</sub> = 13MHz<br>f = 2 to 13MHz                      | -0.6 |     | 0.6        | nS       |

| Differential group delay with full boost | f <sub>C</sub> = 13MHz<br>f = 2 to 13MHz                      | -0.6 |     | 0.6        | nS       |

| Harmonic distortion                      | 2nd, 3rd harmonic<br>Vin,Vout < 1.0Vp-p<br>Vin,Vout < 1.5Vp-p |      |     | -40<br>-30 | dB<br>dB |

| Power supply rejection                   | VDD, 1MHz                                                     | 35   |     |            | dB       |

| Common mode rejection                    | 1MHz                                                          | 45   |     |            | d₿       |

| Output noise                             | Measurement BW= 30MHz                                         |      |     | 1.5        | mVRMS    |

| Filter output differential offset        | Norm and Diff                                                 |      |     | 100        | mV       |

| Filter input common-mode level           | V <sub>DD</sub> = 5V                                          | 2.0  | 2.1 | 2.2        | ٧        |

| Filter input resistance                  | Differential                                                  | 3    |     |            | kohms    |

| Filter input capacitance                 | C to VSS                                                      |      | 10  |            | pF       |

| Filter output common-mode                | V <sub>DD</sub> = 5V                                          | 1.5  |     | 2.5        | ν        |

| Resistive load on filter outputs         | Differential                                                  | 2    |     |            | kohms    |

| Capacitive load on filter outputs        | C to VSS                                                      |      |     | 25         | pF       |

| Tuning PLL lock capture time             | Full range of refctk<br>Change in refctk +/-50%               |      |     | 1.0<br>100 | mS<br>uS |

| Refolk feedthrough                       |                                                               |      |     | 0.5        | mVp-p    |

# **Input Timing Specifications**

| Parameter         | Conditions                      | Min | Max | Units |

|-------------------|---------------------------------|-----|-----|-------|

| T <sub>sui</sub>  | SLOAD setup time to SCLK        | 50  |     | nS    |

| T <sub>hot</sub>  | SLOAD hold time after SCLK      | 50  |     | nS    |

| T <sub>rc</sub>   | SCLK rise time                  |     | 10  | nS    |

| T <sub>fc</sub>   | SCLK fall time                  |     | 10  | nS    |

| T <sub>min</sub>  | SCLK high time and low time     | 100 |     | nS    |

| T <sub>sud</sub>  | SDI setup time to SCLK          | 50  |     | nS    |

| T <sub>hod</sub>  | SDI hold time after SCLK        | 50  |     | nS    |

| T <sub>suc</sub>  | SLOAD high to SCLK falling edge | 50  |     | nS    |

| T <sub>lmin</sub> | SLOAD high time                 |     | 100 | nS    |

| T <sub>clh</sub>  | REFCLK rise time                |     | 10  | nS    |

| T <sub>chi</sub>  | REFCLK fall time                |     | 10  | nS    |

| T <sub>ch</sub>   | REFCLK high time                | 5   |     | nS    |

| T <sub>cl</sub>   | REFCLK low time                 | 5   |     | пS    |

| T <sub>cyc</sub>  | REFCLK cycle time               | 20  |     | nS    |

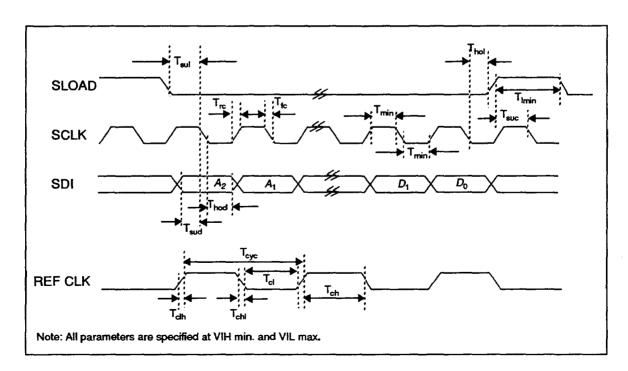

# **Timing Diagram**

### **Serial Interface Programming**

A simple 3 input serial interface is provided to program the filter coefficients. Data is shifted in 8-bit sequences. The 3 bit address (MSB first) is shifted in first, followed by 5 bits of data (MSB first). There are 8 internal register addresses. Data is clocked in on the falling edge of SCLK. Data is loaded to internal registers on the rising edge of SLOAD.

# **Register Programming (Write)**

|                | Data in          |       |                |       |                |                |                | Internal register      |

|----------------|------------------|-------|----------------|-------|----------------|----------------|----------------|------------------------|

| $\mathbf{d}_7$ | $\mathbf{d}_{6}$ | $d_5$ | $d_4$          | $d_3$ | $\mathbf{d}_2$ | d₁             | $\mathbf{d}_0$ | written                |

| 0              | 0                | 0     | X              | Х     | b <sub>2</sub> | b <sub>1</sub> | 0              | Control                |

| 0              | 0                | 1     | $b_4$          | $b_3$ | $b_2$          | b <sub>1</sub> | b <sub>0</sub> | ω <sub>za</sub>        |

| 0              | 1                | 0     | $b_4$          | $b_3$ | $b_2$          | b <sub>1</sub> | b <sub>0</sub> | ω <sub>zb</sub>        |

| 1              | 0                | 1     | b <sub>4</sub> | $b_3$ | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | ω <sub>c</sub> scaling |

| 1              | 1                | 0     | X              | Х     | Х              | X              | X              | Calibrate on demand    |

| 1              | 1                | 1     | X              | X     | b <sub>2</sub> | b <sub>1</sub> | $\mathbf{b_0}$ | Readback               |

Contents of the internal registers may be read back. A register is selected by placing the address of the register to be read in the data field.

During readback, 8-bits of data is shifted out the SDO pin on the falling edge of SCLK. SDO should be sampled on the rising edge of SCLK. Upon receiving a ninth clock pulse, the SDO output will go high impedance.

# **Register Programming (Readback)**

|                |                  |       | Dat   | a in           |                |                |                |                |                |                  | Dat            | a ou           | t              |                |                  | Internal register      |

|----------------|------------------|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|----------------|----------------|----------------|----------------|------------------|------------------------|

| $\mathbf{d}_7$ | $\mathbf{d}_{6}$ | $d_5$ | $d_4$ | $\mathbf{d}_3$ | $\mathbf{d}_2$ | $\mathbf{d}_1$ | d <sub>0</sub> | d <sub>7</sub> | d <sub>6</sub> | $\mathbf{d}_{5}$ | $\mathbf{d}_4$ | $\mathbf{d}_3$ | $\mathbf{d}_2$ | $d_1$          | $\mathbf{d}_{0}$ | bits read              |

| 1              | 1                | 1     | Х     | X              | 0              | 0              | 0              | 0              | 0              | 0                | 0              | 0              | b <sub>2</sub> | b <sub>1</sub> | 0                | Control                |

| 1              | 1                | 1     | X     | Х              | 0              | 0              | 1              | 0              | 0              | 1                | $b_4$          | b <sub>3</sub> | p <sup>5</sup> | b <sub>1</sub> | bo               | ω <sub>za</sub>        |

| 1              | 1                | 1     | X     | X              | 0              | 1              | 0              | 0              | 1              | 0                | $b_4$          | b <sub>3</sub> | $b_2$          | b <sub>1</sub> | bo               | ω <sub>zb</sub>        |

| 1              | 1                | 1     | Х     | X              | 1              | 0              | 1              | 1              | 0              | 1                | b <sub>4</sub> | bз             | b <sub>2</sub> | b <sub>1</sub> | bo               | ω <sub>c</sub> scaling |

#### Control

Register address = 000

Data:

$d_0 = 0$  Program to zero (power up state = 0)  $d_1 = 1$  Continuous calibration enabled (power up state = 1)  $d_2 = 0$  Power down mode enabled (power up state = 1)

If continuous calibration is disabled, then a single calibration cycle may be initiated by writing to the address = 110. Data bits are ignored. Calibration begins on the rising edge of SLOAD.

#### **Pulse Slimmer:**

$$\omega_{Z_a} = 0.65 \cdot \frac{20}{n_a} \cdot \omega_c$$

$n_a \in (0...20)$

#### Register address = 001

| d <sub>4</sub> | d <sub>3</sub> | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub> | n,  |

|----------------|----------------|----------------|----------------|----------------|-----|

| 0              | 0              | 0              | 0              | 0              | 0 * |

| 0              | 0              | 0              | 0              | 1              | 1   |

| ~              | ~              | ~              | ~              | ~              | ~   |

| 1              | 0              | 0              | 1              | 1              | 19  |

| 1              | 0              | 1              | 0              | 0              | 20  |

$$\omega_{z_b} = 0.65 \cdot \frac{20}{n_b} \cdot \omega_c \qquad n_b \in (0...20)$$

# Register address = 010

| Г | d <sub>4</sub> | d <sub>3</sub> | $d_2$ | d <sub>1</sub> | ďo | n <sub>b</sub> |

|---|----------------|----------------|-------|----------------|----|----------------|

| Г | 0              | 0              | 0     | 0              | 0  | 0 *            |

|   | 0              | 0              | 0     | 0              | 1  | 1              |

|   | ~              | ~              | ~     | ~              | ~  | ~              |

| ļ | 1              | 0              | 0     | 1              | 1  | 19             |

|   | 1              | 0              | 1     | 0              | 0  | 20             |

# **Symmetrical Boost:**

|                |                |                    | I                   |

|----------------|----------------|--------------------|---------------------|

| n <sub>a</sub> | n <sub>b</sub> | Boost <sup>1</sup> | დ <sub>3dB</sub>    |

| 0 *            | 0 •            | 0dB                | 1.00 ω <sub>c</sub> |

| 1              | 1              | 0.05dB             | 1.01 ω <sub>c</sub> |

| 2              | 2              | 0.20dB             | 1.03 თ <sub>c</sub> |

| 3              | 3              | 0.45dB             | 1.08 თ <sub>c</sub> |

| 4              | 4              | 0.79dB             | 1.15 ω <sub>c</sub> |

| 5              | 5              | 1,20dB             | 1.25 თ <sub>ი</sub> |

| 6              | 6              | 1.68dB             | 1.37 თ <sub>c</sub> |

| 7              | 7              | 2.21dB             | 1.52 ω <sub>c</sub> |

| 8              | 8              | 2.79dB             | 1.66 ω <sub>c</sub> |

| 9              | 9              | 3.40dB             | 1.81 ω <sub>c</sub> |

| 10             | 10             | 4.04dB             | 1.94 ω <sub>c</sub> |

| 11             | 11             | 4.69dB             | 2.06 ω <sub>c</sub> |

| 12             | 12             | 5.35dB             | 2.18 ω <sub>c</sub> |

| 13             | 13             | 6.02dB             | 2.29 თ <sub>ი</sub> |

| 14             | 14             | 6.69dB             | 2.39 თ <sub>c</sub> |

| 15             | 15             | 7.35dB             | 2.50 თ <sub>c</sub> |

| 16             | 16             | 8.01dB             | 2.59 თ <sub>c</sub> |

| 17             | 17             | 8.66dB             | 2.68 ω <sub>c</sub> |

| 18             | 18             | 9.30dB             | 2.77 ω <sub>c</sub> |

| 19             | 19             | 9.93dB             | 2.85 ω <sub>c</sub> |

| 20             | 20             | 10.54dB            | 2.94 ω <sub>c</sub> |

|                |                |                    | 2.85 ω <sub>c</sub> |

1. Boost measured at  $\omega_c$  relative to -3dB

\* Default state after powerup

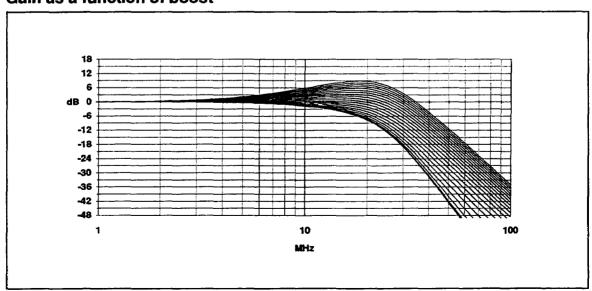

#### Gain as a function of boost

# Frequency Scaling:

$\omega_{\text{c}}$  is the lowpass filter 3dB cutoff

$$\omega_c \equiv 2\pi f_c = 2\pi \cdot \frac{2 \cdot f_{refclk}}{3} \cdot \frac{K}{i} \qquad i \in (1, 2, 3, 4)$$

$$K = \frac{7.17}{3.17 + n_K} \qquad n_K \in (0...7)$$

Register address = 101

#### Data:

| d₄ | <b>d</b> <sub>3</sub> | 1   |

|----|-----------------------|-----|

| 0  | 0                     | 1   |

| 0  | 1                     | 2 * |

| 1  | 0                     | 3   |

| 1  | 1                     | 4   |

| d <sub>2</sub> | d₁ | do | n <sub>K</sub> | K     |

|----------------|----|----|----------------|-------|

| 0              | 0  | 0  | 0              | 2.262 |

| 0              | 0  | 1  | 1              | 1.719 |

| 0              | 1  | 0  | 2              | 1.387 |

| 0              | 1  | 1  | 3              | 1.162 |

| 1              | 0  | 0  | 4 *            | 1.000 |

| 1              | 0  | 1  | 5              | 0.878 |

| 1              | 1  | 0  | 6              | 0.782 |

| 1              | 1  | 1  | 7              | 0.705 |

<sup>\*</sup> Default state after powerup

|        |   | MHz                                              |                                         |     |

|--------|---|--------------------------------------------------|-----------------------------------------|-----|

| 0.1    | 1 | 10                                               |                                         | 100 |

| o ——   |   |                                                  |                                         |     |

| 50     |   |                                                  |                                         |     |

|        |   |                                                  | *************************************** |     |

| 100    |   | <del>                                     </del> |                                         |     |

| 118.00 |   |                                                  |                                         |     |

| nS150  |   | \\                                               |                                         |     |

| 200    |   |                                                  |                                         |     |

|        |   |                                                  |                                         |     |

| 250    |   |                                                  |                                         |     |

# f<sub>cutoff</sub> Look-Up Table - Reg 101

| fc/Refclk | i | n | Binary  |

|-----------|---|---|---------|

| 0.118     | 4 | 7 | 11111   |

| 0.130     | 4 | 6 | 11110   |

| 0.146     | 4 | 5 | 11101   |

| 0.157     | 3 | 7 | 10111   |

| 0.167     | 4 | 4 | 11100   |

| 0.174     | 3 | 6 | 10110   |

| 0.194     | 4 | 3 | 11011   |

| 0.195     | 3 | 5 | 10101   |

| 0.222     | 3 | 4 | 10100   |

| 0.231     | 4 | 2 | 11010   |

| 0.235     | 2 | 7 | 01111   |

| 0.258     | 3 | 3 | 10011   |

| 0.261     | 2 | 6 | 01110   |

| 0.287     | 4 | 1 | 11001   |

| 0.293     | 2 | 5 | 01101   |

| 0.308     | 3 | 2 | 10010   |

| 0.333 *   | 2 | 4 | 01100 * |

| 0.377     | 4 | 0 | 11000   |

| 0.382     | 3 | 1 | 10001   |

| 0.387     | 2 | 3 | 01011   |

| 0.462     | 2 | 2 | 01010   |

| 0.470     | 1 | 7 | 00111   |

| 0.503     | 3 | 0 | 10000   |

| 0.521     | 1 | 6 | 00110   |

| 0.573     | 2 | 1 | 01001   |

| 0.585     | 1 | 5 | 00101   |

| 0.667     | 1 | 4 | 00100   |

| 0.754     | 2 | 0 | 01000   |

| 0.775     | 1 | 3 | 00011   |

| 0.925     | 1 | 2 | 00010   |

| 1.146     | 1 | 1 | 00001   |

| 1.508     | 1 | 0 | 00000   |

#### **Lowpass Characteristics**

$$H_{LOWPASS}(s) = \left(\frac{\omega_{p_1}^2}{\omega_{p_1}}\right) \left(\frac{\omega_{p_2}^2}{\omega_{p_2}}\right) \left(\frac{\omega_{p_2}^2}{\omega_{p_2}}\right) \left(\frac{\omega_{p_3}^2}{\omega_{p_3}}\right) \left(\frac{\omega_{p_3}^2}{\omega_{p_3}}\right)$$

| Biquad | ω <sub>p</sub> | Q <sub>p</sub> |

|--------|----------------|----------------|

| 1      | 1.607          | 0.510          |

| 2      | 1.692          | 0.611          |

| 3      | 1.908          | 1.023          |

Note:  $\omega_c$  normalized to 1 rad/sec

### **Application Information**

To allow the inputs to be AC coupled, the differential filter inputs are internally DC biased to the correct common mode voltage. Using  $0.1\mu$ Fcapacitors to couple the IN- and IN+ inputs is recommended.

Analog and digital supplies must be connected together at the point that they are decoupled.

### **Company Sales Offices**

#### U.S.A.

IMP (Corporate) 2830 North First Street San Jose, CA 95134 (408) 432 -9100 TLX: 499-1041 FAX: (408) 434-0335

IMP Eastern Headquarters 20F Robert Pitt Drive, Suite 203 Monsey, NY 10952 (914) 425-9108 FAX: (914) 425-9309

IMP Mid-Atlantic P.O.Box 292 Blue Bell, PA 19422 (215) 643-3473 FAX: (215) 643-3371

IMP Northwest 70 East Daggett Drive San Jose, CA 95134 (408) 432-9100 FAX: (408) 434-0335

IMP Southwest 1633 Oldcastle Place Westlake Village, CA 91361 (805) 495-2606 FAX: (805) 497-3932

#### **Europe**

Dialog Semiconductor Windmill Hill, Whitehill Way Swindon, Wiltshire SN5 9YZ England 011-44-793-875327 FAX: 011-44-793-875328

#### Far East

Hong Kong Arcon Electronics Company Unit 4, 21/P., Star Centre 443-451 Castle Peak Rd. Kwai Chung, New Territories Hong Kong 852-401-1341 FAX: 852-401-1342

Republic of China QuadRep Electronics (T) Ltd. 6F-2 No. 436, Nanking W. Road Taipei, Taiwan R.O.C. 011-886-2-552-2372 FAX: 011-886-2-552-5388

Singapore QuadRep Marketing (S) Pte Ltd. 5611 North Bridge Road Eng Cheong Tower #02-10 Singapore 0719 011-65-2949998 FAX: 011-65-2911213

#### **DISCLAIMER**

The information contained in this document is confidential and proprietary to International Microelectronic Products, Inc. ("IMP") and may not be copied or disclosed to a third party, in whole or in part, without the express written consent of IMP. The information contained herein is current as of the date of publication; however, delivery of this document shall not under any circumstances create any implication that the information contained berein is correct as of sny time subsequent to such date. [MP does not undertake to inform any recipient of this document of sny changes in the information contained herein, and IMP expressly steed the changes in such information, without notification, even if such changes would render information contained herin inaccurate or incomplete. The products listed herein may not be used as a component within any health care devices or systems without the prior written consent of IMP. IMP makes no representation or warrasty that (i) any circuit designed by reference to the information contained herein will function without errors and as intended by the designer or (ii) that the interconnection of its circuits with any other devices or circuits or the incorporation of such circuits within any devices or systems of third parties.