### UNIVAC CP-823/U MILITARY COMPUTER

### **CENTRAL PROCESSOR UNIT**

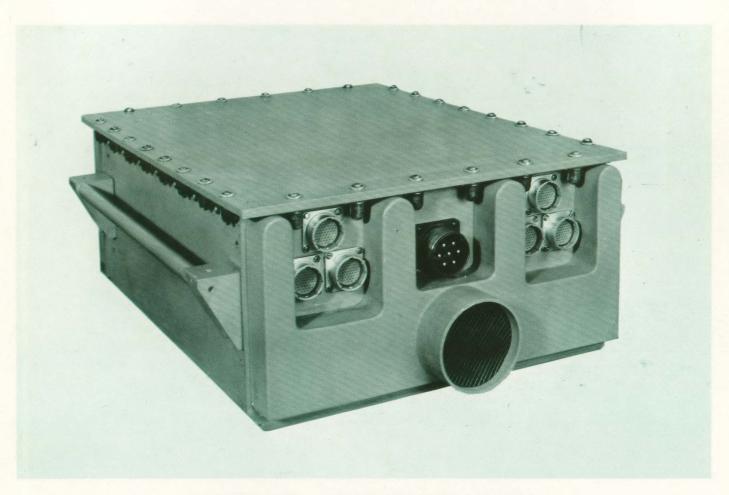

### PHYSICAL SIZE AND WEIGHT

Height: 7.25 inches

Width: 14.50 inches

Weight: 50 pounds

# UNIVAC CP-823/U MILITARY COMPUTER

### TECHNICAL DESCRIPTION

UNIVAC

DEFENSE SYSTEMS DIVISION

5316 W. IMPERIAL HWY.

LOS ANGELES, CALIF, 90045

678-2531

## CONTENTS

|    |                                                 | Page |

|----|-------------------------------------------------|------|

| 1. | INTRODUCTION                                    | 1    |

|    | Technical Characteristics                       | 2    |

|    | Applications                                    | 3    |

| 2. | FUNCTIONAL COMPUTER DESCRIPTION                 | 4    |

|    | General Organization                            | 4    |

|    | Central Processor                               | 4    |

|    | Memory                                          | 6    |

|    | Input/Output                                    | 7    |

|    | Power Supply                                    | 15   |

|    | UNIVAC CP-823/U Computer Control Ground Console | 16   |

| 3. | PHYSICAL CHARACTERISTICS AND ELECTRONICS        | 18   |

|    | General                                         | 18   |

|    | Microelectronics                                | 18   |

|    | Central Processor Construction                  | 21   |

|    | Input/Output Construction                       | 21   |

|    | Memory Unit Construction                        | 22   |

| 4. | INSTALLATION REQUIREMENTS                       | 23   |

| 5. | SOFTWARE                                        | 24   |

|    | Assemblers and Compilers                        | 24   |

|    | Compilers                                       | 25   |

|    | Debugging Aids                                  | 25   |

|    | Cornell Utility Package                         | 26   |

|    | Subroutine Library                              | 27   |

|    | APPENDIX A DEPENDINE OF INSTRUCTIONS            | Δ_1  |

## **ILLUSTRATIONS**

| Figure | Title                                                 | Page |

|--------|-------------------------------------------------------|------|

| 1.     | CP-823/U Computer—Block Diagram                       | 5    |

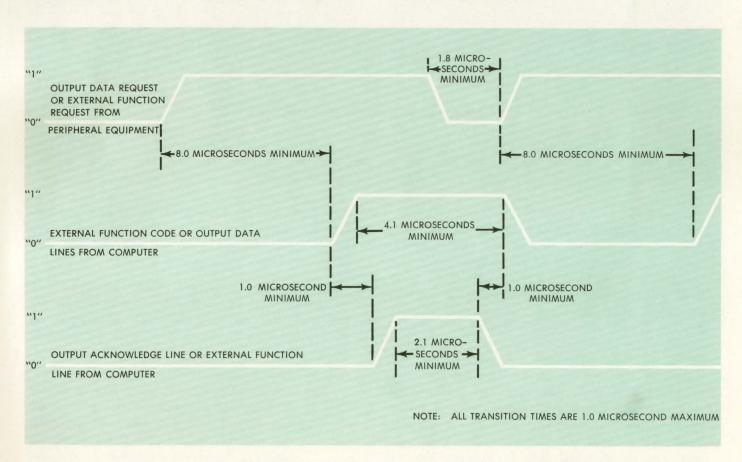

| 2.     | Data Transfer (Buffer Mode)                           | 8    |

| 3.     | External Function Code Transmission                   | 8    |

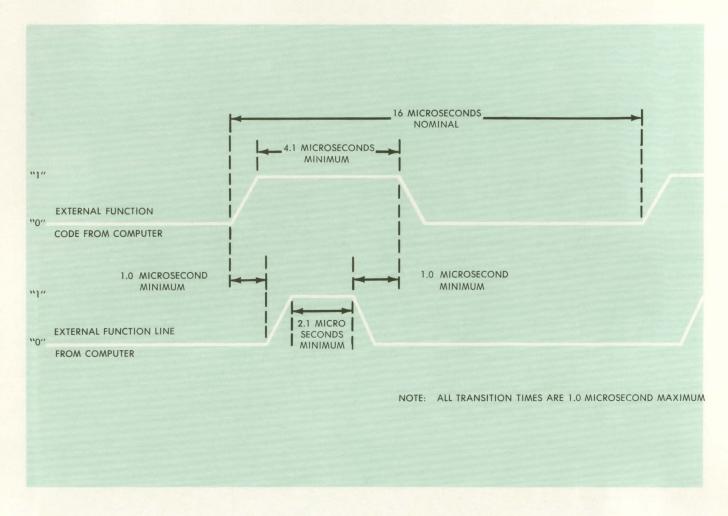

| 4.     | External Function Code Transmission with Force        | 8    |

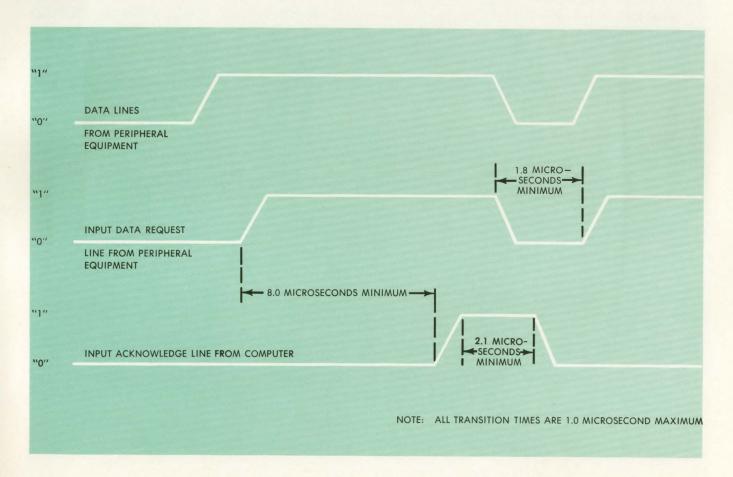

| 5.     | Input Data Transfer (Buffer Mode)                     | 9    |

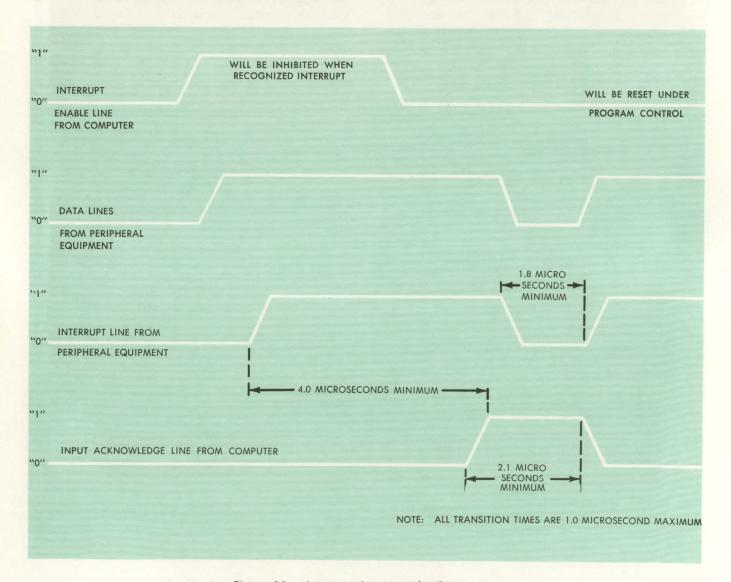

| 6.     | Interrupt Transmission                                | 9    |

| 7.     | Transmitting Command Word (Case 1)                    | 10   |

| 8.     | Transmitting Command Word by Force (Case 1)           | 10   |

| 9.     | Transfer of Data (Buffer Mode) Case 2                 | 10   |

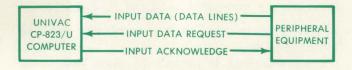

| 10.    | Computer Data Inputs from Peripheral Equipment        | 11   |

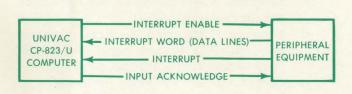

| 11.    | Interrupt Inputs to the Computer                      | 12   |

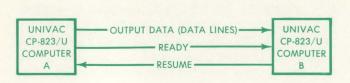

| 12.    | Data Outputs and External Functions from the Computer | 13   |

| 13.    | External Function with Force                          | 14   |

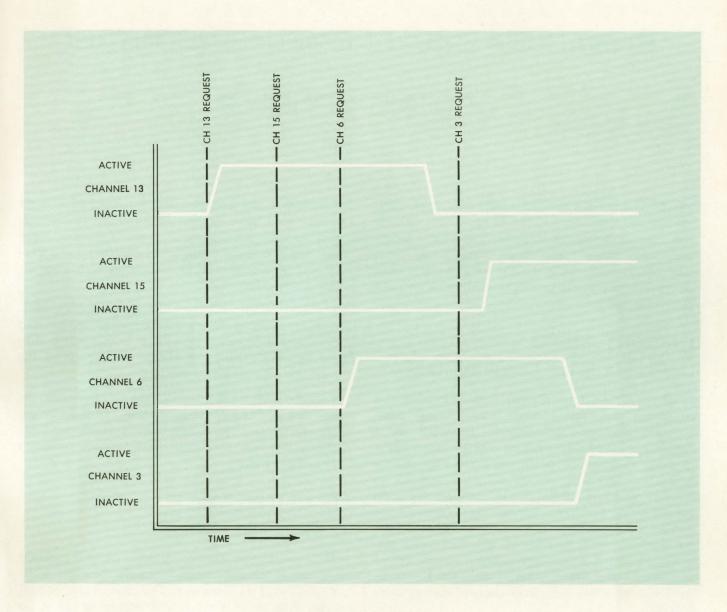

| 14.    | Channel Priority                                      | 15   |

| 15 A.  | UNIVAC 1232A Input/Output Console                     | 17   |

| 15B.   | Maintenance/Control Console                           | 17   |

| 16.    | Basic Logic Circuit Packages                          | 18   |

| 17.    | Schematic—Integrated Logic Element                    | 18   |

| 18.    | Integrated Circuit Cutaway                            | 19   |

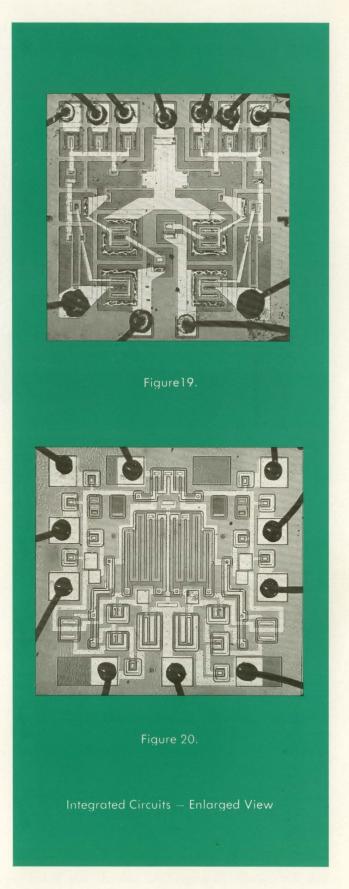

| 19.    | Integrated Circuit—Enlarged View                      | 19   |

| 20.    | Integrated Circuit—Enlarged View                      | 19   |

| 21.    | Computer Logic Module                                 | 20   |

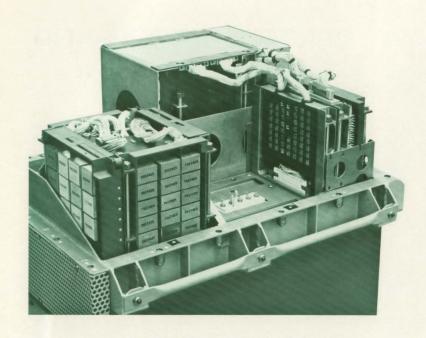

| 22.    | Central Processor                                     | 21   |

| 23.    | Central Processor—Inside View                         | 21   |

| 24.    | Memory Unit                                           | 22   |

|        |                                                       |      |

## **TABLES**

| Table | Title                                                                | Page |

|-------|----------------------------------------------------------------------|------|

| 1.    | Input/Output Channel Control Signals                                 | 7    |

| 2.    | Input/Output Channel Control Signals for Intercomputer Communication | 9    |

| 3.    | Summary of Equipment Characteristics                                 | 23   |

### INTRODUCTION

The UNIVAC CP-823/U\* Digital Computer is a miniaturized, real-time, general-purpose, stored-program computer with performance characteristics which exceed those of many large-scale ground machines. Because of the utilization of solid-state microelectronic circuitry, the CP-823/U is an ultra-reliable device well suited for applications which impose severe volume and weight limitations with a minimum power consumption. The CP-823/U computer was constructed in compliance with the exacting standards of MIL-E-5400F.

The concept of modularity, as it is featured in the computer, allows a selection of memory and input/output capacity as required for the application. Form factor flexibility is achieved by separately packaging the central processor unit, memory unit, power supply units, and the input/output units.

The computer memory unit consists of ferrite core modular arrays, each containing 4096 30-bit words. In addition, a 4096 30-bit word magnetic thin-film array is available when nondestructive readout is required. The memory unit may contain from one array to eight arrays to give a memory capacity of 4096 words (minimum) to 32,768 words (maximum). Current memory unit design provides for a mem-

ory composed of all ferrite core arrays or one thinfilm array and up to seven ferrite core arrays. Cycle times for the core memory and read time for the film memory are four microseconds.

One of the most powerful and most flexible features of the CP-823/U computer is its input/output capability. Input/output to the central processor is provided over four input and four output channels and their associated control circuits. Each channel to the central processor may be further multiplexed into four additional channels by the use of a separately packaged input/output multiplexer unit. Present multiplexer units are designed and packaged to interface four input and four output channels with one of the four input channels and one of the four output channels to the central processor. By interconnecting four input/output units to the central processor, a total of 16 input and 16 output channels can be obtained.

Since the repertoire of instructions is identical with that of other UNIVAC computers, an entire library of programs is readily available. Not the least of the computer's attractions, however, is the direct compatibility with a wide range of existing peripheral equipment.

<sup>\*</sup>CP-823/U is the military nomenclature for the UNIVAC 1830 Avionics Computer.

### TECHNICAL CHARACTERISTICS

### TYPF

TYPE: General-purpose, large-scale, real-time, mi-

croelectronic, parallel-binary.

### MEMORY

Core Memory (DRO): Array of 4096-word, 30 bits magnetic core storage

Cycle Time: 4 microseconds

4096, 8192, 12,288, 16,384, 20,-Capacity:

480, 24,576, 28,672, 32,768 30-bit

words

Magnetic Thin-film Memory (NDRO): Array of

4096-word, thin-film storage Cycle Time: 4 microseconds

### INPUT/OUTPUT

### MICROELECTRONIC MULTIPLEXER

Simplex, 30-bit parallel Type:

(Logical "0" is +3.0 volts, +1,

-0.5)

(Logical "1" is 0.0 volt  $\pm 0.5$ )

16 channels of input/output maxi-Number:

mum, in modules of four

Transfer: Output or input

One output or input channel— Rate:

62,000 words per second, maxi-

mum.

Multi-channel—125,000 words per

second

Features: Full buffer and/or real-time

control on each channel

Intercomputer communication with any or all channels

External commands

Internal interrupt capabilities from buffer monitors on each channel

Channel "active" test

### CONTROL

Command Structure:

Single address, 62 instructions, seven index registers, seven branch designators, and seven operand in-

terpretation designators

Instruction Execution Time

Add: 8 microseconds Subtract: 8 microseconds Multiply: 32-48 microseconds

Divide/Square

Root: 48 microseconds Shift: 8-12 microseconds Jump: 8 microseconds

Real-Time Clock:

Automatic internal clock controlled by main timing. Provision is made for the use of an external real-time

clock source.

### CONSTRUCTION

Modular Construction

Semiconductor Microelectronic Integrated Cir-

### PRIMARY POWER REQUIREMENTS

Voltage:

200 Volts line to line

Phase:

Frequency:

400 cycles

Power:

830 Watts (32,768 words of memory, 16 channels input/output)

### APPLICABLE MILITARY

MIL-E-5400F

**SPECIFICATIONS**

MIL-STD-704

### **APPLICATIONS**

Because the UNIVAC CP-823/U Computer is a flexible, general-purpose computer, it can be used in many challenging real-time and nonreal-time applications requiring high capability, ruggedness, small physical size and weight, and extreme reliability. A list of applications would include the following:

- ASW Systems

- Airborne Command and Control

- Airborne Navigation

- Fire Control

- Battle Field Command and Control

- Missile Command, Control, and Launch

- Radar Data Processing

- Shipboard Systems, Surface and Subsurface

# FUNCTIONAL COMPUTER DESCRIPTION

### GENERAL ORGANIZATION

The CP-823/U computer is composed of three principal units:

- Central Processor—The control section interprets the instructions, carries out the commands, furnishes the timing, and directs the sequence of events for logical execution of programs. The arithmetic section performs the arithmetic and logic functions as directed by the control section.

- Memory—Provides random access storage of up to 32,768 30-bit words.

- Power Supply—provides regulated d-c power to operate the computer. Power supply units can be provided to match a variety of input and output power requirements.

Optional input/output units are available to interface with the computer through the four input and four output channels provided in the central processor.

### CENTRAL PROCESSOR

The control section contains the circuitry necessary to procure, modify, and execute the single address instructions stored in the memory of the computer, and controls all arithmetic, logical, and sequential operations of the computer except those assigned to the input/output section. In addition, the control section regulates transmission into and out of storage and input and output according to the program of instructions

There are 62 basic instructions that may be used: each instruction contains a function code (f-6 bits), an instruction operand designator (y-15 bits), and three execution modifiers (j, k, b - 2, 3, or 4 bits). Execution modifiers provide for address incrementation, operand interpretation, branch-point designation, or input/output channel function. The operand designator may be increased by the amount contained in any one of seven index registers. The operand specified by the execution address may be interpreted as a 30-bit quantity or as a 15-bit upper or lower half-word with or without sign extension. The next sequential program step may be skipped unconditionally or when the branch-point designator places the skip under control of the contents of either the accumulator or the Q-register. (See Appendix A for a complete explanation of the instructions and their modifiers.)

The arithmetic section of the computer performs the

operations of addition, subtraction, multiplication, division, shifting, comparison, and parity check. Arithmetic and logical operations are performed in the parallel binary mode. For most operations, the result appears in a 30-bit accumulator register. Arithmetic is one's complement subtractive, with a modulus (2<sup>30</sup>-1).

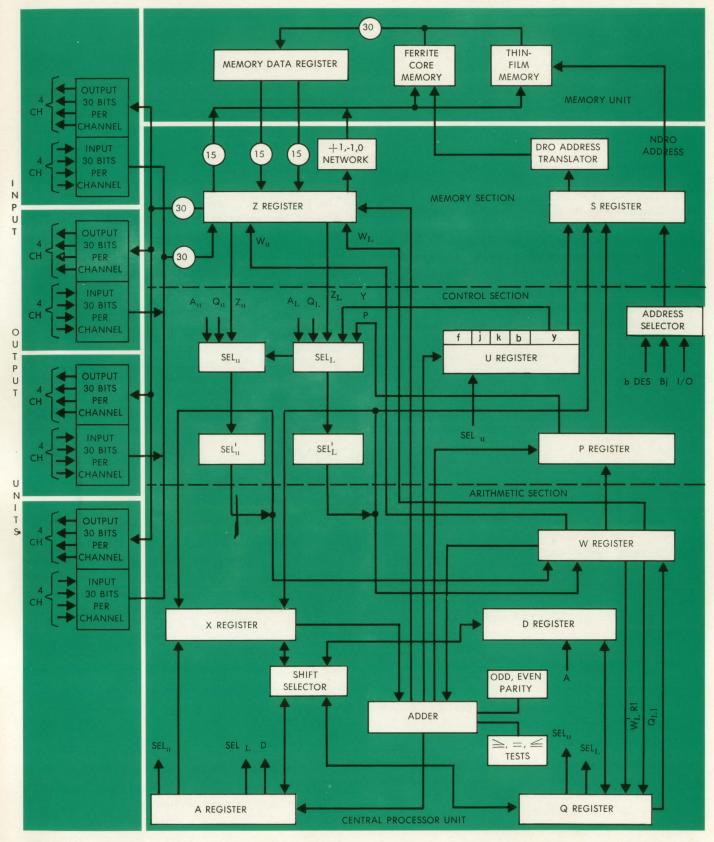

Below is a description of the *control* section registers which are used for computer control and the *arithmetic* section registers used for numerical and logical calculations. (See Figure 1, Block Diagram of the Computer.)

The U-register or program control register is a 30-bit register that holds the instruction word during the execution of an operation. The function code and the various instruction designators are translated from the appropriate sections of this register. If an address modification is required before execution, the contents of the appropriate B-register are added to the lower order 15-bits of the U-register. The lower order 15-bits of the U-register may also be used directly as data, modulus  $2^{15}$ -1.

The 15-bit registers,  $B_1$  through  $B_7$ , store the quantities used for  $U_L$  modification. These B-registers, also called index registers, occupy the lower 15 bits of core memory addresses 161 through 167.

NOTE: Units enclosed within double lines are separately packaged.

Figure 1. CP-823/U Computer — Block Diagram with Full 16 Channels Input and 16 Channels Output

The P-register (15 bits) holds the memory address of a computer instruction word—that of the next instruction to be executed.

The K-registers  $(K_1, K_2, K_3)$  function as a shift counter for all arithmetic operations that involve shifts. Some instructions employing the K-registers are multiply, divide, and square root.

The A-register (30 bits) may be thought of, for programming purposes, as a conventional accumulator. Because of the logic employed, however, the A-register is actually only the main rank of the accumulator; the W-register serves as a second rank. The add operation is typical of the relationship between the A-and W-registers: the augend and addend are initially contained in the A- and W-registers respectively. Before the addition is performed, the contents of the A-register are transmitted to the X-register. The values of X and W are combined by the add network to form the sum of the two numbers in a parallel manner and then placed in the A-register.

The Q-register (30-bits) is used principally during multiply and divide operations. The contents of

both A and Q may be shifted left or right, either individually or as one double-length, 60-bit word. The A- and Q-registers are addressable arithmetic registers.

The X-, D-, and W-registers are 30-bit, nonaddressable registers. These registers are used primarily for the exchange of data within the *arithmetic* section and for communicating with the remaining sections of the computer.

The selector is a logic network that controls transmissions to the *arithmetic* section and is used to place data in the various registers during control sequences. When data is read from memory or written into memory by execution of an instruction, the selector will translate the data read or stored based upon the k designator (see Appendix A for k designator usage). For arithmetic operations, the selector loads the Wregister with data or its complement to satisfy the requirements of the subtractive arithmetic logic. The upper 15 bits of the U-register (U<sub>u</sub>) are loaded directly from the selector as is the S-register for certain input/output operations.

### **MEMORY**

The *memory* unit consists of up to eight memory modules, each module containing 4096 words. Two module types—one a nondestructive readout (NDRO) memory module and one a ferrite core destructive readout (DRO) module—may be used in combinations, which offer unusual flexibility when selecting the type and amount of memory for a specific application.

This discussion of the *memory* unit will include the Z-register, S-register and translator, data control circuits, and timing control circuits. The Z-register, S-register, and translator are physically part of the central processor, but are discussed in the *memory* section because they are most closely associated with it.

Each memory unit allows high-speed random access to 4096 words of storage with a cycle time of four microseconds for DRO memory and a 4-microsecond read time for NDRO. Every storage location (DRO and NDRO) is assigned a separate address (00000<sub>8</sub> through 77777<sub>8</sub>), and each word in storage consists of 30 bits that can be divided into two 15-bit words: the

upper 15 bits (M<sub>U</sub>) and the lower 15 bits (M<sub>L</sub>).

By means of programming and the use of the k designator, each 15-bit word can be handled separately. When reading an address, the whole 30-bit word is read into the Z-register (for core memory, Z is then written back to replace the data) and the selector, as defined by k, will control the transmission of the whole word (Z upper\* [Z<sub>u</sub>] and Z lower\* [Z<sub>L</sub>]) or half word (Zu or ZL) transmission to X or W. When storing half words into memory, only the half word of the DRO storage address that is not to be changed is read into Z from memory. The half word to be stored is transferred from W to Z and the whole word of Z is restored in core. (Example: Store  $A_L$  in  $M_U$ :  $A_L \longrightarrow SEL_L, SEL_L \longrightarrow SEL_u, SEL_u \longrightarrow W_u, M_L \longrightarrow$  $Z_L$ , and  $W_u \longrightarrow Z_u$ ;  $Z \longrightarrow$  storage address). If a whole word is to be stored, computer control inhibits retaining the output of the read portion of the memory cycle and stores the data on the write half of the cycle.

When a specific storage location in memory is referenced, the S-register contains a 15-bit address word

<sup>\*</sup>Z<sub>u</sub> is used to denote the upper 15 bits, and Z<sub>L</sub> is used to denote the lower 15 bits.

that specifies one of the 32,768 storage locations. The *control* and *input/output* sections of the computer have independent access to the storage registers through the use of the S-register and translator, the Z-register, and the memory timing sequence.

The Z-register holds the information to be read out or written into the *memory* unit. Data is normally transferred from the *input/output* section, and the W-regis-

ter to the Z-register for storage in *memory*. Information read from memory is outputted from the Z-register to the *input/output* section, and to the various computer registers through the selector.

The address selector performs the task of translating designator I/O buffer requests and interrupt requests into the proper control word memory address location. After translation, the memory address is placed in S to allow the control word to be read from memory.

### INPUT/OUTPUT

The input/output capabilities of the UNIVAC CP-823/U Computer will allow a variety of input/output units to be utilized. The microelectronic multiplexers have a maximum of 16 input and 16 output channels, each comprised of 30 bits, which provides for a maximum data transfer rate of 125,000 30-bit words per second. Each channel is equipped with four control lines to allow maximum reliable data transfer without monitoring or intervention from the central computer. Packaged modularly, each input/output unit contains four input and four output channels with associated control lines. Table 1 illustrates the control signals associated

with each input/output channel, and the technical discussion that follows is based upon its characteristics.

Through the use of an input/output buffer mode of operation, the CP-823/U has the capability of communicating with peripheral equipment on any and all input/output channels concurrently with the operating program. Buffering operation, once initiated by a programmed instruction, proceed to termination asynchronously with the program.

The CP-642 compatible input/output unit enables direct interfacing with existing peripheral equipments. A list of compatible equipment includes the following:

TABLE 1. INPUT/OUTPUT CHANNEL CONTROL SIGNALS

| FUNCTION                                                                           | SIGNAL ORIGIN                                                      |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| INTERRUPT ENABLE INTERRUPT INPUT DATA REQUEST INPUT ACKNOWLEDGE                    | COMPUTER PERIPHERAL PERIPHERAL COMPUTER COMPUTER COMPUTER COMPUTER |

| EXTERNAL FUNCTION REQUEST EXTERNAL FUNCTION OUTPUT DATA REQUEST OUTPUT ACKNOWLEDGE | PERIPHERAL COMPUTER OUTPUT CHANNEL CONTROL LINES                   |

- Data Links

- Magnetic Tape Units

- Paper Tape (Punch and Flex) Units

- High-Speed Printers

- Video Processors

- Keyset Systems

- Displays

- Teletypewriting Equipment

- Magnetic Drums

- Disc Files

- Punch Card Equipment

- Plotter

- Analog-to-Digital and Digital-to-Analog Converters.

Other input/output units can be provided for special analog or digital applications.

### SEQUENCE OF EVENTS

Normal output sequence for data transfer from computer to peripheral equipment (buffer mode) is as follows:

- a. Computer initiates output buffer for given channel;

- Peripheral equipment sets the Output Data Request line indicating that it is in a condition to accept data;

- c. Computer detects Output Data Request;

- d. Computer, at its convenience, places data on the 30 data lines;

- Computer sets the Output Acknowledge line, indicating that the data is ready for sampling;

- f. Peripheral equipment detects the Output Acknowledge;

- Peripheral equipment may drop the Output Data Request any time after detecting the Output Acknowledge;

- h. Peripheral equipment samples the 30 data lines;

- Computer drops the Output Acknowledge and data lines.

Steps b through i of this sequence are repeated for every data word until the number of words specified in the output buffer have been transferred. Figure 2 shows the sequence for data transfer from computer to peripheral equipment.

The sequence for transmitting an External Function code from computer to peripheral equipment is as follows:

- Peripheral equipment sets the External Function Request line when it is ready to accept an External Function word;

- b. Computer detects the External Function Request;

- c. Computer places the External Function word on the data lines (if its External Function buffer is active);

- d. Computer sets the External Function line to indicate that the External Function word is ready for sampling;

- The External Function clears the External Function Request at the peripheral equipment;

- f. Peripheral equipment samples the External Function word;

- g. Computer drops the External Function line and the External Function word.

This sequence is repeated when the peripheral equipment is ready to accept another External Function word (see Figure 3).

It is possible for the computer to send External Function commands to peripheral equipment without receiving an External Function Request signal. This operation is called External Function with force generation and is shown in Figure 4.

The computer places the External Function code on the 30 output data lines, and a minimum of 1.0 microsecond later energizes the External Function line. The External Function signal indicates to the peripheral equipment that an External Function word, which should now be sampled, is present on the data lines.

The peripheral equipment has no control over the rate at which External Functions with Force are sent. If the rate is too fast so that the peripheral equipments cannot accept External Functions, restrictions must

Figure 2. Data Transfer (Buffer Mode)

Figure 3. External Function Code Transmission

Figure 4. External Function Code Transmission with Force

be made in the programming of External Function instructions to the equipment. It should be noted that if the peripheral equipments have no provision for sending an External Function Request signal, all External Functions to existing peripheral equipment must be sent as External Function with Force.

Normal input sequence for data transfer to computer from peripheral equipment (buffer mode) is as follows:

- a. Computer initiates input buffer for given channel;

- b. Peripheral equipment places data on the 30 data lines;

- Peripheral equipment sets the Input Data Request line to indicate that it has data ready for transmission;

Figure 5. Input Data Transfer (Buffer Mode)

Figure 6. Interrupt Transmission

TABLE 2. INPUT/OUTPUT CHANNEL CONTROL SIGNALS FOR INTERCOMPUTER COMMUNICATION

| FUNCTION                                                        | LINES                                 |

|-----------------------------------------------------------------|---------------------------------------|

| INTERRUPT ENABLE INTERRUPT INPUT DATA REQUEST INPUT ACKNOWLEDGE | COMPUTER INPUT CHANNEL CONTROL LINES  |

| EXTERNAL FUNCTION REQUEST EXTERNAL FUNCTION READY RESUME        | COMPUTER OUTPUT CHANNEL CONTROL LINES |

- d. Computer detects the Input Data Request;

- e. Computer samples the 30 data lines, at its convenience;

- f. Computer sets the Input Acknowledge line, indicating that it has sampled the data;

- g. Peripheral equipment senses the Input Acknowledge line;

- h. Peripheral equipment drops the data lines and the Input Data Request line.

Steps b through h of this sequence are repeated for every data word until the number of words specified in the input buffer have been transferred. Figure 5 shows the input data transfer to computer from peripheral equipment.

The sequence for transmitting an Interrupt from peripheral equipment to the computer is as follows:

- a. Computer sets the Interrupt Enable when it is ready to accept an External Interrupt;

- b. Peripheral equipment detects the Interrupt Enable;

- c. Peripheral equipment places the Interrupt word on the 30 data lines;

- d. Peripheral equipment sets the Interrupt line to indicate that the External Interrupt word is on the data lines;

- e. Computer detects the Interrupt signal, and at its convenience, accepts the Interrupt word;

- f. Computer drops the Interrupt Enable and sets the Input Acknowledge line;

- g. Peripheral equipment detects the drop of the Interrupt Enable and clears the Interrupt line and data lines.

The Input Acknowledge of an interrupt will be initiated simultaneously with the clearing of the Interrupt Enable. The simultaneous occurrence of these conditions is used by peripheral equipment to differentiate between an Interrupt Acknowledge and a Data Acknowledge. An interrupt transfer is illustrated in Figure 6.

## COMPUTER-TO-COMPUTER INTERFACE

It is possible for the CP-823/U computer to communicate with up to 16 other computers by converting any or all of the input/output channels. The control signals for intercomputer communication are shown in Table 2. Two cases of intercomputer communication are discussed. In both cases, computer A is transmitting to computer B.

In case 1 where computer A is transmitting a command word, the following occurs:

- Computer B sets the Interrupt Enable when it is ready to accept a command word from computer A;

- b. Computer A recognizes the Interrupt Enable as an External Function Request and places the External Function word on the data lines;

- Computer A sets the External Function to indicate that the External Function word is on the data lines;

Figure 7. Transmitting Command Word (Case 1)

Figure 8. Transmitting Command Word by Force (Case 1)

Figure 9. Transfer of Data (Buffer Mode) -Case 2

- d. Computer B recognizes the External Function as an Interrupt and accepts the command word;

- e. Computer B clears the Interrupt Enable line and sets the Input Acknowledge line;

- f. Computer A recognizes the Input Acknowledge as a Resume and clears the External Function line.

In the event computer A sets the External Function line while the Interrupt Enable line is cleared (this is possible when an External Function with Force instruction is used), all communications on the associated group of output channels in A are suspended until computer B acknowledges receipt of the External Interrupt or until an intercomputer time-out interrupt in A permits A to resolve the problem. (See Figure 7.)

If either computer A or B is not designed for External Function Requests or Interrupt Enables, then all External Functions are transferred by force, and interrupts are transferred as shown in Figure 8.

In Case 2 where computer A is transferring data, the following occurs:

- a. Computer B initiates an input buffer and computer A initiates an output buffer for the required channel;

- b. Computer A places data on the data lines;

- c. Computer A sets the Ready line to indicate that the data is on the line;

- d. Computer B recognizes the Ready signal as an Input Data Request signal and, at its convenience, accepts the data word;

- e. Computer B sets the Input Acknowledge;

- f. Computer A recognizes the Input Acknowledge as a Resume signal and clears the Ready (Input Data Request) line and the data lines;

- g. Repeat steps b through f for each word specified in the buffer. (See Figure 9.)

### TIMING

Two types of input/output modules are available for the CP-823/U computer. One type matches the computer with existing peripheral equipments and utilizes a -15-volt interface. The other type of input/output unit uses a +4-volt interface.

Because both units operate in a similar manner, the following discussion covers only the microelectronic input/output unit.

### INPUT TIMING CONSIDERATIONS

### Data Input

The Input Data Request signal indicates to the computer that data has been placed on the 30 Input Data lines. To ensure that the data will be accepted, the Input Data Request must be maintained on the lines until an answering Input Acknowledge is received. As shown in Figure 10, there is an 8-microsecond minimum delay between the setting of the Input Data Request and its answering Input Acknowledge. There is no maximum limit stated for the delay since its value for any particular cycle is determined by the interaction with the computer program and the other input/output channels. The data lines must remain stable as long as the Input Data Request is set.

The Input Acknowledge indicates to peripheral equipment that the computer has sampled the 30 data lines. The Input Acknowledge signal is set for a fixed time interval. Peripheral equipment must be capable of detecting, as an Input Acknowledge, a signal which

may exist in the stable "1" state for as little as 2.1 microseconds. The Input Data Request line and data lines may be dropped to the "O" state any time after detecting the Input Acknowledge. The Input Data Request cannot be reset immediately to indicate readiness of a second data word because the computer will not recognize the second Input Data Request unless a minimum time delay of 1.8 microseconds is allowed between the start of the dropping of the first Input Data Request and the start of the setting of the second Input Data Request. Timing would allow a peripheral equipment requiring a maximum data transmission rate to set the Input Data Request legitimately to the "1" state for the second time before the first Input Acknowledge has dropped to the "O" state. This will not affect operation of the cycle, however, since an 8-microsecond minimum delay will again be required between the setting of the second Input Data Request and the setting of the second Input Acknowledge.

Figure 10. Computer Data Inputs from Peripheral Equipment

### Interrupt Inputs to the Computer

The Interrupt line indicates to the computer that the peripheral equipment has placed data on the 30 data lines. The computer then accepts the Interrupt word at its convenience. Simultaneously, the computer drops

the Interrupt Request and sets the Input Acknowledge. Peripheral equipment can now drop the Interrupt signal and the Interrupt word. Data lines must remain stable as long as the Interrupt line is in the "set" condition. Figure 11 shows Interrupts to the computer.

### **OUTPUT TIMING CONSIDERATIONS**

### Data Output and External Functions

Peripheral equipment must first set the Output Request line or External Function Request line indicating that it is in a condition to accept a data or External Function word from the computer. Data lines will not necessarily be cleared to the "O" state before being reset to the "1" state. Minimum time interval between the Output or External Function Re-

quest signal and the placement of answering data on the lines is 8 microseconds. Maximum time interval depends upon the computer program, the priority of the particular channel, and the data request rates of the other peripheral equipment.

The Output Acknowledge or External Function signal indicates to the peripheral equipment that the re-

Figure 11. Interrupt Inputs to the Computer

quested word is now present on the data lines and that the lines should now be sampled. As shown in Figure 12, the Output Acknowledge or External Function signal will be sent a minimum of 1 microsecond after the data has been placed on the lines. The peripheral equipment must be capable of recognizing, as an Output Acknowledge or an External Function, a signal which may exist in the stable "1" state for as short a time as 2.1 microseconds.

The Output or External Function Request may be dropped to the "O" state any time after detecting the Output Acknowledge or the External Function. The Output or External Function Request cannot be reset immediately to indicate readiness of the peripheral equipment to accept a second word because the computer will not recognize the second Output or External Function Request unless a minimum time delay of 1.8 microseconds is allowed between the start of the dropping of the first Output or External Function Request and the start of the setting of the second Output or External Function Request. The timing would allow any peripheral equipment that wishes to receive data from the computer at a maximum rate to set legitimately the Output or

External Function Request to the "1" state for the second time before the first Output Acknowledge or External Function has dropped to the "O" state. However, this will not affect operation of the cycle since an 8-microsecond minimum delay will again exist between the setting of the second Output or External Function Request and the availability of the data on the data lines.

### External Functions with Force

External Functions with Force are unique since no request is sent by the peripheral equipment. The computer places the External Function code on the 30 output data lines and a minimum of 1.0 microsecond later energizes the External Function line. The External Function signal indicates to the peripheral equipment that an External Function word is present on the data lines. The External Function line will remain in the stable "1" state for an interval which may be as short as 2.1 microseconds. The External Function word will remain on the data lines for a minimum of 1.0 microsecond after the External Function signal begins to drop. Figure 13 is an External Function with Force timing diagram.

Figure 12. Data Outputs and External Functions from the Computer

Figure 13. External Function with Force

### Channel Priority

The channel priority will be such that the higher the numerical value of the channel, the greater its priority. Therefore, in order of descending priority, the channels are (15, 14, 13, 12) (11, 10, 9, 8) (7, 6, 5, 4) (3, 2, 1, and 0). Parentheses indicate the channel groups. Each group interfaces with a separate input/output unit. However, if a channel in a group is already active when a request occurs on another channel in the same group, this requesting channel may not be serviced next if a channel in a different group requests control at the same time. This priority method provides maximum I/O transfer rates. The computer requires 8 microseconds to service a single request from an input/output unit, but the input/output unit requires additional time to complete the data transfer. Therefore, rather than waiting for the input/output unit to accomplish the transfer and taking the next highest priority channel request in a group, the computer may service lower priority channels in other units as shown in Figure 14.

The previous discussion dealt with the microelectronic input/output unit. The larger CP-642 compatible input/output unit, designed to be used with existing peripheral equipments, is similar in operation with the following exceptions:

- Timing considerations are generally slower;

- The Interrupt Request signal may be deleted if the peripheral equipment does not have the capability of sensing it. The interrupt operation proceeds as in Figure 6, using only the Interrupt line, Input Acknowledge line, and Data lines.

Figure 14. Channel Priority

### POWER SUPPLY

Two power supply units are furnished with the CP-823/U computer: One furnishes power to the Central Processor and Memory Units, while the second furnishes power to from one to four input/output units.

Input power requirements vary depending upon computer configuration, but both power supplies operate from a 400-CPS, 3-phase, 200-volt, line-to-line source

or a 400-CPS, 3-phase, 115-volt, line-to-line source. Both power supplies have been designed for d-c output voltages, at  $\pm$  5 percent, when the input power source conforms to MIL Standard 704. Power supply units can also be provided which operate on 60-cycle or 28 volt d-c service. The over-all efficiency of each power supply is greater than 75 percent at maximum input and maximum load conditions.

# UNIVAC CP-823/U COMPUTER CONTROL

### GROUND CONSOLE

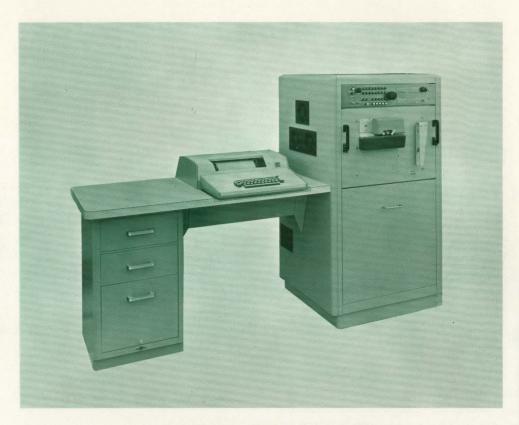

The UNIVAC CP-823/U Computer Ground Console contains the UNIVAC 1232A Input/Output Console and a maintenance/control panel. The 1232A Input/Output Console will provide the capability of paper tape input/output, while the control panel will allow an operator to perform various functions with the computer (Figure 15A).

### UNIVAC 1232A INPUT/OUTPUT CONSOLE

UNIVAC 1232A Input/Output Console consists of a paper tape perforator, paper tape reader, page printer\*, and alphanumeric keyboard\* assembled into a compact unit which operates on a single input/output channel. Programs or program modification may be loaded by the reader on punched paper tape (5- to 8-level) prepared off-line under computer program control by the perforator. Alphanumeric entries to the computer may be made at the keyboard with or without printout. The page printer is also useful as a program monitoring device in providing a running record of real-time and normal program activities. It may be used with all UNIVAC general-purpose military computers.

### **FUNCTIONAL DESCRIPTION**

The UNIVAC 1232A Input/Output Console operates under the control of the computer program. It accepts instructions from the computer program for any function or combination of functions assigned to it. The control circuitry translates the function word to initiate the proper mechanical and electronic response and executes the operations designated. Data are transferred in 6-bit frames from the alphanumeric

keyboard to the computer and are accepted in 6-bit frames from the computer for output on the printer. Five to 8-bit frames may be used with the paper tape reader and the paper tape perforator, and operations may be performed simultaneously with other input or output functions.

The control circuitry supplies the necessary communication signals required between the console and the computer to complete an input/output buffer without program attention. Keyboard interruption of the computer program is also provided.

The UNIVAC 1232A Input/Output Console may be operated off-line to print information, to perforate paper tape, or to perform both tasks simultaneously. The information may be entered from the tape reader or from the keyboard.

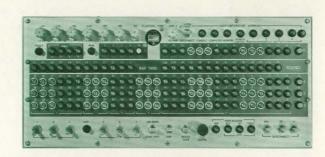

### MAINTENANCE CONTROL PANEL

The maintenance/control panel, on the ground console, is the man-computer interface for the UNI-VAC CP-823/U Computer. The maintenance/control panel contains all controls and displays necessary to operate and maintain the CP-823/U computer. Figure 15B shows the current panel layout and all the controls and indicators on the panel (refer to section entitled "Central Processor.")

The indicators are neon lights that contain a set button to allow an operator to select manually a particular situation for the computer. During times of low-speed operation, or whenever the computer is stopped, the neon indicators give the operator a visual summary of the existing conditions of the computer program.

<sup>\*</sup>The Keyboard and Printer are optional items.

Figure 15A. UNIVAC 1232A Input/Output Console

Maintenance/Control Panel

Figure 15B.

Maintenance/Control

Console

# PHYSICAL CHARACTERISTICS AND ELECTRONICS

### GENERAL

The CP-823/U computer operates over a temperature range of  $-54^{\circ}$ C to  $+55^{\circ}$ C and under extreme shock and vibrational stress as specified by the specification MIL-E-5400F. It is constructed of modularly discrete units (i.e., power supply, central processor, memory, and input/output) to allow the user to match the hardware to the application.

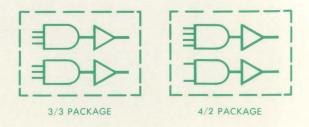

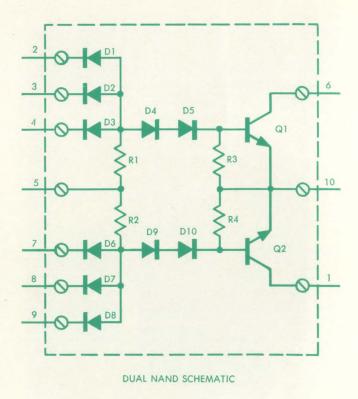

### MICROELECTRONICS

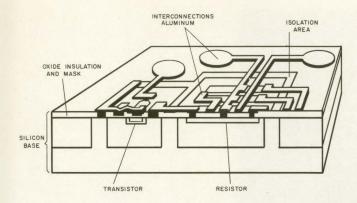

The UNIVAC CP-823/U Computer is constructed primarily of integrated, monolithic semiconductor elements. Resistors, diodes, and transistors are contained within a single chip of silicon and interconnected by deposited aluminum conductors in monolithic semiconductor elements to form a NAND logic element (See Figure 16, logic element, and Figure 17, circuit schematic). Using integrated circuits obtains maximum benefits from the state-of-the-art techniques developed by the semiconductor industry to provide high reliability, small size, light weight, and low cost. The use of integrated semiconductor circuits eliminates most of the packaging of discrete elements now required in welded cordwood or soldered printed card circuits; however, discrete components are not completely eliminated. The number of steps required in manufacturing is reduced to about one-tenth of those required for the same circuit function using conventional components. Complex circuits are being mass produced through the use of automated manufacturing techniques which previously had been restricted exclusively to the manufacture of better transistors.

# INTEGRATED CIRCUIT CONSTRUCTION

Microelectronic integrated computer circuits are subminiature in sizes, formed by selectively oxidizing and photo-etching 0.010-inch thick slices of silicon. The circuits are made on silicon chips small enough to be

Figure 16. Basic Logic Circuit Packages

Figure 17. Schematic - Integrated Logic Element

Figure 18. Integrated Circuit Cutaway

mounted inside 0.25 by 0.25-inch flat packages. Figure 18 depicts an integrated circuit cutaway showing the areas into which P or N type impurities have been diffused to dope the silicon crystal. A siliconoxide coating is placed over the silicon chip, forming a glass resist to stop the diffusion of any impurities. The impurities can be selectively diffused through windows photo-etched in the oxide coating. First, the crystal is divided into discrete components by a diffusion through slots on the top surface, as shown in Figure 18. By growing additional oxide layers, etching new patterns through the oxide, and diffusing impurities through the etched windows, either a resistor, diode, or transistor component is diffused into each isolated area. This component diffusion process is of about the same complexity as the manufacturing process used for single planar transistors. When all components have been diffused into the silicon, an additional oxide layer is placed over the silicon slice, and windows are etched through the oxide where the intercomponent printed circuitry is required. An aluminum layer is then vacuum deposited onto the crystal, and the intercomponent printed circuitry is obtained by photo-etching the aluminum layer. Finally, external connections are made by thermocompression bonding gold wires from the component connection pads to the external leads. The diffused components, intercomponent printed circuitry, and external wire connections for the microelectronic circuit chip designed for a 0.25 by 0.25-inch package are shown in an enlarged view in Figures 19 and 20.

The approach to integrated circuit construction described previously features photo-etching techniques to obtain minimum size, lower costs, and higher reliability.

Figure 21.

Computer Logic Module

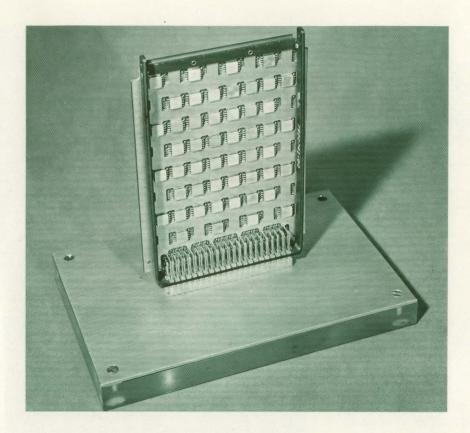

### LOGIC MODULE CONSTRUCTION

The computer logic module (Figure 21) is a pluggable unit designed to mount and interconnect a maximum of 64 integrated circuit flat packs. It is comprised of a frame-connector assembly, two printed circuit boards, and an isolation board. Outside dimensions of the module measure 0.475 x 3.67 x 5.37 inches.

An integral part of the module frame, the 90-pin male connector provides for intermodule and power connections.

There are two double-sided printed circuit boards used on the module. One, of epoxy glass, is the interconnection board which is printed with horizontal circuit interconnection lines on one side and vertical lines on the other. The two sides are interconnected by plated through holes at the desired interconnections to provide a signal path grid work between individual circuits and between circuits and the connector. Circuit element leads and connector pins are also connected to the signal path grid work by means of plated through holes.

The second board provides for a ground, heat sink, and for voltage bussing. One side of the board is

used as a ground plane for the circuit elements and is also used for a heat sink for conductive heat removal from the integrated circuit flat packs, which are mounted flat against it. The other side of the ground voltage board is used for bussing of the two voltages to the various circuits from the connector voltage pins.

These two printed circuit boards are mounted on both sides of a thin piece of insulating board. Flat packs are mounted on the ground side of the ground voltage board with their signal leads bent at 90° and passing through a clearance hole in the ground plane to contact an appropriate point on the signal interconnection board. Ground and voltage leads are terminated on the other board.

Although there are 64 spaces for integrated circuit flat packs on this module, several of the spaces are utilized by a combination resistor-capacitor flat pack, containing eight resistors, and one capacitor. The resistors are used as a collector load, where outputs of the integrated circuit chips are tied together into an "OR" circuit. The capacitor is used as a filter for the supply voltage.

Figure 22. Central Processor

Figure 23. Central Processor with Module Extended-Inside View

# CENTRAL PROCESSOR CONSTRUCTION

The central processor is contained within a case approximately 7 1/4 inches x 17 1/2 inches x 14 1/2 inches (see Figure 22). Within the case are spaces and connectors for up to 72 logic modules, heat exchangers and cooling ducts, and intralogic module chasis wiring (see Figure 23). The CP-823/U Central Processor utilizes 71 removable logic modules (see Figure 21). Each logic module fits into a heat conducting slot provided in the central processor and plugs into the associated connector. The back panel connector into which the modules are inserted is wired by means of a programmed, automatic wire-wrap machine. Since many logic modules of the same type are used within the central processor, the different logic functions depend upon connector wiring. When the logic modules are in place, two sides of the ground plane (heat sink), on the logic module, contact heat exchanger-support ducts to provide a physical path for heat conduction. The heat exchanger ducts have been designed to allow sufficient air flow to maintain proper circuit temperature. All circuits are cooled by conduction, and no air flows directly over the modules and circuits.

The top cover of the unit is secured to the frame with quick-disconnect type fasteners to allow easy access to the replaceable modules.

Connectors are located at each end of the unit to accommodate cables to the memory, input/output, and power supply units.

# INPUT/OUTPUT CONSTRUCTION

Each 4-channel microelectronic input/output unit is similar to the central processor, except it is of smaller size. Case dimensions are approximately 7 1/4 x 13 x 14 1/2 inches. This unit has space for 42 plug-in modules and is, therefore, shorter over-all than the central processor. All other details of construction are similar to the central processor.

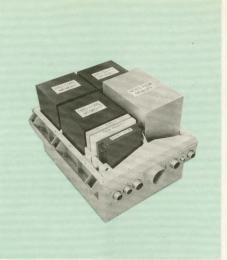

Figure 24. Memory Unit Showing 4K Thin-Film Stack and 4K Core Stack with Service Modules

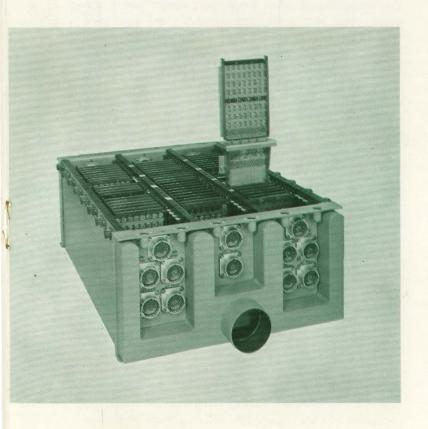

### MEMORY UNIT CONSTRUCTION

The memory unit (Figure 24) consists of removable 4096 word, 30-bit memory modules. Memory unit design provides for eight memory modules with one position designed to accept a 4096-word ferrite core (DRO) module or a 4096-word thin-film (NDRO) module. The entire memory unit is packaged in a case approximately 17.5 inches x 14 inches x 14 inches over-all. The interconnection panel for all the pluggable circuitry is in the center of the unit, with the plug-in memory modules inserted from each side. Modules are accessible by removing a cover on either side of the unit. The same type of air cooling is used as on the other units, with integral heat exchangers.

Memory electronics, which are common to all memory stack modules, data register, voltage regulator, film write, current regulator, stack select, and x-y address select, are contained on six pluggable service modules. Throw-away circuit blocks, similar to those discussed in the core memory section, contain most of the electronic components; some integrated circuit packages and discrete components are mounted directly on the service modules' printed circuit boards.

### CORE MEMORY

Each core memory module consists of a 4096 30-bit word core stack and associated electronics packaged as a pluggable, modular unit. A core stack is com-

posed of 30 double-window planes, with each plane containing 4096 cores. The stack-associated electronics, consisting of sense amplifiers, inhibit switch circuits, read and write transformers, and flat pack strobe gates are mounted on seven printed circuit boards. The read and write transformers and diodes are on boards which form the two ends of the core stack. The other five printed circuit boards are mounted in heat conducting frames for heat transfer to the air heat exchangers. These frame assemblies are mounted to the periphery of the core stack and wired to it, to form the complete 4096-stack module, pluggable to the back panel of the memory unit.

The sense amplifier and inhibit switch circuits are packaged in potted, individually pluggable circuit blocks of approximately 0.5 cubic inch each. The potted blocks are constructed of discrete components, mounted in cordwood fashion, and soldered to a flexible printed circuit board. This assembly is mounted to a connector and potted as a throw-away package. One circuit of each type (sense amplifier, inhibit switch, etc.) is contained within one potted block.

### THIN-FILM MEMORY

Nondestructive readout memories are used when it is necessary to eliminate chance alteration of stored information or critical constants and to achieve higher operating speeds by eliminating the necessity of rewriting after each readout. Basic to the NDRO memory is the Bicore\* element which is used as the NDRO memory storage element. This memory element consists of a high-coercivity storage film and a low-coercivity readout film deposited in a multilayer fashion that physically appears to be a single film. The Bicore elements are deposited on a 3-mil glass substrate measuring 1.7 by 2.4 inches. The Bicore elements are 30 mils square and have a total thickness of 6000 angstroms. Each substrate has 960 elements deposited in a 30 by 32 array.

The NDRO memory plane is made up of two substrates holding 64 30-bit words, placed in a wiring

array which contains the drive and sense conductors. The conductors are the same width as the film and are etched from 2.8-mil copper laminated to 1-mil Mylar film. Two conductor layers are used in the NDRO array.

A component board, which is the final level of address translation, completes the plane assembly. It consists of Permalloy\*\* switch cores, microdiodes, and interconnection wiring. Memory associated electronics are packaged on circuit boards within the thin-film module.

### INSTALLATION REQUIREMENTS

The computer has been designed to be cooled by air, with an operating temperature range of  $-54^{\circ}\text{C}$  to  $+55^{\circ}\text{C}$ . Cooling requirements may be found in Table 3. The operating temperature of the CP-642 compatible input/output unit is  $0^{\circ}\text{C}$  to  $+55^{\circ}\text{C}$ .

Signal interconnection of the units comprising a CP-823/U computer system is accomplished through interconnecting cables terminated in connectors, which are plugged into mating receptacles at each unit.

When using the microelectronic input/output unit, the interface with peripheral equipment may be accomplished with up to 100 feet of shielded cable. The cable is composed of 42 twisted pair, terminated in a 92-pin connector. The CP-642 compatible input/output unit will interconnect with up to 300 feet of cable. Interconnecting cable for the CP-642 compatible input/output unit may be the same as that used for interconnecting the CP-642/USQ-20 with its peripheral equipment.

TABLE 3. SUMMARY OF EQUIPMENT CHARACTERISTICS

| EQUIPMENT                       | WEIGHT<br>LBS. | VOLUME<br>CU. FT. | POWER<br>REQUIREMENTS | LBS. OF AIR**<br>PER HR. | COOLING<br>REQUIREMENTS<br>(CFM SEA LEVEL |

|---------------------------------|----------------|-------------------|-----------------------|--------------------------|-------------------------------------------|

| CENTRAL PROCESSOR               | 50             | 1.1               | 90                    | 59                       | 13                                        |

| MEMORY                          |                |                   | 105                   |                          | 10                                        |

| 32 K CORE                       | 90             | 2.1               | 125                   | 81                       | 18                                        |

| MICROELECTRONIC INPUT/          | 35             | 0.80              | 105                   | 69                       | 17                                        |

| CP-642 COMPATIBLE INPUT/OUTPUT* | 60             | 1.65              | 200                   | 130                      | 30                                        |

| CENTRAL POWER SUPPLY            | 50             | .93               | 65                    | 42                       | 10                                        |

| INPUT/OUTPUT POWER SUPPLY       | 50             | .93               | 110                   | 71                       | 17                                        |

<sup>\*</sup>Contains its own power supply.

<sup>\*\*</sup>Based on the requirement of 65 pounds of air per hour per 100 watts power dissipation.

<sup>\*</sup>Registered trademark of Sperry Rand Corporation.

<sup>\*\*</sup>Registered trademark of Western Electric Company.

### SOFTWARE

Experience with a multitude of digital systems has definitely demonstrated the need for support software that will expedite delivery of the initial program and provide for the rapid and orderly incorporation of programming changes as the system develops. Without such support software the initial programming and subsequent incorporation of program changes become the primary constraint in terms of initial system delivery and subsequent product improvement. As the operational programs required for the various systems become larger in terms of number of computer instructions, the need for support software becomes even more critical.

This consideration was instrumental in determining that the CP-823/U computer would be compatible with the CP-642A/USQ-20(V) and CP-642B/USQ-20(V) computers. Compatible in this case means that the three computers have similar instruction repertoire and input/output. Thus, without modification any program for the USQ-20 computers could be run on the UNIVAC CP-823/U Computer. The CP-823/U computer is also a software subset of the CP-667 in that any program written for it can be run on the CP-667 computer.

The advantages of this software compatibility are considerable: all software previously developed for the CP-642A/USQ-20(V) and CP-642B/USQ-20(V) is available for the CP-823/U computer. Further, any subsequent software development for any of these computers will be available to the CP-823/U. Such available software would not only cost several million

dollars to develop but would require a lead time of several years.

A second advantage of selecting a compatible design is that a large pool of programmers and systems people exist both in the Navy and at UNIVAC who are familiar with the CP-823/U predecessors. Thus, it is not necessary to retrain personnel in the utilization and programming of the computer. The extensive system and software experience gained with the other computers is directly applicable to the utilization of the CP-823/U computer.

Another obvious advantage is that existing computers can be used for data reduction, analysis, program development, etc., pertaining to the CP-823/U computer. For example, CP-823/U programs could be directly checked out on the CP-642B/USQ-20(V) computer. It is not necessary to first develop an instruction simulation, which not only requires development time and money but would normally be very inefficient in its use of computer time and memory.

In addition to the obvious software advantages, the CP-823/U instruction and I/O design were chosen because of their proven excellence in solving a multitude of real-time and command and control problems.

With the selection of the compatible instruction repertoire and input/output, assemblers, compilers, debugging routines, utility packages, and subroutine libaries are available for the CP-823/U computer at no additional development cost.

### ASSEMBLERS AND COMPILERS

### AS-I ASSEMBLER

The AS-1 language defines a problem in machineoriented terminology. A thorough knowledge of the computer is necessary to use this language. There are four basic types of statements that can be used with this assembler:

- Mono-operations, which mnemonically express machine instructions;

- Poly-operations, which mnemonically express functions that give rise to more than one machine instruction;

- Declarative operations, which state control information to the assembler;

Debugging operations, which help the programmer debug his program.

Inputs and outputs of the AS-1 assembler are limited to punched paper tape and on-line typewriter.

### AS-IX ASSEMBLER

The AS-1 assembler has somewhat limited capabilities in processing large programs. AS-1X is an expanded version of AS-1 that will allow assembly of larger programs more quickly through the use of two magnetic tape transports and a high-speed printer.

The added equipment provides much greater versatility of outputs.

### COMPILERS

### CS-I COMPILER

The CS-1 compiler was jointly developed by UNI-VAC and the Navy, primarily for use in real-time command and control applications. It has been used for several years and is constantly being improved.

The CS-1 compiler is a program used as an aid in the preparation of other computer programs. It accepts information coded in an English-language, algebraic-type shorthand and produces a running computer program which is efficient from the standpoint of both time and memory space. Various debugging aids are an integral part of the compiler and significantly reduce the time normally required to debug the program. Program maintenance is simplified by a "librarian" which catalogues subroutines and data designs for subsequent retrieval.

Some typical features included in the CS-1 compiler

- A common mnemonic source language. This language uses alphanumeric terms and subdivides into computer-oriented and problemoriented operations;

- An expandable source language. The compiler design provides the capability of making additions to the source language. More powerful operations may then be continuously devised to increase the usefulness of the system;

- Both punched paper tape and punched card input are used with a uniform set of coding symbols;

- d. Flexible memory assigning ability, for both object program positioning and data positioning in the computer;

- e. A method of correcting the source programs;

- f. Format error detection with printouts;

- g. An integrated librarian. This librarian stores subroutines at the source language level. The subroutines are available for program inclusion when constructing a programming system;

- h. Preparation of edited printouts of the program at various stages and memory address allocations;

- Object program media option of paper tape, magnetic tape, or cards;

- j. The ability to produce object programs for more than one computer version;

- k. The ability to use AS-1 and AS-1X assembler coding as input.

### COBAL

COBAL is primarily a business - oriented compiler designed to operate with a Real-Time Executive Routine (REX). REX controls, sequences, and provides for the efficient use of facilities for user programs.

### DEBUGGING AIDS

### CS-I DEBUGGING PACKAGE

CS-1 debugging aids provide a list of changes in the contents of computer words within a designated area of core storage during execution of the program being debugged. In addition, they make a non-zero dump of the designated area, or areas, at any point of the program during its execution. The areas to be checked and the place in the program where these are to be checked are designated by the debugging operations during the program compiling. The CS-1 debugging packages are then operated concurrently with the program to provide the desired debugged information. Flex code, field data code, or magnetic tape outputs can be selected from the debugging package.

## UTILITY DEBUGGING PACKAGE

The Utility Debugging Package consists of a set of

\*Registered trademark of the Teletype Corporation.

programs designed to assist the programmer to debug and check out his program. The programs are called up via the operator console and consist of the following routines:

- Module loader

- Paper tape handler

- Inspect and change memory addresses

- Store (Q) in memory

- Memory search

- Magnetic tape handler

- Magnetic tape editor/duplicator

- CS-1 magnetic tape output load

- Core dump on printer

- Keyboard entry

- Core dump on magnetic tape in printer format

- Teletype\* handler

### TRACE DIAGNOSTIC

Trace is a diagnostic routine used for tracing the course of a program being executed. For each instruction traced, the contents of all appropriate registers and the instruction itself are recorded on magnetic tape for subsequent listing on a high-speed printer.

### TALK

Besides the debugging operations available in CS-1, a real-time, data-extraction system has been developed to assist in debugging programs in terms of the high-level CS-1 language in which they were written. This language is TALK (Take a Look). Basically, this technique permits programmers to interrupt a program at various points to extract data which they have specified by TALK requests. Extensive editing is performed on the extracted data as a separate function to allow both real-time extractions and a flexible edited format for reading.

Some of the characteristics and capabilities of TALK are as follows:

The users program is written and compiled normally with no additional instructions generated;

- b. The data to be extracted is specified by the same high-level language names as those used in the original source program;

- c. TALK requests, which specify the data units to be extracted during execution of the program, are prepared and processed through a separate translator as a post compiling process. TALK requests may be updated or changed as the debugging progresses;

- d. Real-time capabilities exist since data is merely extracted for later editing;

- e. The edited output is an easily interpreted listing of data associated with its high-level source language identification. For instance, total tables can be listed by their high-level definitions. Decimal or octal may be specified;

- f. Equipment flexibility exists for most environments so that on-site debugging can be achieved;

- g. The TALK process does not necessarily have to be used as a debugging aid; it could be used as a data-extraction procedure with the user writing his own data-editing program.

### CORNELL UTILITY PACKAGE

The Cornell Utility Package is a paper tape and magnetic tape handler. Paper tape operations handle bioctal, Flex code, and Teletype (TWX) code formats. The following programs are available as part of the Cornell Utility Package:

- 1. Paper Tape Operations

- Bioctal, Flex, and TWX dumps with/without zero suppression

- Bioctal, Flex, TWX and relative bioctal loads

- Bioctal check-read with either Flex or TWX code punch tape output of discrepancies

- Duplicate paper tape of any format

- 2. Magnetic Tape Operations

- Write UNIVAC/dual format with/without check sum

- Read UNIVAC/dual format with/without check sum

- Position/rewind tapes

- Read CS-1 machine language outputs

- Dump area for off-line high-speed printer listing

- 3. Miscellaneous Operations

- Fault condition display

- External interrupt control

- Inspect and change

- Store Q

- Memory search with either Flex or TWX code punch tape output of addresses of the found information

- List area on on-line Teletype with/without zero suppression

### SUBROUTINE LIBRARY

A vast subroutine library is available with the CP-823/U computer. The following is a representative list of those subroutines. It should be noted that the list is not complete in that many more subroutines are available than those depicted.

# FIXED POINT MATHEMATICAL ROUTINES

- a. Sine

- b. Cosine

- c. Arcsine

- d. Arccosine

- e. Tangent

- f. Arctangent

- g. Arccotangent

- h. Natural logarithm

- i. Exponential

- Stable Platform to Ships Deck Coordinate Conversion

- k. Ships Deck to Stable Platform Coordinate Conversion

### FLOATING POINT ARITHMETIC PACKAGE

- a. Enter floating point accumulator

- b. Floating point add

- c. Floating point subtract

- d. Floating point multiply

- e. Floating point divide

- f. Floating point store

- g. Floating point compare

- h. Fixed point to floating point conversion

- i. Floating point to fixed point conversion

### FLOATING POINT POWERS PACKAGE

- a. Logarithm

- b. Powers of e

- c. Powers of N

## FLOATING POINT TRIGONOMETRIC PACKAGE

- a. Sine

- b. Cosine

- c. Tangent

- d. Cotangent

- e. Arcsine

- f. Arccosine

- g. Arctangent

- n. Arccotangent

# CONVERSION PROGRAMS

- a. Field data decimal to octal

- b. Octal to field data decimal

- c. XS-3 to octal

- d. Octal to XS-3

- e. Field data to Flex/Flex to field data

### SORT ROUTINES

- a. Sort any number of 1-word items

- b. Modified shell sort (sorting in small units and then merging) with bit capabilities.

# DOUBLE PRECISION ARITHMETIC

- a. Double precision addition

- b. Double precision subtraction

- c. Algebraic double precision addition

- d. Algebraic double precision subtraction

- e. Double precision multiplication

- f. Double precision division

### FIELD DATA ARITHMETIC

- a. Field data addition

- b. Field data subtraction

### APPENDIX A

### REPERTOIRE OF INSTRUCTIONS

The UNIVAC CP-823/U is a self-modifying, stored-program, one-address computer. Although this means that one reference is provided for the execution of an instruction, this reference can be modified automatically during a programmed sequence. Instructions are in the form of 30-bit instruction words stored sequentially in memory; the computer executes the instructions sequentially unless an instruction alters the sequence.

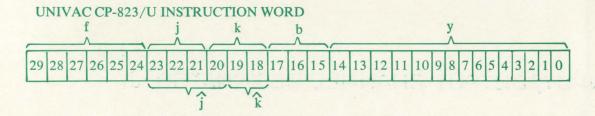

By means of five designators, a computer instruction word completely defines a computer operation. The highest order six bits constitute the function code designator, f. The balance of the upper half of the instruction word contains the designators j, k, and b. The lower half of the word contains the operand designator, y. The  $\hat{j}$  and  $\hat{k}$  are designators that pertain to input/output instructions.

### FUNCTION CODE DESIGNATOR-F

The f designator appears in bit positions 29 through 24 of the U-register, or an instruction, designating the function to be performed by that instruction. Values  $00_8$  and  $77_8$  are fault conditions and if executed will cause a fault interrupt and a jump to the fault entrance address.

### BRANCH CONDITION DESIGNATOR-J

The j designator appears in bit positions 23, 22, and 21 of the U-register, or an instruction; it is used in a majority of the instructions for jump and skip determination, for B-register specification, and for repeat status interpretation. Appropriate interpretations of the j designator are listed below and under the descriptions of the individual instructions.

For those instructions in which the j designator has no special interpretation, it specifies the condition under which the next sequential instruction in the program will be skipped. This permits branching from a sequence without executing a jump instruction, as would normally occur if a skip condition were not satisfied.

Skip of the next sequential instruction is determined by the following rules in all instructions except 04, 12, 13, 16, 17, 26, 27, 60 through 67, and 70 through 76:

- i=0: Execute the next instruction.

- i=1: Skip the next instruction.

- j=2: Skip the next instruction if (Q) is positive.

- j=3: Skip the next instruction if (Q) is negative.

- i=4: Skip the next instruction if (A) is zero (positive zero).

- j=5: Skip the next instruction if (A) is non-zero.

- j=6. Skip the next instruction if (A) is positive.

- i=7: Skip the next instruction if (A) is negative.

When the branch condition involves the sign of the quantity of A or Q, the evaluation examines the sign bit of these quantities: hence, positive zero is considered a positive quantity, and negative zero is considered a negative quantity. A negative zero, however, that is generated as a result of an arithmetic operation is normally forced to a positive zero.

### INPUT/OUTPUT CHANNEL DESIGNATOR-Ĵ

The  $^{\uparrow}_{J}$  designator appears in bit positions 23, 22, 21, and 20 of the U-register, or an input/output instruction, specifying the C-channel for the instruction. Thus the  $^{\uparrow}_{J}$  provides accessibility to the 16 (decimal) input/output channels numbered 0-17<sub>8</sub>. Instructions 13, 17, 62, 66, 67, 73, 74, 75, and 76 use the  $^{\uparrow}_{J}$  designator configuration.

# OPERAND INTERPRETATION DESIGNATOR-K OR K

A k designator (3 bits) appears in bit positions 20, 19, and 18 of the U-register, or an instruction; a  $\frac{1}{k}$  designator appears only in bit positions 19 or 18 since bit 20 is a portion of the  $\frac{1}{j}$  designator. Instructions 13, 17, 62, 63, 66, 67, and 73 through 76 use the  $\frac{1}{k}$  designator configuration since they perform input/output activities and require  $\frac{1}{j}$  designator for channel specification. The  $\frac{1}{k}$  designator is explained under the descriptions of the input/output related instructions.

The k designator controls operand interpretation. Those instructions that read an operand, but do not replace it after the arithmetic is performed are designated read instructions. Those instructions that do not read an operand but store it are designated store instructions. Instructions which both read and store operands are classified as replace instructions.

The various values of k affect the operands (except where noted otherwise under individual instruction description) as follows:

(a) Read Instructions (01-12, 20-23, 26, 27, 30, 31, 40-43, 50-53, 60-65, 70-72):

k=0:  $Y_u=0$ 's;  $Y_L=Y$

$k=1: Y_u=0$ 's;  $Y_L=(Y)_L$

k=2:  $Y_u=O$ 's;  $Y_L=(Y)_u$

k=3: Y=(Y)

k=4: Yu=All bits same as Y14; YL=Y

k=5:  $Y_u$ =All bits same as  $Y_{14}$ ;  $Y_L$ = $(Y)_L$

k=6:  $Y_u$ =Same bits as  $Y_{29}$ ;  $Y_L$ = $(Y)_u$

k=7: Y=(A)

For instructions 22, 52, and 53, k=7 is not used.

(b) Store instructions (14-16, 32, 33, 47):

k=0: Store operand in  $Q^*$ .

k=1: Store operand<sub>L</sub> in  $Y_L$ , leaving  $(Y)_u$  undisturbed.

k=2: Store operand<sub>L</sub> in Y<sub>u</sub>, leaving (Y)<sub>L</sub> undisturbed.

k=3: Store operand in Y.

k=4: Store operand in the A-register\*\*.

k=5: Store complement of operand<sub>L</sub> in Y<sub>L</sub>, leaving (Y)<sub>u</sub> undisturbed.

k=6: Store complement of operand<sub>L</sub> in Y<sub>u</sub>, leaving (Y)<sub>L</sub> undisturbed.

k=7: Store the complement of operand in Y (storing the complement of B<sup>j</sup> is the same as storing a 30-bit register complemented.)

NOTE: When storing  $B^j$ , the B-register is tested as a 30-bit register, with the upper 15 bits set to 0. With a k=7, store  $B^j$  will complement as a 30-bit register ((Y)<sub>u</sub>=77777).

(c) Replace instructions (24, 25, 34-37, 44-46, 54-57):

k=0: Not used.

k=1: Read portion— $Y_u=0$ 's;  $Y_L=(Y)_L$ .

Store portion—Store operand<sub>L</sub> in Y<sub>L</sub> leaving (Y)<sub>u</sub> undisturbed.

k=2: Read portion— $Y_u=0$ 's;  $Y_L=(Y)_u$ .

Store portion—Store operand<sub>L</sub> in Y<sub>u</sub> leaving (Y)<sub>L</sub> undisturbed.

k=3: Read portion—Y=(Y)

<sup>\*</sup>A 1400000000 instruction complements (Q)

<sup>\*\*</sup>A 1504000000 instruction complements (A)

```

Store portion—Stores operand in Y.

```

k=4: Not used.

k=5: Read portion—Y<sub>U</sub>=All bits same as Y<sub>14</sub>; Y<sub>L</sub>=(Y)<sub>U</sub>

Store portion—Stores operand<sub>L</sub> in Y<sub>L</sub> leaving (Y)<sub>u</sub> undisturbed.

k=6: Read portion— $Y_u$ =all bits same as  $Y_{29}$ ;  $Y_L$ = $(Y)_u$

Store portion—Stores operand<sub>L</sub> in Y<sub>u</sub> leaving (Y)<sub>L</sub> undisturbed.

k=7: Not used.

NOTE: Repeat instructions require special interpretation when followed by a replace instruction.

### INDEX DESIGNATOR-B

The B designator appears in bit positions 17, 16, 15 of the U-register, or an instruction and specifies which of the B-index registers, if any, will be used to modify the operand address designator, y, to form  $Y=y+(B^b)$ . This operation employs an additive accumulator; hence, a quantity consisting of all zeros cannot result unless the bits of both the operand designator, y, and  $(B^b)$  are all zeros. Use of a B-index register to modify the operand designator, y, to form  $Y=y+(B^b)$  will cause the higher order 15 bits of the B-register memory address to be made zero.

The effect of the various values of the b designator is a 15-bit one's complement sum as follows:

b=0: Do not modify y.

b=1: Add ( $B^1$ ) to y.

b=2: Add  $(B^2)$  to y.

b=3: Add ( $B^3$ ) to y.

b=4: Add  $(B^4)$  to y.

b=5: Add ( $B^5$ ) to y.

\*b=6: Add ( $B^6$ ) to y.

b=7: Add  $(B^7)$  to y.

### OPERAND DESIGNATOR-Y

The y designator appears in bit positions 14 through 0 of an instruction. The operand or address of an operand, Y, is related to y through the expression  $Y=y+(B^b)$ .

<sup>\*</sup>A repeat instruction makes special use of B-register 6 when followed by a replace instruction.

# LEGEND

|                    | LEGEND                                                                                                                            |           |              |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|

| Symbol             | Represents                                                                                                                        |           |              |

| a                  | A-register (A, Q, B <sup>n</sup> ), a memory location Y, or a constant                                                            |           |              |

| (a)                | Content of a                                                                                                                      |           |              |