# Introduction to integrated semiconductor circuits

# ADI J. KHAMBATA

Senior Development Engineer UNIVAC, Division of Sperry Rand Corporation St. Paul, Minnesota

John Wiley and Sons, Inc., New York • London • Sydney

Copyright © 1963 by John Wiley & Sons, Inc.

All Rights Reserved. This book or any part thereof must not be reproduced in any form without the written permission of the publisher.

Library of Congress Catalog Card Number: 63-22760

Printed in the United States of America

To my mother and father

# **Preface**

This book is intended to serve as an introductory guide for technical and management people in the electronics industry who are on the threshold of becoming involved in the new and fascinating field of Integrated Circuits. Its main purpose is to assist the engineer (and the technician, too) at the working level. The problems faced by these people closely parallel those encountered a decade or so ago, when transistors first made their tremendous impact on the electronics industry. It is assumed that the reader is generally acquainted with semiconductors but is not necessarily an experienced designer of circuits using semiconductor devices. Of course, the reader with circuit-design experience will be better equipped to appreciate the problems associated with Integrated Circuits. literature abounds with excellent articles and reports in this field, but the engineer who might soon be called upon to actively design circuits and equipment utilizing some of these newer devices and techniques will undoubtedly be hard-pressed for time. This book is aimed at his immediate needs and I hope he will find it a convenient source book and a suitable starting point for this new phase in his engineering work. Most of the material presented here has been reported before, scattered in technical journals, magazines, conference proceedings, internal memos, and trip reports. While not intended for people who have been actively working in this field for some time, enough material on the present state-of-the-art is included to make it a handy reference for those in this category, too.

Integrated Circuits—the new frontier of electronics—have come of age. While the field is new and a myriad of problems still remain to be solved, the advances made, to date, give ample reasons for optimism. Several equipment manufacturers are initiating programs incorporating integrated circuits, not only in their special products but also in their future standard product lines.

The broad acceptance and general application of integrated circuits is confirmed by such developments as:

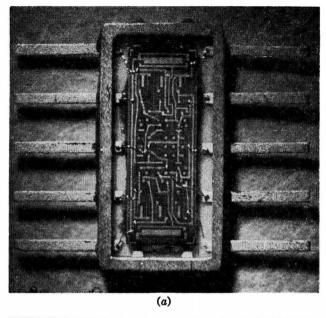

• A microelectronic digital computer with capacity sufficient for ballistic missile explicit guidance has been developed by UNIVAC viii Preface

(a division of Sperry Rand). This system, which weighs less than 17 pounds and occupies a volume less than 0.2 cubic feet including input-output and digital-to-analog conversion circuitry, is approximately 80% smaller than conventional designs of comparable capacity. The computer, designated the UNIVAC 1816, uses 1243 integrated semiconductor circuits and has a magnetic thin-film memory which can be programmed electrically with nondestructive read-out of stored data.

- An AIRBORNE Loran-C receiver using digital integrated circuits, which has been developed by the Sperry Gyroscope Company, is expected to provide position fixes accurate to within a few hundred feet almost anywhere over the Northern Hemisphere. The 19-pound AN/ARN-76 receiver occupies 0.47 cubic feet and is approximately 75% smaller in size and weight than a design using standard solid-state elements. It contains more than 25,000 components and is one of the first complete electronic subsystems designed specifically for integrated circuits.

- A multipurpose computer control system has been developed by Martin-Denver for prelaunch and space booster checkout. About 2000 integrated circuits are utilized in this system, which is designated as MARTAC (Martin Automatic Rapid Test and Control). The principal objective of integration, here, is cost reduction and increased reliability, rather than the more obvious inducements of size and weight reductions.

While cost is still one of the major considerations, present indications show that integrated circuits will be cost-competitive in the near future. Engineers and engineering managers involved in proposal-writing and planning new products are constantly under pressure to make decisions regarding the pros and cons of going the way of integrated circuits. Choices of various circuit types, off-the-shelf units versus custom-made circuits, vendors' present and future production capabilities, status of deliveries, expected reliability, choices between fully, partially, or hybrid integrated units, and cost projections are some of the typical considerations confronting these people. Perhaps the problem can be best exemplified by a question recently asked by an engineering manager: "Integrated circuits are fine, I'm sold on them, but can we afford them?" I sincerely hope that engineers and managers faced with these and similar problems will find answers to some of their questions in this book.

To assist the reader who may not want to read the book in sequence, the chapters are grouped in five sections, each section

PREFACE ix

covering a specific phase of the field. The first section is general and contains two chapters intended to provide the background information. Chapter 1 traces the evolution of the "Micro" concept and goes back to the Second World War to acquaint the reader with the reasons for this trend in electronics. Chapter 2 discusses some of the systems considerations associated with microsystems and the problems introduced by this technology, which integrates the traditionally separate functions of the materials, components, circuits, and systems engineers.

The second section deals with the techniques and processes involved in the functioning and the fabrication of the integrated circuits. The integrated circuit in its two fundamental forms is based on the semiconductor or the thin-film technologies, or suitable combinations of both. Chapter 3 gives a brief description of the fundamental semiconductor processes, and Chapter 4 gives the basic thin-film processes involved. Chapter 5 is essentially a word-picture of a guided tour through a typical semiconductor facility engaged in the fabrication of integrated circuits. A better understanding of the characteristics of the integrated circuits and their limitations can be obtained by a realization and an appreciation of the fabrication steps.

The third section contains the meat of the book. Various aspects of the fully integrated circuit are presented. Chapter 6 introduces the reader to the integrated circuit elements and some of the characteristics peculiar to them. Designing circuits for integrated fabrication presents some rather unique and unconventional problems. These are discussed in Chapter 7, along with a typical circuit design example, which is intended to illustrate some of the problems discussed in this chapter. Since the user of integrated circuits is continually faced with the problem of special circuits for his own particular requirements, which are not available as standard product line items, several vendors have suggested certain procedures for designing custom circuits. These are discussed in Chapter 8. The material presented in Chapters 6, 7, and 8 is intended to be used as guidelines and is based on the presently available information. These guidelines are mostly general and are applicable to most present-day vendors within reasonable limits. As the technology advances, they will undoubtedly change.

The bulk of the market for integrated circuits right now is in the digital field—largely in computing systems. It is therefore quite understandable that the vendors are actively pushing digital circuits for their standard product lines. For the engineer or the technician

X PREFACE

who is not intimately acquainted with the various forms of transistor logic circuits, Chapter 9 provides a brief introduction. For the reader who is well acquainted with transistor logic circuits, I hope that this chapter will come in handy as a guide for occasional reference. Included in this chapter are the comparatively recent transistor-transistor-logic (TTL), the emitter-coupled-transistor-logic (ECTL), and the load-compensated diode-transistor-logic (LCDTL) circuits.

At the present time, the fully integrated circuit has several limitations, which may be serious handicaps in some applications. The fourth section presents some of the alternate schemes that are possible. The partially integrated circuit, or the chip approach as it is commonly called, offers an interim solution to some of these limitations, along with several advantages of its own. This approach is described in Chapter 10. Thin-film techniques widen the scope still further, with some unique characteristics and advantages, when used in conjunction with semiconductor active devices. This hybrid-integration approach is described in Chapter 11.

The fifth section contains several associated topics. One of the problems in this new field relates to the form factor of the container of these circuits, and the bonding of leads to the integrated circuits. These subjects are covered in Chapter 12, which also includes a description of the thermocompression bonding process.

Integrated circuits present some unique problems as far as testing and maintainability are concerned. These topics, along with reliability, are discussed in Chapter 13. This field is advancing at such a rapid pace that it is virtually impossible to include all the latest developments in a book like this. Nonetheless, an attempt is made to include some of the most significant new developments in Chapter 14, which also includes a section on price projections.

The Appendixes contain a condensed catalog of the circuits offered as standard product lines by several vendors at this time. It is realized that the vendors included do not make up a complete roster of companies engaged in this field. I attempted to include most of the vendors' lines which had readily available information at the time of this writing. This book concludes with a bibliography of literature in this field. This list is compiled from my personal file and is not the result of a detailed literature search. The categorizations are my own, intended for convenience in filing, thus several articles could have been classified under more than one heading.

This book is definitely oriented from the users' point of view and not from the manufacturers' viewpoint. It is my opinion that excellent books will soon be forthcoming, authored by engineers and PREFACE xi

scientists actively engaged in the development and manufacture of these devices, which will present the problems and solutions from the vendors' point of view. If this book makes the transition from conventional to integrated circuitry a little smoother and easier for the equipment manufacturers' engineering personnel, it will have served its purpose.

I would like to thank several of my colleagues at UNIVAC (St. Paul) who helped me during the writing of this book, particularly Frank W. Kline and William J. Rydrych, for supplying some of the information, reading the rough draft, and making valuable suggestions relating to content and coverage of the book. I would also like to acknowledge Mrs. Teresa Tisthammer for retyping some of the revised portions of the book. Finally, I owe special thanks to my wife, Ruth, for her patience, and particularly for struggling with the original manuscript and transcribing it into an intelligible typed form.

Adi J. Khambata

St. Paul, Minnesota October, 1963

# Contents

#### section one General Information, 1

# chapter 1 Introduction—a historical review of microminiaturization, 3

- 1.1 Demand for miniature electronics, 3

Military needs, 3, Nonmilitary needs, 5

- 1.2 Evolution of "micro" concepts, 6

Miniaturization, 6, Subminiaturization, 7, Microminiaturization, 7, Morphological integrated technology, 7,

Integration by thin-film technology, 8, Integration utilizing semiconductor technology, 8, Partial and hybrid integration, 9, References, 9

## chapter 2 Systems considerations, 10

- 2.1 Microsystems, 10

- 2.2 Engineer's role in microsystems, 10

Traditional concept of engineering functions, 10, Microsystems integrate engineering functions, 12, Reasons for interweaving of engineering functions, 12

- 2.3 Systems problems, 13

Power requirements and heat problems, 13, System speed, 15, Systems hardware layout (topology), 15, Reliability, 16, Serviceability and maintenance problems, 18, Cost considerations, 18, References, 19

# section two Techniques and Processes, 21

# chapter 3 Review of fundamental semiconductor processes, 23

3.1 Active elements, 24

Surface passivation and planar technology, 24, Epitaxial techniques, 27

- 3.2 Resistive elements, 28

Substrate resistivity (bulk), 28, Diffused resistors, 28,

Epitaxially grown layers, 29

- 3.3 Capacitive elements, 29

Diffused back-biased junctions, 29, Alloyed back-biased junctions, 30, Epitaxial back-biased junctions, 30

- 3.4 Inductive elements, 30

The inductance diode, 30, Inversion of capacitance by active elements, 31

- 3.5 Conduction between circuit elements, 31

Juxtaposition of circuit elements, 31, Degenerate regions, 31

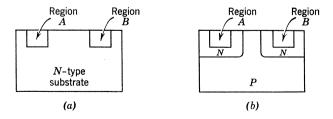

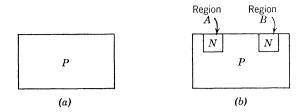

- 3.6 Circuit and component isolation, 32

Back-biased junctions, 32, Thermal oxidation, 33,

Isolation by etching, 33, Intrinsic layer by epitaxial

growth, 33, Through diffusion or separation diffusion,

34, Triple diffusion, 35, Through diffusion in epitaxial

layers, 35, References, 36

## chapter 4 Review of fundamental thin-film processes, 37

- 4.1 Active elements, 37

Vapor deposition of semiconductor active elements, 37,

Vapor deposition of nonsemiconductor active elements,

37, Use of discrete active elements, 38

- 4.2 Resistive elements, 38

Tin-oxide films, 38, Indium-oxide films, 38, Metal films, 39, Nichrome films, 39

- 4.3 Capacitive elements, 39

Metal-oxide dielectric (glass), 39, Tantalum, titanium, aluminum, and niobium, 40, Deposited ferroelectrics, 40, Thermal oxidation, 40

- 4.4 Inductive elements, 41

Deposited nickel-iron films, 41, Deposited Ferrites, 41,

Ferrite substrates, 41, Air-Core Geometries, 41

- 4.5 Conduction between circuit elements, 42

- 4.6 Circuit and component isolation, 43 References, 44

# chapter 5 Integrated circuit fabrication process—a brief description, 45

- 5.1 Zone refining, 45

- 5.2 Crystal growing, 45

CONTENTS XV

- 5.3 Slicing and polishing, 47

- 5.4 Epitaxial growth and surface passivation, 47

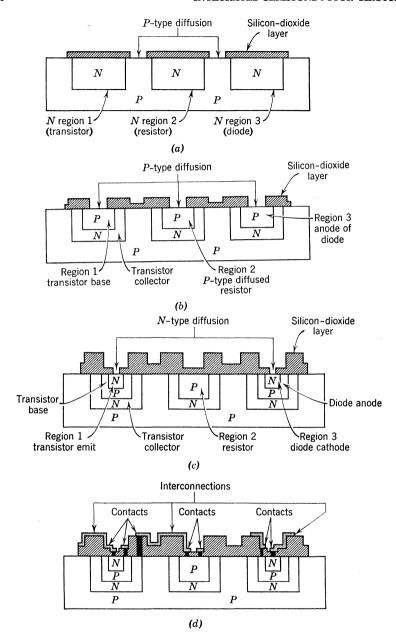

- 5.5 Isolation masking, 48

- 5.6 First diffusion for isolation, 48

- 5.7 Second diffusion for transistor base and resistor, 49

- 5.8 Third diffusion for transistor emitter, 49

- 5.9 Ohmic contacts for interconnections, 51

- 5.10 Wafer scribing and dicing, 51

- 5.11 Die mounting and thermocompression bonding, 51

- 5.12 Hermetic sealing, 52 References, 52

#### section three The Fully Integrated Circuit, 53

# chapter 6 Integrated circuit elements and their characteristics, 55

6.1 Circuit elements for integrated circuits, 55

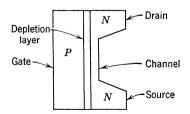

Transistors, 55, Silicon planar epitaxial transistors, 55,

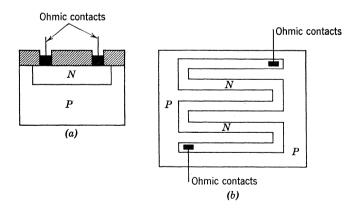

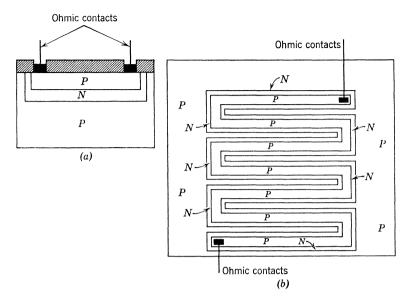

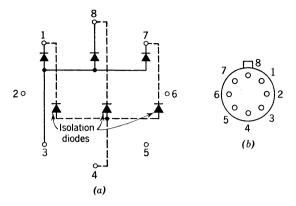

The unipolar or the field-effect transistor, 58, Diodes, 59,

The parasitics associated with integrated diodes, 59,

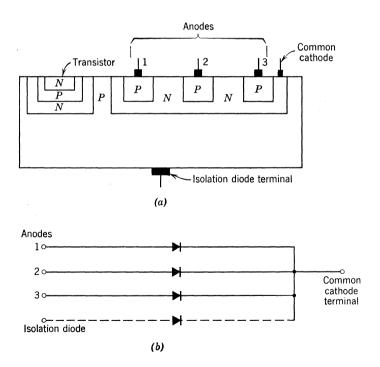

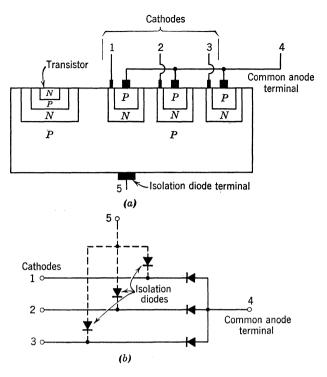

Common cathode arrays, 61, Common anode arrays,

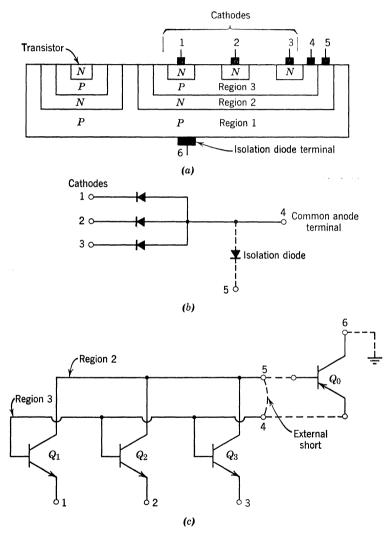

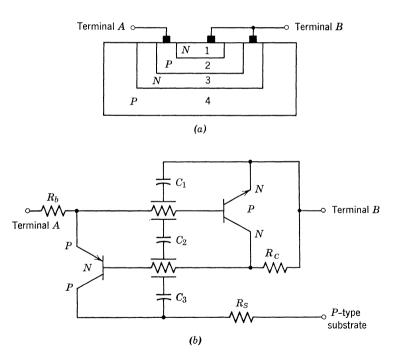

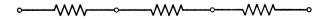

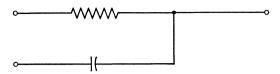

61, Capacitors, 64, Resistors, 66, The equivalent diode,

68, The distributed capacitance, 68, Temperature

coefficient of resistance, 69, Equivalent model of the

double-diffused integrated resistor, 69, References,

# chapter 7 Integrated circuit design considerations, 71

- 7.1 Design problems unique to integrated circuits, 71

Interrelations of circuit elements, 71, Fundamental limitations of circuit elements, 72

- 7.2 The need for circuit simplicity, 72

Importance of component count, 72, Simplicity means reduced cost, 73

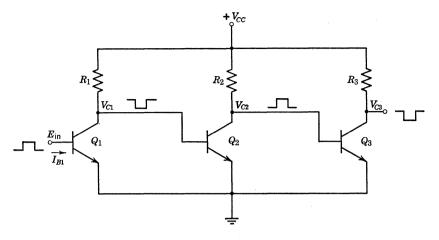

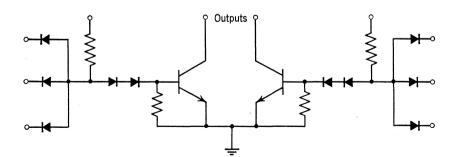

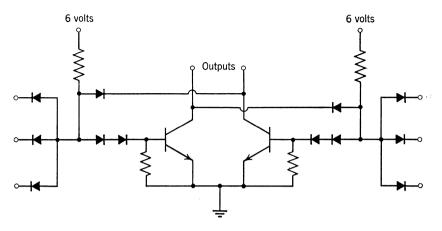

- 7.3 Design considerations for typical integrated logic circuits, 74

Performance capability requirements, 74, Logical capabilities, 74, Circuit capabilities, 74, Conflicting require-

ments and compromises, 74, Minimization of interconnections, 75, Problems due to peculiarities in device technology, 75, Parasitic coupling between circuit components, 75, Temperature effects, 75, Power supply variations, 76, Wide tolerance limits, 76

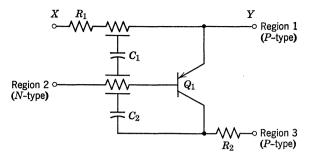

7.4 A typical example, 76

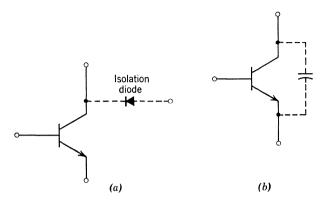

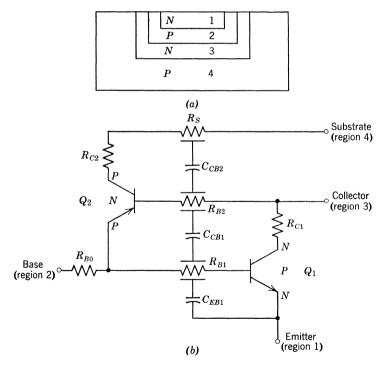

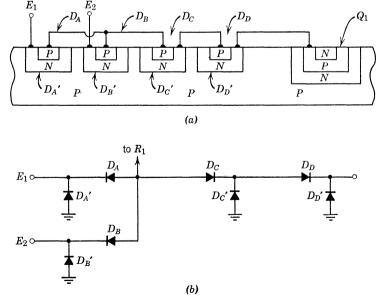

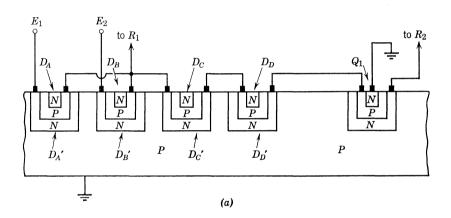

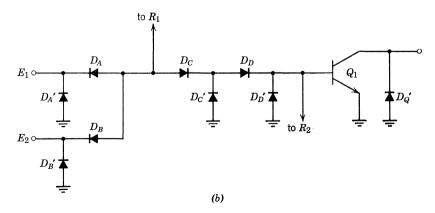

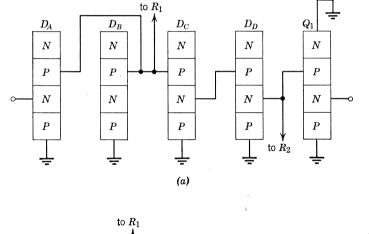

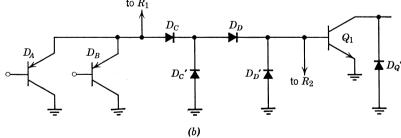

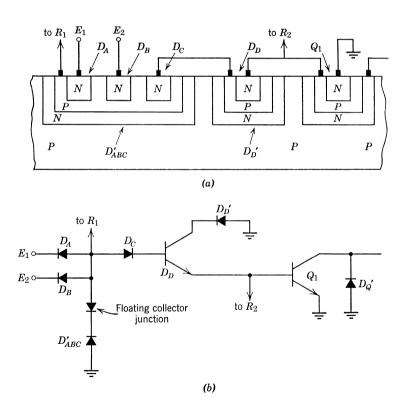

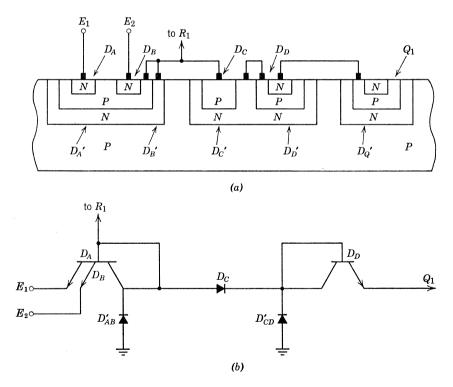

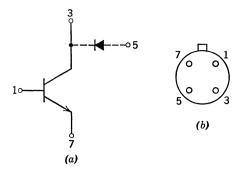

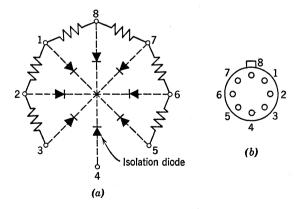

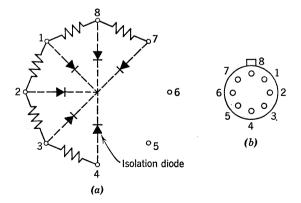

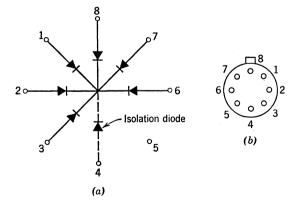

The circuit, 76, Effects of isolation diodes, 77, Individual diode structures, 77, Transistor diodes using base-collector junctions, 79, Transistor diodes using base-emitter junctions, 81. References, 83

## chapter 8 Custom integrated circuits, 84

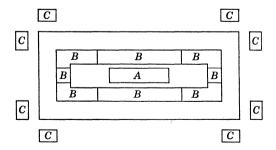

- 8.1 General Electric M1 matrix, 85

Circuit elements on the M1 matrix, 86, Guidelines for

circuit design, 87, New matrices from General Electric,

88

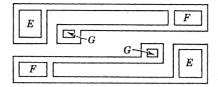

- 8.2 Fairchild custom-integrated circuit breadboards, 88

The standard elements, 89, Ground rules for circuit designing, 93

- 8.3 Texas Instruments, Incorporated, Master Slice, 95

The components on the Master Slice, 96

- 8.4 Signetics Corporation customized integrated circuits, 96

The variFEBS custom integrated circuits, 96, The preFEBS integrated circuit breadboard units, 99, References, 100

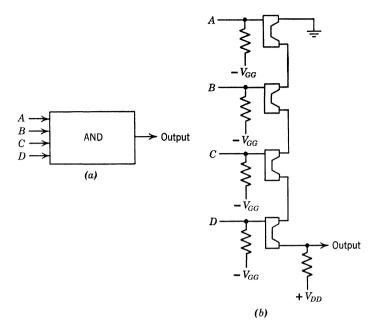

# chapter 9 A review of digital logic circuits, 101

- 9.1 Purpose of this chapter, 101

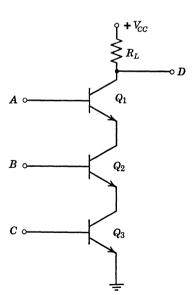

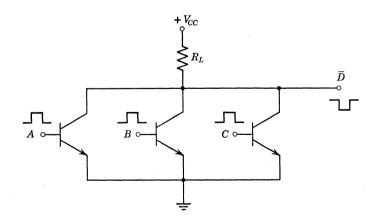

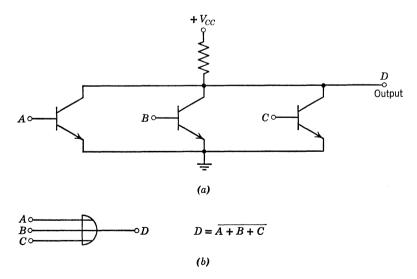

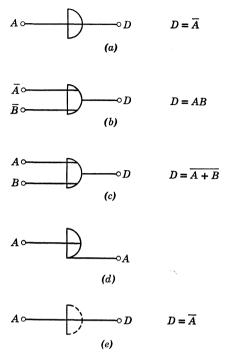

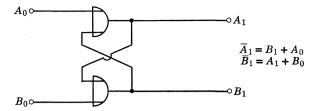

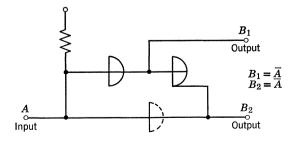

- 9.2 Direct-coupled transistor logic—DCTL, 101

Basic DCTL concept, 101, Disadvantages of DCTL,

106, Switching speed, 108, Advantages of DCTL, 108,

Modified DCTL, 108

- 9.3 Resistor-transistor logic-RTL, 110

Basic RTL concept, 110, The reasons for diode clamping, 111, Advantages of RTL, 111, Disadvantages of RTL, 112

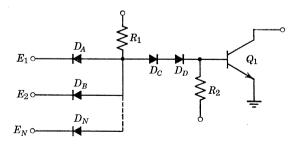

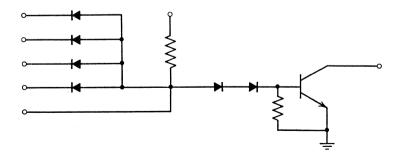

- 9.4 Diode-transistor logic—DTL, 112

- 9.5 Low-level logic—LLL, 114

CONTENTS xvii

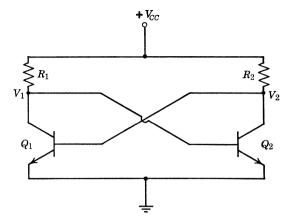

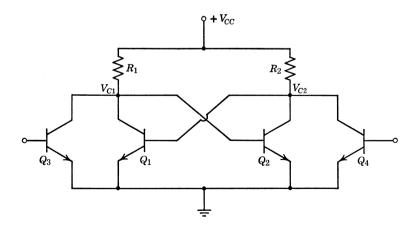

9.6 Nonsaturating logic circuits, 115

Current mode logic—CML, 116, Current-inhibit logic,

118

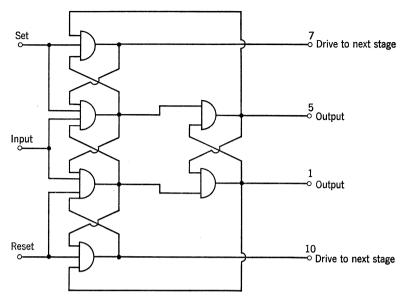

- 9.7 Transistor-transistor logic—TTL or T<sup>2</sup>L, 120

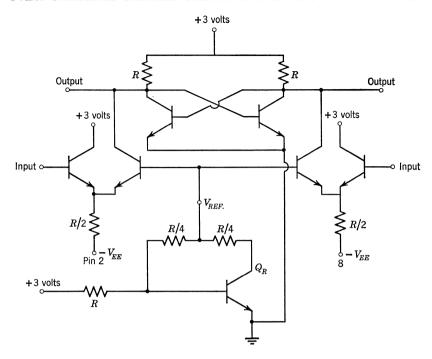

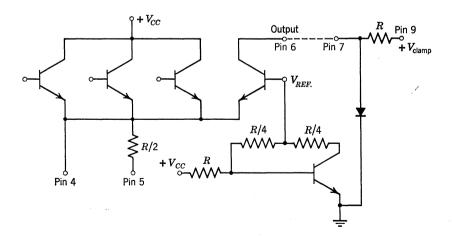

- 9.8 Emitter-coupled transistor logic—ECTL, 123

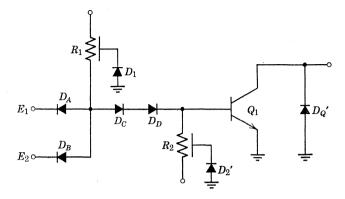

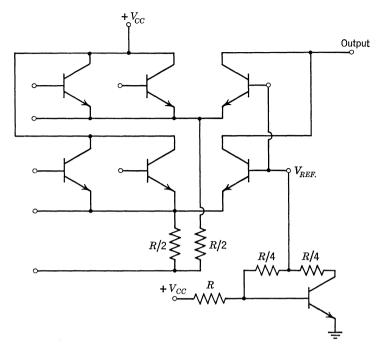

- 9.9 Load-compensated diode-transistor logic—LCDTL, 125

- 9.10 Summary of logic circuits characteristics, 129 References, 129

## section four The Partially Integrated Circuit, 131

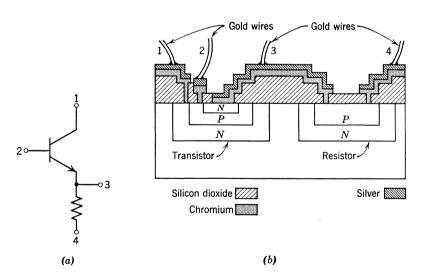

## chapter 10 The multiple-chip approach, 133

- 10.1 Why partial integration?, 133

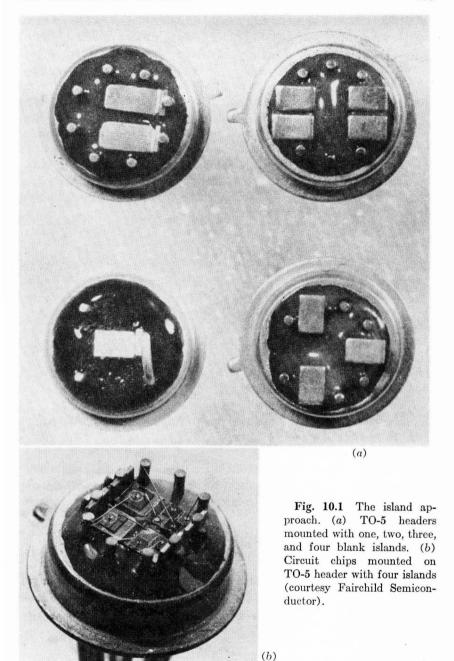

- 10.2 Islands on TO-5 header, 134

Description of the island approach, 134, Typical component elements used, 134, Advantages of this approach, 134, Limitations of the island approach, 136

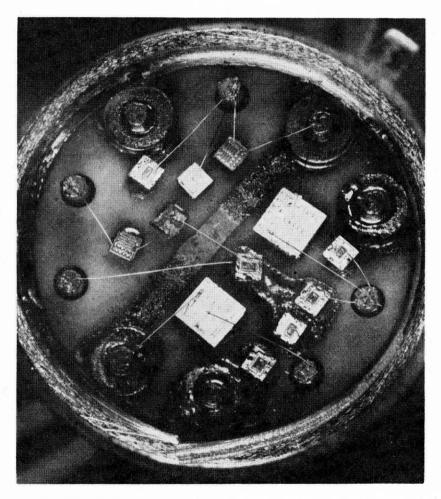

- 10.3 Individual chips on TO-5 header, 136

Description of this approach, 136, Typical component elements used, 138, Advantages and short-comings of this approach, 138

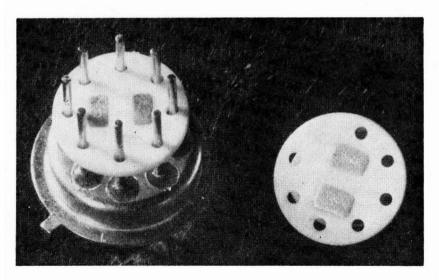

- 10.4 Multiple discs on TO-5 header, 139

Description of this approach, 139, Advantages of the multiple discs, 140, Limitations of this approach, 140

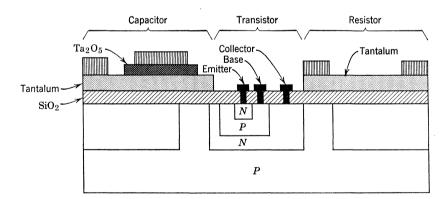

# chapter 11 Thin-film semiconductor hybrid integration, 141

- 11.1 Why thin-film circuits?, 141

- 11.2 Past drawbacks of thin films, 141

- 11.3 Present status of thin-film circuits, 142

Passive components, 142, Motorola Semiconductor

Products, 142, Fairchild Semiconductor, 142, Philco,

143, Active devices—developmental work, 143, Sylvania Electric Products, 143, General Electric

Company, 143

- 11.4 The case for thin films, 144

References, 145

xviii Contents

#### section five Miscellaneous Related Topics, 147

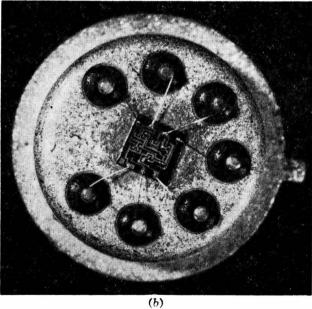

# chapter 12 Integrated circuit packages and mechanical considerations, 149

- 12.1 Introductory remarks, 149

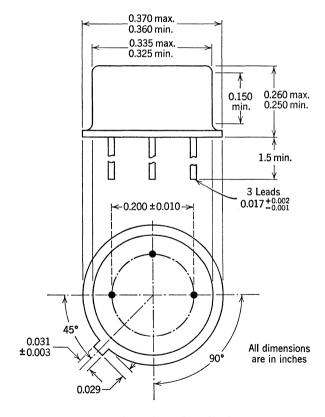

- 12.2 Brief description of the TO-5 can, 150

Mechanica Idescription of the Jedec TO-5 package,

150, Encapsulation, 150, The problem of contamination, 151, Thermal considerations, 151, Hermetic sealing for electrical stability, 151

- 12.3 Thermocompression bonding, 152

The problem and requirements of lead bonding, 152,

Direct bonding process and its properties, 152

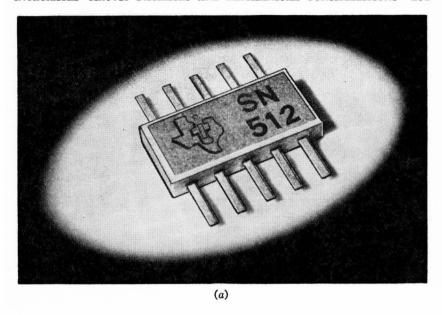

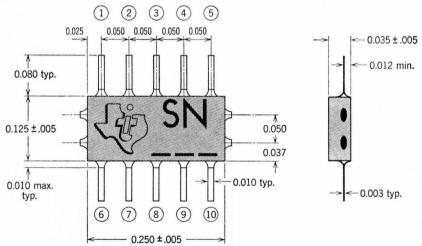

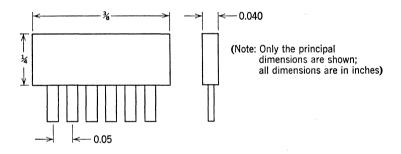

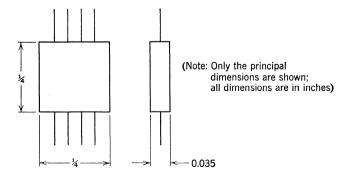

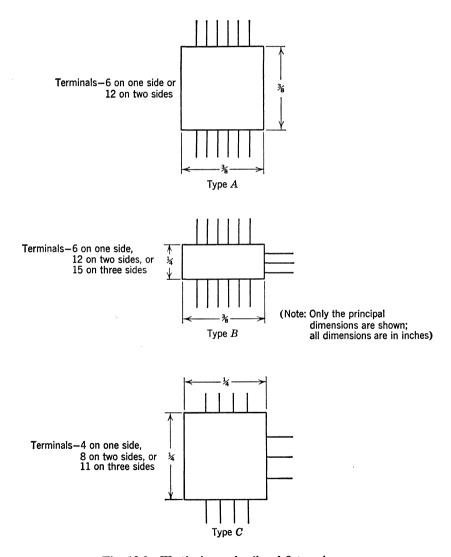

- 12.4 The flat rectangular package, 154

Advantages of the flat package, 154, Commercially available flat rectanglar packages, 155, The Texas

Instruments package, 155, The Signetics package, 155, The Westinghouse flat packages, 156, References, 157

## chapter 13 Testing, reliability, and maintainability, 158

- 13.1 Testing, 158

The necessity of functional testing, 158, Testing of digital logic units, 159, Testing of linear circuits, 159

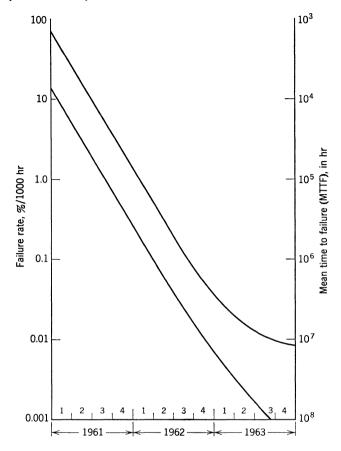

- 13.2 Reliability, 159

Inherent reliability in integrated circuits, 159, Reliability as indicated by some vendors, 160, Fairchild Semiconductor, 160, Texas Instruments, Incorporated, 160, UNIVAC's reliability experience, 162, Reliability predictions, 162

- 13.3 Maintainability, 162 References, 163

# chapter 14 Recent advances and projections, 164

- 14.1 Purple plague, 164

The problem, 164, A possible solution, 165

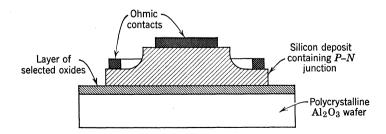

- 14.2 Deposition of passive components on silicon substrates, 166

CONTENTS xix

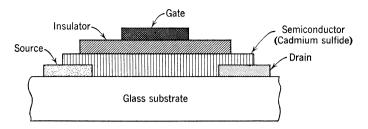

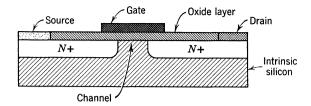

14.3 Thin-film active devices, 166

Insulated gate, thin-film transistors, 167, Metal

interface amplifier, 168, Junction-type deposited

active devices, 168

- 14.4 Insulated-gate, nonjunction, semiconductor, field-effect devices, 169

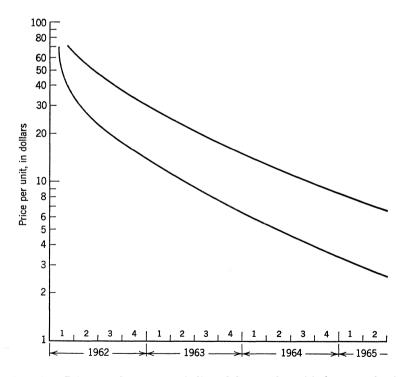

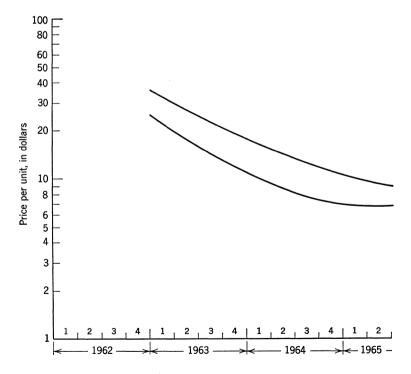

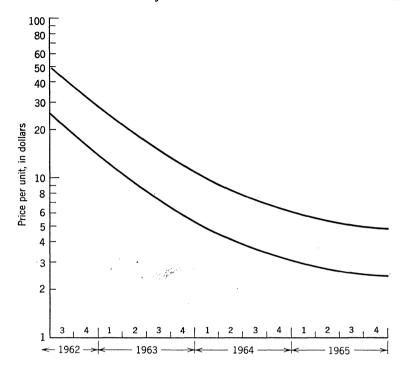

- 14.5 Price projections, 170

Factors affecting price, 170, Masks, 170, Batch

processes, 170, Increased competition, 171, Price

indications by vendors, 171

- 14.6 Concluding remarks, 173

References, 174

#### appendix A Fully integrated standard product-line circuits, 177

- A.1 Texas Instruments, Incorporated, 178

The standard series 51 line, 179, The standard series

52 line, 183

- A.2 Signetics Corporation, 185

The DTL standard line, 185, The TTL standard line, 188, The SE104 diode array, 188, Some characteristics of the Signetics product line, 189

- A.3 Amelco, Incorporated, 189

MC100 diode logic gate, 189, SA100 differential

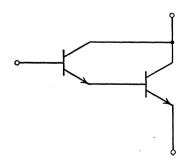

amplifier element, 190, SA102 Darlington amplifier,

190, Characteristics of the Amelco line, 190

- A.4 Pacific Semiconductors, Incorporated, 190

The standard line, 190, Characteristics of the PSI

line, 192

- A.5 Westinghouse Electric Corporation, 192

The standard digital logic line, 192, The standard nondigital line, 194

- A.6 Fairchild Semiconductor, 195

The standard micrologic line, 196

Some notes on the Micrologic line, 199

- A.7 Sperry Semiconductor Division, 199

The standard digital line, 200, The standard amplifier line, 202, Characteristics of the Sperry line, 203

- A.8 General Electric Company, 204

The standard ECLO line, 204, Some notes on the General Electric line, 207

XX CONTENTS

A.9 Motorola Semiconductor Products, Inc., 208

The MECL standard digital line, 209, Some notes

on the Motorola MECL line, 210

- A.10 Siliconix, Incorporated, 210

- A.11 Other vendors, 211

- A.12 Activities in foreign countries, 212

Tokyo University, Japan, 212, Nippon Electric

Company Ltd., Japan, 212, European countries, 213,

References, 213

# appendix B Standard-line circuits using the multiple-chip approach, 214

- B.1 The Fairchild special products line, 214

- B.2 General Instruments' Nanocircuits line, 214

The NC-8C flip-flop, 214, The NC-9 flip-flop steering

gate, 215, The NC-10 NOR gate, 215

- B.3 Motorola chip circuits, 217

References, 217

# appendix C Product-line circuits using semiconductor thin-film hybrid integration, 218

C.1 The Philco μ7000 line, 218

The μ7004 3-input NOR circuit, 218, The μ7005

flip-flop circuit, 218

Bibliography, 221

Index, 229

$\begin{array}{c} \text{section } 1 \\ \text{General information} \end{array}$

# Introduction— a historical review of microminiaturization

The 1950's can best be described as the decade of the transistor. It was in the early 50's that the transistor emerged from a laboratory novelty to a matured component in its own right and seriously challenged the time-honored vacuum tube. The transistor was truly a revolution in the electronics industry, but it did not stop there. The advances made in semiconductor technology opened up new horizons, which are developing a further advanced technology—the integrated circuit. This new concept, which is an outcome of semiconductor development, is not only an evolution but also a revolution.

This new technology will undoubtedly revolutionize several existing concepts and thereby introduce some distasteful problems. It cuts across several engineering and scientific disciplines. Integrated circuits break down the traditional boundaries separating the functions of the components engineer, the circuits engineer, and the systems engineer and consolidate them to an extent which until now was not considered possible or even desirable. This revolution will perhaps present the industry with some of its most agonizing growing pains in this field.

#### 1.1 DEMAND FOR MINIATURE ELECTRONICS

A natural question asked by many is, "why miniaturize electronic equipment?" To answer this question satisfactorily it is almost necessary to backtrack to the Second World War and trace its history from thereon. Broadly, the need for miniature and microminiature electronics can be categorized by military and nonmilitary needs in science and industry.

# Military Needs

The Second World War imposed some stringent demands on the electronics industry. Military requirements put a constantly increasing pressure on the production of electronic equipment of smaller and lighter weight. This trend was mainly the outcome of the necessity to put more capability and higher performance in the then existing weapons and delivery vehicles. American industry met this challenge squarely by developing the miniature tube. Further demands for size

reduction were met by the subminiature tube and finally by the emergence of the transistor.

The immediate postwar years saw several problems created by these new developments. The subminiature tube and the transistor eased the demand for size and weight reduction. The termination of the war eased the pressure for higher performance. This resulted in a decrease of safety factors, which engineers normally incorporated in their designs. The inevitable outcome of this was a period of intolerable unreliability in electronic equipment. An increasing demand for reliability from the dissatisfied customer brought back the safety factors, which were earlier removed, and this produced larger equipment with reduced performance. Understandably, this met with blunt disapproval by the military, who were by then very much accustomed to miniaturized electronic equipment.

The cold war and the increasing emphasis on national defense, as well as interest in exploration of space, put a further demand on size reduction and increased performance. Today's space vehicles and satellites, while not necessarily requiring the ultimate in speed of operation, do demand a high degree of reliability for relatively long periods. On the other hand, manned aircraft as well as missile systems demand a much higher degree of performance, with increased speeds and reliability, which can only be fulfilled by complex electronic systems. Our nation's survival may well depend on the missile, which might be called upon to intercept and destroy hostile aircraft or intercontinental ballistic missiles, and which will require an absolute degree of reliability for a short period of time.

With the rise in demand for reliability of increasingly complex electronic equipment requiring enhanced performance, as well as size and weight reduction, cost becomes a very significant factor. For instance, the high cost of putting satellites into orbit may be justified, and partially offset, only if the system maintains minimum satisfactory performance over a prolonged period of time. "The ratio of payload weight to gross launch weight could be as small as one to one-thousand." This means that the whole launch system could be fantastically expensive. Consequently, any reduction in the size and weight of the payload itself could result in a significant reduction of gross launch weight, and thus a substantial reduction in cost. This naturally places more pressure for microminiaturization of electronics.

The cost factor is further reflected in a different manner. Size reductions of components and subsystems make it increasingly difficult to use human operators during fabrication, thereby forcing the manufacturer into automation. Initially, automation would prove

rather costly, but the increase in reliability resulting from reduction, and possibly complete elimination later on, of human errors would certainly justify the cost. Eventually, it is conceivable that this may reach a point where the total cost of a complex system may even be less than what it would be if conventional components were used.

### Nonmilitary Needs

While size, weight, reliability, and cost are sufficiently attractive reasons for miniaturization in nonmilitary applications, other incentives also exist. Space medicine is an expanding field, which presents some very challenging problems. Sensors attached to an astronaut's body for picking up reactions and responses in space environments must be small and light. Space limitations within a space vehicle impose severe restrictions on the size and weight of the equipment required for transmitting the data picked up by the sensors. sciences, even in normal ground environments, have very special needs for miniaturized electronics. Diagnostic and later even corrective devices, which must be embedded in animals for experimental purposes (and later in human beings, too), obviously have very severe size and space limitations. Biological sciences will undoubtedly make good use of electronics if sufficiently miniaturized. For instance, the study of communication and navigational systems in small animals, and even insects, could be greatly facilitated if signals could be transmitted by microminiature transmitters attached to their bodies. Obviously the transmitting system must be small and light enough to ensure that it will not hamper the mobility of the subject under study.

Self-adaptive bionic systems will probably advance and reach a stage of real usefulness when miniaturization of electronics has advanced to a much greater degree. These systems, which will have synthesized neural networks, will certainly require a large amount of redundancy to meet near-perfect reliability. In space exploration, these systems will be fed large quantities of data from the various sensors. These data will have to be evaluated and analyzed, pertinent information will be sorted, and the required control signals generated and transmitted. All this must be accomplished in very short periods of time. Both the redundancy and speed requirements will only be satisfied by microminiaturization.

In the area of nonmilitary needs, the biggest spur to miniaturization will unquestionably be provided by the computer industry. In the field of commercial data processing, cost and reliability considerations will take precedence over size and weight. The latter two considerations will come as bonus by-products of miniaturization. Present

indications are that by 1964 the cost of integrated logic circuits, will not only be compatible with that of conventional component-printed circuit boards, but will be competitive as well. This will benefit both the computer manufacturer and the user. The manufacturer will be able to sell systems that will cost less to produce, with increased built-in reliability. Size reduction will make it possible to introduce higher computing speeds, larger computing capability, and more widespread use of redundancy, resulting in still greater reliability. Thus the computer user will undoubtedly benefit.

#### 1.2 THE EVOLUTION OF "MICRO" CONCEPTS

Having established the various needs for microminiaturization, it is interesting to observe the evolution of the various concepts which have resulted in distinctly different approaches. For purposes of explanation they are divided into the following seven categories:

- 1. Miniaturization

- 2. Subminiaturization

- 3. Microminiaturization

- 4. Morphological integrated technology

- 5. Integration by thin-film technology

- 6. Integration utilizing semiconductor technology

- 7. Partial or hybrid integration by combination of thin-film and semiconductor technologies

The last three techniques are the ones that appear most promising for applications in the immediate future, particularly for the computer industry. For this reason this book is confined to these three approaches only. Nonetheless, we will briefly look into all seven approaches to get a coherent historical picture of the entire miniaturization phenomenon.

#### Miniaturization

The earliest real need for miniaturization was established during the Second World War. The first significant goal was reached when the miniature vacuum tube made its appearance, followed by the subminiature tube. As a result, pressure was put on manufacturers to reduce the sizes of other electronic components; smaller forms of conventional components were the outcome. Each component, however, retained its own discrete nature and its usual form and shape. Furthermore, the components were mounted in the usual manner, and conventional wiring and soldering were employed for assembling them

in circuits. The only advancement was the size reduction of the individual components.

#### **Subminiaturization**

Pressure for further size reduction resulted in still smaller individual components. The discrete nature of the various components was still maintained. The significant advantage now was that the weight and size of each part was reduced to a point where the component-mounting hardware became unnecessary. The wire leads themselves were sufficiently rigid to provide the mechanical support for mounting. One very important technique that evolved from this is the familiar cordwood package, in which all the components are stacked like cordwood and are held in place by printed circuit boards on both sides of the stack. The component leads protrude through holes in the boards, which are properly aligned. The leads are either soldered or welded to the printed circuit boards. Semiconductor diodes and transistors are particularly suited to this form of packaging.

#### Microminiaturization

Subminiaturization was followed by microminiaturization, which perhaps denotes the maximum size reduction at which the component still retains its discrete individual identity. However, at this stage the components lose their familiar forms and usually the leads are also left out. The form factor of the component is now determined by the supporting printed board or matrix. The pellet Micro-Components by Mallory and the Microseal components by Hughes are typical examples of this approach.

The three approaches described up to this point allow the circuit designer almost unrestricted choice in the selection of components for his circuit. Packaging techniques and packaging densities perhaps dictate the only restrictions.

# Morphological Integrated Technology

This technology is very recent, in fact it is still in its infancy. However, it appears to hold a promising future. It is often referred to as the "functional-block" or the "molecular-electronics" approach, and is considered by many as the ultimate answer to both reliability and ultra-microminiaturization.

This approach dispenses with the traditional concept of componentand-circuit combination to obtain electronic functions. Instead, the present knowledge of the structure of matter and solid-state phenomenon is applied to synthesize functional blocks, composed and arranged in such a manner that each domain performs an electronic function in transforming and controlling energy flow. This results in a single block of semiconductor material performing the function of a circuit or a subsystem. In such a composite block, neither the electronic components nor the circuits are identifiable as individual entities.

#### **Integration by Thin-Film Technology**

Chronologically, this technology introduced the most significant and revolutionary advance in microminiaturization. For the first time, the conventional components in discrete form are replaced by depositing them on a single substrate, either ceramic or glass. Furthermore, no wires are used for interconnecting the components. Instead, conducting film patterns are deposited such that they overlap the respective components. Currently, magnetic, insulating, and conducting thin films are successfully deposited.

At the present time, the major limitation of this approach is the fact that successful deposition of active elements, diodes and transistors is still some time away. There are several companies actively working on deposition of active devices with very encouraging results, but in the interim it is necessary to use individual discrete diodes and transistors in conjunction with deposited passive elements and thin-film interconnections.

#### Integration Utilizing Semiconductor Technology

This is a semiconductor-based approach in which all the components of a circuit or a subsystem form an integral part of a piece of bulk semiconductor material. In this approach, all the circuit components. both active and passive elements, are formed in the bulk material and become an indivisible and unalterable part of this material. presently known semiconductor technologies, such as diffusion, passivation, epitaxial growth, etc., are used to obtain the particular desired Interconnections between various components are components. obtained by deposition of conductors by thin-film technology or in some cases by ingenious juxtaposition of some of the components within the bulk material itself. Connections to the outside world are made by bonding thin wire leads to selected points on the surface of the semiconductor slice representing the required nodal points of the particular circuit configuration. We should realize that while this technique is very promising, particularly for computer applications, its future is directly linked with the advance of the semiconductor art, and its present limitations are basically the shortcomings of the semiconductor state-of-the-art.

In this book, when we talk about the "pure integrated" circuit, the "fully integrated" circuit, or just plain "integrated" circuit, we are referring to this particular approach to microminiaturization.

# Partial Integration and Hybrid Integration by Combination of Thin-Film and Semiconductor Technologies

These approaches utilize thin-film technology to supplement the "pure integrated" circuit in those areas which are limited by the present state of the semiconductor art. Of all the existing forms of microminiaturization, these approaches give the widest choice of both active and passive elements and consequently offer the greatest potential flexibility to the circuit designer. The most attractive feature of either approach is that they are compatible in size and packaging densities to the "pure integrated" technique. Currently, two variations of this approach are being actively developed, and it is interesting to note the differences between the two.

HYBRID INTEGRATION. In this approach all the active elements of the circuit are diffused into the bulk semiconductor material. In one version of this approach, passive elements, such as resistors and capacitors, are deposited by successive evaporations. Interconnections between all the components are similarly deposited, and external connections are made by bonded leads. In another version of this approach, the passive elements are deposited on a separate substrate, either glass or ceramic. Interconnections between the two substrates are either by bonded leads, or sometimes the package leads of a TO-5 can are used as common nodal posts. In industry, either version is commonly referred to as the "hybrid integrated" approach; we shall use the same terminology.

THE MULTIPLE-CHIP APPROACH. In this variation, the circuit is distributed in pieces on two or more chips or substrates. All the active elements are diffused on one or more semiconductor chips. The passive elements are similarly grouped on one or more separate chips. In some cases the passive components may be diffused into separate semiconductors, or they may be deposited on some other base material, usually ceramic. The whole group of separate chips is interconnected by bonded wires, and connections for external purposes are similarly made by bonded leads. The terminology commonly used for this approach is the "chip version" of integration or the "multiple-chip approach;" these are the terms we shall use.

#### REFERENCE

H. V. Noble, "The Need for Microsystems," Electrical Engineering, July 1961, pp. 483-484.

#### 2.1 MICROSYSTEMS

Having established the need and the evolution of the phenomenon we refer to as microminiaturization, it is necessary to investigate some of the fundamental and rather broad problems which must be taken into consideration in planning and designing a microminiaturized system. Recently a new term has been added to the glossary of the electronics industry—microsystems. As of this writing, industry has not established a precise and widely accepted definition of this term. Many different definitions are offered, but the one characteristic common to all is small size of the subsystems and systems, and so the generic prefix micro is appropriate.

"Microsystems range from those using discrete but miniaturized active components and thin-film passive components (where possible), to those employing hardly distinguishable active and passive regions within single semiconductor structures." This is the definition offered by H. W. Henkels of Westinghouse. It covers the entire gamut of "micro" concepts in Chapter 1.

Since this book is limited to integrated circuits using semiconductor and thin-film technologies, and combinations of the two, perhaps the most directly applicable definition would be as follows: Microsystems are electronic systems consisting of circuits and subsystems fabricated by the application of semiconductor or thin-film technologies, or suitable combinations of the two; they are packaged in present-day transistor cans, such as the TO-5 can, or in containers of other geometry of compatible or smaller volume.

#### 2.2 ENGINEER'S ROLE IN MICROSYSTEMS

# **Traditional Concept of Engineering Functions**

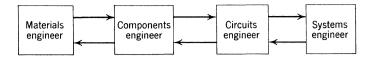

The complex nature of today's technology demands that each individual scientist and engineer specialize in a comparatively narrow area of his field of interest. Limitations in time make this a necessity. A discussion about the merits or otherwise of specialization is not intended here. Suffice it to say that it exists and that in the electronics industry it can be broadly categorized, as shown in Fig. 2.1. We can see that various engineering functions essentially form a serial chain

Fig. 2.1 Traditional interrelationships within engineering functions.

as far as planning and developing the ultimate product is concerned, and with regard to liaison and communications between them. The interrelations can best be understood by considering the functions of each engineering group separately.<sup>2</sup>

MATERIALS ENGINEER. The function of the materials engineer is clearly the development of new materials or modification of existing ones as indicated by the needs of the components engineer. His efforts in research and development are solely directed by the information fed to him by the components manufacturer. It is quite apparent that the materials man has little or no direct contact with the circuits or the systems engineer.

COMPONENTS ENGINEER. The scope of the components engineer's activities is somewhat wider than that of the materials engineer. His primary responsibility is to fulfill the needs of the circuits engineer, and so he plays the dual role of communicating with both the materials and the circuits people. Even then, his field of activity is pretty much specialized, and he seldom, if ever, has direct dealings with the systems engineer.

CIRCUITS ENGINEER. The circuit engineer's functions parallel those of the components engineer in that he has a two-way communication need with both the components and the systems engineer. He goes to the components man for the essential building blocks of his circuits, which in turn must satisfy the requirements of the systems engineer. His demands on the components man are principally dictated by the systems engineer's demands on him. In this case, his contacts with the materials engineer is via the medium of the components manufacturer, not directly.

SYSTEMS ENGINEER. In the functional chain, the efforts of the previous three are geared to the ultimate requirements of the systems engineer. The systems engineer's demands, however, are the primary concern of the circuits engineer. We should note that the systems engineer does not need to communicate his requirements directly to either the materials or the components engineer. The systems engineer, of course, has to satisfy the ultimate needs for his products.

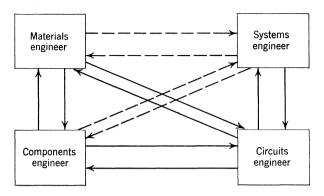

Fig. 2.2 Microsystems require interwoven relations of engineering functions.

#### Microsystems Integrate Engineering Functions

The natural outcome of the rigid partitioning of engineering functions is a high degree of specialization. Very often this specialization is carried to such an extent that the working engineers in each of the four categories have rather limited knowledge of the problems and workings of the functions adjacent to their own. They often have a technical language of their own. Microsystems demand much closer coordination between the aforementioned functions; in fact the barriers separating them are broken down to such a degree that they tend to merge into a coherent, interdependent, single function. Regardless of this, the serial chain of Fig. 2.1 is now modified to an interwoven complex of Fig. 2.2. The communication channels between the systems engineer and the materials and components engineers are shown by broken lines to indicate that, in microsystems, the systems engineer's principal line of communication is with the circuits engineer, with little, if any, direct contact with the other two categories.

# Reasons for Interweaving of Engineering Functions

Figure 2.2 clearly shows that a much closer liaison and understanding of each function has become mandatory. Microsystems by their very nature demand this. In fact, quite frequently the functions of the components engineer now merge with those of either the materials or the circuits engineer, or both. Briefly, there are three reasons:

1. A manufacturer producing either a pure integrated or a hybrid integrated circuit or subsystem certainly combines materials and components engineering functions, and to a large extent even the circuits engineer's functions. This is simply because he produces the desired circuit by the fabrication of active and passive components within, or on, one or more pieces of material (usually semiconductor, glass, or ceramic substrates).

- 2. In conventional systems, circuits and subsystems are designed around available components, both active and passive. The situation is radically different with microsystems. Now, the components which are circuits or subsystems, themselves, must be designed to systems requirements. This is the main reason why active coordination between systems engineering and the other three functions is so vital.

- 3. Another very compelling factor for close working relations is a purely economic reason. The production of an integrated circuit or a subsystem entails a substantial cost, particularly in the fabrication of the diffusion masks. It is therefore expensive and time-consuming to modify or replace designs. Costly redesigns can be avoided if sufficient coordination and exchange of information takes place initially between the systems engineers and the integrated circuits or subsystems suppliers. Such cooperation in the early stages of product design induces the systems engineers to formulate requirements which are within realistic capabilities of the vendor supplying the integrated circuits.

#### 2.3 SYSTEMS PROBLEMS

In a system constructed out of integrated circuits, it is necessary to consider some of the basic problems associated with microsystems and decide on the most acceptable design trade-offs. These problems can be broadly classified in the following six areas: (1) power requirements and heat dissipation; (2) speed; (3) systems hardware layout, or topology; (4) reliability; (5) serviceability and maintenance problems; and (6) cost considerations. These areas are interrelated and in most cases cannot be considered separately. For purposes of presentation it is expedient to look at them individually.

# Power Requirements and Heat Problems

In microsystems, perhaps the biggest problem confronting the design engineer is the power requirements of the circuits and subsystems which go to make up the total power requirements of the entire system. It is, of course, advantageous to keep the total consumption as low as possible, since the heat generated within the system is directly dependent on power. Since circuit components are basically temperature-limited, it is necessary that the internally generated heat be dissipated as quickly as possible. Heat dissipation, therefore, is a prime factor

in establishing the weight, volume, and packaging densities of microsystems.

Obviously, the most direct solution to the heat problem is the development and use of extremely low-power devices. But even this desirable goal has its limitations. Basically, the function of any electronic circuit or system is the transfer of energy; thus, signal-power levels, operating speeds, noise levels, component tolerances, ambient temperatures, and characteristics of power sources all tend to restrict the lower limit of power dissipation.

At the present time, perhaps the largest potential use for integrated circuits is in the area of logic circuits in digital systems. It is therefore worthwhile to briefly look at the various logic circuits and how power can affect the decision to use them. Saturating transistor circuits have several desirable features as compared to the nonsaturating types. Low power requirements and reduced number of components are the main items favoring the saturating circuit. Even in this case, power dissipation exerts a decisive influence. In a system where speed may be of prime importance, obviously resistor-transistor logic (RTL) would be a rather poor choice. If other factors dictate that RTL be used, then perhaps a speed-up capacitor may offer some solution to speed, provided reduced logical gain can be tolerated. buffer stages may also be necessary to reduce transient coupling. noise levels within the system are high, the direct-coupled-transistorlogic (DCTL) should be avoided. In view of these limitations, diodetransistor-logic (DTL) might offer an acceptable compromise.3 Chapter 9 for additional information on digital logic circuits.)

Power supply and component tolerances also affect power dissipation. If tolerances for component manufacture, temperature effects, and drift due to aging, as well as power supply tolerances, can be improved, then circuits can be designed with tighter tolerances, and power can be reduced. Sometimes additional power dissipation can be traded off for looser tolerances. This trade-off may set off an inevitable chain reaction, which may be undesirable. Tolerance slack compensated by added power level may necessitate reducing the load of a circuit. Of course, this compensation may allow fanouts to be maintained, or more circuits may have to be added to maintain the desired logical performance of the system. This would increase the system complexity, as well as size and weight. It is apparent, therefore, that some of the very basic features of microsystems may be compromised.

In saturating circuits, the lower power dissipation limit is established by the low-current gain of the transistor. Also, the upper speed limit is set by the gain-bandwidth of the transistor. Consequently, these two factors define the speed-power dissipation relation of the circuit, because, as the operating speed increases, power dissipation also increases. Another factor is prominent in this consideration: distributed capacitance loads the circuits quite significantly and slows them down. To maintain the required speed, power levels of the signal would have to be increased.

#### System Speed

High operating speed is one major factor associated with computing systems. While higher speeds are desirable in practically all computer applications, they become a very critical requirement in today's aerospace systems, since the fantastic speeds attained by missiles and orbiting vehicles demand exceptionally high computing speeds.

In the past, the demand for increased speeds in electronic equipment was satisfied by developing components and devices which were inherently faster and more efficient. This approach is rapidly reaching its upper limit. Speeds of components and devices will undoubtedly be improved in the future. On the other hand, in certain computer applications, a point is now reached where propagation delays in wiring become a very prominent factor in the overall speed of operation, as compared to the speed of the components. quite evident that the physical size of a system directly limits its operating speed. In a system that has reached this speed-size ceiling. the only way that speed can be increased is by a reduction of its physical size. Microsystems offer a very substantial advantage with regard to this problem. Connecting leads between circuits can be reduced to such a degree that propagation delays may often be reduced by at least an order of magnitude. By incorporating two or more fully integrated circuits on one piece of semiconductor material, signals can be transmitted directly from one circuit element to an adjacent one, which may comprise the input element of the next circuit in the logical chain. Obviously, in such a configuration, the propagation delay can be reduced to almost zero.

# Systems Hardware Layout (Topology)

Some recent studies of packaging problems of electronic systems<sup>3</sup> reveal that as much as 90% of the total volume of a system may be taken up by wiring, printed-circuit board connectors, mounting hardware, and cooling equipment. According to this, the volume occupied by the actual electronic components would be approximately 10%. This 9:1 proportion in conventional hardware would undoubtedly become more lopsided with microsystems, unless serious consideration is given to both circuit and system layouts.

In circuitry using conventional components, electrical problems generally dictate circuit layouts with relatively minor attention given to thermal considerations. In systems using integrated circuits, the systems layout is determined by power density, speed, and interconnections. From the circuit point of view, whether the circuit is fully integrated or partially integrated, the components must be laid out in such a manner that the temperature rise of adjacent or nearby components do not affect them adversely. Circuit reliability requires that all components operate within the allowable temperature limits. From the systems point of view the heat dissipated by the various component subsystems must be adequately sinked.

In order to insure high-speed operation, it is necessary to provide adequate shielding against external noise. In microsystems, the compact packaging of circuits greatly increases the possibilities of stray coupling between circuits. To minimize this problem, signal leads must be located away from clock pulse lines, and power lines must be properly shielded. Additional shielding may be necessary in special cases, and local ground planes may become an absolute necessity in some systems.

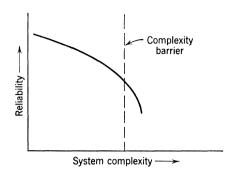

# Reliability

The complexity of modern electronic equipment is increasing at a tremendous rate, and this applies to communications equipment, weapons systems, as well as computers. Present trends indicate that increased demands on higher performance, particularly in aerospace applications, will result in increased complexity; thus correspondingly larger quantities of components will have to function simultaneously. In terms of reliability, we appear to be approaching a limit where additional complexity can be realized only if some reliability is sacrificed. Perhaps this situation can be more graphically illustrated by a curve, as shown in Fig. 2.3, for a purely hypothetical electronic system.

In the past, electrical connections have been the largest single factor contributing to unreliability of electronic equipment. In microsystems, the number of point connections of the conventional type are reduced. Of course, connections between circuit components on a silicon block have to be made. However, in such fully integrated circuits, these connections are normally made by deposited interconnecting patterns, which are inherently more reliable than individual discrete connections. Consequently, reliability can be expected to increase significantly in microsystems.

The reliability of a system depends on both the drift and the catastrophic failures of its components and subsystems. Microsystems

Fig. 2.3 Reliability—complexity curve for a hypothetical system.

offer a large measure of relief from catastrophic failures, but with drift failures conventional engineering considerations still largely apply. Drift failures can best be combated by introducing sufficiently wide component-tolerance margins in circuit designs. However, the price of component tolerances is increased circuit power dissipation. It is therefore quite evident that these trade-offs must be carefully weighed in terms of overall reliability in the design of a system.

One school of thought advocates redundancy as a means of handling catastrophic failures. There are three types of redundancies—(1) component, (2) logic, (3) standby—which can be used either individually or in suitable combinations. In component redundancy, a group of components can be used to perform a function that would normally be accomplished by a single component. When any component within the group fails, the external characteristics of the group naturally change, but it can still perform its intended function. This type of redundancy can be readily obtained with integrated circuitry. Logical redundancy is basically a majority-decision-type of redundancy. The logical output of a circuit block is established by the majority of the logical inputs to the block. In standby redundancy, a standby unit is always available for each subsystem. A failure of the subsystem is detected by a detection device, which then actuates a transfer device which, in turn, switches out the failed subsystem and switches in the standby unit. It is quite clear that whatever philosophy of redundancy is adopted, microsystems greatly increase both the technical and economic possibilities of incorporating them in complex systems.

#### Serviceability and Maintenance Problems

Servicing and maintaining a complex electronic system is a major challenge, even using conventional components. In microsystems, using integrated circuits, the problems can be compounded. Evidently, it is impossible to replace a defective component in an integrated circuit. The entire circuit must be treated as a single component, and a faulty one must be replaced by a known good component circuit. A throw-away philosophy of maintenance, therefore, appears Since several circuits would often be combined into a module or a subsystem, it may become necessary to discard a whole subsystem. This is obviously an expensive proposition and one that merits very careful study in the early stages of systems design. keep this cost to a minimum, it is desirable to keep the number of circuits per module as low as possible. However, to fully exploit the advantages of the smaller number of interconnections possible with microsystems, it is necessary to incorporate as large a number of circuits as possible within a module. These conflicting requirements must be resolved in such a manner that the reliability goals are satisfied within the economic boundaries of production and maintenance in the field.

Another maintenance problem is accessibility. Because integrated circuits are inherently small, physical handling becomes a very serious problem. Removing a module from a system and replacing it with a new one would require special tools and equipment which would ensure that the modules are not damaged in the process.

#### Cost Considerations

Initially, integrated circuits can be expected to be more expensive than similar circuits built out of conventional components. Thus the first significant applications would probably be in military-sponsored programs. Two reasons account for the high initial cost. First, the semiconductor industry has put in a sizable investment in the research and development of the various processes. This would naturally be reflected in the initial cost. Second, at the present time, the process yield is relatively low, and this means that the unit cost will be higher.

However, there is good reason for optimism too. As the processes are improved, the higher yields will bring the cost down. Furthermore, during manufacture, the same process run usually forms all or most of a certain type of circuit component on an integrated circuit substrate. This simultaneous fabrication of all diffused or deposited elements means that all elements of that run tend to be uniform. Thus, if an element is good, chances of the rest being good are pretty

high. This is a major advantage of this technique which offers possibilities of substantial price reductions. The price of integrated circuits will favorably compete with other forms of circuits very soon.

## REFERENCES

- H. W. Henkels, "What are Microsystems?," Electrical Engineering, July 1961, pp. 482.

- 2. Peter B. Meyers, "A Survey of Microsystem Electronics," Paper presented at the *Joint IRE-AIEE-ACM Computer Conference*, Los Angeles, California, May 9-11, 1961, National Joint Computing Committee.

- 3. J. D. Meindl, and H. Jacobs, "Microelectronic Systems Engineering," *Electrical Engineering*, July 1961, pp. 484–486.

$\begin{array}{c} \text{section } 2 \\ \end{array}$  Techniques and processes

# Review of fundamental semiconductor processes

Engineers who design circuits for equipment manufacturers, of course, have a reasonably good understanding of the physical processes involved in semiconductor devices—diodes and transistors. By far the great majority of them have a rather limited understanding or appreciation of the various processes associated with the manufacture of these devices, mainly because this knowledge is not an absolute prerequisite for the design of conventional circuits. Data supplied by the vendors and supplemented by the user's own reliability data, test information, and past experience provide sufficient material for the design of circuits. The demands of integrated circuits are more exacting, and it is imperative that both the circuits and the systems designers acquaint themselves, to some degree, with the fabrication processes, since their design efforts will be largely influenced and directed by the manufacturer's capabilities.

The purpose of this chapter is to briefly describe most of the commonly used processes. Detailed descriptions of the processes are beyond the scope of this book. Rather, the objective is to list the processes (and their simple descriptions) in such a manner as to provide some background for the material that follows in the later chapters. To this end, the processes are divided into two major categories: (1) semiconductor processes—those involved in the fabrication of the semiconductor devices and the various functions associated with them; and (2) thin-film processes—processes which are external to the semiconductors or other substrate material.

This chapter covers only the first category. Thin-film processes are covered in the next chapter. Also, in order to facilitate the understanding of the processes from the circuits point of view, both the semiconductor and the thin-film processes are further subdivided and investigated in terms of their being able to provide the familiar functions of (1) active elements, (2) resistive elements, (3) capacitive elements, (4) inductive elements, (5) conduction between circuit elements, (6) circuits and components isolation.

#### 3.1 ACTIVE ELEMENTS

# Surface Passivation and Planar Technology

The conventional mesa transistor has some serious limitations. The electronic properties of the crystal are sensitive to impurity conditions at the surface and the ambient humidity. As a result, the operating characteristics of the device suffer degradation and wide variations. Unfavorable environments introduce chemical impurities, that is, large quantities of acceptor, donor, and lifetime carriers at the surface of the semiconductor. These impurities are very loosely bound and so have high mobility as compared to the strongly bound impurities in the material which has relatively low mobility. The thin oxide layer on the semiconductor material tends to attract moisture. In ambient humidity, this produces a solution of ions and dipoles which have high mobility. The hermetically sealed package does not remedy this situation. It merely restricts these detrimental environmental factors to a confined location.

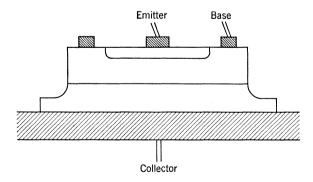

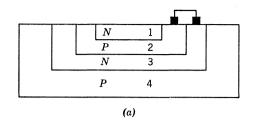

Figure 3.1 shows a cross-sectional view of the typical mesa transistor, where the base dopant is uniformly diffused in the entire top area of the silicon material, which forms the collector of the transistor. The emitter is diffused at the desired location. The chip is then etched to give the desired mesa shape. The reason for the mesa is to limit the area of the base-collector junction to the point desired by the electrical characteristics of the device. Metallic contacts are alloyed into the base and emitter areas and gold leads are attached on the metalized surfaces by thermocompression bonding. The collector is soldered to the header. As a result of the mesa etching process, both the base-

Fig. 3.1 Typical mesa transistor.

collector and the emitter-base junctions are now exposed and thus easily accessible to ambient environments or to mechanical damage in handling (Fig. 3.1). This results in degradation of electrical characteristics, such as high reverse leakage current, low breakdown voltages, high noise figure, low betas at low currents, and low power dissipation rating.

The shortcomings of the mesa process are largely reduced by the planar or surface passivation technique. In this technique, the lateral flow of the base dopant in the semiconductor is restricted from the start to the extent desired by the transistor requirements, thereby eliminating the need for mesa etching later on. The term *planar* or surface passivation can be defined as the growth of a chemical film layer on the surface of a semiconductor material which provides electrical stability of the surface and isolates the surface from the electrical and chemical conditions in the environment, which degrade device characteristics and thereby adversely affect its operating performance.

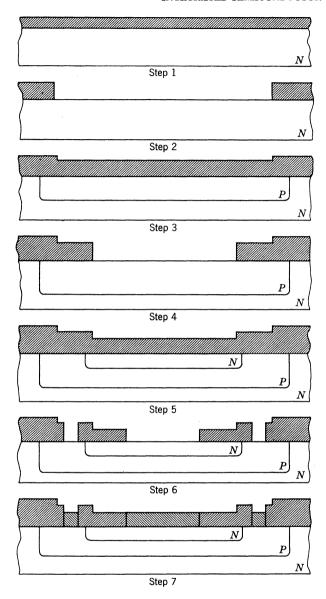

Figure 3.2 illustrates the steps involved in the fabrication of the planar transistor.<sup>2</sup> The basic N-type silicon substrate, is shown in Step 1 with a thin layer of silicon oxide on its surface. Using standard photo-processing techniques, the oxide is selectively etched off on a series of dots, as shown in Step 2, thereby exposing the surface of the semiconductor material. The exposed surface is subjected to a vapor of the base diffusant, such as boron for a NPN transistor or phosphorus for PNP units, at a high temperature. The oxide layer limits the lateral diffusion of the dopant, as shown in Step 3, under the original oxide, usually by an amount equal to the depth of the junction. During this operation, oxygen is introduced so that the previously exposed area is reoxidized. During formation of the base-collector junction this area was protected by the first oxide layer and this junction was not exposed to contaminating environments at any stage of the process.

In Step 4, a portion of the reoxidized base area is removed by a similar masking and etching process. In Step 5 the exposed base area is subjected to a vapor of the emitter dopant, such as phosphorus, and the emitter area is again reoxidized during the process. Once again, a junction emerges under the area of the second oxidation process and is thus protected from adverse environments. This junction is, of course, the emitter-base junction of the transistor. Following this the final oxidized layer is again etched off at specific areas as shown in Step 6. Metal contacts are deposited and alloyed in as shown in Step 7. Wire leads are attached to the metalized areas by thermocompression bonding.

Fig. 3.2 Steps in the planar process: (1) passivated oxide layer on substrate; (2) part of oxidized layer is selectively etched; (3) P layer is diffused and surface is reoxidized; (4) reoxidized layer is again selectively etched off; (5) N layer for emitter is diffused and surface is reoxidized; (6) oxidized areas are again selectively etched off for contacts; (7) metal contacts are deposited and alloyed on the substrate at etched-off areas.

# **Epitaxial Techniques**

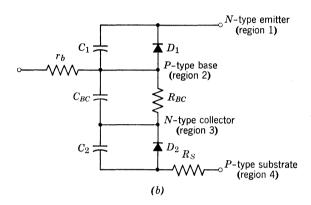

The conventional mesa transistor has the advantage of high-frequency cut-off and rugged physical construction. Its principal limitation is the fact that the semiconductor material has to be relatively thick to insure physical rigidity. Since the entire piece of semiconductor material, which is several mils thick, is cut from one large crystal, it has uniform purity and, consequently, uniform conductivity throughout its entire bulk. The degree of purity of the semiconductor material is governed by the desired electrical characteristics of the device, which is diffused on the surface. The high degree of purity in that portion of the bulk material, not used for either the emitter or the base diffusions, gives added resistance in the collector of the transistor and stores electrical charges, which slow down switching speeds. Consequently, saturation resistance is high; however, it can be lowered by using lower resistivity collector material, but only at the expense of lower breakdown rating. The conventional alloy transistor has the advantage of low saturation resistance. Epitaxial transistors combine the advantages of both the mesa and the alloy transistor without any undesirable compromise.

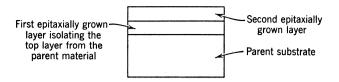

In epitaxial transistors, the original bulk material is cut from a crystal with very high electrical conductivity. This slice is then subjected to an atmosphere of hydrogen and a gaseous compound, which may be a chloride of the same semiconductor material at high temperature. This results in the deposition of a lightly doped semiconductor material on top of the original substrate material. This epitaxial layer is grown to give the right thickness for the desired

Fig. 3.3 Epitaxial planar transistor.

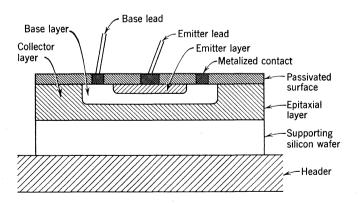

transistor, and is of the same conductivity type as the original substrate—either P or N-type. The transistor is then diffused in the epitaxial layer. Since the original substrate has low resistivity, it contributes very little resistance to the collector of the transistor. Consequently, more current can be passed through the transistor. The main advantage of this type of transistor is low saturation resistance and lower collector storage time, as compared to a similar non-The low saturation resistance makes the epitaxial epitaxial unit. transistor suitable for direct-coupled transistor logic (DCTL). thin epitaxial layer has relatively high resistivity, which gives the unit a higher voltage rating. The higher resistivity of the epitaxial layer reduces the collector capacitance quite appreciably. Reduction in saturation resistance makes it possible to use devices with smaller geometries, thereby reducing the area of the emitter. These two factors greatly increase the frequency limits of the epitaxial transistor (Fig. 3.3).

## 3.2 RESISTIVE ELEMENTS

# Substrate Resistivity (Bulk)

The easiest way to obtain resistive elements in integrated circuitry is to use the bulk resistivity of the semiconductor substrate itself. Since this resistivity can be controlled quite easily, this approach may appear very attractive and certainly very economical. However, it has some very serious shortcomings, which limit its usage in practical applications. A maximum usable resistivity of about 500 ohm-cm is possible, but this is not compatible with the present technology of fabricating either the collector or the base of the transistor. This means that it would be almost impossible to use the same substrate for both the resistors and the transistors. A more realistic upper limit is probably around 100 ohm-cm. Even then, the most compatible value would not be greater than 50 ohm-cm. Another drawback of this approach is that the bulk material has a fairly complicated temperature coefficient. Occasionally, this temperature dependence can be used advantageously for compensation in some circuits.<sup>3</sup>

#### **Diffused Resistors**

A very useful resistor can be obtained by diffusing a thin layer in the parent semiconductor material, and back-biasing the junction. Two major advantages of this type of resistor are (1) by ingenious layouts, the resistor can be located adjoining another element such that additional interconnection between the two components can be eliminated, and (2) by controlling the diffusion profile and the doping levels, the temperature coefficients can be controlled such that either negative, positive, or virtually zero coefficients can be realized at room temperature.<sup>3</sup> Diffused resistors can be of great value in applications where tolerances are not very critical.

The two principal disadvantages of this type of resistor are (1) the resistance is sensitive to the back-biasing voltage, with wide variations resulting in practical circuits, and (2) the voltage drop in the resistor generates a self-back-biasing component, which can further affect the resistance value. This also provides a means of obtaining electrically variable resistance, which may be advantageously used in some circuit applications.

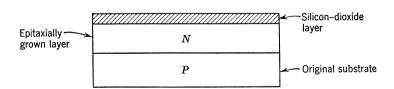

# **Epitaxially Grown Layers**

Resistive regions with desired characteristics have been grown on semiconductor substrates using epitaxial techniques. This technique requires masking for obtaining the right geometry. Back-biasing is required, so the advantages and the disadvantages of back-biasing, which were previously discussed, apply here just as they do with the diffused resistor. However, better control of the junction characteristics is possible with the epitaxial technique, as compared to the diffusion technique.

## 3.3 CAPACITIVE ELEMENTS

# **Diffused Back-Biased Junctions**

At the present time, perhaps the easiest method of obtaining capacitors in integrated circuits is by back-biasing diffused junctions. The depletion layer at the junction forms the dielectric, and values in the neighborhood of  $1 \text{ v-}\mu\text{f/cm}^2$  have been successfully realized for step junctions at low voltages. It is quite apparent that the value of capacitance obtained will depend on the width of the depletion layer, thus it is important to consider the factors which affect the depletion layer width.

The width of the depletion layer is primarily determined by the impurity concentration gradient on either side of the junction, and the reverse voltage applied across the junction. The diffusion process produces a graded junction which means that, for a given value of reverse voltage, a diffused capacitor would tend to have lower values of capacitance as compared to capacitors fabricated with other techniques. The physical location of the diffused junction in the semiconductor material is sometimes very critical. If the junction is located such that current flows parallel to the junction but outside the depletion layer, then, the bias on the junction itself would not be uni-

form. This current would be particularly troublesome if it flows through the bulk resistor and if the junction in question is not biased. In such a situation, the floating junction will tend to conduct in order to stabilize the potential at one end, and in so doing it will back-bias the rest of the junction. This can also be used to advantage in some circuits.

## Alloyed Back-Biased Junctions

Capacitors made by back-biasing alloyed junctions approach a step junction much more closely than do the diffused back-biased junction units. As a result, higher values of capacitance can be obtained with relatively lower back-bias voltages. This is due to the fact that the impurity concentration on one side of the junction is effectively the same as or close to that of the parent substrate material. Thus a steep impurity gradient can be readily obtained across the junction. The impurity concentration in the substrate is low, thus, at large values of reverse bias voltage, the width of the depletion layer can be as large as in the diffused junction capacitor.

# **Epitaxial Back-Biased Junctions**

Capacitors obtained by applying back-bias to epitaxially grown junctions are still in their infancy, but work done to date promises some encouraging possibilities. In this case, the high impurity concentration of N-type on one side can approximate the step junction very closely to the high impurity concentration of P-type on the other. Consequently, at low values of reverse bias, a relatively high value of capacitance is obtainable. This means that the voltage dependence of the capacitance is reduced to some extent and it also becomes more controllable and predictable.

## 3.4 INDUCTIVE ELEMENTS

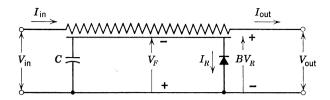

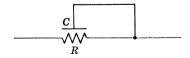

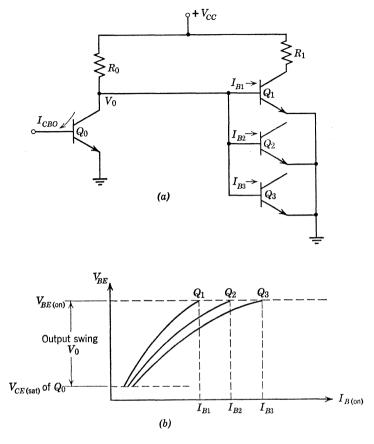

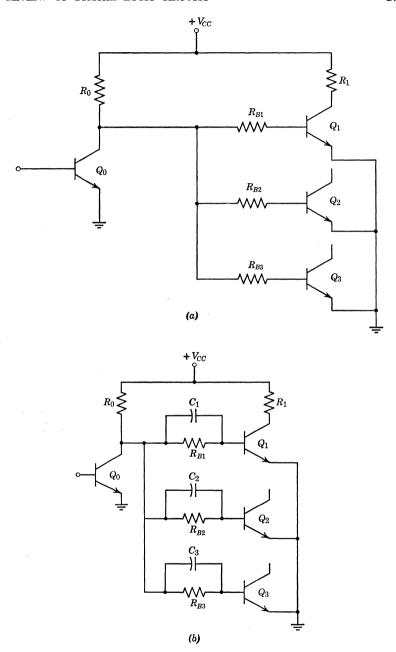

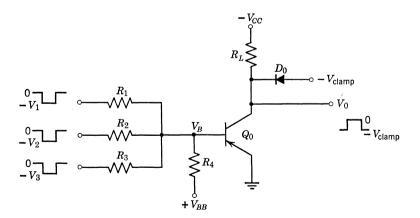

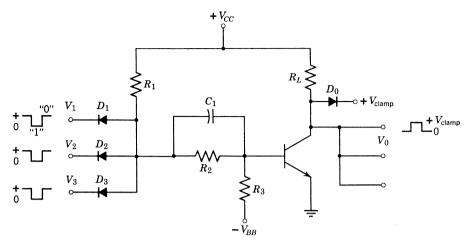

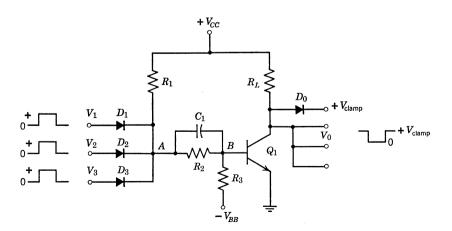

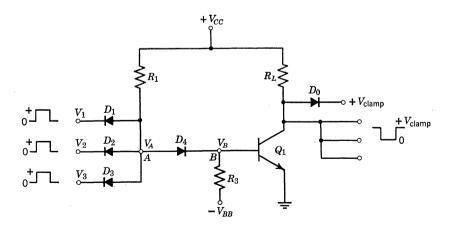

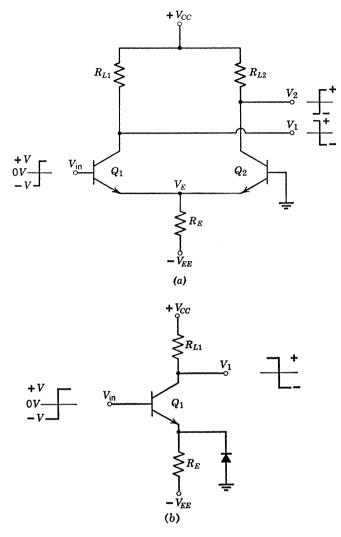

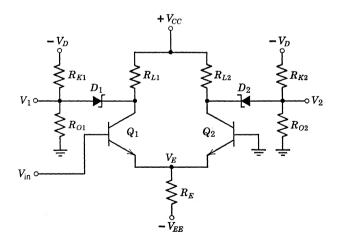

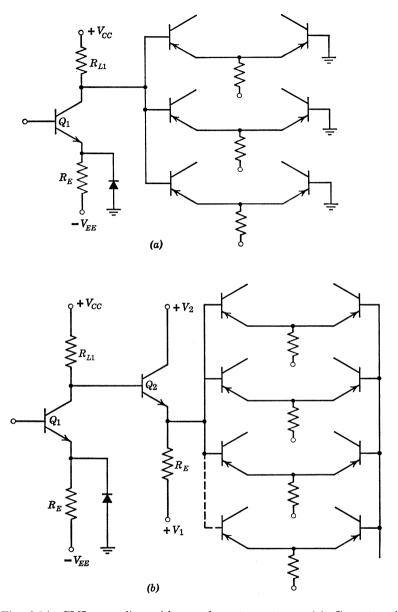

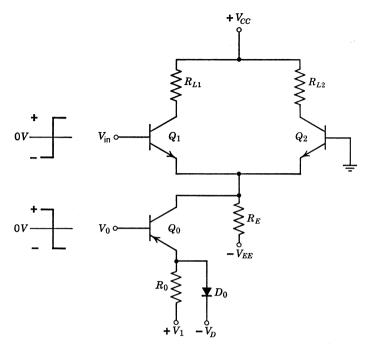

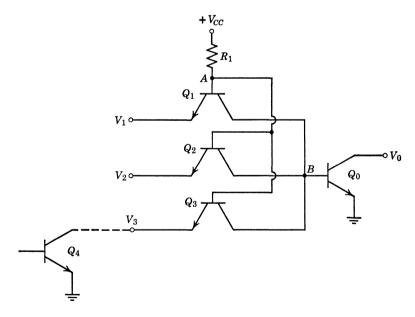

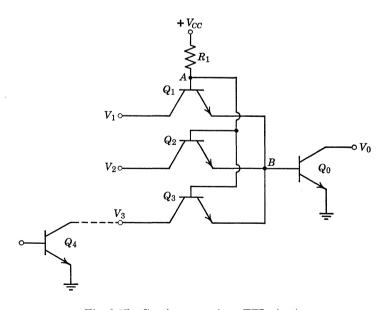

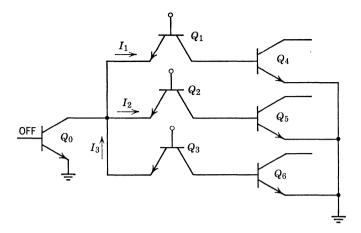

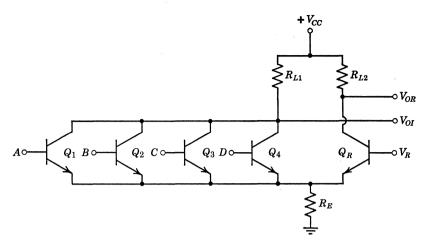

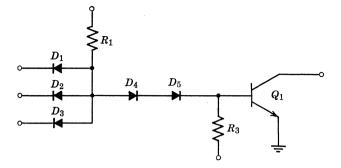

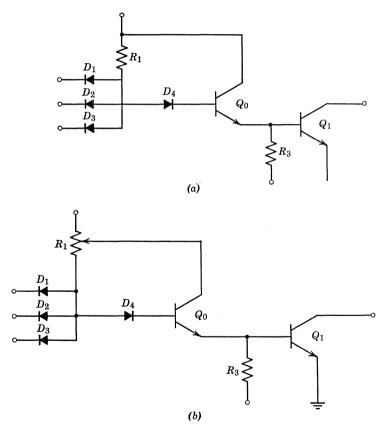

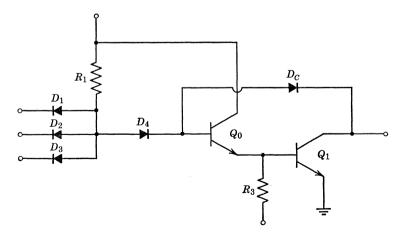

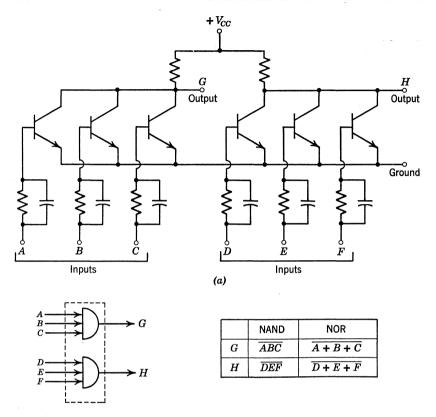

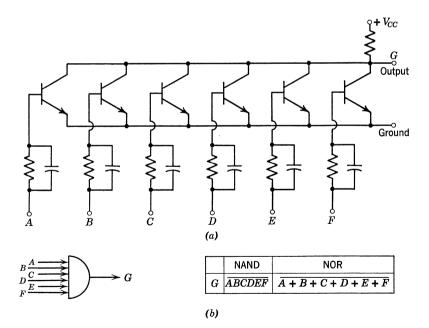

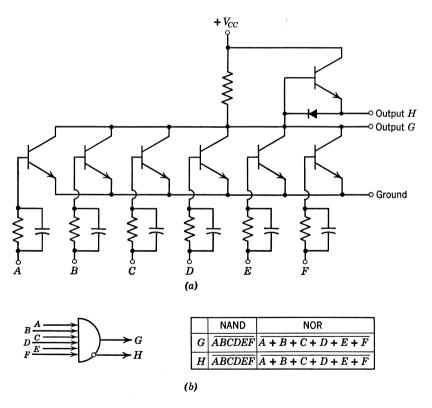

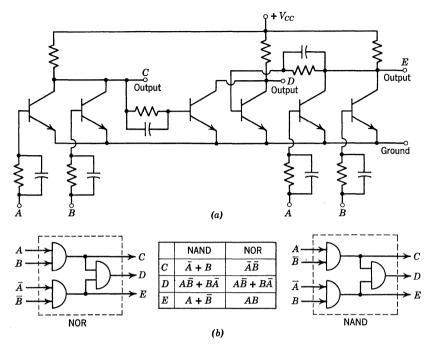

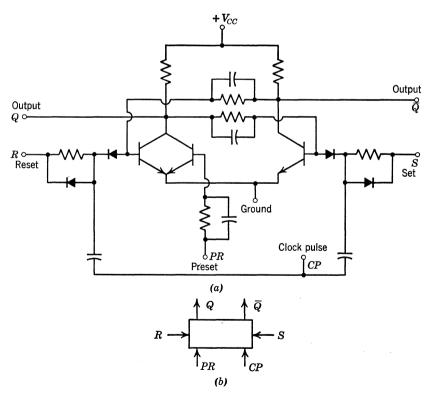

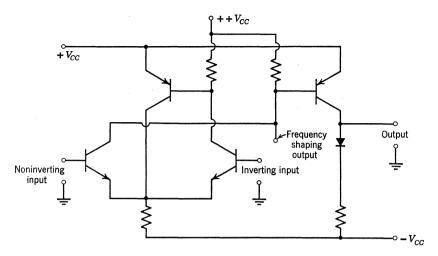

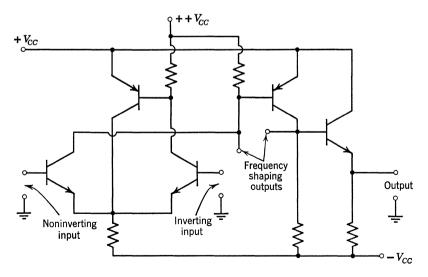

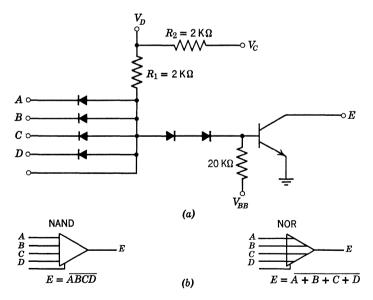

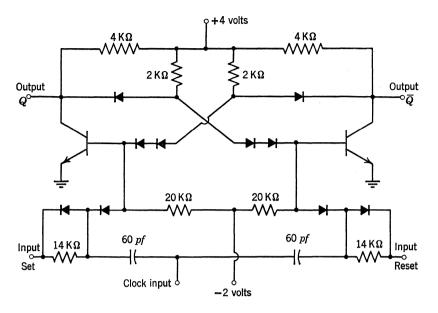

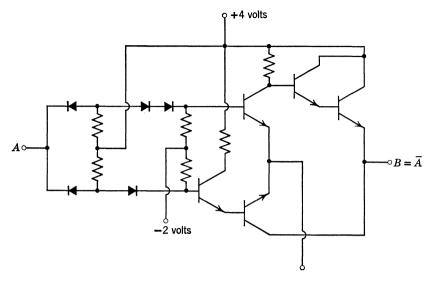

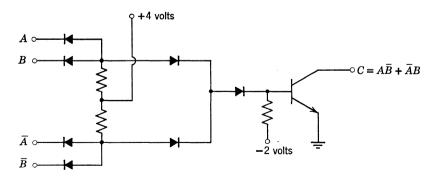

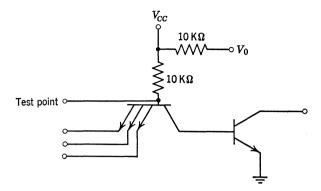

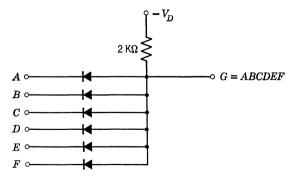

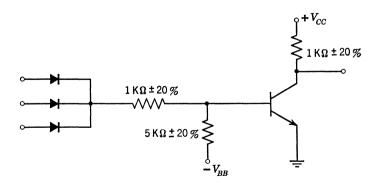

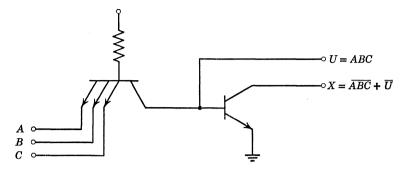

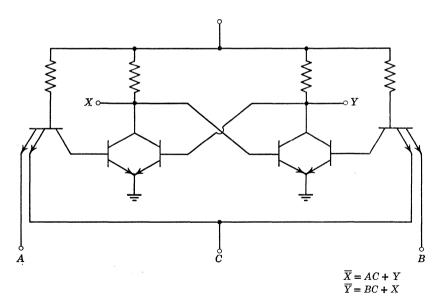

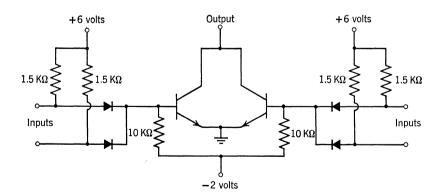

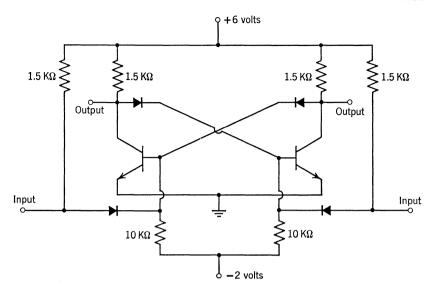

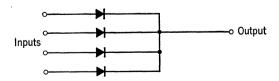

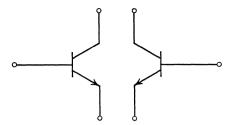

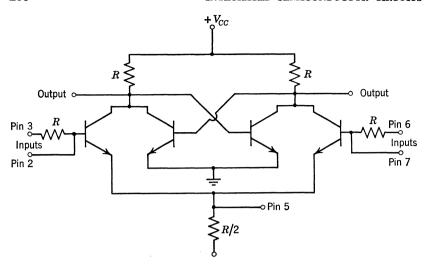

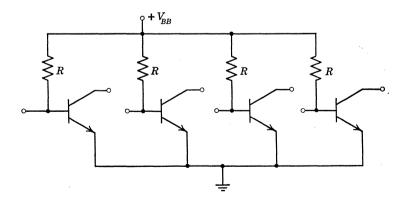

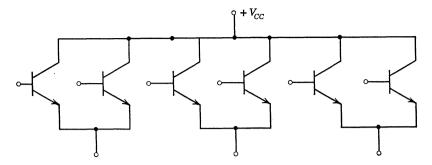

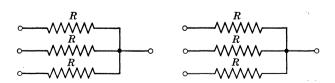

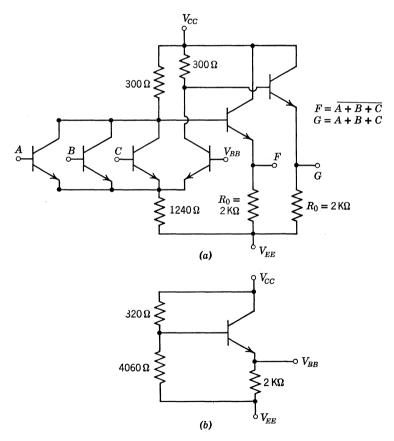

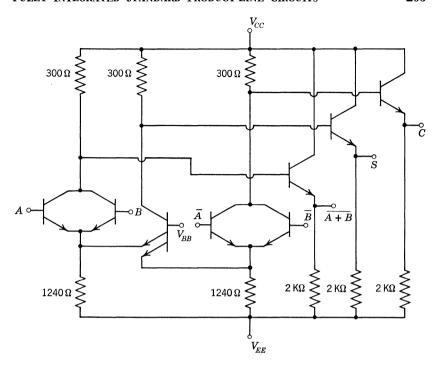

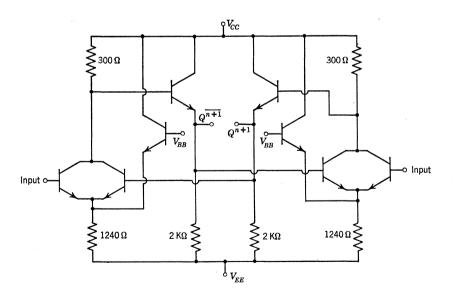

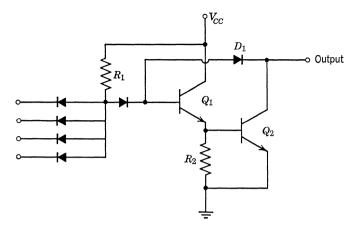

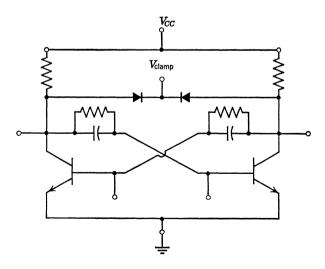

## The Inductance Diode