An Introduction to the 980 Series **Minicomputer Prepared By TI-MIX** ll '11-11111 .... UTH: MAN 9808 Texas instrume TI-MIX

### To the Reader –

When I first became involved with the TI 980 a few months ago, I decided to write a collection of notes and code samples for my own use. The project eventually evolved into this manual which I hope will be of use to new programmers. The pressures of time and other work caused the effort to be cut short, so many of the code samples have not been tested, and certain statements may be in error. I would sincerely appreciate it if those of you who find errors would assist me in correcting them by responding on the tear-out sheet which is bound in this publication.

I acknowledge my indebtedness to you in advance in addition to those who have already contributed a great deal. In particular, I would like to thank Jerry Junkins of the Equipment Group for supporting the project, Floyd Burton of TI-MIX for publishing the manual, Wilburn Jones of the Services Group for technical illustrations, Jim Simpfenderfer and Jon Jentink of the Equipment Group for reading sections of the manuscript, and Fred Wedemeier of the Equipment Group for answering my incessant questions.

S.N.S.

May our efforts be useful to you, the reader, in some way.

Fred thanks your hart

### About the Author -

Sue Nickerson Stidham has been involved with many aspects of computer technology. She holds a Ph.D. in physical chemistry from the University of Massachusetts (Amherst) and an A.B. in chemistry and physics from Smith College. She was assistant professor of Computer Science at the University of Massachusetts, an instructor in physics at the University at Bridgeport, Connecticut and at Mount Holyoke College. She held a Petroleum Research Fund Fellowship for 2 years.

Dr. Stidham was a National Science Foundation stipend recipient in 1963 at the Winter Institute in quantum chemistry and solid-state physics, Gainesville, Florida, and in 1970 at CASSAD, (computer-assisted system simulation and design), Houston, Texas. She joined Texas Instruments in 1973.

# TABLE OF CONTENTS

# Section

.

.

| 1 | INTRODUCTION TO ASSEMBLY LANGUAGE                              |

|---|----------------------------------------------------------------|

|   | 1-1 Assembly Language Programming: What It Is And Why Learn It |

|   | 1-2 Assembly Language vs. Machine Language                     |

|   | 1-3 Organization of a Computer System                          |

|   | 1-4 Octal and Hexadecimal Number Systems                       |

|   | 1-5 Hexadecimal Addressing Scheme                              |

|   | 1-6 Memory Organization and the Program Counter                |

|   | 1-7 Pseudo-Operations and Assembly                             |

|   | 1-8 The Role of the Accumulator in Execution                   |

|   | 1-9 Assembling, Loading and Executing the Program              |

|   | 1-10 Finding the Answer                                        |

| 2 | MACHINE WORDS AND THE BINARY NUMBER SYSTEM                     |

|   | 2-1 What's in a Word                                           |

|   | 2-2 Number System Conversion Between Binary and Hexadecimal    |

| • | 2-3 Conversion to and from Decimal                             |

|   | 2-3.1 Hexadecimal to Decimal                                   |

|   | 2-3.2 Decimal to Hexadecimal                                   |

|   | 2-3.3 Conversion of Fractions                                  |

|   | 2-4 Number Conversion to and from Octal                        |

|   | 2-4.1 Number Conversion Between Binary and Octal               |

|   | 2-4.2 Conversions Between Octal and Hexadecimal                |

|   | 2-4.3 Octal to Decimal                                         |

|   | 2-4.4 Decimal to Octal                                         |

|   | 2-5 Conversions Between Binary and Decimal                     |

|   | 2-6 Positive and Negative Data Values                          |

|   | 2-6.1 The Sign Bit                                             |

|   | 2-6.2 Negative Numbers                                         |

|   | 2-6.3 Two's Complement Arithmetic                              |

| 3 | INTRODUCTION TO 980 ASSEMBLY LANGUAGE                          |

|   | 3-1 Elementary Programming Considerations                      |

|   | 3-2 The Instruction Format Skeleton                            |

|   | 3-3 Data Declarations                                          |

|   | 3-4 Two Addressing Modes, P-Relative and Immediate             |

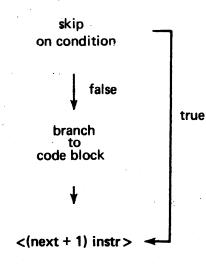

|   | 3-5 Transfer of Control: Branch and Skip                       |

|   | 3-6 The Assembly Process and Some Assembler Directives         |

|   | 3-7 Register Organization and Definition                       |

|   | 3-8 Notation Used in Describing Instructions                   |

|   | 3-9 A Basic Group of Instructions                              |

|   | 3-9.1 Idle Instruction (IDL)                                   |

# Section

4

.

~

/

| 3-9.2 Register-To-Memory and Memory-To-Register Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-9.3 Register-To-Register Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                            |

| 3-9.4 Unconditional Branch Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

| 3-9.5 Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

| 3-9.6 A Sample Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

| 3-9.7 IMO and DMT Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                            |

| 3-9.7 MO and DMT instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |

| 3-10.1 Register Skips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                            |

| 3-10.2 Loops, Counters, and Indexed Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

| 3-11 Sample Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            |

| 3-12 The Index Register and its Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            |

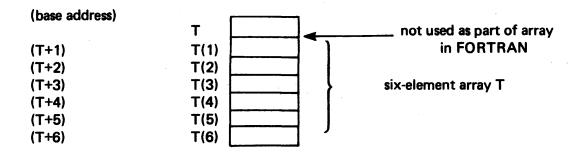

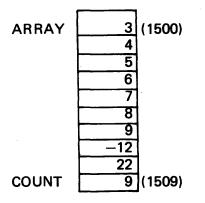

| 3-12.1 Handling an Array: A Typical Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                            |

| 3-12.2 The Index Register (X)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

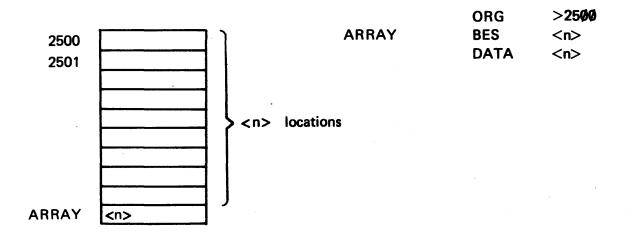

| 3-12.3 Setting up the Data for an Array Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |

| 3-12.3.1 Incrementing Index Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

| 3-12.3.2 Decrementing Index Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                                                                                         |

| 3-12.4 Address Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46                                                                                                                                                         |

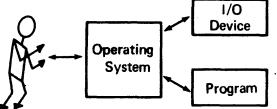

| 3-13 The Bare Machine vs. the Basic Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |

| 3-14 Use of the Basic Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS<br>4-1 Summary of Model 980 Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STER<br>                                                                                                                                                   |

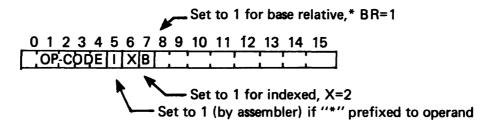

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register                                                                                                                                                                                                                                                                                                                                                                                                                                          | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution                                                                                                                                                                                                                                                                                                                                                                              | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only                                                                                                                                                                                                                                                                                                                      | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive                                                                                                                                                                                                                                                                                     | STER<br>                                                                                                                                                   |

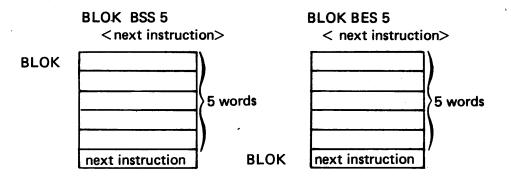

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage                                                                                                                                                                                                                                                     | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive                                                                                                                                                                                                                                                                                     | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage                                                                                                                                                                                                                                                     | STER<br>                                                                                                                                                   |

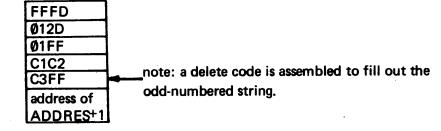

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration                                                                                                                                                                                                                      | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration         4-6.4 Print Control Directives                                                                                                                                                                               | STER<br>                                                                                                                                                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration         4-6.3 Equate                                                                                                                                                                                                 | STER<br>51<br>52<br>53<br>53<br>53<br>54<br>54<br>56<br>56<br>56<br>57<br>58<br>57<br>58<br>58<br>58<br>59<br>61<br>61<br>61                               |

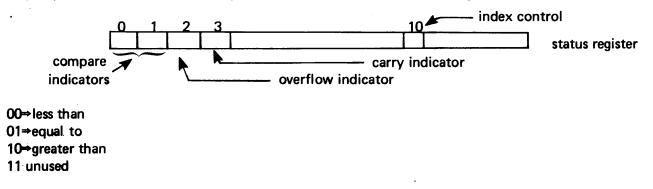

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration         4-6.3 Equate         4-6.4 Print Control Directives         4-7 The Status Register: Overflow, Carry, and Compare                                                                                            | STER<br>51<br>52<br>53<br>53<br>53<br>54<br>56<br>56<br>56<br>56<br>57<br>58<br>57<br>58<br>58<br>59<br>61<br>61<br>61<br>62                               |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration         4-6.3 Equate         4-6.4 Print Control Directives         4-7 The Status Register: Overflow, Carry, and Compare         4-7.1 Carry and Overflow                                                           | STER<br>51<br>52<br>53<br>53<br>53<br>54<br>54<br>56<br>56<br>56<br>56<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58                   |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration         4-6.3 Equate         4-6.4 Print Control Directives         4-7 The Status Register: Overflow, Carry, and Compare         4-7.1 Carry and Overflow                                                           | STER<br>51<br>52<br>53<br>53<br>53<br>54<br>54<br>56<br>56<br>56<br>57<br>58<br>58<br>58<br>58<br>58<br>59<br>61<br>61<br>61<br>61<br>61<br>62<br>63<br>65 |

| TI MODEL 980 ADDRESSING MODES AND THE STATUS REGIS         4-1 Summary of Model 980 Characteristics         4-2 Effective Address         4-3 Address Modes: Immediate; Indirect and Indexed P-Relative         4-4 Normal and Extended Format         4-5 The Base* Register         4-5.1 Base Register Relative Assembly and Execution         4-5.2 Base Register Used at Execution Time Only         4-6 The Origin Directive         4-6.1 Reserving Storage         4-6.2 Data Declaration         4-6.3 Equate         4-6.4 Print Control Directives         4-7 The Status Register: Overflow, Carry, and Compare         4-7.1 Carry and Overflow         4-7.2 Program to Test Carry and Overflow Behavior | STER       51                                                                                                                                              |

# Section

.

.

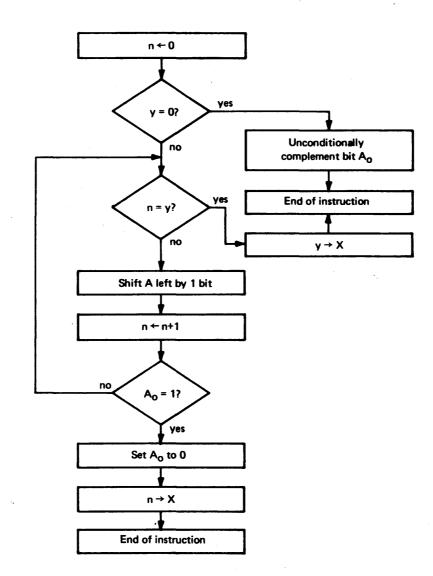

| 5 | REGISTER SHIFT AND DOUBLE-LENGTH                           |

|---|------------------------------------------------------------|

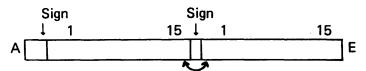

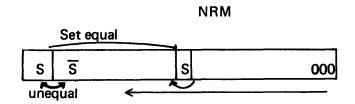

|   | 5-1 Single Register Shift Operation Format                 |

|   | 5-2 Circular Shifts                                        |

|   | 5-3 Arithmetic Shifts                                      |

| • | 5-3.1 Arithmetic Right Shift                               |

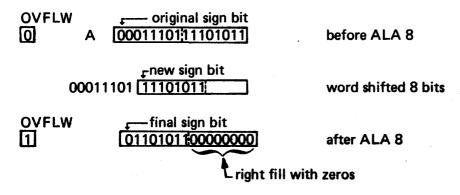

|   | 5-3.2 Arithmetic Left-Shift                                |

|   | 5-4 Logical Shifts                                         |

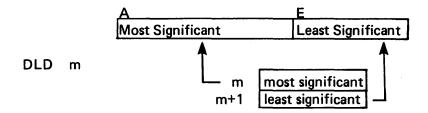

|   | 5-5 Double Length Register Instructions                    |

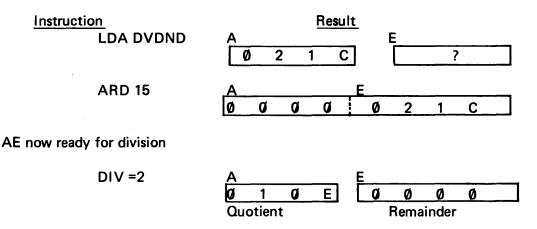

|   | 5-5.1 Multiply and Divide Instructions                     |

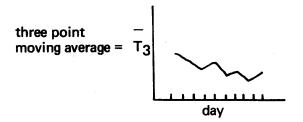

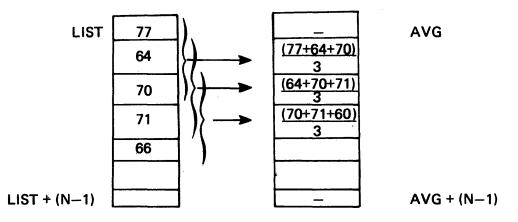

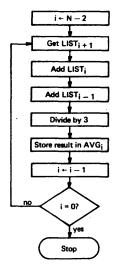

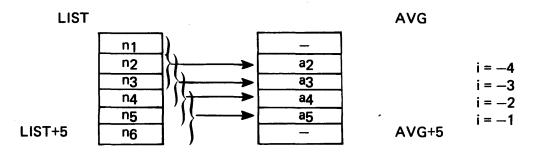

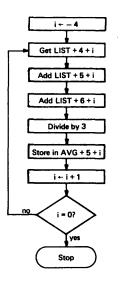

|   | 5-5.2 The Moving Average Problem                           |

|   | 5-5.3 Shift Operations in a 32-Bit Register                |

|   | 5-5.4 Double-Length Shift in Preparation for Divide        |

|   | 5-5.5 Division by 2 or any of its Powers                   |

|   | 5-6 Double Precision Arithmetic                            |

|   | 5-7 Execution Times and the Space-Versus-Time Tradeoff     |

| • |                                                            |

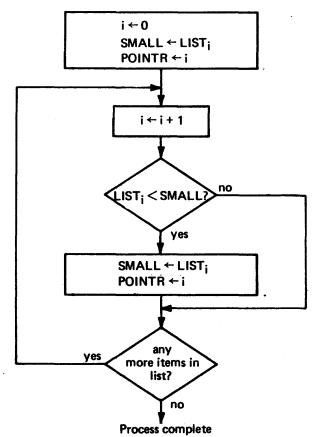

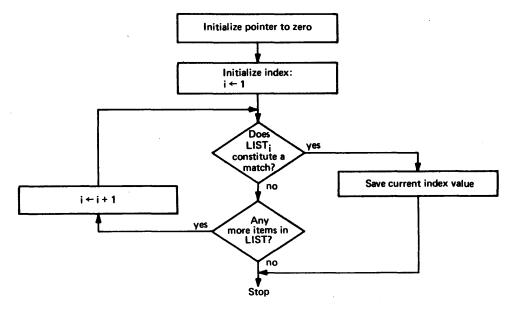

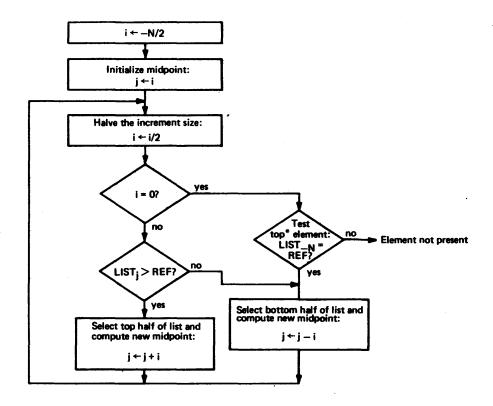

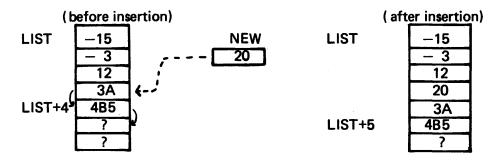

| 6 | ARRAY TECHNIQUES: SORTS, SEARCHES, AND STACKS              |

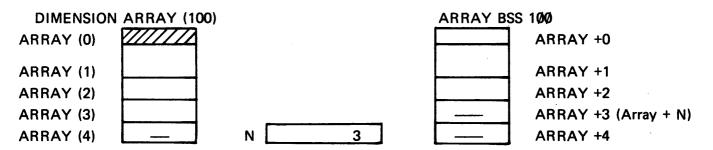

|   | 6-1 Array Manipulation Through Indexing                    |

|   | 6-2 Indexed B-Relative Mode                                |

|   | 6-3 Variable-Length Arrays                                 |

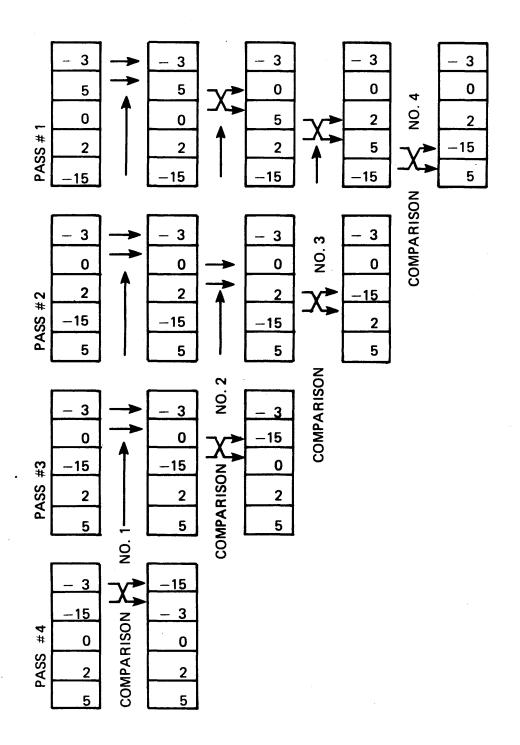

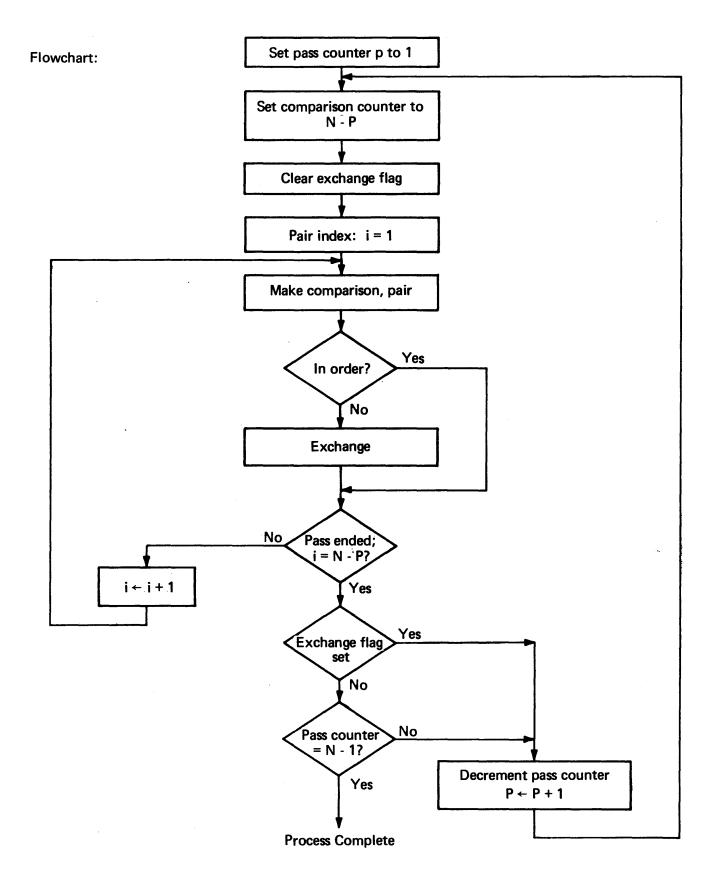

|   | 6-4 The Exchange Sort (Bubble Sort) Technique              |

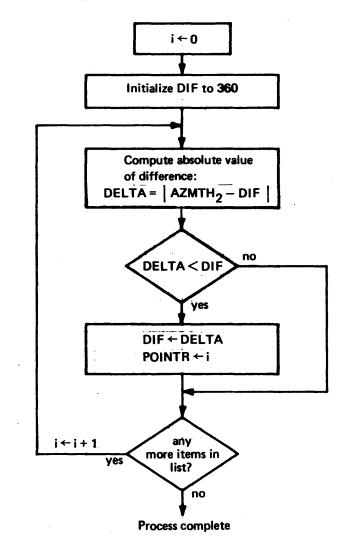

|   | 6-5 Search Techniques                                      |

|   | 6-6 Sequential Search                                      |

|   | 6-7 Binary Search                                          |

|   | 6-8 Searches Using Hash Technique                          |

|   | 6-9 Insertion and Deletion in a List                       |

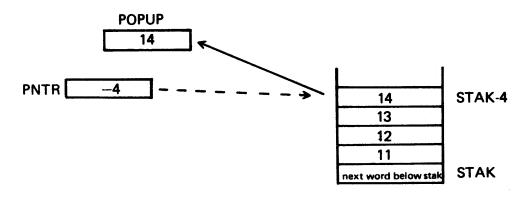

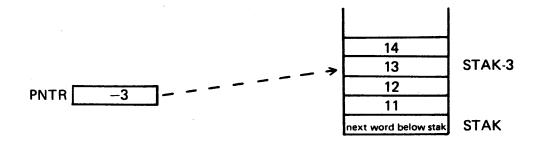

|   | 6-10 The Pushdown Stack                                    |

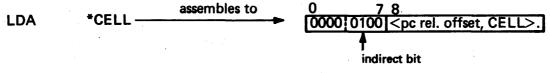

|   | 6-11 Indirect Addressing                                   |

|   | 6-12 Summary: Three Methods of Array Handling              |

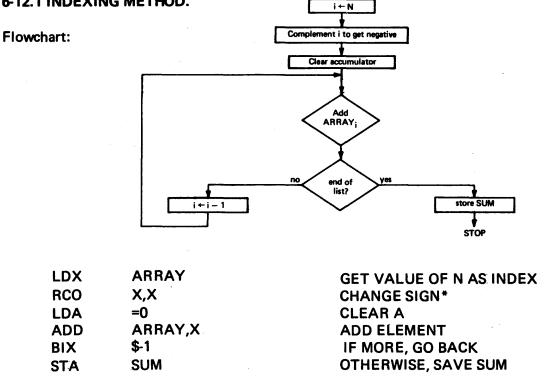

|   | 6-12.1 Indexing Method                                     |

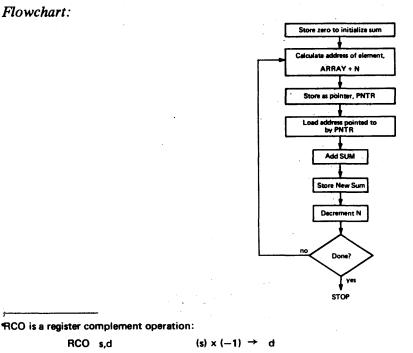

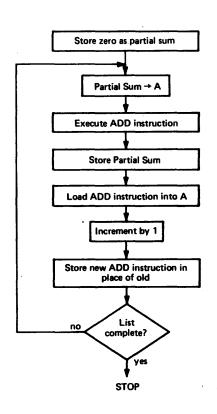

|   | 6-12.2 Self-Modifying Code ("Impure Procedure")            |

|   |                                                            |

| 7 | ASCII DATA, BUFFERS, AND I/O SERVICE CALLS                 |

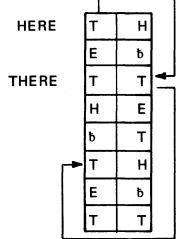

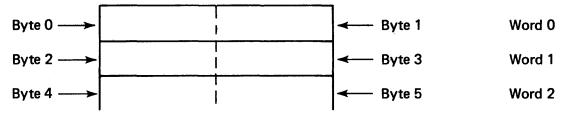

|   | 7-1 Introduction to Character Strings                      |

|   | 7-2 Character Strings in 980AL: The ASCII Data Declaration |

|   | 7-3 Non-Printing Characters                                |

|   | 7-4 Buffers                                                |

|   | 7-5 Bytes and Byte Manipulation                            |

|   | 7-5.1 Move Character String (MVC)                          |

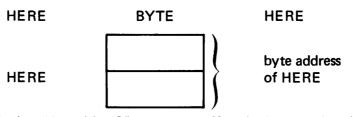

|   | 7-5.2 Generate Byte Address: The Byte Declaration          |

|   | 7-5.3 Compare Logical Characters (CLC)                     |

|   |                                                            |

| С | oot | ·in | n |

|---|-----|-----|---|

| J | ect | .10 |   |

8

9

•

.

| 7-6 Conversion From Internal to External Format: Integers                  | 115 |

|----------------------------------------------------------------------------|-----|

| 7-7 Hash Totals                                                            |     |

| 7-8 I/O Service Calls                                                      |     |

| 7-8.1 Service Calls vs. The Bare Machine                                   |     |

| 7-8.2 I/O and Program Termination Using Supervisor Service Calls           |     |

| 7-8.3 Definition of Service Calls With OPD                                 |     |

| 7-8.4 Program Skeleton: I/O and Program Termination Using Supervisor Calls |     |

|                                                                            |     |

| SUBROUTINES                                                                |     |

| 8-1 The Subroutine: A Labor-Saving Device                                  | 127 |

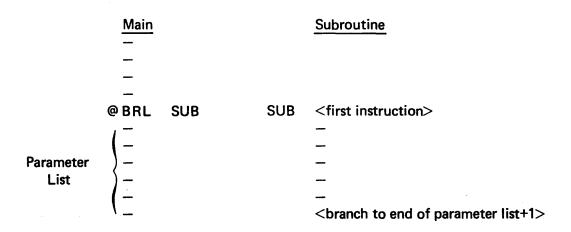

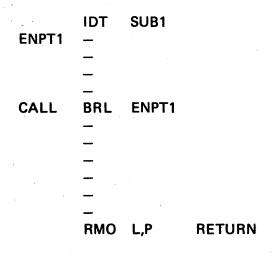

| 8-2 The Primitive Subroutine Linkage Problem                               | 129 |

| 8-3 Parameter Passing to a Primitive Subroutine                            | 130 |

| 8-3.1 Parameter Passing via Registers (Call by Value)                      | 130 |

| 8-3.2 In-Line Parameter List (Call by Address)                             |     |

| 8-3.2.1 Fixed Number of List Entries                                       | 131 |

| 8-3.2.2 Variable Number of List Entries                                    | 132 |

| 8-3.3 In-Line Address of Parameter List                                    | 133 |

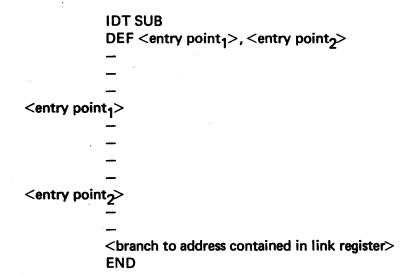

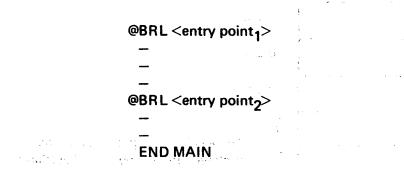

| 8-4 Formal Structure of a Subroutine                                       | 133 |

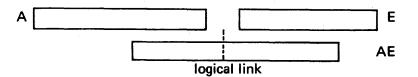

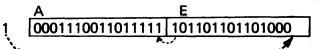

| 8-5 Entry Points and External Symbols: DEF and REF                         | 134 |

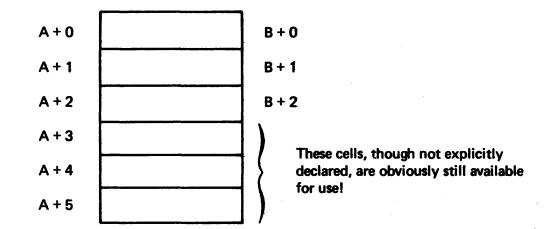

| 8-6 Parameter Passing and Common Storage                                   | 135 |

| 8-6.1 Common Storage                                                       | 135 |

| 8-6.2 Via Registers (Call by Value)                                        | 136 |

| 8-6.3 In-Line Parameter Lists (Call by Address)                            | 136 |

| 8-6.4 Call by Name                                                         | 136 |

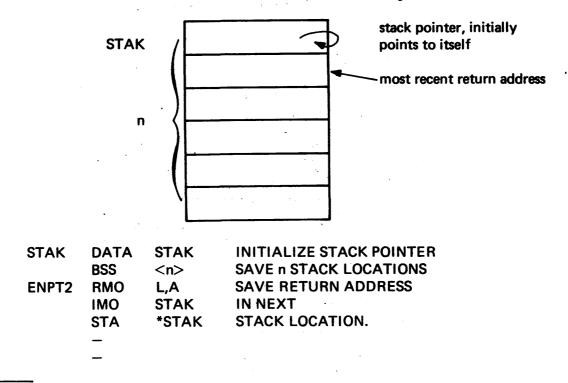

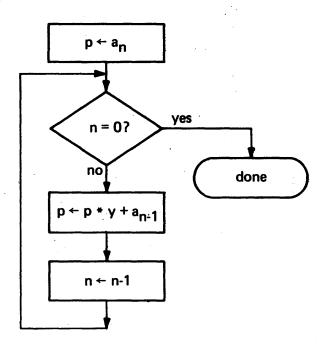

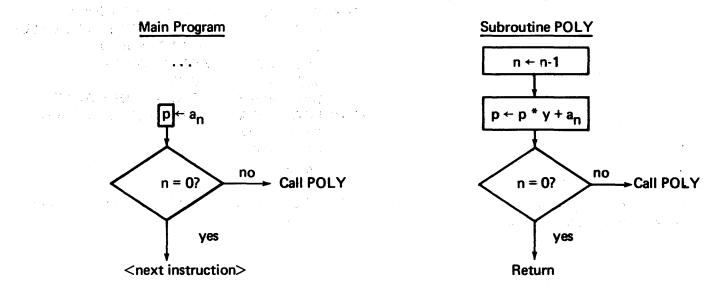

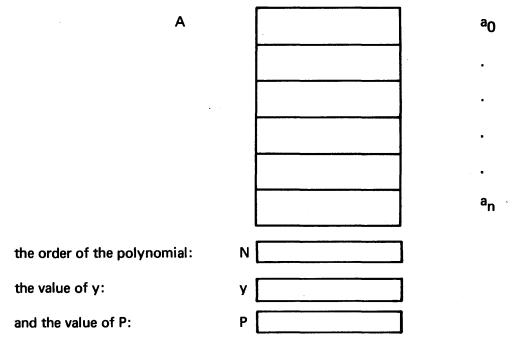

| 8-7 Recursive Calls to a Primitive Subroutine                              | 138 |

| 8-7.1 Recursion Using the X-Register                                       | 139 |

| 8-7.2 Recursion Using Indirect Addressing                                  | 139 |

| 8-7.3 Example of a Recursive Subroutine                                    | 140 |

|                                                                            |     |

| LOGICAL OPERATIONS, BIT MANIPULATION, MASKS, AND FLAGS                     |     |

| 9-1 Truth Tables                                                           | 143 |

| 9-2 Logical Operations                                                     |     |

| 9-2.1 Memory-To-Register Logical Operations                                |     |

| 9-2.2 Register-To-Register Operations                                      |     |

| 9-2.2.1 Complementing Operations                                           |     |

| 9-3 Bit Operations                                                         |     |

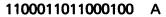

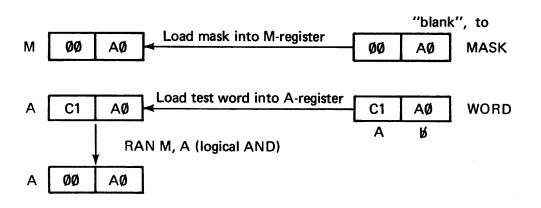

| 9-4 Masking: One Practical Use of Logical Operations                       |     |

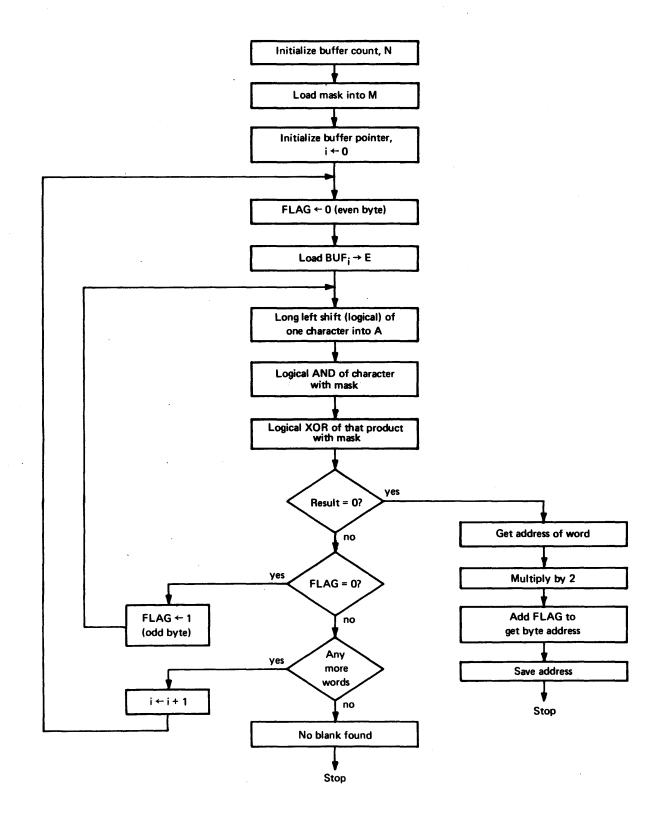

| 9-5 The Search for a Byte String Delimiter                                 | 149 |

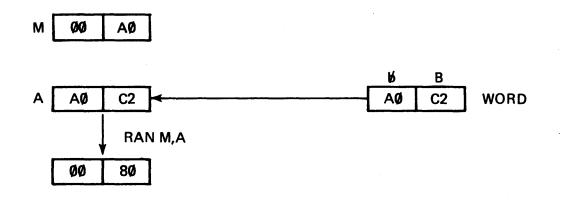

| 9-6 Tests for Ones and Zeros in the Accumulator                            | 151 |

# Section

| 10 | INPUT/OUTPUT ON THE BARE MACHINE                            |

|----|-------------------------------------------------------------|

|    | 10-1 Instructions                                           |

|    | 10-2 Two I/O Techniques                                     |

|    | 10-2.1 I/O by Polling                                       |

|    | 10-2.2 I/O by Interrupt                                     |

|    | 10-2.3 Double Buffering                                     |

|    | 10-3 Internal and External Addresses                        |

|    | 10-4 Read or Write (Low-Speed Data Bus Device)              |

|    | 10-5 External Devices: Data, Status, Command Words          |

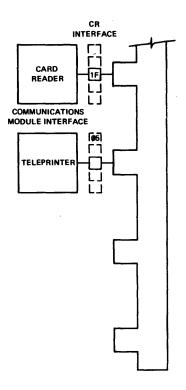

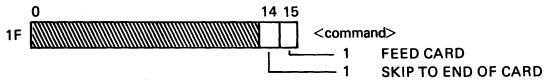

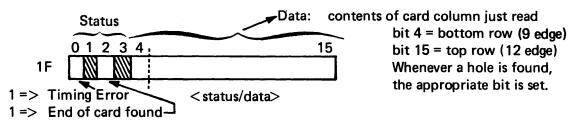

| ·  | 10-6 Card Reader                                            |

|    | 10-6.1 Reading a Card by Polling                            |

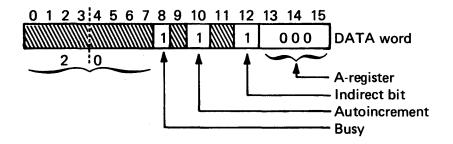

|    | 10-6.2 Polling the Reader with Autoincrement                |

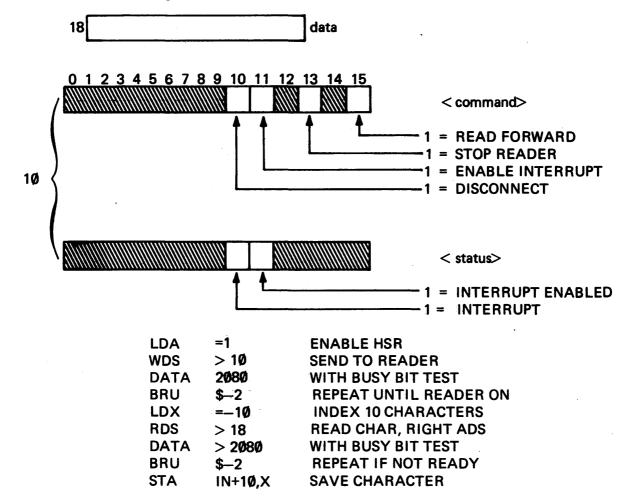

|    | 10-7 High-Speed Paper Tape Reader                           |

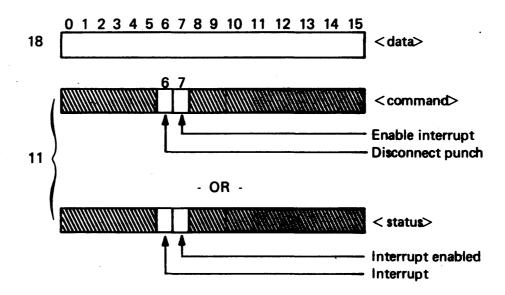

|    | 10-8 High-Speed Paper Tape Punch                            |

|    | 10-9 733 ASR/KSR Data Terminal                              |

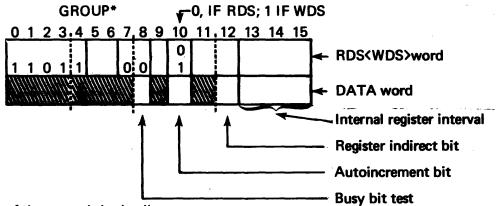

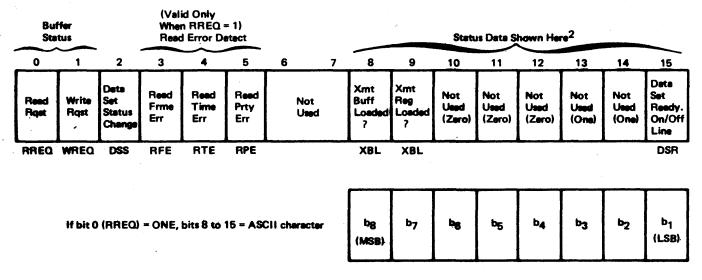

|    | 10-9.1 RDS Data Word                                        |

|    | 10-9.2 WDS Data Word                                        |

|    | 10-9.3 733 ASR Subcommands                                  |

|    | 10-9.4 Programming Examples                                 |

|    | 10-9.4.1 Write/Read KSR Example                             |

|    | 10-9.4.2 ASR Subcommand Example                             |

|    | 10-9.4.2 ASK Subcommand Example                             |

|    | •                                                           |

|    |                                                             |

|    | 10-10 DMAC I/O: The ATI Instruction                         |

|    | 10-11 Single DMAC Device: Line Printer                      |

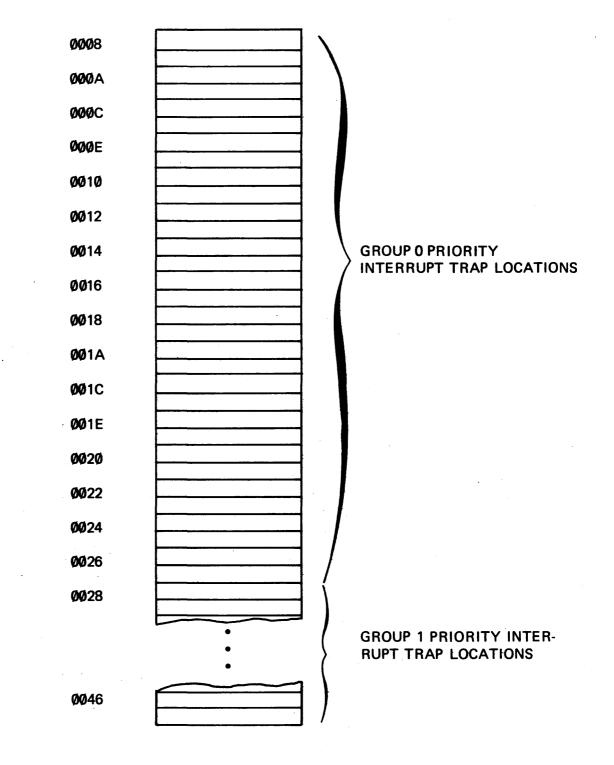

| 11 | THE INTERRUPT SYSTEM                                        |

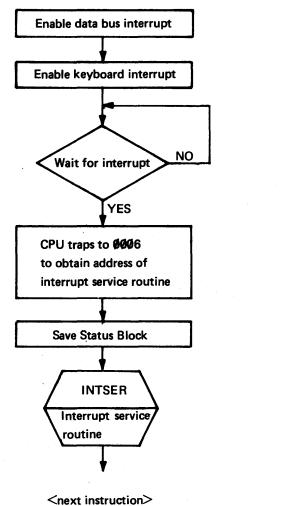

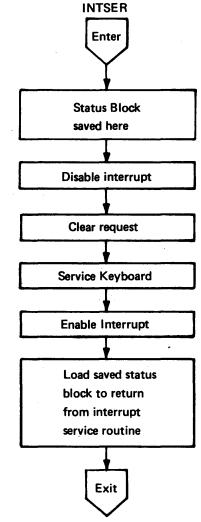

|    | 11-1 Introduction to the Interrupt System                   |

|    | 11-2 Internal Interrupts                                    |

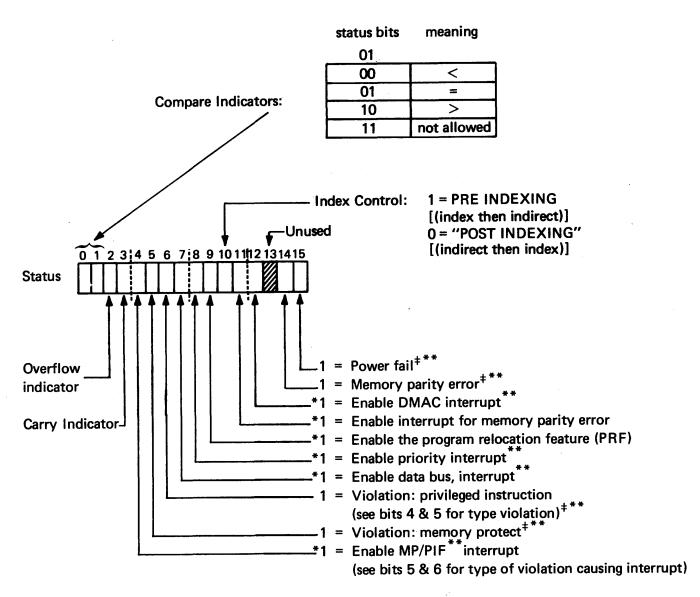

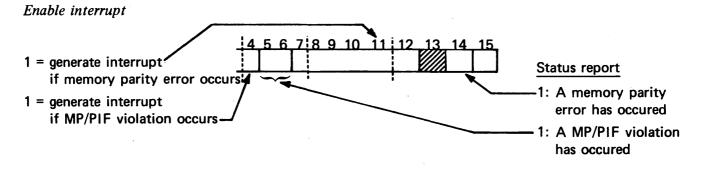

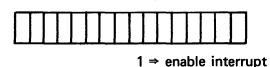

|    | 11-3 Loading the Status Register                            |

|    | 11-3.1 The LSB Instruction                                  |

|    | 11-3.2 Register or Instruction                              |

|    | 11-4 Handling Internal Interrupts                           |

|    | 11-5 Startup After Power Failure                            |

|    | 11-6 Memory Protect/Privileged Instruction Feature (MP/PIF) |

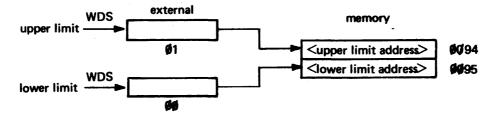

|    | 11-6.1 Memory Protect                                       |

|    | 11-6.2 Privileged Instructions                              |

|    | 11-7 Program Relocation Feature                             |

|    | 11-8 Data Bus and DMAC Interrupts                           |

|    | 11-9 DMAC Interrupt                                         |

|    | 11-9.1 Data Bus Interrupt                                   |

|    |                                                             |

| Section |                                                                | Page |

|---------|----------------------------------------------------------------|------|

|         | 11-9.2 Competing Data Bus Devices                              |      |

| APPENDI | ĸ                                                              |      |

| Α       | 980AL EXECUTION TIMES                                          |      |

| В       | 980 REGISTER DESIGNATIONS                                      |      |

| С       | HEXADECIMAL ARITHMETIC                                         |      |

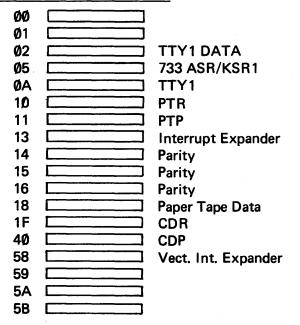

| D       | STANDARD ADDRESS OF EXTERNAL REGISTERS                         |      |

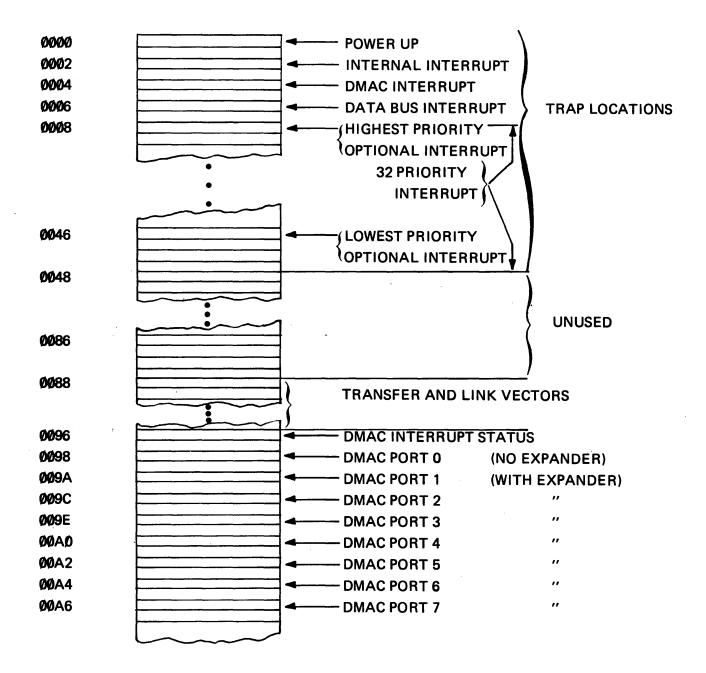

| Е       | SPECIALIZED LOW-ORDER MEMORY LOCATIONS                         |      |

| F       | BASIC SYSTEM MEMORY MAP                                        |      |

| G       | SAP ERROR MESSAGES                                             |      |

| н       | 980 OPERATING PROCEDURE                                        |      |

| I       | ASCII CHARACTERS BY NUMERICAL SEQUENCE                         |      |

| J       | OPERATION CODES - NUMERICAL ORDER REGISTER-MEMORY INSTRUCTIONS |      |

| к       | LOGICAL UNIT INPUT/OUTPUT FUNCTIONS                            |      |

# LIST OF ILLUSTRATIONS

| Figure No. | Pag                                                       | e |

|------------|-----------------------------------------------------------|---|

| 1-1        | Major Steps in Writing a Program                          | 2 |

| 1-2        | Information Flow in a Simple Computer System              | 4 |

| 1-3        | Information Flow in Computer System Equipped with DMAC    | 4 |

| 1-4        | Typical Memory Organization for a Simple Program          |   |

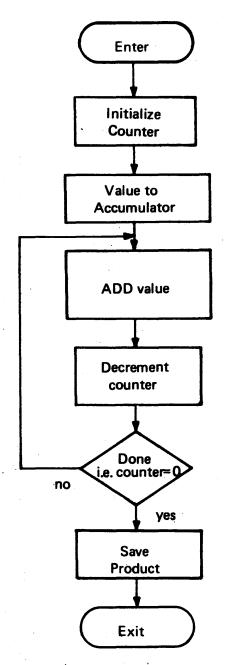

| 3-1        | Adding a Number to Itself (Multiplication) Flowchart      | 7 |

| 4-1        | Carry and Overflow Tast Program                           | 3 |

| 6-1        | Exchange Sort Technique                                   | 7 |

| 10-1       | Input/Output by Polling                                   | 3 |

| 10-2       | Four-Port Data Bus and 15 Port Bus Expander Block Diagram | 5 |

| 10-3       | Data Bus/Device Interfaces, Showing External Registers    | 5 |

| 10-4       | RDS Data Word                                             | 2 |

| 10-5       | WDS Data Word                                             | 3 |

| 10-6       | Status Character Bits                                     | 5 |

| 11-1       | The Status Register                                       | 4 |

# LIST OF TABLES

| Table No.         |                                                                      | Page  |

|-------------------|----------------------------------------------------------------------|-------|

| 1-1               | Octal, Decimal, and Hexadecimal Number Systems                       | 6     |

| 2-1<br>2-2<br>2-3 | Comparison of Decimal, Octal, Binary, and Hexadecimal Number Systems | 15    |

| 3-1               | Elementary Language                                                  | 23    |

| 4-1               | 980 AL Subset                                                        | 52    |

| 5-1<br>5-2        | Register Shift and Double-Length Instructions                        |       |

| 7-1<br>7-2        | Untitled                                                             |       |

| 8-1               | Untitled                                                             | . 127 |

| 9-1               | Untitled                                                             | . 144 |

| 10-1<br>10-2      | Untitled                                                             |       |

| 11-1<br>11-2      | Interrupt Instructions                                               |       |

#### **SECTION 1**

### INTRODUCTION TO ASSEMBLY LANGUAGE

#### 1-1 ASSEMBLY LANGUAGE PROGRAMMING: WHAT IS IT AND WHY LEARN IT?

Writing a program, whether in assembly language or a higher level language, actually begins when the programmer devises some kind of abstract process (called an *algorithm*) to accomplish a computational task.

One realization of the abstract algorithm is a *program*, which is an ordered sequence of steps (instructions) which tell a machine to do a given job. The nature of these instructions depends on the type of language being used. Algebraic languages such as FORTRAN permit the user to transmit via a single statement a request for a collection of machine activities; whereas use of assembly language requires the programmer to write a separate instruction for each machine activity. Compare the following program fragments: a FORTRAN statement with its four-instruction counterpart in 980 series Assembly Language (980 AL).

| FORTRAN | 980 AL |

|---------|--------|

| •••     |        |

| X=R+S—T | LDA R  |

|         | ADD S  |

|         | SUB T  |

|         | STA X  |

|         |        |

The number of assembly language instructions seen above might lead us to suspect that coding a program in 980 AL will result in more work than doing the same job in FORTRAN: in general, that is correct. However, since we have to pay such meticulous attention to detail, we will be in a position to exercise tighter control over the entire process. The real programming world tends to choose a language more or less according to the following rule of thumb:

If the primary objective of the computation is to obtain the numerical result of a set of arithmetic operations, the appropriate choice is probably an algebraic language such as FORTRAN. On the other hand, if the computer is to be used to monitor or control some physical process (for example, a chemical plant or a timesharing system), a strong case can be made for the use of assembly language. For many types of problems, though, the choice may not be clear cut.

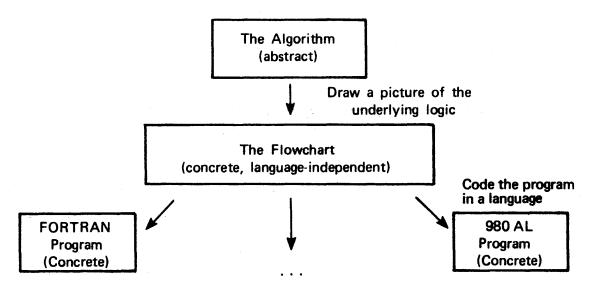

Another realization of the algorithm is a graphic representation (called a *flowchart*) of the logic underlying the process. Ideally, a flowchart is no more than the logical essence of the process; therefore, it is completely independent of (i.e. contains no characteristics of) any programming language. One should be able to use the same flowchart to code equivalent programs in numerous languages (see Figure 1-1).

Figure 1-1. Major Steps in Writing a Program

What we've discussed is an ideal situation: it's what we would *like* to have. In practice it works a little differently.

From the very inception of the problem, the programmer will start to incorporate a language-oriented bias — but hopefully as little as possible at each step of the way. A decision should be made very early whether the job should be done in a higher level language (such as FORTRAN) or in an assembly language. In real-world programming some awareness of the advantages and limitations of the language of intended use will creep into the development of the problem solution — often as early as the abstract or algorithmic stage. While this state of affairs cannot be avoided completely, it is to the programmer's advantage to avoid as much language dependence as possible until he comes to the last stage: writing the program.

Why computer people attach so much importance to flowcharts is often puzzling to the novice programmer. The reasons for composing a logical picture of the process may be summerized as follows.

- A flowchart helps the programmer write a better program and helps him do it more efficiently.

- A flowchart helps other people who may have to understand the program, or interface it with other programs, or write the same program for other machines.

- A flowchart makes possible the design and construction of large computer systems.

Knowledge of assembly language is a *must* for computer systems programmers. For others, concerned mostly with user applications programming, the study of assembly language may prove useful for a number of reasons; three of which come to mind easily:

1. With the spread of minicomputers and the increasing amount of automation of laboratory apparatus in fields from physics to psychology, many people are discovering a need for assembly language programming ability.

- 2. Many users of higher level languages find that a knowledge of assembly language programming is useful in debugging programs when the language diagnostics fail to adequately indicate the source of error.

- 3. Most importantly, assembly language programming reflects very accurately the machine's architecture and operation — thus it contributes heavily to a person's general understanding of how computers really work.

#### 1-2 ASSEMBLY LANGUAGE vs. MACHINE LANGUAGE.

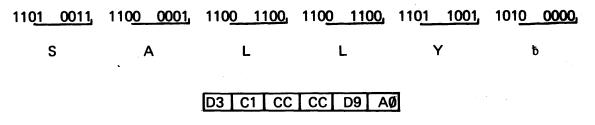

When a computer is first designed and built, it is provided a rudimentary language in which the user may talk to it; this is the so-called "machine language" associated with that particular model. The machine language is a numerical code to indicate to the machine which of its circuits should be activated in order to accomplish the operation desired by the programmer. The program fragment on page 1 might look something like the following when expressed in machine language:

| Assembly language form | Machine language form |

|------------------------|-----------------------|

|                        |                       |

| LDA R                  | 0004                  |

| ADD S                  | 2006                  |

| SUB T                  | 28F5                  |

| STA X                  | 80F7                  |

| •••                    | •••                   |

As we will discuss later, the second line uses 20 as the machine language equivalent of an *add* operation, and the quantity known as S is to be found in some location associated with the number 06.

Once upon a time, all programming was done in machine language, and the programmer had to keep referring to code-tables and memory maps in order to avoid burying himself in tons of numerical garbage. The tedium of this constant look-up process led to the development of assembly language, in which the programmer gave the machine a mnemonic operation code (op-code) such as ADD, and the machine used a special translator program (known as an *assembler*) to look up the corresponding numerical code. (The translation process became known as the *assembly*.) As computers evolved, the assemblers were given more and more of the routine bookkeeping jobs necessary to writing a program. Ultimately, the assemblers were given additional responsibilities, such as selecting and printing error messages designed to give an unlucky programmer some clue why his program failed to assemble (i.e. why the translation process did not work). In general, most current machines come equipped with more sophisticated assemblers; although a few, small, specialpurpose computers still must be programmed in machine language.

What we as assembly language programmers will do is to enter our programs into the computer in assembly language and then instruct the computer to translate (or *assemble*) the instructions into machine code.\* The time during which this translation process occurs is called *assembly time*. Just translating the program into machine code is not enough: the machine code program then must be loaded into the computer to run (*execute*). The period during which the program runs is called *execution time*.

<sup>\*</sup>Just to add to the confusion of the newcomer, computer people are sometimes ambigious in their use of the term machine language; it usually refers to the machine code discussed above, but it is sometimes used to refer to the assembly language, which is really only one small step away.

### **1-3 ORGANIZATION OF A COMPUTER SYSTEM.**

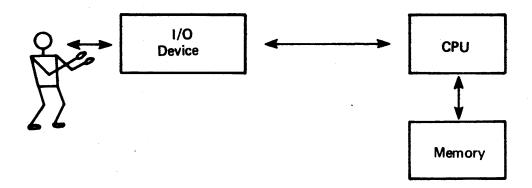

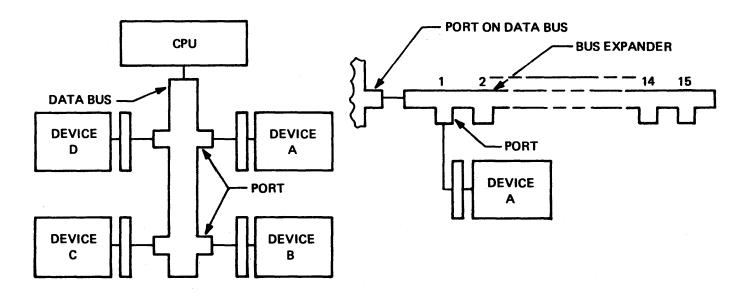

The two parts essential to any computer system are a *central processing unit* (CPU) which handles arithmetic and control functions and a *memory*. In addition, some means must be available for the operator/programmer to communicate with the machine. In a very crude system, communication can occur through a set of switches and lights on the front panel of the CPU; however, usually at least one input/output (I/O) device is present. The most economical device is often a *terminal* which is actually two devices in one; the keyboard serves as the input device and the printing mechanism serves as the output device. Characters entered through the keyboard are sent as a pulse train to the CPU, which (if the program has such a provision) may be sent back ("echoed") to the printing mechanism with sufficient speed so that the terminal resembles a typewriter in its operation.

Actually, a number of I/O devices may be attached to the computer: a card reader or paper tape reader (or both) for input; and a line printer, card punch, or paper tape punch for output. Other devices like magnetic tape (reel or cassette) may serve for both input and output.

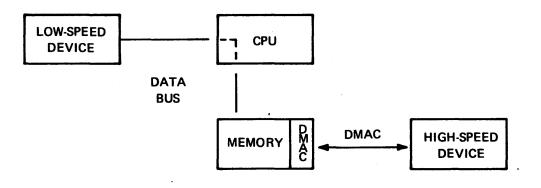

Figure 1-2 is a crude representation of the information flow.

Figure 1-2. Information flow in a Simple Computer System.

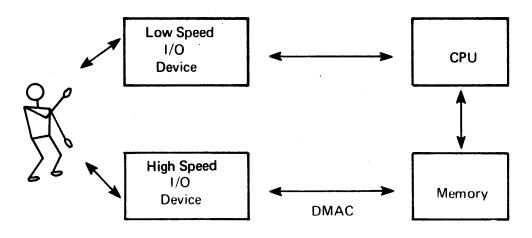

A number of computers, like the TI980 series, also have provisions for direct access by an I/O device to the memory using a direct memory access channel (DMAC) as shown in Figure 1-3.

Figure 1-3. Information Flow in a Computer System equipped with DMAC

For now we will ignore the DMAC capabilities of the 980 and consider the system as shown in Figure 1-2.

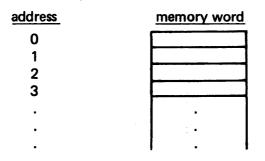

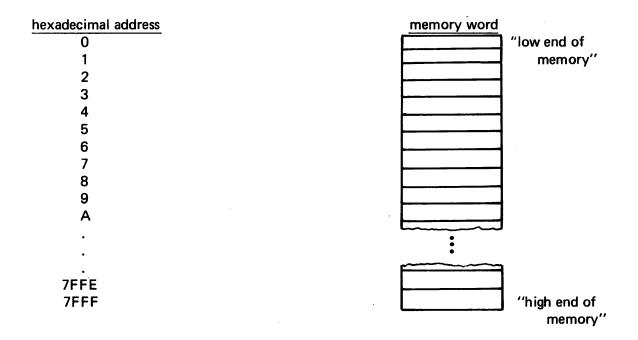

The memory, simply speaking, consists of an array of pigeon holes in which items of information can be stored. In more formal parlance, these pigeon holes are called *words* or *locations*. For the machine's convenience in referencing a given location, the entire set is numbered, and the counting numbers associated with these locations are called *addresses*. We could conceive of the memory as orgainzed as follows:

Not all computers are supplied with the same size memory; the amount varies, depending on the power resources and compactness of the chassis. Usually the smallest amount supplied is 4096 (or "4k") words. Depending upon the manufacturer of the unit, memory is commonly provided in incremental units of 4k or 8k. The most commonly occurring configurations, in addition to 4k are -

| 4k  | (4096 words)  |

|-----|---------------|

| 8k  | (8192 words)  |

| 16k | (16384 words) |

| 24k | (24576 words) |

| 32k | (32768 words) |

| 64k | (65536 words) |

The limit to the amount of memory which can be attached to a computer is usually dictated by the size (number of bits) of a machine word, since a word ultimately must have enough bits to contain a complete address.

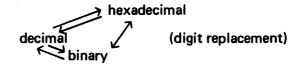

Each memory location has an address and is capable of containing either a machine language instruction or a data number. One complexity confronting us in dealing with the 980 computer (and with many other machines, as well) is that we often find ourselves having to use the base 16 (or *hexadecimal*) number system. The reason for the hexadecimal number system will become apparent later when we examine the detailed bit (bit = binary digit) structure of a computer word.

The 980 Computer has other electronic pigeon holes that look quite a bit like memory words except:

- they are physically located in the CPU rather than in the memory

- they are made of expensive high-speed circuitry

- they have names instead of hexadecimal addresses.

Such high-speed pigeon holes are called *registers*, and are used for special purposes which are discussed as each register is introduced:

accumulator program counter (PC or P-register) extension arithmetic (E-register) index register (X-register) base register (B-register) link register (L-register) maintenance register (M-register) storage register (S-register) status register (ST).

### 1-4 OCTAL AND HEXADECIMAL NUMBER SYSTEMS.

Most assembly languages use either an octal (base 8) or a hexadecimal (base 16) number system to represent instructions and data contained internally. The TI980, as well as a number of other machines, mainly uses the hexadecimal system. However, the octal system is in common use, and occasional octal numbers are encountered in programming the 980.

At first inspection, octal numbers look very similar to the familiar decimal numbers except for the fact that the digits 8 and 9 never appear. The concepts *eight* and *nine* do exist, however, and somehow have to be represented. In contrast, hexadecimal numbers have not only 8 and 9, but six more digits as well. (Rather than invent new digit symbols for the six additional, we use the letters A through F.)

In the decimal number system when we wish to count, we write down each of the decimal digits in order 0, 1, 2, 3, 4, 5, 6, 7, 8, 9; at which point we have used up all the single digits and need to have some way of expressing the concept *ten*. We do this by starting over again with the first digit (0) and inscribe a 1 to its left, giving us 10. Then we can run through all our digits again until reaching 19, when we once again run out of digits. We start over again with 0 as the number on the left takes on its next value in the ordered digit string (i.e., 2), giving us 20. The process continues until we run out of digits in both positions at the number 99; whereupon we start both positions over again at zero and inscribe a "1" to the left, giving us 100.

To build up numbers in, for example, the octal system, we do the very same thing except we never have the digits 8 or 9 to work with. Table 1-1 shows what happens:

| (decimal)<br>concept | octal<br>representation | decimal representation | hexadecimal representation |

|----------------------|-------------------------|------------------------|----------------------------|

| zero                 | 0                       | 0                      | 0                          |

| one                  | 1                       | - 1                    | 1                          |

| two                  | 2                       | 2                      | 2                          |

| three                | 3                       | 3                      | 3                          |

| four                 | 4                       | 4                      | 4                          |

| five                 | 5                       | 5                      | 5                          |

| six                  | 6                       | 6                      | 6                          |

| seven                | 7                       | 7                      | 7                          |

| eight                | 10                      | 8                      | 8                          |

#### Table 1-1. Octal, Decimal, and Hexadecimal Number Systems

| (decimal)     | octal          | decimal        | hexadecimal    |

|---------------|----------------|----------------|----------------|

| concept       | representation | representation | representation |

| nine          | 11             | 9              | 9              |

| ten           | 12             | 10             | Α              |

| eleven        | 13             | 11             | В              |

| twelve        | 14             | 12             | С              |

| thirteen      | 15             | 13             | D              |

| fourteen      | 16             | 14             | E              |

| fifteen       | 17             | 15             | F              |

| sixteen       | 20             | 16             | 10             |

| seventeen     | 21             | 17             | 11             |

| eighteen      | 22             | 18             | 12             |

| nineteen      | 23             | 19             | 13             |

| twenty        | 24             | 20             | 14             |

| twenty-one    | 25             | 21             | 15             |

| twenty-two    | 26             | 22             | 16             |

| twenty-three  | 27             | 23             | 17             |

| twenty-four   | 30             | 24             | 18             |

| twenty-five   | 31             | 25             | 19             |

| twenty-six    | 32             | 26             | 1A             |

|               | •              |                | •              |

| •             | •              | •              | •              |

| four thousand | •              | •              | •              |

| ninety-five   | 7777           | 4095           | FFF            |

| four thousand |                | 4030           | FFF            |

| ninety-six    | 10000          | 4096           | 1000           |

Table 1-1. Octal, Decimal, and Hexadecimal Number Systems (continued)

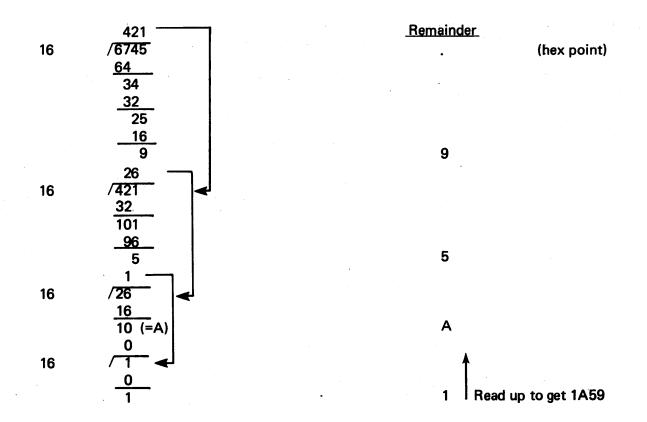

If we examine a number like 4096, we see immediately that it cannot be an octal number because it contains the digit 9; however, if we examine a number like 100, we have no way of knowing to what number base it refers unless we are told explicitly or can decide from the context in which the number appears. One way of indicating which number system is in use is to place a small subscript next to the number. Thus 76510 (or just 765) is seven hundred sixty-five represented in the familiear decimal system; while 7658 is a representation of some-number-or-other in the octal system and 76516 is yet a different number in the hexadecimal system. Fortunately, a straightforward technique for converting numbers back and forth between number systems is available so we don't have to learn each octal or hexadecimal representation as a special case. But for the time being, let's use numbers in our examples that are sufficiently small that we can determine the hexadecimal representation simply by looking at Table 1-1.

### 1.5 HEXADECIMAL ADDRESSING SCHEME.

The TI 980 computer uses the hexadecimal number system for internal representations of:

- the machine-language contents of all the memory words

- most of the numbers appearing in assembly language instructions

- the address of all the memory words.

Referring to item c. above, we can again draw a schematic diagram of the memory, this time showing how it *really* looks to the user:

We are assuming the 32k words (actually 32768) are addressed from 0 (which is the same as 0000) to 3276710 (or 7FF16). The significance of the addressing scheme is this: If we want to examine the contents of the word following location 9, we have to refer to it as location "A" rather than "10". If we want to put some information in the word following location 7FFF, we're out of luck because on a 32k system, there are no more pigeon holes beyond the one at 7FFF.

### 1-6 MEMORY ORGANIZATION AND THE PROGRAM COUNTER.

Before the computer can be let loose to grind out the problem solution, certain information must appear in the memory locations. This information consists of:

- a. a collection of instructions (i.e., a *program*) for manipulation (or generation) of data (e.g., add, subtract, etc.)

- b. the data numbers themselves.

Once this information is available, the computer can be told to execute the instructions; and the instructions (if the programmer has written them correctly) will operate on the data.

For now we will consider only those cases in which each instruction of the program and each data number occupies a single word of memory. (Later, in more sophisticated problems these restrictions are relaxed.)

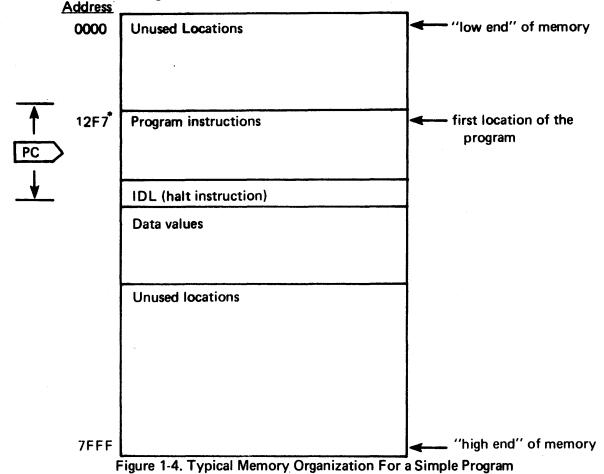

When we instruct the machine to execute the program, we want it to start in the first location containing a program instruction (the *entry point*) and perform all the instructions up to and including some kind of halt instruction. The halt instruction is the last instruction in the program; it keeps the execution from trying to proceed past the locations containing viable program instructions.

Within the machine is a register known as the *program counter*, often called the PC (or P register), which always contains the address of the next instruction the machine is supposed to

execute. If the first program instruction is in location 12F7, \*the PC will somehow have to have a 12F7 loaded into it at the beginning of execution. After that, the computer itself will undertake to keep the value of the PC updated. The PC could be visualized as a sliding arrow (see Figure 1.4) that always points to the next instruction to be executed, but in reality it is no such thing. The PC is a register that stays in a fixed position in the CPU but does its "pointing" by holding the address of the next memory location to be executed.

It is reasonable to ask at this point, "if the halt instruction separates the program from the block of data values, how does the PC ever get to point to the data?" The answer is: "during normal program execution, it doesn't."

When the machine needs a number which is stored in the data block, it has the happy capability to "look ahead" and acquire a number out of the data block without ever needing the PC to point to the datum in question. Although the job of updating the contents of the PC is handled by the computer most of the time, there are occasions when we may wish to insert an address of our own choosing: why and how we'll do this are discussed later.

### 1-7 PSEUDO-OPERATIONS AND ASSEMBLY.

In an earlier discussion, we saw one possible layout of the program instructions and the data values within the computer memory. We, as programmers, can exercise control over which instructions appear in which memory locations by giving the assembler a special assembly-time directive (or *pseudo-op*) with an op-code of ORG (short for *origin*).

<sup>\*</sup>The selection of 12F7 is arbitrary

Every time we include within the program an instruction of the form

ORG <address>

the very next instruction the machine finds will be placed in the location specified by <address>. For example, let's look at the program fragment we discussed earlier and convert it into a complete assembly language program which will direct the first instruction to be assembled into location 12F7 and which will place the data numbers 7, 10, and 14 in locations 1300, 1301, and 1302, respectively. Note that the ORG pseudoop does its job at assembly time; and since it is not needed at execution time, it never appears in the machine-language memory listing.

| Assembly-time |      | <u>E</u> | Execution time |      |  |

|---------------|------|----------|----------------|------|--|

| ORG >         | 12F7 | Assembly |                |      |  |

| LDA           | R    |          | 01000500       | 12F7 |  |

| ADD           | S    |          | 03000501       | 12F8 |  |

| SUB           | Т    |          | 04000502       | 12F9 |  |

We will use the data declaration (DATA) both to label the addresses with the names R, S, T, and X and to place into those locations the appropriate hexadecimal values for 7, 10, and 14. We can either declare these values to be hexadecimal numbers (by prefixing the number with the symbol >) or we can write them as decimal numbers and let the machine perform the conversion for us.

|        | Assembly-time* |        | Execution tim | ne   |

|--------|----------------|--------|---------------|------|

|        | IDT            | SAMPLE |               |      |

|        | ORG            | > 12F7 |               |      |

| SAMPLE | LDA            | R      | 0008          | 12F7 |

|        | ADD            | S      | 2008          | 12F8 |

|        | SUB            | т      | 2808          | 12F9 |

|        | STA            | X      | 8008          | 12FA |

|        | IDL            |        | CEØØ          | 12FB |

|        |                |        | · · · · ·     | 12FC |

|        |                |        |               | 12FD |

|        | ORG            | > 1300 |               | 12FE |

|        |                |        |               | 12FF |

| R      | DATA           | 7      | <b>Ø00</b> 7  | 1300 |

| S      | DATA           | 10     | ØØØA          | 1301 |

| т      | DATA           | 14     | ØØØE          | 1302 |

| х      | DATA           | Ø      | 0000          | 1303 |

|        | END            | SAMPLE |               |      |

IDT is a pseudo-op which gives the program a name. END is a pseudo-op used to inform the assembler there are no more instructions to be translated. Since END is not part of the executable instructions, it never appears in the machine code listing.

The first two digits of an instruction represent the op-code, and the last two represent the displacement of the location in which the operand (the data value, in this example) is to be found. The machine finds the appropriate operand during execution by adding Ø8 (displacement) to the current value of the PC. The result is the address where the appropriate number will be found.

<sup>\*</sup>Note that the alphabet letter O is often differentiated from zero by writing a slash through the zero (Ø).

The fact that each instruction has the same displacement ( $\emptyset$ 8) arises from the fact that the values are used in consecutive locations and declared in the same order in a block of consecutive locations which starts eight addresses below the instruction block. (The data address increases by one for each successive location; but then, so does the PC.) The reason the displacement is  $\emptyset$ 8 instead of  $\emptyset$ 9 is that the PC automatically increments by one (i.e., points to the next instruction) before the operand address has been calculated. Thus, we can always think of the PC as being one address higher than the instruction being executed.

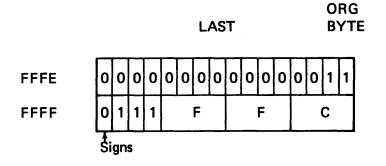

### **1-8 THE ROLE OF THE ACCUMULATOR IN EXECUTION.**