Digital Systems Division

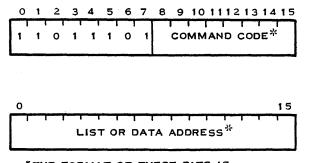

#### C Texas Instruments Incorporated 1975 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or set of organization without the prior consent of Texas Instruments Incorporated. As the prior consent of Texas Instruments Incorporated.

1.1

# LIST OF EFFECTIVE PAGES

١

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

a transfer and the

Note:

The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Model 980 Computer Input/Output and Auxiliary Processor Port Manual (960694-9701)

Original Issue

15 August 1972

Revised and Reissued

15 March 1973

Revised and Reissued

1 October 1975 (ECN 393198)

Revised and Reissued

1 April 1977 (ECN 419694)

Total number of pages in this publication is 82 consisting of the following:

| PAGE CHANGE<br>NO. NO.                                                                                                  | PAGE<br>NO. | CHANGE PAGE CHANGE<br>NO. NO. NO.                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| over 0<br>ff. Pages 0<br>i - viii 0                                                                                     |             |                                                                                                                                                                |

| 1 • 1-24 0<br>1 • 2-4 0                                                                                                 |             | 1997年1997年19月1日(1997年19月1日)(1997年19月1日)(1997年19月1日))<br>1997年1月1日(1997年19月1日)(1997年1月1日)(1997年1月1日))<br>1997年1月1日(1997年1月1日)(1997年1月1日)(1997年1月1日)(1997年1月1日)) |

| 1 - 3-4 0<br>1 - 4-12 0<br>1 - 5-8 0                                                                                    |             | n an                                                                                                                       |

| 1 - 6-12       0         lphabetical Index Div.       . 0         idex-1 - Index-4.       0         ser's Resp.       0 |             |                                                                                                                                                                |

| is. Reply 0<br>over Blank 0<br>over 0                                                                                   |             |                                                                                                                                                                |

|                                                                                                                         |             |                                                                                                                                                                |

|                                                                                                                         |             |                                                                                                                                                                |

| -                                                                                                                       |             |                                                                                                                                                                |

|                                                                                                                         |             |                                                                                                                                                                |

### PREFACE

This manual provides users of the Model 980A and 980B Compatters with information about the input/outputs (140) bus and 1/0 bus expansion hardware. Healso contains information for the personnel who install and maintain this hardware.

The description of the I/O bus includes interfaces, signals, and transfer of data. The functioning of the expansion system and the physical characteristics of the I/O bus are also presented. Individual sections cover the installation, operating instructions, and principles of operation of the I/O bus system

An entire section is devoted to the auxiliary processor port on the Model 980 Computer chassis.

Related publications, including maintenance manual volumes and assembly language programming manuals, are as follows:

| Title                                                                             | TI Part Number |

|-----------------------------------------------------------------------------------|----------------|

| Model 980A Computer Maintenance Manual:<br>System Description                     | 960699-9701    |

| Model 980B Computer Maintenance Manual:<br>System Description                     | 943012-9701    |

| Model 980 Computer Maintenance Manual:<br>Input/Output and Thput/Output Expansion | 960699-9704    |

| Model 980 Computer Input/Output Data Module<br>User's Manual                      | 965956-9701    |

| Model 980 Computer Assembly Language<br>Programmer's Reference Manual             | 943013-9701    |

| Model 980 Computer Assembly Language<br>Input/Output                              | 961961-9734    |

iii/iv

960694-9701

.

# TABLE OF CONTENTS

Title

| Paragraph |

|-----------|

|-----------|

Page

.

### SECTION I. GENERAL DESCRIPTION

| 1.1   | Introduction                                            |  |  |  |

|-------|---------------------------------------------------------|--|--|--|

| 1.2   | I/O Bus Configurations                                  |  |  |  |

| 1.3   | Interface Description                                   |  |  |  |

| 1.3.1 | Signals                                                 |  |  |  |

| 1.3.2 | I/O Data Transfers                                      |  |  |  |

| 1.3.3 | Instruction Format                                      |  |  |  |

| 1.3.4 | Data Transfer Cycles                                    |  |  |  |

| 1.4   | Physical Characteristics of Basic I/O Bus Configuration |  |  |  |

| 1.5   | Expansion                                               |  |  |  |

| 1.5.1 | Bus Expansion                                           |  |  |  |

| 1.5.2 | Group Expansion                                         |  |  |  |

| 1.6   | Interrupts and Interrupt Expansion                      |  |  |  |

| 1.6.1 | Computer Chassis Interrupts                             |  |  |  |

| 1.6.2 | Interrupt Expansion                                     |  |  |  |

| 1.7   | External Register Assignments                           |  |  |  |

| 1.8   | Equipment Specifications                                |  |  |  |

|       |                                                         |  |  |  |

|       | SECTION II. INSTALLATION                                |  |  |  |

| 2.1   | General                                                 |  |  |  |

| 2.2   | Standard I/O Ports                                      |  |  |  |

| 2.3   | Internal Expansion Ports                                |  |  |  |

| 2.4   | External Expansion Ports                                |  |  |  |

|       |                                                         |  |  |  |

|       | SECTION III. OPERATING INSTRUCTIONS                     |  |  |  |

| 3.1   | General                                                 |  |  |  |

| 3.2   | I/O Expander Chassis                                    |  |  |  |

| 3.3   | Software Instructions                                   |  |  |  |

| 3.3.1 | Read Direct Single Instruction                          |  |  |  |

| 3.3.2 | Write Direct Single Instruction                         |  |  |  |

|       |                                                         |  |  |  |

| •     | SECTION IV. PRINCIPLES OF OPERATION                     |  |  |  |

| 4.1   | Introduction                                            |  |  |  |

| 4.2   | Arithmetic Unit Control                                 |  |  |  |

| 4.3   | Input/Output Interface                                  |  |  |  |

| 4.4   | Input/Output Expansion                                  |  |  |  |

| 4.5   | I/O Expander Signal Descriptions and Logic              |  |  |  |

| 4.5.1 | Output Data Bus                                         |  |  |  |

| 4.5.2 | Input Data Bus                                          |  |  |  |

| 4.5.3 | Interrupt Lines                                         |  |  |  |

| 4.5.4 | Clock                                                   |  |  |  |

| 4.5.5 | Control Signals and Logic                               |  |  |  |

| 4.6   | Input/Output Signals                                    |  |  |  |

960694-9701

# TABLE OF CONTENTS (Continued)

4

| 5.1       General         5.2       Instructions         5.3       Theory of Operation         5.3.1       Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | 5-1                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------|--|

| 5.5 Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2017<br>1997 | 5-1                                                  |  |

| 5.3.1         Signals         Signals |              | 5-1<br>5-2                                           |  |

| SECTION VI. I/O BUS DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                                      |  |

| 6.1       General       General         6.2       I/O Data Module       General         6.3       Vectored Interrupt Module       General         6.4       Communications Module       General         6.5       Full Duplex Synchronous Communication Module       General         6.6       Regulator Module, ±15 Volts       General         6.7       Card Reader Controller       General         6.8       Paper Tape Punch Interface Module       General         6.9       Paper Tape Reader Interface Module       General         6.10       Interval Timer       General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | c            | 5-1<br>5-3<br>5-3<br>5-4<br>5-5<br>5-6<br>5-6<br>5-9 |  |

Figure

$\sim 1.5 \pm 0.5$

### LIST OF ILLUSTRATIONS

#### Title

#### Page

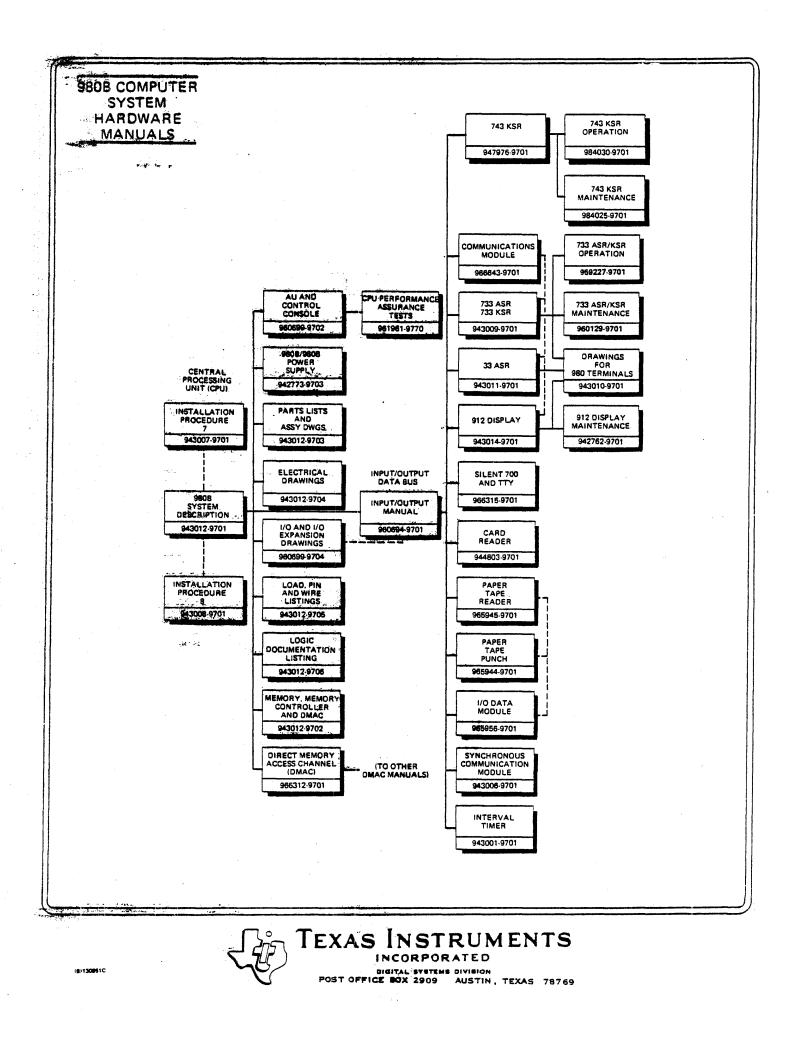

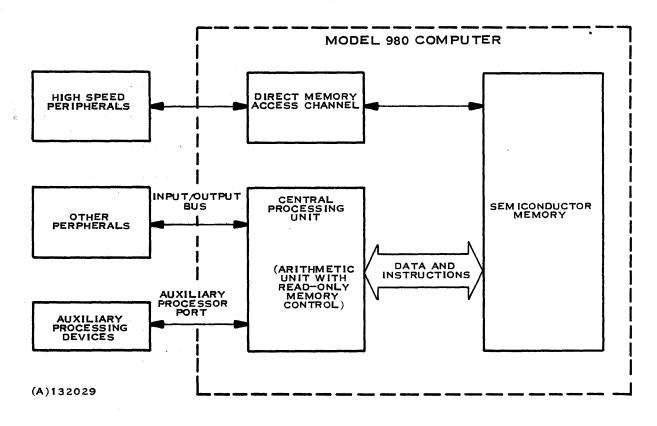

| 1-1  | Model 980 Computer System Functional Diagram     |

|------|--------------------------------------------------|

| 1-2  | 980 I/O System, Simplified Interface Diagram     |

| 1-3  | Printed Circuit Card Ports, 980 Computer Chassis |

| 1-4  | I/O Interrupts to CPU                            |

| 1-5  | I/O Expander Cards and Expansion Cable           |

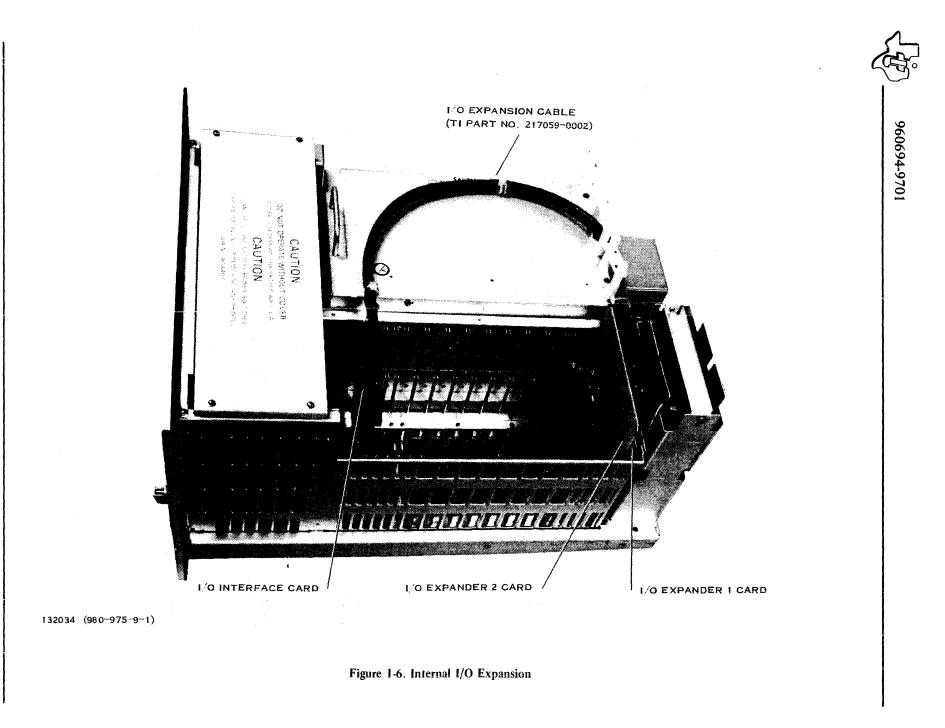

| 1-6  | Internal I/O Expansion                           |

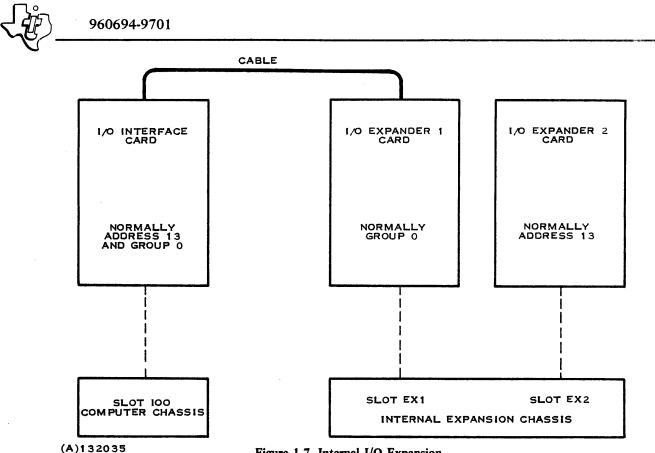

| 1-7  | Internal I/O Expansion                           |

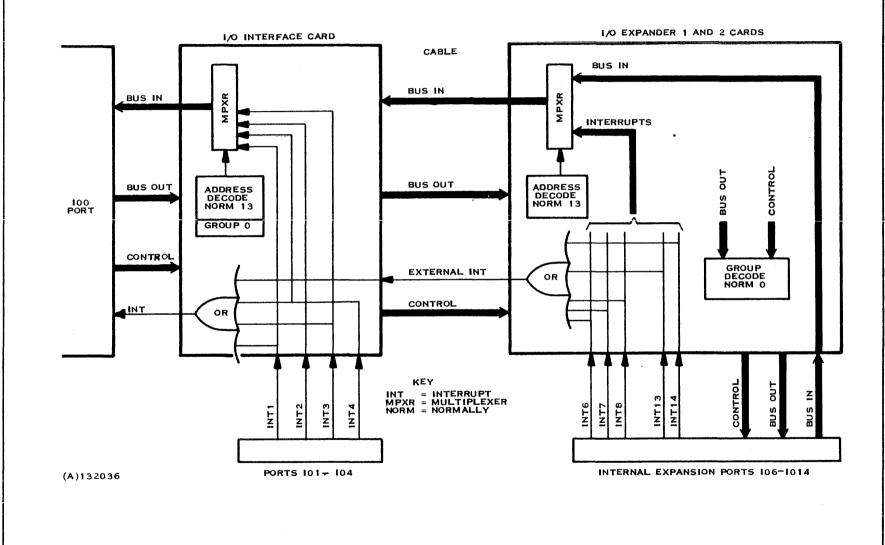

| 1-8  | Internal Expansion, Functional Block Diagram     |

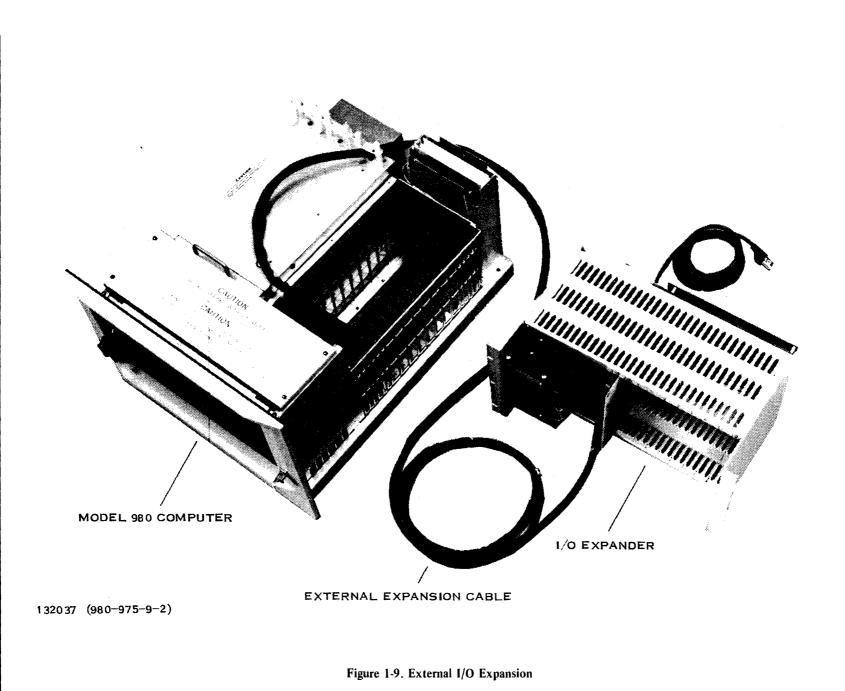

| 1-9  | External I/O Expansion                           |

| 1-10 | Single External I/O Expansion Configuration With |

|      | No Internal Expansion                            |

| 1-11 | Multiple I/O Expansion                           |

| 1-12 | Multilevel I/O Expansion                         |

| 1-13 | Example of Two-Level I/O Expansion               |

| 1-14 | Internal and External I/O Expansion              |

| 1-15 | External Register Number Assignments             |

| 1-16 | Input/Output Port Connector Pin Numbers          |

| 2-1  | I/O Interface Card                               |

| 2-2  | I/O Expander 1 Card                              |

| 2-3  | I/O Expander 2 Card                              |

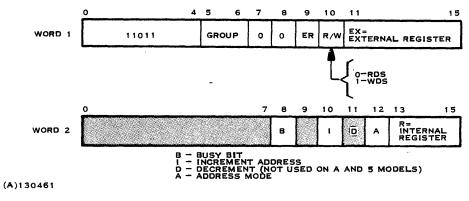

| 3-1  | RDS/WDS Instruction Format                       |

| 5-1  |                                                  |

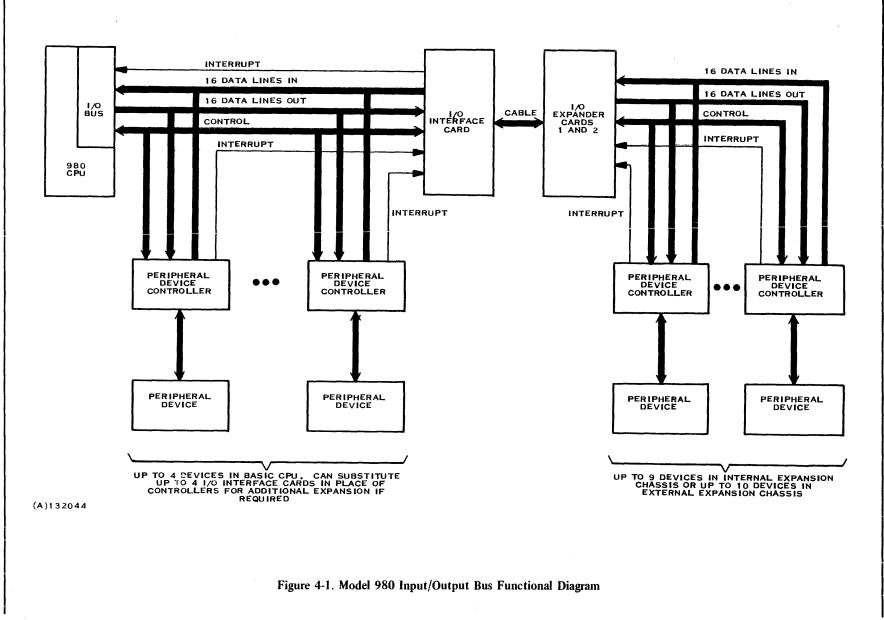

| 4-1  | Model 980 Input/Output Bus Functional Diagram    |

| 4-2  | RDS Instruction Word Timing Diagram              |

| 4-3  | WDS Instruction Word Timing Diagram              |

| 4-4  | I/O Channel Expander, Simplified Block Diagram   |

| 5-1  | Auxiliary Processor Port Memory Timing           |

| 5-2  | Auxiliary Processor Port Control Timing          |

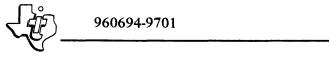

| 6-1  | Communications Module Interface Connector Pins   |

ander ander son der son Son der son der

the prove descent of the second of the secon

#### LIST OF TABLES

#### Table Title Page 1-1 980 I/O Bus System Interface Signals 1-2 1-3 Device Interrupt Bit Locations for Computer Chassis 1-4 Device Interrupt Bit Locations for Internal Expansion 1-5 Device Interrupt Bit Locations for External Expansion Chassis I/O Port 1-6 1-7 3-1 4-1 4-2 4-3 4-4 5-1 5-2 5-3 Typical Environmental Specifications for I/O Bus Module 6-1 6-2 6.3 Input/Output Data Module Signals and Connector · ···· 64 Vectored Interrupt Module Signals and External Connector 6-5 Vectored Interrupt Module Characteristics and Specifications 6-6 Communications Module Characteristics and Specifications 6-7 6-8 Synchronous Communication Module Top Edge Connector 6-9 Synchronous Communication Module Characteristics and 6-10 6-11 6-12 Card Reader Controller Characteristics and Specifications 6-13 6-14 6-15 Paper Tape Punch Interface Module Characteristics and 6-16 Paper Tape Reader Interface Module Signals and Connector • • • • • • • • • • • • Paper Tape Reader Interface Module Characteristics and 6-17 6-18 201 A 127-20 ر به بدین

#### SECTION I

#### **GENERAL DESCRIPTION**

#### 1.1 INTRODUCTION

Input/output operations in the Texas Instruments Model 980 Computer are handled by an input/output (I/O) bus system. The fundamental element of this system is a 16-bit in, 16-bit out, parallel bus which is used to transfer single data words between the Central Processing Unit (CPU) and low- and medium-speed peripheral devices.

Signal lines are provided for transmission of data to or from the computer, control of data transfer, timing, and indication of hardware interrupt status. The I/O expander provides signal fanout and fanin capabilities required to permit several device controllers to share the I/O bus. The I/O expander may be located either within the 980 computer chassis or in a separate external chassis. Data and status transfers are initiated by two software instructions, one to read data and one to write data.

A separate section discusses the software instructions and the theory of operation of the auxiliary processor port in the 980 computer.

The functional diagram in figure 1-1 shows the relation of the I/O bus to the rest of the computer.

and the second second second second

#### 1.2 I/O BUS CONFIGURATIONS

In order to complete the I/O interface between the CPU and peripheral hardware devices, any of three configurations may be used:

- Basic I/O Bus. Handles up to four devices. Five I/O ports on the computer chassis accommodate the I/O interface printed circuit card and up to four I/O device controller printed circuit cards.

- Internal expansion. Handles up to 13 devices. An optional expansion back panel in the 980 computer chassis accommodates additional printed circuit cards. I/O expander cards are required in addition to the interface and controller cards to provide I/O bus expansion.

- *External expansion.* Handles up to 256 devices. Expansion is accomplished in an I/O expansion chassis separate from the 980 computer chassis. Multiple expansion chassis are used if a large number of devices interface with the CPU.

#### 1.3 INTERFACE DESCRIPTION

The computer communicates with the device controllers through 16 output lines (data or address), 16 input data lines, and a number of control and status lines. These lines may be expanded for communication with a number of controllers.

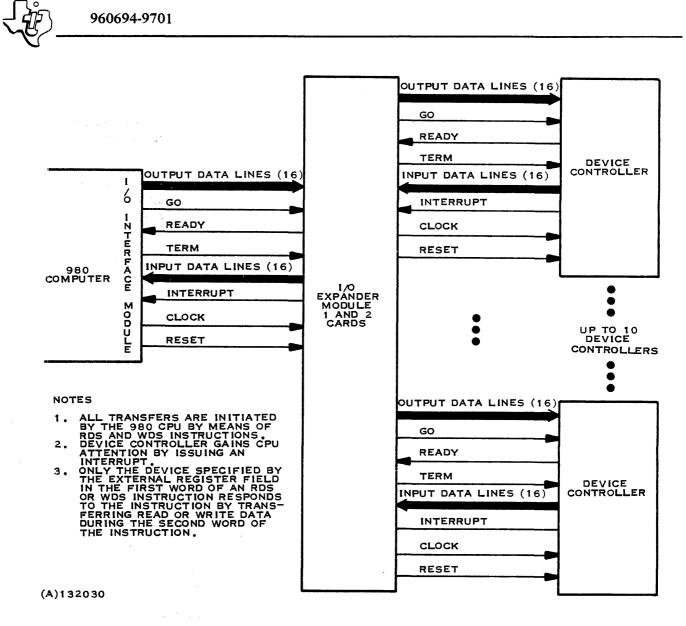

A simplified block diagram of the expanded interface between the 980 CPU I/O port and device controllers is shown in figure 1-2. If an expander is not included, the computer I/O interface module is required only for reading I/O interrupt line status.

1.3.1 SIGNALS. The functions of the data, control and status signals are summarized in table 1-1.

1.3.2 I/O DATA TRANSFERS. All data and status transfers between the computer and the device controllers connected to the I/O port are initiated by the 980 via two software instructions: Write Direct Single (WDS) and Read Direct Single (RDS). The WDS instruction is used to perform a 16-bit write to the addressed external device, and the RDS instruction performs a 16-bit read from the addressed external device. In each case, there is one instruction for each 16-bit data transfer.

1.3.3 INSTRUCTION FORMAT. Both WDS and RDS are two-word instructions within the 980 computer. A data word containing a character and/or control information is associated with each WDS or RDS instruction. When one of these instructions is executed, the first word is applied to the I/O data bus. During the second word, the 980 either sends a 16-bit data or command word to the device controller, or accepts a data or status word.

The WDS and RDS instructions are discussed in more detail in Section III.

1.3.4 DATA TRANSFER CYCLES. To start a data transfer cycle, the first word of the RDS or WDS instruction from the CPU is enabled to the output (write) data bus. A strobe pulse (GO) is generated which indicates to the external device, specified by the ER field of the instruction, that a valid GO word (same as the first word of the instruction) is on the output data bus. The external device examines bit 10 of the first word. If this bit is reset (logic 0), the device recognizes an RDS instruction; if it is set (logic 1), the device recognizes a WDS instruction.

Figure 1-2. 980 I/O System, Simplified Interface Diagram

If an RDS instruction is recognized, the device controller loads the data or status word on the input (read) data lines (as directed by the command portion of the GO word). The device controller then sends a READY pulse to the CPU. The CPU acknowledges the read data transfer by sending a TERM pulse back to the originating controller.

If a WDS instruction is recognized, the device acknowledges the GO word by sending back a READY pulse. The CPU then loads a data or command word on the output data lines and sends a TERM pulse to the device controller.

| Interface Signal | Function                                                                                                                                        |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Data Bus  | Data signals, written from the computer into the data buffer of an output device controller.                                                    |

| Input Data Bus   | Data signals, read into the computer from the data buffer of an input device controller.                                                        |

| Ready            | Signal indicating that a device is ready for a data transfer to or from the computer.                                                           |

| Go               | Signal indicating that an instruction is present on the output data lines.                                                                      |

| Term             | Signal indicating termination of the transfer of a single word of data.                                                                         |

| Clock            | Signal used to control the timing of operations related to data transfer.                                                                       |

| Reset            | Signal that resets all controllers so that none of them have access to the computer for data transfer imme-<br>diately after the reset.         |

| Interrupt        | Signal indicating that a controller has requested an interrupt and is waiting to gain the attention of the CPU or has the attention of the CPU. |

#### Table 1-1. 980 I/O Bus System Interface Signals

#### 1.4 PHYSICAL CHARACTERISTICS OF BASIC I/O BUS CONFIGURATION

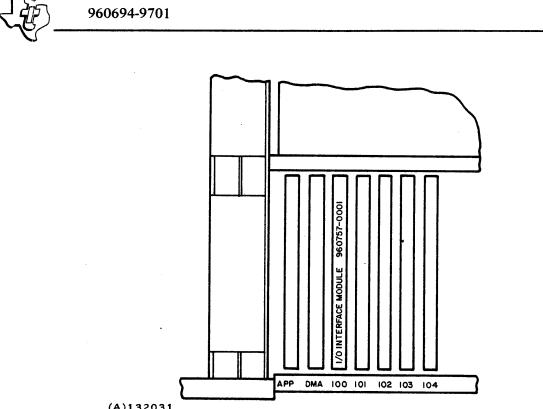

The basic 980 I/O bus consists of five I/O ports numbered IO0 through IO4 (figure 1-3). The printed circuit cards fit into slots in the chassis so that the cards plug into the port connectors properly. Normally, the I/O interface card (TI part no. 960757-0001) is placed in slot IO0 and I/O controller cards are placed in slots IO1 through IO4. Interrupt multiplexing for ports IO1 through IO4 is accomplished on the I/O interface card located in slot IO0.

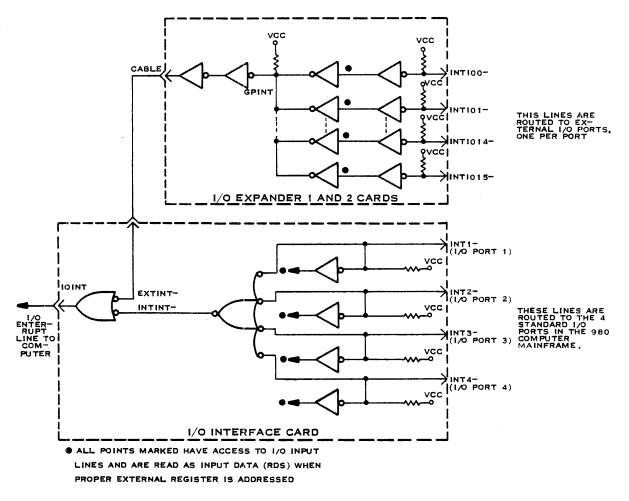

Interrupts from I/O ports IO1 through IO4 are wired to IO0 where these interrupts are ORed on the I/O interface card. From the I/O interface card, the interrupts are supplied to the CPU as a single interrupt (figure 1-4).

The I/O interface card logic can be read with an RDS instruction to determine the port number of the device controller which generated the interrupt.

The 980 computer card slots in the basic I/O bus configuration with the I/O interface card in slot IOO is illustrated in figure 1-3.

Detailed information about the available I/O controller cards manufactured by Texas Instruments is included in the user's manuals for the associated peripheral devices.

(A)132031

Figure 1-3. Printed Circuit Card Ports, 980 Computer Chassis

#### 1.5 EXPANSION

Bus and group expansion are discussed in the following paragraphs.

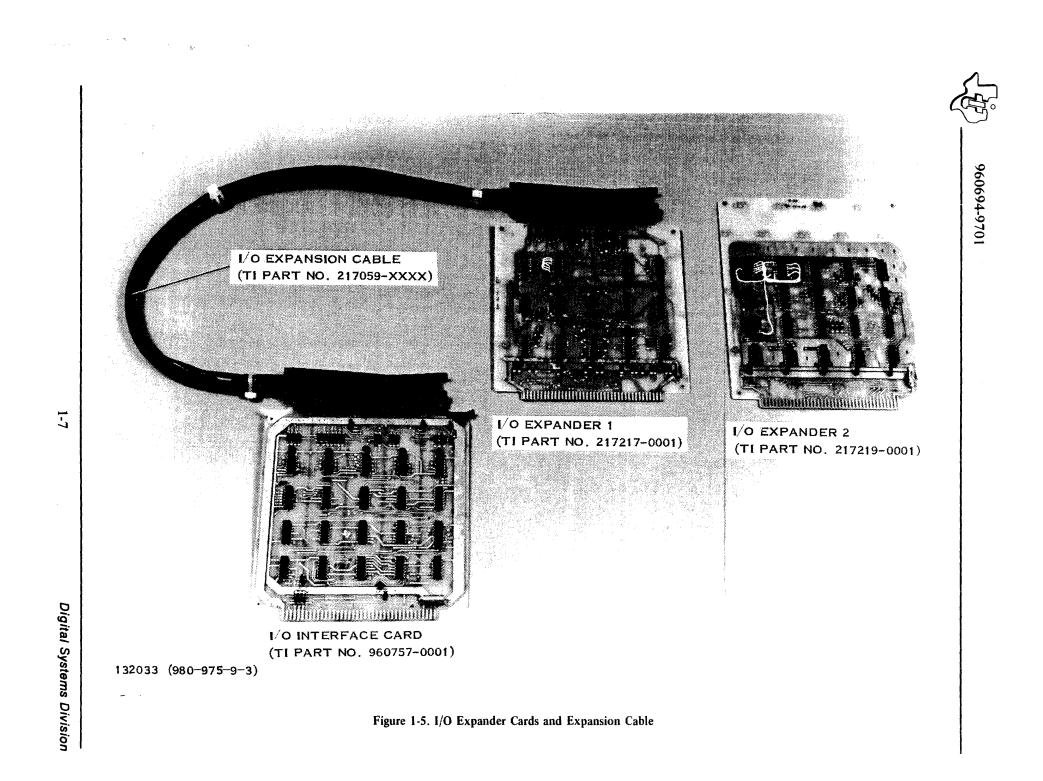

1.5.1 BUS EXPANSION. Since there are 4 groups of 64 possible external register numbers available to address the I/O controllers, up to 256 (4  $\times$  64) I/O devices may be connected to the Model 980 through the I/O structure. Input/output expansion is accomplished internal to the Model 980 mainframe by use of an optional internal I/O expansion kit (TI part no. 960703-0001), or externally by use of a separate I/O expander chassis kit (TI part nos. 966796-0001 through 966796-0004) that is designed for installation in a standard equipment rack. Two additional cards (I/O expander 1 and 2 cards) are utilized when the I/O bus is expanded. Figure 1-5 illustrates the I/O interface card, I/O expansion cable, and the two I/O expander cards.

These three cards provide I/O bus and control signal buffering, group decoding, and interrupt ORing of all individual ports for the expansion back panel. They also provide register address and group decoding for reading of all the interrupt lines in the expansion I/O slots using the RDS instruction to determine the slot number of the interrupting device.

(A)132032

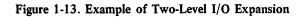

**1.5.1.1 Internal Expansion.** When expansion is accomplished internally, I/O expander 1 and I/O expander 2 are installed in the optional expansion back panel (TI part no. 960744-0004) of the Model 980 (see figure 1-6). A cable (TI part no. 217059-0002) from the I/O interface card is connected to I/O expander 1 to complete the expansion signal interface.

Figure 1-7 shows a block diagram of the interconnect and address setting. Refer to figure 1-8 for a functional block diagram of how the I/O bus internal expansion is implemented.

The optional expansion back panel contains 12 ports which can be wired to accommodate any combination of I/O, DMAC, and API devices.

**1-**8

Digital Systems Division

Figure 1-7. Internal I/O Expansion

The standard configuration of the optional internal I/O expansion kit (TI part no. 960703-0001) is wired to permit 9 of the 12 ports to be used for I/O devices. Two of the remaining ports (EX1 and EX2) are required for I/O expanders 1 and 2, respectively. The remaining one port (REG) is reserved for the optional  $\pm 15$  volt regulator card (TI part no. 226855-0001) which is required if device controller interface cards requiring  $\pm 15$  volts will be used in the internal expansion.

The addition of the nine optional I/O ports provides a total of 13 I/O ports available for external device interfaces within the Model 980 Computer mainframe.

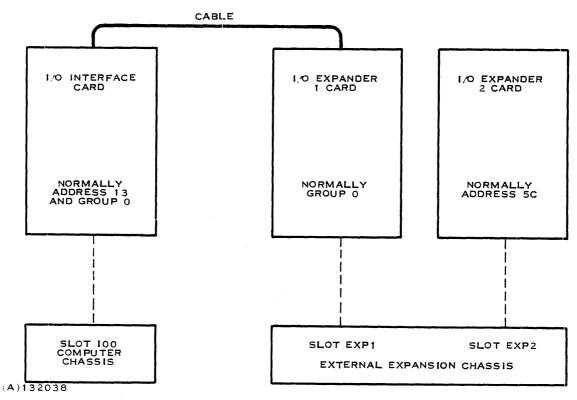

**1.5.1.2 External Expansion.** When expansion is accomplished outside the Model 980 mainframe, I/O expander 1 and I/O expander 2 are installed in the separate I/O expander chassis. A cable (TI part no. 217059-XXXX) from the I/O interface board to I/O expander 1 completes the expansion signal interface (figure 1-9). The four X's in the part number indicate that it may be any of several different dash numbers. Refer to table 1-2 for a list of available cables.

The I/O expander chassis has 10 ports for device interface boards and two ports, EXP1 and EXP2, for the I/O expander 1 and 2 cards.

960694-9701

Figure 1-8. Internal Expansion, Functional Block Diagram

1-10

**Digital Systems Division**

960694-9701

# Table 1-2. Part Numbers for Cable Assembly, CPU to I/O Bus Expander

| Part No.    | Length |

|-------------|--------|

| 217059-0002 | 2 ft   |

| 217059-0006 | 6 ft   |

| 217059-0012 | 12 ft  |

| 217059-0020 | 20 ft  |

The I/O expander chassis kit comes in four models (TI part nos. 966796-0001 through 966796-0004). The configurations are as follows:

| TI Part Number | AC Power | +5 V | ±15 V |

|----------------|----------|------|-------|

| 966796-0001    | 115 V    | Yes  | Yes   |

| 966796-0002    | 115 V    | Yes  | No    |

| 966796-0003    | 230 V    | Yes  | Yes   |

| 966796-0004    | 230 V    | Yes  | No    |

Figure 1-10 shows the configuration for a single external I/O expansion with no internal expansion.

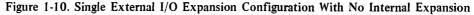

**1.5.1.3 Multiple Expansion.** For large I/O systems, more than one expansion chassis may be required. Up to four additional I/O interface cards may be installed in the basic I/O ports. Each I/O interface card is cabled to another expansion chassis. Also, the I/O interface card may be installed in any of the I/O ports in an expansion chassis to provide greater expansion capability.

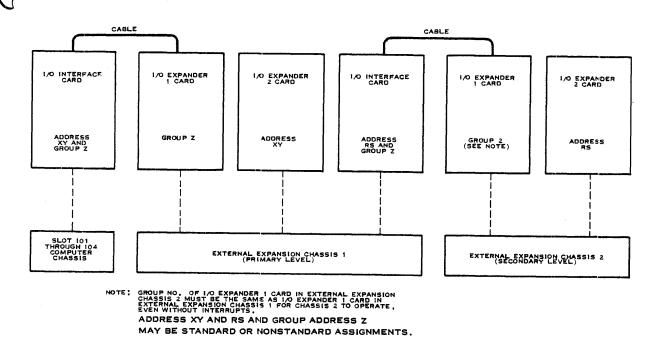

Figure 1-11 shows a configuration of one internal and four external expansion units and their normal addresses and group codes. Figure 1-12 shows expansion from an external expansion chassis. Note that the group code must be the same whether or not interrupts are being used.

1.5.2 GROUP EXPANSION. There are four possible groups of peripheral devices identified by the contents of bits 5 and 6 of the first word of the WDS and RDS instructions. By assigning them different group numbers, four I/O controllers with the same external address number may be operated separately. Groups are assigned by hardwiring one of the four combinations of bits 5

Figure 1-11. Multiple I/O Expansion

(A)132040

Figure 1-12. Multilevel I/O Expansion

and 6 on the I/O expander 1 card. Logic circuits decode the contents of bits 5 and 6. As a result of the decoding, GO, TERM and READY control signals are either gated to or inhibited from the other expansion ports on that back panel. The combination of 4 groups and 64 possible register addresses yields a total of 256 ( $4 \times 64$ ) port addresses with group expansion. Group decoding is also performed on the I/O interface card so that its register address can be reused with different groups. This is done because the I/O interface card is normally plugged into one of the five connector ports designated IOO through IO5, in which no group decoding is performed.

On the Model 980A only, there is no group decoding done on the Privileged Instruction registers 0 and 1; therefore, these registers may not be used in any other group expansion for a read (RDS) input. On the Model 980B, group decoding is done on the Privileged Instruction registers 0 and 1. Privileged Instruction registers 0 and 1 are located on the memory controller card.

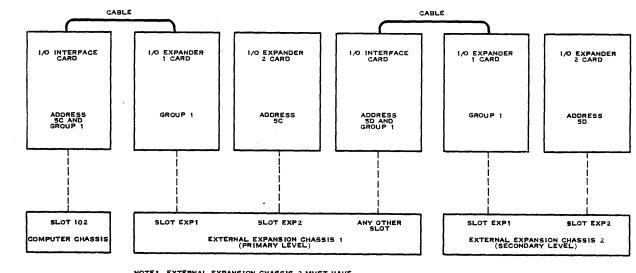

When expansion is performed from a primary expansion chassis, the secondary expansion chassis must have the same group number as the primary chassis. This is required because of the gating or inhibiting of the control signals GO, TERM and READY by the I/O expander 1 card in the primary chassis. Refer to figure 1-13 for an example of two-level external expansion.

#### NOTE

Most I/O expander 1 cards are delivered with group decode strapped to VCC: therefore, their control signals GO, TERM and READY are always enabled for any group.

OTE: EXTERNAL EXPANSION CHASSIS 2 MUST HAVE The same group no. As external expansion Chassis 1

(A)132041

#### 1.6 INTERRUPTS AND INTERRUPT EXPANSION

The following paragraphs discuss the functions of the interrupts for the basic I/O bus configuration and the expanded bus configurations.

**1.6.1 COMPUTER CHASSIS INTERRUPTS.** There is a single interrupt line for each I/O port on the 980 computer chassis. The interrupt lines for ports IO1 through IO4 are wired through the computer back panel to the IO0 port. These four interrupt lines and the external interrupt from the expansion cable are logically ORed on the I/O interface card. (See figure 1-4.)

When one or more device controllers produce an interrupt through the device interface cards and the I/O ports, the I/O interface card is slot IOO produces an interrupt to the computer, which then traps to memory location 6 (dedicated for this purpose) if interrupts are enabled. Status register bit 7 can be set to 1 to enable I/O bus interrupts.

After the interrupt trap has occurred, the I/O data bus interrupt service routine causes the I/O interface card to be read by means of an RDS instruction specifying register 13 (the external register normally designated for reading interrupts). In this way, the programmer can find out the port number of the device that caused the interrupt.

Table 1-3 lists the interrupt bit locations for ports IO1 through IO4. Note that more than one device may cause an interrupt so that more than one bit may be set. If a device has an interrupt pending, then its interrupt bit location is set to logical 1. An interrupt bit stays set until the associated device is serviced, at which time the bit is reset to logical 0. The I/O interface card can be read repeatedly without resetting any of the interrupt location bits.

| Port | Interrupt<br>Bit Location |

|------|---------------------------|

| 100  | _                         |

| IO1  | Bit 1                     |

| IO2  | Bit 2                     |

| IO3  | Bit 3                     |

| IO4  | Bit 4                     |

#### Table 1-3. Device Interrupt Bit Locations for Computer Chassis I/O Ports

1.6.2 INTERRUPT EXPANSION. Interrupt expansion, a function provided by the I/O expansion cards, is a means for determining the source of interrupt without reading the status of each I/O device. The I/O interface card and I/O expander 2 card, in response to RDS instructions, cause interrupt values to be gated onto the input data bus to be read into the CPU as a 16-bit data word.

There is an interrupt line for each port in the I/O expansion back panel. These lines are ORed on the I/O expander 2 card. The resultant signal is sent to the I/O expander 1 card, then over the expansion cable to the I/O interface card, which produces an I/O bus interrupt to the computer. Figure 1-4 shows the ORing and signal routing of the interrupts.

After the computer has trapped to the I/O bus interrupt, the programmer can interrogate the I/O interface card to determine the source of the interrupt. If the computer system has internal expansion, then when the programmer reads register 13 (the register containing the interrupt expander address in the normal configuration), he gets the interrupt status of ports IO1 through IO4 in bits 1 through 4. If the internal I/O expander cards are also set on group 0, register 13 (the normal selection for these cards), the interrupt status of internal expansion ports IO6 to IO14 is also gated in and read in bits 6 through 14 of the interrupt status word. In this way, the source of the interrupt may be identified. Table 1-4 gives the device interrupt bit locations for the internal expansion chassis I/O ports. If the system has external as well as internal expansion, the configuration is similar to the one shown in figure 1-14.

As an example of how the interrupting device is identified, suppose a device in external expansion chassis slot IO9 interrupted. After reading register 13 (hexadecimal) to determine the source of the interrupt, the programmer would find out that bit 1 was set. This tells him that the device in slot IO1 interrupted, but because there is an I/O interface card in that slot, he reads register 5C (hexadecimal), group 0 on the external expander cards with an RDS instruction. He would see that bit 9 is set, indicating that the controller card in slot 9 is the source of the interrupt. Table 1-5 shows the device interrupt bit locations for external expansion ports.

Note that the I/O interface card in slot IO1 is also set to register 5C, group 0, the same register and group as its expander cards. Even though no information can be read from it because of its slot location, it does not use up another address.

| Port | Interrupt<br>Bit Location |

|------|---------------------------|

| REG  | None                      |

| IO6  | Bit 6                     |

| IO7  | Bit 7                     |

| IO8  | Bit 8                     |

| IO9  | Bit 9                     |

| IO10 | <b>Bit</b> 10             |

| IO11 | Bit 11                    |

| IO12 | Bit 12                    |

| IO13 | Bit 13                    |

| IO14 | Bit 14                    |

| EX2  | _                         |

| EX1  | · _                       |

#### Table 1-4. Device Interrupt Bit Locations for Internal Expansion Chassis I/O Ports

#### NOTE

The "Skip on Ready" option is not to be used with the RDS instruction which reads the interrupt expander.

#### **1.7 EXTERNAL REGISTER ASSIGNMENTS**

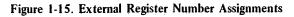

Each I/O controller has one or more external register numbers assigned which may be selected using switches or jumpers, A list of standard external register number assignments for controllers operated through the I/O structure is provided in figure 1-15 and table 1-6. Users may change the external register assignments for special applications.

#### NOTE

The standard group number assignment for all I/O controllers is 0. Group numbers and register numbers can be changed on the individual cards, by jumper wires on some and by pencil switches on others.

(A)132042

Figure 1-14. Internal and External I/O Expansion

### 1.8 EQUIPMENT SPECIFICATIONS

The characters of the 980 computer input/output bus are listed in table 1-7.

Pullups on the I/O interface card keep the False interrupt signals high when controllers are not in the basic I/O ports. Pullups for all other open collector outputs are located in the CPU.

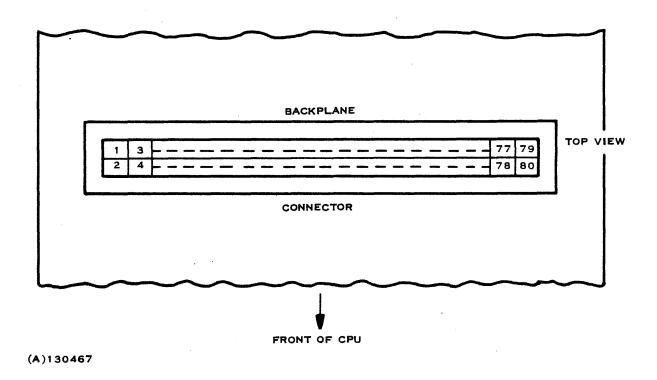

Standard pin numbers for 980 computer 80-pin back panel connectors are illustrated in figure 1-16.

All signals at the I/O bus interface are compatible with Texas Instruments Series 54/74 transistor-transistor logic (TTL) circuits. The logic 0 (low) level is 0.0 to +0.4 volts dc. The logic 1 (high) level is +2.4 to +5.0 volts dc.

| Port | Interrupt<br>Bit Location |

|------|---------------------------|

| IO5  | Bit 5                     |

| IO6  | Bit 6                     |

| IO7  | Bit 7                     |

| IO8  | Bit 8                     |

| IO9  | Bit 9                     |

| IO10 | Bit 10                    |

| IO11 | Bit 11                    |

| IO12 | Bit 12                    |

| IO13 | <b>Bit</b> 13             |

| IO14 | Bit 14                    |

| EX2  | -                         |

| EX1  | -                         |

# Table 1-5. Device Interrupt Bit Locations for External Expansion Chassis I/O Port

960694-9701

#### 6 7 с D 5 4 TTY 2 (SEE NOTE 1 TTY I CATION MODULE COMMUNI-CATION MODULE TTY 1 (SEE NOTES AND 5) INTERVAL COMMUNI-CATION MODULE CUSTOMER TTY 2 (SEE NOTE 1 COMMUNI-CATION MODULE I (SEE NOTES AND S) USE SEE NOTE . SEE NOTE 2 SEE NOTL ? CUSTOMER CUSTOMER USE COMMUNI-CATION MODULE 4 (SEE NOTE 2) COMMUNI-CATION MODULE USE TTY 2 (SEE NOTE 1 INTERVAL TTY I (SEE NOTE 1) TTY 2 (SEE NOTE 1 PRIV.INST. FEATURE (SEE NOTE 3 TTY I (SEE NOTES AND 5) PRIV, INST, FEATURE (SEE NOTE 3 COMMUNI-CATION MODULE SEE NOTE 2) SEE NOTE 2 INTERNAL INTERRUPT EXPANDER CARD READER TAPE READER TAPE READER TAPE PUNCH CUSTOMER USE (SEE NOTE 1) (SEE NOTE 1) TAPE PUNCH TAPE PUNCH READER TAPE READER ыт5 9. 10. 11, ISEE A A TO D A TO A CARD PUNCH CUSTOMER USE A TO D D TO A A TO D CARD PUNCH A 10 A 6 <del>1</del>8 **2** A 10 A EXTERNAL INTERRUPT EXPANDER EXTERNAL INTERRUPT EXPANDER EXTERNAL INTERRUPT EXPANDER 3 EXTERNAL INTERRUPT EXPANDER LOW SPEED LINE PRINTER (SEE NOTE 5) -CUSTOMER USE LOW SPEED LINE PRINTER (SEE NOTE 5) VECTORED VECTORED VECTORED VECTORED VECTORED VECTORED NOTES 1. TTY 1 33 ASR RDS - BIT 10 0 SILENT 700 OLDER INTERFACES OR TTY 2 CRT (HAZELTINE) 2. THE COMMUNICATIONS MODULE INTERFACES WITH THE 733 ASR/KSR, 33 ASR, OR 912 VIDEO DISPLAY TERMINAL, WDS - BIT 10 1 3. 980A COMPUTER DOES NO GROUP DECODE ON PIF REGISTERS. 4. BIT 10 IN THIS COLUMN ALWAYS REFERENCED TO ZERO. 5. INDICATES PRIMARY DEVICE ADDRESS. (8)132043

BITS 12,13,14,15 (HEX)

1-20

| Ë) |  |

|----|--|

| V  |  |

| Register<br>Number |                                                                                                                |                                                              |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| (Bits 9-15)        | Device                                                                                                         | Function                                                     |  |  |

| 00                 | PIF - Privileged Instruction Feature*                                                                          | Out - Set lower memory boundary                              |  |  |

| 01                 | PIF - Privileged Instruction Feature*                                                                          | Out - Set upper memory boundary                              |  |  |

| 02                 | TTY1 - ASR33, Silent 700 or CRT<br>(primary) old interface                                                     | In - Read data<br>Out - Write data                           |  |  |

|                    | part no. 217394                                                                                                |                                                              |  |  |

| 03                 | TTY2 - (Secondary) old interface<br>part no. 217394                                                            | In - Read data<br>Out - Read data                            |  |  |

| 04                 | Interval Timer                                                                                                 |                                                              |  |  |

| 05                 | Communication Module (primary addr.)<br>33 ASR, 733 ASR/KSR or CRT                                             | In - Input data and status<br>Out - Output data and commands |  |  |

| 06                 | New Interface part no. 966637<br>Communication Module (secondary addr.)                                        | In - Input data and status<br>Out - Output data and commands |  |  |

| 07                 | Customer use                                                                                                   | -                                                            |  |  |

| 08                 | Customer use                                                                                                   |                                                              |  |  |

| 0A                 | TTY1 - ASR-33, Silent 700 or CRT<br>(primary) old interface part no. 217394                                    | In - Read status<br>Out - Write command                      |  |  |

| 0B                 | TTY2 - Secondary (old interface<br>part no. 217394)                                                            | In - Read status<br>Out - Write command                      |  |  |

| 0C                 | Customer use                                                                                                   |                                                              |  |  |

| 0D                 | Communication Module (secondary addr.)                                                                         | In - Input data and status<br>Out - Output data and commands |  |  |

| 0E                 | Communication Module (secondary addr.)                                                                         | In - Input data and status<br>Out - Output data and commands |  |  |

| 10                 | PTR - Paper Tape Reader                                                                                        | In - Read status<br>Out - Write command                      |  |  |

| 11                 | PTP - Paper Tape Punch                                                                                         | In - Read status<br>Out - Write command                      |  |  |

| 13                 | INT - Interrupt expander address for<br>internal expander; interrupt expander<br>is relative to board location | In - Read interrupt                                          |  |  |

| 14                 | Customer use                                                                                                   |                                                              |  |  |

| 15                 | Customer use                                                                                                   |                                                              |  |  |

| 16                 | Customer use                                                                                                   |                                                              |  |  |

| 18                 | PTR - Paper Tape Reader                                                                                        | In - Read data                                               |  |  |

|                    | PTP - Paper Tape Punch                                                                                         | Out - Write data                                             |  |  |

| *The Mo            | *The Model 980A Computer does no group decode on PIF register.                                                 |                                                              |  |  |

# Table 1-6. Standard 980 External Register/Function Details

\*The Model 980A Computer does no group decode on PIF register.

|--|

## Table 1-6. Standard 980 External Register/Function Details (Continued)

| Register<br>Number |                                                                     |                                                  |

|--------------------|---------------------------------------------------------------------|--------------------------------------------------|

| (Bits 9-15)        | Device                                                              | Function                                         |

| 1A                 | TTY1 - ASR33, 700 or CRT (primary old interface part no. 217394     | Disconnect function                              |

| 1B                 | TTY2 - (secondary) old interface<br>part no. 217394                 | Disconnect function                              |

| 1F                 | CDR - Card Reader                                                   | In - Read status and data<br>Out - Write command |

| 40                 | CDP - Card Punch                                                    | In - Read status<br>Out - Write data and command |

| 41                 | Customer use                                                        |                                                  |

| 42                 | Customer use                                                        |                                                  |

| 44-46              | ADA - Analog to Digital Converter or<br>Digital to Analog Converter | Data Module (See ADA User's<br>Manual)           |

| 4C-4E              |                                                                     |                                                  |

| 50                 | LLP - Low Speed Line Printer                                        | Data Module (See Line Printer<br>User's Manual)  |

| 54                 | Vectored interrupt (I/O 1 and 2)                                    | Set mask                                         |

| 55                 | Vectored interrupt $(I/O \ 1 \ and \ 2)$                            | Clear mask                                       |

| 56                 | Vectored interrupt $(I/O \ 1 \ and \ 2)$                            | Set interrupt (T)                                |

| 57                 | Vectored interrupt $(I/O \ 3 \ and \ 4)$                            | Set mask                                         |

| 58                 | Vectored interrupt $(I/O \ 3 \ and \ 4)$                            | Clear mask                                       |

| 59                 | Vectored interrupt (I/O 3 and 4)                                    | Set interrupt (T)                                |

| 5C                 | Interrupt expander address for<br>external expansion chassis 1      | In - Read interrupts                             |

| 5D                 | Interrupt expander address fsor<br>external expansion chassis 2     | In - Read interrupts                             |

| 5E                 | Interrupt expander address for<br>external expansion chassis 3      | In - Read interrupts                             |

| 5F                 | Interrupt expander address for<br>external expansion chassis 4      | In - Read interrupts                             |

| (T) - Test         | only                                                                |                                                  |

(T) - Test only

| Characteristic              | Specification                      |

|-----------------------------|------------------------------------|

| I/O Instructions (2)        | Read (1) and Write (1)             |

| Word Length                 | 16 Bits                            |

| Data Transfer               | Parallel                           |

| Data Lines (32)             | 16 in and out                      |

| Control Lines               | 10 lines                           |

| Transfer Rate               | 130,000 words per second, maximum  |

| I/O Bus Interrupt           | 1 interrupt                        |

| I/O Bus Interrupt Expansion | 1 interrupt bit per I/O controller |

| I/O Ports:                  |                                    |

| Basic CPU                   | 4 maximum                          |

| CPU with Internal Expansion | 13 maximum                         |

| CPU with External Expansion | 256 maximum                        |

# Digital Systems Division

# Table 1-7. Model 980 I/O Characteristics

#### SECTION II

#### INSTALLATION

#### 2.1 GENERAL

The I/O bus system is based on three hardware configurations, referred to as standard, internal expansion or external expansion. A particular site may have any one or all of these configurations.

#### 2.2 STANDARD I/O PORTS

Installation of the standard configuration requires no hardware in addition to the I/O interface card (TI part no. 960757-0001) provided with the basic CPU. This interface card is placed in port IOO and provides the signal interface for the standard I/O ports plus the first-level expansion (internal or external). This module is inserted with the component side facing the front of the computer. The module must be jumpered to select the group and module address. The module address is necessary to permit a read operation of the interrupt lines which are multiplexed at the I/O interface card. Refer to figure 2-1 and table 4-1 to establish the necessary jumper connections. Solder jumpers with 22 to 26 gauge, single conductor, insulated wire.

#### 2.3 INTERNAL EXPANSION PORTS

An internal I/O expansion requires an optional, factory-wired connector panel installed behind the standard I/O back panel. This paragraph covers installation of the cables and buffer cards within a CPU with this internal expansion hardware already in place. When installing or removing

Figure 2-1. I/O Interface Card

a connector panel, refer to the I/O Expansion Kit drawing (TI part no. 960703-0001) provided with the hardware. This drawing is also included in the *Model 980 Computer Maintenance Manual: Input/Output and Input/Output Expansion*, Manual No. 960699-9704.

To configure an internal expansion, set up the address jumpers for the I/O interface card and install the module as specified in the section covering standard ports. Install the set of expander cards (I/O expander 1 card and I/O expander 2 card) as shown in figure 1-6. Connect the I/O expansion cable, TI part no. 217059-0002 as illustrated.

Expander 1 card jumpers determine the group of the internal expansion. Install jumpers of 22 to 26 gauge, insulated, single conductor wire and solder into place. The location of jumpers is determined from table 4-2 (the jumper schedule for the I/O expander 1 card) and figure 2-2. The group address selected generally is identical to the group address of the I/O interface card associated with this expansion. The I/O expander 1 card is installed in the last port of the internal expansion chassis labeled EX1. The Expander 2 card inserts into the adjacent slot marked EX2.

The I/O expander 2 card specifies the register address used to interrogate the interrupt lines and access the expanded slots. Install jumpers as described above. Refer to the illustration of the I/O expander 2 card (figure 2-3) and table 4-3 to determine the jumper locations. Again, this address is usually the same as the address specified on the associated I/O interface card.

Figure 2-2. I/O Expander 1 Card

(A)132049

Figure 2-3. I/O Expander 2 Card

#### 2.4 EXTERNAL EXPANSION PORTS

An external expansion includes a chassis, an I/O bus expansion cable, two I/O expander cards, and a wired connector panel for 10 I/O bus ports. The chassis assembly includes a power supply. This procedure details the interconnections required to install an external expansion.

- External Chassis The external chassis is installed on the rear rails of the cabinet. Note that the air will not circulate properly over the equipment when installed on the front rails and will cause equipment damage. Place the external chassis so that the cards can be removed from the back of the cabinet and with the power supply located on the left side (as one faces the assembly).

- Cable assemblies are of various lengths as specified in table 1-2. Select a location for the chassis which can be reached by the cable provided.

- I/O expander 1 and 2 cards should be jumpered as described in the internal expansion ports description (paragraph 4.4). Install the cards as shown in figure 1-9 (I/O expander 1 card in slot EX1 and I/O expander 2 card in slot EX2, both with the component side facing away from the power supply). Note that generally the group and register addresses on the I/O expander 1 and 2 cards are the same as the associated I/O interface card. The associated I/O interface card is located in slot IOO unless multiple expansion is employed. For multiple expansions, the I/O interface card may be located in a standard, external or internal port.

### SECTION III

#### **OPERATING INSTRUCTIONS**

### 3.1 GENERAL

This section presents both hardware and software operating instructions for the 980 I/O bus and expansion system. The information is presented in two parts: information about the I/O expander chassis, and software instructions needed to operate and control the basic I/O bus and the expanded I/O bus.

#### 3.2 EXTERNAL I/O EXPANDER CHASSIS

The external I/O expander chassis contains no controls or indicators. However, it has a power cord for connection to either 115 volts or 230 volts line power, as required chassis ac input power is fused.

#### 3.3 SOFTWARE INSTRUCTIONS

Operation of the Model 980 Computer input/output bus structure is controlled by two software instructions, the Read Direct Single (RDS) and Write Direct Single (WDS) instructions. They are described briefly in the following paragraphs. For more detailed information about these instructions, refer to the following software program development manuals:

- Model 980 Computer Assembly Language Programmer's Reference Manual, Manual No. 943013-9701.

- Model 980 Computer Assembly Language Input/Output, Manual No. 961961-9734.

**3.3.1 READ DIRECT SINGLE INSTRUCTION.** The RDS instruction consists of two 16-bit words (WD1 and WD2) as illustrated in figure 3-1. The first word of the RDS instruction (WD1) is applied to the output bus and an output strobe (GO) is generated which indicates to the external device that is addressed by the ER field that its data must enter the input bus. This data is retained on the input bus until a release pulse (TERM) is generated by the Model 980.

The destination of the input data is controlled by the second word of the instruction (WD2). The format of the read direct instruction is illustrated in figure 3-1 and the control functions are described in separate subparagraphs which follow. The instruction fields are summarized in table 3-1.

| Word/Bit(s)  | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/0-4, 7, 8  | Op-code bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1/5,6        | Group bits, used to define 1 of 4 groups. Each group can be<br>used to specify up to 64 external devices. The group and external<br>register fields combine to specify the external device involved<br>in the WDS/RDS instruction. Typically, the group bits are zero<br>unless the expansion of data bus ports exceeds 64.                                                                                                                                                                                                                                             |

| 1/9, 11-15   | External register bits, used to specify 1 of 64 devices in the selected group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1/10         | Read/write bit, used to specify either a RDS or WDS instruction.<br>A logic zero specifies a RDS instruction; a logic one specifies<br>a WDS instruction.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2/0-7, 9, 11 | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2/8          | Busy bit, an optional field (B) used with external devices that<br>may not be ready to transfer data when queried by the computer.<br>If this bit is a logic one and successful data transfer takes place,<br>the instruction following the WDS/RDS instruction is skipped.<br>If this bit is a logic one and no data transfer takes place, the in-<br>struction following the WDS/RDS instruction is executed. If the<br>bit is a logic zero, the device transfers data unconditionally and<br>the instruction following the WDS/RDS instruction is executed.          |

| 2/10         | Increment (I) field, used in conjunction with the A field (bit 12<br>of word 2) to increment or decrement the contents of the register<br>specified by the R field (bits 13 of 15 of word 2). If both the<br>I and A fields are logic ones, the address contained in the register<br>specified by the R field is incremented by one each time a data<br>word is transferred. If the A field is a logic one, but the I field is<br>a logic zero, the address contained in the register specified by the<br>R is decremented by one each time a data word is transferred. |

| 2/11         | Decrement (D) field, included for compatibility with earlier models of the computer. It performs no function in the 980.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2/12         | Address (A) mode field, used to specify indirect addressing. If the A field is a logic zero, data is transferred to or from the register specified by the R field. If the A field is a logic one, data is transferred to or from the memory location specified by the contents of register $R$ .                                                                                                                                                                                                                                                                        |

| 2/13-15      | Register (R) field, used to specify 1 of 8 internal registers in the computer. The specified register holds the data or the address of data involved in the transfer.                                                                                                                                                                                                                                                                                                                                                                                                   |

## Table 3-1. WDS/RDS Instruction Field Breakdown

### SECTION IV

### PRINCIPLES OF OPERATION

#### 4.1 INTRODUCTION

This section describes the principles of operation of the Model 980 Computer input/output bus system and its associated electronic circuits. It includes a theoretical description of the I/O instructions, the I/O interface card and the I/O expander cards. A functional diagram of the I/O bus is illustrated in figure 4-1.

Refer to the Model 980 Computer Maintenance Manual: Input/Output and Input/Output Expansion, Manual No. 960699-9704, for detailed logic diagrams, assembly drawings, parts lists, and load, pin and wire lists related to the I/O bus and I/O expansion.

#### 4.2 ARITHMETIC UNIT CONTROL

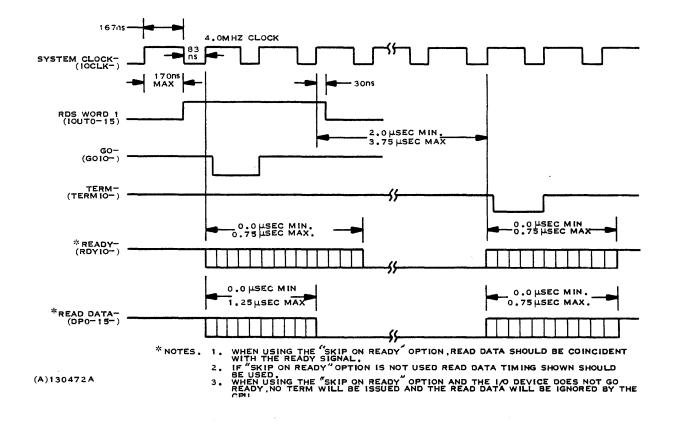

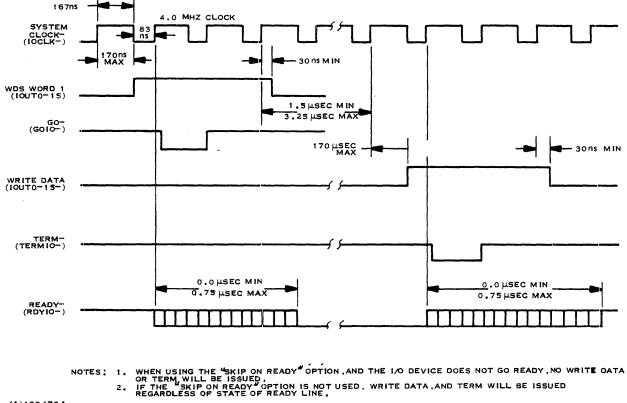

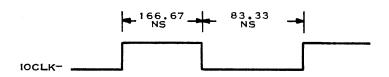

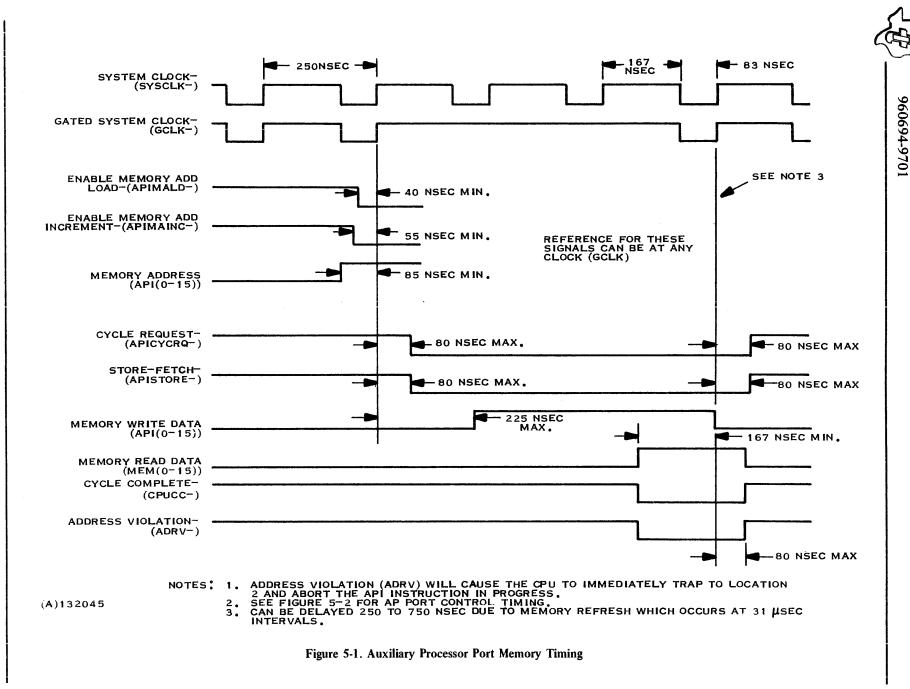

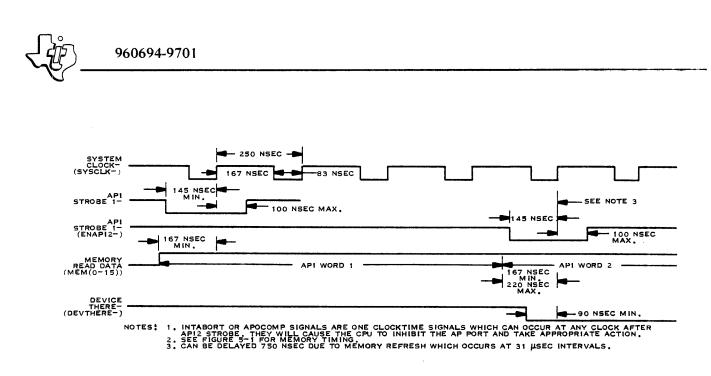

The Arithmetic Unit (AU) in the Model 980 Computer contains control and data path logic for the I/O bus. When an RDS or WDS instruction is acquired, the AU ROM controller gates the first word of the instruction on the I/O output data lines for 750 nanoseconds or three clock periods (250 nanoseconds). During the second clock period a GO signal is applied to the I/O bus which signifies that the I/O controllers should decode the external register lines to determine which controller or function is being addressed by the I/O instruction. The RDS and WDS timing is illustrated in figures 4-2 and 4-3, respectively.

The top two waveforms in figures 4-2 and 4-3 include the RDS/WDS word 1 and GO signal timing. If the "SKIP ON READY" option is used (RDS/WDS word 2, bit 8 equal to 1), the I/O controller should supply a READY signal to the AU within 750 nanoseconds as shown in figures 4-2 and 4-3. If the controller is ready or the command is issued without testing busy, then the AU produces a TERM signal to indicate acceptance of input data for the RDS instruction (figure 4-2) or to indicate that output data is available to the I/O controller for a WDS instruction (figure 4-3).

### 4.3 INPUT/OUTPUT INTERFACE

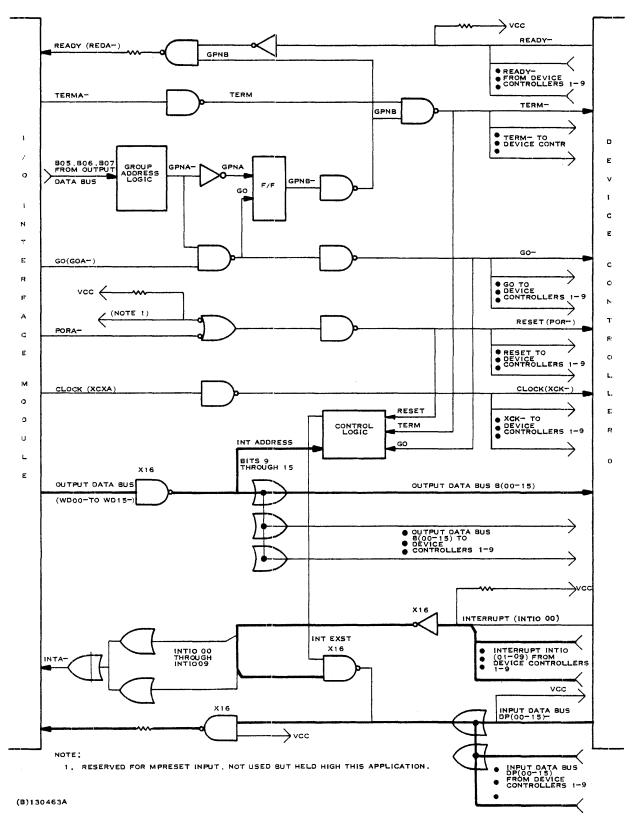

The I/O interface card which normally occupies card slot IOO in the Model 980 mainframe provides a means to expand the I/O bus to other back panels. The I/O interface card also contains the logic necessary to OR the interrupt lines from the I/O ports in the Model 980 basic mainframe to form one I/O interrupt line to the CPU. Jumper wires enable the user to select the address to read the I/O interrupts.

In the normal configuration, the I/O interface card may be used in ports IO1 through IO4 for further expansion of the external expansion chassis. The card decodes the group number to allow the maximum use of the available device addresses. The card also functions as a buffer of both input and output signals from and to the expansion back panel.

A detailed diagram of the I/O interface logic is illustrated in the Model 980 Computer Maintenance Manual: Input/Output and Input/Output Expansion.

960694-9701

4-2

Digital Systems Division

Figure 4-2. RDS Instruction Word Timing Diagram

Two types of symbols should be noted. When a connector pin symbol  $(\rightarrow)$  is shown, the connector is labeled P1 or P2. This label is followed by a dash and the pin number. The P1 designation indicates the connector is a bottom connector and P2 designates a top connector which can complete the connection to a cable with the proper cable connector.

The jumper pad symbol (--o) indicates a pad that is provided to permit jumper wires to be inserted for address selection. Normally, the pad identifier (E19 for example) as shown is also reproduced on the component side of the printed circuit board. Refer to table 4-1 for the jumper address schedule.

2.

(A)130473A

### Figure 4-3. WDS Instruction Word Timing Diagram

Example:

As an example of jumper connections using table 4-1, the connections for address 13, group 0 are:

-E-2 to E-24 E-4 to E-23 E-5 to E-22 E-7 to E-21 E-10 to E-20 E-13 to E-19 E-15 to E-27 E-17 to E-26

|      | Instruction Word 1 Bits                              |      |      |      |             |      |      |                                                                                                                                 |  |  |

|------|------------------------------------------------------|------|------|------|-------------|------|------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | Group<br>Address Bits External Register Address Bits |      |      |      | Explanation |      |      |                                                                                                                                 |  |  |

| 5    | 6                                                    | 9    | 11   | 12   | 13          | 14   | 15   |                                                                                                                                 |  |  |

| E-18 | E-16                                                 | E-14 | E-10 | E-8  | E-6         | E-4  | E-2  | Jumpered when address bit true                                                                                                  |  |  |

| E-17 | E-15                                                 | E-13 | E-9  | E-7  | E-5         | E-3  | E-1  | Jumpered when address bit false                                                                                                 |  |  |

| E-26 | E-27                                                 | E-19 | E-20 | E-21 | E-22        | E-23 | E-24 | A jumper must start at each of<br>these terminators and select<br>either true or false sense for<br>each of these address bits. |  |  |

### 4.4 INPUT/OUTPUT EXPANSION

The I/O expander 1 and 2 cards are used with the I/O interface card to expand the Model 980 I/O bus. The electrical schematics of the I/O expander cards are illustrated in the *Model 980 Computer Maintenance Manual: Input/Output and Input/Output Expansion.* The expander cards provide buffered I/O bus signals to additional I/O back panels at the same logic level and pins as the mainframe I/O bus ports.

The I/O expander 1 card also provides group decoding for the expansion back panel. The result of the decode either gates or inhibits the GO, TERM and READY control signals to or from the expansion back panel. Table 4-2 gives the jumper schedule for the expander 1 card.

### Example:

As an example of jumper connections using the table 4-2, the connections for group 0 are:

E-1 to E-8 E-3 to E-9 E-5 to E-7

The I/O expander 2 card provides register decoding for expansion interrupt inputs. It also contains the logic for interrupt ORing. Table 4-3 gives jumper schedule for the expander 2 card.

Example:

As an example of jumper connections using table 4-3, the connections for register address 13 are:

E-1 to E-4 E-9 to E-8 E-12 to E-3 E-13 to E-5 E-16 to E-6 E-18 to E-7

Digital Systems Division

| Table 4-2. | Jumper   | Schedule | for I/O | Expander | 1 | Card |

|------------|----------|----------|---------|----------|---|------|

|            | o an por | ochedute | 101 1/0 | Expander |   | Caru |

|       | Group Bit |       |                                                                                                                                                             |

|-------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | 6         | 7     | Explanation                                                                                                                                                 |

| E-6   | E-2       | E-4   | Jumpered when address bit true                                                                                                                              |

| E-5   | E-1       | E-3   | Jumpered when address bit false                                                                                                                             |

| E-10* | E-11*     | E-12* | Jumpered when address bit is not decoded (always selected)                                                                                                  |

| E-7   | E-8       | E-9   | A jumper must start at each of these terminals<br>and select either true or false sense, for each of<br>these address bits if multiple groups are utilized. |

\*Normally, card is delivered with decode always enabled (VCC).

Table 4-3. Jumper Schedule for I/O Expander 2 Card

### **External Register Address Bits**

| 9    | 11   | 12   | 13           | 14   | 15  | Explanation                                                                                                         |

|------|------|------|--------------|------|-----|---------------------------------------------------------------------------------------------------------------------|

| E-11 | E-9  | E-17 | <b>E-</b> 15 | E-13 | E-1 | Jumpered when address bit true                                                                                      |

| E-12 | E-10 | E-18 | <b>E-</b> 16 | E-14 | E-2 | Jumper when address bit false                                                                                       |

| E-3  | E-8  | E-7  | E-6          | E-5  | E-4 | A jumper must start at each of these terminals<br>and select true or false sense for each of these<br>address bits. |

Standard register addresses for I/O expansion are as follows:

| Register<br>Address | I/O Expansion<br>Chassis |

|---------------------|--------------------------|

| 13                  | Internal                 |

| 5C                  | External 1               |

| 5 <b>D</b>          | External 2               |

| 5E                  | External 3               |

| 5F                  | External 4               |

The register address is the hexadecimal equivalent of the binary value in bits 9 through 15 of the RDS/WDS instruction (first word). Bit 10 is always 0.

The cable between the I/O interface card and the I/O expander 1 card permits the transfer of signals to and from the I/O interface to access the basic I/O bus. Signals are transferred from the top edge connector of the I/O interface card to I/O expander 1. Except for SYSCLK-, these signals are transferred through twisted pairs of wires that are series-terminated with 82 ohms at the transmission end.

The SYSCLK- line is parallel-terminated at the receiving end with 390 ohms to Vcc and ground. Provisions are included at the I/O interface to disable the 16 data input lines (DP0-15) when an expansion cable is not connected to the top edge connector of the card. All output signals to the expansion back panel from I/O expanders 1 and 2 are driven by 74H40TTL networks.

## 4.5 I/O EXPANDER SIGNAL DESCRIPTIONS AND LOGIC

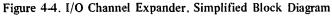

A simplified functional block diagram of the I/O expander is shown in figure 4-4. The I/O expander consists of the output data bus, the input data bus, interrupt lines, a clock, and control signals.