Technical Report 1074

# Model-Based Troubleshooting of Digital Systems

Walter Charles Hamscher

MIT Artificial Intelligence Laboratory

# Model-Based Troubleshooting of Digital Systems

by

### Walter Charles Hamscher

Revised version of a thesis submitted to the Department of Electrical Engineering and Computer Science on 12 August 1988 in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

### Abstract

This thesis describes a methodology, a representation, and an implemented program for troubleshooting digital circuit boards at roughly the level of expertise one might expect in a human novice. Existing methods for model-based troubleshooting have not scaled up to deal with complex circuits, in part because traditional circuit models do not explicitly represent aspects of the device that troubleshooters would consider important. For complex devices the model of the target device should be constructed with the goal of troubleshooting explicitly in mind. Given that methodology, the principal contributions of the thesis are ways of representing complex circuits to help make troubleshooting feasible. Temporally coarse behavior descriptions are a particularly powerful simplification. Instantiating this idea for the circuit domain produces a vocabulary for describing digital signals. The vocabulary has a level of temporal detail sufficient to make useful predictions about the response of the circuit while it remains coarse enough to make those predictions computationally tractable. Other contributions are principles for using these representations. Although not embodied in a program, these principles are sufficiently concrete that models can be constructed manually from existing circuit descriptions such as schematics, part specifications, and state diagrams. One such principle is that if there are components with particularly likely failure modes or failure modes in which their behavior is drastically simplified, this knowledge should be incorporated into the model. Further contributions include the solution of technical problems resulting from the use of explicit temporal representations and design descriptions with tangled hierarchies.

# Acknowledgements

Success is humbling: I am permanently indebted to the many fine people who have done so much for me during my years at MIT.

Randall Davis, my advisor, spent countless hours providing intellectual guidance, unflagging moral and financial support, and of course the all-important comedic perspective.

My readers Ramesh Patil, Howard Shrobe, and Peter Szolovits, spent a great deal of time with me and with this document, providing their own indispensably unique viewpoints.

All the usual suspects at the weekly Hardware Troubleshooting group meetings, including my friends Meyer Billmers, Choon Goh, Hal Haig, Paul Resnick, Mark Shirley, Reid Simmons, Raúl Valdés-Pérez, Jeff Van Baalen, Dan Weld, and Peng Wu, provided close comradeship and a constant stream of intellectual stimulation and feedback on my work and on my presentations of it. Brian Williams deserves special mention for providing so many patient explanations, penetrating observations, and encouraging words.

Comments from Eugene Charniak, Johan de Kleer, Tom Knight, Drew McDermott, John McDermott, Chuck Rich, Gordon Robinson, Bill Swartout, Dick Waters, and Mike Wellman, sometimes only a single incisive sentence, all helped to clarify my thinking at crucial moments. Everyone at the MIT Artificial Intelligence Laboratory contributed to its atmosphere of challenge and excitement.

The Joshua group and others at Symbolics, including my friends Steve Anthony, John Aspinall, Brian Bauer, Bob Cassels, Jackie Covo, Doug Evans, John Hotchkiss, Jim Loftus, Neil Mayle, and Steve Rowley, taught me much about AI in the world outside this ivory tower.

The love and encouragement of my parents and of my wife, Cristina Ciro, enabled me to carry the work through to its completion. Their patient and unwavering support is most humbling of all. This is their success, too!

This report describes research done at the Artificial Intelligence Laboratory of the Massachusetts Institute of Technology. Support for the author's artificial intelligence research on troubleshooting is provided by the Digital Equipment Corporation, Wang Laboratories, Symbolics, and the Advanced Research Projects Agency of the Department of Defense under Office of Naval Research contract N00014-85-K-0124.

To my Family

# Contents

| 1 | Intr | roduction                                 | 1  |

|---|------|-------------------------------------------|----|

|   | 1.1  | Model-Based Troubleshooting               | 1  |

|   | 1.2  | A Troubleshooting Scenario                | 6  |

|   | 1.3  | Contributions                             | 11 |

|   | 1.4  |                                           | 14 |

| 2 | Bac  | kground 1                                 | 16 |

|   | 2.1  | The Symptom-Based Approach                | 16 |

|   |      | 2.1.1 Dealing with Uncertainty            | 17 |

|   |      | 2.1.2 Organizing Knowledge                | 18 |

|   |      |                                           | 18 |

|   |      | 2.1.4 Summary of Symptom-Based Approaches | 19 |

|   | 2.2  | The Model-Based Approach                  | 19 |

|   |      | 2.2.1 Modeling                            | 20 |

|   |      |                                           | 23 |

|   |      | 2.2.3 Candidate Generation                | 24 |

|   |      | 2.2.4 Discrimination                      | 31 |

|   |      |                                           | 33 |

|   |      |                                           | 35 |

| 3 | Tro  | ubleshooting Scenarios                    | 38 |

|   | 3.1  | Clock Generator Examples                  | 40 |

|   |      |                                           | 41 |

|   |      |                                           | 42 |

|   | 3.2  | Audio Decoder Examples                    | 43 |

|   |      |                                           | 44 |

|   |      | <del>-</del>                              | 49 |

|   |     | 3.2.3   | Audio Decoder Example I                      |   |  |   | 49  |

|---|-----|---------|----------------------------------------------|---|--|---|-----|

|   |     | 3.2.4   | Audio Decoder Example II                     |   |  |   | 52  |

|   |     | 3.2.5   | Audio Decoder Example III                    |   |  |   |     |

|   |     | 3.2.6   | Audio Decoder Example IV                     |   |  |   | 54  |

|   |     | 3.2.7   | Summary of the Audio Decoder Examples        |   |  |   | 57  |

|   | 3.3 | Input 3 | Encoder Examples                             |   |  |   | 57  |

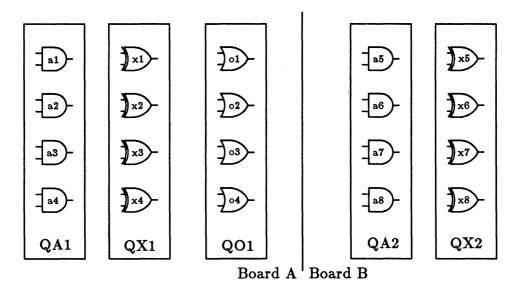

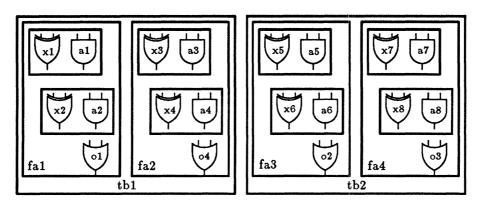

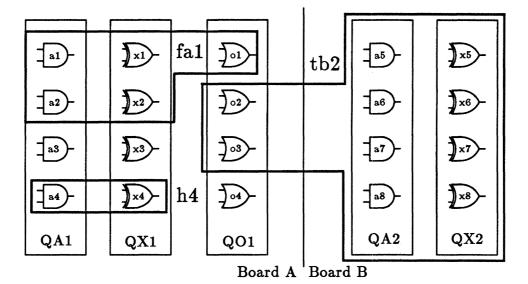

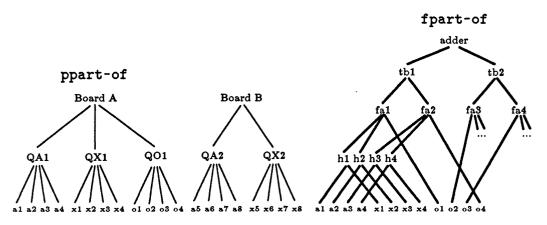

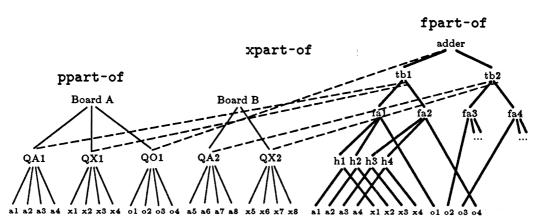

|   |     | 3.3.1   | Functional Organization of the Input Encoder |   |  |   | 57  |

|   |     | 3.3.2   | Physical Organization of the Input Encoder . |   |  |   | 59  |

|   |     | 3.3.3   | Expected Behavior of the Input Encoder       |   |  |   | 62  |

|   |     | 3.3.4   | Finding a faulty Input Processor             |   |  |   | 63  |

|   |     | 3.3.5   | Finding a faulty Console Controller          |   |  |   | 67  |

|   | 3.4 | Summ    | ary of Troubleshooting Scenarios             |   |  |   | 69  |

| 4 | Rep | resent  | ing Circuit Structure                        |   |  |   | 70  |

|   | 4.1 |         | al Organization                              |   |  |   | 71  |

|   |     | 4.1.1   | Primitive Components                         |   |  |   | 71  |

|   |     | 4.1.2   | BASIL                                        |   |  |   | 74  |

|   |     | 4.1.3   | The Physical Part-Of Hierarchy               |   |  |   | 76  |

|   | 4.2 | Functi  | onal Organization                            |   |  |   |     |

|   |     | 4.2.1   | The Functional Part-Of Hierarchy             |   |  |   | 80  |

|   |     | 4.2.2   | Principles for Structural Composition        | • |  | • | 82  |

| 5 | Rep | resent  | ing Circuit Behavior                         |   |  |   | 86  |

|   | 5.1 | TINT    |                                              |   |  |   | 90  |

|   |     | 5.1.1   | Signals                                      |   |  |   | 90  |

|   |     | 5.1.2   | Rules                                        |   |  |   | 92  |

|   |     | 5.1.3   | Signal Histories                             |   |  |   | 93  |

|   |     | 5.1.4   | Equality                                     |   |  |   |     |

|   |     | 5.1.5   | Summary                                      |   |  |   | 96  |

|   | 5.2 | Combi   | national Behaviors                           |   |  |   | 98  |

|   | 5.3 | Sequer  | ntial Behaviors                              |   |  |   | 103 |

|   | 5.4 | Abstra  | actions                                      |   |  |   | 107 |

|   |     | 5.4.1   | Temporal Abstractions                        |   |  |   | 110 |

|   |     | 5.4.2   | =                                            |   |  |   |     |

|   |     | 5.4.3   | Summary of Abstractions                      |   |  |   |     |

|   | 5.5 | Event   | Preservation                                 |   |  |   |     |

|   | 5.6 |         | tion                                         |   |  |   |     |

|   | 5.7  | Synchronization                                                                                        |

|---|------|--------------------------------------------------------------------------------------------------------|

|   | 5.8  | Encapsulation                                                                                          |

|   |      | 5.8.1 The Reset Hold Counter                                                                           |

|   |      | 5.8.2 The Audio Counter                                                                                |

|   |      | 5.8.3 Microprocessors                                                                                  |

|   |      | 5.8.4 Abstract Buffers                                                                                 |

|   |      | 5.8.5 Programmed Microprocessors                                                                       |

|   | 5.9  | Related Work                                                                                           |

|   |      | 5.9.1 Temporally Quantified Statements                                                                 |

|   |      | 5.9.2 Intervals and Constraints on Intervals                                                           |

|   |      | 5.9.3 Persistence                                                                                      |

|   |      | 5.9.4 Temporal Indexing                                                                                |

|   | 5.10 | Summary of Behavior Representation                                                                     |

| 8 | Ren  | resenting Faults and Misbehaviors 166                                                                  |

|   | 6.1  | Failure Likelihoods                                                                                    |

|   | 6.2  | Representing Syndromes                                                                                 |

|   | 6.3  | Principles for Using Syndromes                                                                         |

|   | 6.4  | Consequences of Using Syndromes                                                                        |

|   | 6.5  | Summary of Faults and Misbehaviors                                                                     |

| 7 | Troi | ıbleshooting 184                                                                                       |

| • | 7.1  | Conflicts and Candidates                                                                               |

|   | 7.2  | Decomposition                                                                                          |

|   | 7.3  | Ranking and Refinement                                                                                 |

|   | 7.4  | Making Observations                                                                                    |

|   | 1.4  | 7.4.1 Prediction Strength and Probe Selection                                                          |

|   |      | 7.4.1 Trediction Strength and Frobe Selection 202<br>7.4.2 Temporal Quantification and Granularity 204 |

|   | 7.5  |                                                                                                        |

|   | 1.5  | Evaluation                                                                                             |

|   |      | 3                                                                                                      |

|   |      |                                                                                                        |

|   | 7 C  | 7.5.3 Speed                                                                                            |

|   | 7.6  | Summary                                                                                                |

| 8 |      | clusions and Future Work 211                                                                           |

|   | 8.1  | Engineering Issues                                                                                     |

|   | 8.2  | Deriving the Representation 216                                                                        |

|              | 8.3            | Generalizing the Methodology                 | 7 |

|--------------|----------------|----------------------------------------------|---|

| A            | Scer           | ario Transcripts 220                         | ) |

|              | <b>A.1</b>     | Clock Generator Example                      | _ |

|              | A.2            | Audio Decoder Example I                      | ļ |

|              | <b>A.3</b>     | Audio Decoder Example I with Syndromes       | , |

|              |                | Audio Decoder Example II                     |   |

|              |                | Audio Decoder Example II with Syndromes      |   |

|              |                | Audio Decoder Example III                    |   |

|              |                | Audio Decoder Example III with Syndromes 241 |   |

|              |                | Audio Decoder Example IV                     |   |

|              |                | Audio Decoder Example IV with Syndromes      |   |

|              |                | Input Encoder Example I                      |   |

|              |                | Input Encoder Example II                     |   |

| В            | Abs            | tractions and Behaviors 268                  | ļ |

| $\mathbf{C}$ | Rese           | et Hold Counter Behavior 273                 | j |

| D            | Aud            | io Counter Behavior 284                      | Ļ |

|              |                |                                              |   |

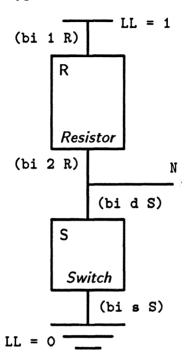

| ${f E}$      |                | Switch Level Model 288                       |   |

|              | E.1            | Pins and other Connections                   | ţ |

|              | $\mathbf{E.2}$ | Resistors                                    | ) |

|              |                | Switches                                     |   |

| ${f Bi}$     | bliog          | raphy 306                                    | Ł |

# List of Figures

| 1.1  | Model-Based Troubleshooting                                      |

|------|------------------------------------------------------------------|

| 1.2  | Model-Based Troubleshooting Problems                             |

| 1.3  | A Portion of the Console Controller Board                        |

| 1.4  | Likely Suspects After Probing Interrupt                          |

| 1.5  | Likely Suspects After Probing Reset                              |

| 1.6  | Likely Suspects After Probing Constant                           |

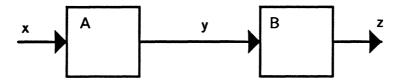

| 2.1  | Behavior Prediction Example                                      |

| 2.2  | Reasoning from Effects to Causes                                 |

| 2.3  | Behavior Prediction Example                                      |

| 2.4  | Reasoning from Effects to Causes                                 |

| 2.5  | Discrepancies Produce Conflicts                                  |

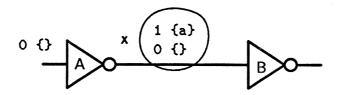

| 2.6  | If x is not 1, Only A Could be Broken                            |

| 2.7  | Inverter B Could be Pulling x Down                               |

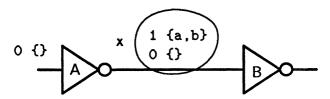

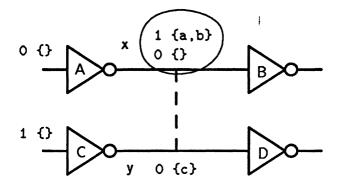

| 2.8  | A Short Could be Pulling x Down                                  |

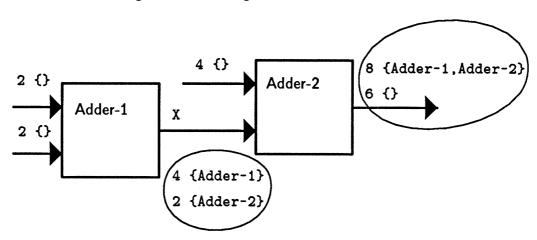

| 2.9  | Diagnosis of Adder-1                                             |

| 2.10 | Diagnosis of Adder Substructures                                 |

| 3.1  | Overall Troubleshooting Program Organization                     |

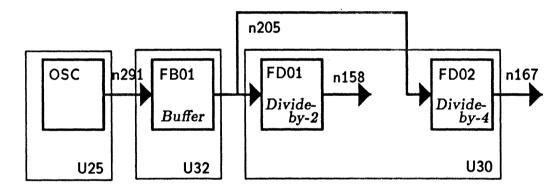

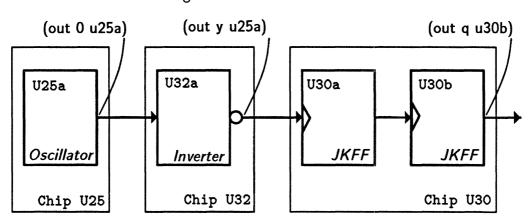

| 3.2  | Clock Generator Schematic                                        |

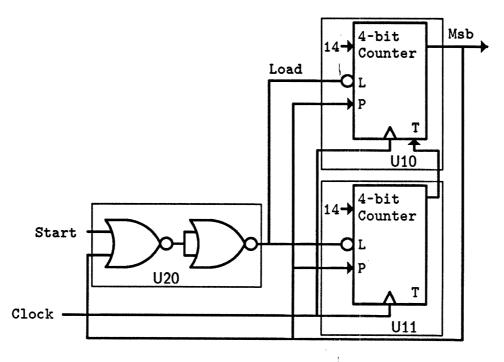

| 3.3  | Clock Generator Structure 41                                     |

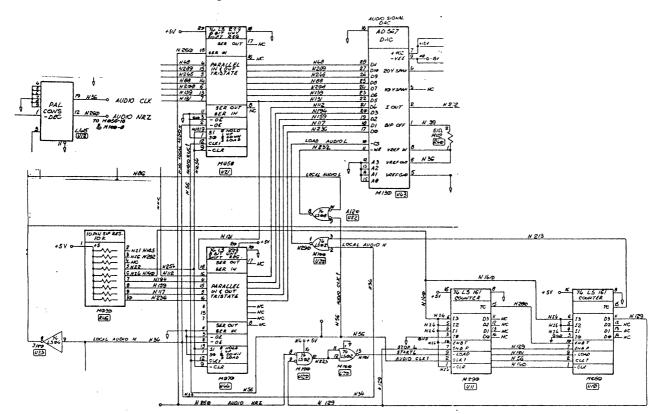

| 3.4  | Audio Decoder Schematic                                          |

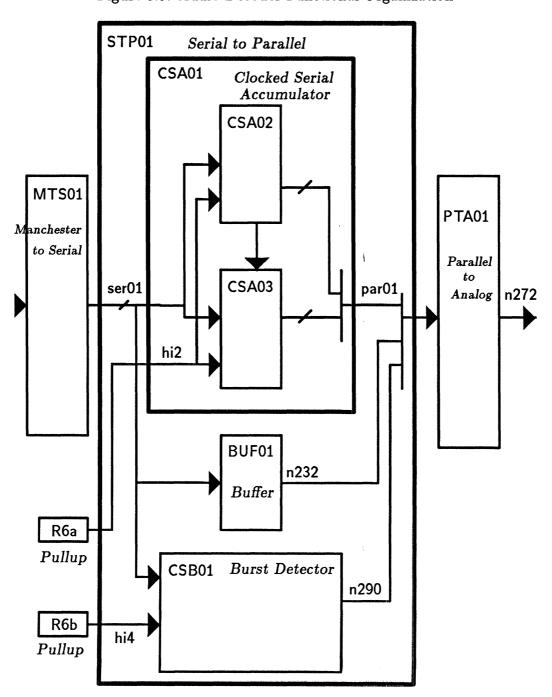

| 3.5  | Audio Decoder Functional Organization 46                         |

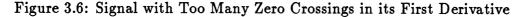

| 3.6  | Signal with Too Many Zero Crossings in its First Derivative . 47 |

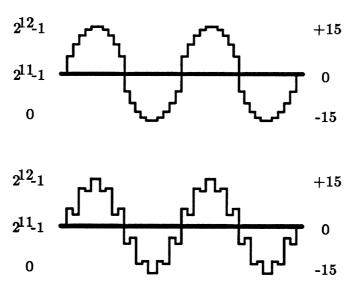

| 3.7  | Audio Decoder Physical Organization 50                           |

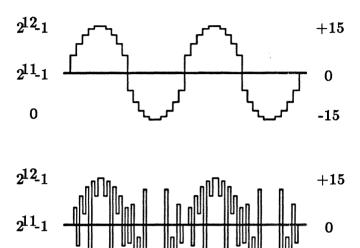

| 3.8  | Signal with Too Many Zero Crossings                              |

| 3.9  | Internal Structure of CSB01                                      |

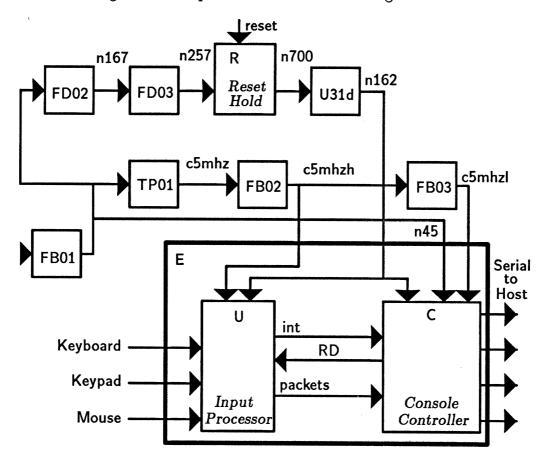

| 3.10 | Input Encoder Functional Organization                            |

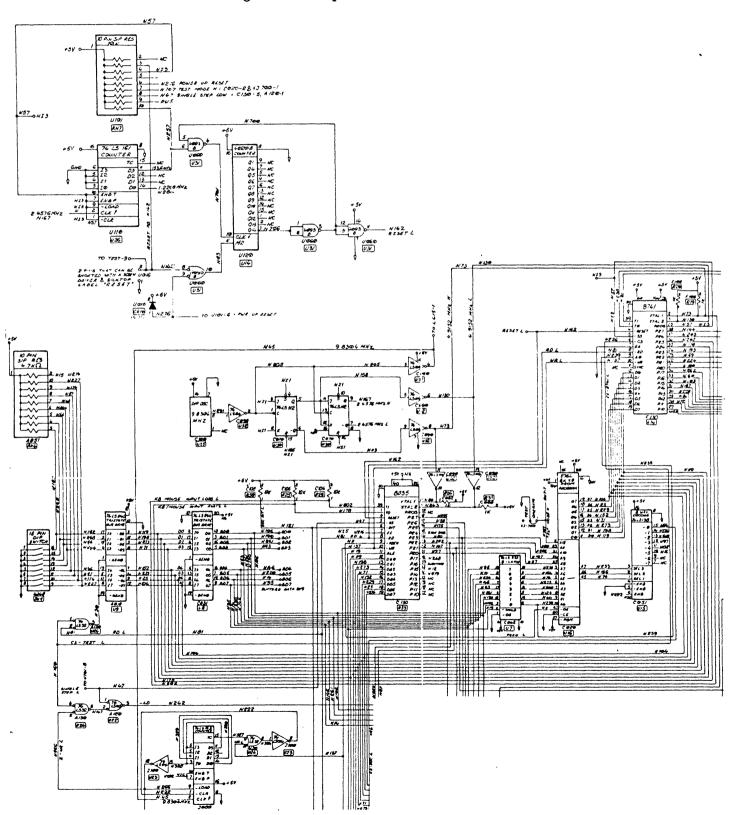

| 3.11                                                                        | Input Encoder Schematic                                                                                                                                                                                                                                                                                                                    | 60                                                                        |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 3.12                                                                        | Input Encoder Physical Organization                                                                                                                                                                                                                                                                                                        | 61                                                                        |

| 4.1                                                                         | Chip Cross Section                                                                                                                                                                                                                                                                                                                         | 72                                                                        |

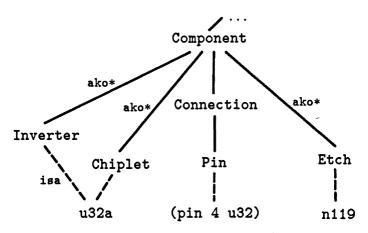

| 4.2                                                                         | Abbreviated AKO hierarchy                                                                                                                                                                                                                                                                                                                  | 74                                                                        |

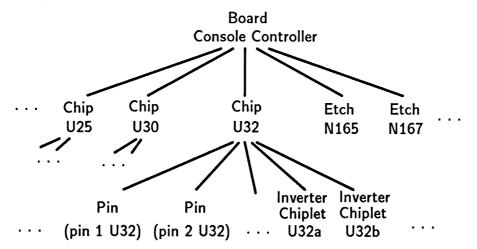

| 4.3                                                                         | A Portion of the ppart-of Relation                                                                                                                                                                                                                                                                                                         | 77                                                                        |

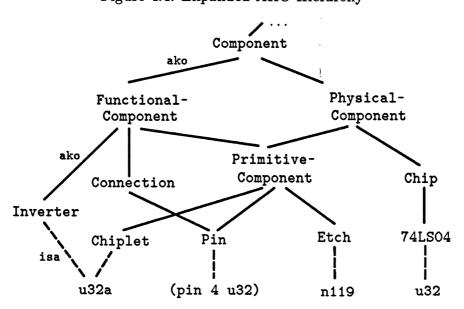

| 4.4                                                                         | Expanded AKO Hierarchy                                                                                                                                                                                                                                                                                                                     | 79                                                                        |

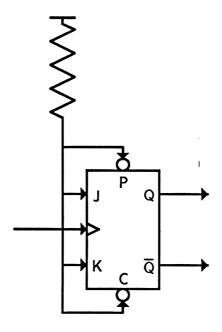

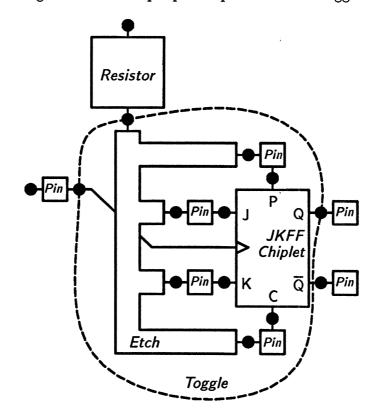

| 4.5                                                                         | JK Flipflop Unencapsulated                                                                                                                                                                                                                                                                                                                 | 80                                                                        |

| 4.6                                                                         | JK Flipflop Encapsulated as a Toggle                                                                                                                                                                                                                                                                                                       | 81                                                                        |

| 4.7                                                                         | Power Ports of Chip U30 and its Chiplets                                                                                                                                                                                                                                                                                                   | 83                                                                        |

| 4.8                                                                         | Encapsulating Reconvergence                                                                                                                                                                                                                                                                                                                | 84                                                                        |

| 4.9                                                                         | Encapsulating a Sequential Loop                                                                                                                                                                                                                                                                                                            | 84                                                                        |

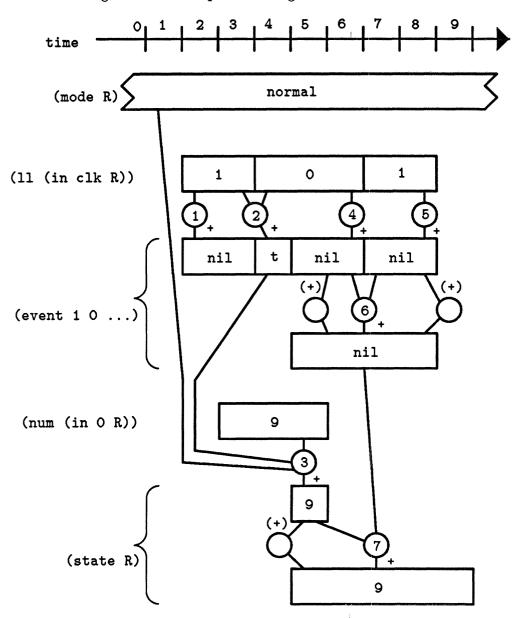

| 5.1                                                                         | TINT Signal History Example                                                                                                                                                                                                                                                                                                                | 95                                                                        |

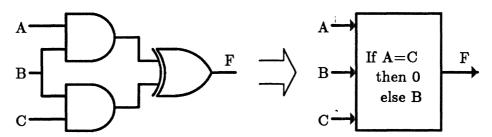

| 5.2                                                                         | Combinational Behavior Example                                                                                                                                                                                                                                                                                                             |                                                                           |

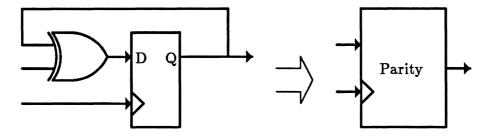

| 5.3                                                                         | Example with Register Behavior Rules                                                                                                                                                                                                                                                                                                       |                                                                           |

| 5.4                                                                         | Abstractions and Behaviors                                                                                                                                                                                                                                                                                                                 | 107                                                                       |

| 5.5                                                                         | Example of Abstractions and Behaviors                                                                                                                                                                                                                                                                                                      | 108                                                                       |

| 5.6                                                                         | Sufficiently Complex Abstractions Make Any Behavior Trivial                                                                                                                                                                                                                                                                                | 109                                                                       |

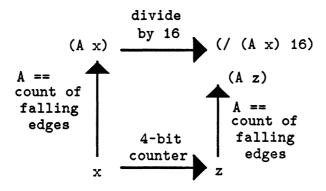

| 5.7                                                                         | The Behavior of a Counter with Respect to a "Counting" Ab-                                                                                                                                                                                                                                                                                 |                                                                           |

|                                                                             | -4 1 ·                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|                                                                             | straction                                                                                                                                                                                                                                                                                                                                  | 109                                                                       |

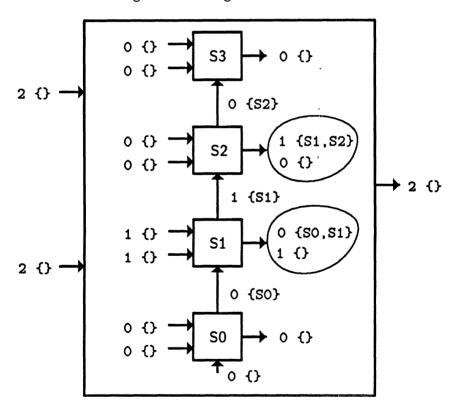

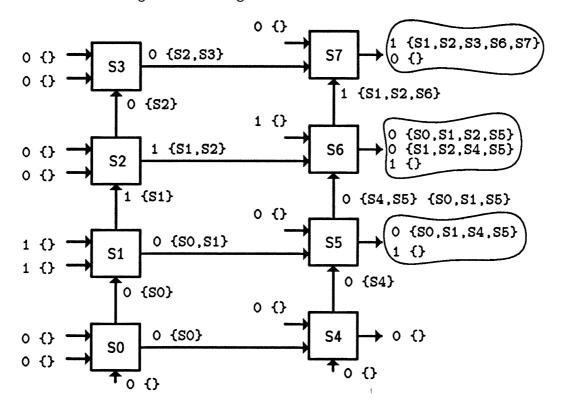

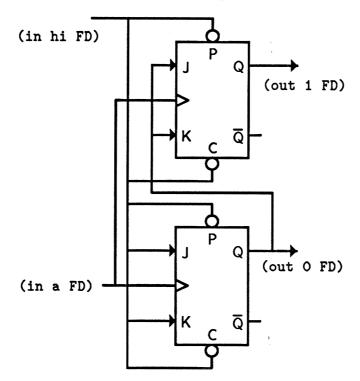

| 5.8                                                                         | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   |                                                                           |

| 5.8<br>5.9                                                                  |                                                                                                                                                                                                                                                                                                                                            | 129                                                                       |

| 5.9<br>5.10                                                                 | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   | 129<br>134<br>136                                                         |

| 5.9<br>5.10                                                                 | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   | 129<br>134<br>136                                                         |

| 5.9<br>5.10<br>5.11                                                         | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   | 129<br>134<br>136<br>141                                                  |

| 5.9<br>5.10<br>5.11<br>5.12                                                 | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   | 129<br>134<br>136<br>141<br>142                                           |

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13                                         | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   | 129<br>134<br>136<br>141<br>142<br>145                                    |

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14                                 | Frequency Divider Implemented with JKFFs                                                                                                                                                                                                                                                                                                   | 129<br>134<br>136<br>141<br>142<br>145<br>150                             |

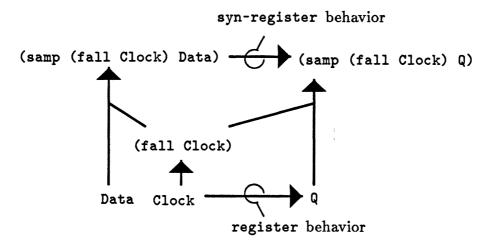

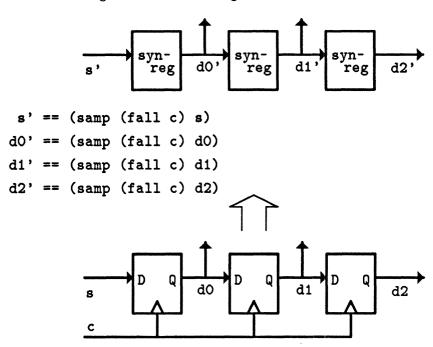

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15                         | Frequency Divider Implemented with JKFFs Register Abstractions                                                                                                                                                                                                                                                                             | 129<br>134<br>136<br>141<br>142<br>145<br>150                             |

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16                 | Frequency Divider Implemented with JKFFs Register Abstractions                                                                                                                                                                                                                                                                             | 129<br>134<br>136<br>141<br>142<br>145<br>150<br>156<br>157               |

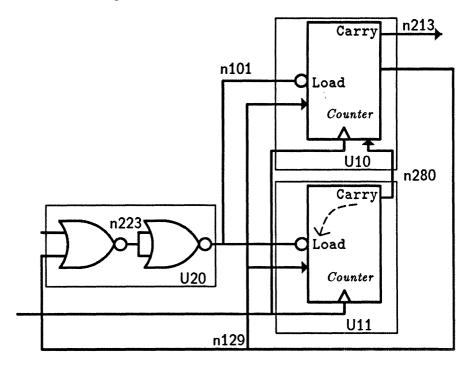

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17         | Frequency Divider Implemented with JKFFs Register Abstractions                                                                                                                                                                                                                                                                             | 129<br>134<br>136<br>141<br>142<br>145<br>150<br>156<br>157               |

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17         | Frequency Divider Implemented with JKFFs Register Abstractions Shift Register as Cascade Reset Hold Counter Reset Hold Counter Three State Automaton Audio Counter The Third Key is Pressed Functional Organization of Console Controller Components of B Components U and C Together form Component E State Diagram of E                  | 129<br>134<br>136<br>141<br>142<br>145<br>150<br>156<br>157<br>159        |

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18 | Frequency Divider Implemented with JKFFs Register Abstractions Shift Register as Cascade Reset Hold Counter Reset Hold Counter Three State Automaton Audio Counter The Third Key is Pressed Functional Organization of Console Controller Components of B Components U and C Together form Component E State Diagram of E  Clock Generator | 129<br>134<br>136<br>141<br>142<br>145<br>150<br>157<br>159<br>159        |

| 5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18 | Frequency Divider Implemented with JKFFs Register Abstractions Shift Register as Cascade Reset Hold Counter Reset Hold Counter Three State Automaton Audio Counter The Third Key is Pressed Functional Organization of Console Controller Components of B Components U and C Together form Component E State Diagram of E                  | 129<br>134<br>136<br>141<br>142<br>145<br>150<br>157<br>159<br>170<br>177 |

| 7.2 | Physical Organization of Four-Bit Adder 189                      |

|-----|------------------------------------------------------------------|

| 7.3 | Functional Organization of Four-Bit Adder 189                    |

| 7.4 | Physical and Functional Organizations                            |

| 7.5 | Physical and Functional Decompositions of the Four-Bit Adder 191 |

| 7.6 | XPART-OF Relations in the Four-Bit Adder 192                     |

| 7.7 | Clock Generator                                                  |

| 7.8 | Distinguishing Between Diagnoses                                 |

| 7.9 | Detail of Audio Decoder                                          |

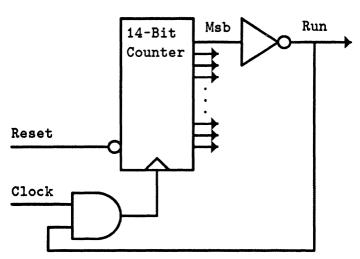

| C.1 | Reset Hold Counter                                               |

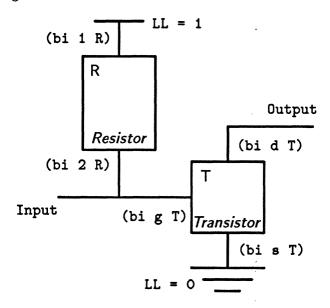

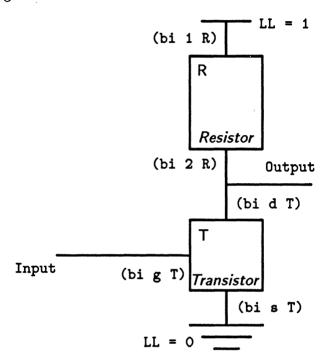

| E.1 | Typical Switch-Resistor Combination                              |

| E.2 | TTL Inverter as Modeled with TINT                                |

| E.3 | nMOS Inverter as Modeled with TINT 295                           |

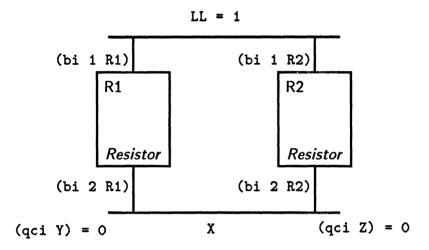

|     | Impasse Example                                                  |

# Chapter 1

# Introduction

A field engineer plugs in a broken circuit board, makes a half dozen simple probes with an oscilloscope, and after ten minutes ends up swapping a chip, which fixes the problem.

A model-based troubleshooting program spends a day simulating the expected behavior of the same misbehaving board, and requests that a logic analyzer be used to capture a certain subset of the signals. After some hours of computation it concludes that any of the 40 chips or 400 wires on the board could be responsible for the misbehavior.

What does the field engineer know that the program does not? How can a model-based troubleshooting program represent and use that knowledge? Both the program and the field engineer have the circuit schematic and the specifications of the individual chips. The field engineer additionally has expectations about the design of the circuit, expectations about which signals in the circuit ought to be changing and how fast, and expectations about the kinds of failures that are likely to occur in digital circuits. Incorporating this knowledge into the circuit model makes it possible to be more discriminating in the generation of diagnoses and more efficient in the use of observations.

# 1.1 Model-Based Troubleshooting

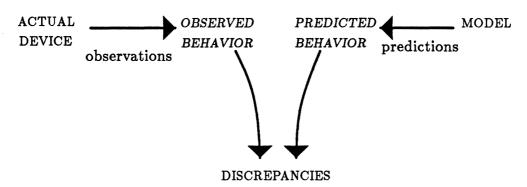

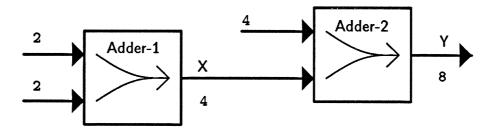

Model-based troubleshooting is driven by the interaction of observation and predictions (Figure 1.1). A device model produces predictions about what

ought to be observed; comparison with observations of the actual device produce discrepancies; these discrepancies are then traced to their possible underlying causes in the model and repairs of the actual device proposed.

Figure 1.1: Model-Based Troubleshooting

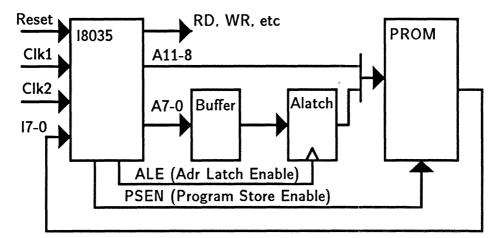

This report describes a model-based troubleshooting program. Its primary input is a model of a digital circuit that is a network of components and connections. Each component has a description of its dynamic time-dependent behavior and each connection transmits signals between components. The secondary input to the program is a description of the stimuli presented to the circuit and observations of its actual responses. The model uses those stimuli to predict what the outcomes of observations ought to be. When discrepancies are discovered, the program produces lists of components that could be responsible for the discrepancies, ranked by their relative likelihood. The program interactively suggests what observations should be made next to discriminate among these possibilities, then uses any new observations to incrementally focus on the correct diagnosis.

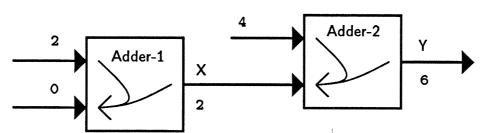

Model-based troubleshooting has been extensively demonstrated on simple devices. One of the prime motivations of this work is to scale up model-based troubleshooting techniques to deal with significantly more complex devices. The fundamental problems in scaling model-based troubleshooting technology to do this can be understood as problems within each element of the paradigm (Figure 1.2). These five problems and their solutions are discussed individually below.

Models are incomplete. No model can possibly capture every detail of

ACTUAL OBSERVED PREDICTED MODEL

DEVICE observations

Observations are costly

Observations are incomplete

DISCREPANCIES

Figure 1.2: Model-Based Troubleshooting Problems

the actual device. Lack of detail in the device representation means that some failures will be indistinguishable and others will be misdiagnosed. For example, if a wire connecting several terminals is represented as a single component, then the program will diagnose a break anywhere along the wire as a failure of the whole wire. If the model says that the only devices affecting the state of the wire are the ones that it was meant to connect, then the troubleshooting program will misdiagnose a short between that wire and another as having been caused by one or more other failures. The selection of the primitive elements of the device representation constitutes a commitment to a set of failures worth identifying and worth distinguishing from each other.

Models are incomplete, but the consequences of that incompleteness can be controlled in part by the choice of primitive elements and their connections to each other. Principles are needed for making these choices in a way that sacrifices completeness in favor of efficiency, since the aspiration is to troubleshoot circuits with many thousands of wires, transistors, and interactions between them. One such principle is that physically separate components with indistinguishable failure effects can be treated as a single component. Another principle is that components whose failures result in the same repair can be treated as a single component. A third principle is that unlikely failures are not worth representing explicitly, so that components whose failures are individually very unlikely can all be treated as a single aggregate com-

ponent whose failure is more likely. These principles introduce additional approximations into a device model that will make some component failures indistinguishable from one another. A deeper problem arises from the fact that any model explicitly represents only some of the possible interactions between components; the program will misdiagnose any failures involving interactions that the model does not represent. The standard example is an unintentional short between two wires that are unrelated in the circuit structure diagram. The best that the troubleshooting program will do is to diagnose this as two failures, one in each wire. The approach taken in this work is not a general solution: at any given level of detail, decisions about which interactions between components ought to be represented are made solely on the basis of what is needed to explain the normal operation of the device. In the case of wires, only the interactions with the devices they are supposed to be connected to are represented, hence shorts are misdiagnosed. When it comes time to repair the two wires one may assume that their true (mutual) problem will be discovered by visual inspection.

Observations are costly. Taking measurements is nearly always appropriately regarded as being more costly than computation spent on choosing that measurement. The problem that scaling brings is that the more complex the device, the more events there are to observe, and the shorter the intervening intervals, the more difficult they are to observe. It is, for example, more costly to set up a logic analyzer to capture digital signals at particular moments than it is to observe whether they are staying at a constant zero or one.

Observations are costly, and although there is nothing that can be done about this directly, the device model can describe signals in ways that are relatively cheap to observe. For example, it is easier to observe whether a particular signal is rising or falling than to observe its changing value at every moment. This is an example of a useful temporal abstraction; a long sequence of changes of value can be summarized into a simple description that is stable over a longer time interval. A behavior model can use this kind of temporally abstract observation to make other temporally abstract predictions, without requiring that any explicit deductions ever be made about the individual changing values. As a general principle temporal abstractions are useful because they provide a better match to the observations that can be made cheaply.

Observations are incomplete and imprecise. Discrepancies can only be

detected where observations can be made. But even when observations can be made, they may be too coarse to detect discrepancies with the model. For example, if the model predicts that a certain current should be flowing in a wire, but the troubleshooter can only measure currents to within 20%, then the current could actually be wrong and yet yield no apparent discrepancy, hence yield no new information. One of the consequences of incomplete observations is that there will inevitably be pairs of diagnoses that cannot be discriminated, since their only difference might be in some unobservable feature. Inability to make certain observations economically imposes limits on the ability of the troubleshooting program to isolate faults.

Because observations are incomplete, ambiguity among the logically possible diagnoses is inevitable. If the troubleshooting goal is to find the most likely diagnosis, however, other sources of information are available. One of these sources is information about the relative failure rates of different physical components, from which the troubleshooter can produce a rank ordering of the diagnoses by plausibility. A related source is information about how components usually fail and what misbehaviors they produce; this can be used to refine the likelihood estimates for some diagnoses. These sources of knowledge alleviate the indiscriminacy caused by incomplete observations because they can be used to discount unlikely diagnoses and leave the remaining (relatively more likely) ones behind.

Prediction is costly. It is impractical within a troubleshooting session to simulate an entire circuit board at the gate level for more than a few clock cycles. The culprit is not the structural complexity of the board in number of gates or wires. The culprit is the complexity of the behavior — the number of events that happen and need to be simulated. Waiting for more computing power to apply to the problem is not a solution if the boards to be diagnosed themselves get faster and more complex.

Prediction is costly, but this can be addressed by using temporally abstract behavior descriptions. Temporal abstractions can summarize many individual events into an aggregate description stable over a longer interval. For example, a given signal may be described as a sequence of many thousands of individual alternating zeroes and ones, or more abstractly in terms of the number of falling edges that have appeared, or even more abstractly as the number of one-to-zero cycles per unit time. Although the value of the underlying signal may be changing many times per second, the average number of cycles per unit time may be relatively stable. Descriptions that are

stable in this way are less costly to make predictions from. For example, the troubleshooting scenario to be presented shortly is simple because the behavioral complexity of microprocessors can be reduced to a simple relationship between the rates of change at their inputs and outputs.

Predictions are incomplete. A consequence of using abstract models of behavior to achieve more economical prediction is that the resulting predictions may be imprecise or ambiguous. Predictions that are too coarse make it difficult to detect discrepancies with observations, and this in turn sacrifices some of the ability of the program to isolate faults.

Economical predictions are incomplete, but the indiscriminacy that results can be alleviated by using multiple levels of behavioral abstraction. If needed, more detailed predictions can be made for only a subset of the entire device. This may allow more discrepancies to be detected and thereby rule out some diagnoses.

# 1.2 A Troubleshooting Scenario

The troubleshooting program described in this report uses a rich and multilayered circuit model that is designed to address the problems identified above. The model represents the physical organization in terms of chips, wires, and so forth, and represents the functional organization in terms of how its parts interact to achieve the overall intended behavior. Its levels of detail range from a qualitative model of resistors and switches up to arbitrarily large computational modules. It represents the behaviors of components using both traditional digital abstractions and a novel set of temporal abstractions that describe signals in terms such as cycles, frequency, and change. Finally, it incorporates knowledge not just about how the circuit components should work, but for a few, how they break and how often. Only one circuit has been modeled this way, but it is large, complex, internally diverse, and real: a portion of the Symbolics 3600 Console Controller Board that contains two microprocessors (both running programs with several hundred instructions), thirty supporting chips, and one hundred sixty wires.

Seven troubleshooting scenarios using this circuit will be presented in this document. One of these scenarios, presented here in abbreviated form, serves to illustrate the distinctive features of the circuit model and the interaction of the troubleshooting program with it.

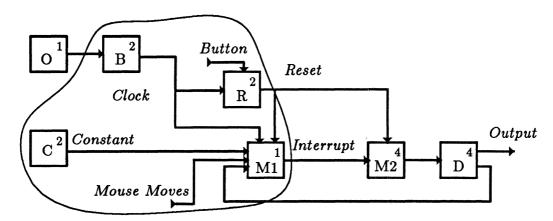

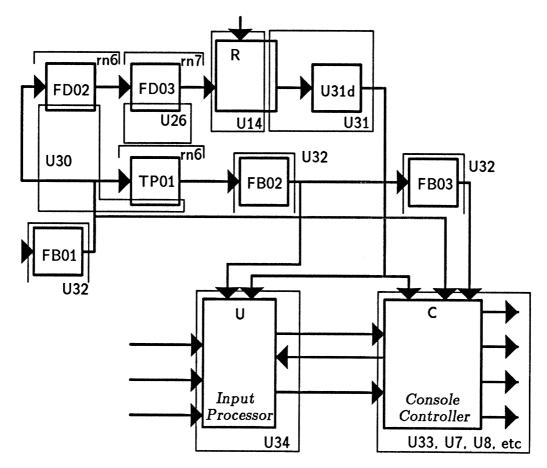

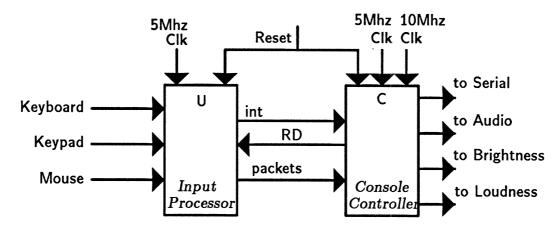

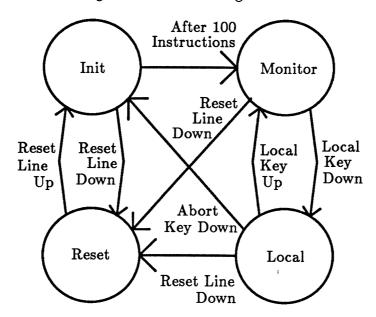

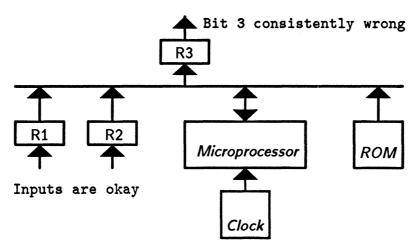

The Console Controller Board is responsible for transmitting keystrokes and mouse motions to the host computer and for decoding the video signal coming from the host for display on a CRT and the audio signal for output to a speaker. Some keystroke sequences can change the volume of the speaker, the brightness of the CRT, and so forth. Figure 1.3 shows abstractly a few of the components (boxes) and the signals through which they interact (arrows).

Clock

Reset

Reset

Reset

Reset

Reset

Reset

Muse Moves

Reset

Reset

Muse Moves

Figure 1.3: A Portion of the Console Controller Board

Each small superscript represents the number of chips in that component; there are 16 in all. The oscillator O produces a clock signal that is buffered by B and sent on to two places: the reset circuitry R and to a microprocessor M1. The microprocessor M1 polls the mouse inputs. Each tenth of an inch of mouse motion along its x or y axes causes M1 to interrupt a second microprocessor M2 with a two-byte message. M2 responds to the interrupt through some bus control circuitry D. After receiving the two-byte message M2 then sends the message on to the host, again through the bus control circuitry D. The host displays the changed mouse position on the screen.

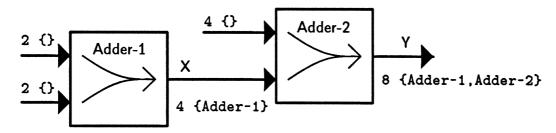

Suppose the Console Controller Board reset button is pressed and the mouse rolled around for a couple of seconds. The model predicts that if all 16 chips are working, then mouse motion will be observed at *Output*. The model is too coarse to predict how fast or how far the cursor will move on the screen — it predicts only that motion will be observed. This temporally abstract behavior is both more efficient to make predictions from and easier to observe than the traditional clock-cycle-by-clock-cycle model of digital circuit behavior.

But suppose the mouse cursor does not move at all. The program indicates that any one of the 16 chips might be broken; each chip is a suspect. There are now many possible signals to probe, and the program ranks them. The likeliest chip to fail by far is the onboard oscillator O. The program suggests probing its output; suppose it is observed to have a frequency of approximately 10 Mhz.

The oscillator O can be discounted as an unlikely suspect using knowledge in the model about how some components fail. The model says that when oscillators fail, they usually fail catastrophically, producing an output frequency of 0. Because the signal was observed to be changing, the program concludes that the oscillator chip is probably not responsible. It is still a suspect, just a relatively unlikely one. This leaves 15 chips as likely suspects.

The program now needs to suggest another probe. To suggest a probe it considers the predictions that the model makes at each signal. For example, the model predicted that the output of the oscillator O should have frequency 10 Mhz, and the probe verified this. The model also predicts that the *Clock* signal should have frequency 5 Mhz. The representation of these clock signals in terms of their frequencies is an example of a temporal abstraction; millions of underlying events (rising and falling edges) have been abstracted into a simple description that is easy to reason about and easy to observe.

Although the model represents many signals in temporally abstract ways, there are other signals for which the standard digital vocabulary suffices. For example, the *Constant* output of C is a constant 1 throughout the entire session, and the model predicts that. Also, the *Reset* signal should be asserted while the reset button is pressed and unasserted otherwise, and the model predicts that as well.

These predictions — that the clock frequency is 5 Mhz, and so forth — can be used in subsequent predictions. The temporally abstract behavior model for the first microprocessor M1 says that if the Clock input is 5 Mhz, the Constant input is 1, and the Reset signal is not asserted, then the microprocessor is running. While M1 is running, each movement of the mouse results in the Interrupt line being asserted. If all that is known is that the mouse is moving around, the model does not predict exactly when it will be asserted; rather it predicts that the signal will be changing while the mouse is moving and a constant 1 value otherwise.

The model makes many other predictions, but these are all that will be needed in this example. The important one at the moment is the predic-

tion that *Interrupt* signal will be changing while the mouse is moving. This prediction depends on eight chips working properly, those in all components except M2 and D.

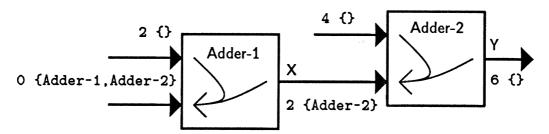

The probe that the program now suggests is the *Interrupt* output of M1. Suppose the interrupt line is probed, revealing that it is a constant 1 even while the mouse is rolled around. This is a discrepancy, since it was supposed to be changing so long as those eight chips were working properly. One of the chips was the oscillator, which has been shown to be an unlikely suspect; this leaves seven as likely suspects (Figure 1.4).

Figure 1.4: Likely Suspects After Probing Interrupt

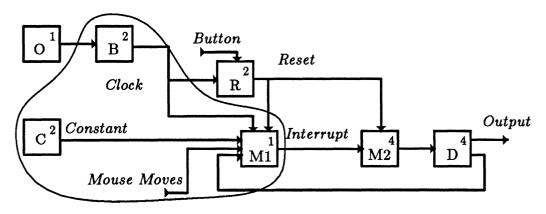

The model predicted that the *Reset* signal should be asserted just while the reset button was pressed, so long as the five chips in O, B and R were working. Probing the *Reset* signal reveals that upon pressing the button it is asserted, then unasserted. This means that the chips in R are no longer suspects, since their failure could not explain the observations made. Now there are 5 likely suspects (Figure 1.5).

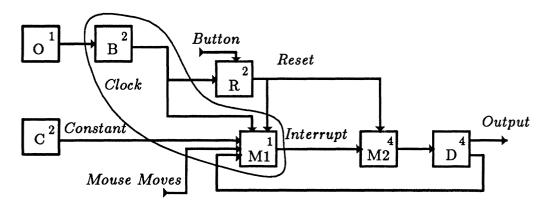

The model predicted that the *Constant* signal should be 1 throughout the session, so long as the chips in C were working. Probing this signal reveals that it is indeed 1, so the chips in C are no longer suspects. Now there are 3 likely suspects (Figure 1.6).

Finally, a probe of the Clock signal reveals that it has frequency around 5 Mhz. The model says that if the clock input to M1 has a high enough

Figure 1.5: Likely Suspects After Probing Reset

Figure 1.6: Likely Suspects After Probing Constant

frequency and the reset input is not asserted, then the microprocessor should be running. This means that the *Interrupt* signal should be changing, which contradicts previous observations. Hence M1 is the only remaining suspect and the program terminates.

The interesting thing about this scenario is that it is so simple compared to the underlying complexity of the real circuit. The circuit is structurally complex; there are thousands of transistors in the chips, hundreds of possible flaws in the wires alone. It is behaviorally complex; consider all the micro-

processor instruction cycles that occurred during the one second of mouse motion. People can troubleshoot the circuit without thinking about all those details, and the program can troubleshoot it without explicitly representing them.

The important thing about the model is not that it uses abstractions to deal with complexity; any representation does that. The important idea is that there are structural and behavioral abstractions appropriate to troubleshooting. Temporal abstractions, in particular, allow the program to avoid simulating long sequences of events and instead reason in terms of "moving" mice, "running" clocks, "changing" signals, and so forth. There are also principles by which those abstractions can be manually applied to a complex circuit to construct the rich representation that makes troubleshooting of complex devices tractable. The model of the Console Controller Board is appropriate for model-based troubleshooting because it was constructed according to those principles.

## 1.3 Contributions

This thesis presents a methodology, a representation, and an implemented program for troubleshooting digital circuit boards at roughly the level of expertise of a human novice.

The methodological claim is that existing methods for model-based troubleshooting have not scaled up to deal with complex digital circuits because traditional circuit models do not explicitly represent aspects of the device that troubleshooters would consider important. For complex devices the model of the target device should be constructed with the goal of troubleshooting explicitly in mind.

Given that methodology, there are principles by which complex circuits can be represented so as to make those important aspects explicit and thereby help make the troubleshooting task tractable. Some of the salient principles follow.

One set of principles concerns how the structure of a given circuit should be represented.

• Components in the representation of the physical organization of the circuit should correspond to the possible repairs of the actual device.

The representation of physical organization plays a central role in the troubleshooting program, and the program represents all of its diagnoses in terms of the physical components that could be damaged. In the scenario presented earlier, for example, the diagnoses were expressed in terms of chips, which are "repaired" by replacement. Making the elements of this representation correspond to possible repair actions ensures that the troubleshooting program will not waste effort trying to discriminate between diagnoses that have identical repairs.

• Components in the representation of the functional organization of the circuit should facilitate behavioral abstraction.

The only role that an explicit representation of functional organization plays in model-based troubleshooting is to make behavior prediction more efficient. For example, the only reason that the component M2 exists in the model is because the combined behavior of the four chips inside it can be described more simply in the aggregate than individually. In extracting the functional organization from a raw schematic the modeler need only represent what will make the behavior easiest to reason with, rather than necessarily what the designer had in mind.

A second set of principles concerns the representation of circuit behavior.

• The behavior of components should be represented in terms of features that are easy for the troubleshooter to observe.

Some features of time-varying signals are easier to observe than others. The frequency of a clock, for example, is easier to observe than the timing of each of its individual transitions. Expressing the behavior of components in the terms that are more easily observed is a way of choosing where to sacrifice precision in favor of efficiency.

• The behavior of a component for which changes on its inputs always results in changes on its outputs should be represented in temporally coarse terms.

A powerful representation technique uses relationships between component inputs and outputs in terms that are stable over long periods of time or

that summarize much activity into a single parameter. In the troubleshooting scenario, the number of mouse step increments over a period of seconds (a single parameter describing much activity) determined the number of times the interrupt line would be asserted over that period. Such relationships can be derived when each individual change results in one or more other changes.

• A temporally coarse behavior description that only covers part of the behavior of a component is better than not covering any at all.

Although the full behavior of a component may be too complex to reduce to a simple relationship between (say) the number of changes on its inputs and the number of changes on its outputs, there may be such a relationship that involves only a subset of its inputs, assuming that the others are held constant. In the case of the microprocessor, for example, the relationship between the mouse motion inputs and interrupt output holds only so long as the clock input is running and the reset input is not asserted. Since the troubleshooting program will eventually use the more detailed behaviors as long as the diagnosis remains ambiguous, no diagnostic resolution will be lost by only representing a subset of the possible behaviors abstractly.

• A sequential circuit should be encapsulated into a single component to enable the description of its behavior in a temporally coarse way.

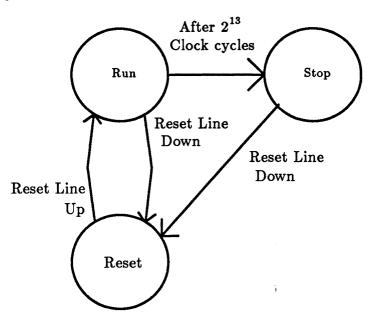

Although the individual behaviors of the components in a sequential circuit may not lend themselves to temporally coarse descriptions, the loop may be performing a simple function when taken as a whole. For example, the R component in the troubleshooting scenario is actually a sequential circuit with 2<sup>14</sup> distinct states. When viewed in temporally coarse terms, however, there is a simple correspondence between the states of the button and the state of the output. Encapsulating the group of components makes it possible to reason about its behavior in a temporally coarse way, and as in the troubleshooting scenario described, it may not be necessary to ever consider the details of its behavior.

A final set of principles concerns what knowledge about failures should be represented explicitly.

• An explicit representation of a given component failure mode should be used if the underlying failure has high likelihood.

Components break in the field in certain ways much more often than other ways. Chips, for example, fail more often with breaks in the tiny wires that connect their pins to the silicon chip inside than in other ways. The benefit of knowledge about such failures comes when they are inconsistent with the symptoms, since this can reduce the ambiguity among the possible diagnoses.

An explicit representation of a given component failure mode should be used if the resulting misbehavior is drastically simpler than the normal behavior of the component.

If a component with normally complex behavior has some internal fault or faults that cause it to misbehave catastrophically, then any partially correct behavior observed for the component makes it a less likely suspect. In the troubleshooting example, the oscillator was known to fail in a way that made it produce a zero output frequency, and that misbehavior was easy to rule out even though the measurement of its output was imprecise. The benefit of knowledge about these failure modes is especially great when the misbehavior has high likelihood as well.

The implemented model of the Console Controller Board is a concrete embodiment of the methodology and representation principles. The troubleshooting program that uses that model is an extension of standard model-based troubleshooting technology, incorporating solutions to technical problems of (i) hierarchic diagnosis with multiple and tangled hierarchies (ii) integration of explicit knowledge about failure modes into a framework for diagnosing multiple faults, and (iii) troubleshooting circuits with time-dependent behavior.

# 1.4 Organization

This document is primarily organized by the different kinds of circuit knowledge to be represented. Preliminary background material is contained in Chapter 2, which presents an overview of knowledge-based automated diagnosis, especially model-based troubleshooting. Chapter 3 presents the troubleshooting scenarios for the Console Controller Board so as to provide context for the many details to follow. The next four chapters contain the essential ideas. Chapter 4 presents a representation for circuit structure

motivated by troubleshooting requirements. Chapter 5 contains the bulk of the document and describes a representation for circuit behavior using multiple temporal abstractions and a temporal reasoning program for predicting behavior using those same abstractions. Chapter 6 describes how faults and misbehaviors are modeled and how this knowledge is used by the troubleshooting program to heuristically discount unlikely diagnoses. Chapter 7 presents the details of the troubleshooting engine and how it interacts with the choices made in representing circuit structure and behavior. Finally, Chapter 8 summarizes and presents ideas for future work. Sections on related research are distributed throughout the individual chapters.

# Chapter 2

# Background

A number of knowledge-based programs for automated diagnosis have been built for a variety of domains using a variety of implementation technologies. These programs can be characterized by the knowledge that they represent explicitly: (i) associations between underlying diseases or faults and their consequences for the system as a whole, as opposed to (ii) knowledge about the parts of the system and how they interact to produce its overall behavior. In medical diagnosis, for example, the contrast is between knowledge about diseases and their symptoms versus knowledge about the underlying mechanism; it is the difference between knowledge that emphysema causes shortness of breath versus knowledge that CO<sub>2</sub> exchange is proportional to the surface area of the alveoli. Programs that rely on the former type of knowledge will be termed symptom-based and the latter model-based. A number of programs incorporate both kinds of knowledge, but for any given program it is typically clear which one predominates. A brief review of each paradigm is presented below. One particular program for model-based diagnosis will be presented in some detail, since it provides the basis for the troubleshooting technology in this report.

# 2.1 The Symptom-Based Approach

One approach to automated diagnosis is to organize the program as a database that associates underlying diseases (faults) with their outward symptoms (manifestations). To find the underlying problem from a set of

symptoms requires straightforward lookup or pattern matching. The notion of a "fault dictionary" is the canonical example of this approach. The principal difficulty in this approach revolves around the coverage of diseases in the knowledge base. First, associations between single diseases and their symptoms does not easily support reasoning about interactions between diseases. Second, even if multiple simultaneous diseases can be handled the program is limited to considering those individual diseases that were anticipated and explicitly included by the knowledge base builder — there is no theory about how to enumerate the possible diseases of a given system. Third, given a knowledge base intended to be used for diagnosing a particular system there is no principled way to modify the knowledge base when there has been a change in the design (or in our understanding) of that system. Although the paradigm has these inherent limitations and is not used here, some important techniques that generalize beyond it were first developed within this tradition: techniques for dealing with uncertainty, for organizing large knowledge bases, and for dealing with multiple diseases. These techniques are each treated briefly below.

## 2.1.1 Dealing with Uncertainty

The notion of a disease-symptom database requires some elaboration in domains for which the underlying diseases have widely varying likelihoods and for which the associations between diseases and symptoms is less than certain. One approach is to assign prior probabilities to the diseases, assign conditional probabilities to the symptoms given each disease, and use Bayes' Theorem to find the likeliest disease given a set of symptoms [Szolovits78]. Many automated diagnosis systems use statistical information in this form in spite of the large number of conditional probabilities needed when diseases or symptoms are not independent. One reason for the enduring popularity of the probabilistic framework is that it allows the use of decision theoretic techniques to choose observations that are most likely to reduce the ambiguity among competing diagnoses. Estimating ambiguity using Shannon entropy and choosing the next observation based on a one-ply lookahead turns out to provide good results on average [Gorry73]. A non-Bayesian approach to dealing with uncertain knowledge is taken by the MYCIN program [Shortliffe76], which computes "certainty factors" for its conclusions, but it suffers from the same difficulties with interacting diseases as Bayesian approaches.

### 2.1.2 Organizing Knowledge

Obtaining diagnostic coverage of any interesting domain requires the maintenance of a large knowledge base. This in turn implies the need for principles for organizing this knowledge. Organizing knowledge about diseases, symptoms, and diagnostic procedures into frames [Minsky75] appears in the diagnosis program PIP [Pauker76]. The use of frames implies no commitment as to whether knowledge about diseases, symptoms, or causal mechanisms will be stored; rather it allows modularization of the knowledge base and thereby simplifies its maintenance. The organization of diseases and their symptoms into specialization hierarchies, as in the internal medicine diagnosis program INTERNIST [Pople82], is an elaboration of this idea. A hierarchic organization makes only a minimal commitment to the character of the knowledge, but it does allow the program to deal with groups of related diseases more efficiently. A stronger organizing principle appears in the glaucoma diagnosis program CASNET [Kulikowski82], in which knowledge is organized around disease states and their temporal progression. This network of states and their successor relationships was intended to represent a causal explanation of the disease. Although the use of this knowledge in CASNET is probabilistic and not substantially different from other symptom-based programs, it was recognized that causality could be a powerful organizing principle because the knowledge acquired from domain experts is often couched as categorical explanation that can be translated into causal terms.

# 2.1.3 Diagnosing Multiple Diseases

Among the most difficult cases in medicine and other diagnostic tasks are those in which more than one underlying disease or fault is present. One approach is to assume that all underlying diseases are statistically and causally independent. The program can then simply evaluate the likelihood of every disease individually. This approach is taken in MYCIN [Shortliffe76] but it requires such strong independence assumptions that it is only feasible in restricted domains. Another approach is taken by INTERNIST [Pople82], in which diagnoses are incrementally constructed by repeatedly choosing a disease that explains the most unexplained symptoms, until there are no unexplained symptoms left. While intuitively appealing, this does not guarantee coverage of the possible disease combinations. The approach used in

[Reggia83] addresses this coverage problem by considering every set of diseases whose combined symptoms cover all and only the observed symptoms. By Occam's razor, the hypotheses that should be considered are the minimal covering sets — those that do not include diseases not needed to explain the symptoms. Using probabilistic knowledge the likeliest of the minimal combinations is then chosen as the preferred diagnosis. Each of these approaches, however, perform poorly when the symptoms of the various diseases interact.

# 2.1.4 Summary of Symptom-Based Approaches

Work on symptom-based programs for automated diagnosis has yielded a number of powerful and useful techniques. These include (i) observation and test selection based on decision theory, with entropy as the heuristic evaluation function (ii) the use of causality as an organizing principle for diagnostic knowledge, and (iii) the formalization of diagnosis in terms of covering sets, allowing for diagnosis of multiple simultaneous diseases. The principal difficulty with symptom-based approaches is that the correctness and coverage of the knowledge base is difficult to guarantee, especially in the face of changes to the underlying system. When the available domain theory is weak, with only empirical associations between underlying diseases and observable symptoms, the symptom-based approach is reasonable and can be successful. Its limitations, however, motivate the model-based approach discussed below, which can provide better coverage and extensibility in domains where those properties are important.

# 2.2 The Model-Based Approach

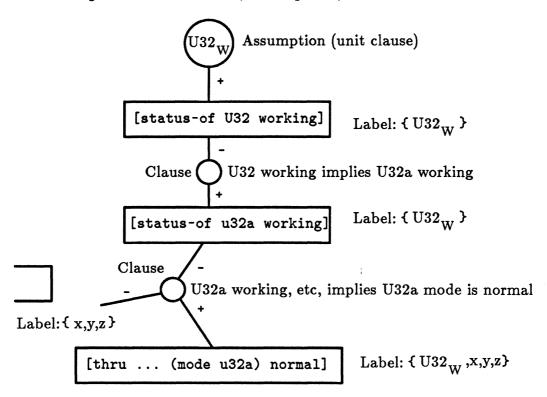

Model-based troubleshooting is a widely investigated and well established methodology. The majority of the programs that share this paradigm are for diagnosis of designed artifacts such as circuits, so the term "device" will be used interchangeably with "system," and the notion of a "disease" will be replaced by that of a "fault." The key to the model-based approach is the representation of the structure and behavior of the correctly functioning device. This representation is used to make predictions about the behavior of the real device and about the outcomes of possible observations. Discrepancies between the predicted behavior and the actual observations are

traced to sets of possibly malfunctioning components. Each set of components whose failure could explain the observations will be called a *candidate*; these candidates can be ranked according to their relative likelihood. As new discriminating observations are added some candidate will eventually dominate the others and be chosen as the final diagnosis, a set of components believed to be failing. With a hierarchic representation of structure, the isolation process can be repeated recursively on the substructure of each component believed to be faulty.

The key advantage of using knowledge about the correct behavior of components is that it dispenses with the need for storing associations between underlying faults and observed misbehaviors of the entire device. Instead, any subset of components whose predicted combined behavior disagrees with the behavior actually observed contains at least one broken component. By gathering more observations the troubleshooter can narrow down this set. Furthermore, this requires no commitment to the number of faults actually in the device, since the model can support reasoning about the interactions between any number of failing components. Finally, as noted earlier, when causal knowledge is available it can be easier to obtain than knowledge about overall associations between symptoms of failures and possible underlying faults.

It is useful to consider model-based troubleshooting in terms of four basic activities: modeling, behavior prediction, candidate generation, and discrimination. The following sections discuss each of these activities; a more complete survey appears in [Hamscher87].

# 2.2.1 Modeling

In model-based troubleshooting the notion of a "device model" is almost universally understood to mean a lumped element description, that is, the structure of the device is represented as a network of typed components and connections between them. Examples of models in various domains include:

• Circuit schematics with resistors, diodes, and so forth. This representation of analog circuits is used in INTER [deKleer76], WATSON [Brown76], SOPHIE [Brown82], IDS [Pan84], IN-ATE [Cantone83], DEDALE [Dague87], and others [Milne85].

- Circuit schematics using logic gates and higher-level digital components such as multiplexors and adders. This representation is used in HT [Davis84], DART [Genesereth84], and others [Friedman83] [AbuHanna88].

- Piping and instrumentation diagrams, which include components such as valves, potentiometers, lamps, and so forth, used in LES/LOX [Scarl85].

- Models of human physiology. Fluid models in terms of compartments, their permeable membranes, and so forth were used by ABEL [Patil81], by the system proposed in [Kuipers84], and by the Heart Failure Program [Long86]. A model of the human nervous system in terms of unidirectional neural pathways was used in LOCALIZE [First82].

The behavior of the entire device is taken to arise from the interaction of the behaviors of the individual components through the connections. Developing a particular description involves choosing a vocabulary of components and their behaviors, then representing the device as a connected network of these components. Therein lies a key advantage of model-based troubleshooting over traditional approaches: for designed artifacts, it can work directly from device models already developed for design and analysis. Model-based circuit troubleshooting, for example, can in principle work from ordinary circuit schematics and board layout information needed for design and manufacture. Therein also lie some of the deepest problems in the methodology: identifying the principles for building device models that are appropriate for model-based troubleshooting when the inherited models are inappropriate. Indeed, one of the reasons that there are relatively few projects using the model-based approach in medical domains is the scarcity of good analytic models for any substantial system.

The modeler confronts three goals simultaneously: achieving fidelity, precision, and efficiency. A model has fidelity when it does not support incorrect predictions about the device. A model has precision to the extent that the predictions it makes are strong enough to be falsifiable by observations of the actual device. A model is efficient when the work needed to make predictions using it is proportional to the benefits to be gained.

Fidelity is the primary modeling goal in troubleshooting. This is because if the model makes incorrect predictions, then discrepancies between the ac-