# CPZ-186 SINGLE BOARD CENTRAL PROCESSOR

4020 Leaverton Court • Anaheim, California 92807-1692 • (714) 630-0964 • Telex: 821375 SUPPORT UD

### TABLE OF CONTENTS

| 1. | INTRO | DDUCTION                                                  |

|----|-------|-----------------------------------------------------------|

|    |       | Technical Features2                                       |

|    | 1.2.  | Specifications                                            |

| _  |       | τ                                                         |

| 2. |       | TIONAL DESCRIPTION                                        |

|    | 2.1.  | Input/Output Structure                                    |

|    |       | 2.1.1. Off-Board I/O Controllers                          |

|    | •     | 2.1.1.1. Serial I/O Port Control                          |

|    |       | 2.1.1.2. Serial I/O Controller                            |

|    |       | 2.1.1.3. Baud Rate Clock Generator7                       |

|    |       | 2.1.1.4. Parallel I/O Port Control Interface8             |

|    |       | 2.1.1.5. Floppy Disk Controller (FDC)9                    |

|    |       | 2.1.2. ON-BOARD I/O CONTROLLERS                           |

|    |       | 2.1.2.2. DMA Controller                                   |

|    |       | 2.1.2.3. DMA Channel Assignments10                        |

|    |       | 2.1.2.4. Interrupt Control Logic                          |

|    |       | 2.1.2.5. Interrupt Controller/Select                      |

|    |       | 2.1.2.6. MEMORY MANAGEMENT UNIT                           |

|    | 2.2.  | 256 Kbyte/1 Megabyte Dynamic RAM/Controller14             |

|    |       | 2K/4K/8K EPROM                                            |

|    | 2.4.  | I/O Chip Selects                                          |

|    | 2.5.  |                                                           |

|    | 2.6.  | CLOCK GENERATOR                                           |

|    | 2.7.  | S-100 BUS CONTROL SIGNALS GENERATOR16                     |

|    | 2.8.  | S-100 Bus Interface17                                     |

|    |       | 2.8.1. Address Bus                                        |

|    |       | 2.8.2. Input Data Bus                                     |

|    |       | 2.8.3. Output Data Bus                                    |

|    |       | 2.8.4. Status Bus                                         |

|    |       | 2.8.4.1. SMEMR (Memory Read)                              |

|    |       | 2.8.4.2. sM1 (Opcode Fetch)                               |

|    |       | 2.8.4.3. sINP (Input)                                     |

|    |       | 2.8.4.4. sOUT (Output)20<br>2.8.4.5. sWO* (Write Cycle)20 |

|    |       | 2.8.4.6. SINTA (Interrupt Acknowledge)20                  |

|    |       | 2.8.4.7. sHLTA (Halt Acknowledge)20                       |

|    |       | 2.8.4.8. sXTRQ* (16-Bit Data Transfer)20                  |

|    |       | 2.8.5. Control Input Bus                                  |

|    |       | 2.8.5.1. RDY (Slave Ready)                                |

|    |       | 2.8.5.2. XRDY (Special Ready)                             |

|    |       | 2.8.5.3. INT* (Maskable Int. Reg.)                        |

|    | 21    | 2.8.5.4. NMI* (Non-maskable Int. Req.)22                  |

|    |       | 2.8.5.5. HOLD* (DMA Request)                              |

|    |       | 2.8.5.6. SIXTN* (Sixteen Acknowledge)22                   |

|    |       | 2.8.6. Control Output Bus                                 |

|    |       | 2.8.6.1. pSYNC (Cycle Start)                              |

|    |       | 2.8.6.2. pSTVAL* (Status Valid)23                         |

|    |       | 2.8.6.3. pDBIN (Read Strobe)                              |

|    |       | 2.8.6.4. pWR* (Write Strobe)                              |

|    |       | 2.8.6.5. pHLDA (Hold Acknowledge)                         |

|    |       | 2.8.7. DMA Control Bus                                    |

|    |       | 2.8.8. Vector Interrupt Bus                               |

|    |       | 2.8.10.<br>2.8.11.<br>2.8.12.<br>2.8.13.<br>2.8.14.<br>2.8.15.<br>2.8.16. | Utility E<br>O (Syste<br>CLOCK (C<br>POC* (PC<br>SLAVE CI<br>ERROR* (<br>PWRFAIL*<br>System F<br>MANUFACT<br>2.8.17.1<br>2.8.17.2 | m Clock).<br>wer-on<br>R* (Sl:<br>Error)<br>(Power<br>WRER S:<br>• PCHA<br>• RFSH | k)<br>Clean<br>ave Cl<br>r Fai<br>PECIF<br>IN (In<br>* (Re: | r)<br>Lear).<br>Lure).<br>LED LI<br>nterru<br>fresh) | NES.      | iori            | •••••••••••••••••••••••••••••••••••••• |                       |

|----|-------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|-----------|-----------------|----------------------------------------|-----------------------|

| 3. | OPER/ | ATING IN                                                                  | STRUCTION                                                                                                                         | S                                                                                 |                                                             |                                                      |           |                 |                                        |                       |

|    | 3.1.  | Hardwar                                                                   | e Setup I                                                                                                                         | nstruc                                                                            | tions                                                       |                                                      |           |                 |                                        | 28                    |

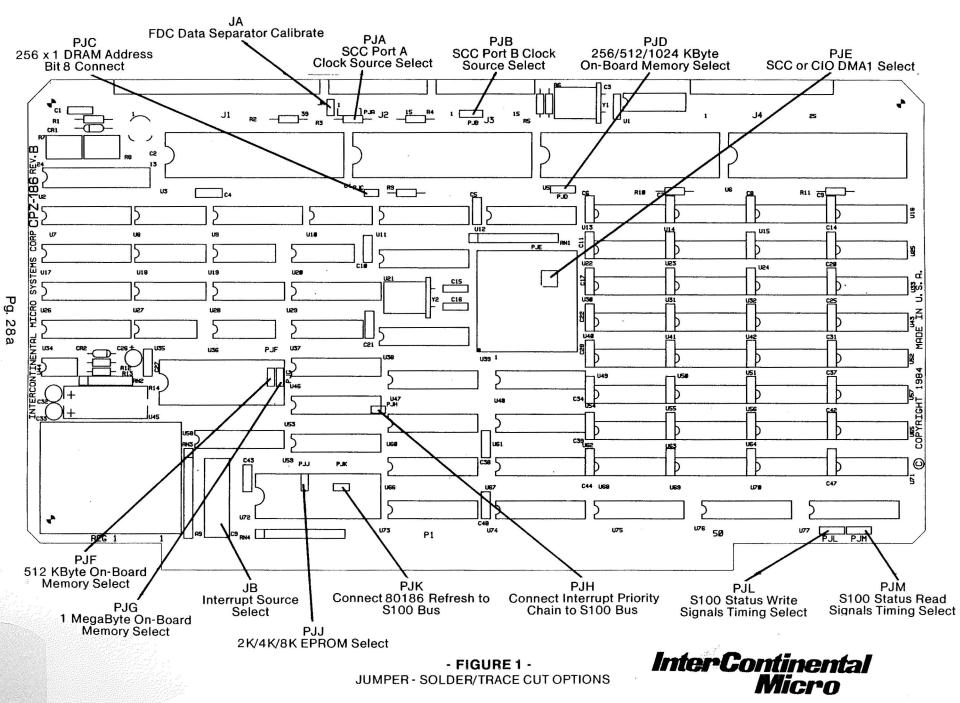

|    |       | 3.1.1.                                                                    | JUMPER OF                                                                                                                         | TIONS.                                                                            |                                                             |                                                      |           |                 |                                        | 29                    |

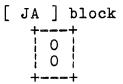

|    |       | -                                                                         | 3.1.1.1.                                                                                                                          | JA – FI                                                                           | DC Da                                                       | ta Sep                                               | arato     | or Ca           | librat                                 | e29                   |

|    |       |                                                                           | 3.1.1.2.                                                                                                                          | JB - I                                                                            | nterri                                                      | ipt So                                               | urce      | Sele            | ct                                     | 29                    |

|    |       | 3.1.2.                                                                    | SOLDER/TR                                                                                                                         |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.1.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.2.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.3.<br>3.1.2.4.                                                                                                              |                                                                                   | 290 X                                                       | 1 DRA                                                |           | able.           | <b></b>                                | •••••))               |

|    |       |                                                                           | 3.1.2.5.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.6.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.7.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.8.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.2.9.                                                                                                                          | PJJ – S                                                                           | 2K/4K                                                       | /8ř ef                                               | ROM S     | Selec           | t                                      |                       |

|    |       |                                                                           | 3.1.2.10.                                                                                                                         | PJK -                                                                             | Conne                                                       | ect 80                                               | 186 E     | Refre           | sh to                                  | Bus .38               |

|    |       |                                                                           | 3.1.2.11.                                                                                                                         | PJL -                                                                             | Write                                                       | e Sign                                               | ial Ti    | iming           | • • • • •                              |                       |

|    |       |                                                                           | 3.1.2.12.                                                                                                                         | PJM -                                                                             | Read                                                        | Signa                                                | l Tin     | ning            |                                        | ••••39                |

|    |       | 3.1.3.                                                                    | FLOPPY DF                                                                                                                         |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    | •     |                                                                           | 3.1.3.1.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.3.2.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.3.3.<br>3.1.3.4.                                                                                                              |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.3.5.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 3.1.3.6                                                                                                                           | MTTSIIR                                                                           |                                                             | )-∠⊵••<br>¥2806-                                     | 63 (1     | ат.р.<br>Тат.р. | ·····                                  | 1 43                  |

|    |       |                                                                           | 3.1.3.6.<br>3.1.3.7.                                                                                                              | MITSUB                                                                            | ISHI 2                                                      | 2894-6                                               | 3 (FI     | JLL H           | EIGHT)                                 |                       |

|    |       |                                                                           | 3.1.3.8.                                                                                                                          | SEIMEN                                                                            | S FDD                                                       | 100-80                                               |           |                 |                                        | ••••44                |

|    |       |                                                                           | 3.1.3.9.                                                                                                                          | TANDON                                                                            | TM100                                                       | )-2 (5                                               | 5 1/4'    | dri             | ve)                                    | ••••45                |

| _  |       |                                                                           |                                                                                                                                   |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

| 4. |       |                                                                           | BOARD USE                                                                                                                         |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    | 4.1.  | INTRODU                                                                   |                                                                                                                                   | ••••••                                                                            | • • • • •                                                   | • • • • • •                                          |           |                 | • • • • • •                            | ••••40                |

|    | 4•2•  | rersona<br>A 2 4                                                          | ality Boar<br>Descripti                                                                                                           | or inte                                                                           | rconn                                                       | ection                                               | I INST    | truct           | lons                                   | •••• <b>4</b> 0<br>53 |

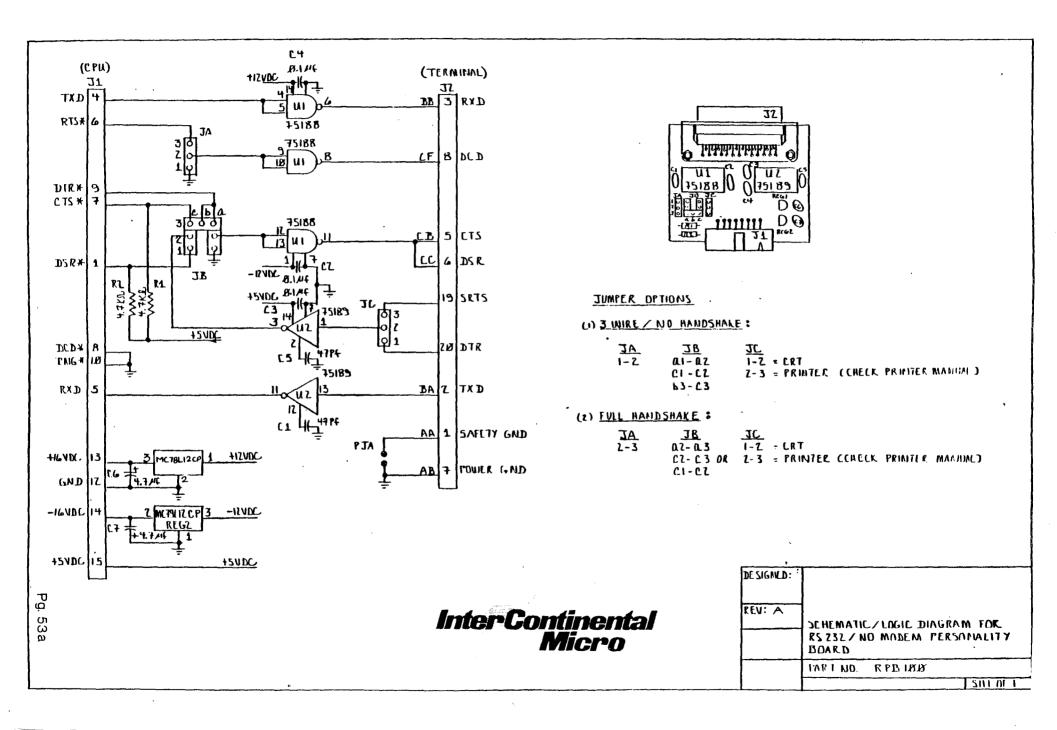

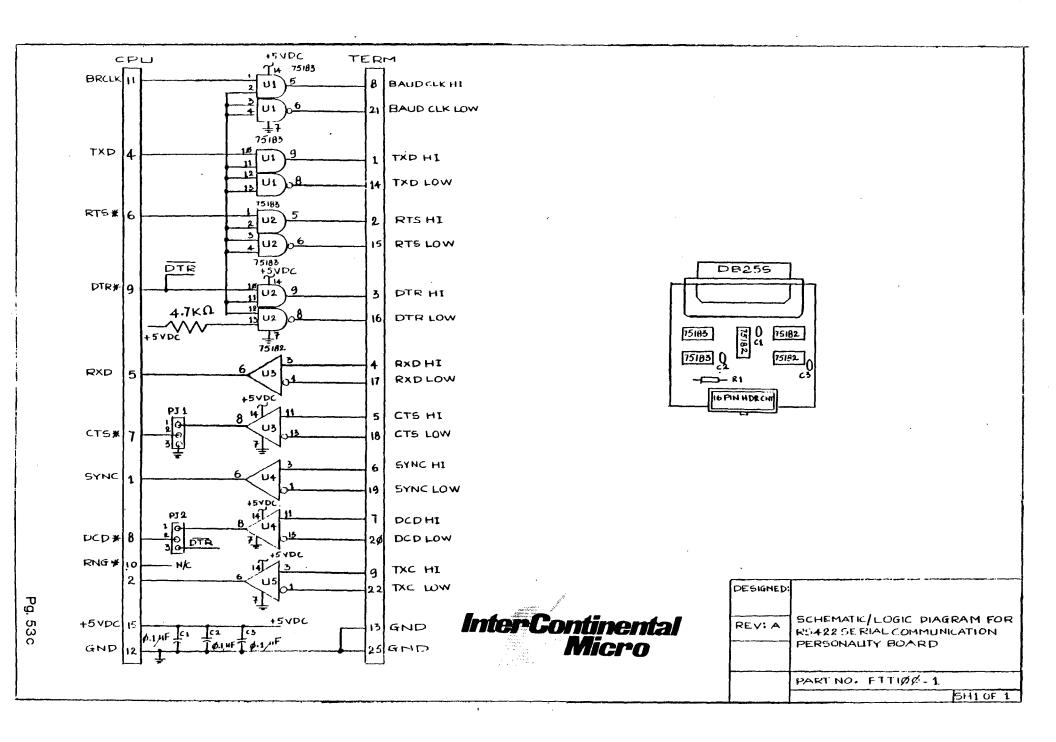

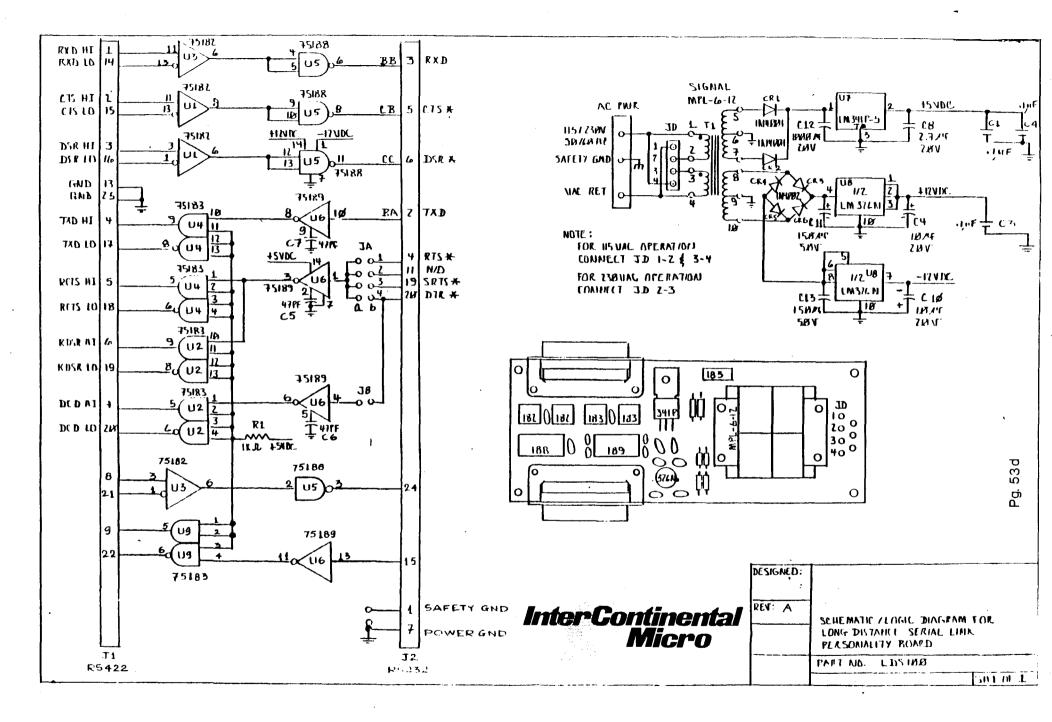

|    |       | 4•2•1•                                                                    | 4.2.1.1.                                                                                                                          | BS232/                                                                            |                                                             | •••••                                                | • • • • • |                 | • • • • • •                            | ••••• <u>5</u> 7      |

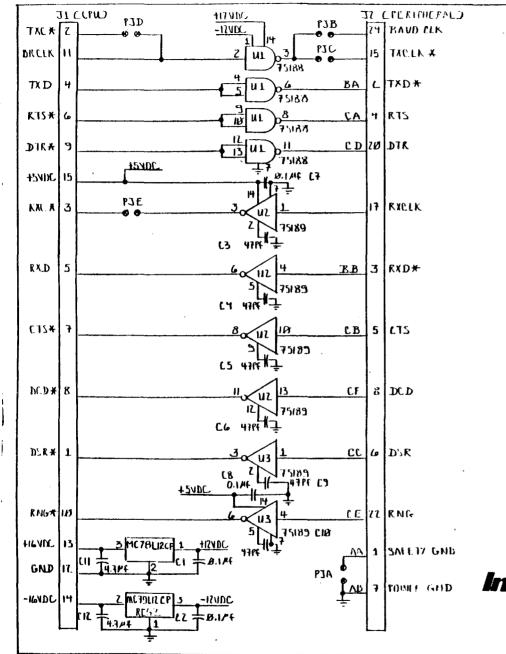

|    |       |                                                                           | 4.2.1.2.                                                                                                                          | RS232/                                                                            | FUT.T. I                                                    | MODEM -                                              |           |                 |                                        | 59                    |

|    |       |                                                                           | 4.2.1.3.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 4.2.1.4.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 4.2.1.5.                                                                                                                          | FLOPPY                                                                            | DISK                                                        | CONTR                                                | OLLER     | 2               |                                        | 70                    |

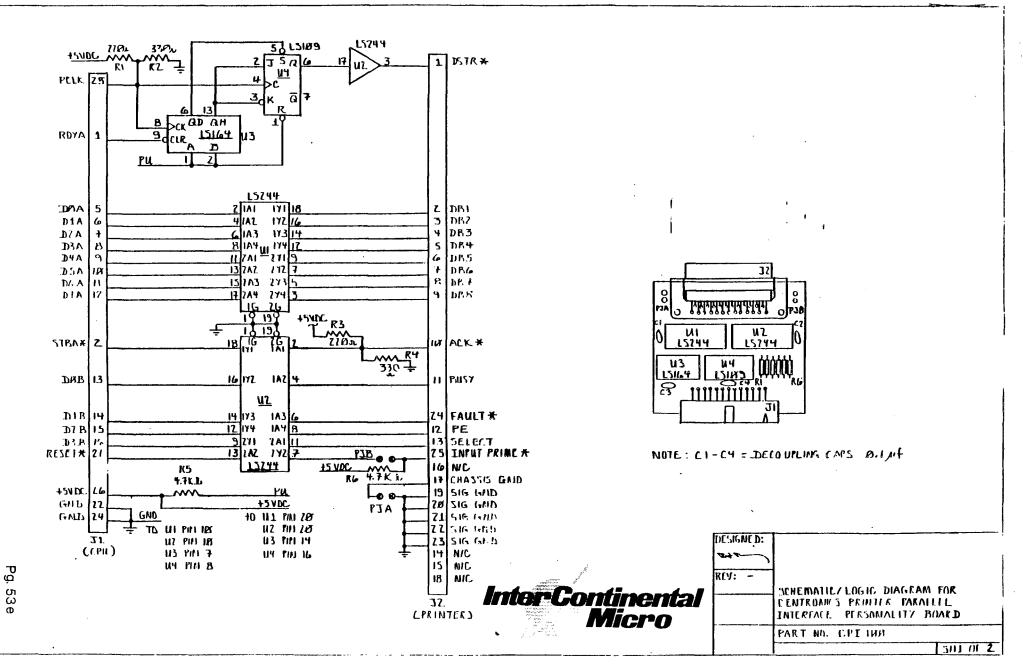

|    |       |                                                                           | 4.2.1.6.                                                                                                                          | CENTRO                                                                            | NICS 3                                                      | PRINTE                                               | ER        |                 |                                        | 83                    |

|    |       |                                                                           | 4.2.1.7.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 4.2.1.8.                                                                                                                          |                                                                                   |                                                             |                                                      |           |                 |                                        |                       |

|    |       |                                                                           | 4.2.1.9.                                                                                                                          | PERSON                                                                            | ALITY                                                       | BOARI                                                | ) – Cl    | LOCK/           | CALEND                                 | AR99                  |

| 5.  | CRT TERMINAL SET-UP INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                           | 102                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 6.  | <pre>HARD DISK COMPATABILITY GUIDE.<br/>6.1. PARALLEL PORT INTERFACE.<br/>6.2. S100 BUS.<br/>6.2.1. MD1010 &amp; MD1013 JUMPER OPTIONS.<br/>6.2.2. MD1013/1016 Drive List.</pre>                                                                                                                                                                                                                                           | .103<br>.104                                                 |

| 7.  | SOFTWARE SECTION                                                                                                                                                                                                                                                                                                                                                                                                           | 106                                                          |

| 8.  | CPZ-186 MASTER MULTI-USER SYSTEM CHANGES.<br>8.1. Software Modifications.<br>8.2. Hardware Modifications.<br>8.3. 16 Bit Slaves.<br>8.3.1. One Megabyte 16 Bit Slaves.<br>8.3.2. Mixing 8 And 16 Bit Slaves.<br>8.4. Automatic Logon.<br>8.5. Batch Processing.<br>8.5.1. Master Batching.                                                                                                                                 | 107<br>109<br>111<br>113<br>115<br>117<br>120                |

| 9.  | I/O Port Address Assignments. 9.1. Serial Port A and B Assignments. 9.2. Floppy Disk Controller Assignment. 9.3. Parallel Port A and B Assignment. 9.4. Interrupt Controller Assignments. 9.5. Control Registers. 9.6. Memory Management Registers. 9.7. Control Register Bit Assignments. 9.7.1. On-board Functions Register (Port 308 Hex). 9.7.2. FDC Wait Register (Port 308 Hex). 9.7.3. S-100 Bus I/O Address Space. | .124<br>.124<br>.124<br>.124<br>.124<br>.124<br>.125<br>.125 |

| 10. | WARRANTY                                                                                                                                                                                                                                                                                                                                                                                                                   | .126                                                         |

| 11. | APPENDIX A                                                                                                                                                                                                                                                                                                                                                                                                                 | .127<br>.127<br>.127<br>.127<br>.127<br>.127<br>.127         |

## LIST OF TABLES

| 2-2:         | I/O Port Address Assignments               |

|--------------|--------------------------------------------|

| 4-2:<br>4-3: | Connector J1 Pin Assignments               |

| 7-1:         | File extensions used in 16-bit TurboDOS106 |

| 8-1:         | CPZ-186 Memory Usage Map109                |

####

All information contained herein is proprietary to Intercontinental Micro Systems Incorporated and may not be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Intercontinental Micro Systems, Corp. 4015 Leaverton Court, Anaheim, California 92807.

#### DISCLAIMER

Intercontinental Micro Systems Corp. makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Intercontinental Micro Systems Corp. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Intercontinental Micro Systems Corp. to notify any person of such revision or changes.

#### 1. INTRODUCTION

The INTERCONTINENTAL MICRO SYSTEMS CORP. (ICM) CPZ-186 single board central processor (SBCP) is a 80186 (tm) based computer board designed to meet or exceed the IEEE S-100 Bus specification. This fourth generation computer incorporates all the features necessary for a complete, stand alone CP/M (tm) or MSDOS (tm) system and is perfect for use in multi-processor or multi-user /multi-tasking architectures utilizing operating systems such as TurboDOS (tm), MP/M (tm), OASIS (tm), ZENIX (tm), UNIX (tm) and CP/NET (tm).

Features such as an independent interrupt structure, Direct Memory Access, a 4 Megabyte Memory Management Unit and a linearly addressable on-board 256Kbyte or 1 Megabyte memory coupled with I/O devices such as a floppy disk controller which controls 5 1/4" or 8" drives simultaneously, a 2-port serial controller and a 2 1/2-port parallel controller provides the user computing power on a single board heretofore unmatched in the S-100 Bus industry. Other features incorporated are listed as follows:

#### 1.1. Technical Features

- []IEEE 696.1/D2 S-100 compliance. The CPZ-186 will interface with most IEEE S-100 Bus products on the market.

- [] RS232 Communications and Floppy Controller Personality Boards included.

- [] 8 MHz 80186 Operation

- [] Floppy Disk Controller (FDC) with on-chip data separator. Single or double density. Single or double sided simultaneous 8" and 5-1/4" in any combination. The choice is yours, up to 4 drives.

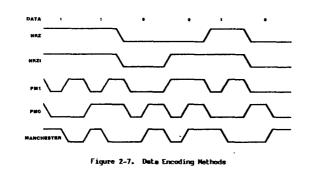

- [] Two synchronous (SCC) or asynchronous (ASCC) serial I/O channels. Both channels are programmable in interrupt or programmable I/O mode. One channel can be programmed in Direct Memory Access (DMA), interrupt, or programmable I/O mode.

- [] Two parallel I/O channels (CIO). Both channels are programmable in interrupt or programmable I/O mode. One channel can be programmed in Direct Memory Access (DMA), interrupt, or programmable I/O mode.

- [] Two channel on-chip DMA controller

- []256K Bytes of on-board RAM, expandable to 512KB or 1 Megabyte.

- [] Memory Management Unit (MMU). Addresses up to 4 Megabytes of system memory.

[] Eighteen vectored priority interrupts.

- []Provisions for 2K, 4K or 8K of on-board EPROM. A boot up function in a 4K 2732 EPROM is supplied.

- [] Software selectable baud rates. Eliminates costly, complicated hardware modifications to change baud rates. Up to 1 MegaBAUD in synchronous mode.

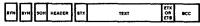

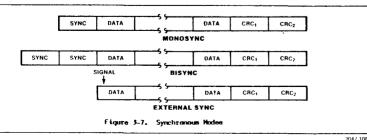

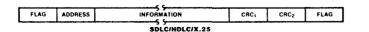

- [] IBM Bisync, HDLC, SDLC and other protocols. All are handled through a Z8530 SCC chip. Permits communication with micro's, mini's or mainframes.

- [] TurboDOStm operating system available.

- [] DMA to extended memory.

#### 1.2. Specifications

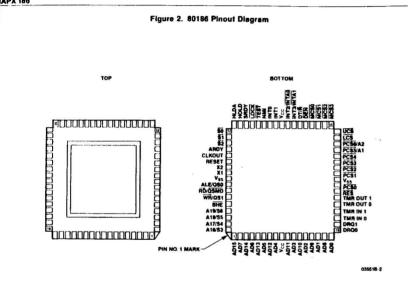

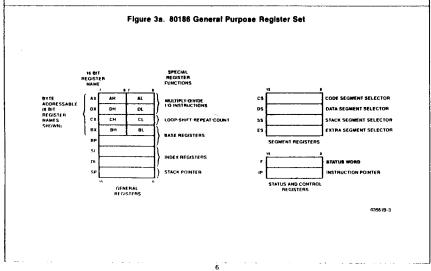

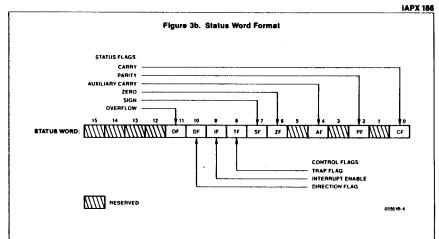

MICROPROCESSOR Clock Rate ..... 8 MHz 80186

BUS INTERFACE...IEEE 696.1/D2 S100

DYNAMIC RAM MEMORY Capacity.....256K Bytes (64K x 1 DRAM's) or 51.2KB or 1 MegaByte (256K x 1 DRAM's) Wait States...None

SERIAL I/O CHANNELS

Synchronous Operation Baud Rate.....Up to 921.6K BAUD Data Transfer...DMA, interrupt or Programmed I/O Asynchronous Operation Baud Rate.....Up to 921.6K BAUD Clock Rate .....1, 16, 32, or 64 times Baud Rate Bits/Character...5, 6, 7 or 8 Stop Bits.....1, 1-1/2 or 2 Parity.....Odd, Even or None Data Transfer....DMA, Interrupt or Programmed I/O I/O Interface....Through Personality Boards

PARALLEL I/O CHANNELS

DATA RATE......Up to 500 KBytes/Sec Channel A Data Transfer...Interrupt, DMA or Programmed I/O Channel B Data Transfer...Interrupt or Programmed I/O Interface Signals......16 DataLines Plus 4 Handshaking Lines I/O Interface.....Through Personality Boards

FLOPPY DISK CONTROLLER Data Rate/8-inch Single-Density.....250,000 Bits/Sec Data Rate/8-inch Double-Density......500,000 Bits/Sec Data Rate/5-1/4-inch Single-Density...125,000 Bits/Sec Data Rate/5-1/4-inch Double-Density...250,000 Bits/Sec Format.....IBM 3740 or 512 x 16 Sectors Data Transfer.....DMA, Interrupt or Programmed I/O I/O Interface.....Through Personality Boards INTERRUPT CONTROL Number of Channels....18 Priority.....Rotating or Fixed Interrupt Mode.....Master Cascade REAL-TIME CLOCK Operation....Software Polled or Interrupt Driven DIRECT MEMORY ACCESS CONTROLLER Channel O....Floppy Disk Controller Channel 1....Channel A of ASCC Controller or Channel A of CIO Controller Memory-to-Memory utilizes both Channel O and 1 DIRECT EXTERNAL MEMORY TRANSFERS To/From ASCC (SCC), CIO, FDC or Memory EPROM Wait States...Three Function.....Boot up POWER REQUIREMENTS Voltages...+8 VDC @ 3.0A (max) +16 VDC @ 0.2A (max) -16 VDC @ 0.2A (max) OPERATING ENVIRONMENT Temperature...... to 45 Degrees Celsius Relative Humidity...0 to 95% CONSTRUCTION Circuit Board...Four Layer Glass Epoxy, Soldermask over copper All IC's in sockets Connectors.....Shrouded for Protection TESTING.....Completely tested and 24 hour burn-in WARRANTY..... One Year Warranty (Parts and Labor)

## Announcing! Intercontinental Micro Systems' **CPZ-186 16-Bit Single Board Computer - Master Processor**

#### **TECHNICAL FEATURES**

- □ IEEE 696.1/D2 S-100 compliance. The CPZ-186 will interface with most IEEE S-100 Bus products on the market.

- □ RS232 Communications and floppy controller Personality Boards included.

- BMHz 80186 Operation

- Broppy Disk Controller (FDC) with on-chip data separator. Single or double density. Simultaneous 8" and 51/4" in any combination. The choice is yours, up to 4 drives.

- Two synchronous (SCC) or asynchronous (ASCC) serial I/O channels. One channel can be programmed in Direct Memory Access (DMA), interrupt, or programmable I/O mode.

- Two parallel I/O channels (CIO). Both channels are programmable in interrupt or programmable I/O mode.

- Two channel on-chip DMA controller.

- 256K Bytes of on-board RAM, expandable to 512KB or 1 Megabyte.

- Memory Management Unit (MMA). Addresses up to 4 megabytes of system memory.

- Eighteen vectored priority interrupts.

- Provisions for 2K, 4K or 8K of on-board EPROM. A boot up function in a 4K 2732 EPROM is supplied

- Software selectable baud rates. Eliminates costly, complicated hardware modifications to change baud rates. Up to 1 MegaBAUD in synchronous mode.

- □ IBM Bisync, HDLC, SDLC and other protocols. All are handled through a Z8530 SCC chip. Permits communication with micro's, mini's or mainframes.

- □ TurboDOS<sup>™</sup> operating system available.

- DMA to extended memory.

## **Specifications**

#### MICROPROCESSOR

- BUS INTERFACE..... IEEE 696.1/D2 S100

#### DYNAMIC RAN MEMORY

256 K Bytes (64 K x 1 DRAM's) or Capacity 512KB or 1 MegaByte (256K x 1 DRAM's) Wait States. ..... None

#### SERIAL I/O CHANNELS

Synchronous Operation Baud Rate ..... UP to 921.6K BAUD Date Transfer. ..... DMA, interrupt or Programmed I/O Asynchronous Operation Baud Rate. . . . . . . . . . . Up to 921.6K BAUD

| GIOCK Rate     | I, IO, 32, 01 64 times       |

|----------------|------------------------------|

| Baud Rate      |                              |

| Bits/Character |                              |

| Stop Bits      |                              |

| Parity.        | Odd, Even or None            |

|                | DMA. Interrupt or            |

| Programmed VO  |                              |

| I/O Interface  | . Through Personality Boards |

PARALLEL I/O CHANNELS

- DATA RATE ..... Up to 500 KBytes/Sec Channel A Data Transfer. . . . . . . . . . Interrupt or Programmed I/O

- Channel B Data Transfer. ..... Interrupt or Programmed I/O

Interface Signals ..... 16 DataLines Plus 4 Handshaking Lines

VO Interface ..... Through Personality Boards FLOPPY DISK CONTROLLER

#### Data Rate/8-inch Single-Density

| Data matero-men Single-Density     |

|------------------------------------|

| 250.000 Bits/Sec                   |

|                                    |

| Data Rate/8-inch Double-Density    |

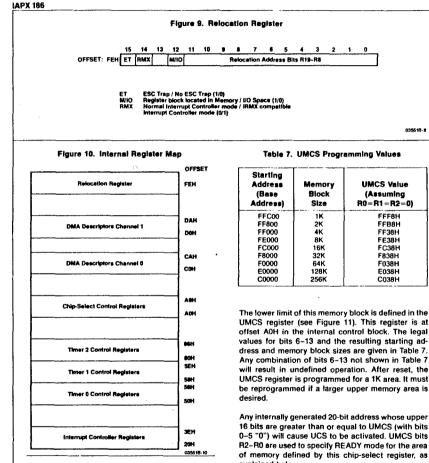

| 500.000 Bits/ Sec                  |

|                                    |

| Data Rate/514-inch Single Density  |

| 125.000 Bits/Sec                   |

| Data Rate/51/4-inch Double-Density |

|                                    |

| 250,000 Bits/ Sec                  |

| Format                             |

|                                    |

| Data Transfer                      |

Programmed I/O

#### REAL-TIME CLOCK Operation..... Software Polled or Interrupt Driven

INTERRUPT CONTROL

DIRECT MEMORY ACCESS CONTROLLER Channel O ..... Floppy Disk Controller Channel 1 ..... Channel A of ASCC Controller or Channel A of CIO Controller Memory-to-Memory utilizes both Channel 0 and 1 **DIRECT EXTERNAL MEMORY TRANSFERS**

Priority..... Rotating or Fixed

Interrupt Mode. . . . . . . . . . . . . . Master Cascade

#### To/From ASCC (SCC), CIO, FDC or Memory

#### ----

| Type                     | . 2716 2K, 2732 4K (standard), |

|--------------------------|--------------------------------|

| (ypo                     | or 2764 8K                     |

| Wait States              | Three                          |

| Function                 | Boot up                        |

| POWER REQUIREMEN         | ITS                            |

|                          | +8 VDC @ 3.0A (max)            |

| •                        | +16 VDC @ 0.2A (max)           |

|                          | —16 VDC @ 0.2A (max)           |

| Power                    |                                |

| <b>OPERATING ENVIRON</b> | INENT                          |

| Temperature              | 0 to 45 Degrees Celsius        |

| Relative Humidity        | 0 to 95%                       |

#### CONSTRUCTION

| Circuit Board       | Four Layer Glass Epoxy,       |

|---------------------|-------------------------------|

| Soldermask over     | er copper                     |

| All IC's in sockets | 5                             |

| Connectors          | Shrouded for Protection       |

| TESTING             | Completely tested and 24 hour |

|                     | burn-in                       |

|                     |                               |

WARRANTY. . . . . . One Year Warranty (Parts and Labor)

VO Interface ..... Through Personality Boards

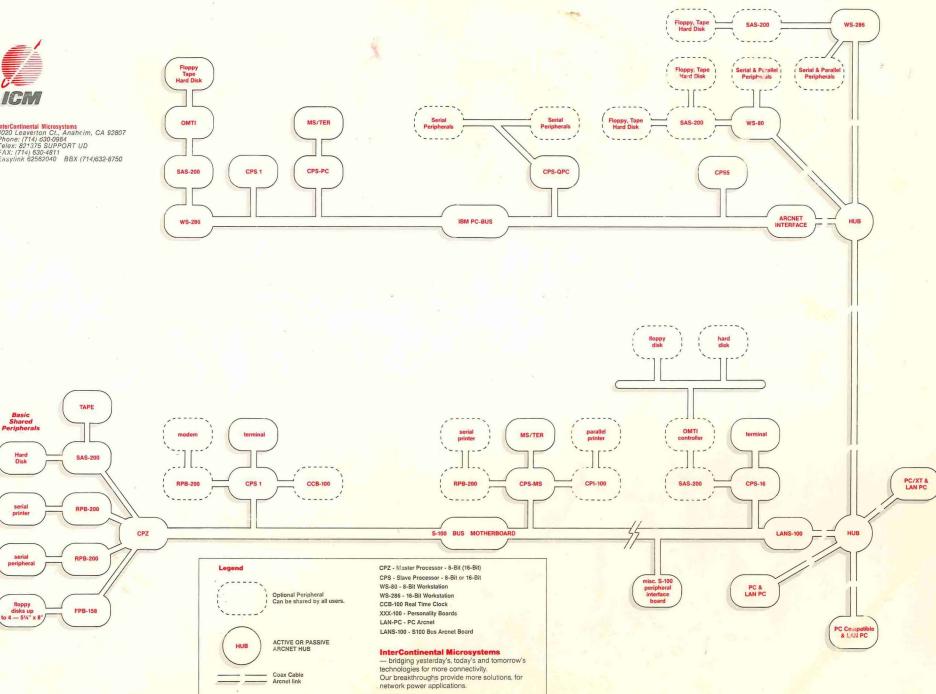

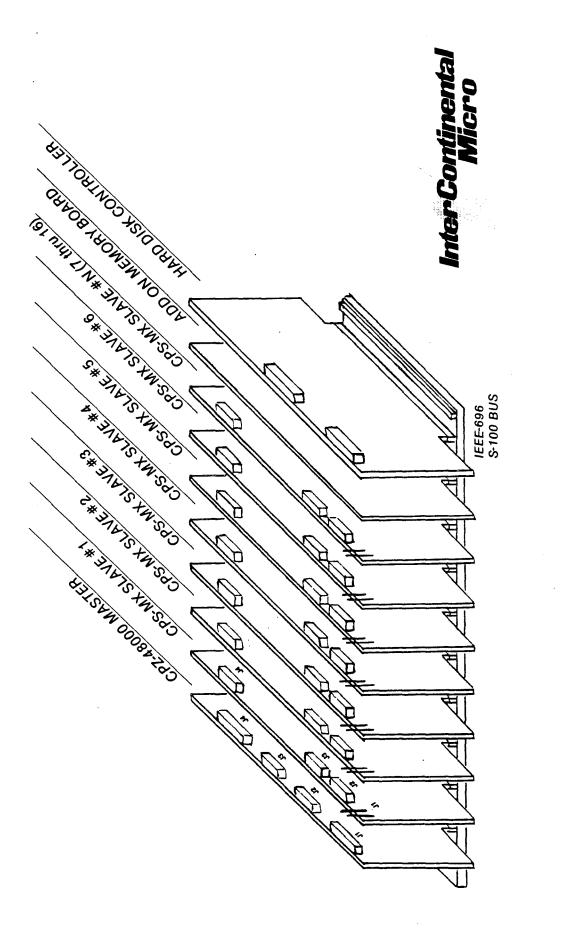

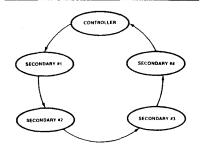

TYPICAL TURBODOS MASTER / SLAVE NETWORK

#### CPZ - Master Processor - 8-Bit (16-Bit, 4th Qtr 84)

(see back for description)

1944

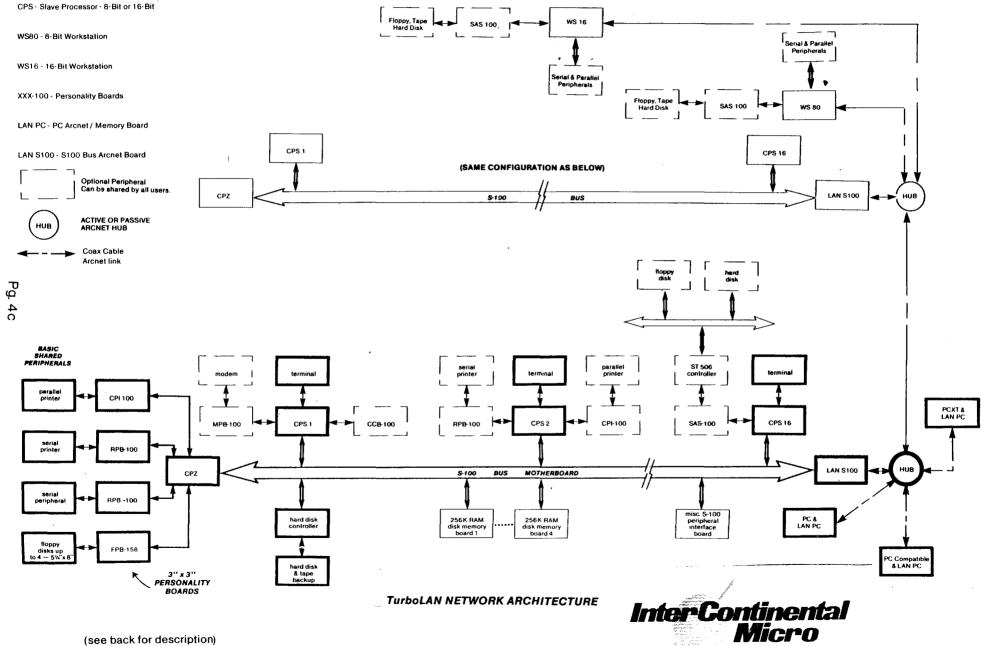

#### INTERCONTINENTAL MICRO SYSTEMS TurboLAN NETWORK ARCHITECTURE

ICM's revolutionary TurboLAN, multi-user architecture uses the sophisticated, cost effective TurboDOS Operating System. TurboLAN provides the flexibility of building multi-user systems with S-100 BUS Structured Networks and ARCnet protocol Local Area Networks. TurboLAN offers:

- (A) Ability to network S-100 Bus Systems, IBM-PC's. PC Compatibles, ICM's WS80 & WS16 Workstations, and other computers with ARCnet capability

- (B) Requires a Master Processor/File Server such as ICM's CPZ-4800X SBC

- (C) Up to 400 users per network with 255 nodes per network segment

- (D) Network self configures and efficiency increases as nodes are added

- (E) Up to 40 miles between processors (Active Hub) or 2300 FT (Passive Hub)

- (F) 2.5 MBIT/SEC data transfers across S-100 BUS, Coax cable, or twisted pair

#### **TURBODOS OPERATING SYSTEM**

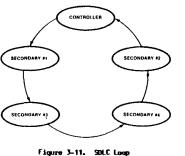

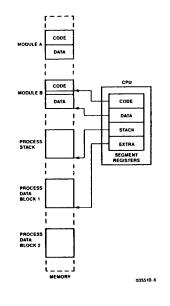

TurboDOS is a true multi-user Operating System because it was designed from its beginnings to handle multiple computers running simultaneously on one or more networks. Each user is assigned an individual PC of a terminal attached to a Single Board Computer/Processor. This PC or individual processor is called a Slave Processor in the TurboDOS architecture and acts independently of all slaves on the network. A Master Processor, also known as a File Server, controls the network by downloading the operating system to each slave. The Master also downloads system files and orchestrates the use of all common peripherals. With its modular architecture, TurboDOS can increase the number of users or add peripherals on the network with a general software command that "links and patches". TurboDOS is the most sophisticated, yet cost effective Multi-user operating system available today. It offers FEATURES such as:

- Compatible with many OS's Application Software: CP/M, CP/M-86, PC-DOS, MS-DOS. MP/M, MP/M 86, CP.M PLUS, CONCURRENT CP/M 86

- (2) Ability to mix Z-80, 8-bit; and 8086, 16-bit families of processors.

- (3) Flexibility to build Bus Structured (Tightly Coupled) Networks and Local Area (Loosely Coupled) Networks using ICM's TurboLAN.

- (4) Record and File Locking with File Sharing among multiple users

- (5) Typically 300% faster than CP/M, MP/M, Oasis or similar multi-user, single processor, multitasking OS's

- (6) 16 Logical Disk Drives per Master Processor/File Server

- (7) Up to 1000 MB per drive and 134 MB per file

- (8) 32 user areas (file libraries) on each disk

- (9) 25% to 30% more floppy disk capacity

- (10) Each user can independently STOP, RESUME of ABORT a program

- (11) Sharing of costly peripherals and disk drives

- (12) Read after Write verification of Floppy Disks and Hard Disks

- (13) Logon/Logoff & Privileged/Non-privileged Security

- (14) Background processing & Archival Back-up of files

- (15) Queueing of multiple tasks-processing or printing

- (16) Automatic Print Spooling

- (17) Each individual TurboDOSOS has 4 Circuit Drivers with 255 nodes (slaves) per circuit driver = 1020 users per OS

- (18) Multiple File Servers can be linked together with ICM's TurboLAN drivers theoretically no limit to the number of users on a single network.

#### 2. FUNCTIONAL DESCRIPTION

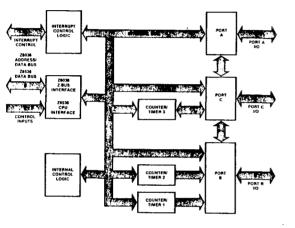

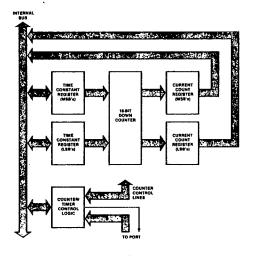

The CPZ-186 is functionally partitioned into the following major groups:

- INPUT/OUTPUT STRUCTURE

- OFF-BOARD PERIPHERAL CONTROLLERS

- SERIAL I/O PORT CONTROL

- PARALLEL I/O PORT CONTROL

- FLOPPY DISK CONTROL

- ON-BOARD PERIPHERAL CONTROLLERS

- DMA CONTROL

- INTERRUPT CONTROL

- MEMORY MANAGEMENT UNIT

- 256 KBYTE OR 1 MEGABYTE DYNAMIC RAM/LOGIC

- 2/4/8 KBYTE EPROM

- INPUT/OUTPUT CHIP SELECT LOGIC

- CPU CONTROL SIGNALS GENERATOR

- CLOCK GENERATOR

- POWER-ON CLEAR/RESET LOGIC

- S-100 BUS INTERFACE

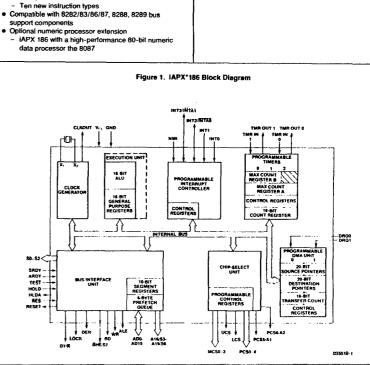

Each group is described below to give the user a clear understanding of the hardware and software setup options and to give a full appreciation of the computing power available to the user. A block diagram is included in the following page.

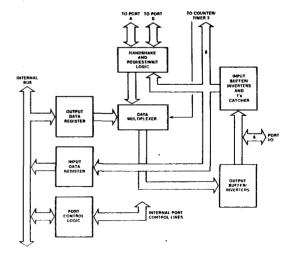

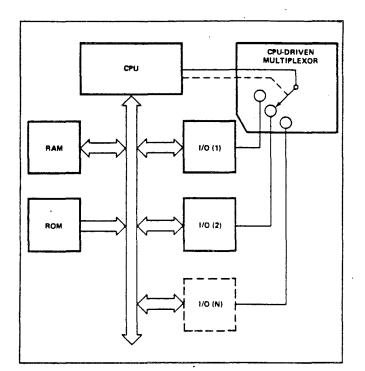

#### 2.1. Input/Output Structure

As a point of reference, an I/O device is defined as a device which, under program control of the 80186 CPU, controls a peripheral device or memory.

The I/O devices contained on the CPZ-186 consist of:

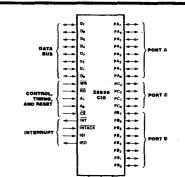

- 8531 ASCC (Serial Port Controller, SCC Optional)

- 8536 CIO (Parallel Port Controller, CIO)

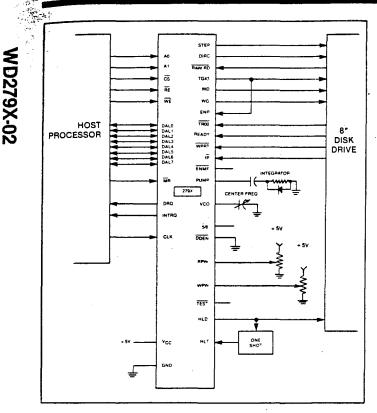

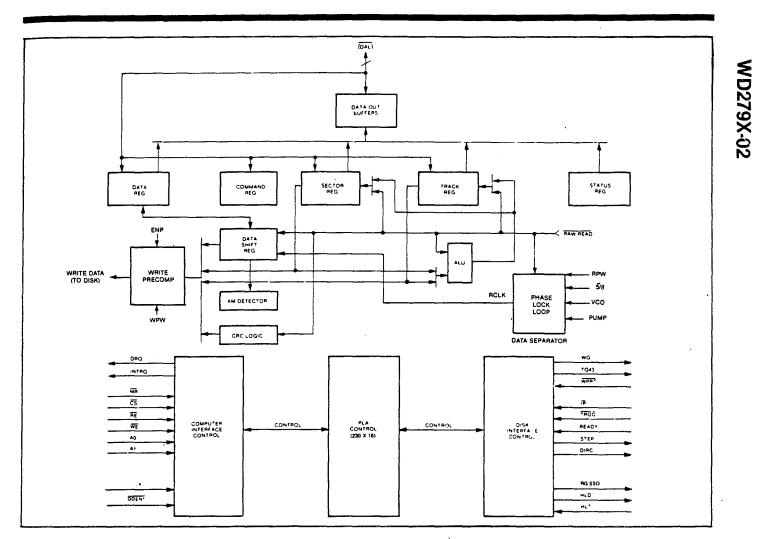

- WD2793 (Floppy Disk Controller, FDC)

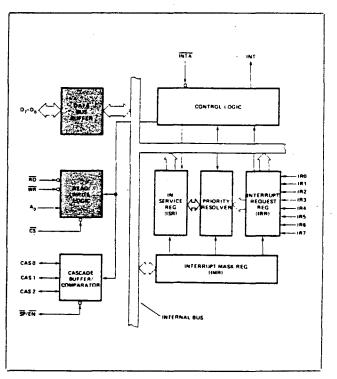

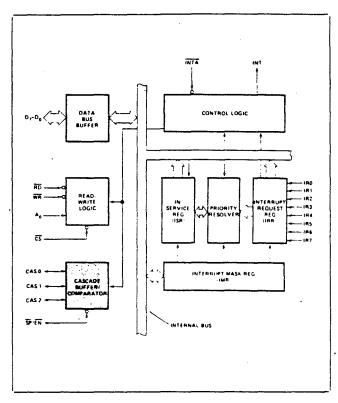

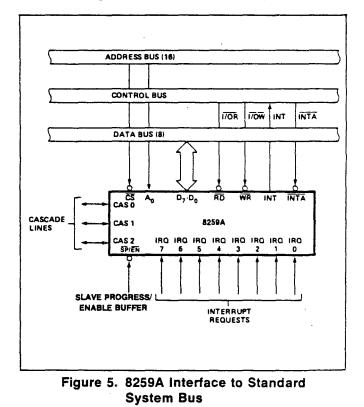

- 8259A (Universal Interrupt Controller, UIC)

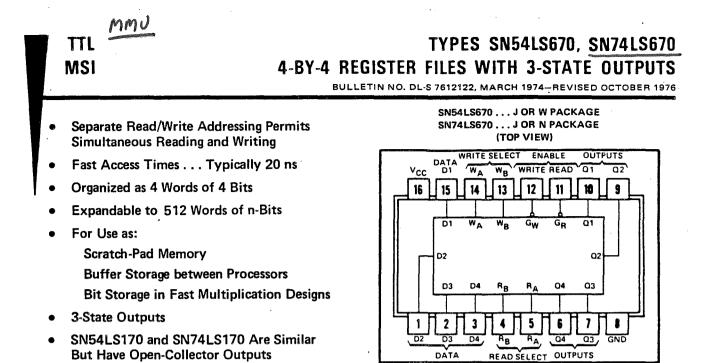

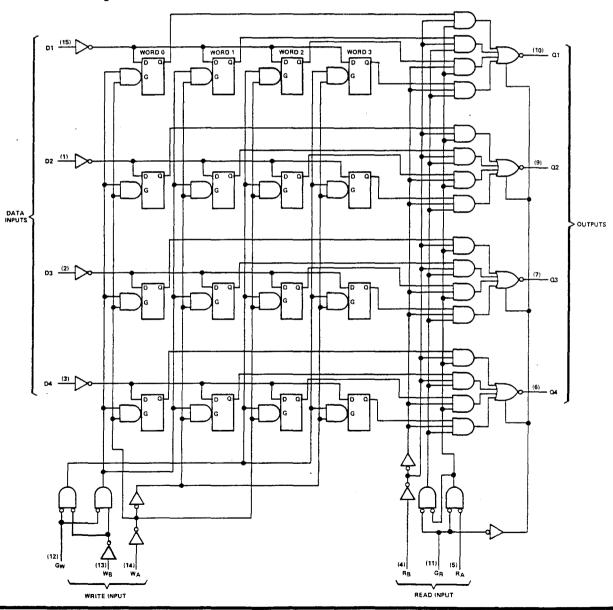

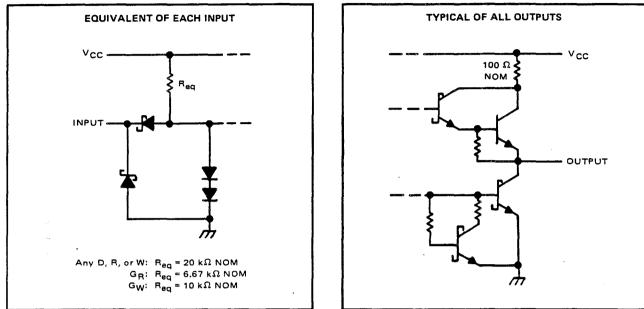

- 74LS670 (Memory Management Unit, MMU)

Of these, the first three are used to communicate with offboard peripheral devices and will be referred to as the "OFF-BOARD" peripheral I/O controllers. The remaining are "ON-BOARD" I/O controllers.

Programmed I/O, Interrupt or Direct Memory Access (DMA) is possible to/from SCC port A, CIO port A and the FDC. No DMA is possible for SCC port B or CIO port B. The 80186 HOLD input line is assigned to the S-100 Bus DMA request line to allow temporary bus masters to capture the bus for DMA transfers to off-board memory. Fixed priority selection allows arbitration between internal DMA and external DMA requests from the S-100 Bus. Fixed priority gives the S-100 Bus the highest priority and the SCC or CIO ports, the lowest. The priority level of the Floppy port versus the SCC or CIO ports may be defined under software control. Thus,

| DEVICE     | PRIORITY                |                                  |

|------------|-------------------------|----------------------------------|

|            | خت وي جو جو جو حو عو عو |                                  |

| S-100 Bus  | 1 High                  |                                  |

| FDC        | 2 or 3 (under           | • sftwr control)                 |

| SCC or CIO | 2 or 3 (under           | sftwr control)<br>sftwr control) |

The CPZ-186 I/O PortAddress assignments are as follows:

| 0001 - | FFFF | Available for External Use<br>(except as noted below) |

|--------|------|-------------------------------------------------------|

|        | 0002 | Reserved for Internal Use                             |

|        | 0004 | Reserved for Internal Use                             |

|        | 0006 | Reserved for Internal Use                             |

|        | 0008 | Reserved for Internal Use                             |

| 00F8 - | 7FFF | Unavailable                                           |

| 8000 - | FFFF | Available for External Use                            |

#### T A B L E 2-1: I/O Port Address Assignments

Please refer to the SOFTWARE Section of this manual for further explanation.

2.1.1. Off-Board I/O Controllers

The Off-Board I/O Controllers consist of the Serial I/O Port Control, Parallel I/O Port Control and the Floppy Disk Control.

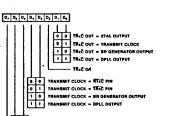

#### 2.1.1.1. Serial I/O Port Control

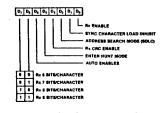

The Serial I/O Port Control consists of the Serial I/O Controller and the Baud Rate Clock Generator.

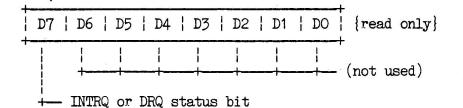

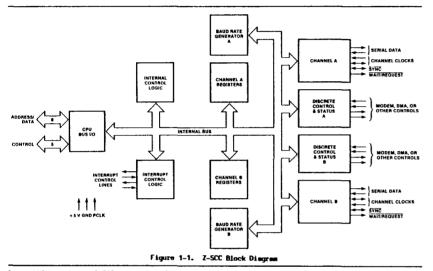

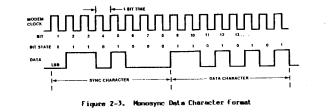

#### 2.1.1.2. Serial I/O Controller

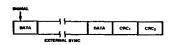

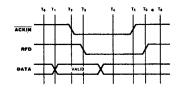

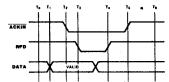

The Serial I/O (SCC) Controller is a programmable dual channel device which provides formatting for serial data communications. The channels can handle either asynchronous or synchronous data transfers to/from serial peripheral devices. The SCC operates either under programmed I/O, Interrupt Control

or DMA control. DMA is provided for Port A only. All lines necessary to handle asynchronous, synchronous, synchronous bit oriented protocols and other serial protocols are available to the user at the interface connectors. In addition, +/- 16 volt DC and +5 volt DC power are available at these connectors. The SCC may be interfaced to peripheral devices requiring differing protocols. This interface is tailored to the exact device requirements by use of a Personality Module. The interface is implemented through two 16-pin Header connectors.

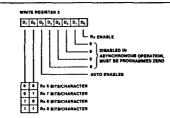

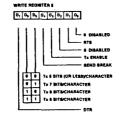

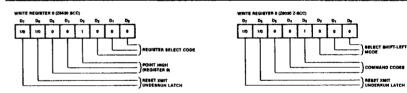

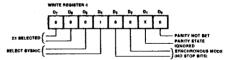

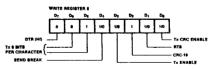

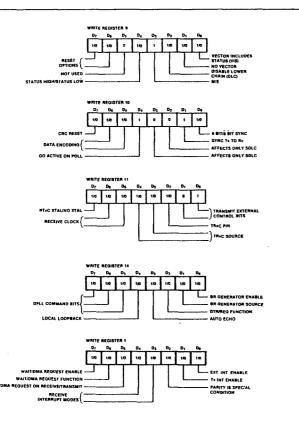

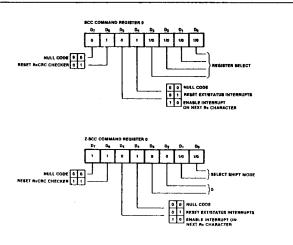

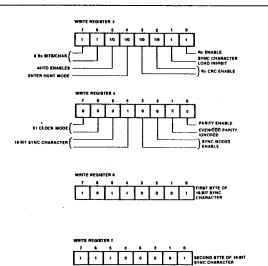

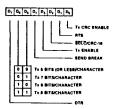

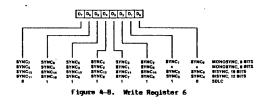

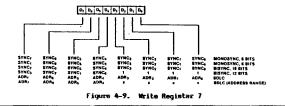

To program the ASCC or SCC the system software issues commands to initiate the mode of operation. Write registers exist for that purpose. In addition, read registers allow the programmer to read the status of each channel.

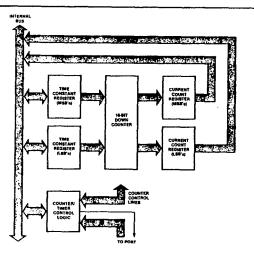

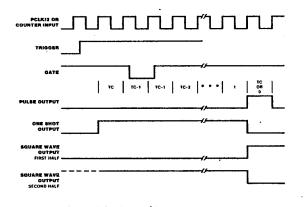

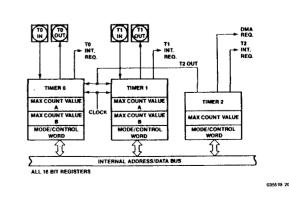

#### 2.1.1.3. Baud Rate Clock Generator

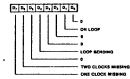

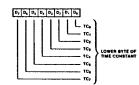

The Baud Rate Clock Generator consists of a 1.8432 Mhz clock generator and an internal 80186 interval timer. The internal timer can, under software control, generate variable clock periods which are a multiple of the base input clock.

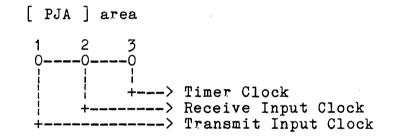

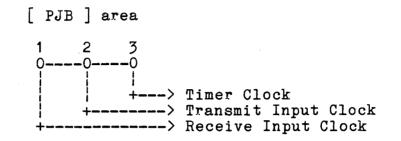

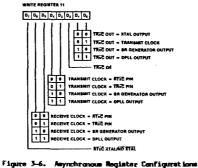

Two 80186 timer outputs are used to provide the SCC ports with a Baud Rate Clock. Channels O and 1 of the SCC are connected to these clock sources via jumper options PJA and PJB. These signals are also tied to the serial interface connectors. If clock signals are originated by the interfacing devices, the jumpers are cut appropriately. The jumpers provide for separate transmit and receive clock inputs from the interface connectors, J2 & J3, or may serve as baud rate generator outputs to the interface. This arrangement is intended to provide a clock to synchronous MODEM's via "external" clock in accordance with the EIA RS-232C standards. The modem can then return a transmit/receive clock to the serial controller. In summary, means are provided to implement serial interfaces accommodating asynchronous, synchronous, HDLC and a great number of currently defined communications protocols.

The Baud rates that can be derived from the 1.8432 Megahertz clock are listed as follows:

| Baud Rate                                                                                                              | Theoretical Frequency (16 x clock)                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50<br>75<br>110<br>134.5<br>150<br>300<br>600<br>1200<br>1800<br>2000<br>2400<br>3600<br>4800<br>7200<br>9600<br>19200 | 0.8 kiloHertz<br>1.2 kiloHertz<br>1.76 kiloHertz<br>2.152 kiloHertz<br>2.4 kiloHertz<br>4.8 kiloHertz<br>9.6 kiloHertz<br>19.2 kiloHertz<br>28.8 kiloHertz<br>38.4 kiloHertz<br>57.6 kiloHertz<br>76.8 kiloHertz<br>115.2 kiloHertz<br>307.2 kiloHertz |

|                                                                                                                        |                                                                                                                                                                                                                                                        |

#### T A B L E 2-2: Baud Rate Table

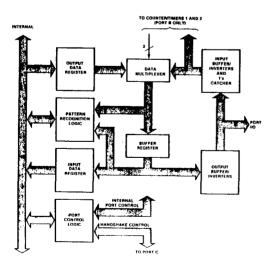

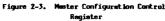

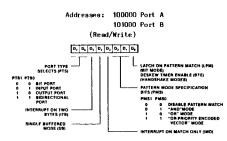

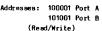

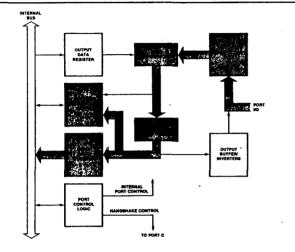

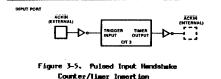

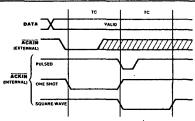

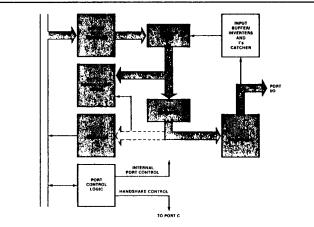

2.1.1.4. Parallel I/O Port Control Interface

The parallel I/O Port Control Interface consists of the Parallel I/O Controller (CIO). The Parallel I/O Controller is a programmable two-port LSI component, which interfaces peripheral devices to the 80186 microprocessor. The CIO provides data transfer to and from peripheral devices under programmed I/O, interrupt control or DMA control. Handshaking data transfer control lines are provided to the interface in addition to the two eight-bit data ports. The CPU reset line and the CPU clock are also connected to this interface. The CIO is flexible and may be connected to peripheral devices requiring differing protocols.

The interface is tailored to the exact device requirements by use of a "Personality Module". The Personality Module is a small external circuit board which connects to the CPZ-186 to provide the hardware drivers and receivers, logic and other circuitry as required. Refer to Personality Board Users Guide Section for a description of the parallel Personality Modules currently available.

An interrupt line is brought into the interface to give the user the capability of servicing interrupts. The interface is implemented through a 26-pin Header connector.

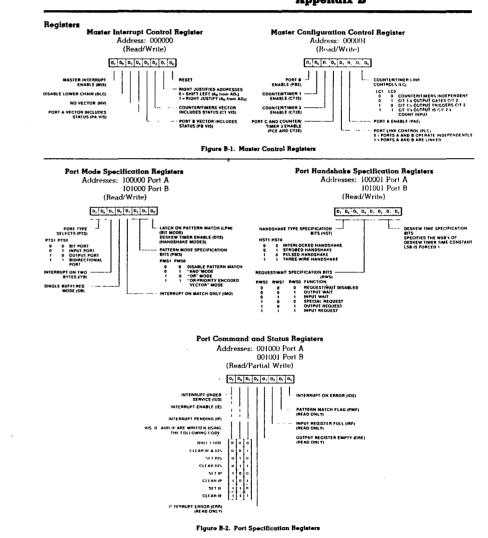

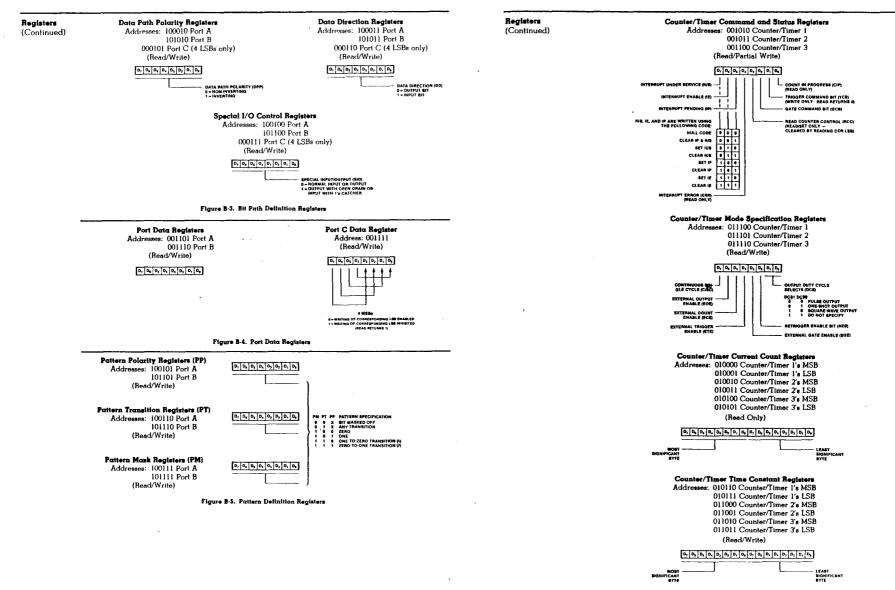

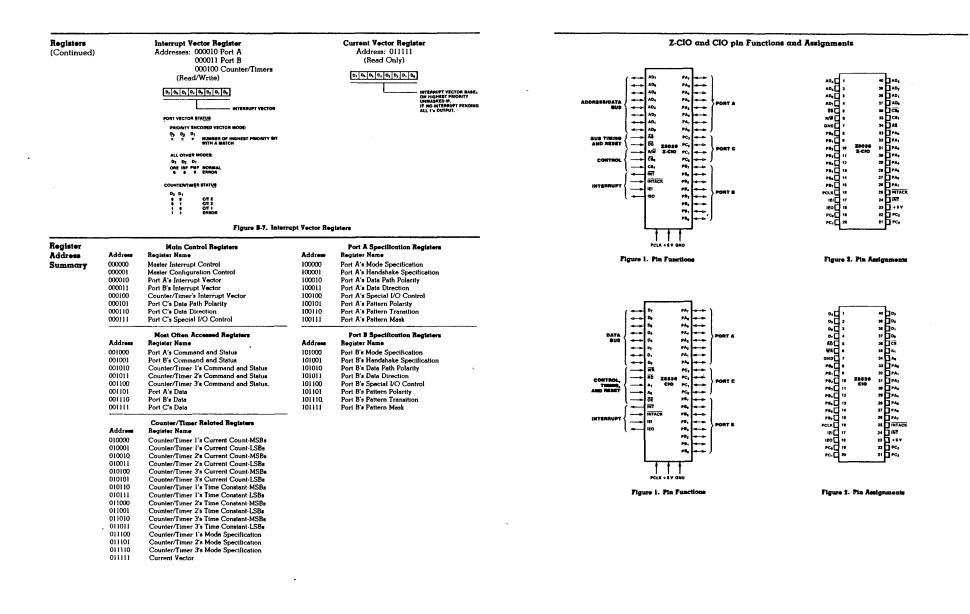

To program the CIO, the system software issues commands to initialize the mode of operation. Initialization is provided by loading the interrupt vector, mode, I/O and interrupt control registers.

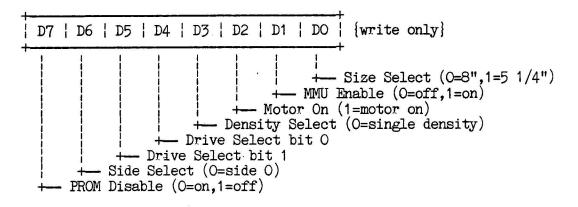

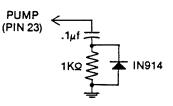

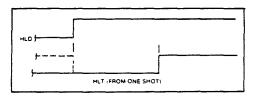

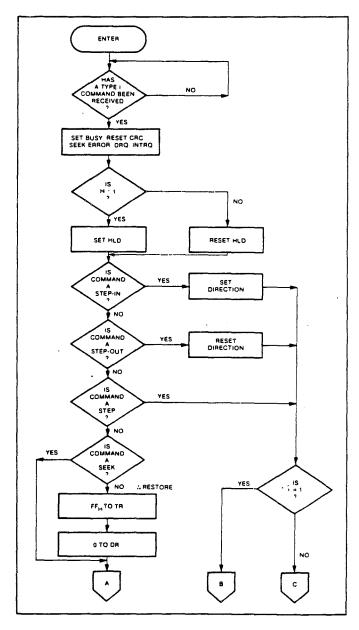

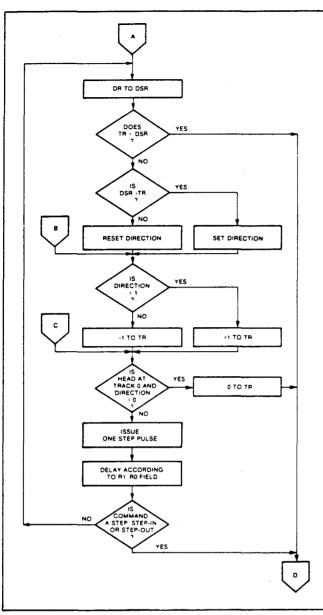

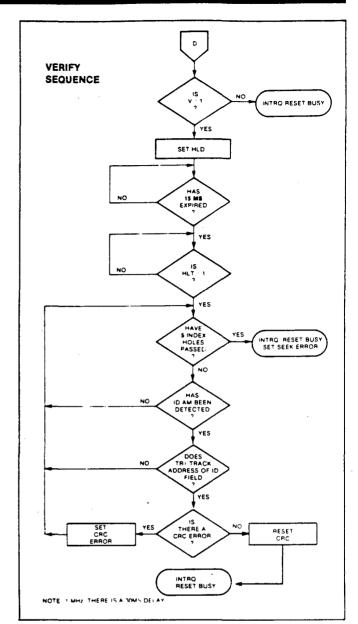

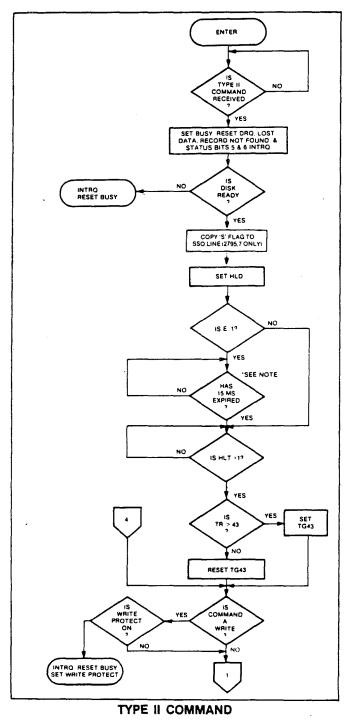

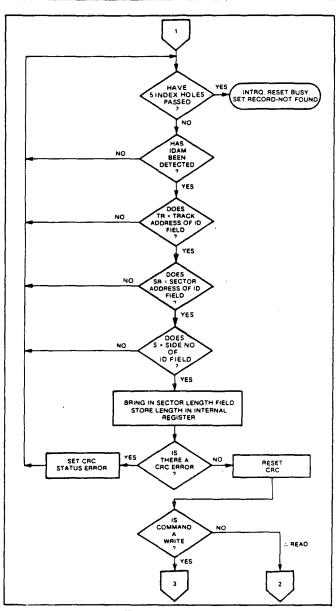

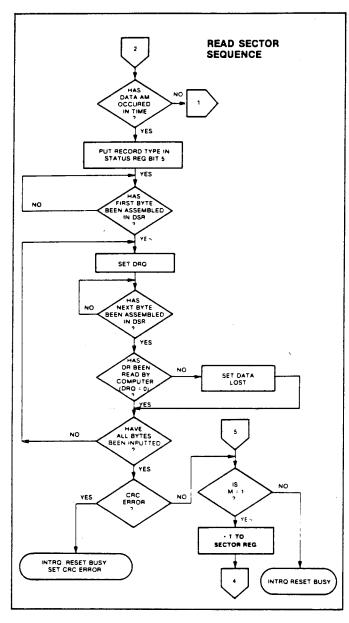

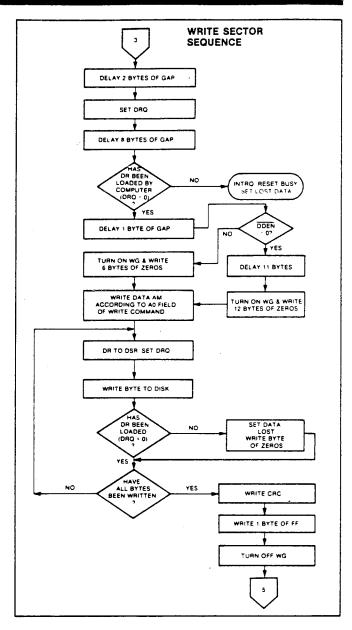

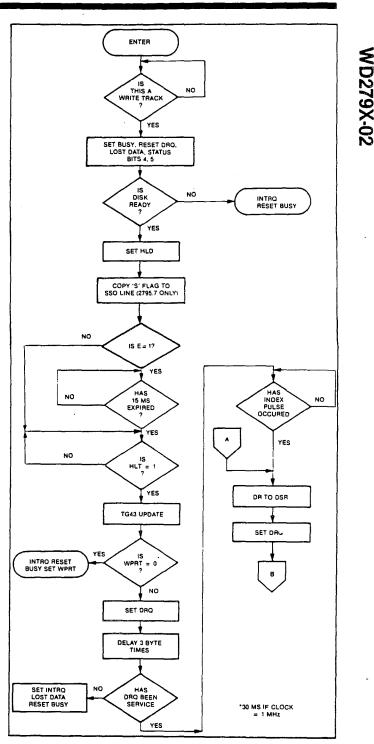

#### 2.1.1.5. Floppy Disk Controller (FDC)

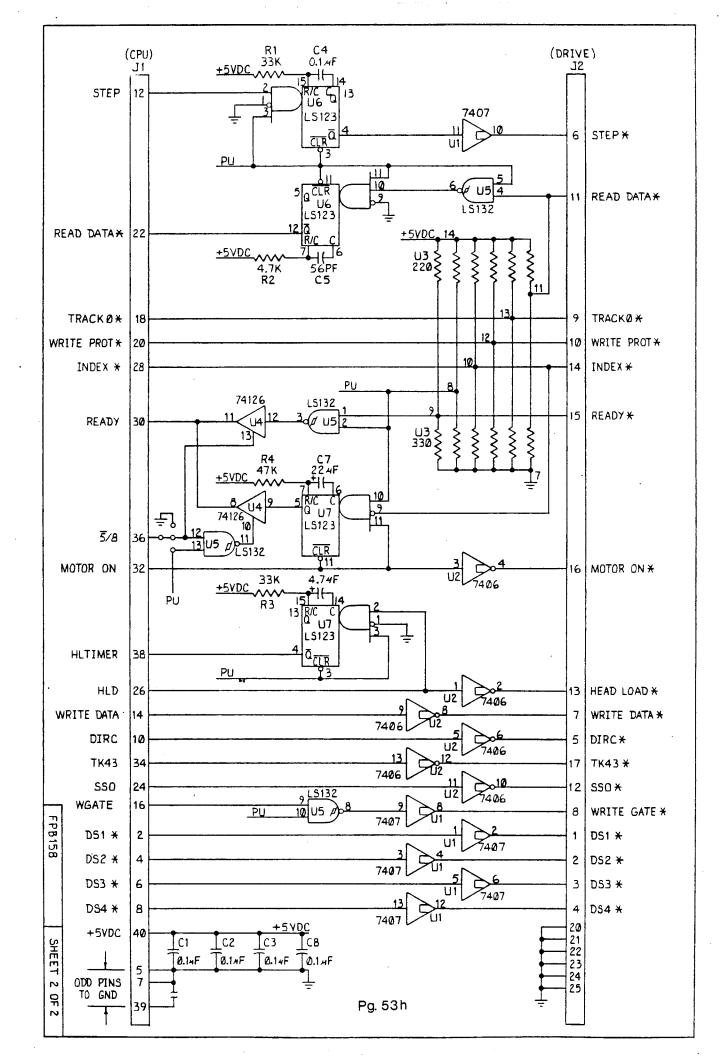

The CPZ-186 uses the Western Digital WD2793 Floppy Disk Controller plus descrete support circuitry as the basis for the controller. A reliable phase-lock-loop circuit is implemented giving the user error free disk operation. Up to four 8-inch, four 5 1/4-inch or any combination of four 8 or 5 1/4-inch Floppy Disk drives may be connected. A mix of single- or double-sided drives and of single- or double-density drives may be interconnected. Any combination of single/double sided and single/double density drives may be connected.

The FDC is connected to the drives via Personality boards FPB100-XY or FPB158-XY and adaptor boards FPB100-XY or FPB158-XY The FPB158-30 accommodates both 5 1/4 and 8-inch drives by providing means to connect a 34 pin edge card connector for 5 1/4-inch drives and a 50 pin box connector for 8-inch drives. The FPB100-11 adapts 8-inch drives only and the FPB100-22 adapts 5 1/4-inch drives only. This technique greatly reduces the overall cost of interfacing to floppy drives. With a low cost personality board and even lower cost adaptor, the user may connect the drive configuration fitting their particular needs.

See the "PERSONALITY BOARD USERS GUIDE" section for clarification on the use of the Floppy Personality boards discussed above.

#### 2.1.2. ON-BOARD I/O CONTROLLERS

The On-Board I/O controllers consist of the DMA Controller, Interrupt Control Logic and the Memory Management Unit.

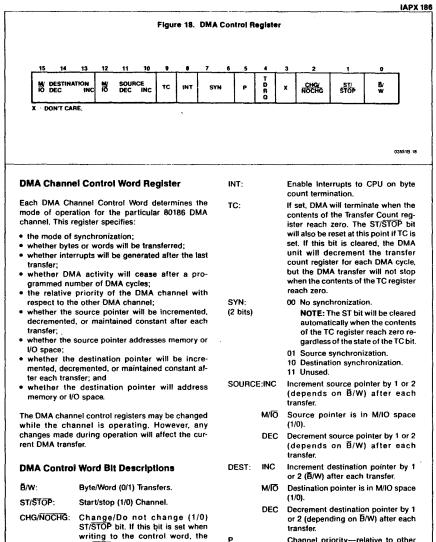

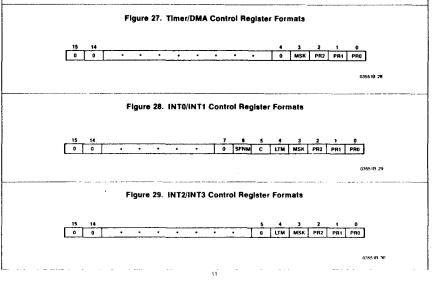

#### 2.1.2.1. DMA Controller

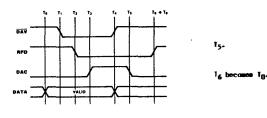

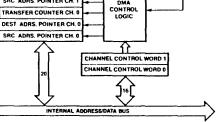

The DMA Controller is internal to the 80186 and consists of logic designed to allow external peripheral devices to transfer data directly to and from the on-board system memory. The use of this data transfer technique greatly enhances the system data throughput because the 80186 microprocessor CPU core does not have to deal directly with the transfers, and is free to perform other computing functions.

#### 2.1.2.2. DMA Operations

The 80186 DMA Logic enables the programmer to free the CPU from the repetitive task of controlling data block transfers by providing hardware control over such operations. For example. the programmer may specify that a data block of "X" number of bytes contained in system memory starting at location "Y" is to be transferred. The programmer may further specify that at the end of said transfer an interrupt is to be generated (perhaps to initiate a subsequent transfer, or to determine the peripheral device status prior to initiating a subsequent transfer). Alternately, the programmer may wish to automatically reinitialize the data block transfer. Once the software command is transmitted to the DMA logic, it performs all of the indicated actions without further supervision from the 80186 CPU core. In all cases, the user of the CPZ-186 has full control over these parameters and events. Once the DMA transfer has begun (also enabled under software control), the CPU may then be used for other processing or for controlling other peripheral data transfers in a similar manner.

The DMA Control channels may be operated in either byte or word transfer mode. DMA transfers can occur between memory and I/O or between memory and memory. This means that in executing memory-to-memory transfers, DMA transfers can occur from on-board memory to off-board memory or from the I/O controllers to offboard memory. The transfer rate is 2 megabytes/sec. with DMA operating in burst mode.

#### 2.1.2.3. DMA Channel Assignments

The CPZ-186 provides three channels of DMA. Channel O is dedicated to the S-100 Bus pHOLD line, channel 1 to the FDC Data Request Line and channel 2 to the SIO serial data channel A or channel A of the CIO parallel I/O port. The 80186 HOLD input line is assigned to the S-100 Bus DMA request line to allow temporary bus masters to capture the bus for DMA transfers to off-board memory. Fixed priority selection allows arbitration between internal DMA and external DMA requests from the S-100 Bus. Fixed priority gives the S-100 Bus the highest priority and the SCC or CIO ports, the lowest. The priority level of the Floppy port versus the SCC or CIO ports may be defined under software control. Thus,

| DEVICE     | PRIORITY                                                     |

|------------|--------------------------------------------------------------|

| ~ <b>-</b> |                                                              |

| S-100 Bus  | 1 High                                                       |

| FDC        | 2 or 3 (under sftwr control)                                 |

| SCC or CIO | 2 or 3 (under sftwr control)<br>2 or 3 (under sftwr control) |

A memory-to-memory block transfer feature is provided which enables the user to transfer blocks of data from a source area of memory to a destination area of memory with an overall throughput increase of 5 times that available using Z80 (4 Mhz) block moves. Further, programming overhead is reduced in that the CPU need only initiate the DMA device and enable the DMA transfer. The CPU may then execute other code if so desired.

Combining DMA with the Memory Management Unit (MMU), a block of memory may be transferred from the on-board system memory to off-board system memory and vice-versa at DMA speeds. Additionally, FDC, SCC or CIO data may be transfered directly to off-board memory and vice-versa at DMA speeds. The MMU is loaded with appropriate address translation information. When the DMA transfers data to addresses translated by the MMU, the data is directed to the off-board memory. Memory-to-memory transfers within the on-board memory may also be made. While the 80186 executes block move transfers at 16 clock cycles per byte, the memory-to-memory function of the DMA controller will move a byte in 8 clock cycles, or 2 times faster.

The S-100 Bus channel (channel 0) is normally operated in "CASCADE" mode. The DMA Controller simply isolates the CPZ-186 from the S-100 Bus while the off-board DMA transfer occurs. The power of this technique is that any number of DMA type devices may reside on the S-100 Bus limited only by system data throughput considerations.

During power-up or reset, the DMA Controller is cleared to a state in which the Start/Stop bit for each channel will be set to STOP. Also, any transfer in progress is aborted.

Refer to the 80186 Data sheets for a detailed description of the DMA section.

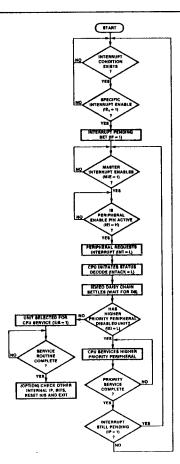

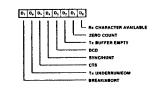

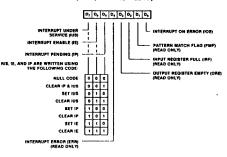

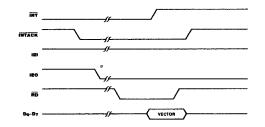

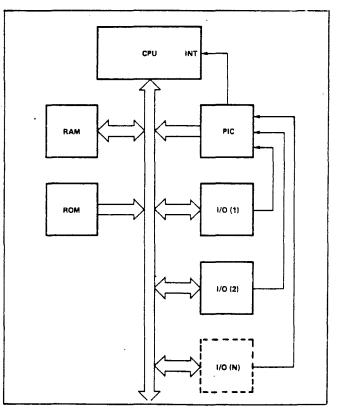

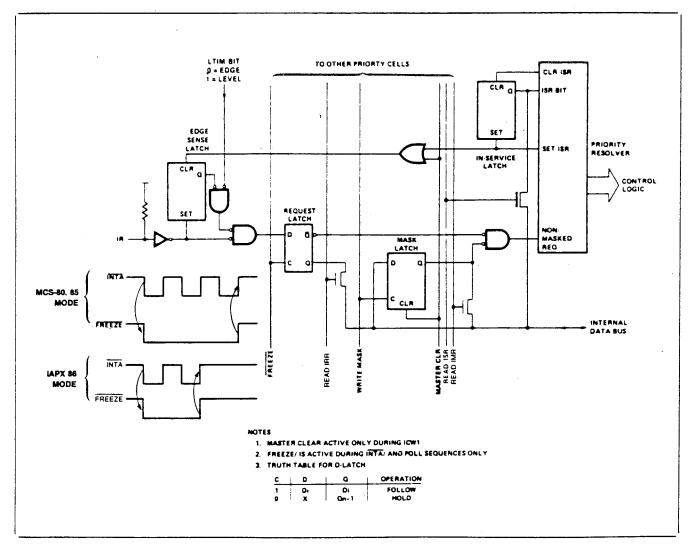

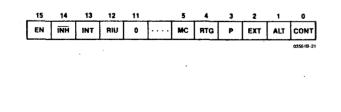

#### 2.1.2.4. Interrupt Control Logic

The interrupt control logic gives the CPZ-186 user the power to respond to the maskable interrupt (INT\*) allowing the user a short form indirect call to any memory location within the 80186's address space.

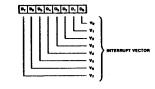

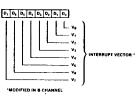

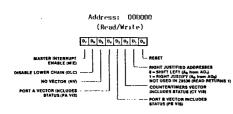

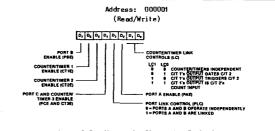

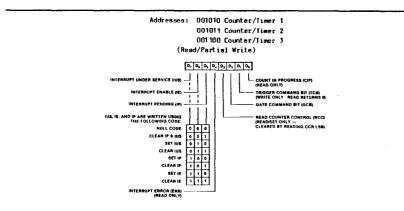

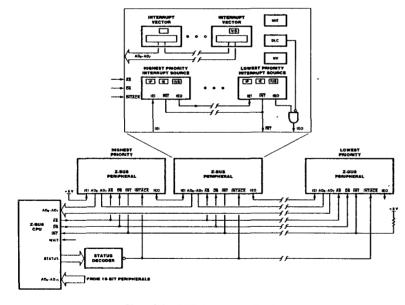

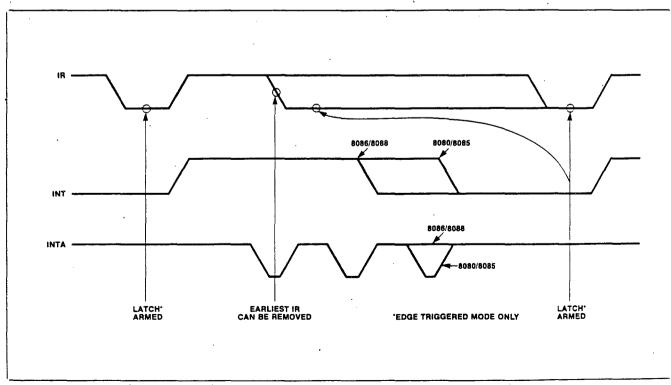

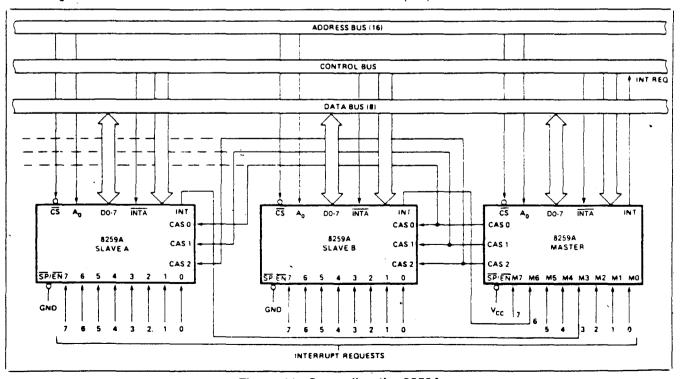

#### 2.1.2.5. Interrupt Controller/Select

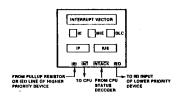

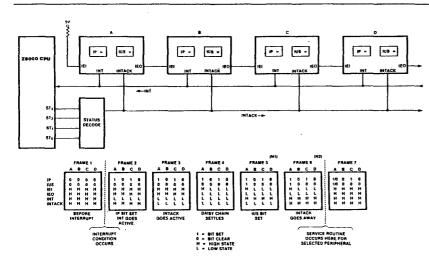

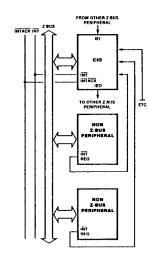

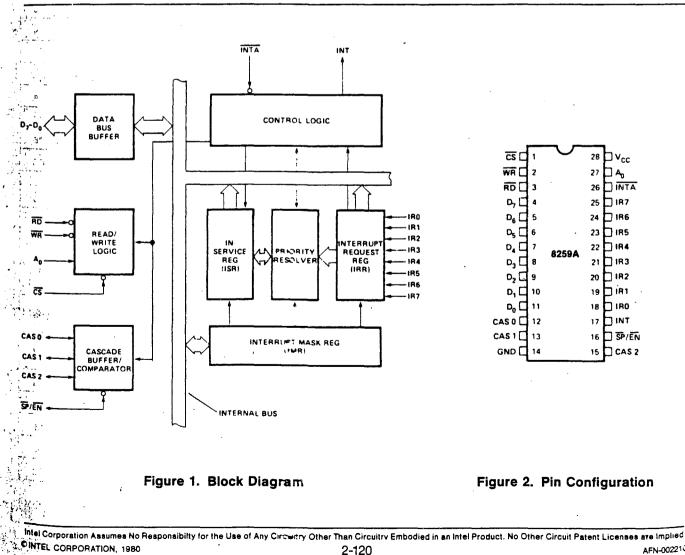

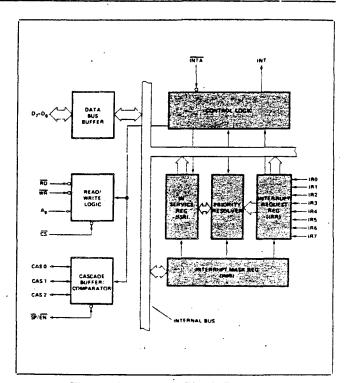

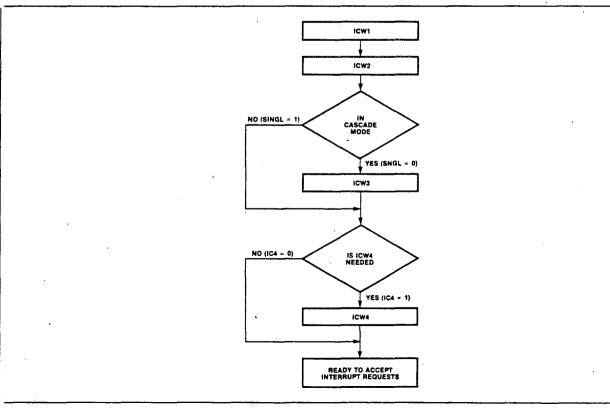

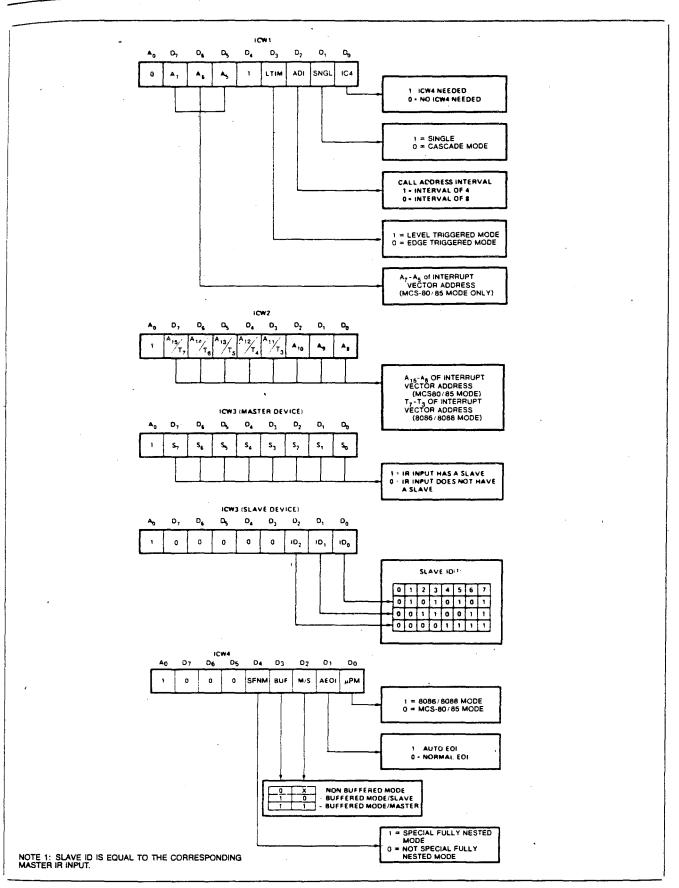

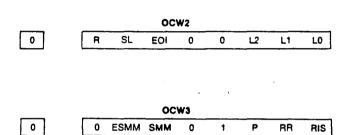

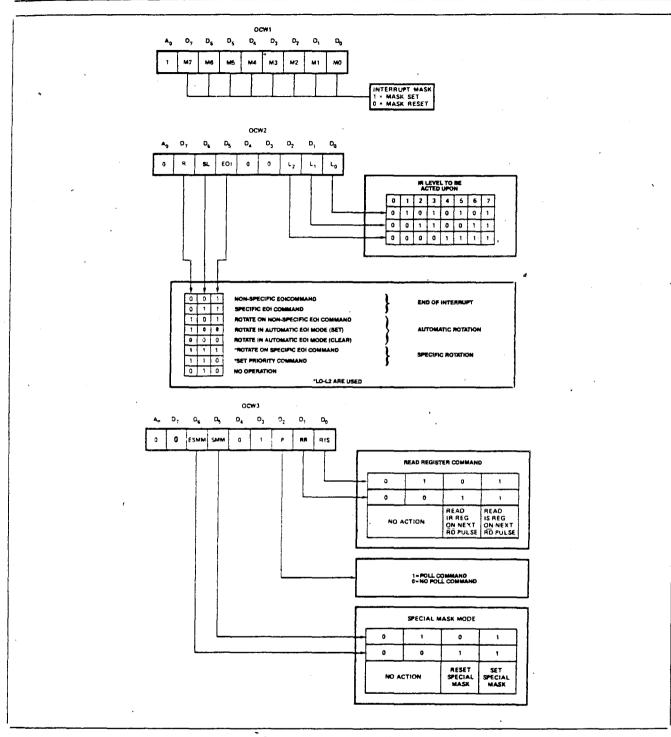

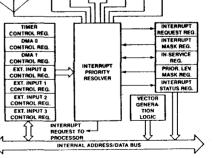

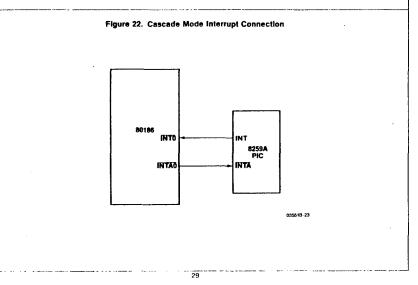

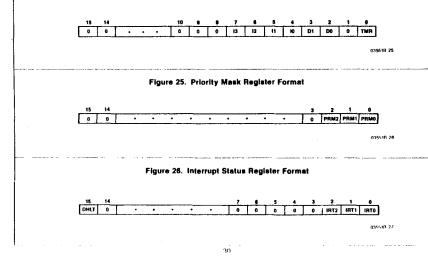

The CPZ-186 interrupt controller consists of the 8259A Programmable Interrupt Controller. This is a LSI device which provides up to eight maskable interrupt request inputs. Upon receipt of an unmasked interrupt request, a byte of previously stored information is output to the data bus. This enables the CPU to process interrupt service routines by executing indirect jumps to those service routines. Expansion to the interrupt structure is provided by a priority technique in which enable in/enable out signals are connected in series ("daisy-chained").

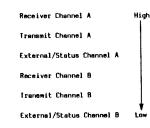

The 8259A interrupt output is connected to Interrupt Channel 1 input of the 80186. The SCC and the CIO interrupt outputs are connected to channel O of the 80186 thus giving the SCC and CIO interrupts higher priority over the interrupts connected to the 8259A Controller. The higher priority interrupting device's enable input is set to logical ONE by permanently connecting it to a pull-up resistor. The SCC enable input line is pulled up to a logical ONE, its enable output line is tied to the enable input line of the CIO. The enable input line of the 8259A is pulled up. The eight interrupting channels are serviced on a fixed or rotating basis. Within the SCC, priority is fixed, Channel A is assigned a higher priority than Channel B. The receiver, transmitter, and external status are assigned priority in that order within each channel. Similarly, interrupt priority for the CIO is fixed, with Port A having higher priority than Port B.

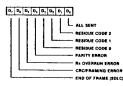

During Interupt Acknowlege O, the SCC or CIO will place its interrupt onto the data bus. During Interupt Acknowledge 1, the 8259A will place iits interrupt vectory onto the data bus.

In summary, the CPZ-186 interrupt priority daisy chain is as follows:

| Priority                                     | Device                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9–16 | SCC channel A receiver<br>SCC channel A transmitter<br>SCC channel A transmitter<br>SCC channel B receiver<br>SCC channel B transmitter<br>SCC channel B transmitter<br>SCC channel B external status<br>CIO port A<br>CIO port B<br>8259A inputs (fixed or rotating)<br>S-100 Bus interrupt device(s) |

| 17-nn                                        | S-100 Bus interrupt device(s)                                                                                                                                                                                                                                                                          |

#### T A B L E 2-3: Interrupt Priority Daisy Chain

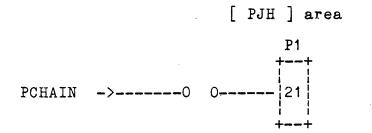

NOTE: Any I/O device in the S-100 Bus which uses the INT\* line must use this priority chain scheme and must supply its own vector. The INT\* signal must be connected to interupt 7 of the 8259A by jumpering B2 to C2 of block JB. The 8259A must be programmed so that the IR7 input has a slave. The I/O device must connect to the PCHAIN (Priority enable output Line, pin 21 of the S-100 Bus).

An additional feature of the CPZ-186 is that data transfers from the peripheral devices may be handled in a polled mode. This requires that the 8259A device be programmed for polled mode and the status register interrogated for the occurrence of the interrupt source signal. In polled mode no interrupts are generated, but the status signal indicating the occurrence of an event remains active. Having detected that occurrence, the remaining status is then interrogated to determine which of the eighteen events occurred.

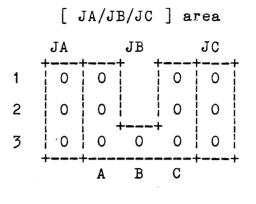

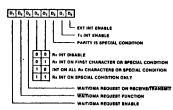

Jumper options allow the user to choose among twelve S-100 Bus interrupt signals (VIO\* to V17\*, INT\*, PWRFAIL\*, NMI\* and ERROR\*), as well as two internally generated interrupt signals, FINT\* and PINT\* corresponding to the FDC interrupt and the parallel port interrupt. Four spare inputs are provided. The user selects eight of these signals to be inputs to the Interrupt Controller.

| Signal    | Source                  |

|-----------|-------------------------|

| VIO*-V17* | S-100 Bus               |

| FINT*     | FDC Interrupt           |

| SERR*     | S-100 BUS ERROR         |

| PINT*     | Parallel port interrupt |

The S-100 Bus signal INT\* is connected to the 8259A'S interrupt input 7 via jumper JB b2-to-c2.

The CPU's non-maskable interrupt line (INMI) may be selected to respond to signals on the S-100 Bus NMI\* or PWRFAIL\* line. Also, it may be left in its factory set default condition where it is permanently disabled. All of these options are implemented by use of jumper plugs.

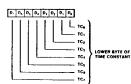

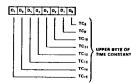

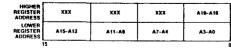

#### 2.1.2.6. MEMORY MANAGEMENT UNIT

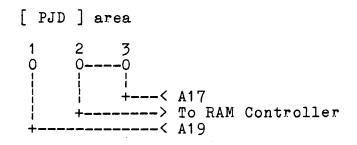

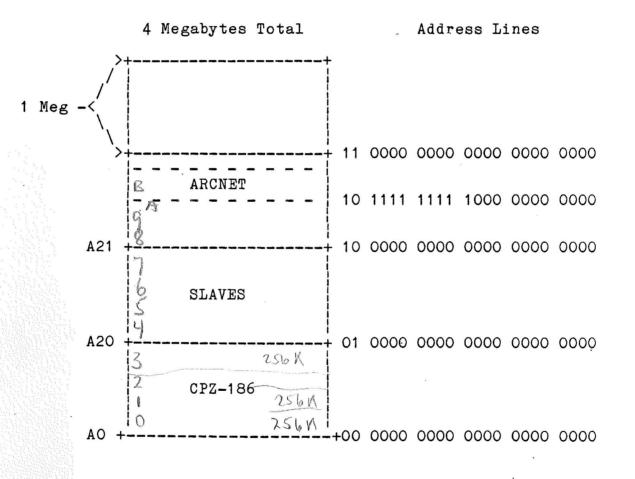

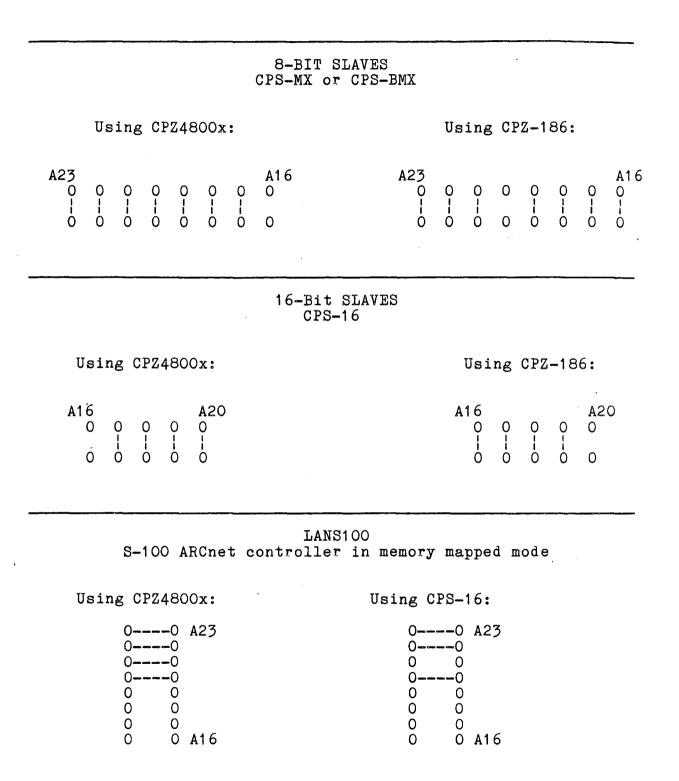

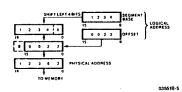

The Memory Management Unit (MMU) consists of a 74LS670 4x4 Register File used as a memory mapping device plus associated logic to expand the 80186 20-bit address to 22 bits, increasing the addressing capability of the CPZ-186 from 1 Megabytes to 4 Megabytes. Two modes of operation are possible. These are the "PASS" and "MAP" modes. Bits A18 and A19 of the 80186 are input to the 74LS670. These bits address one of four 4-bit registers, the outputs of which are output on the address bus. In pass mode, the 80186's A18 and A19 address bits merely pass through the 74LS670 to the corresponding 74LS670 address outputs. The remaining 4 bits of extended address lines are forced to logic zero. In map mode, the contents of the addressed mapping register are output on the address bus. This technique proves to

be quite powerful since the extended address lines A20 and A21 appear on the bus dynamically. Address bits A22 and A23 are always at logic O level. This gives a total of 4 active bits of extended address constituting a "PAGE" address. The remaining 18 lower order address lines address the locations within each page. A "PAGE" consists of 256 Kbytes. There are sixteen 256 Kbyte pages to give a total of 4 megabytes of storage.

The Memory Management Unit allows the user to map any logical 256K block of memory to any physical 256K block within the 4 megabyte range. Thus, several programs or "TASKS" can share one main program by changing logical 256K block addresses.

#### 2.2. 256 Kbyte/1 Megabyte Dynamic RAM/Controller

The 256 Kbyte/1 Megabyte Dynamic RAM consist of sixteen 64Kby-one-bit or 256K-by-one-bit Dynamic RAM's and the 4500A Dynamic RAM Controller.

Internal RAM Controller logic provides effective refresh techniques suitable for 80186 and S-100 Bus operations. The 4500A multiplexes 16-bit address lines (A1 through A16) to the RAM's. External logic multiplexes address lines A17 and A18 for the 9th multiplexed line required for 256 Kbyte RAM chip operation. A RAS/CAS/REFRESH circuit generates the required timing for the proper reading, writing and refresh operations of the RAM. RAM enable logic is provided to disable the on-board RAM when offboard RAM is addressed.

During cold-start boot-up, the first function is to open up a 4 or 8 Kbyte memory space for the boot-up EPROM. Next the EPROM contents is moved and executed. After boot-up, the EPROM is turned off and the full linear address of 1 megabyte becomes available.

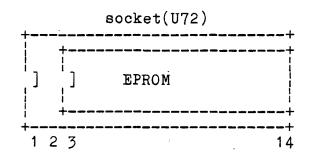

#### 2.3. 2K/4K/8K EPROM

The CPZ-186 may accommodate either a 2K (2716), 4K (2732) or 8K (2764) EPROM. A jumper (jumper PJJ) is made available to select either of the three EPROM types. The EPROM functions as both a boot-up and a monitor PROM. As a boot-up PROM, the EPROM contains the software routines necessary to manipulate the EPROM address and Deselect Circuitry and to load the required Disk Operating System contained on Floppy Disk Drive diskettes. The EPROM also contains monitor routines which are discussed in the SOFTWARE/PROM MONITOR sections.

#### 2.4. I/O Chip Selects

The 80186 CPU generates the "chip select" signals for the SCC, CIO, Interrupt Controller, FDC, Memory Management Unit (MMU), Boot/Monitor Enable, Memory Deselect Logic, and the FDC Configuration Register.

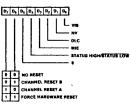

#### 2.5. POWER-ON CLEAR/RESET LOGIC

This logic provides reset signals to the CPU as well as to the S-100 Bus interface. The logic is activated under two conditions, when power is first applied to the board, and when the S-100 Bus signal RESET\* is activated.

Signals asserted upon applying power are:

- a. S-100 Bus signals POC\*, RESET\*, and SLAVE CLR\*

- b. Internal CPZ-186 reset

Signals asserted when RESET\* is asserted are:

- a. S-100 Bus signal SLAVE CLR\*

- b. Internal CPZ-186 reset

#### 2.6. CLOCK GENERATOR

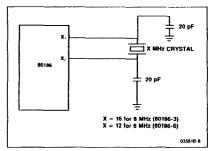

The 80186 CPU generates an 8 Mhz clock based on a 16 Mhz crystal connected to its inputs. The clock generator divides the 8 Megahertz clock signal to provide the internal CPZ-186 clock (8MHZ) and the S-100 Bus clocks (0 and CLOCK). These clock signals are utilized to implement S-100 Bus signals in conformance with the IEEE standard for the S-100 Bus on a welldefined, clocked-logic basis.

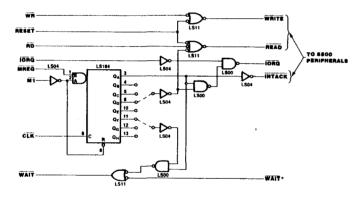

#### 2.7. S-100 BUS CONTROL SIGNALS GENERATOR

The S-100 Bus Control Signals Generator consists of the logic necessary to generate key S-100 Bus signals such as pSYNC, pSTVAL\*, pWR\*, pDBIN, pHLDA, SOUT, SM1, SINP, SMEMR, SHLTA, SINTA, SXTRQ and sWO.

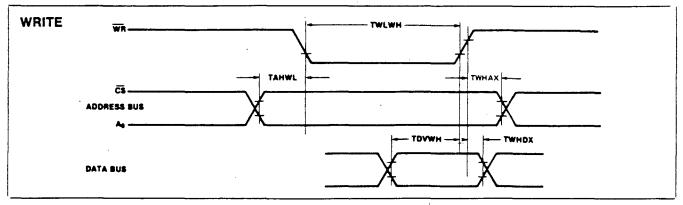

The S100 Bus signal, SWO, may be output from the CPZ-186 so that the timing is in conformance with the write signal directly out of the 80186 CPU (pulsed mode) or with the timing in an NRZ form (latched mode). The CPZ-186 is factory configured for pulsed mode. Jumper PJL is provided to select the mode.

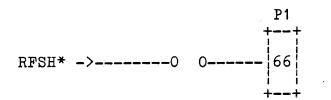

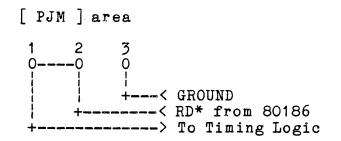

The S100 Bus signal, SMEMR, may be output from the CPZ-186 so that the timing is in conformance with the read signal directly out of the 80186 CPU (pulsed mode) or with the timing in an NRZ form (latched mode). The CPZ-186 is factory configured for pulsed mode. Jumper PJM is provided to select the mode.

#### 2.8. S-100 Bus Interface

The S-100 Bus consists of 100 electrical signal lines. These are grouped into sets of lines used to transmit data and control among interconnected devices.

The groups are:

| Group                     | No. of Lines     |

|---------------------------|------------------|

|                           |                  |

| Address Bus               | 24               |

| Input Data Bus            | 8                |

| Output Data Bus           | 8                |

| Status Bus                | 8                |

| Control Input Bus         | 5<br>6           |

| Control Output Bus        | 6                |

| DMA Control Bus           | 8                |

| Vectored Interrupt Bus    | 8                |

| Utility Bus               | 8                |

| System Power              | 9 `              |

| Manufacturer specified 1: | 9<br>ines 3<br>5 |

| Reserved lines            | 5                |

Devices connected on the bus are classified as either bus masters or bus slaves and as either permanent or temporary masters. The CPZ-186 is a permanent bus master. Any other master connected to the S-100 bus may take control of the bus by making the appropriate DMA request provided no internal DMA by the SCC, FDC, or CIO is in progress. The S-100 Bus DMA request will be honored first if simultaneous DMA requests occur.

Each of the S-100 Bus signals utilized by the CPZ-186 are described on the following pages.

#### 2.8.1. Address Bus

The address bus consists of 24 lines used to select a memory location or an input/output device during a bus cycle. All but A22 and A23 of the 24 address lines are active during a memory read, write or opcode fetch (M1) cycle unless the Memory Management Unit has been programmed for pass mode in which case the uppermost 4 bits (A20-A23) are forced to logic zero. The least significant byte of the address lines is active for input or output cycles. Address bus lines are enabled while ADSB\* is inactive (no S-100 Bus DMA cycle in progress). The address bus lines are denoted as A0 through A23, with line A0 representing the least significant bit. Lines A0 through A7 compromise the least significant byte and lines A8 through A15 make up the "high" address byte with bits A16 through A23 constituting the extended address byte. Two octal-drivers and the Memory Management Unit are used to condition the lines in conformance with the characteristics required by the IEEE S-100 Bus standard.

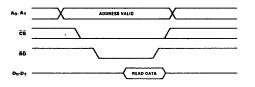

#### 2.8.2. Input Data Bus

There are eight input data lines (DIO-DI7) which are treated strictly as input when the CPZ-186 communicates with an 8 bit bus device. If a 16 bit bus device communicates with the CPZ-186, the Output Data Bus (DOO-DO7), which also consists of 8 bits, doubles up as an input bus to give a total of 16 data bits for input. The input data bus is enabled onto the CPZ-186 under the following conditions:

- 1. AN EXTERNAL I/O CYCLE IS INITIATED.

- 2. AN EXTERNAL MEMORY CYCLE IS INITIATED.

- 3. AN EXTERNAL DEVICE INTERRUPTS THE CPU AND PLACES A VECTOR ON THE DATA BUS.

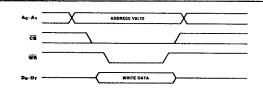

#### 2.8.3. Output Data Bus

There are eight data output lines (DOO-DO7) which are enabled by the signal DODSB\*. A line driver conditions these lines to conform with the IEEE S-100 Bus standard. These 8 data lines are treated strictly as output when the CPZ-186 communicates with an 8 bit bus device. If a 16 bit bus device communicates with the CPZ-186, the Input Data Bus (DIO-DI7), which also consists of 8 bits, doubles up as an output bus to give a total of 16 data bits for output.

#### 2.8.4. Status Bus

The status bus consists of seven output lines which define the current CPU bus cycle type. These lines are enabled while the enabling signal SDSB\* is inactive. An eight line, SXTRQ, is output when the CPZ-186 is requesting 16 bit data transfers on the bus.

The eight lines of the Status Bus are:

| Status | Function                     |

|--------|------------------------------|

|        |                              |

| SMEMR  | Memory Read                  |

| sM1    | Opcode Fetch                 |

| sINP   | Input                        |

| sOUT   | Output                       |

| sWO*   | Write cycle                  |

| sINTA  | Interrupt acknowledge        |

| SHLTA  | Halt acknowledge             |

| sXTRQ  | 16-Bit Data Transfer Request |

These are individually described below:

#### 2.8.4.1. sMEMR (Memory Read)

sMEMR is a status signal indicating that a memory read cycle is in progress. This signal is valid during a normal memory read cycle (memory read or opcode fetch cycle).

sMEMR, may be output from the CPZ-186 so that the timing is in conformance with the read signal directly out of the 80186 CPU (pulsed mode) or with the timing in an NRZ form (latched mode). The CPZ-186 is factory configured for pulsed mode. Jumper PJM is provided to select the mode.

#### 2.8.4.2. sM1 (Opcode Fetch)

sM1 is a status signal indicating that a memory read/opcode fetch cycle is in progress.

#### 2.8.4.3. sINP (Input)

sINP is a status signal indicating that a peripheral device read cycle is in progress.

#### 2.8.4.4. sOUT (Output)

sOUT is a status signal indicating that a peripheral device - write cycle is in progress.

#### 2.8.4.5. sWO\* (Write Cycle)

sWO\* is a status signal indicating that a write cycle is in progress, wherein data is transferred from an S-100 Bus master to a slave.

sWO\*, may be output from the CPZ-186 so that the timing is in conformance with the write signal directly out of the 80186 CPU (pulsed mode) or with the timing in an NRZ form (latched mode). The CPZ-186 is factory configured for pulsed mode. Jumper PJL is provided to select the mode.

#### 2.8.4.6. sINTA (Interrupt Acknowledge)

sINTA is a status signal indicating that an interrupt acknowledge cycle is in progress.

#### 2.8.4.7. sHLTA (Halt Acknowledge)

sHLTA is a status signal indicating that the CPU is in a halt state.

#### 2.8.4.8. sXTRQ\* (16-Bit Data Transfer)

The status signal sXTRQ\* (16-bit data transfer request) is used in the CPZ-186 to indicate to bus slaves that a 16 bit data transfer is requested by the CPZ-186. If the slave is able to respond to the masters request, it will cause the input signal, SIXTN\* to go active which will then cause the CPZ-186 to transfer 16 bit data transfers using both 8 bit input and output data ports for bi-direction transfers. If the signal SIXTN\* is inactive and if that transfer is output from the CPZ-186, the CPZ-186 will transfer the 16 bit data by sequencing that data out a byte at a time via the DO lines. If the signal SIXTN\* is inactive and if that transfer is input to the CPZ-186, the CPZ-186 sequences in the 16 bits a byte at a time.

#### 2.8.5. Control Input Bus

The Control Input Bus consists of six signals, five of which are used in the CPZ-186. These lines allow S-100 Bus slaves to synchronize the CPZ-186 with conditions internal to the bus slave, to request the relinquishment of the S-100 Bus (DMA request) and to disable the CPU from the S-100 Bus. The signals are conditioned by pull-up resistors and Schmitt-trigger input receivers.

The six lines of the Control Input Bus are:

| Line   | Function                       |

|--------|--------------------------------|

| RDY    | Slave ready                    |

| XRDY   | Special ready                  |

| INT*   | Maskable interrupt request     |

| NMI*   | Non-maskable interrupt request |

| HOLD*  | DMA request                    |

| SIXTN* | Sixteen acknowledge            |

These lines are described in the following paragraphs.

2.8.5.1. RDY (Slave Ready)

This control line is used by S-100 Bus slaves to suspend bus cycles by inserting wait states in a CPU cycle. Slaves may connect to this line by using an open-collector driver.