## TECHNICAL INFORMATION EXCHANGE

February 25, 1969

PRINCIPLES OF TIME-SHARING

Mr. Milon H. Cluff

Mr. David Thompson

IBM Corporation

Building 005-2

South Road

Poughkeepsie, New York 12602

This paper is intended to introduce IBM marketing personnel to the fundamentals of terminal based computing. The nature of time sharing and its place in the spectrum of computing is discussed. In addition, the monograph covers basic implementation techniques and surveys topics related to time sharing systems, such as multi-processing and virtual memory system structures. An appendix includes a time sharing acronym and reference list, reading and a glossary of time sharing terms.

For IBM Internal Use Only

### CONTENTS

| 1          | What i                                                           | 1                                       |         |  |  |  |  |

|------------|------------------------------------------------------------------|-----------------------------------------|---------|--|--|--|--|

| 11         | Why is "Time-Sharing"?                                           |                                         |         |  |  |  |  |

| ш          | How is "Time-Sharing" Accomplished? 17 Implementation Techniques |                                         |         |  |  |  |  |

| ľV         | Multi-Processing Systems 54                                      |                                         |         |  |  |  |  |

| v          | Design of a Virtual Memory Based 78 Programming System           |                                         |         |  |  |  |  |

| VI         | Remote Batch Computing 88                                        |                                         |         |  |  |  |  |

| VП         | Communications for Terminal Based 92 Computing                   |                                         |         |  |  |  |  |

| Append     | lix A                                                            | Time-Sharing Acronym and Referen        | ce List |  |  |  |  |

| Appendix B |                                                                  | Time-Sharing Reading and Reference List |         |  |  |  |  |

| Appendix C |                                                                  | Glossary of Time-Sharing Terms          |         |  |  |  |  |

| Append     | lix D                                                            | HYPERVISOR                              |         |  |  |  |  |

### PREFACE

These notes have evolved as a result of teaching a one-week course entitled Principles of Time Sharing. This course is designed to introduce IBM Marketing people to the fundamentals of terminal oriented computing and to acquaint them with the support offered by IBM in this area. Much of the value of the course is derived from the actual hands-on terminal sessions during the class. These notes are intended to document the classroom lectures and provide background for analysis and evaluation of the terminal sessions.

It is said that in the course of a lifetime one should plant a tree, sire a child, and write a book. The authors have accomplished the first two of these life goals and now submit this monograph in partial fulfillment of the third.

### I. What is "time-sharing"?

### A. Introduction

- 1. The term "time-sharing" was introduced in 1959 in a paper delivered by a British mathematician. Christopher Strachev. Almost at the same time, Professor John McCarthy, then of MIT, produced independently an unpublished paper on the same subject. In the intervening years, much discussion, development. publicity, time, and money have been devoted to "time-sharing." The term has been applied broadly to include any system where components are used in an interleaved manner. The term has also been applied in a narrower sense to mean specific implementations of interactive data processing systems. As a result, "time-sharing" has no universally accepted definition. Today there are many and varied definitions in the data processing industry. Like much of the jargon in our marketplace, "timesharing" has been overused and misunderstood. It is frequently equated to multiprogramming, or to remote job entry, or to "on-line" systems, or even to "real-time" systems. In IBM particularly, "time-sharing" has meant TSS - the S/360 Model 67 hardware and software system. It is important to recognize that there is no rigorous and widely accepted definition of "time-sharing." When you hear or speak of "time-sharing", remember the scornful but dangerous counsel of Humpty Dumpty who said. "When I use a word, it means just what I choose it to mean - neither more nor less."

- 2. Time-sharing in the literal sense of the term refers to the allocation of computer resources in a time dependent manner to the several programs simultaneously core resident. In this general context time-sharing is merely synonymous with multiprogramming. It represents an attempt to maximize utilization of the collective resources of a computing system. It was this concept of time-sharing that was presented by Christopher Strachey at UNESCO's International Conference on Information Processing in 1959. Note that in this use of the term, "time-sharing" is not concerned, at least not directly, with what an individual computer user wants to do.

- 3. In the late 1950's there existed a number of people with certain computing requirements requirements that were not being met satisfactorily by the existing batch systems. For the most part these people were located in the M.I.T. Lincoln Laboratory complex and the SAGE related activity at the RAND Corporation and System Development Corporation. Their concern was the efficiency of persons trying to use a computer facility. Their objective was to provide a man-computer relationship to enhance

man's problem-solving ability. It is from this group that a second "time-sharing" concept has evolved. It is this concept of "time-sharing" that we are concerned with in these notes.

4. "Time-sharing" then is merely one way of using a computing facility. It is "user oriented" in that it is intended to provide convenient access to data processing capability. It is a technique that accentuates the man-machine relationship in the problem-solving environment. This technique permits the user to deal "directly" with the system by means of a terminal device. The user is on-line and interacts or engages in a conversation with the computer system. Hence, conversational and interactive computing are synonymous terms with "time-sharing."

Before giving the definition of "time-sharing" to be used in this class, let's look briefly at other techniques of computer usage.

- B. Comparision of techniques of computer usage

- 1. Methods of computer use:

- a. User at the console

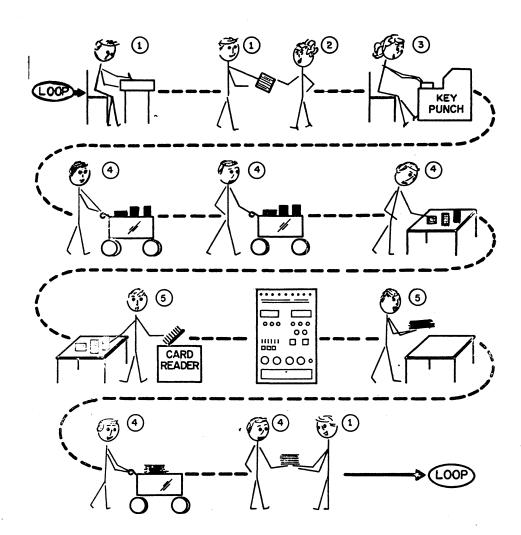

- b. Traditional Batch Computing System

- c. Remote Computing

- 1) Remote Batch Processing

- a) Remote Job Entry

- b) Remote Job Output

- 2) "Time-Sharing"

- d. Real Time Computing

- 2. Characteristics of "User at the console"

- a. The user is in direct contact with a system via its console.

- b. An interactive situation exists with minimum turnaround.

The degree of interaction depends on software.

- c. Thruput is not a serious factor with the relatively lowcost desk-type computer. However, as system size and cost increase, direct access by single user at the console cannot be justified.

- d. The size and characteristics of problems are limited by the following in desk size computers:

- 1) Core size

- 2) Programming Systems/Languages

- 3) I/O Capability

### 3. Characteristics of traditional batch system:

- a. Thruput has been the major consideration in the development of the local or on-site batch system.

- b. The jobs to be run are accumulated in batches.

- c. The system depends on the queue of jobs to keep the system busy.

- d. The user is divorced from direct contact with the computer. He may even be divorced from the program where professional programmers operate in a "closed shop" environment.

- e. Turnaround time is a problem in the batch system.

- Directly coupled systems such as ASP were developed to reduce turnaround time.

- g. Simple errors cause frustrating re-runs and the delay of turnaround adds greatly to total problem solution time.

- h. "Local" batch system jobs are submitted physically to computer center.

### 4. Characteristics of remote batch:

- a. Communication facilities are used in lieu of submitting jobs physically to the computer center.

- Jobs are submitted on-line into the normal batch processing mode.

- c. Response is a function of the design of the host batch system. Job scheduling can be handled in a number of ways. With priority scheduling, remote jobs can be integrated into the local batch queue on an automatic basis. On the other hand, a separate queue may be used to accumulate remote jobs. The operator would have to intervene to switch to this alternate input job stream.

- d. Remote batch processing does not necessarily mean that results will be returned to the input station. Remote job entry (RJE) does not imply remote job output (RJO).

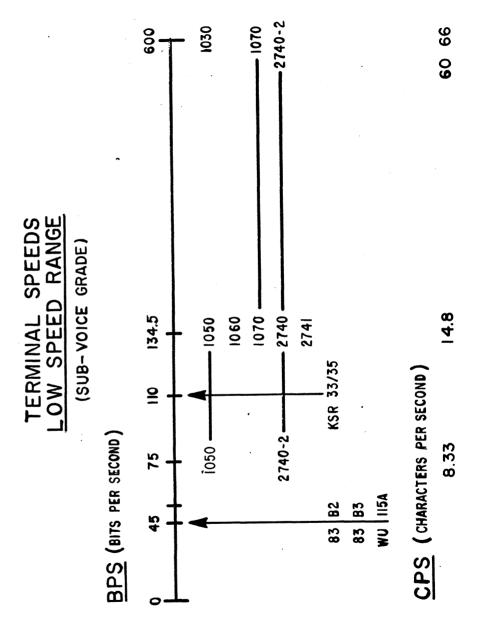

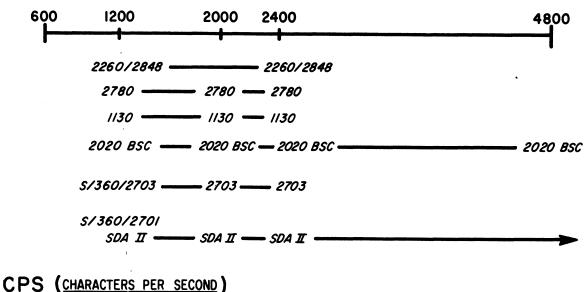

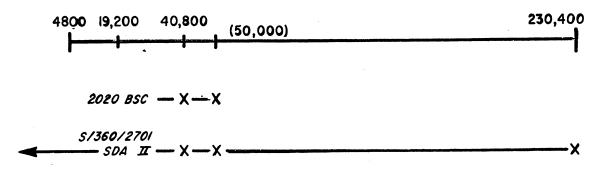

- e. Keydriven devices such as Teletype, 1050, and 2740/41 lend themselves to low speed remote job entry, but are too slow for output listings and dumps, etc.

- f. Higher speed devices such as the 2780 Data Transmission Terminal provide both job input and output to the remote station over communication facilities.

- g. So-called "intelligent" terminals, i.e. the 1130, Model 20, and other models of System/360 have the speed, storage, and logic of stored programming to enhance the input/output station capability. Preediting, formatting, and data compaction are functions possible with "intelligent" terminal stations.

### **BATCH**

h. Remote batch improves the access for remote users and reduces turn-around time. The amount of improvement is a function of the local batch performance and the scheduling of remote jobs into the batch.

### 5. Characteristics of "time-sharing:"

- a. "Time-sharing" is a system in which multiple users concurrently engage in a series of interactions with a system via terminal devices in order to develop a program, solve a problem, or get information from the system.

- b. "Series of interactions" is key. "Time-sharing" is interactive - also called conversational. Users engage in a direct and continuous dialogue - input, "reject" response, corrected input, "accepted" response, etc.

- c. Multiple concurrent users are necessary to economically justify a "time-sharing" system.

- d. Each user appears to have the full resources of the system at his disposal. Rapid multi-plexing from user to user provides this illusion.

- e. Although "time-sharing" is classified as remote computing, a user of a "time-sharing" system is not necessarily located very far from the host computer. User terminals could be located in the same room with the computer. On the other hand, the user may be located many miles away. Distance is not a criteria for "time-sharing". Man-machine direct interaction is key!

### 6. Characteristics of real-time computing:

- a. A real-time system is one that controls an environment by receiving data, processing it and taking action or returning results fast enough to affect the functioning of the environment at that time.

- b. Some definitions of real-time would put a limiting time response as a criteria.

- c. Time response is critical; the system cannot degrade or defer. There is no second chance.

- d. Since strict time dependency is the key, systems are often dedicated, special purpose. Often one cannot afford the overhead of a general purpose programming system in meeting real time requirements.

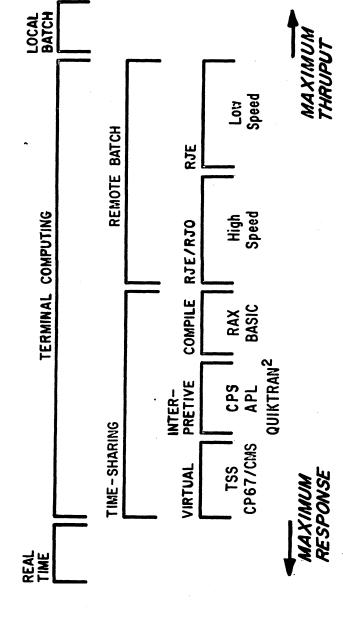

### 7. Spectrum of computing:

a. The great bulk of computing is done today in the local batch mode. Although terminal oriented systems will grow significantly in the years ahead, batch processing will be with us for a long time.

# PECTRUM OF COMPUTING

- b. The first steps in the development of programming systems was to automate flow of work through the computer and make it effeciently process work in the batch mode.

- c. Emphasis has been on keeping the CPU busy and maximize thruput.

- d. At the other end of the spectrum, response is the critical consideration in real time applications.

- e. In between these extremes, berminal computing provides improved service to the user.

- f. Terminal computing can be classified as remote batch or "time-sharing" where "time-sharing" means interactive or conversational computing.

- g. The various techniques are highly inter-related.

- b. It is possible to have the entire spectrum of techniques employed concurrently in the same hardware software system. Multiprogramming makes this possible.

### C. Some Myths Exploded

- 1. Multi-programming and its relation to "time-sharing:"

- a. Multi-programming takes place when two or more independent programs reside in main storage at the same time and operate in an inter-leaved manner. The programs time share the CPU sequentially.

- b. Local batch systems such as DOS, OS-MFT, and OS-MVT are multi-programming systems.

- c. In multi-programming, the highest priority program or task demands the CPU and will always get it when it is ready.

Lower priority programs will only get the CPU resource when no higher priority programs are ready to use the CPU, i. e. are waiting for the completion of some event such as I/O activity.

- d. In "time-sharing," the CPU time is divided among the user programs on a scheduled basis. All ready users will get a "slice" of the CPU time based upon some scheduling procedure. This scheduling procedure, or scheduling algorithm, determines which user gets the CPU next and for what length of time.

- e. The attached chart compares multi-programming and "timesharing" characteristics.

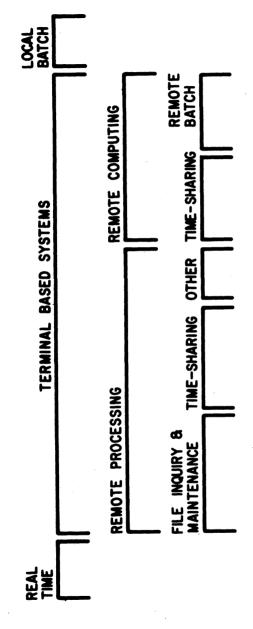

- 2. "Time-sharing" is not limited to the "computing" applications:

- a. The "time-sharing" technique applies equally well to the applications that are data oriented.

- b. The Spectrum of Applications diagram, shows on-line or remote processing as well as the remote "computing" requirements.

- c. Computer Assisted Instruction (CAI) and Text Processing (ATS and DATATEXT) are interactive applications that are non-computing type.

- d. Most applications of the on-line file maintenance/inquiry type are non-conversational. Inputs are strictly formatted and functions possible from the terminal are limited.

### MULTIPROGRAMING

Shares CPU time on demand basis.

Prime Objective: keep computer busy.

<u>Little</u> man/machine interaction,

"Slow" Response Time

Response implies completion of computing requirements.

### TIME SHARING

- Shares CPU time on scheduled basis.

- Prime Objective: keep <u>user</u> busy.

- Basic design philos ophy emphasizes man/machine inter action.

- "Rapid"

Response Time

- Initial and successive responses imply partial completion of computing requirements

8

# SPECTRUM OF APPLICATIONS

- e. More flexibility and capability from the terminal will be necessary to provide access to the on-line integrated information systems required in the years ahead. The time-sharing mode of operation can meet this requirement of Management Information Systems.

- f. "Time-sharing" is much more than just providing a better slide rule for the engineer.

### 3. "Time-sharing" is not a meaningful term:

- a. There is much more to time-sharing than just the sharing of CPU time. Time-sharing involves sharing resources of the entire hardware-software system.

- b. Space-sharing is required in main core storage and in direct access auxiliary storage. Storage allocation is an important consideration in a time-sharing system.

- c. Program sharing is a capability that makes timesharing particularly valuable and operationally efficient.

- d. A program can be shared "externally" from a program library when the "owner" makes the program available to other users. Each user granted access can have his own copy to use or modify.

- e. System programs, compilers for instance, can be shared "internally" when the code is designed as serially re-usuable or re-entrant. Each user executes the same "public" copy of read-only code.

- f. Data sharing is very much like program sharing, and is a facility of great value in a time-sharing system. Security controls, as in program sharing, permit limited or unlimited access to read or change datasets.

### 4. "Time-sharing" is not a specific system:

- a. The IBM System/360 Model 67 Time Sharing System is only one specific "time-sharing" system.

- b. RAX, CPS, APL, CALL/360: BASIC, QUIKTRAN, CP67/CMS, ATS, and TSS are all IBM "time-sharing" systems.

- No one specific system will satisfy the needs of all our customers.

- d. "Time-sharing" can be provided by a customer "inhouse" system or he can buy service from a vendor of "time-sharing."

- Purchasing of "time-sharing" service provides capability with a minimum investment by the user.

- 5. Classification of "time-sharing" systems

- Time-sharing systems can be categorized by several attributes;

- 1) Function provided to the user

- 2) Implementation technique

- 3) Environment

- General purpose as opposed to special purpose or limited function systems.

- The definition of "time-sharing" given earlier listed the following user functions:

- a) Solve a problem

- b) Create a program

- c) Get information from a system

- A general purpose system would permit the terminal user to perform any of the above functions.

- 3) A special purpose system might be limited to one of the above functions. Airline Reservations, for for example, can be considered a special purpose "time-sharing" system because the terminal user is limited to data entry or retrieval.

- 4) Generality in a "time-sharing" system is determined to some extent by the number of programming languages available, size of programs and file space available. Certainly a system that provides only one language is limited.

- 5) Note that some people consider "time-sharing" as general purpose if batch processing takes place concurrently.

- c. Classification by implementation techniques

- A "time-sharing" systems may use a traditional batch compiler that produces object code from source language entered at the terminal RAX and Call/360: BASIC are examples of such systems.

- 2) Interpretive systems or incremental compilers provide another type of implementation for "timesharing" systems. QUIKTRAN, CPS, and APL are examples of interpretive systems.

- 3) Virtual memory systems employ special hardware for dynamic address translation and paging. TSS and CP67 may be classified as such. Note that 1) and 2) are concerned with a compiler technique while 3) is a method of memory management. The compilers used in virtual memory systems are essentially batch compiler types but there is no reason why an interpretive system could not be incorporated into a virtual memory system.

- d. Classification by environment

- A "time-sharing" system can be implemented as a subsystem of an operating system such as OS or DOS.

- 2) Conversely, a "time-sharing" system can be a stand-alone variety. A stand-alone system is dedicated to the time-sharing function. As a result, it has no background or batch capability. On the other hand, the stand-alone version will generally require less core, be easier to install and maintain, and perform more reliably and faster than its counterpart imbedded in an operating system.

### 6. Characteristics of the Ideal Time-Sharing System:

- a. From the standpoint of the user, the ideal system should have unlimited function with instantaneous response.

- Program development languages should fit the range of problems to be solved: FORTRAN, COBOL, PL/I, ASSEMBLER.

- c. Application oriented languages for problem solving for non-computer professionals: i.e. COGO, STRESS, statistical packages, Simulators, and list processing languages.

- d. Full data management capabilities are necessary to satisfy file maintenance and information retrieval requirements. Program libraries are included.

- e. No limit is placed on program size and number of users.

- f. Debugging capability.

- g. Simplicity of operation.

- h. Optional help or prompting information when required.

- Selection of terminal support including keyboard, card, paper tape, CRT display.

- j. Language capability compatible with batch systems.

- k. One must recognize that there is a trade-off in terms of function and response. Clearly, as all the functions of the ideal system are implemented, it becomes increasingly difficult to maintain ideal performance. More facility means more complex relationships and more over head. As the capability offered at the terminal grows, the language necessary to invoke the capability, becomes more comprehensive. Simplicity of operation gives way as capability grows.

- As of this time, no one has an "ideal time-sharing"

system as described above. All of the existing systems

have limited capability and features. The "ideal" may

never be achieved but sound, general-purpose time-sharing

systems are not far off as we approach the 1970s.

### II. Why is "time-sharing"?

- A. What motivates the growing desire to use computers interactively?

- The frustration with delays involved in the batch processing mode have generated a desire for a more responsive and accessible mode of operation.

- The shortage of trained and talented people make it imperative that the available resources be used to the best advantage.

- The growth and diversification of computer usage demands a man-computer relationship that enhances man's problem solving ability.

- B. Time-sharing offers the opportunity to improve performance in what is currently being done with computers.

- Interaction in program development has proven very effective.

- Elapsed time for program development has been reduced and consequently lowered the total cost of development.

- Better utilization of a limited resource qualified people.

- 4. A time-sharing approach permits a user to concentrate on a single job without fill-ins or additional programming tasks because of "wait" periods. Immediate turnaround eliminates need for secondary tasks.

- Management of programming development is simplified where "time-sharing" permits continuous, dedicated effort to a single problem solution.

- 6. There are an estimated 100,000 trained programmers active at the present time. Another 50,000 to 75,000 are probably needed. Every programmer is a potential "time-sharing" user for program creation.

- Interactive development, debugging, and execution can reduce some of the erroneous output and unnecessary listings and voluminous dumps that frequent the batch processing mode.

- 8. If the user can interact, as the solution unfolds, unproductive runs can be eliminated, exception coding can be reduced simplifying program logic, and the printing of repetitive listings, dumps, and results can be avoided.

- 'C. "Time-sharing" extends the range of computer usage to the problems "too small" for traditional computer methods.

- Small jobs presently done by slide rule, desk calculator, "seat of the pants," or not done at all because of impracticality in batch mode are made practical in "time-sharing mode."

- The experience of the Ford Motor Company with 16,000 small jobs, cited in EDP Analyzer, showed that the median user was on the terminal for 10 minutes.

- 3. In the university environment, student problem solving can be best handled in the time-sharing mode. There are nearly three million students in the schools and universities of the United States.

- D. "Time-sharing"extends the range of computer usage to the problems "too complex" for traditional computer methods.

- There is a whole span of problems that probably cannot be solved except by a highly interactive manmachine environment.

- 2. In problem solving, man excels in setting goals, in laying down guide lines, choosing approaches, following intuition, exercising judgement, and evaluating results. These aspects are heuristic, meaning that they lead toward or facilitate invention or discovery.

- The great value of computers lie in their ability to execute very rapidly and very accurately, procedures that have been defined explicitly and in detail. These procedures are called algorithms.

- 4. In batch mode processing, the heuristic contributions are supplied by the user before the program gets into the computer. The heuristic contribution then ceases abruptly, and the execution of the algorithm begins. This separation of the two aspects is a serious handicap to the solution of the problems that face our customers in the frontiers of computing.

- E. "Time-sharing" extends the range of computer usage by making the computer more accessible to other professionals.

- In addition to the 800,000 to 1,000,000 scientists and engineers at work in the United States, other nonprogrammer professionals are potential users of "time-sharing" systems.

- Financial institutions are particularly active in using and providing "time-sharing" service to their customers. Investment analysis is the salient application area.

- Statisticians, actuaries, market-forecasters, and analysts of every kind have need of the immediate problem solving made possible by "time-sharing."

- 4. Doctors, lawyers, accountants, brokers, credit managers, real estate people, and legislators have need of "data bank" access that "time-sharing" can provide.

- Authors, educators, and technical writers have found text processing at the terminal to be an excellent tool to facilitate text-book and manual preparation.

- 6. Application oriented languages are vital in extending computer usage to non-computer professionals. Conversational programs like COGO, STRESS, GPSS, ECAP, PMS, STATPAK, MPS (LP), AND GIS will pave the way for other professionals to avail themselves of computing or processing utility.

- 7. Professional users who are not programmers and have no intention of becoming such are often motivated or stimulated by "time-sharing" to incorporate additions or modifications to packages or even write processors of their own.

- F. Expertise with attendant publicity, salesmanship, and financial support have contributed significantly to "time-sharing" evolvement.

- Acknowledged centers of computer technology have been leaders in the development of "time-sharing" systems. Our leading universities and the so-called "think tanks" have contributed the expertise in the early and continuing evolvement of "time-sharing."

- Many respected and articulate proponents of

"time-sharing" have voiced their convictions

fervently and repeatedly. Computer conventions,

and journals have provided a continuing forum for

papers and presentations.

- 3. The United States government through ARPA of Department of Defense (DOD), National Science Foundation (NSF), Atomic Energy Commission (AEC), and National Institutes of Health (NIH), has contributed millions of dollars toward development costs at the universities and "think tanks." ARPA spending reported at \$12 million to \$13 million a year on "time-sharing" by FORTRAN article, August, 1967.

- 4. IBM has contributed significantly to the "time-sharing" development with internal experimental systems, i.e. TSM, M44, CP40, and APL. Many customer projects in "time-sharing" have been jointly developed with IBM. IBM programs in addition to TSS, include RAX, CPS, ATS, QUIKTRAN, CALL/360: BASIC, CALL/360: DATATEXT, and CP67.

- 5. First generation systems have proven the concept to be workable. Satisfied users continue to promote and extol the virtues of "time-sharing," Demonstration is crucial in selling interactive computing.

- 6. Although there are many statements about improved productivity and efficiency of users, there are little or no statistics to cost justify "time-sharing" facilities.

### III. How is "time-sharing" accomplished? Implementation techniques.

### A. Consideration of user environment

- "Time-sharing" is defined as interactive or conversational computing. The degree of interaction is highly variable.

Depending on design and implementation techniques, it is possible to develop a wide range of conversational capability.

- 2. The degree of interaction can vary with the function being performed. During program creation one level of interaction may be possible, whereas program execution may have a lesser degree of conversationality. Again, the type and sophistication of the system implementation will determine the amount of user interaction.

- A very high degree of interaction may be achieved, but only at the expense of some other desirable characteristic, i.e., response or execution speed. As in any system, trade-offs between facility and performance must be considered.

- 4. The user must have the capability to specify the "time-sharing" system function to be used whether program creation, modification, execution, etc. A "Command Language" is necessary to permit the user to direct his activity.

- Commands may be explicitly stated by key words or verbs in the terminal user's language to select the mode of operation.

- 6. Some commands are administrative in nature. Other commands allow the user to load, list, create, modify, execute a program, list the program names in the library, interrupt a program, and save a program in the library.

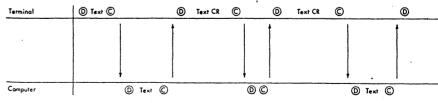

- 7. The concept of "time-sharing" works or is economically feasible because at any instant of time, a large number of the terminal users are making little or no demand on the system. So-called "think" time and user typing time make no demand or very little demand on the system. Output printing, likewise, requires little system effort.

- 8. Users in "hard execution," compilation for instance, do make heavy demands on the system. Few of the total population of users are in "hard execution" at the same time however.

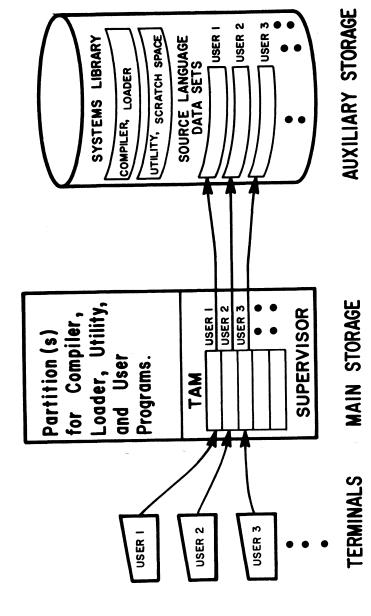

### B. Components of the "time-sharing" system.

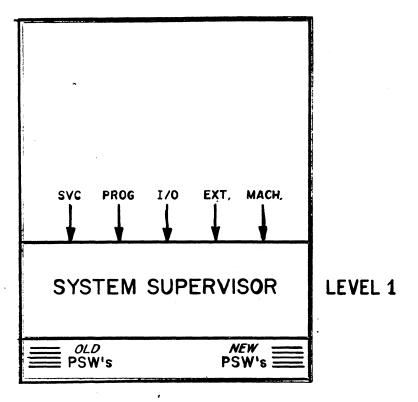

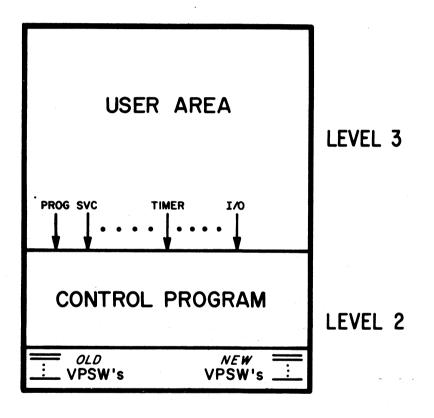

Like the traditional batch system, the heart of a "time-sharing" system is the supervisor. The normal functions of interrupt handling, physical IOCS, communication region, etc., are included in the "time-sharing" supervisor.

- Additional capability required in the supervisor for "time-sharing" is as follows:

- a) Terminal Access Method

- b) Command Language Interpreter

- c) Storage management

- i) Scheduler

- On-line libraries, providing "private" and "public" storage for programs are a must in "time-sharing" systems. Data storage is also required on-line.

- Language processors and application oriented programs are a necessity.

- 5. Utility routines are generally included for housekeeping functions in the "time-sharing" system. Source program update, library purge, and accounting information processing routines are typical utility routines required.

### C. Batch Compiler Implementation.

- One technique of developing a "time-sharing" system

is to use components originally developed for a batch

compiler system. A compiler, loader, basic supervisor, and library facility provide the framework and

are modified and extended for "time-sharing."

- BPS FORTRAN provided the basis for RAX. Many changes were required. Not the least of which was a change of residence from tape to disk.

- 3. The user creates a source language data set from the terminal. Each character of an input line is transmitted to a terminal buffer in core storage. At the end of the input line, the terminal buffer is transferred to the input source data set on auxiliary storage. Eventually, the complete source data set is processed by the batch compiler when the appropriate command is entered.

- 4. Diagnostic messages are returned to the terminal so that input source language can be corrected - assuming errors were detected. User then enters update mode to make changes to the source program. When the user finishes modifications, the changes are merged into the source input data set. The compiler is again invoked and the process is repeated.

## BATCH-COMPILER IMPLEMENTATION SHARING

- 5. When a compiler run is without serious errors, the program is loaded and executed. Execution is time-sliced. Each user who is ready to execute will get an increment of time. The time-slice can be a fixed length of time set by a sysgen parameter.

- 6. Note that interaction is relatively limited in the batch compiler implementation of "time-sharing." As each line is entered, there is generally no response from the system. The user is informed of detected errors only at the completion of the compilation.

- 7. A pre-processor can be added to perform certain analysis as each line is entered. This analysis is called line-by-line syntax checking. It basically examines the ordering or format of the input line. A good example of something that can be checked on an intra-line basis is a balanced number of parentheses.

- A line-by-line syntax check duplicates some compiler function. Global checking, that is the inter-statement consistency of the program, requires the compiler.

- 9. Adequate response from the batch-compiler timesharing system depends on the compiler performance. Speed, efficiency and minimum overhead are obviously required. The need for line-by-line syntax is negated if the compiler performance is high.

- 10. Program modification permits program changes without re-entering the entire program. Lines in error are generally completely re-entered in the batch-compiler system. More sophisticated editors permit "context editing" whereby only the item in error in the line is changed.

- 11. During program execution, conversational READ and WRITE from and to the terminal allow the user to interact. The running program can solicit input from the terminal with prompting messages.

- 12. Conversational READ and WRITE are basic requirements in order for the user to interact with a program during execution. Additional capability for user interaction can be added with a de-bug language for core "snap-shots"

13. The batch compiler produces object code. Program execution is direct without loss of speed. Given an assignment statement:

$$Y = A + B$$

The possible symbolic code is as follows:

LD 8, A AD 8, B STD 8, Y

- 14. The CALL/360: BASIC system is a compile-type time-sharing system. However, the compiler was specifically designed for the time-sharing environment. It may or may not reside "in-core" depending on the instantaneous load on the system.

- D. Interpretive Time-Sharing Implementation:

- One method of achieving a high degree of conversationality in a time-sharing system, is to employ an interpretive system for program creation and execution.

- 2. In the interpretive system, the source language is converted to an internal tabular form instead of being compiled to object code. The internal tabular form must then be "interpreted" to be executed.

- 3. Each statement or line of the source language is handled individually as entered. The program is compiled incrementally into the internal tabular form a statement at a time. Hence, the term "incremental compiler" is inherent to an interpretive system.

- 4. This mode of operation provides interaction on a line-by-line basis. The user will know immediately that a statement has been rejected or accepted since each statement is compiled individually.

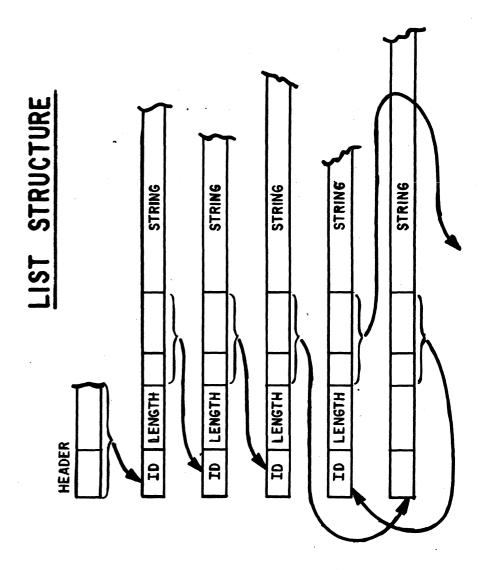

- 5. The internal form is generally a chained list structure. Each statement represents an element in the chain. The statements are chained together in statement number order. Since each statement points to the next one in the chain, variable length elements and changes to elements are accommodated easily.

- 6. Each element of the chain includes a control portion that contains the statement number or identity, the length of the element, the forward pointer to the next element, statement type, etc. In addition to the control information, the element contains the string representing the source language statement.

- 7. Generally, a form of Polish notation is used to represent the source language in the "string."

This string must be interpreted by an execution monitor in order to run the program. A discussion of Polish notation is included in the following section of the outline.

- 8. Since a program is executed interpretively by chaining through the statements of the program, it is possible to limit execution to a range of the total statements. The interpretive system provides "incremental execution" of the source program.

- A program can be partially executed, variables then displayed, and then execution continued. The nature of the interpretive system makes for a highly interactive mode of operation during both program creation and execution.

- 10. New statements are added and incorrect statements are replaced by simply adding or replacing elements in the chain. Except for changing the pointer in at least one statement, the remaining statements are unaffected. The complete program is not recompiled each time a change is made. Only the new or corrected statements are processed by the "incremental compiler."

- 11. The capability of incremental compilation and execution provides a valuable feature in interpretive systems called, "Desk Calculator" mode. The user can, in effect, write a one statement program that is immediately compiled and executed. Thus one-time slide rule or desk calculator type computations can be performed at the time-sharing terminal. This mode of operation must be distinguished from the normal program creation mode. A special character can be employed to indicate the mode desired.

- 12. The interactive advantages of the interpretive system are obvious. Unfortunately, the gain in conversationality is paid for in slower execution speed. Interpretive execution is not efficient when compared to object code performance.

- 13. This problem becomes acute with the "number cruncher" type job. There is one line of reasoning that says that "number crunchers" or "floating-point grinders" should not be run from the time-sharing terminal. Develop the program there, but run the production job in the traditional batch environment. Several approaches have been tried to improve execution speeds of the interpretive system.

- 14. Special hardware in the form of additional instructions to process the list structures is one approach to solving the performance problem. There is an RPQ for the Model 50 that will increase execution speed on the order of 20 to 30 per cent for CPS programs.

- 15. Another approach to increasing execution speed is to provide an option to compile object code from the internal tabular form. This technique was employed in QUIKTRAN2 to improve program execution performance. The following figures provide some relative guide to execution performance:

Interpretive Execution 200 statements/sec.

Compile from internal form to object code

Compile from source language to object code 20,000 statements/sec.

NOTE: These are execution speeds, not compilation speeds!

- 16. In the interpretive system, the program is generally retained only in the internal tabular form. The source language input is discarded when the internal form is compiled. In order to list a program, it is necessary to recompose the source language from the internal tabular form.

- 17. The recomposition capability provides an interesting possibility for interpretive systems. If multiple source language compilers are available to produce the same internal form, the recompcapability could be used to translate one source language, i.e., FORTRAN to PL/I or vise versa.

- 18. The first interpretive time-sharing system is credited to the Rand Corp. The system was called JOSS (Johnniac Open-Shop System) and provided an ALGOL dialect language called the JOSS language. QUIKTRAN, CPS, and APL are IBM interpretive time-sharing systems.

### E. What is Polish notation?

Polish notation is an alternate method of expressing the relationship between an operator (in this instance arithmetic) and the two operands (variables) which it binds. The notation that all of us are familiar with and the one used in the Fortran and PL/I languages is Infix. That is, the operator in question lies between its operands; thus: A + B is Infix notation whereas

AB + is one form of Polish notation

2. In Polish notation, if the operator lies to the right of its operand pair, then the form is called reverse or suffix Polish. However, sometimes a form of Polish called prefix Polish is used, in which case the operator is placed to the left of the operand pair that it binds; e.g.:

+ AB

3. Here are some examples of infix notation paired with the corresponding reverse Polish form:

| Infix                  | Polish        |

|------------------------|---------------|

| A + B - C              | AB+C-         |

| A + B x C              | ABC x +       |

| Z = A + B              | Z A B + =     |

| $Z = A \times B + C$   | Z A B x C + = |

| $Z = (A + B) \times C$ | Z A B + C x = |

- 4. The advantage of Polish notation over the more familiar infix notation lies in the fact that the order of the operators in the Polish string reflects the order in which these operators are to be executed. Consequently, in an interpretive mode of program execution only a single scan is needed to convert the Polish string into executable object code.

- 5. Operands, when encountered in the scan, are placed in a push down stack. When an operator is met, the two top most operands are accessed from the stack and combined with the operator. The temporary operand representing the result of the operation relative to the accessed operands is then placed back in the stack and the scan continues as before.

- 6. Polish notation was developed by the Polish mathematician J. Lukasewicz as a "normal form" for the representation of formulae in logic. The notation permits an unambiguous sequential specification of the order of evaluation of logical and arithmetic expressions without requiring the use of parentheses. For this reason it has been found useful as a normal form for computer oriented mathematical languages. The work by the above named mathematician was done in the 1920s in Warsaw on a broken typewriter, and thereby hangs a tale.

- 7. CPS uses reverse Polish notation to represent the PL/I statement in the "L" string.

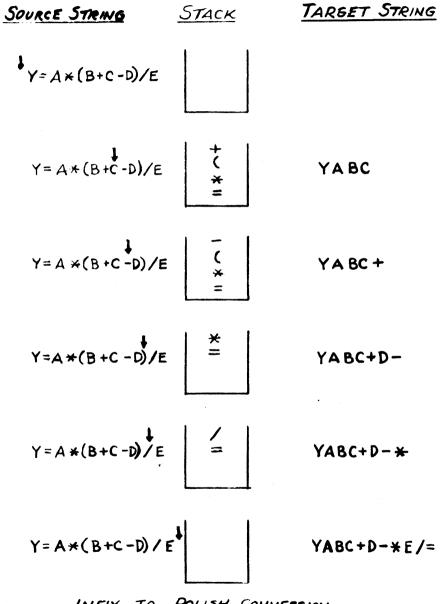

- 8. Converting from Infix to Polish Form

- a. The order of operands remains the same in both source and target string. A push down stack is used to permute the operators so that they occur in the target (Polish) string in the order in which they are to be used. This order reflects the precedence hierarchy given below.

| low precedence  | (   | when in the stack      |

|-----------------|-----|------------------------|

|                 | =   |                        |

| to              | + - |                        |

| •               | * / |                        |

| high precedence | (   | when outside the stack |

- b. The rules for manipulating the stack are as follows:

- 1. Source operands bypass the pushdown stack and enter the target string directly.

- If an operator in the source string has greater precedence than the

operator at the top of the stack, then enter the operator into the stack;

otherwise, remove the operator currently at the top of the stack, move

it to the target string and repeat this test.

- A left parenthesis always enters the stack and is assigned lowest precedence.

- 4. A right parenthesis always forces operators from the stack until a left parenthesis is encountered.

- The attached page contains an example which shows the intermediate steps in forming a Polish string.

- 9. Converting from Polish Form to Object Code

- a. Rules

- An operand, when encountered in the scan of the Polish string is entered into a pushdown stack.

- When an operator is met, the two topmost operands are accessed from the stack.

- 3. Object code with a temporary operand is outputted.

- 4. The temporary operand is placed in the stack.

- Conversion of a Polish string to object code is illustrated on a following page.

### 10. Summary

- a. The order of operators in a Polish string reflects the order in which these operations are to be executed. It is for this reason that the original infix form of the arithmetic statement is converted to Polish notation for the L string.

- b. This conversion from infix to Polish form is done only once, namely by the incremental compiler at the time the L string is formed.

- c. The subsequent scan of the Polish string to produce object code is done each time the original arithmetic statement is to be executed. However, this scan is relatively fast because of the ordering of the operators within the string.

INFIX TO POLISH CONVERSION

| POLISH STRING      | SMCK              | OBJECT CODE |

|--------------------|-------------------|-------------|

| 1<br>YABC+D-4E/=   |                   |             |

| YABC+D-#E/=        | S<br>B<br>A<br>Y  |             |

| ¥<br>YABC+D-¥E/=   | Ţ' <b>\</b>       | TI - B+C    |

| <b>YABC+D-+E/=</b> | D<br>TI<br>A<br>Y |             |

| YABC+D-+E/=        | T2<br>A<br>Y      | T2 = TI-D   |

| YABC+D-# E/=       | T3<br>Y           | T3 = A* T2  |

| YABC+D-*E/=        | E<br>T3<br>Y      |             |

| YABC+D-*E/=        | T4<br>Y           | T4 = T3/E   |

| YABC+D-*E/=        |                   | Y= T4       |

- F. Storage Management in Time-Sharing Systems:

- Storage management is a fundamental consideration in the implementation

of time-sharing systems. As in any multi-programming environment,

storage allocation and management techniques are critical design

factors determining the number of users, system response, and

system thruput.

- 2. One can conceive of unlimited main core storage in a time-sharing system that would permit all users to reside in-core at all times. This "infinite" size one-level store would accommodate programs of any size for each user. If this main storage were combined with an infinitely fast CPU, then the users could be serviced instantaneously. An "ideal" time-sharing system would be the result.

- 3. Of course, in practice the "ideal" time-sharing system does not exist and various techniques attempt to simulate this "ideal" system. The techniques of main storage management can be classified as follows:

- a) Segmented-core-resident

- b) Swapping or Roll-in/Roll-out

- c) Paging

- 4. In segmented -core-resident storage management, core storage is divided into blocks. These blocks are assigned to users as required from the pool of blocks made available when main core was segmented. A user retains those blocks assigned to him as long as he is logged-on at the terminal. When he logs-off, the blocks are put back into the pool for subsequent use by others. Note that for a given user, the program (s) and data remain in the same blocks of core storage. They are not swapped-out to a second level storage device while another user's program is swapped-in.

- 5. The advantages of the segmented-core-resident system are obvious. It is the closest approach to the "ideal" system cited above. System overhead is minimized since users' programs are not swapped between time-slices. It is not necessary to wait for one program to be rolled-out before another can be rolled-in for execution. Where programs remain in storage, there is no contention for channel time and storage access cycles.

- Since the segmented -core-resident system uses standard size blocks, it is impossible to have pieces of non-contiguous storage wasted because they are too small.

## SEGMENTED—CORE—RESIDENT SYSTEM

- 7. One disadvantage of this method of storage management is the large core necessary to implement this technique. LCS is required in order to put a number of users in core and keep them there. Even so, this implementation strategy limits program size to the maximum number of blocks allowed each user.

- 8. From a practical standpoint, only the interpretive type system, using list processing techniques can effectively use the non-contiguous set of blocks that a user would acquire in the fragmented system. CPS is an example of the segmented -coreresident storage management method. The CPS Monitor program and the user blocks make up a partition of MFT or a region of MVT.

- 9. The most common method for storage management in time-sharing systems is some form of swapping. Program swapping or roll-out/roll-in is the technique whereby a user program, User A for instance, at the end of its time slice is written out to an auxiliary storage device. The necessary registers, etc., are saved and written out with the program. Another program, User B, is then read from the auxiliary storage into core storage. When the loading is complete, User B's program is executed. At the next end of time slice, Program B is in turn swapped with the next program in the ready queue, User C for instance.

- 10. Swapping techniques can use one or more partitions for swapping. In the single partition swap, the CPU will have to "wait" while one program is rolled-out and the next is rolled-in. In this serial approach, necessary with one partition, the CPU will be waiting 30 35 per cent of the time. Of course, the single partition swap requires the least amount of memory to implement time-sharing.

- 11. Multiple partitions permit several user programs to be on their way in or their way out to auxiliary storage at the same time.

Hence, roll-out/roll-in is overlapped with execution. The more partitions, the more likelihood that the CPU will be executing a users program. Of course, the more partitions there are, the greater the core requirement. The housekeeping and overhead are also greater because of the complexity of multiple partitions.

- 12. A slight variation of the single partition swap is the so-called "onionskin" approach. In this technique, only enough of the first program is rolled out to accommodate the next program in the queue. Program A is "peeled back" just enough to make room for program B. If program C is greater than B, additional "peeling" will be required to accommodate C. The CTSS system at MIT uses the onionskin approach.

- 13. It is relatively easy to relocate a program when it is initially loaded before execution begins. It is another matter to relocate a program that has been partially executed during a previous time slice. Consider the program that came to time-slice-end when a base register had just been loaded. If this program is saved and properly re-loaded to the same storage locations, the program can be re-started without problem. However, to move this program to another partition or set of locations introduces some real complications--in base addressing, adcon resolution, etc. Dynamic relocation generally requires some hardware assist such as a relocation register to adjust addresses by the relocation constant. It is possible to relocate dynamically by programming if the user programs adhere to very strict, perhaps intolerable, programming conventions.

- 14. In the single-partition swap, all programs are loaded into the same starting locations. Hence, dynamic relocation is not necessary. Dynamic relocation is also not necessary in the multiple-partition swap if the programs are always rolled in to the same partition on each time slice. Interpretive-type systems using list structures can be easily relocated to different swapping partitions since address-dependent information is either relative or nonexistent.

- 15. The problem of "Who's minding the store?" extends to auxiliary storage also. Space for swapping, program libraries, scratch-work areas, check point, and data file areas must be allocated on the direct-access storage units of the time-sharing system.

- 16. Rolling out a program is essentially a check point operation. Certain status information must be saved and written out with the program. Contents of the general registers, floating-point registers, PSWs, etc., are obviously required for the next time-slice. The simplest approach is to allocate enough direct-access storage for each user to accommodate the saved status information plus the entire swapping partition.

- 17. RAX uses this straightforward approach in rolling out its single swap partition. A 2311 cylinder is used for each user-swap area. A simple count of available cylinders is incremented and decremented as user programs are rolled in and rolled out.

- 18. APL uses a sophisticated extension of the above approach in swapping a "work space." Only that portion of the "work space" that is occupied is actually written to disk, thereby reducing I/O time and space required on the disk. The swapped areas are no longer fixed-size blocks. Thus, allocation and management of auxiliary storage space becomes more complex as variable length blocks are accommodated.

- 19. It should be noted that the complete program is rolled out at the end of time slice and rolled in before the next time slice started. No matter how much of the code is actually executed during a time slice, all of it is written out and subsequently read in. Obviously, a great deal of code, especially exception routines, is repeatedly moved in and out but never executed. This characteristic of swapping contributes to the overhead and degrades performance. Time-sharing architects developed new techniques in second generation systems to eliminate or reduce the swapping of unnecessary code. Paging or page-turning is a refined storage management technique intended to improve program swapping time. Programs are developed in fixed-size blocks called pages. Only those pages actually required or demanded are placed in core storage during a time slice. At time-slice end only changed pages need be written to auxiliary storage device. The subject of paging and virtual memory is treated in a following section.

- G. Paging--An Advanced Storage Management Technique

- 1. In a multiprogramming environment a job step generally is constrained to execute in a contiguous area of core storage. This area of core may be static and hence used sequentially by a succession of jobs. On the other hand, the areas may be dynamic in that its fences come down after completion of the job step in order to release the core used. The static area of core is called a partition and is representative of multiprogramming under DOS or OS-MFT. In contrast, the region concept of OS-MVT represents a more general approach to storage management. A job step is allowed to specify its core requirement on a control card. The operating system will then attempt to satisfy this request from its pool of unassigned core. However, in both the partition and region approach, all core requests made by the job step during execution must be satisfied from the partition or region. Both region and partition, to repeat, represent contiguous areas of core storage.

- When a time-sharing subsystem uses an existing operating system which handles the multiprogramming by either a partition or region approach, the time-sharing tasks roll out from and roll back into an assigned partition or region. Furthermore, a module of code which is rolled out of some core area prior to completion of execution must be rolled back into its original core locations. This is the essence of static relocation. In contrast, dynamic relocation implies the freedom of the system to move code which has not completed execution to another set of core locations before allowing execution to resume. To do this without restriction extra hardware is required.

3. Consider the following example:

| loc | Instruction   |

|-----|---------------|

| 100 | L 15, X' 108' |

| 104 | BALR 14, 15   |

| 108 | DC A (700)    |

This program loads register 15 with the address constant 700 at location 108 and then branches to location 700 within the program. If this code is moved unaltered elsewhere we have, say:

| loc  | Instruction   |

|------|---------------|

| 1500 | L 15, X' 108' |

| 1504 | BALR 14, 15   |

| 1508 | DC A(700)     |

In order for the relocated program to execute properly, the instruction at location 1500 must generate address 1508 and the instruction at 1504 must cause a branch to location 2100 to take place. This can be accomplished by introducing a single hardware register. The content of this relocation register is added to core addresses generated during instruction executions. It is these relocated core addresses that are sent to the address register. In our example the relocation register should contain, obviously, 1400.

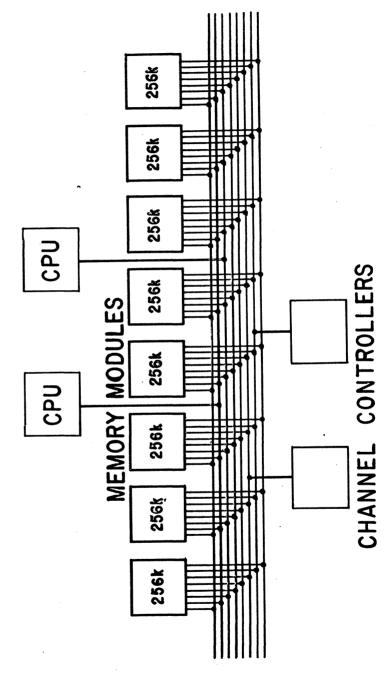

It has long been thought that to support a large general purpose timesharing system, a less restrictive method of managing core is necessary. Partitioned core, together with the absence of a dynamic relocation facility, imposes many system constraints. In the following allocation scheme real core is divided into standard-size units called blocks, whose size depends upon system architecture and software design considerations. A given program can occupy several core blocks. These need not be contiguous. Any available blocks may be assigned to a program. Moreover, if a core block is assigned to a section of a program, it is only because that section is actually referenced during program execution. This program section to which a block can be assigned is called a page. Page size and block size are the same. A page is referenced by execution of an RX, RS, or SS type instruction or by the instruction address in the PSW. If the referenced page already has a core block assigned, instruction execution continues to completion. Otherwise an interrupt occurs, and the supervisor assigns a core block to the offending page within the program. Note that no unreferenced page can have a core block assigned to it. Consequently, only the active portions of a program will take up core.

- 5. With this introduction let us take another tack. Often a programmer is forced to code an application in two phases. In phase one he constructs an algorithm to implement the application. In phase two he faces up to the fact that there is not sufficient core to execute his algorithm. That is to say, the programmer structures the application as an overlay module. Inasmuch as phase two coding is concerned with implementing a strategy to execute the algorithm, it is evidently desirable to relieve the programmer of this burden and place it on the system.

- 6. This was first done on the ATLAS machine produced in 1961 by Ferranti Ltd. in England. In this machine a program was spread out over core and drum. During execution the program, of course, referenced code not yet in core, hence an interrupt occurred. The page containing the referenced item was assigned a block of core by the supervisor, and the contents of that page was read from the drum into the newly assigned block. When I/O was complete, the program was again given control, and the instruction that caused the interrupt was re-executed. All of this was entirely transparent to the programmer. He merely assumes that he always has as much core as he needs for his application and hence can dispense with creation of an overlay program structure.

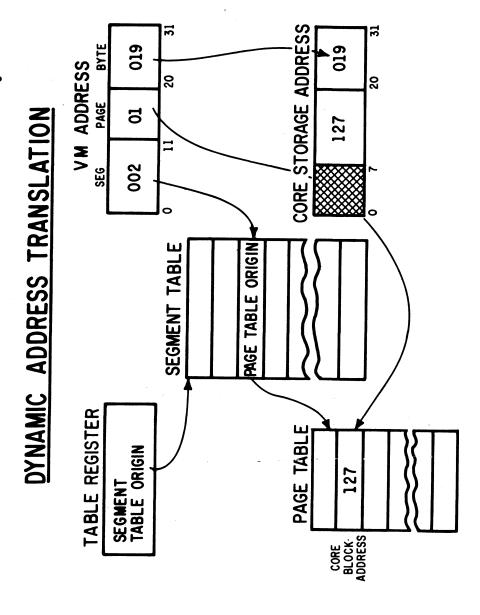

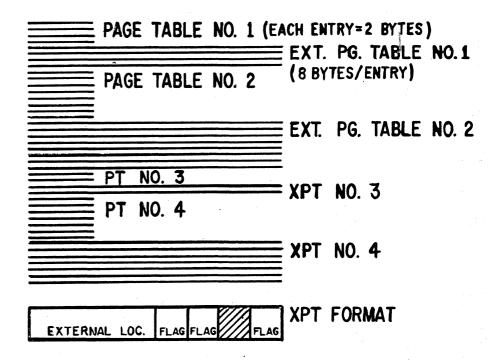

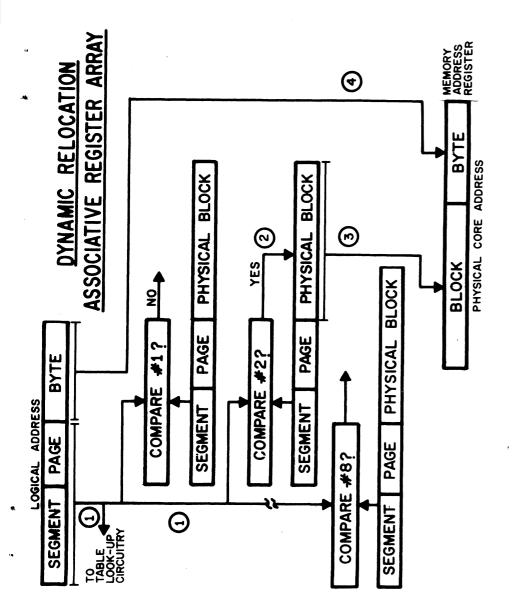

- The key to implementing such a scheme is recognition that a core address represents two things: First, it represents the unique name of some data item; and secondly, it also represents the core location of the said item. The thought occurs of splitting apart these attributes. Let what is ordinarily the address now represent only the name of the data. Using this name as an argument, do a table look-up to determine the location of the data. Thus, we now have the concept of a set of names whose range is dependent only on the addressing capability of the hardware. In contrast, the set of core locations has a range determined by the amount of core possessed by the system. Inasmuch as System/360 works with a 24 bit effective address, names can range from 0 to 2<sup>24</sup>-1=16 million, whereas core locations range from 0 to typically 512K or lM, depending upon how much core the machine possesses. The programmer codes within this name space of 16 million bytes and so can dispense with overlays. The memory corresponding to these names is nonexistent. This conceptual memory within which the programmer works is called a virtual memory. Only its addresses are real. These addresses are generated in the usual fashion by adding a 12-bit displacement to the contents of the base register. However, this virtual memory address provides an argument for a table look-up to determine the corresponding real core address, if any. If the translation (look-up) process indicates that the referenced item is not in core, an interrupt occurs. The supervisor assigns a core block to the virtual memory page containing the referenced item. Then an I/O operation is initiated to read the page contents (on drum or disk) into the assigned core block. One can think of a typical translation table entry as

consisting of the following fields:

Virtual Memory Page Address A F B

A Core block address

F Flag

Off--core block address is valid

On--core block address is invalid

(i.e., no block is assigned)

B External page address =

Device address and relative

page number within the device

Upon completion of the read operation the program is eligible to resume execution. The instruction which caused the original interrupt is reexecuted.

8. Note that this method of memory management allows a program to execute within core blocks which are scattered throughout memory. Any available core block is eligible for assignment to any program. Moreover, if a page is assigned at one time to some core block, later during execution (say during a subsequent time slice) it is not necessary for that page to be assigned to the same core block.

Thus, this fragmented approach to storage management offers dynamic relocation. There is an obvious penalty in implementing this scheme, and that is the increased instruction execution time resulting from the need to translate the page address to the core block address. However, typically extra hardware is introduced to minimize this overhead. Finally, let it be emphasized that a virtual memory is unique to each user. That is to say the system keeps a separate translation table for each task in the system. Depending upon system architecture, the translation may be accomplished completely by means of hardware registers or by use of tables in core at time of use, together with associative hardware to decrease most translation times.

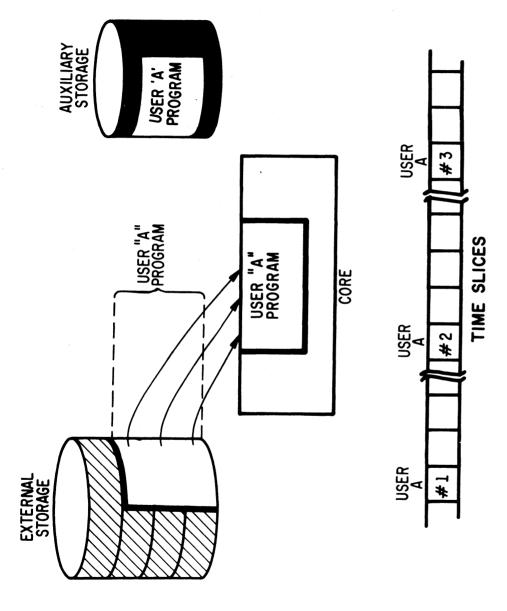

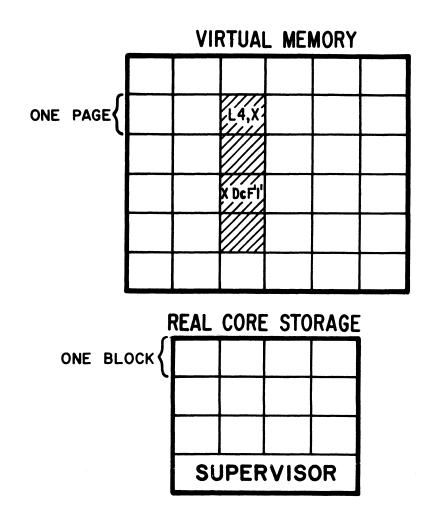

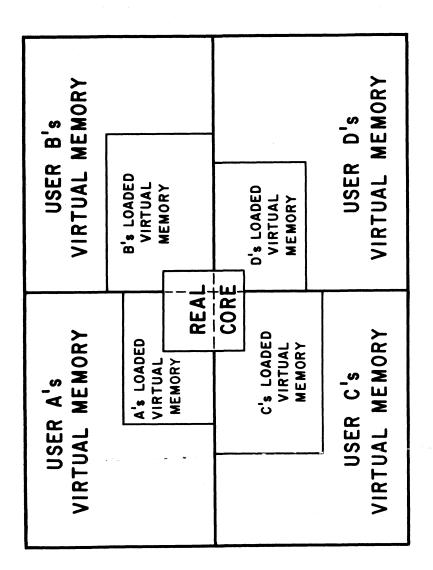

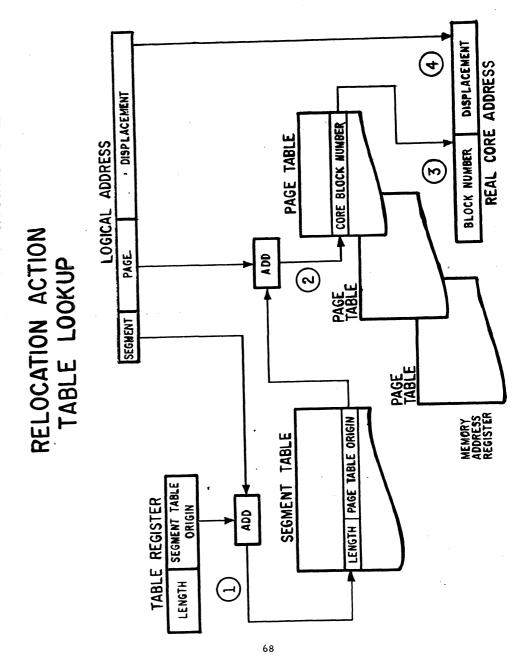

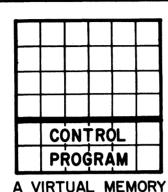

Consider the following with reference to Figures 1, 2, 3, and 4. Figure 1 illustrates the situation extant after a programmer has caused a four-page program to be "loaded" into his virtual memory. Since program execution has not yet commenced, no portion of the program has been mapped into core storage. "Loading" the program into virtual memory involves essentially making entries in the user's translation table. These entries relate the addresses of the "loaded" virtual memory pages to addresses of program pages in some library on a direct access device.

1. LOADED VIRTUAL MEMORY - NO REAL CORE BLOCKS ASSIGNED

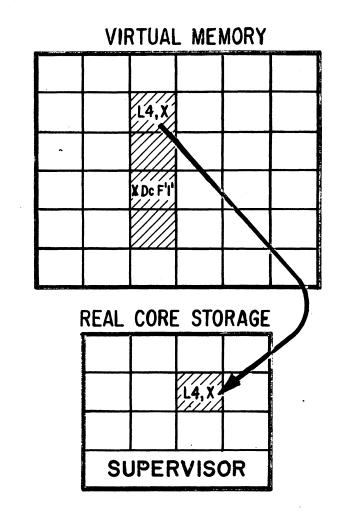

2. LOADED VIRTUAL MEMORY — ONE REAL CORE BLOCK ASSIGNED

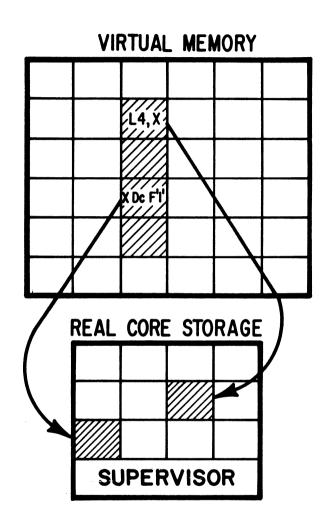

3. LOADED VIRTUAL MEMORY - TWO REAL CORE BLOCKS ASSIGNED

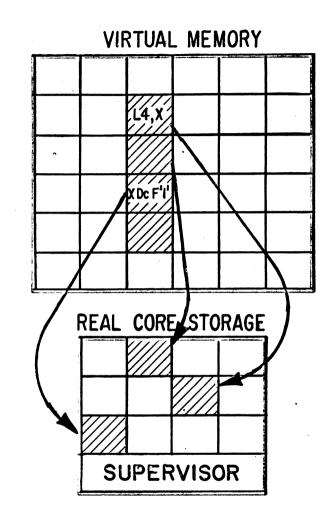

4. LOADED VIRTUAL MEMORY—THREE CORE BLOCKS ASSIGNED

4 l

In Figure 2 program execution has commenced. In the time span between the snapshot represented by Figure 1 and that of Figure 2, the system has assigned a core block to the initial virtual memory page. The content of that page is read into the assigned core block. Note that during execution within this page there is a reference to data item X located in another page--one to which no core block has been assigned.

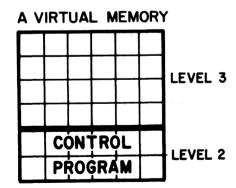

Figure 3 illustrates the correspondence between virtual memory pages and core blocks as a result of execution of the L 4, X instruction in the first page. In the process of translating the virtual memory address corresponding to the symbol X, the hardware was signaled that no block had been assigned to the page containing the data item X. The resulting interrupt caused control of the system to pass to the supervisor. The supervisor assigned a core block to the "offending" virtual memory page and caused its content to be read into this block.

Figure 4 indicates that another block has been assigned to a page in virtual memory. This assignment, for example, could have been triggered by the instruction counter stepping across the boundary from Page 1 to Page 2 in virtual memory. Dynamic address translation of the instruction address would generate an interrupt to the supervisor. Note that Page 5 in virtual memory, although a part of the program under execution, does not have core block assigned to it. If during program execution no reference is ever made to this page, no block will be assigned at all.

10. The above discussion makes reference to a "loaded" virtual memory. Since a virtual memory is one which the user has but the real system does not, some remarks about "loading" a program module into something purely conceptual are in order.

A program module to be loaded into virtual memory is located at load time in some library on direct access storage. The loader of virtual memory causes the module to be loaded by making entries in the translation tables which exist for the user and his virtual memory. The loader allocates a set of virtual memory addresses as yet unassigned and assigns these to the module. Table entries are made to relate these allocated virtual memory addresses to the symbolic device address and relative page numbers used by the module on direct access storage. No text ever moves.

Note that the loading of information into virtual memory is independent of the contents of real core memory. Indeed, only the paging mechanism of the system will cause a real core block to be assigned to a loaded virtual memory page.

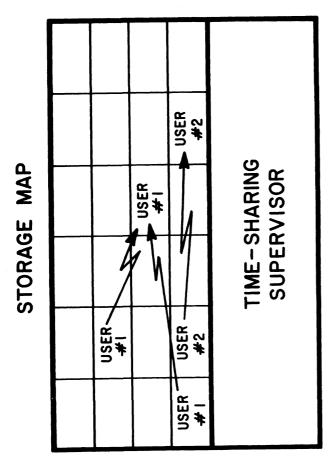

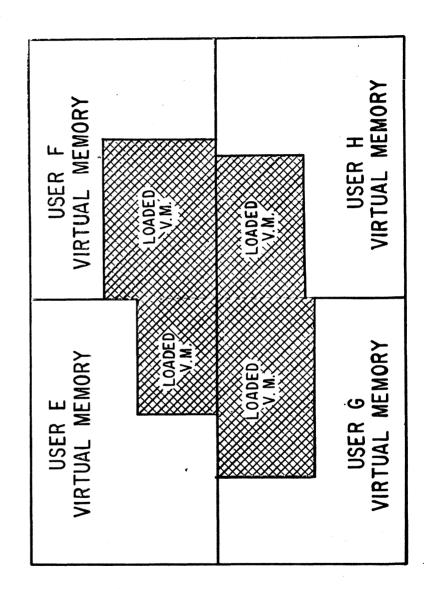

The two accompanying figures each illustrate four users with loaded virtual memories. In one case none of these users have real core blocks assigned to the loaded portion of their virtual memories. In the other illustration each user has a portion of his loaded virtual memory mapped into real core.

### H. Scheduling Techniques in Time-sharing Systems

- "Who gets the CPU and for how long?" is the question addressed by the scheduler. In managing this important resource, the scheduler is an integral part of the time-sharing supervisor. It plays the role of time-keeper, dispatcher, and housekeeper. Scheduler designs can range from a very simple, straightforward approach to very complex algorithms to multiplex user programs. The purpose of this section is to provide an understanding of this range of scheduling techniques. Its activity affects response and performance and is a key consideration in the design of the system.

- 2. In a non multi-programming system the CPU scheduling problem does not exist. There is only a single program in the user area of storage, and this program is to run to completion prior to starting the next program. Even in a multiprogrammed batch operating system, scheduling the CPU is relatively minor in nature and is usually referred to as task switching. In this latter case the supervisor contains a task switching routine. This routine is entered when the supervisor has completed all the processing it can do as the result of some interrupt. Task switching passes control of the CPU to the highest priority ready task. In many instances determination of this task can be made by comparing the dispatching priority of the task which was last in execution with the priority of the task causing the interrupt. At worst only a partial scan of the chain of task control blocks is necessary.

In contrast, scheduling the CPU in a time-sharing system is accomplished in many ways--some simple, others highly sophisticated. Some of these scheduling algorithms are discussed in the following paragraphs.

### 3. Simple Round Robin

This method is the most straightforward. All tasks are served on a first-come-first-served basis and are ordered in a single queue. Whenever a task reaches time slice end, its dispatching priority is lowered by one, and those of all the tasks are raised by one. Note that these contending tasks could be core resident or using storage on a roll-in, roll-out basis. CPS tasks, for example, are core resident and use the terminal line number instead of an internal priority as an ordering device for its queue. The queue consists of commutator bytes, one for each terminal line in the system. The dispatcher scans the queue in circular fashion. If a

8 8 8 9 SE 100 SE 8 90 **E** 8 SE 9 B SLICE OPERATION CYCLE TIME SE 90 E USER 001 SE 90 SE 00 SE

given commutator byte indicates that the associated task is either not logged on or is in head-scratching mode, then it is by-passed, and the scan continues in its search for a task with processing requirements.

In this category of CPU scheduling algorithms, the time slice value may be fixed or may be supplanted by a function work slice. In a work slice approach, a task is allowed to hold the CPU, if possible, until a compilation is completed or in the case of interpretive systems, until a fixed number of statements have been executed.

TSS uses a variant of round robin with variable quanta. However, this will be treated separately.

### 4. Multi-queued Exponential Scheduling

In this scheme used by MIT in their CTS System, a given task is in one of several queues. Each queue has an assigned priority (level number.) Choice of an initial queue for any task is dependent on the core requirements of that task. The less core required, the higher the priority of the queue to which it is assigned. All tasks are handled FIFO within a queue. No queue is serviced unless all higher priority queues are empty. Whenever a task makes a terminal I/O request, it is placed at the end of the highest priority queue. But if a task is in hard execution at the end of time slice, then it is placed at the end of the next lower priority queue. Finally, let Q represent the time slice value associated with the highest priority queue. Successively lower priority queues are assigned time slice values of 2Q. 4Q, 8Q, 16 Q .... This scheme favors small short running programs typical of a student environment. "Grinder" type jobs progress to successively lower priority queues, but once getting the CPU, they receive longer and longer time slices. In the MIT CTS System, storage is managed in a roll in-roll out basis.

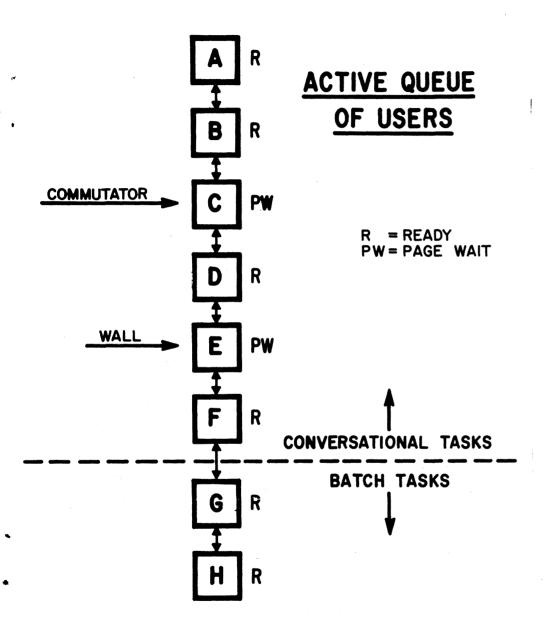

### 5. Modified Round Robin with Variable Quanta

This system is used by IBM Model 67 TSS to schedule virtual memory resident tasks for the CPU. Task control blocks representing users belong to one of two queues. Those tasks in the Inactive Queue are those waiting for a response from the terminal. This type response is measured in seconds or longer. Such tasks have previously been paged out of core storage and even from the paging drum to a slower direct access device. The scheduler (task dispatcher) never searches this queue of dormant tasks. Instead, it confines itself to a subset of tasks in the Active Queue. This subset of tasks in the active queue lies between two pointers, the Commutator, and the wall, as illustrated in the accompanying figure.

Those tasks above the Commutator are ready for their next time slice. Those below the Wall are ready for their current time slice. The tasks between the Commutator and the Wall pointers are currently undergoing their time slice. Their referenced virtual memory pages have been assigned core blocks, to be held until end of time slice. These are the tasks currently being multiprogrammed. The scheduler scans the tasks between the Commutator and the Wall (i.e. scans the tasks "in the Wall") and gives the CPU to the first ready task encountered. If no task in the wall is ready, then the wall pointer is moved down to include a new task. At this time, the translation tables for this task are paged in by the dispatcher.

When a task in the wall comes to time slice end, it is so flagged and hence will no longer be considered for CPU control. When the task pointed to by the Commutator reaches time slice end, the Commutator moves down the active queue. It stops when it finds a task is Ready or Page Wait status. Intervening tasks in Time Slice End status are passed by and reset to Ready. Thus, effectively all tasks in the active queue are treated in round robin fashion. Those tasks in the Inactive Queue which receive a terminal response are moved back to the Active Queue. They are flagged "Ready" and placed just below the Wall pointer.

6.

There is a refinement of the above scheduling algorithm which reflects the use of demand paging as the basis of storage management. It is evident that the ability of a task to hold the CPU improves steadily during its time slice, i. e. during the period of time the task resides in the wall. Each page exception causes another core block to be assigned to the offending virtual memory page within the task's virtual memory. Unfortunately, at time slice end just when the task has accumulated a number of core blocks, these core blocks must be given up. Unchanged pages are immediately made available for assignment to other tasks. Changed pages are scheduled for writing to paging drum or disk then freed for use by other tasks. In an attempt to keep the entire system in balance, the following decision is made whenever a task reaches time slice end. If the paging time during the time slice exceeds the CPU time accumulated during the time slice (this latter is the time slice value), then the task is flagged ready, hence stays within the wall and receives another time slice. Thus the task does not relinquish its assigned core blocks. It continues to accumulate them as paging exceptions occur during the extended time. Additional time slice values called quanta are made available to this task. However, for each N additional quanta obtained while in the wall, tasks are penalized by being flagged

Time Slice End the next N times they are included in the wall. Thus, in the long run any task averages a single quantum per . time slice. The maximum number of successive quanta allowed any task is set as a system parameter.

7. IBM Model 67 TSS makes provision for servicing background (batch) tasks as well as time-shared tasks. Batch tasks are represented by task control blocks at the end of the Active Queue. When the wall pointer has reached the last time-shared task, a decision must be made whether to return the wall pointer to the top of the Active Queue or allow it to include tasks to be run in batch mode. This decision is made on the basis of the operational cycle time set as a system parameter. If this time, typically two or three seconds, has not been exceeded, then a batch task is included in the wall. Otherwise the wall moves immediately to the top of the Active Queue and no batch task receives a time slice this operational cycle time.

### 8. Table Driven Schedulers

It is difficult to find two people with the same philosophy of CPU scheduling in a time sharing environment. This arises, in part, because the subject is not yet well understood. As yet, there is a paucity of practical experience with large scale time-sharing systems. In any event, there is ever present the desire of most installations to tailor the algorithm to their job profile or at least to adjust it according to the dynamic work load on the system.

In spite of the parameterization of key variables, such as length of time slice, maximum number of quanta per time slice, operational cycle time, etc., flexibility of CPU scheduling has been very difficult to achieve. The most flexible method of implementing a scheduler-dispatcher is to have the behavior of every task dependent upon entries stored in a table. These entries can be easily changed, perhaps even dynamically, in response to a changing environment.

In one such system, each row in the table contains all the parameters necessary to control the behavior of any task. Each task with processing requirements is queued relative to a single row in the table. All tasks in one such queue have the same priority. They are ordered within the queue by their scheduled start time for their next time slice. The accompanying illustration shows a hypothetical table and suggests entries relevant to CPU Scheduling. Notice that on the basis of parameters stored in a given row (level number) a task may be subsequently queued on the same or on a different row. Thus, over a terminal session a task may be scheduled in a variety of ways. A single table can easily accomodate, for instance,

| TWAIT Level Max. Pages | 100%  | 25%     | 25%     | 25%     | 20%      | 20%     | 20%                                     |  |

|------------------------|-------|---------|---------|---------|----------|---------|-----------------------------------------|--|

| TWAIT Level            | 0     | 0       | 2       | m       | ٥        | 9       | 9                                       |  |

| TSE Level              | 1     | 1       | 2       | °,      | )<br>)=  | 11      | ======================================= |  |

| DTR                    | 0 ms  | 3400 ms | 4200 ms | 4200 ms | 5000 ms  | 9000 ms | 6800 ms                                 |  |

| T/S                    | 50 ms | 100 ms  | 100 ms  | 100 ms  | 100 ms   | 100 ms  | 100 ms                                  |  |

| a                      |       | 10      | 10      | . 3     | ر ع      | 32      | 64                                      |  |

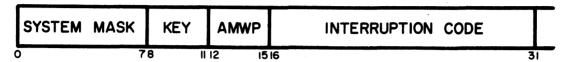

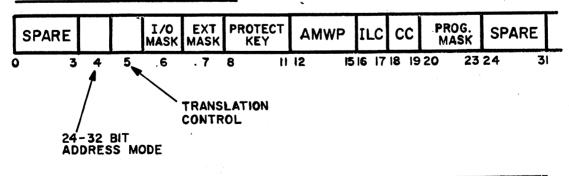

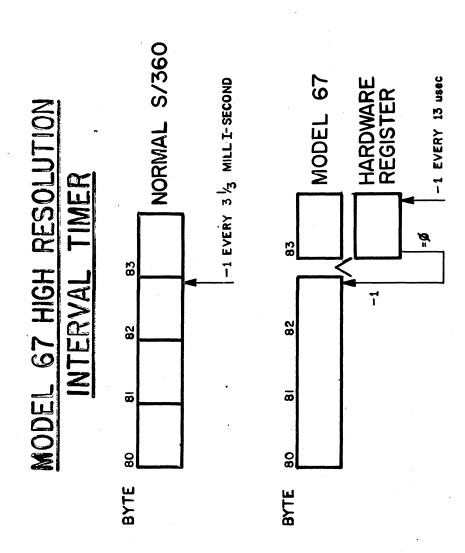

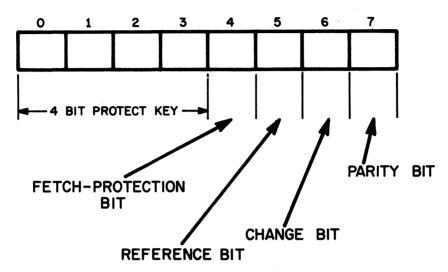

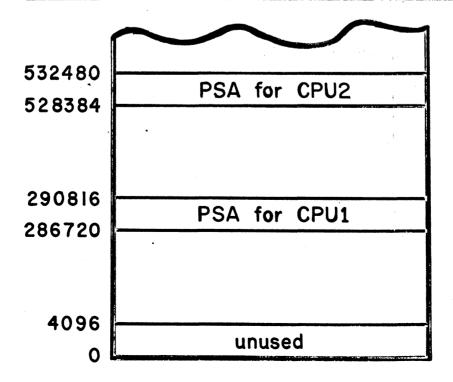

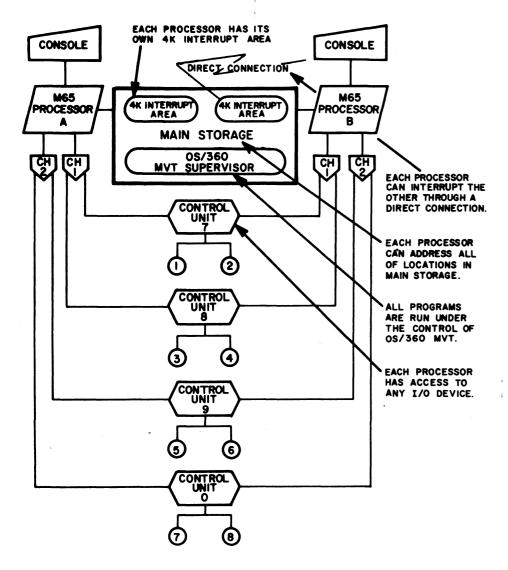

| ۵l                     | 0     | 0       | 1       | 7       | <b>)</b> | 6       | 10                                      |  |