File No. 9020-01 Form A27-2734-2 Contract No. FA64WA-5223

# IBM Systems Reference Library

This manual is a comprehensive presentation of the characteristics, functions, and features of the IBM 9020 D/E System.

The manual defines 9020 D/E System operating principles, computing and Input/Output Control elements, instructions, System control and monitoring facilities, branching, status switching, interruption system, and input/output operations.

Descriptions of specific input/output devices used within the 9020 D/E System appear in separate publications.

For additional information concerning units attached to the 9020D or 9020E, reference should be made to specific interface control documents.

This information is furnished in accordance with the requirements of contract FA64WA-5223, and is subject to clause 24 thereof entitled Reproduction and use of Technical Data, which provides for its use, reproduction or disclosure by the government for governmental purposes.

This publication, form number A27-2734-2, obsoletes the previous version of the manual, form number A27-2734-1, and incorporates information contained in the following Technical Newsletters:

| N27-2937  | July 28, 1969     |

|-----------|-------------------|

| GN27-2942 | November 13, 1970 |

This major revision to the publication includes the attachment of the Direct Access Storage Facility.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer with a 120-character chain containing upper and lower case letters, special characters, and numerals.

Address comments concerning the contents of this publication to: IBM Corporation, Federal Systems Division, FAA Project Office, 18100 Frederick Pike, Gaithersburg, Maryland 20760

JANUARY 31, 1973

TNL: GN31-3005

Table of Contents

| CHAPTER 1: INTRODUCTION TO 9020D/E SYSTEMS   | 1        |

|----------------------------------------------|----------|

| 1.1 INTRODUCTION                             | 1        |

| 1.1 INTRODUCTION                             | 1        |

| 1.1.2 9020E SYSTEM                           |          |

| 1.2 COMPATIBILITY                            | 2        |

| 1.2.1 SYSTEM/360 COMPATIBILITY               |          |

| 1.2.2 9020A COMPATIBILITY                    | 3        |

|                                              | 3        |

|                                              | 3        |

| 1.5 DISPLAY ELEMENT                          |          |

| 1.6 SYSTEM CONSOLE AND CONFIGURATION CONSOLE |          |

| 1.6.1 9020D SYSTEM CONSOLE                   |          |

| 1.6.2 9020E CONFIGURATION CONSOLE            | +        |

| 1.6.2 9020E CONFIGURATION CONSOLE            |          |

| 1.7 INPUT/OUTPUT CONTROL ELEMENT             |          |

|                                              | S        |

| 1.9 TAPE CONTROL UNIT                        | ò        |

| 1.10 STORAGE CONTROL UNIT                    | 6        |

| 1.11       DATA ADAPTER UNIT                 | б        |

| 1.12 SYSTEM ALERTS                           | 6        |

|                                              |          |

| CHAPTER 2: SYSTEM STRUCTURE                  | 8        |

| 2.1 MAIN STORAGE                             | 8        |

| 2.1 MAIN STORAGE                             | 1        |

| 2.1.2 ADDRESSING $1.1.1$                     | 1        |

| 2.1.3 INFORMATION POSITIONING                | 2        |

| 2.2 DISPLAY ELEMENT                          | 3        |

| 2.2 DISPLAY ELEMENT                          | 3        |

| 2.2.2 ADDRESSING                             | 3        |

| 2.3 COMPUTING ELEMENT                        | 4        |

| 2.3 COMPUTING ELEMENT                        | 5        |

| 2.3.2 FLOATING-POINT REGISTERS               | 5        |

| 2.4 ARITHMETIC AND LOGICAL UNIT              | 6        |

| 2.4.1 FIXED-POINT ARITHMETIC                 | ĥ        |

|                                              | 7        |

| 2.4.2 DECIMAL ARITHMETIC                     | <u>,</u> |

| 2.4.4 LOGICAL OPERATION                      | o<br>o   |

| 2.5 PROGRAM EXECUTION                        | 2        |

| 2.5.1 INSTRUCTION FORMAT                     |          |

|                                              |          |

| 2.5.2 ADDRESS GENERATION                     | 5<br>6   |

| 2.5.4 BRANCHING                              | с<br>С   |

| 2.5.4 BRANCHING                              | ð<br>7-  |

| 2.5.5 PROGRAM STATUS WORD                    | /•       |

| 2.5.6 INTERRUPTIONS                          | 8        |

| 2.5.6.1 Input/Output Interruption            | •        |

| 2.5.6.2 Program Interruption                 | 0        |

| 2.5.6.3 Supervisor Call Interruption         | 0        |

| 2.5.6.4 External Interruption                | 0        |

| 2.5.6.5 Machine Check Interruption           | 1        |

| 2.5.6.6 Priority of Interruption             |          |

| 2.5.6.7 Program States                       | 2        |

| 2.6 PROTECTION                               | 3        |

| 2.7 TIMER                                    | 3        |

| 2.8 DIRECT CONTROL                           | 4        |

| 2.9 MULTIPROCESSOR OPERATION                 | 4        |

| 2.9.1 COMPUTING ELEMENT                      | 4        |

| 2.9.2 IOCE-PROCESSOR OPERATION               | 4        |

| 2.10 DISPLAY PROCESSOR OPERATION             | 5        |

| 2.10.1 COMPUTING ELEMENT                     | 5        |

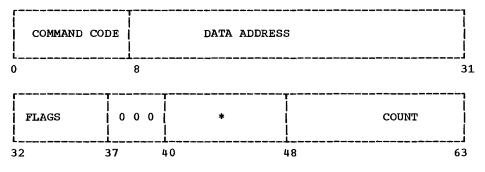

| 2.11 INPUT/OUTPUT                            | 5        |

JANUARY 31, 1973

Table of Contents, Cont.

| 2.11.1 INPUT/OUTPUT DEVICES AND CONTROL UNITS |

|-----------------------------------------------|

| 2.11.2 INPUT/OUTPUT INTERFACE                 |

| 2.11.3 CHANNELS                               |

| 2.11.4 INPUT/OUTPUT INSTRUCTIONS              |

| 2.11.4.1 Start I/O                            |

| 2.11.4.2 Test Channel                         |

| 2.11.4.3 Test I/O                             |

| 2.11.4.4 Halt I/O                             |

| 2.11.4.5 Set PCI                              |

| 2.11.5 INPUT/OUTPUT OPERATION INITIATION      |

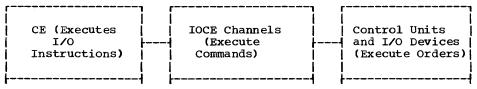

| 2.11.5.1 Channel Address Word                 |

| 2.11.5.2 Channel Command Word                 |

| 2.11.6 INPUT/OUTPUT COMMANDS                  |

| 2.11.6.1 Read                                 |

| 2.11.6.2 Write                                |

| 2.11.6.3 Read Backward                        |

| 2.11.6.4 Control                              |

| 2.11.6.5 Sense                                |

| 2.11.6.6 Transfer In Channel                  |

| 2.11.6.7 Search                               |

| 2.11.7 INPUT/OUTPUT TERMINATION               |

| 2.11.7.1 Channel Status Word                  |

| 2.11.8 INPUT/OUTPUT INTERRUPTIONS             |

| 2.12 SYSTEM CONTROL FACILITIES                |

| 2.12 SISTEM CONTROL FACILITIES                |

|                                               |

| 2.12.1.1 Store and Display                    |

| 2.12.1.2 Initial Program Load                 |

| 2.12.2 OPERATOR SECTION                       |

| 2.12.3 MAINTENANCE SECTION                    |

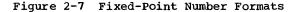

| CHAPTER 3: FIXED-POINT ARITHMETIC             |

|                                               |

| 3.1 DATA FORMAT                               |

| 3.2 NUMBER REPRESENTATION                     |

| 3.3 CONDITION CODE                            |

| 3.4 INSTRUCTION FORMAT                        |

| 3.5 INSTRUCTIONS                              |

| 3.5.1 LOAD                                    |

| 3.5.2 LOAD HALFWORD                           |

| 3.5.3 LOAD AND TEST                           |

| 3.5.4 LOAD COMPLEMENT                         |

| 3.5.5 LOAD POSITIVE                           |

| 3.5.6 LOAD NEGATIVE                           |

| 3.5.7 LOAD MULTIPLE                           |

| 3.5.8 ADD                                     |

| 3.5.9 ADD HALFWORD                            |

| 3.5.10 ADD LOGICAL                            |

| 3.5.11 SUBTRACT                               |

| 3.5.12 SUBTRACT HALFWORD                      |

| 3.5.13 SUBTRACT LOGICAL                       |

| 3.5.14 COMPARE                                |

| 3.5.15 COMPARE HALFWORD                       |

| 3.5.16 MULTIPLY                               |

| 3.5.17 MULTIPLY HALFWORD                      |

| 3.5.18 DIVIDE                                 |

| 3.5.19 CONVERT TO BINARY                      |

| 3.5.20 CONVERT TO DECIMAL                     |

| 3.5.21 STORE                                  |

| 3.5.22 STORE HALFWORD                         |

| 3.5.23 STORE MULTIPLE                         |

| 3.5.24 SHIFT LEFT SINGLE                      |

| 3.5.25 SHIFT RIGHT SINGLE                     |

| 3.5.26 SHIFT LEFT DOUBLE                      |

| 3.5.27 SHIFT RIGHT DOUBLE                     |

| 3.6 FIXED-POINT ARITHMETIC EXCEPTIONS         |

|                                               |

JANUARY 31, 1973

TNL: GN31-3005

# Table of Contents

| CHAPTER 1: INTRODUCTION TO 9020D/E SYSTEMS                                                                                                    |   | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 1.1 INTRODUCTION                                                                                                                              | • | 1   |

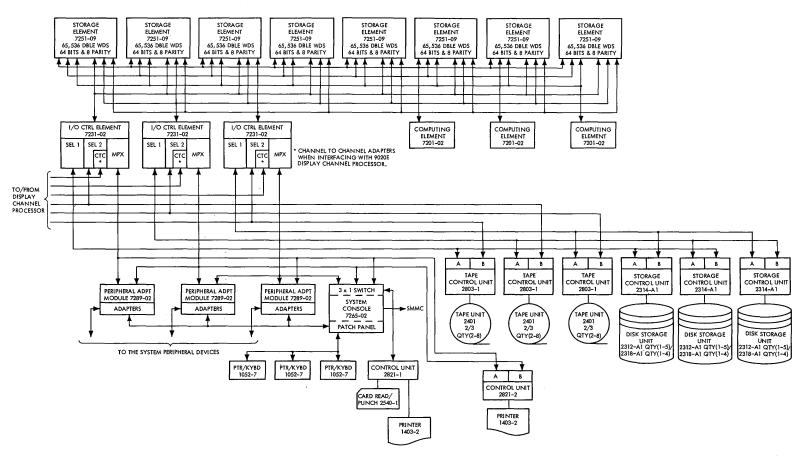

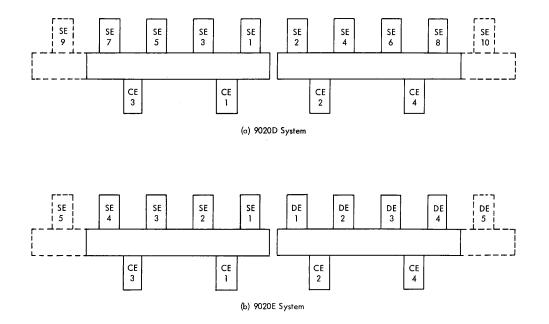

| 1.1.1 9020D SYSTEM                                                                                                                            |   |     |

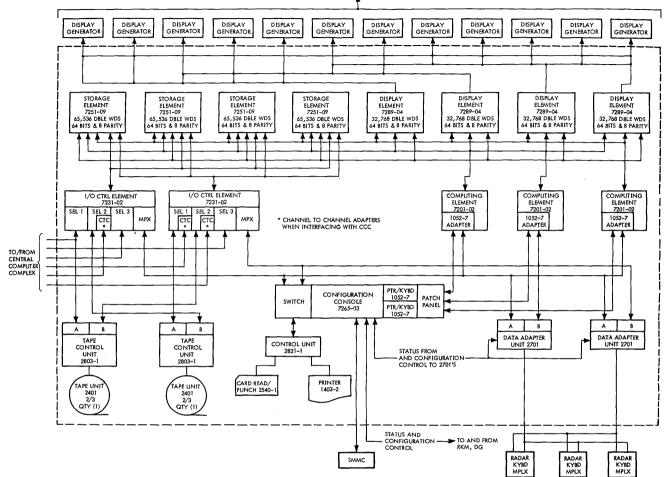

| 1.1.2 9020E SYSTEM                                                                                                                            | • | 1   |

|                                                                                                                                               |   | 2   |

| 1.2.1 SYSTEM/360 COMPATIBILITY                                                                                                                |   | 2   |

| $1.2.2 9020A COMPATIBILITY \dots \dots$ |   | - 3 |

| 1.3 COMPUTING ELEMENT                                                                                                                         |   | 3   |

| 1.4 STORAGE ELEMENT                                                                                                                           |   | 3   |

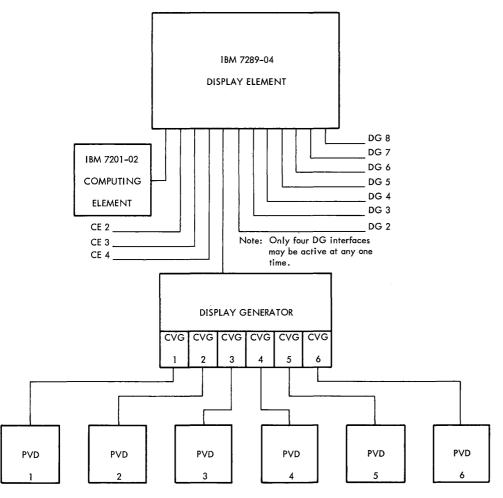

| 1.5 DISPLAY ELEMENT                                                                                                                           |   |     |

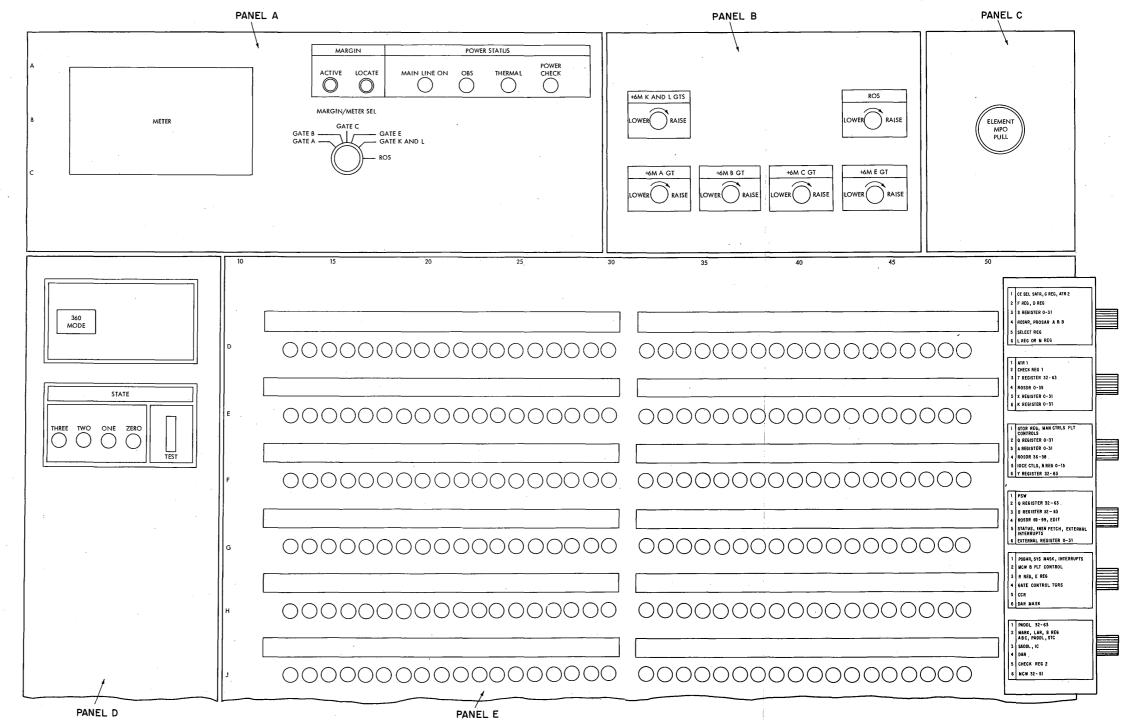

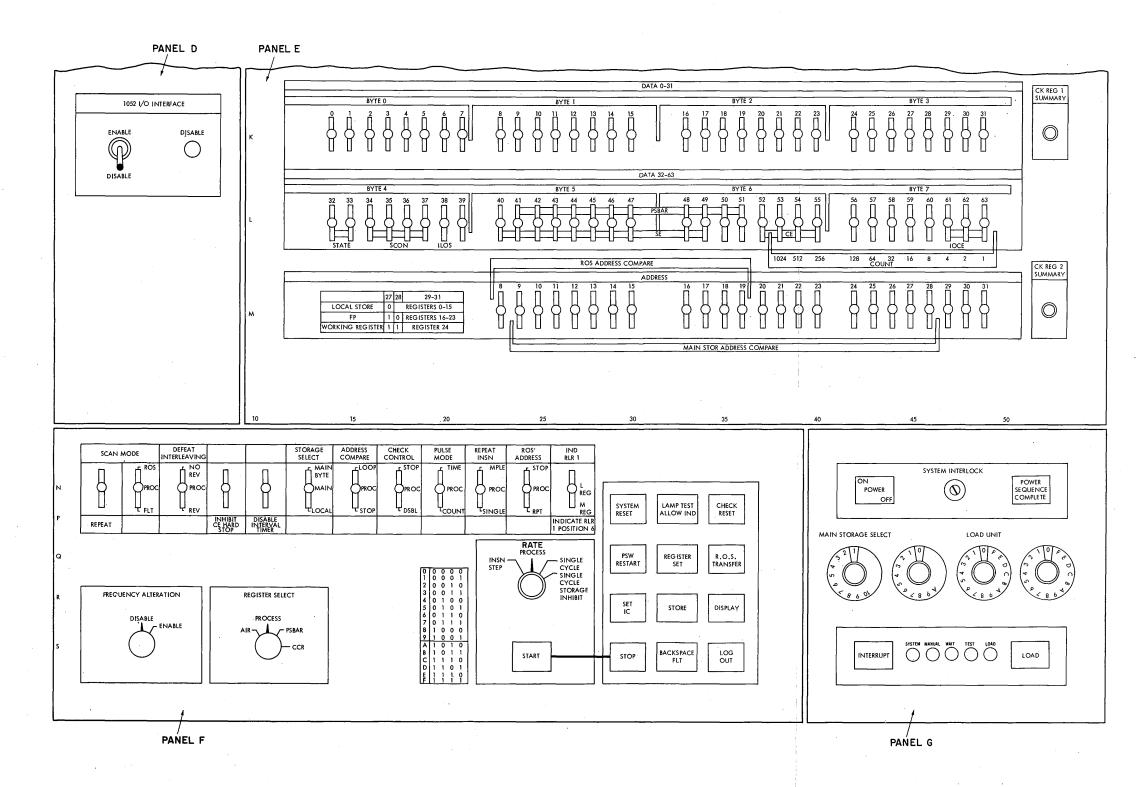

| 1.6 SYSTEM CONSOLE AND CONFIGURATION CONSOLE                                                                                                  | • | 4   |

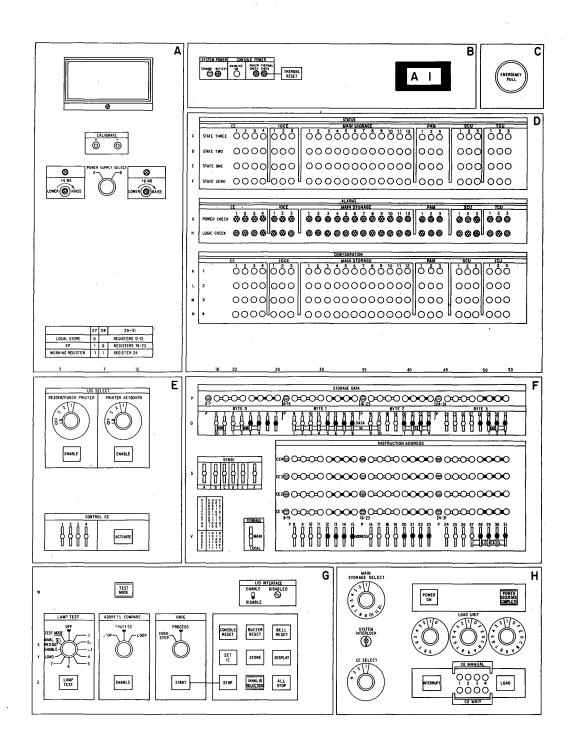

| 1 6 1 9000 SUCTEM CONSCIE                                                                                                                     | • | 4   |

| 1.6.1 9020D SYSTEM CONSOLE                                                                                                                    | • | 4   |

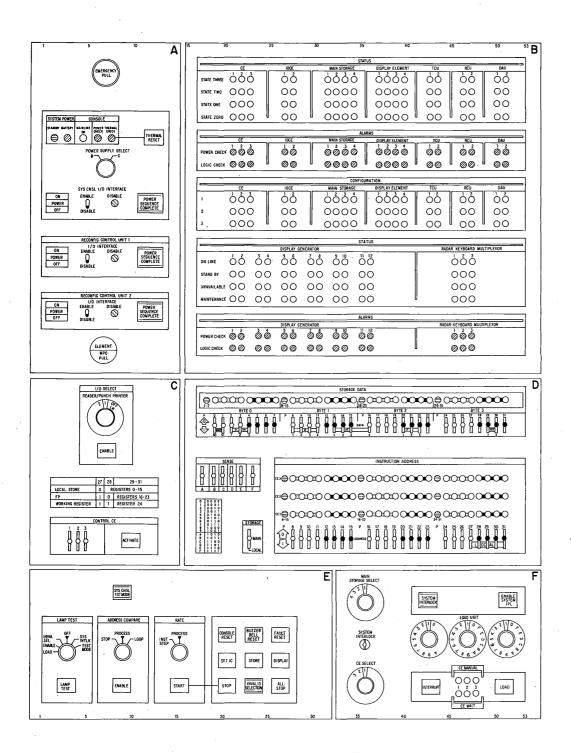

| 1.6.2 9020E CONFIGURATION CONSOLE                                                                                                             | • | 5   |

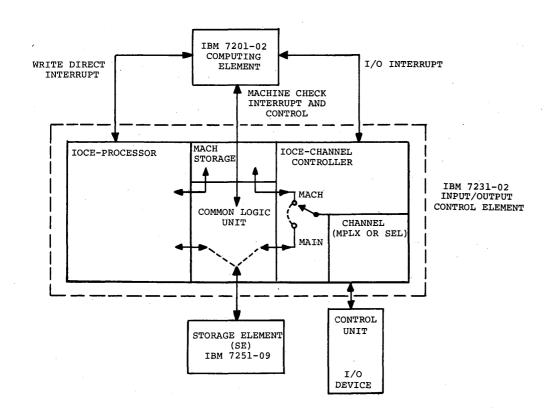

| 1.7 INPUT/OUTPUT CONTROL ELEMENT                                                                                                              | • | 5   |

| 1.8 PERIPHERAL ADAPTER MODULE                                                                                                                 | • | 5   |

| 1.9 TAPE CONTROL UNIT                                                                                                                         | • | 6   |

| 1.10 STORAGE CONTROL UNIT                                                                                                                     | • | 6   |

| <b>1.11 DATA ADAPTER UNIT</b>                                                                                                                 | • | 6   |

| 1.12 SYSTEM ALERTS                                                                                                                            | • | 6   |

|                                                                                                                                               |   |     |

| CHAPTER 2: SYSTEM STRUCTURE                                                                                                                   |   | 8   |

| 2.1 MAIN STORAGE                                                                                                                              |   |     |

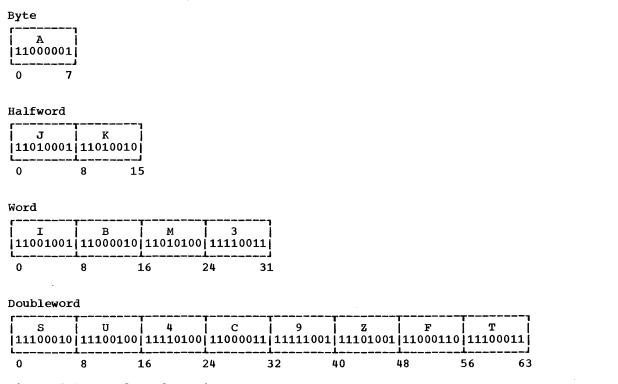

| 2.1.1 INFORMATION FORMATS                                                                                                                     |   | 11  |

| 2.1.2 ADDRESSING                                                                                                                              |   | 11  |

| 2.1.2 ADDRESSING                                                                                                                              | • | 12  |

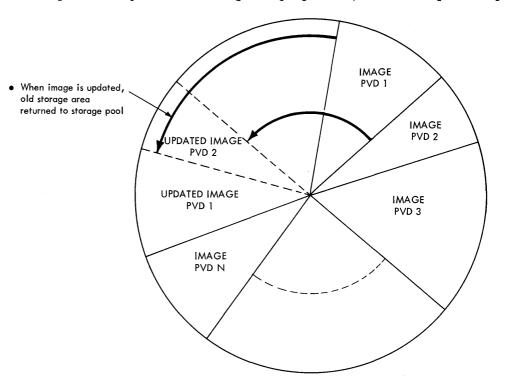

| 2.2 DISPLAY ELEMENT                                                                                                                           | • | 12  |

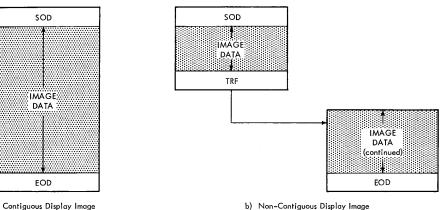

| 2.2.1 INFORMATION FORMATS                                                                                                                     | • | 12  |

| 2.2.2 ADDRESSING                                                                                                                              | • | 10  |

| 2.2.2 ADDRESSING                                                                                                                              | • | 10  |

|                                                                                                                                               |   |     |

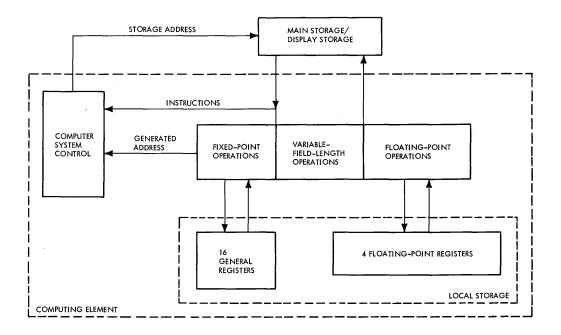

| 2.3.1 GENERAL REGISTERS                                                                                                                       | • | 15  |

| 2.3.2 FLOATING-POINT REGISTERS                                                                                                                | • | 15  |

| 2.4 ARITHMETIC AND LOGICAL UNIT                                                                                                               |   |     |

| 2.4.1 FIXED-POINT ARITHMETIC                                                                                                                  | • | 16  |

| 2.4.2 DECIMAL ARITHMETIC                                                                                                                      | • | 17  |

| 2.4.3 FLOATING-POINT ARITHMETIC                                                                                                               | • | 18  |

| 2.4.4 LOGICAL OPERATION                                                                                                                       |   | 19  |

| 2.5 PROGRAM EXECUTION                                                                                                                         |   | 23  |

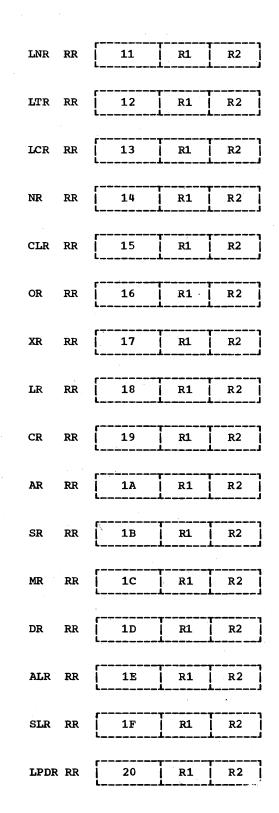

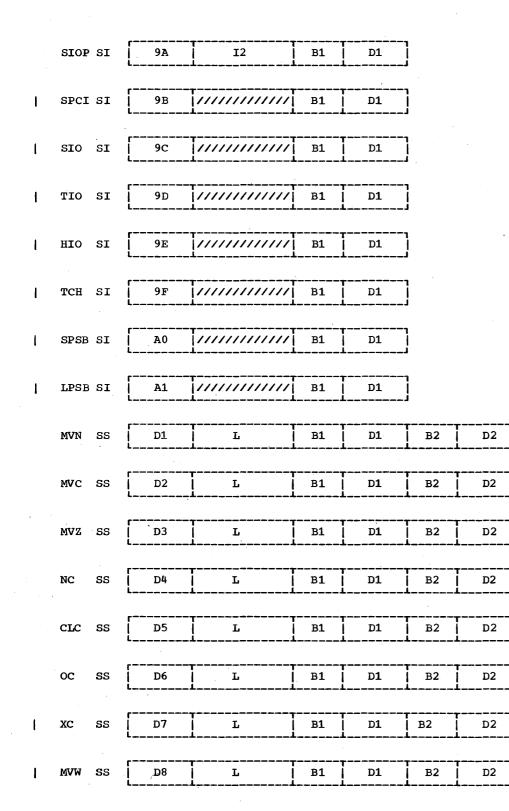

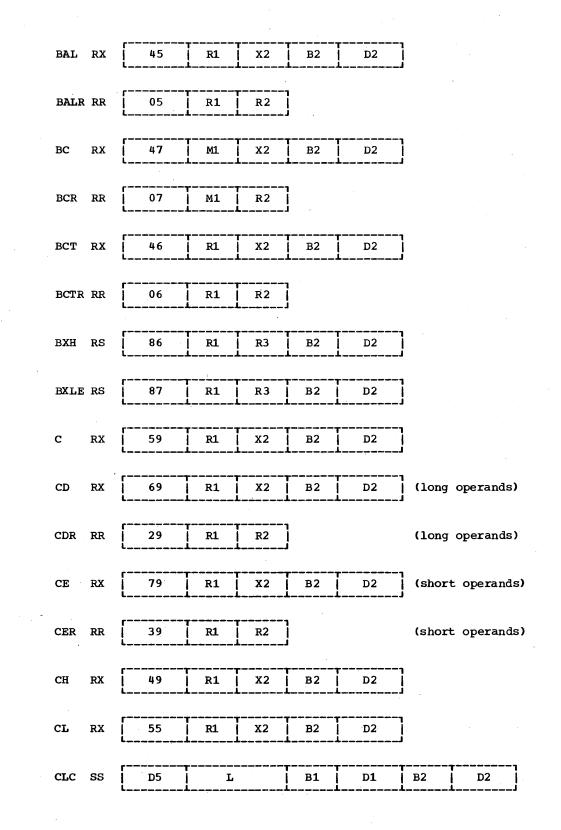

| 2.5.1 INSTRUCTION FORMAT                                                                                                                      | • | 23  |

| 2.5.2 ADDRESS GENERATION                                                                                                                      | • | 25  |

| 2.5.3 SEQUENTIAL INSTRUCTION EXECUTION                                                                                                        |   | 26  |

| 2.5.4 BRANCHING                                                                                                                               |   | 26  |

| 2.5.4 BRANCHING                                                                                                                               | - | 27  |

| 2.5.6 INTERRUPTIONS                                                                                                                           | • | 28  |

| 2.5.6.1 Input/Output Interruption                                                                                                             | • | 20  |

|                                                                                                                                               | • | 20  |

| 2.5.6.2 Program Interruption                                                                                                                  | • | 20  |

| 2.5.6.3 Supervisor Call Interruption                                                                                                          | • | 30  |

| 2.5.6.4 External Interruption                                                                                                                 | • | 30  |

| 2.5.6.5 Machine Check Interruption                                                                                                            | • | 31  |

| 2.5.6.6 Priority of Interruption                                                                                                              |   |     |

| 2.5.6.7 Program States                                                                                                                        | • |     |

| 2.6 PROTECTION                                                                                                                                | • | 33  |

| 2.7 TIMER                                                                                                                                     | • | 33  |

| 2.8 DIRECT CONTROL                                                                                                                            | • | 34  |

| 2.9 MULTIPROCESSOR OPERATION                                                                                                                  | • | 34  |

| 2.9.1 COMPUTING ELEMENT                                                                                                                       | • | 34  |

| 2.9.2 IOCE-PROCESSOR OPERATION                                                                                                                |   | 34  |

| 2.10 DISPLAY PROCESSOR OPERATION                                                                                                              |   | 35  |

| 2.10.1 COMPUTING ELEMENT                                                                                                                      |   | 35  |

| 2.11 INPUT/OUTPUT                                                                                                                             |   |     |

|                                                                                                                                               | - |     |

| Form: | A27. | -273 | 4-2 |

|-------|------|------|-----|

|-------|------|------|-----|

1

1

)

)

)

Table of Contents, Cont.

| 2.11.2 INPUT/OUTPUT INTERFACE 2.11.3 CHANNELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | N     |                   | · · · · · · · · · · · · · · · · · · · |       |       | <ul> <li>.</li> <li>.&lt;</li></ul> |     | • | 36<br>37<br>37<br>37<br>37<br>37<br>37<br>37<br>37<br>37<br>38<br>38                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------|---------------------------------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|----------------------------------------------------------------------------------------------------------------------|

| <pre>2.11.6.3 Read Backward<br/>2.11.6.4 Control<br/>2.11.6.5 Sense<br/>2.11.6.6 Transfer In Channel .<br/>2.11.6.7 Search<br/>2.11.7 INPUT/OUTPUT TERMINATION .<br/>2.11.7.1 Channel Status Word .<br/>2.11.8 INPUT/OUTPUT INTERRUPTIONS .<br/>2.12 SYSTEM CONTROL FACILITIES .<br/>2.12.1 CONTROL PANEL FUNCTIONS .<br/>2.12.1.1 Store and Display<br/>2.12.1.2 Initial Program Load .<br/>2.12.2 OPERATOR SECTION</pre>                                                                                                                                                                     |     |       |                   | • • • • • • • • • • • • • • • • • • • |       |       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | • | 39<br>39<br>39<br>39<br>39<br>40<br>40<br>41<br>41<br>41                                                             |

| 2.12.3 MAINTENANCE SECTION<br>CHAPTER 3: FIXED-POINT ARITHMETIC<br>3.1 DATA FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ••• | • • • | •••               | •••                                   | • •   | •••   | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ••• | • | 43<br>43                                                                                                             |

| 3.3 CONDITION CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • • |       | · ·               | •••                                   | • •   | •••   | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |   | 44                                                                                                                   |

| 3.5 INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ••• | •••   |                   | •••                                   | •     | • •   | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • • | • | 46                                                                                                                   |

| 3.5.2 LOAD HALFWORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       |                   | •••                                   |       | ••    | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | - |                                                                                                                      |

| 3.5.3 LOAD AND TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ••• | •••   | •••               | •••                                   | • •   | •••   | • •<br>• •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ••• | • | 49                                                                                                                   |

| 3.5.3 LOAD AND TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ••• |       |                   |                                       | • •   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ••• | • | 49<br>49<br>50                                                                                                       |

| 3.5.3 LOAD AND TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ••• | •••   | •••               | •••                                   | • •   | · ·   | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • • | • | 49<br>49<br>50<br>50<br>51                                                                                           |

| 3.5.3 LOAD AND TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       | • •<br>• •<br>• • | <br><br>                              | • •   | · ·   | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | • | 49<br>49<br>50<br>50<br>51<br>51<br>51<br>52                                                                         |

| 3.5.3 LOAD AND TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       | · · ·             | <br><br><br><br><br>                  | · · · | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 49<br>49<br>50<br>51<br>51<br>52<br>53<br>54                                                                         |

| 3.5.3 LOAD AND TEST3.5.4 LOAD COMPLEMENT3.5.5 LOAD POSITIVE3.5.6 LOAD NEGATIVE3.5.6 LOAD NEGATIVE3.5.7 LOAD MULTIPLE3.5.8 ADD3.5.9 ADD HALFWORD3.5.10 ADD LOGICAL3.5.11 SUBTRACT3.5.12 SUBTRACT HALFWORD3.5.13 SUBTRACT LOGICAL                                                                                                                                                                                                                                                                                                                                                                |     |       | · · ·             | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 49<br>49<br>50<br>51<br>51<br>52<br>53<br>54<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55 |

| 3.5.3 LOAD AND TEST         3.5.4 LOAD COMPLEMENT         3.5.5 LOAD POSITIVE         3.5.5 LOAD NEGATIVE         3.5.6 LOAD NEGATIVE         3.5.7 LOAD MULTIPLE         3.5.7 LOAD MULTIPLE         3.5.8 ADD         3.5.9 ADD HALFWORD         3.5.10 ADD LOGICAL         3.5.11 SUBTRACT         3.5.12 SUBTRACT HALFWORD         3.5.13 SUBTRACT LOGICAL         3.5.14 COMPARE         3.5.15 COMPARE HALFWORD                                                                                                                                                                          |     |       |                   | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 49<br>49<br>50<br>51<br>51<br>52<br>53<br>54<br>54                                                                   |

| 3.5.3 LOAD AND TEST         3.5.4 LOAD COMPLEMENT         3.5.5 LOAD POSITIVE         3.5.5 LOAD NEGATIVE         3.5.6 LOAD NEGATIVE         3.5.7 LOAD MULTIPLE         3.5.7 LOAD MULTIPLE         3.5.8 ADD         3.5.9 ADD HALFWORD         3.5.10 ADD LOGICAL         3.5.11 SUBTRACT         3.5.12 SUBTRACT HALFWORD         3.5.13 SUBTRACT LOGICAL         3.5.14 COMPARE         3.5.15 COMPARE HALFWORD         3.5.16 MULTIPLY                                                                                                                                                  |     |       |                   | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 4990<br>55555555555555555555555555555555555                                                                          |

| 3.5.3 LOAD AND TEST         3.5.4 LOAD COMPLEMENT         3.5.5 LOAD POSITIVE         3.5.5 LOAD NEGATIVE         3.5.6 LOAD NEGATIVE         3.5.7 LOAD MULTIPLE         3.5.7 LOAD MULTIPLE         3.5.8 ADD         3.5.9 ADD HALFWORD         3.5.10 ADD LOGICAL         3.5.11 SUBTRACT         3.5.12 SUBTRACT HALFWORD         3.5.13 SUBTRACT LOGICAL         3.5.14 COMPARE         3.5.15 COMPARE HALFWORD                                                                                                                                                                          |     |       |                   | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 49900112344567<br>5555555555555555555555555555555555                                                                 |

| 3.5.3 LOAD AND TEST         3.5.4 LOAD COMPLEMENT         3.5.5 LOAD POSITIVE         3.5.5 LOAD NEGATIVE         3.5.6 LOAD NEGATIVE         3.5.7 LOAD MULTIPLE         3.5.8 ADD         3.5.9 ADD HALFWORD         3.5.10 ADD LOGICAL         3.5.11 SUBTRACT         3.5.12 SUBTRACT HALFWORD         3.5.13 SUBTRACT LOGICAL         3.5.14 COMPARE         3.5.15 COMPARE HALFWORD         3.5.16 MULTIPLY         3.5.17 MULTIPLY         3.5.18 DIVIDE         3.5.19 CONVERT TO BINARY                                                                                               |     |       |                   | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 499505555555555555555555555555555555555                                                                              |

| 3.5.3 LOAD AND TEST3.5.4 LOAD COMPLEMENT3.5.5 LOAD POSITIVE3.5.5 LOAD NEGATIVE3.5.6 LOAD NEGATIVE3.5.7 LOAD MULTIPLE3.5.8 ADD3.5.9 ADD HALFWORD3.5.10 ADD LOGICAL3.5.11 SUBTRACT3.5.12 SUBTRACT HALFWORD3.5.13 SUBTRACT LOGICAL3.5.14 COMPARE3.5.15 COMPARE HALFWORD3.5.16 MULTIPLY3.5.17 MULTIPLY3.5.18 DIVIDE                                                                                                                                                                                                                                                                                |     |       |                   | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 499505555555555555555555555555555555555                                                                              |

| 3.5.3 LOAD AND TEST         3.5.4 LOAD COMPLEMENT         3.5.5 LOAD POSITIVE         3.5.5 LOAD NEGATIVE         3.5.6 LOAD NEGATIVE         3.5.7 LOAD MULTIPLE         3.5.8 ADD         3.5.9 ADD HALFWORD         3.5.10 ADD LOGICAL         3.5.11 SUBTRACT         3.5.12 SUBTRACT HALFWORD         3.5.13 SUBTRACT LOGICAL         3.5.14 COMPARE         3.5.15 COMPARE HALFWORD         3.5.16 MULTIPLY         3.5.17 MULTIPLY HALFWORD         3.5.18 DIVIDE         3.5.19 CONVERT TO BINARY         3.5.20 CONVERT TO DECIMAL         3.5.21 STORE         3.5.22 STORE HALFWORD |     |       |                   | · · · · · · · · · · · · · · · · · · · | • •   | · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   | 499<br>555<br>555<br>555<br>555<br>555<br>555<br>555<br>555<br>555                                                   |

| 3.5.3 LOAD AND TEST3.5.4 LOAD COMPLEMENT3.5.4 LOAD COMPLEMENT3.5.5 LOAD POSITIVE3.5.6 LOAD NEGATIVE3.5.6 LOAD NEGATIVE3.5.7 LOAD MULTIPLE3.5.8 ADD3.5.9 ADD HALFWORD3.5.10 ADD LOGICAL3.5.11 SUBTRACT3.5.12 SUBTRACT HALFWORD3.5.13 SUBTRACT LOGICAL3.5.14 COMPARE3.5.15 COMPARE HALFWORD3.5.16 MULTIPLY3.5.17 MULTIPLY3.5.18 DIVIDE3.5.19 CONVERT TO BINARY3.5.20 CONVERT TO DECIMAL3.5.21 STORE3.5.22 STORE HALFWORD3.5.23 STORE MULTIPLE                                                                                                                                                    |     |       |                   |                                       |       | · · · |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |   | 499<br>555<br>555<br>555<br>555<br>555<br>555<br>555<br>555<br>555                                                   |

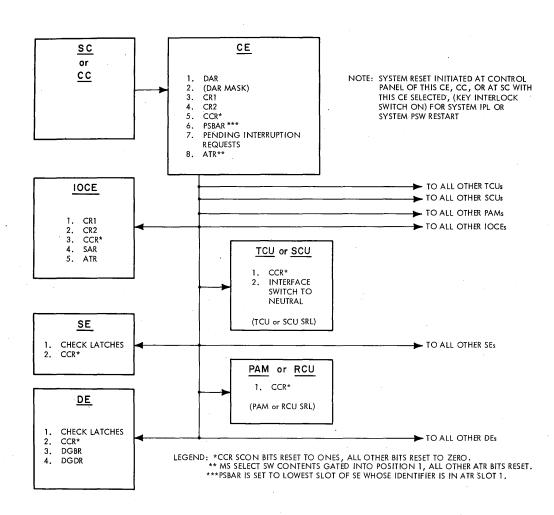

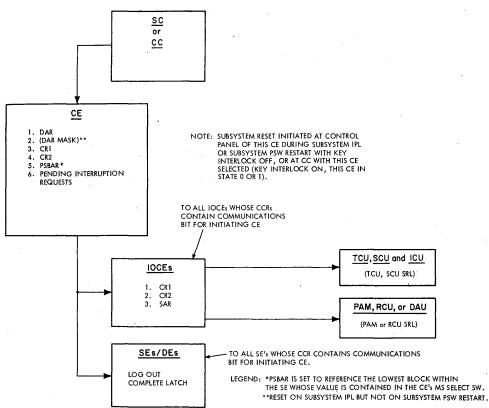

| 3.5.3 LOAD AND TEST3.5.4 LOAD COMPLEMENT3.5.5 LOAD POSITIVE3.5.5 LOAD NEGATIVE3.5.6 LOAD NEGATIVE3.5.7 LOAD MULTIPLE3.5.8 ADD3.5.9 ADD HALFWORD3.5.10 ADD LOGICAL3.5.11 SUBTRACT3.5.12 SUBTRACT HALFWORD3.5.13 SUBTRACT LOGICAL3.5.14 COMPARE3.5.15 COMPARE HALFWORD3.5.16 MULTIPLY3.5.17 MULTIPLY3.5.18 DIVIDE3.5.19 CONVERT TO BINARY3.5.20 CONVERT TO DECIMAL3.5.21 STORE3.5.23 STORE MULTIPLE3.5.24 SHIFT LEFT SINGLE3.5.25 SHIFT RIGHT SINGLE                                                                                                                                             |     |       |                   |                                       |       | · · · |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |   | 499001123555555555555555661122                                                                                       |