9020 D System 9020 E System **Design Data**

July 1, 1971

International Business Machines Corporation

# Second Edition (July 1971)

This major revision of the manual obsoletes the previous edition, dated December 1, 1969, and incorporates Technical Newsletter GN27-2943, dated December 1, 1970. This revision includes information pertaining to the 2314 Direct Access Storage Facility (DASF) and corrects errors found since publication of the Technical Newsletter mentioned previously. Chapter 14 has been extensively revised for clarity and a new appendix, Appendix G, has been added to describe channel data transfer rates. The Glossary, which was previously Appendix G, is now Appendix H.

A technical change or addition to the text is indicated by a vertical line to the left of the change. A changed or added figure is indicated by the symbol  $\bullet$  to the left of the caption. When the figure number but not the figure itself is changed, a revision bar is placed to the left of the figure caption.

Address comments concerning the contents of this publication to: IBM Corporation, Federal Systems Division, FAA Project Office, 18100 Frederick Pike, Gaithersburg, Maryland 20760

# CONTENTS

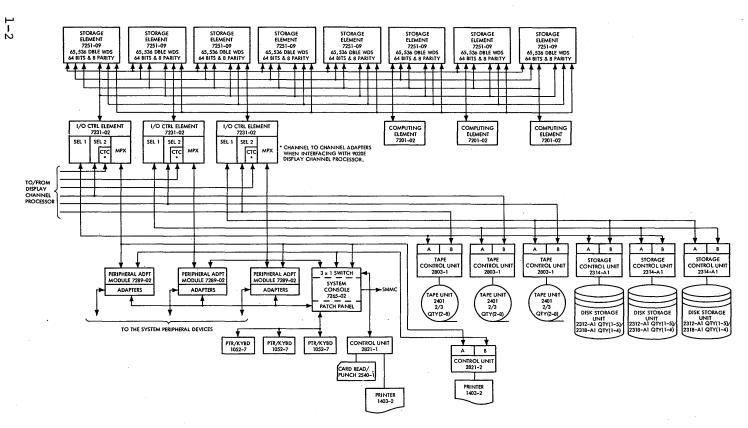

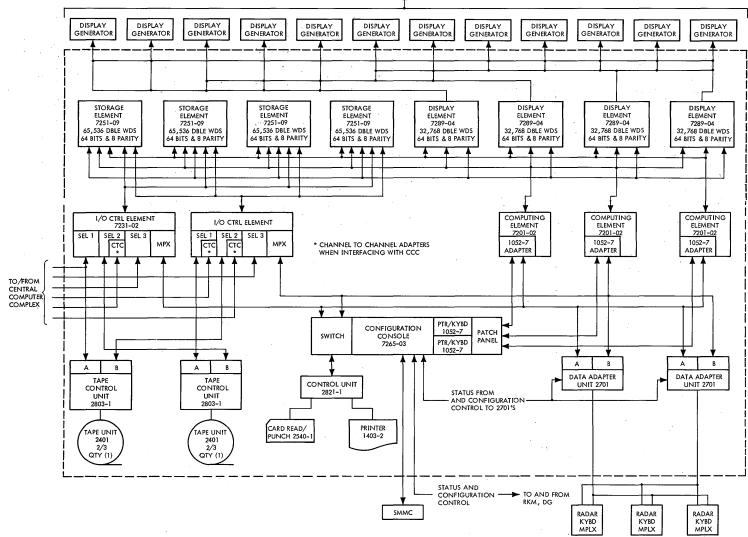

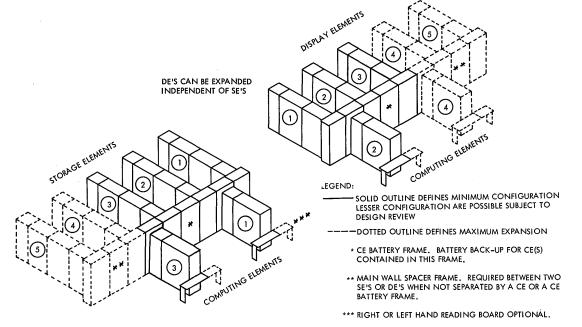

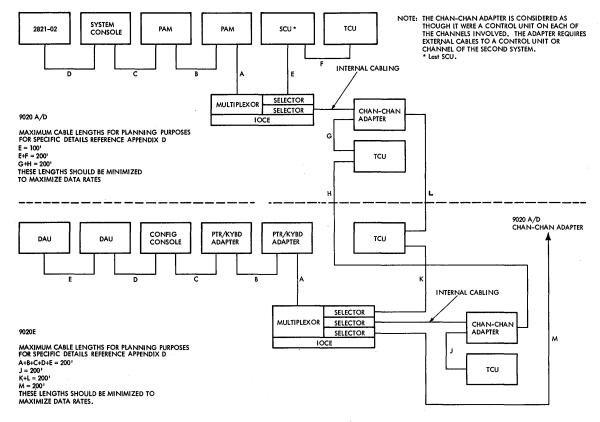

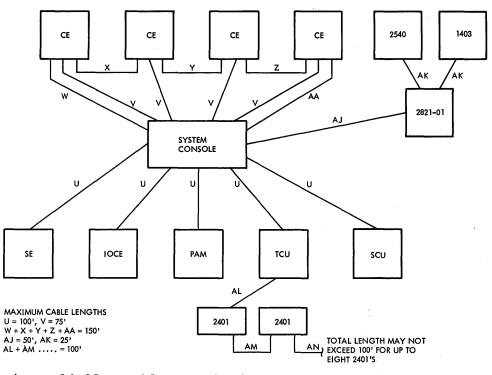

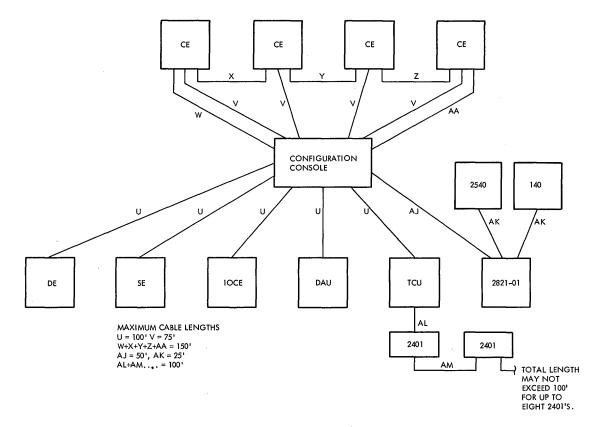

| CHAPTER 1. INTRODUCTION.<br>9020D EXPANSION OPTIONS .<br>7201-02 Computing Element (CE).<br>7251-09 Storage Element (SE).<br>2803-1 Tape Control Unit (TCU).<br>7231-02 Input/Output Control Element (IOCE) .<br>9020E EXPANSION OPTIONS .<br>7201-02 Computing Element (CE).<br>7251-09 Storage Element (SE).<br>7289-04 Display Element (DE).<br>7231-02 Input/Output Control Element.<br>7265-03 Configuration Console (CC).<br>2803- 1 Tape Control Unit (TCU). | 1-1<br>1-1<br>1-4 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

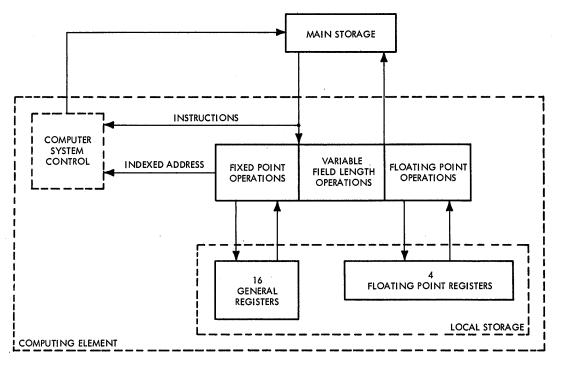

| CHAPTER 2. IBM 7201-02 COMPUTING ELEMENT                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1<br>2-1        |

| GENERAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1               |

| FUNCTIONAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-4               |

| Control Section                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-5               |

| Storage Control Interface (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-5               |

| Instruction Fetching                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-6               |

| Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-6               |

| INTERNAL OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-11              |

| Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-11              |

| Instruction Fetching                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-12              |

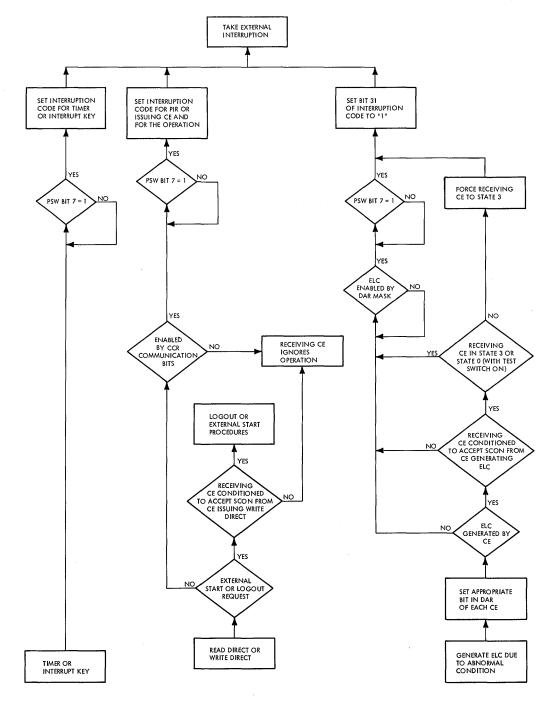

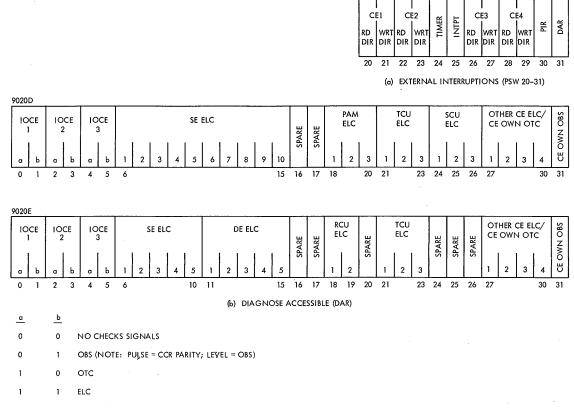

| Interruption Processing                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-12              |

| External Interruption Handling                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-12              |

| Classes of CE Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-13              |

| Display Processing Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 - 14            |

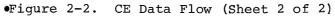

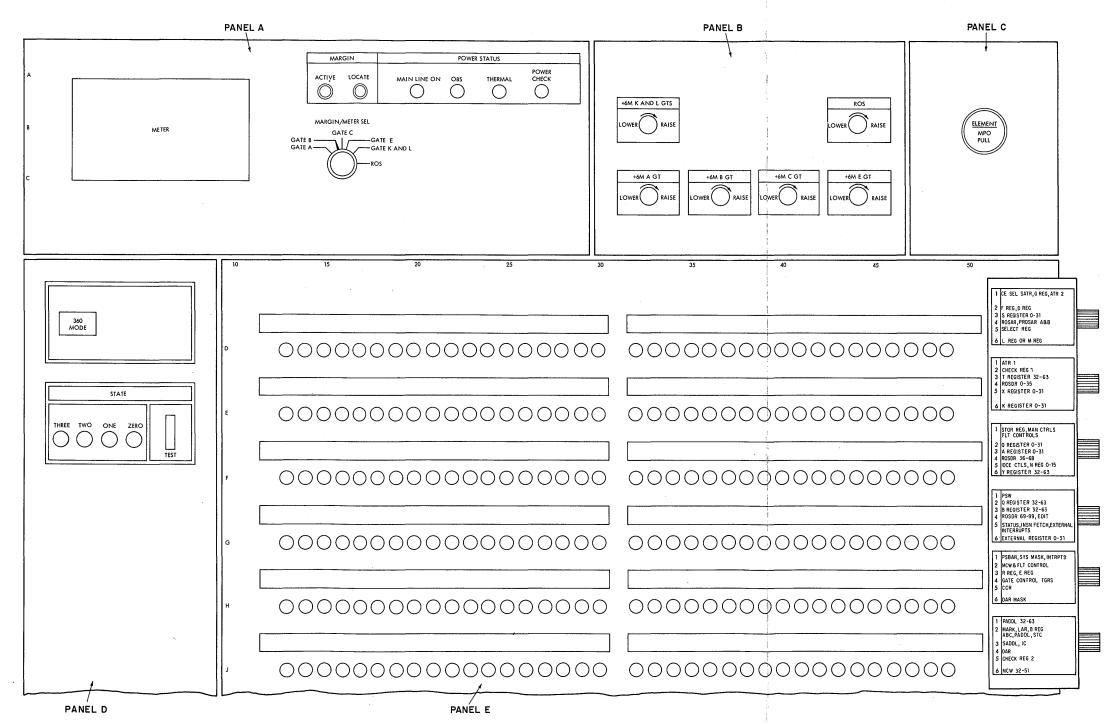

| Computing Element Control Panel                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-15              |

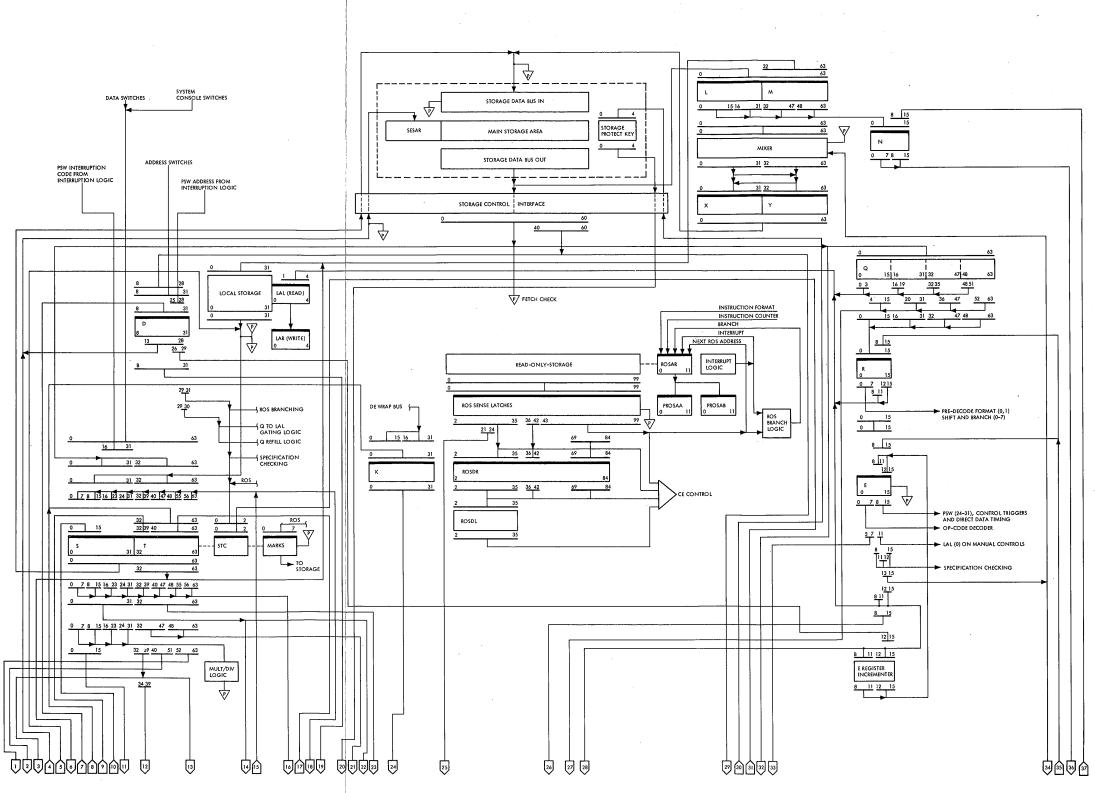

| DESIGN DETAILS                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-16              |

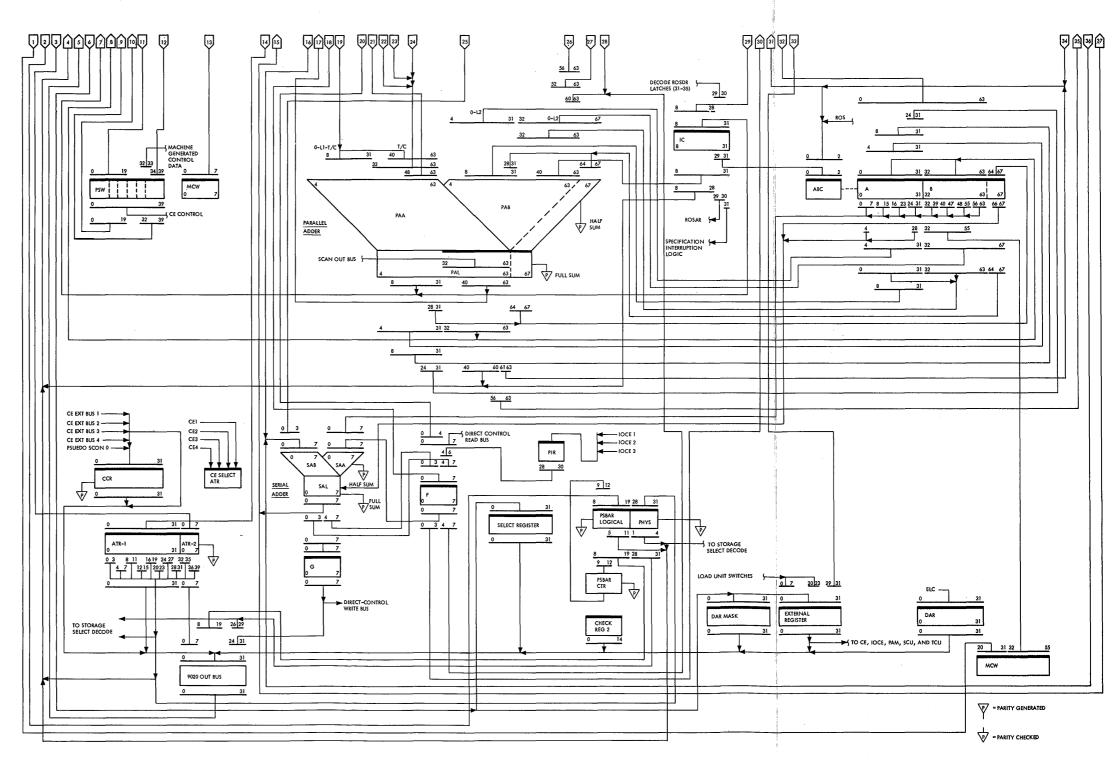

| Arithmetic and Logical Unit                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-16              |

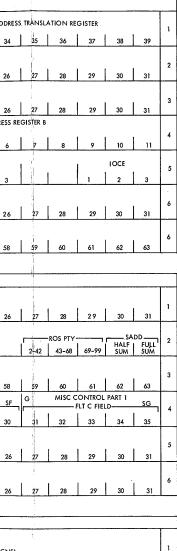

| Registers and Counters                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-17              |

| Interval Timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-21              |

| Storage Control Interface                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-22              |

| Address Translation Feature                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-22              |

| 9020D System.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-22              |

| 9020E System                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-29              |

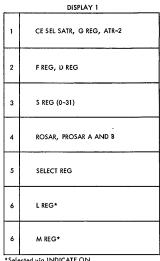

| Read Only Storage (ROS)                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-29              |

| $\begin{array}{c} \text{Acad}  \text{Min}  \text{Stollage}  (\text{NOS})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                          | 2-29              |

| 360 Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-29<br>2-31      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-51<br>2-51      |

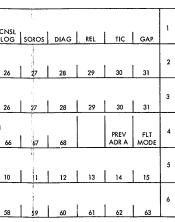

| MAINTENANCE FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-51              |

| Uniconting                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-52              |

| Half-Sum Check                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-52              |

| Check Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-52              |

| Check Stop.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-52              |

| CE Control Danol                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| CE Control Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-32              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-54              |

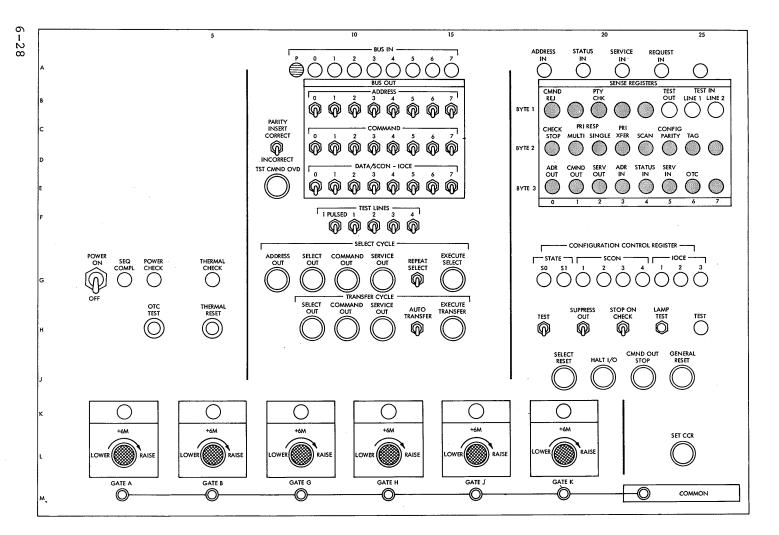

| Marginal Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-35              |

i

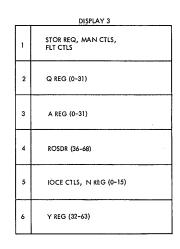

| Diagnose Instructions                                             | 2-55  |

|-------------------------------------------------------------------|-------|

| DE Wrap Bus                                                       | 2-55  |

| ·                                                                 |       |

| CHAPTER 3. IBM 7251-09 STORAGE ELEMENT                            |       |

| INTRODUCTION                                                      | 3-1   |

| FUNCTIONAL CHARACTERISTICS.                                       | 3-2   |

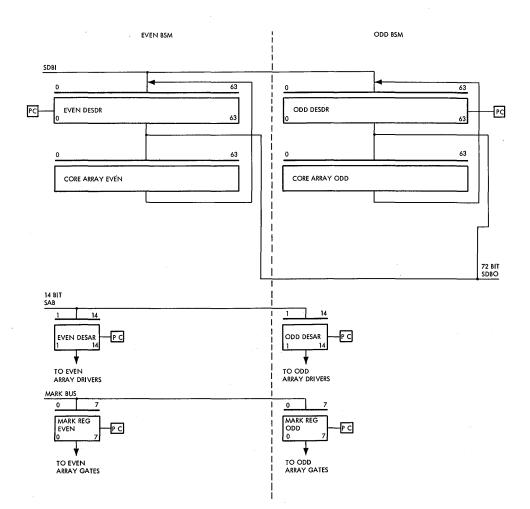

| Basic Storage Module                                              | 3-2   |

| Storage Protect                                                   | 3-2   |

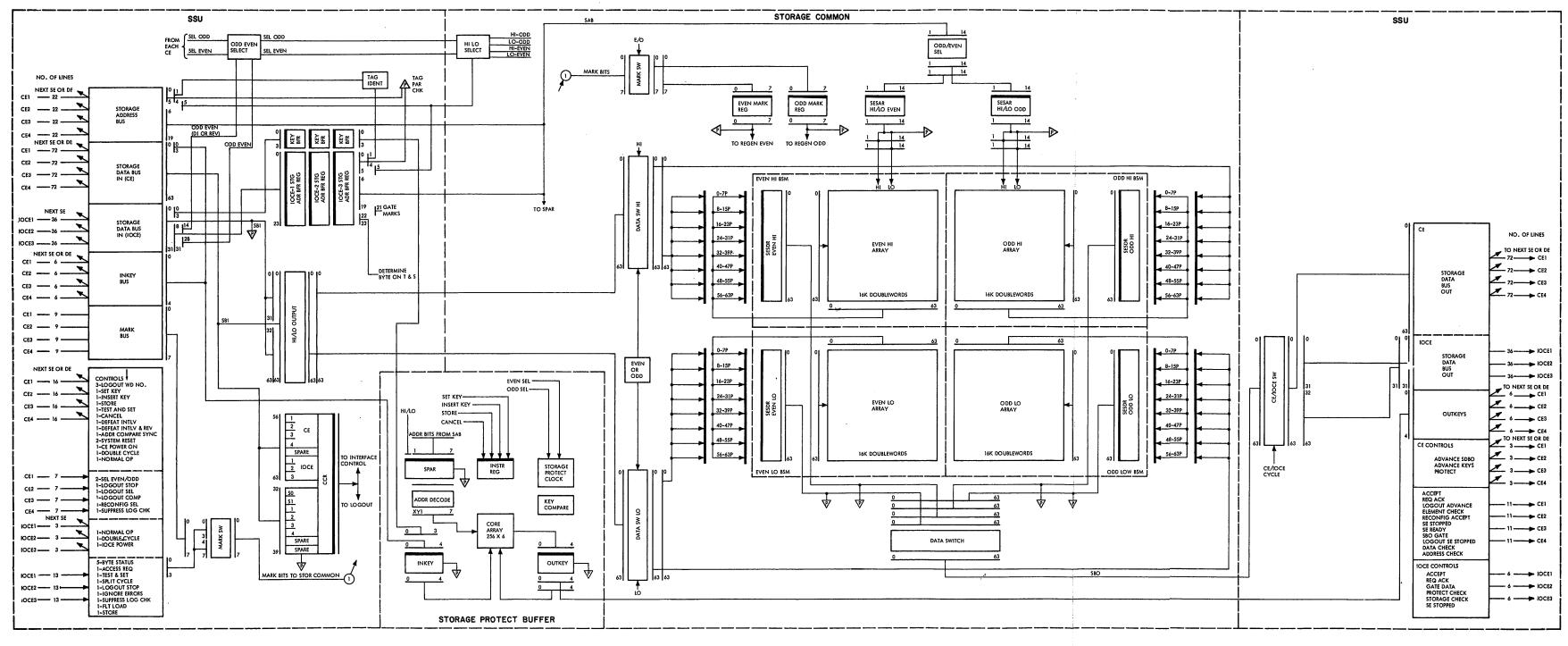

| DESIGN DETAILS                                                    | 3-2   |

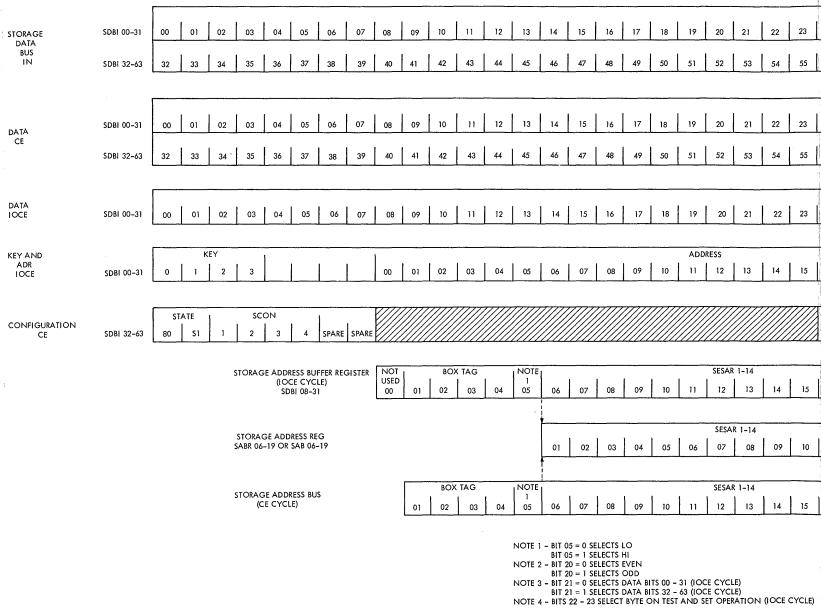

| Storage Element Storage Data Register (SESDR)                     |       |

| Storage Element Storage Address Registers (SESAR)                 | 3-3   |

| IOCE Storage Address Buffer Registers (SABR)                      | 3-3   |

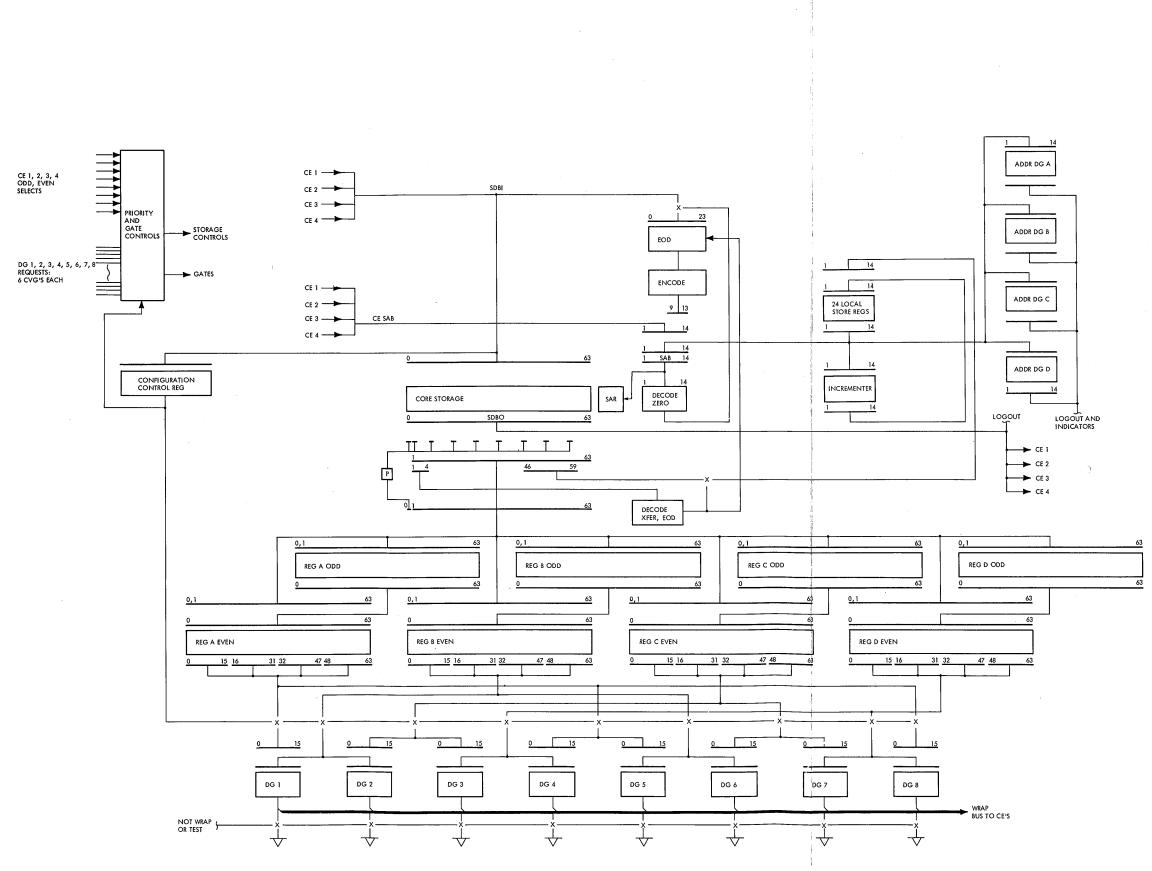

| Configuration Control Register                                    | 3-3   |

| Storage Protect Buffer (SPB)                                      | 3-10  |

| Logout                                                            | 3-10  |

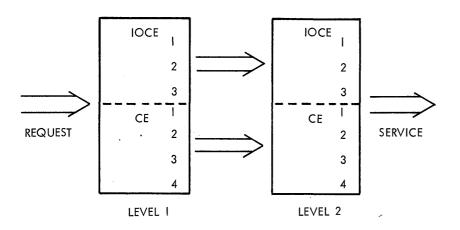

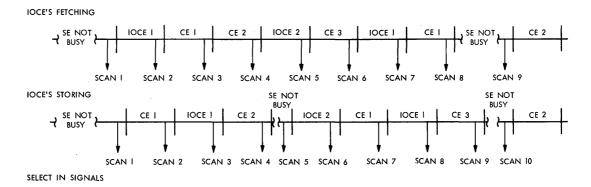

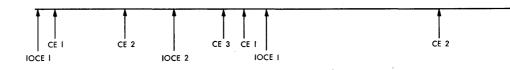

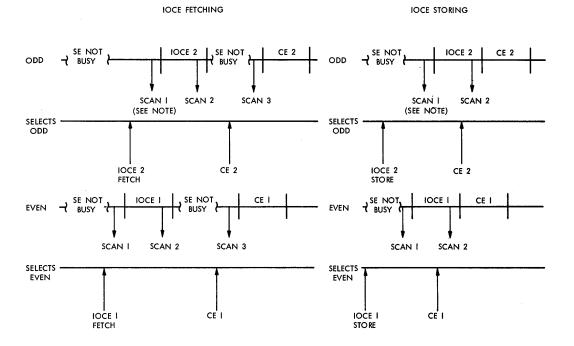

| Interfacing Switching Control                                     | 3-13  |

| Checking                                                          | 3-17  |

|                                                                   |       |

| CHAPTER 4. IBM 7289-04 DISPLAY ELEMENT                            |       |

| INTRODUCTION                                                      | 4-1   |

| FUNCTIONAL CHARACTERISTICS                                        | 4-1   |

| Basic Storage Module (BSM)                                        | 4-1   |

| Storage Protect Buffer (SPB)                                      | 4-1   |

| Switch Unit (SU)                                                  | 4-2   |

| DESIGN DETAILS                                                    | 4-2   |

| Basic Storage Module                                              | 4-2   |

| Storage Protect Buffer                                            | 4-2   |

| Switch Unit                                                       | 4-4   |

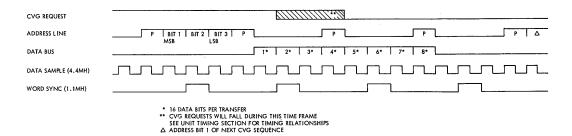

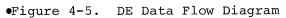

| DG Data Transfer                                                  | 4 - 4 |

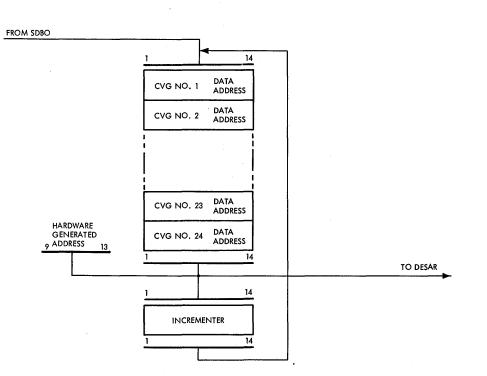

| Address Registers                                                 | 4-4   |

| Data Buffers                                                      | 4-5   |

| Priority                                                          |       |

| DE/DG Refresh Control Words                                       | 4-9   |

| Transfer                                                          |       |

| End-of-Display                                                    | 4-11  |

| Refresh Clock                                                     | 4-11  |

| Refresh Synchronization                                           | 4-11  |

| Configuration Control Register (CCR)                              | 4-12  |

| Logout                                                            | 4-15  |

| Fetch                                                             | 4-15  |

| Store                                                             | 4-15  |

| Test and Set.                                                     | 4-16  |

| Checking.                                                         | 4-16  |

| DE/DG Interface                                                   | 4-21  |

| Interface Seququences                                             | 4-22  |

| Configuration                                                     | 4-22  |

| Electrical Characteristics.                                       | 4-23  |

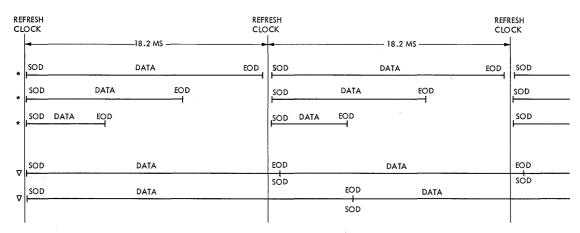

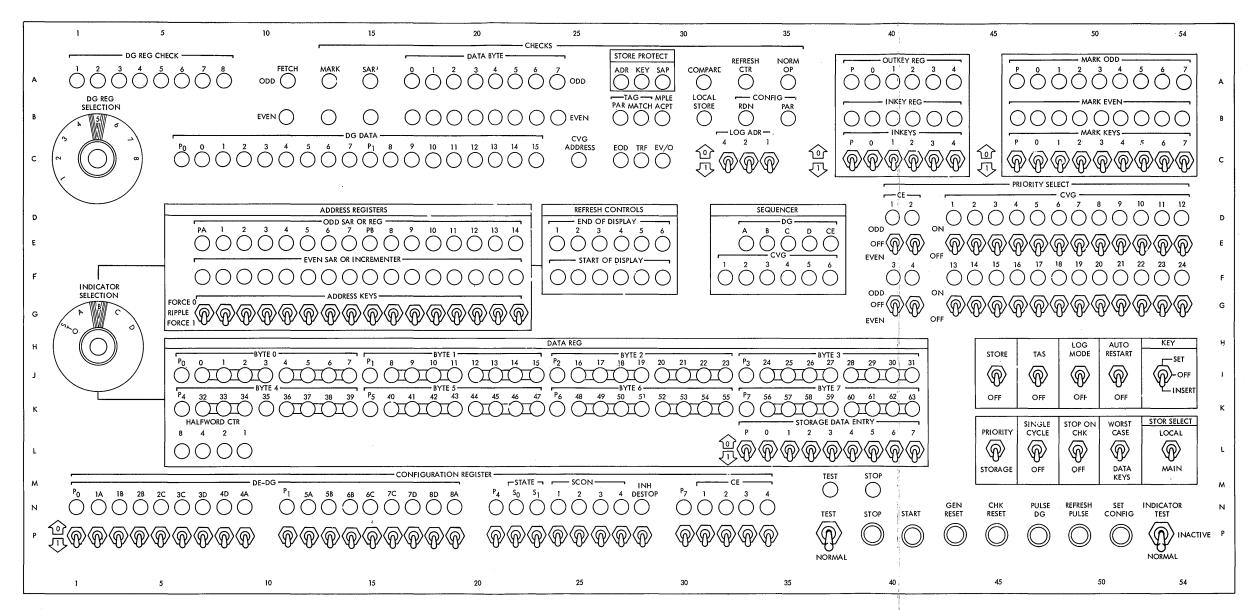

| MAINTENANCE PANELS.                                               | 4-23  |

| Switches.                                                         | 4-27  |

| Switches.       Indicators.         Indicators.       Indicators. | 4-34  |

|                                                                   | 4-39  |

| DE/DG CONFIGURATION                                               | 4-42  |

|                                                                   |       |

| DE/DG CONFIGURATION (60 PVD SYSTEM)                               | 4-43  |

| DE/DG CONFIGURATION (90 PVD SYSTEM)                               | 4-45  |

1

| CHAPTER 5. IBM 7231-02                    | IN    | PUT | /0  | JTP  | UT  | C   | ON | TR         | OL | ΕI  | EMI  | ENI | • | • | • | •   | •  |      |

|-------------------------------------------|-------|-----|-----|------|-----|-----|----|------------|----|-----|------|-----|---|---|---|-----|----|------|

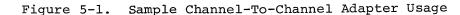

| INTRODUCTION                              | •     | • • | •   | •    | •   | •   | •  | •          | •  | •   | • •  | •   | • | • | • | •   | •  | 5-1  |

| GENERAL CHARACTERISTICS                   | •     | • • | •   | •    | •   | •   | •  | •          | •  | • • | • •  | •   | • | • | • | • , | •  | 5-2  |

| Common Logic Unit (CLU)                   | •     | • • | •   | •    | •   | •   | •  | •          | •  | • • | • •  | •   | • | • | • | •   | •  | 5-2  |

| MACH Storage                              | •     | • • | •   | •    | •   | •   | •  | •          | •  | • • | • •  | •   | • | • | • | •   | •  | 5-2  |

| Multiplexor Channel                       | •     | • • | •   | •    | •   | •   | •  | •          | •  | • • | • •  | •   | • | ٠ | • | •   | •  | 5-2  |

| Selector Channel                          | •     | • • | •   | •    | •   | •   | •  | •          | •  | •   | •    | •   | • | • | • | •   | •  | 5-3  |

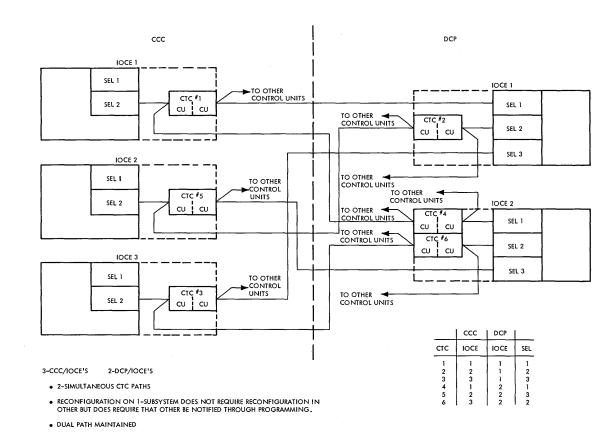

| Channel-to-Channel Adap                   |       |     |     |      |     |     |    |            |    |     |      |     |   |   |   |     |    | 5-3  |

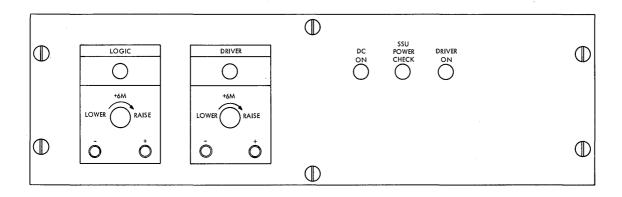

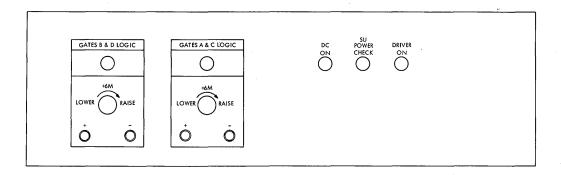

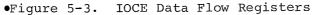

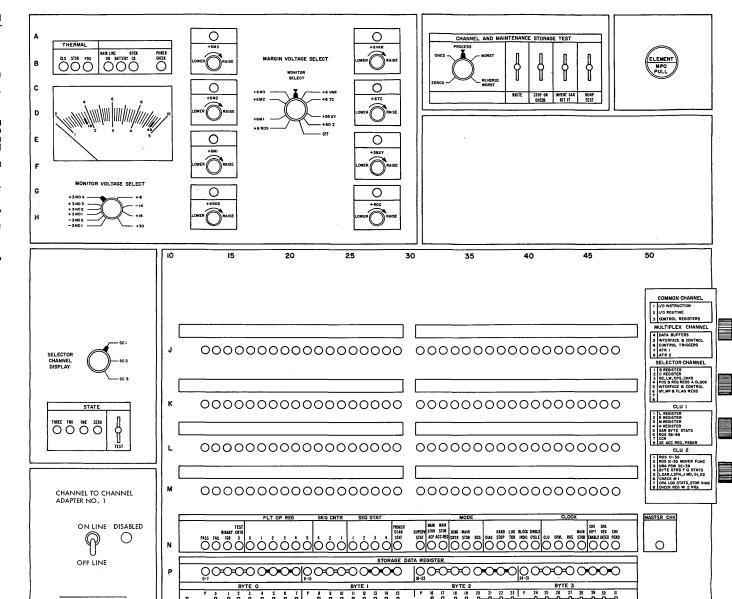

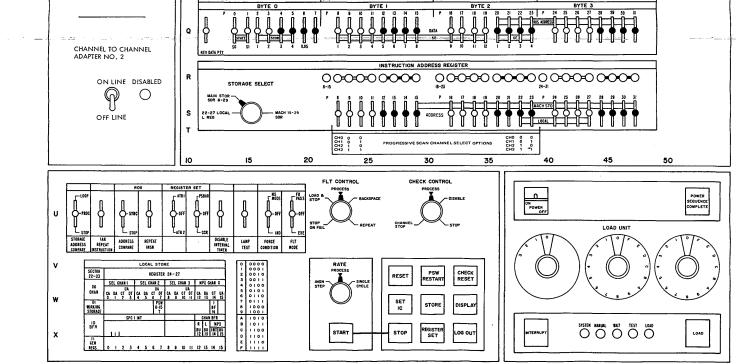

| IOCE Control Panel                        | •     | • • | •   | •    | •   | •   | •  | •          | •  | • • | •    | •   | • | • | • | •   | •  | 5-3  |

| I/O Attachment FUNCTIONAL CHARACTERIST    | •     |     | •   | •    | •   | •   | •  | •          | •  | •   | • •  | •   | • | • | • | •   | •  | 5-5  |

| FUNCTIONAL CHARACTERIST                   | ICS   | • • | •   | •    | •   | •   | •  | •          | •  |     | •    | •   | • | • | • | •   | •  | 5-5  |

| I/O Operations<br>I/O Processor Operation | •     |     | •   | •    | •   | •   | •  | •          | •  | •   |      | •   | • | • | • | •   | •  | 5-6  |

| I/O Processor Operation                   | s.    | • • | •   | •    | •   | •   | •  | •          | •  | •   | • •  | •   | • | • | • | •   | •  | 5-7  |

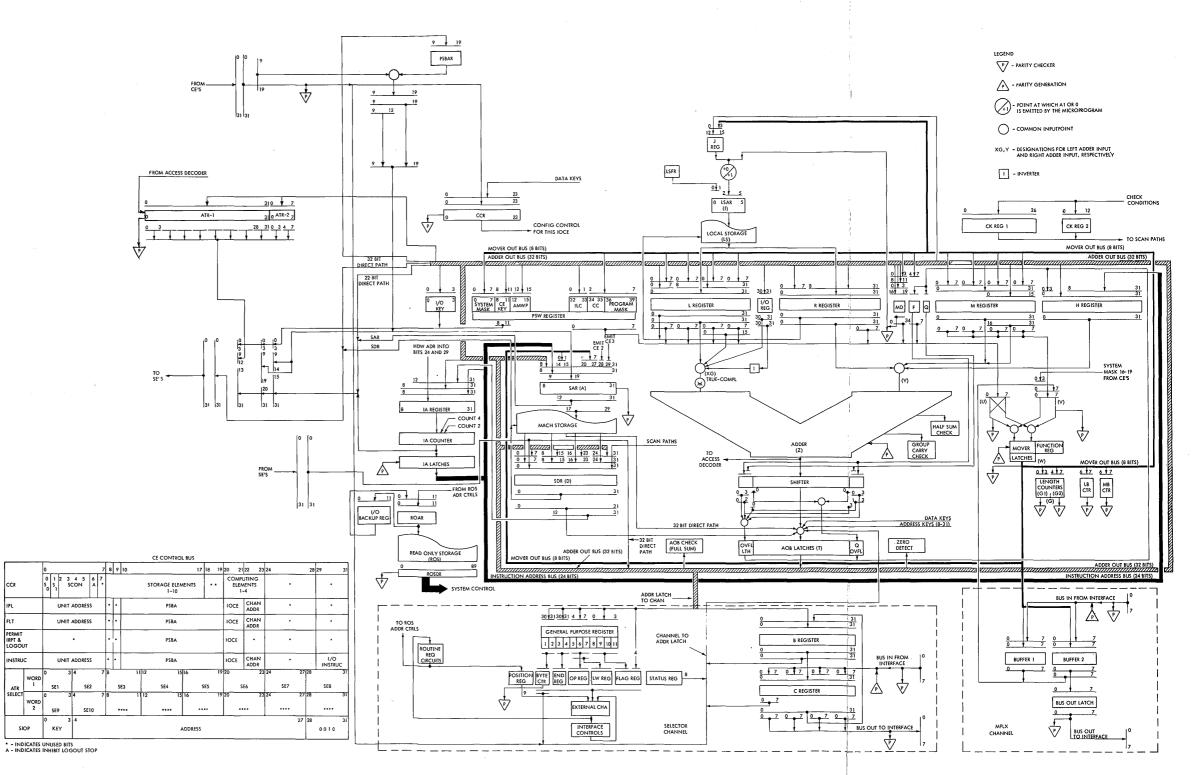

| Data Flow, 2nd Diagram.                   | •     |     | •   | •    | •   | •   | •  | •          | •  | •   | • •  | •   | • | • | • | •   | •  | 5-7  |

| Common Logic Unit                         | •     |     | •   | •    | •   | •   | •  | •          | •  | •   |      | •   | • | • |   | •   | •  | 5-8  |

| Channels                                  |       |     |     |      |     |     |    | • •        | •  | •   |      |     |   |   |   |     |    | 5-9  |

| Channel-to-Channel Adap                   | ter   | ·   |     |      |     |     |    |            |    |     |      |     |   |   |   |     |    | 5-10 |

| Interfaces<br>DESIGN DETAILS              | •     |     |     | •    | •   | •   |    |            |    | •   |      | •   | • |   | • | •   | •  | 5-10 |

| DESIGN DETAILS                            | •     |     |     | •    | •   |     |    |            |    | •   |      | .•  |   |   | • | •   |    | 5-11 |

| Internal Design Details                   |       |     |     |      |     |     |    | •          | •  | •   |      |     |   | • |   | •   |    | 5-11 |

| Data Flow Registers                       |       |     |     |      |     |     |    |            |    | •   |      |     |   |   |   |     | •  | 5-11 |

| 360 Mode Operation                        |       |     |     |      |     |     |    |            |    |     |      |     |   |   |   |     |    | 5-23 |

| Control                                   | •     |     |     |      |     |     |    |            |    |     |      |     | Ì |   |   |     |    | 5-23 |

| Microprogram Control                      |       |     |     |      |     |     |    |            |    |     |      | -   | ÷ | - |   |     |    | 5-23 |

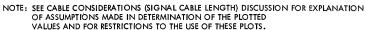

| Selector Channel Organi                   | zat   | ion |     | •    |     |     | •  |            |    |     |      | •   |   | · |   | Ī   |    | 5-24 |

| Channel Output Operatio                   | n     |     | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 5-25 |

| Channel Input Operation                   |       | ••• | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  |      |

| Multiplexor Channel Org                   | 2 n i | • • | i   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 5-26 |

| Input/Output Operation.                   | anı   | Jac | 101 | 1.   | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 5-27 |

| Interruption Preparatio                   | •     | • • | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •. | 5-28 |

| Checking                                  |       | ••• | •   | •    | •   | •   | •  | • .        | •  | •   | •••  | • ` | • | • | • | •   | •  | 5-20 |

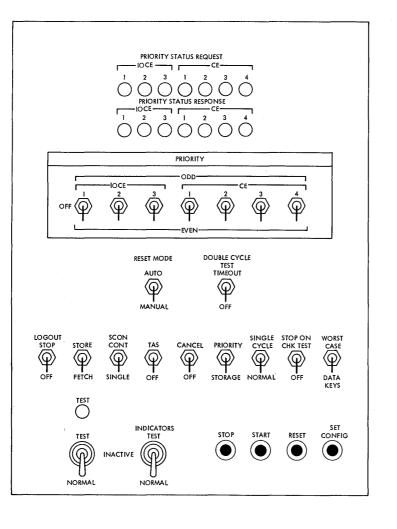

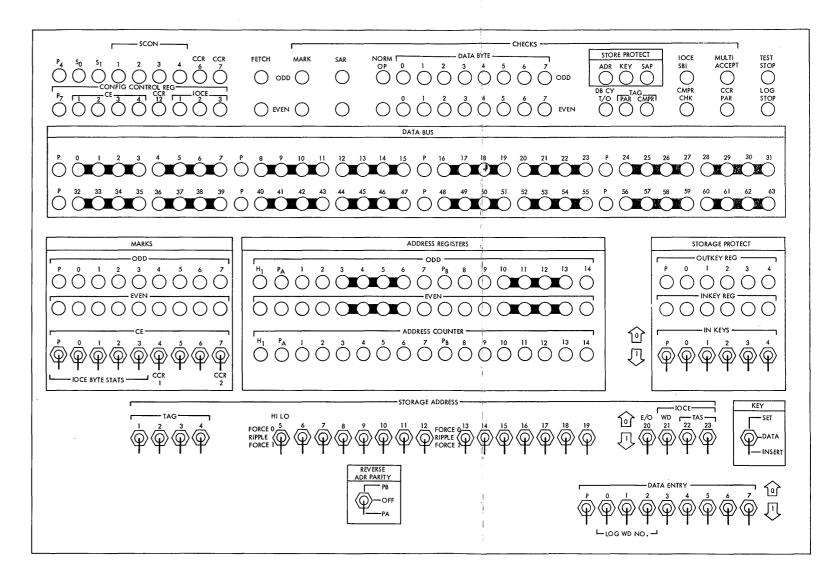

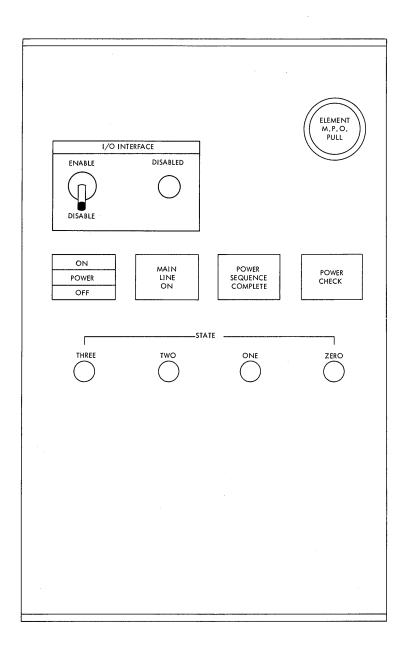

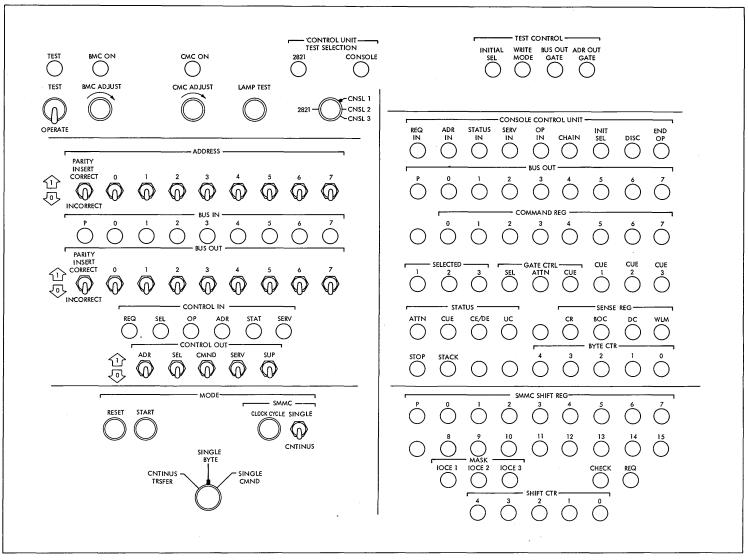

| IOCE CONTROL PANEL                        | •     | ••• | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 5-34 |

| ICCE CONTROL PANEL                        | •     | ••• | •   | •    | •   | •   | •  | •          | •  | •   | ••   | •   | • | • | • | •   | •  | 5-54 |

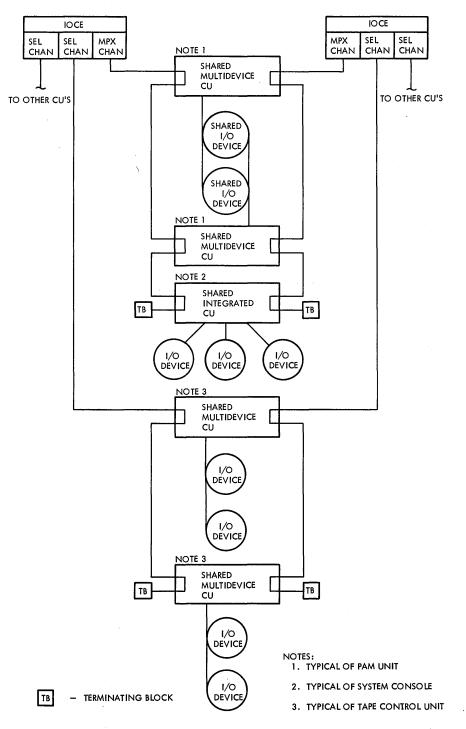

| CHAPTER 6. IBM 7289-02                    | DE    | PTD | HEI | RAT. | . д | בח  | рψ | <b>R</b> I | M  | זסס | T.F. |     |   |   |   |     |    | 6-1  |

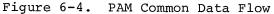

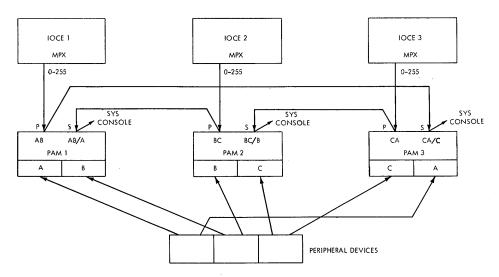

| INTRODUCTION                              |       |     |     |      |     | 011 |    |            |    | 000 |      | •   | • | • | • | •   | •  | 6-1  |

| INTRODUCTION                              | •     | • • | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-1  |

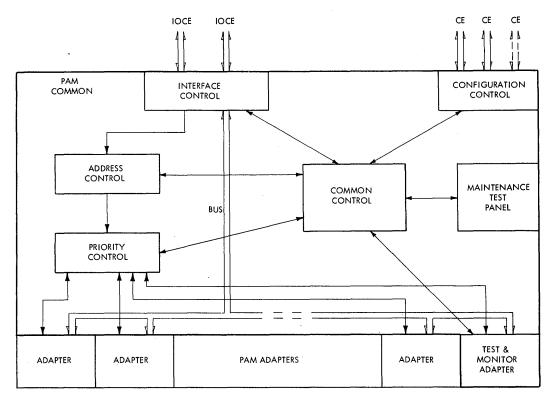

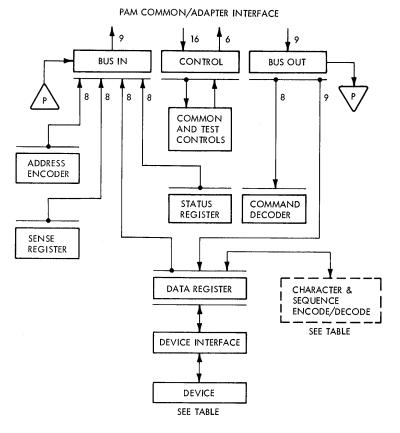

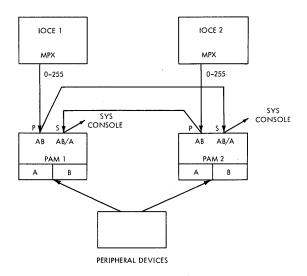

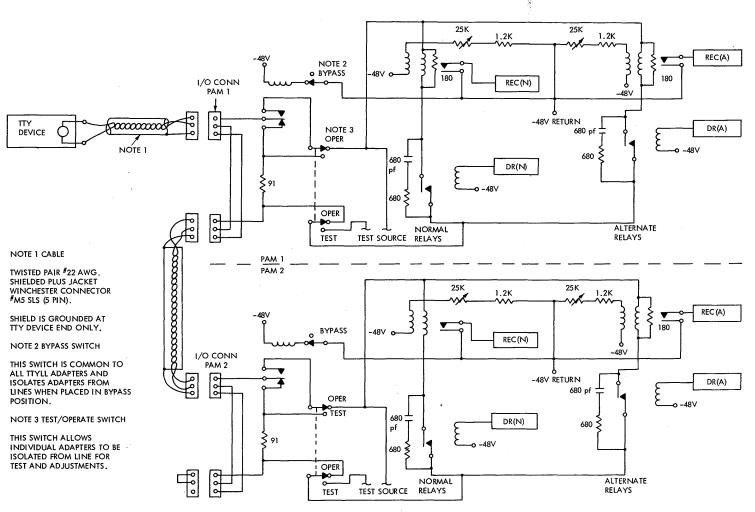

| PAM Common                                | •     | ••• | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-1  |

| Adapters.                                 | •     | ••• | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-2  |

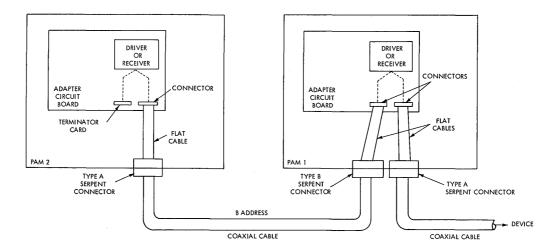

| Connection and Terminat                   |       |     |     |      |     |     |    |            |    |     |      |     |   |   |   |     |    |      |

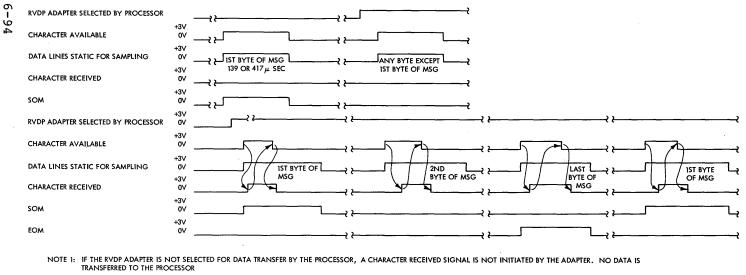

| FUNCTIONAL CHARACTERIST                   |       |     |     |      |     |     |    |            |    |     |      |     |   |   |   |     |    |      |

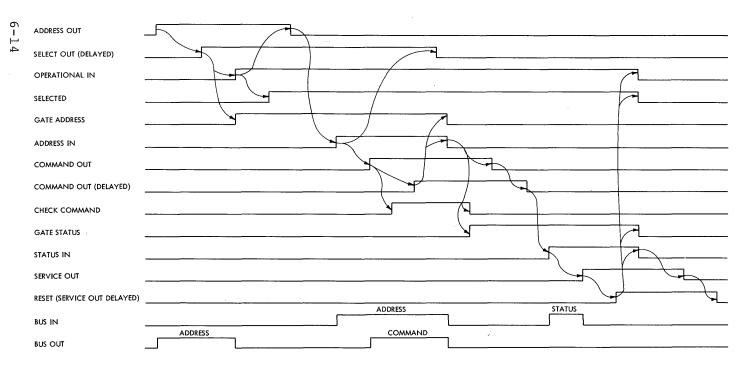

| Initial Selection                         | тса   | ••• | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-5  |

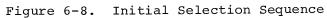

| Data Servicing                            | •     | ••• | •   | •    | •   | •   | •  | •          | •  | • . | ••   | •   | • | • | • | •   | •  | 6-6  |

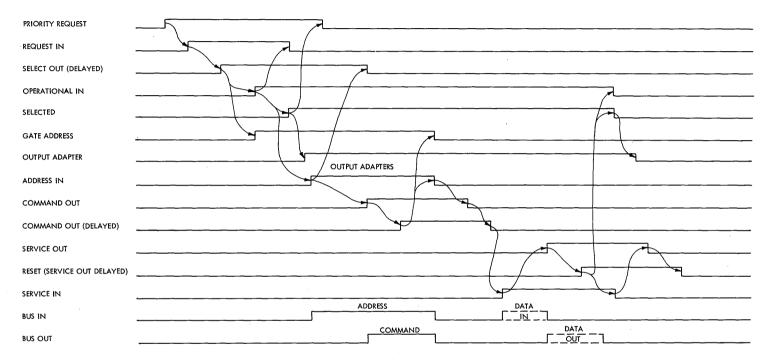

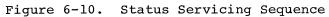

| Status Servicing                          | •     | • • | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-6  |

|                                           |       |     |     |      |     |     |    |            |    |     |      |     |   |   |   |     |    |      |

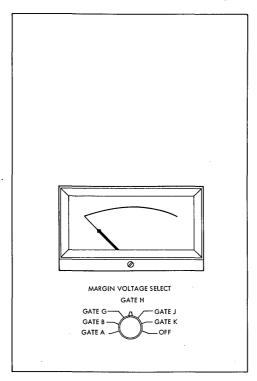

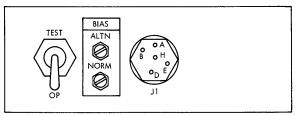

| Test and Monitor Adapte                   |       |     |     |      |     |     |    |            |    | •   | •••  | •   | • | • | • | •   | •  | 6-7  |

| Maintenance Test Panel.                   |       |     |     |      |     |     |    |            | •  | •   | •••  | •   | • | • | • | •   | •  | 6-7  |

| DESIGN DETAILS                            |       |     |     |      |     | •   | •  | •          | •  | •   | ••   | •   | • | • | • | •   | •  | • •  |

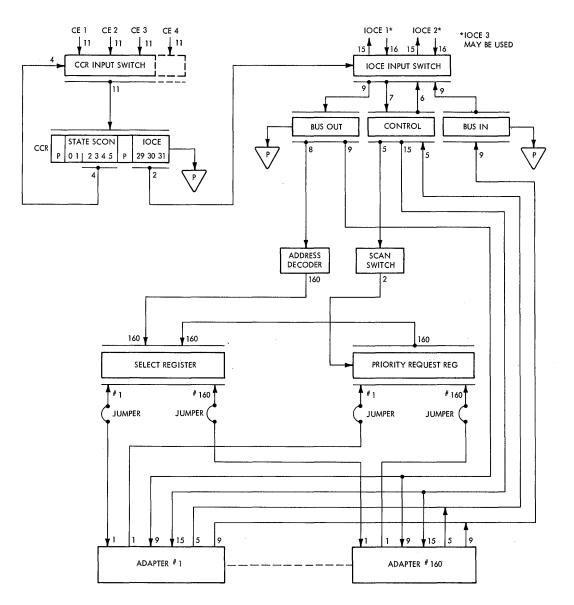

| PAM Common.                               |       |     |     |      |     | •   | •  | •          | •  | •   | • •  | •   | • | • | • | •   | •  | 6-7  |

| Test and Monitor Adapte                   |       |     |     |      |     |     | •  | •          | •  | •   | ••   | •   | • | • | • | •   | •  | 6-18 |

| Maintenance Panel                         | •     | • • | •   | •    | •   |     | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-27 |

| Relay Test Panel Adapte                   | rs    | • • | •   | •    | •   | •   | •  | •          | •  | •   | ••   | •   | • | • | • | •   | •  | 6-32 |

| Operators Panel                           | •     | • • | •   | •    | •   | •   | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-33 |

| ADAPTERS                                  |       |     |     |      |     |     | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-35 |

| General Purpose Input A                   |       |     |     |      |     |     | •  | •          | •  | •   | •••  | •   | • | • | • | •   | •  | 6-36 |

| General Purpose Output                    | Ada   | pte | r.  | •    | •   | •   | •  | •          | •  | •   | • •  | •   | • | • | • | •   | •  | 6-46 |

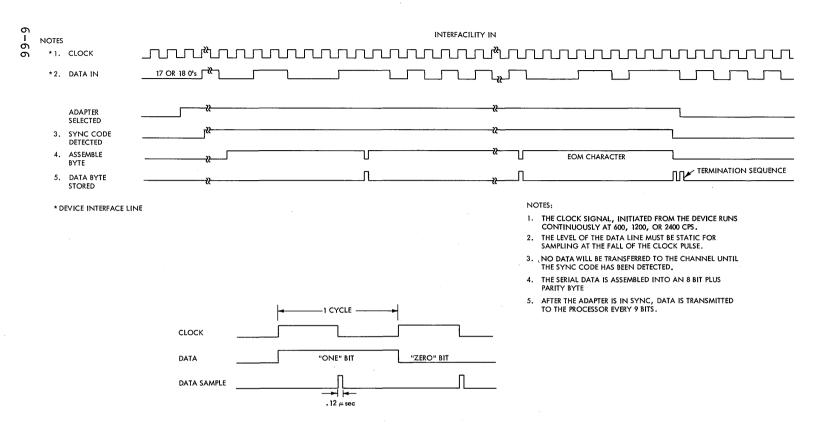

| Interfacility Input Ada                   | pte   | er. | •   | •    | •   | •   | •  | •          | •  | •   |      | •   | • | • | • | •   | •  | 6-58 |

iii

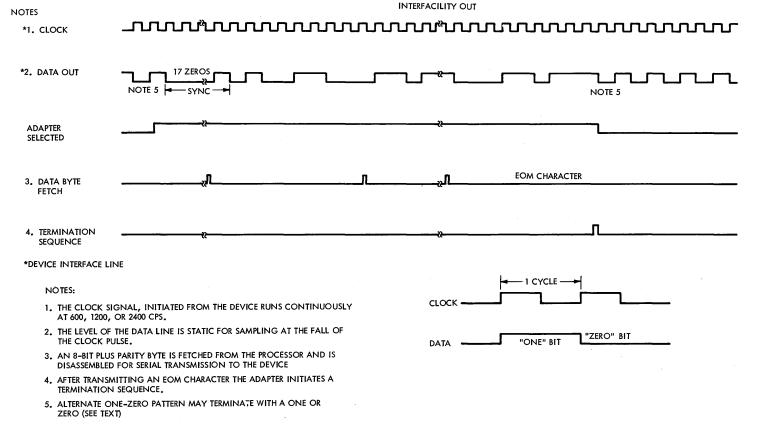

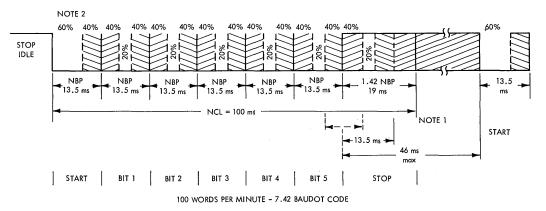

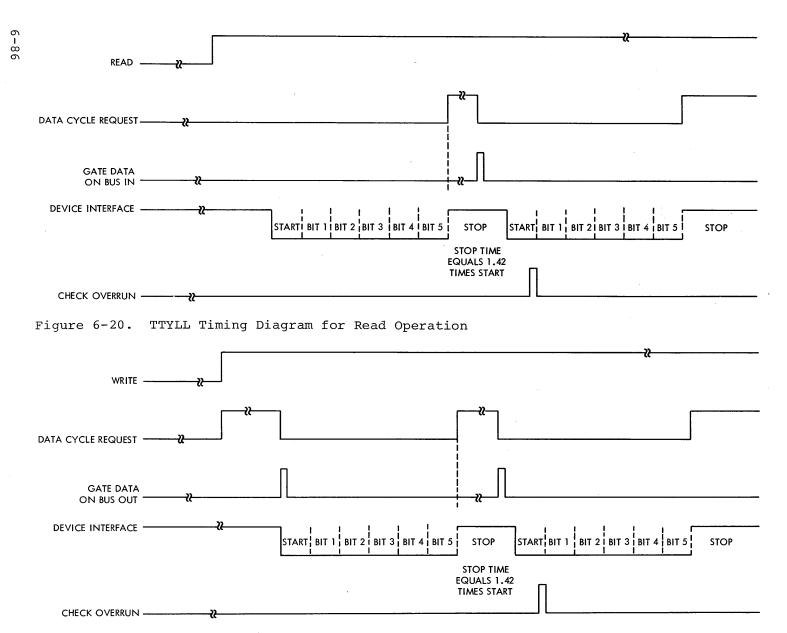

| Interfacility Output Adapter.6-6Teletypewriter, Half-Duplex, Long Line Adapter.6-7Radar Video Data Processor Adapter (RVDP)6-81052 Keyboard Adapter6-9Common Digitizer Adapter.6-1Flight Data Entry Entry and Printout Adapter.6-1Buffer Processor Adapter.6-1                                                                                                                   | 4<br>5<br>19<br>29<br>47                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

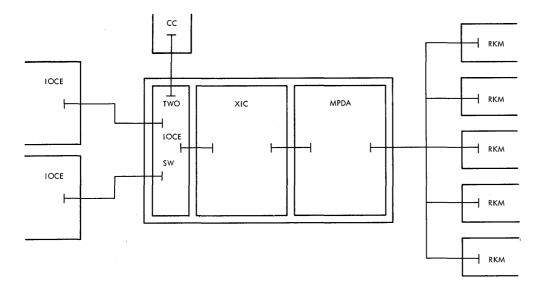

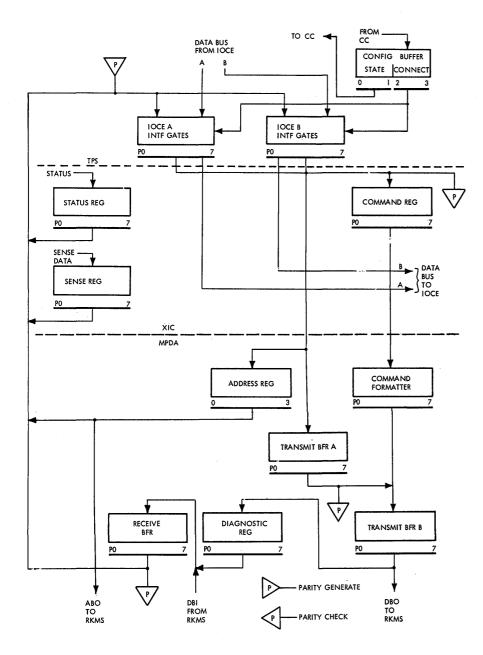

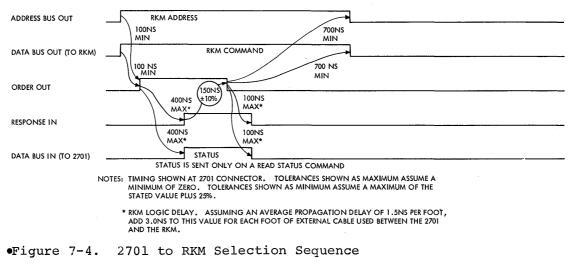

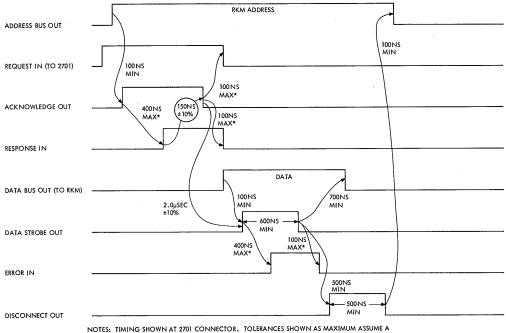

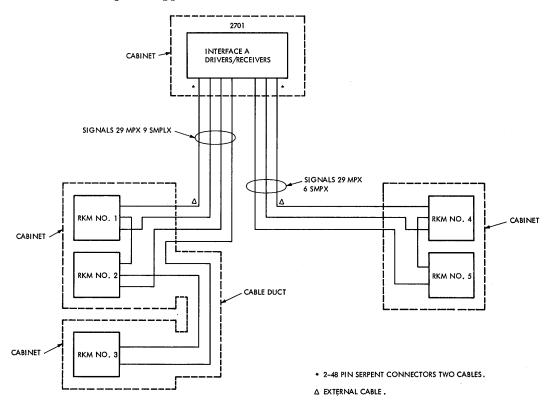

| CHAPTER 7. DATA ADAPTER UNIT 2701-017-1INTRODUCTION.7-1FUNCTIONAL DESCRIPTION.7-1DESIGN DETAILS.7-2Two Processor Switch (TPS).7-2Transmission Interface Converter (XIC).7-3Modified Parallel Data Adapter (MPDA)7-1Simplex Lines7-1DAU/RKM Interface Sequences7-1Electrical Characteristics - Multiplex Signals7-2                                                               | -1<br>-4<br>-9<br>-9                                          |

| Electrical Characteristics - Simplex Signals7-2MAINTENANCE PANELS7-2Operators Panel7-2CE Panel7-2CE Panel7-2                                                                                                                                                                                                                                                                     | 24                                                            |

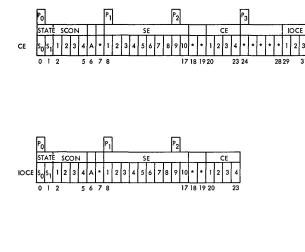

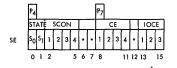

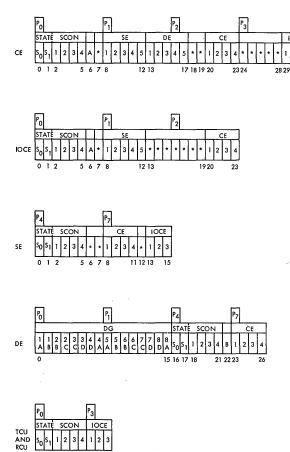

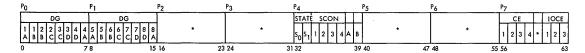

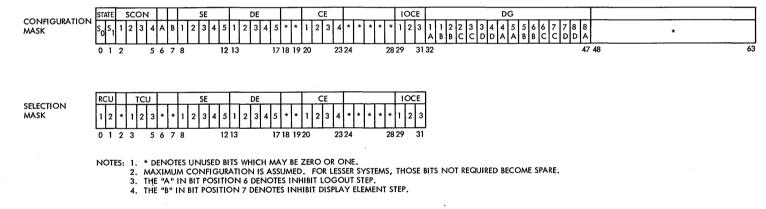

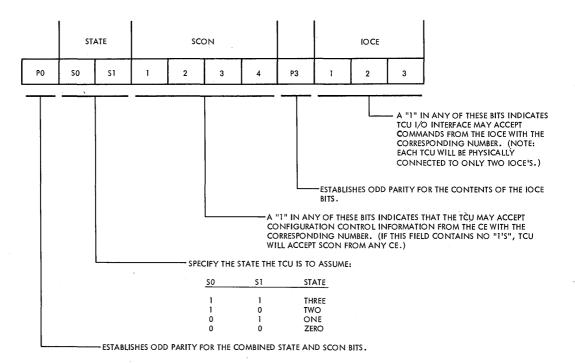

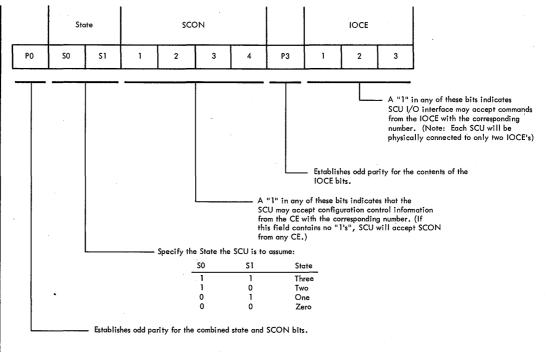

| CHAPTER 8. CONFIGURATION CONTROL8-1INTRODUCTION.8-1GENERAL CHARACTERISTICS8-1GENERAL DESCRIPTION OF ELEMENT STATES8-2State Three8-2State Two8-2State One8-4State Zero.8-4SCON INSTRUCTION.8-5CONFIGURATION CONTROL REGISTER.8-9Selection Mask.8-9SYSTEM MONITORING8-9Program Communication8-1Overall Operation8-1                                                                |                                                               |

| System Facilities8-1Logout8-1Logout8-1Special Element and System Condition Signals8-2                                                                                                                                                                                                                                                                                            | .3                                                            |

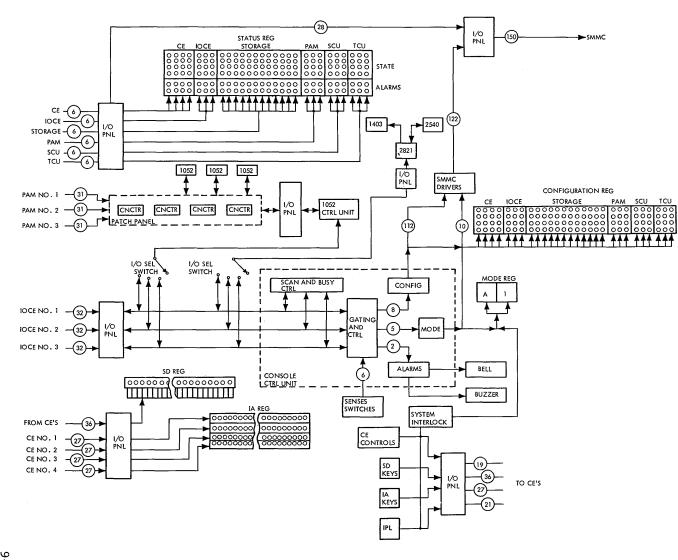

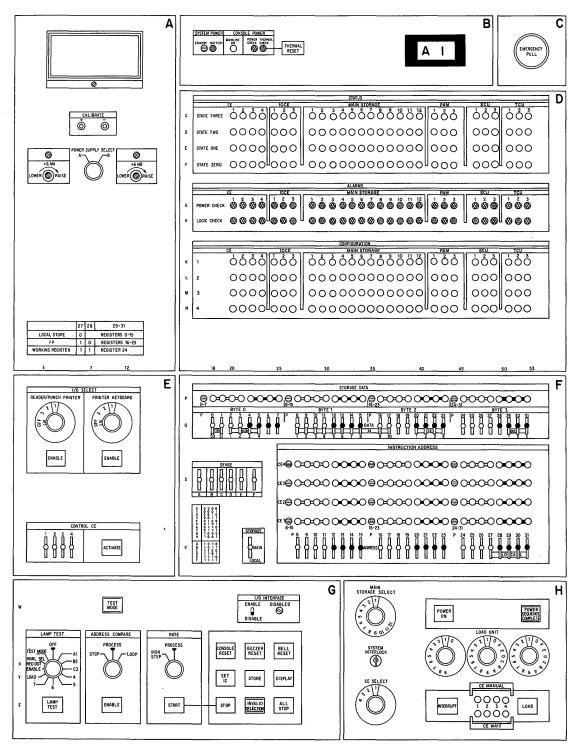

| CHAPTER 9. IBM 7265-02 SYSTEM CONSOLE. 9-1<br>GENERAL 9-1<br>FUNCTIONAL OPERATION 9-1<br>Operator Intervention 9-1<br>Program Generated Control and Status. 9-1<br>CONSOLE INDICATORS, KEYS AND SWITCHES 9-1<br>Console Indicators. 9-1<br>Console Keys and Switches 9-1<br>POWER CONTROL, MARGINAL CHECKING, AND INDICATORS. 9-2<br>Power Switches 9-2<br>Power Indicators. 9-2 | L<br>L<br>L<br>L<br>L<br>J<br>J<br>J<br>J<br>J<br>G<br>Z<br>Z |

iv

| $\sim$     |   |                                                                                                    |

|------------|---|----------------------------------------------------------------------------------------------------|

| · · · · ·  | * |                                                                                                    |

|            |   |                                                                                                    |

|            |   |                                                                                                    |

|            |   |                                                                                                    |

|            |   |                                                                                                    |

|            | , |                                                                                                    |

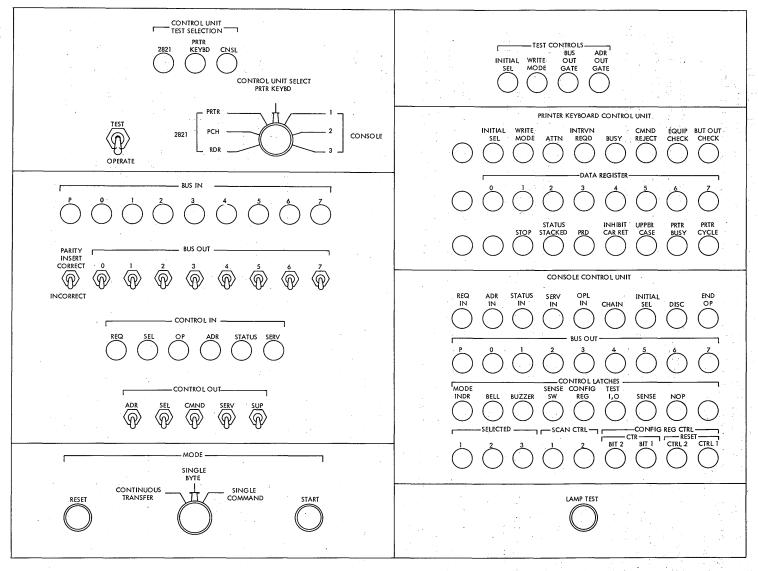

|            |   | MAINTENANCE AND TEST                                                                               |

|            |   | Controls and Switches                                                                              |

|            |   | Indicators                                                                                         |

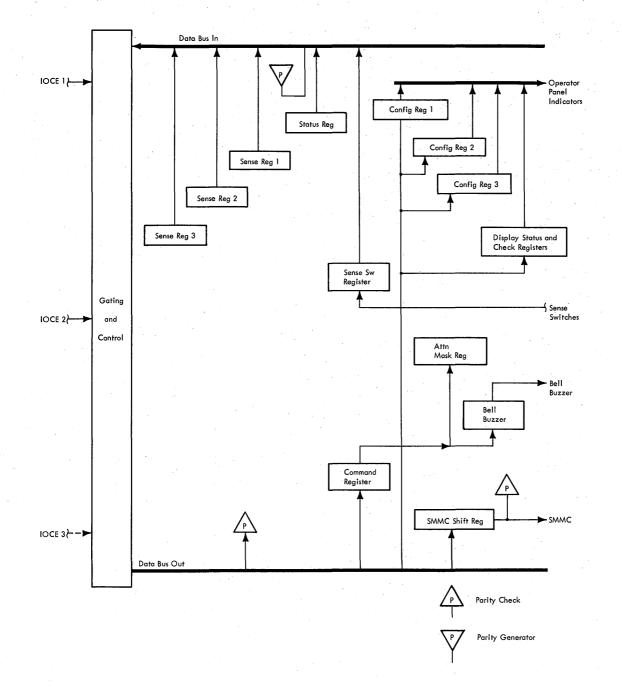

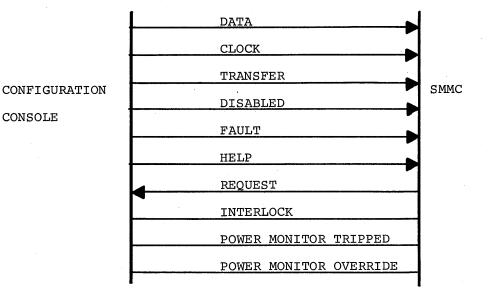

| ·          |   | SYSTEM MAINTENANCE MONITOR CONSOLE INTERFACE                                                       |

|            |   | Interface Signals                                                                                  |

|            |   | ELECTRICAL CHARACTERISTICS                                                                         |

|            |   | Configuration and Mode Indicator Signals 9-32                                                      |

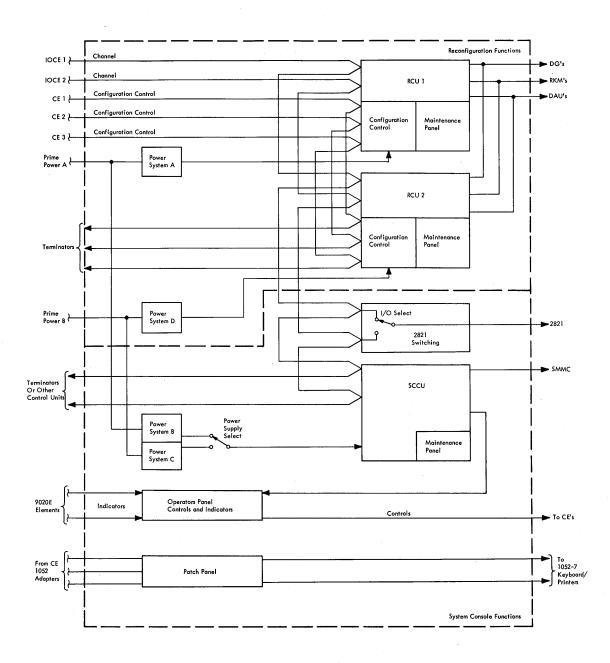

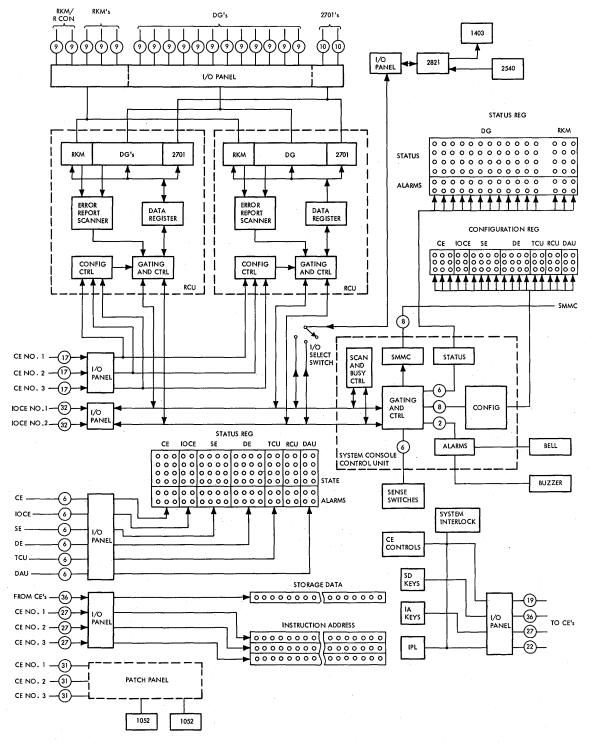

|            |   | CHAPTER 10. CONFIGURATION CONSOLE                                                                  |

|            |   | INTRODUCTION                                                                                       |

|            |   | SYSTEM CONSOLE FUNCTIONAL OPERATION 10-1                                                           |

|            |   | Operator Intervention                                                                              |

|            |   | Program Generated Control and Status 10-11<br>Program Generated SMMC Messages and Controls 10-14   |

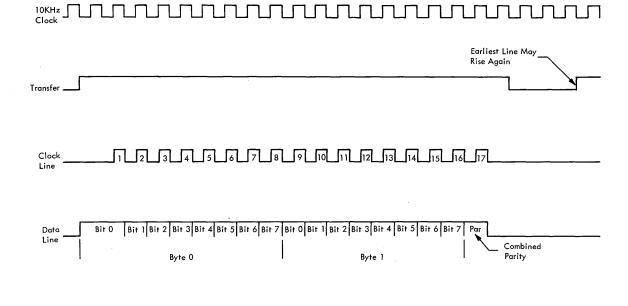

|            |   | Program Generated SMMC Messages and Controls 10-14<br>SMMC Interface General Characteristics 10-16 |

|            |   | SCCU Status Information                                                                            |

|            |   | SCCU Sense Information                                                                             |

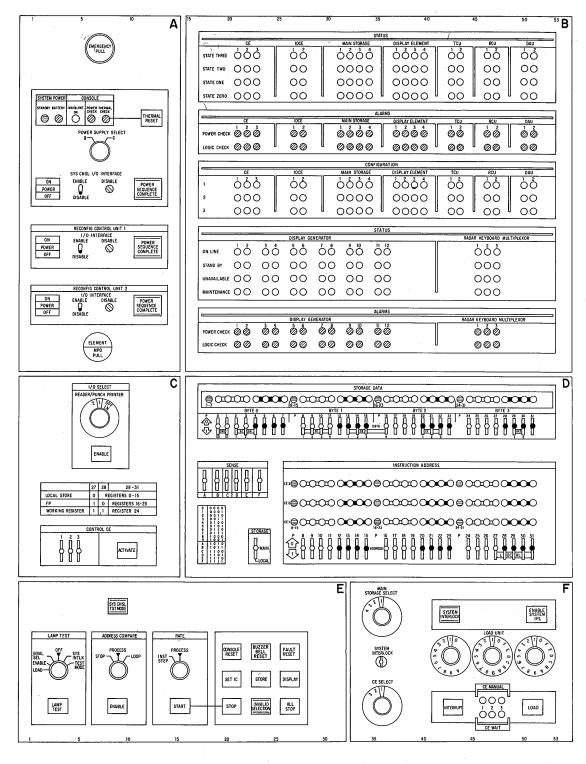

|            |   | CONSOLE INDICATORS, KEYS AND SWITCHES                                                              |

|            |   | Console Indicators                                                                                 |

|            |   | Console Keys and Switches                                                                          |

|            |   | RECONFIGURATION FUNCTION                                                                           |

| ()         |   | Functional Characteristics.                                                                        |

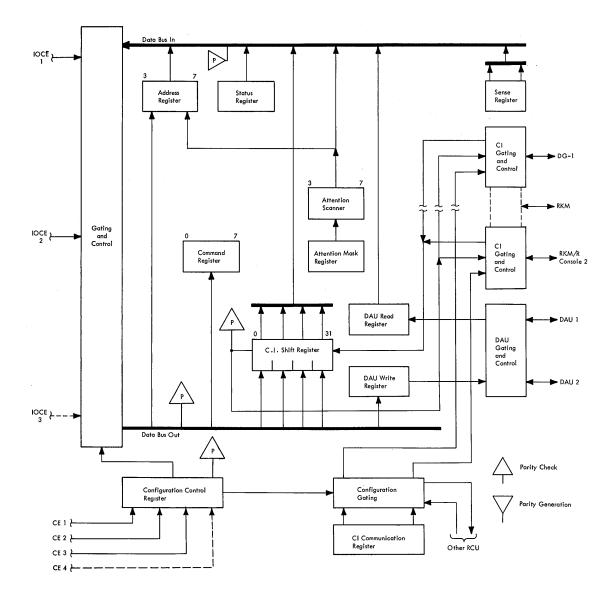

|            |   | DESIGN DETAILS                                                                                     |

|            |   | POWER CONTROL AND INDICATORS                                                                       |

|            |   | General                                                                                            |

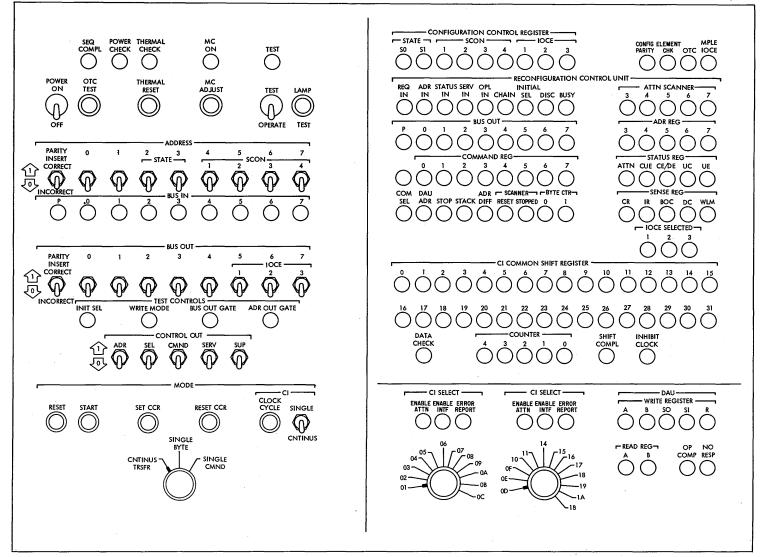

|            |   | MAINTENANCE PANELS.         10-68           SCCU Maintenance Panel.         10-68                  |

|            |   | RCU Maintenance Panel                                                                              |

|            |   |                                                                                                    |

|            |   | CHAPTER 11. INPUT/OUTPUT EQUIPMENT                                                                 |

|            |   | GENERAL CHARACTERISTICS                                                                            |

|            |   | Magnetic Tape Equipment                                                                            |

|            |   | Disk Storage Equipment                                                                             |

|            |   | Card Read Punch - Line Printer Equipment                                                           |

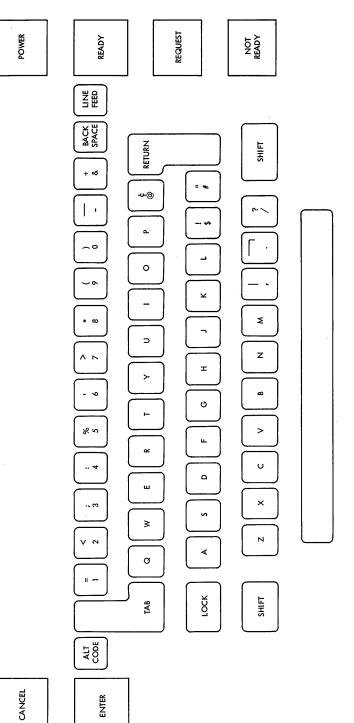

|            |   | Printer Keyboard                                                                                   |

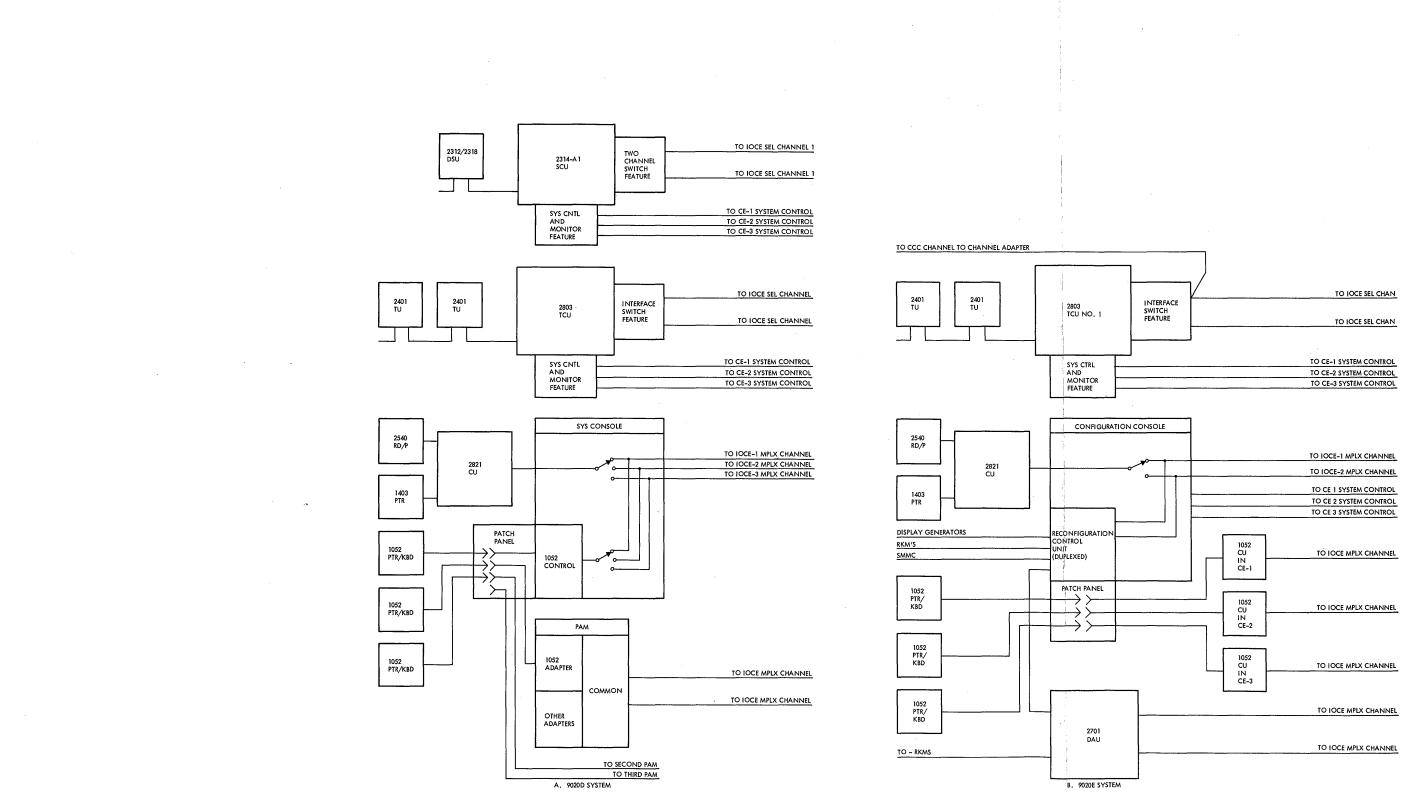

|            |   | FUNCTIONAL CHARACTERISTICS       11-7         IBM 2803 TCU with 2401 TCU's       11-7              |

|            |   | IBM 2314-A1 SCU with 2312-A1/2318-A1 DSUs                                                          |

|            |   | IBM 2821 CU with 2540 and 1403                                                                     |

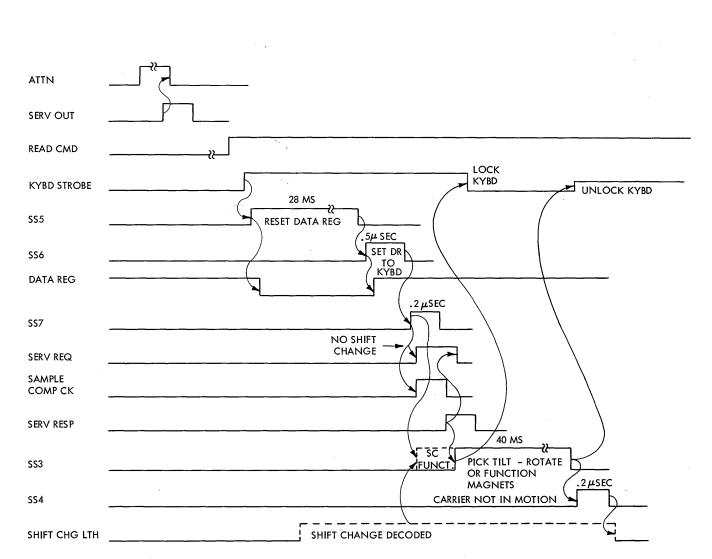

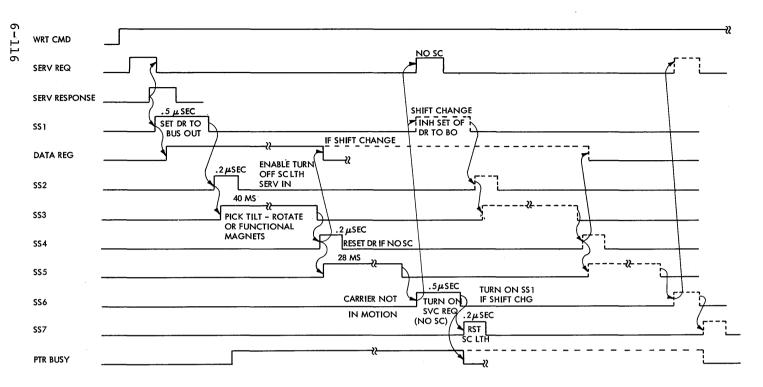

|            |   | IBM 1052 Printer-Keyboard                                                                          |

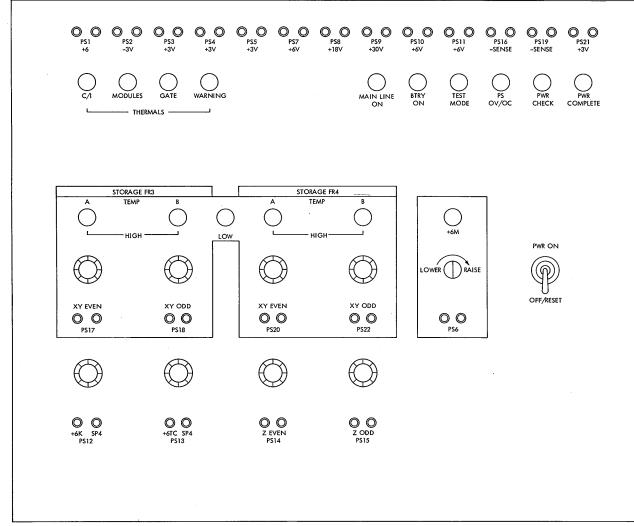

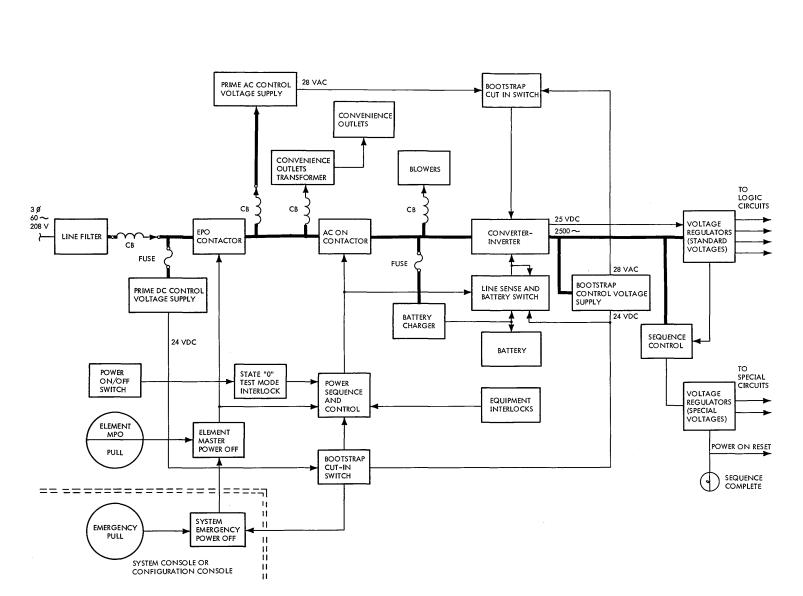

|            |   | CHAPTER 12. POWER CONTROL                                                                          |

|            |   | INTRODUCTION. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $12-1$       |

|            |   | SYSTEM POWER CONTROL FACILITIES                                                                    |

|            |   | Power Control Functions                                                                            |

|            |   | Element Indicators - Local                                                                         |

|            |   | Power System Interruptions                                                                         |

|            |   | System Power On/Off                                                                                |

|            |   | Element Power Equipment                                                                            |

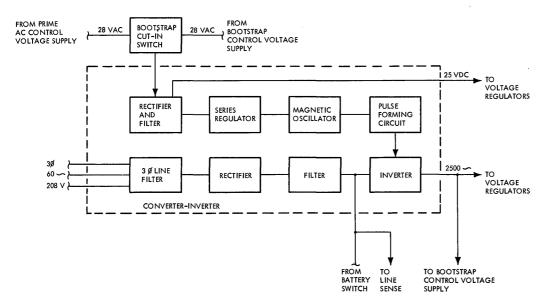

|            | - | Power Control and Sequencing                                                                       |

| $\bigcirc$ |   | Converter-Inverter                                                                                 |

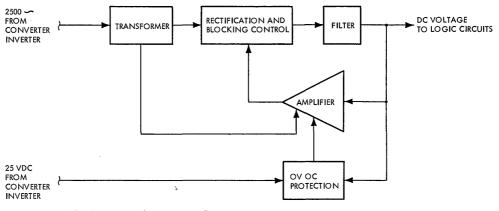

|            |   | AC/DC Regulators                                                                                   |

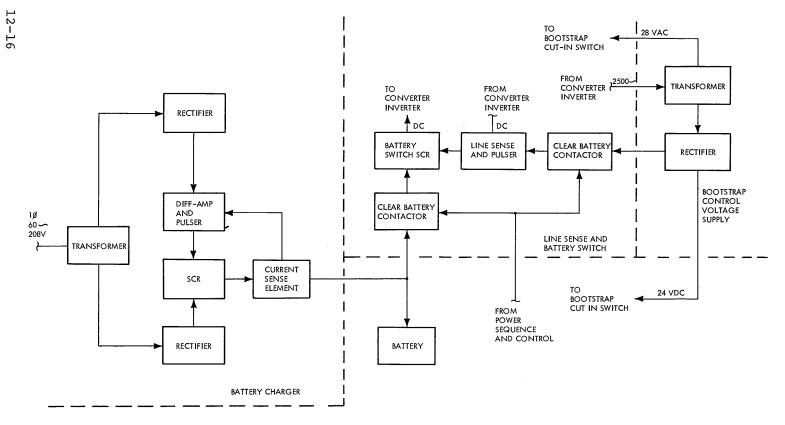

|            |   | Battery Back-up System                                                                             |

|            |   | v                                                                                                  |

|            |   |                                                                                                    |

| · ·        |   |                                                                                                    |

|            |   |                                                                                                    |

· ·

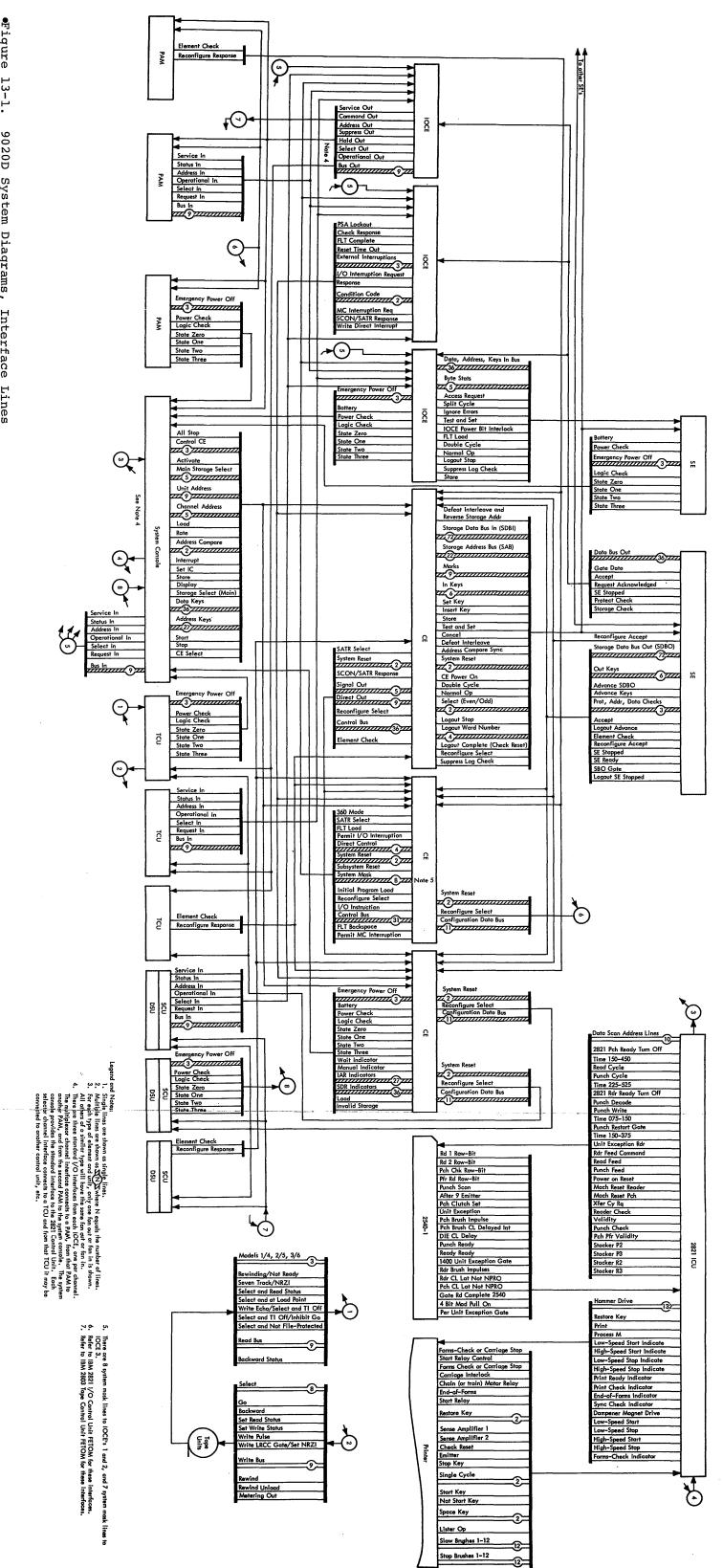

| CHAPTER 13. INTERFACE LINES                |       |

|--------------------------------------------|-------|

| CHAPTER 13. INTERFACE LINES                | 13-1  |

| PART I. 9020D SYSTEM                       | 13-1  |

| INTRODUCTION                               | 13-1  |

| CE-CE INTERFACE                            | 13-1  |

| CE/IOCE - SE INTERFACE                     | 13-6  |

| SYSTEM CONSOLE - SE INTERFACE              | 13-14 |

| CE - IOCE INTERFACE                        | 13-15 |

| IOCE - SYSTEM CONSOLE INTERFACE            | 12-20 |

| CE - SISTEM CONSULE INTERFACE              | 12 20 |

| CE - SYSTEM CONSOLE INTERFACE              | 13-20 |

| PAM - SYSTEM CONSOLE INTERFACE             | 13-24 |

| TCU - SYSTEM CONSOLE INTERFACE             | 13-25 |

| SCU - SYSTEM CONSOLE INTERFACE             |       |

| CE - SCU INTERFACE                         | 13-27 |

| SCU - CE INTERFACE                         | 13-28 |

| CE – TCU INTERFACE                         | 13-28 |

| TCU - CE INTERFACE                         | 13-29 |

| TCU - CE INTERFACE                         | 13-29 |

| PAM-CE INTERFACE                           | 13-30 |

| TCU - TAPE UNIT INTERFACE                  | 13-30 |

| Interface to Tape Unit                     | 12-20 |

|                                            | 12 20 |

|                                            | 13-32 |

| PRINTER - CONTROL UNIT (ICU) INTERFACE     | T3-33 |

| Interface to Printer                       | T3-33 |

| Interface to Control Unit                  | 13-36 |

| 2821 - 2540 INTERFACE                      | 13-38 |

| 2821 - 2540 INTERFACE                      | 13-38 |

| Interface from 2540                        | 13-41 |

| 9020D SYSTEM, EXTERNAL INTERFACE LINES     | 13-43 |

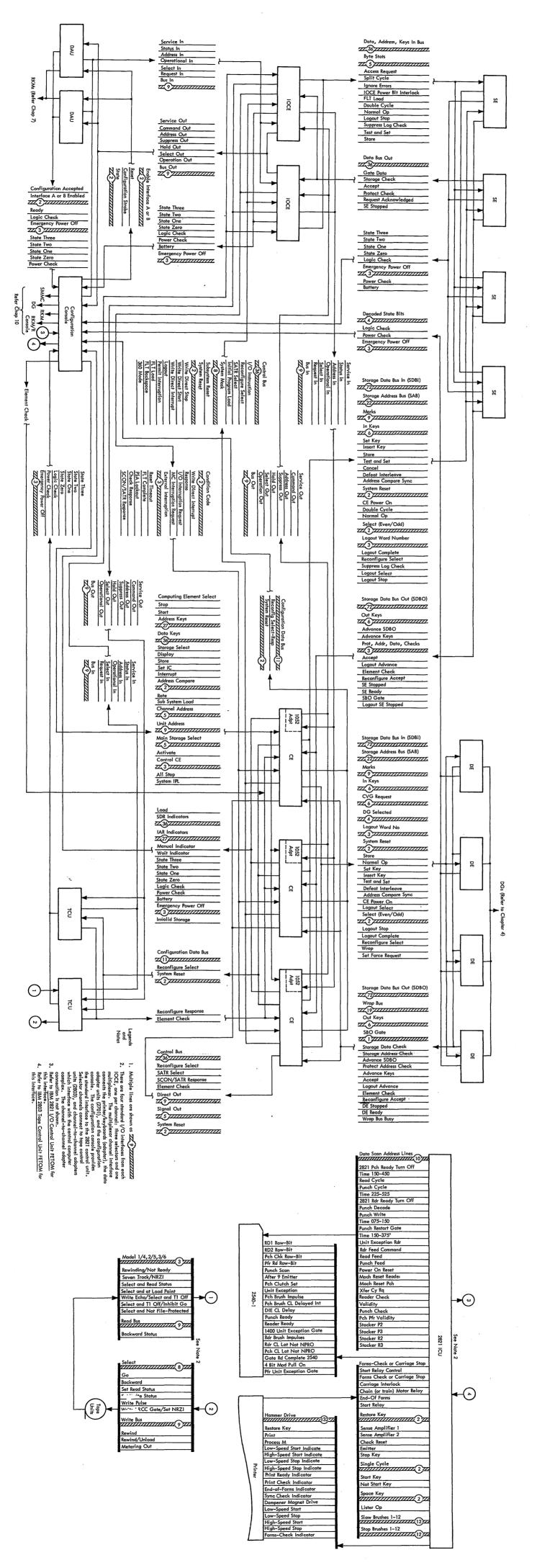

| PART 2. 9020E SYSTEM                       | 13-43 |

| CE - CE INTERFACE                          | 13-44 |

| CE/IOCE - SE INTERFACE                     | 13-44 |

| CONFIGURATION CONSOLE - SE INTERFACE       | 13-44 |

| CE - IOCE INTERFACE                        |       |

| IOCE - CONFIGURATION CONSOLE INTERFACE     | 13-44 |

| CE - CONFIGURATION CONSOLE INTERFACE       | 12-44 |

| CE - CONFIGURATION CONSOLE INTERFACE       | 10 47 |

| TCU - CONFIGURATION CONSOLE INTERFACE      | 13-47 |

| CE - TCU INTERFACE                         | 13-48 |

| CE - DE INTERFACE                          | 13-48 |

| Interface to DE                            | 13-48 |

| Interface from DE                          | 13-52 |

| DE - CC INTERFACE                          |       |

| 2701 - IOCE INTERFACE                      | 13-54 |

| CC - 2701 INTERFACE                        |       |

| TCU - TAPE UNIT INTERFACE                  |       |

| PRINTER - CONTROL UNIT INTERFACE           |       |

| CARD READER/PUNCH - CONTROL UNIT INTERFACE | 13-56 |

| GOODE SYSTEM SYMPEDIAL INTERPACE I THE     | 13-56 |

| 9020E SYSTEM, EXTERNAL INTERFACE LINES     | 12-56 |

|                                            | 12-20 |

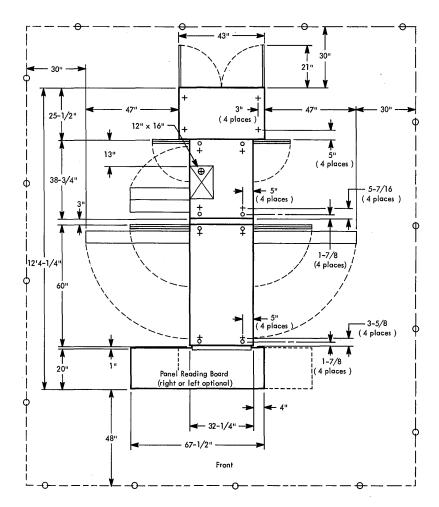

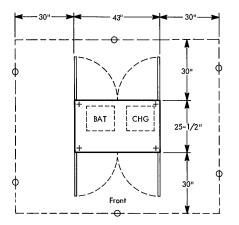

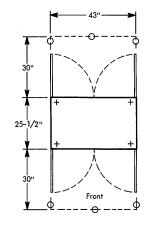

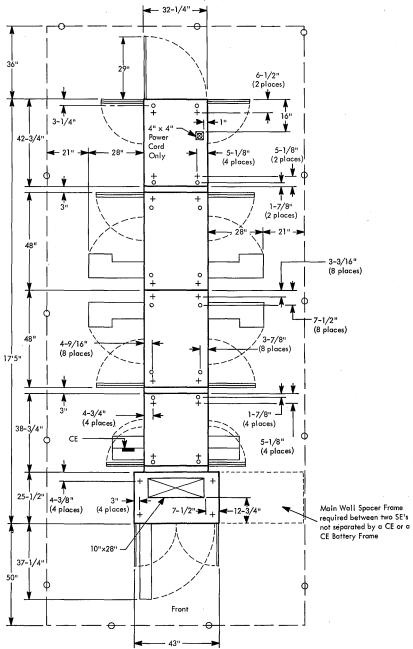

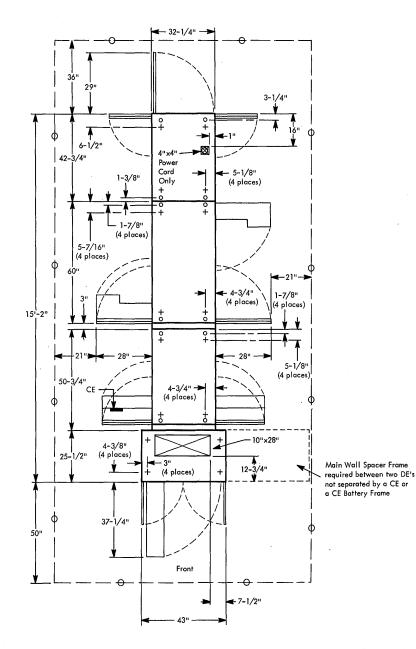

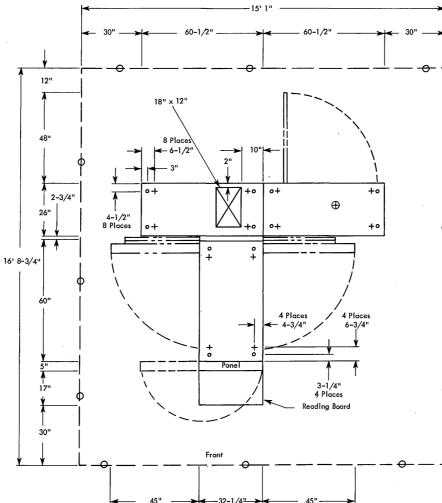

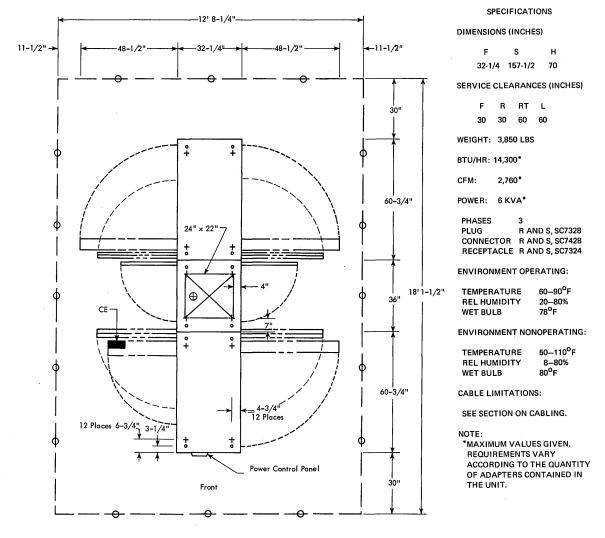

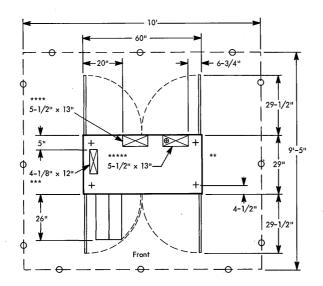

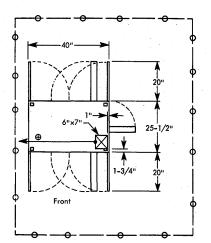

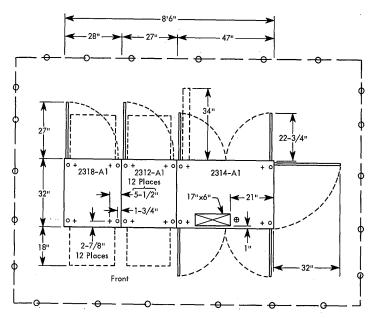

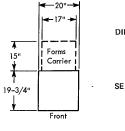

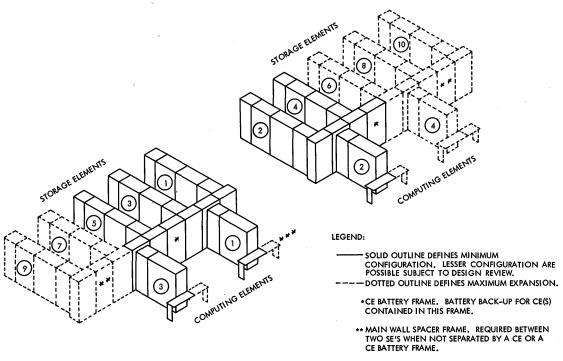

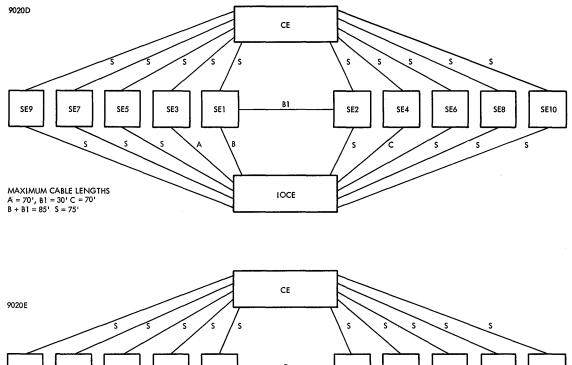

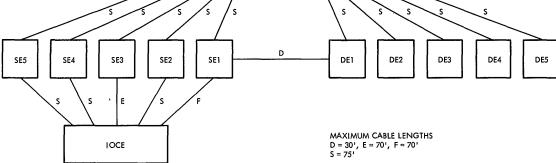

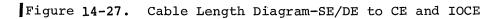

| CHAPTER 14. PHYSICAL PLANNING              | 14-1  |

|                                            |       |

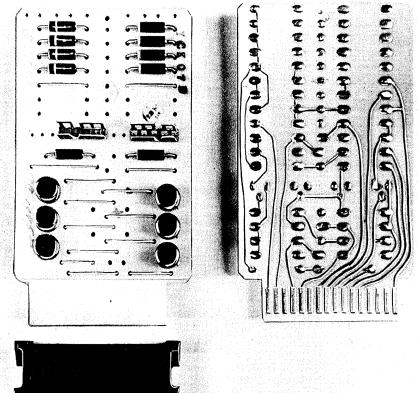

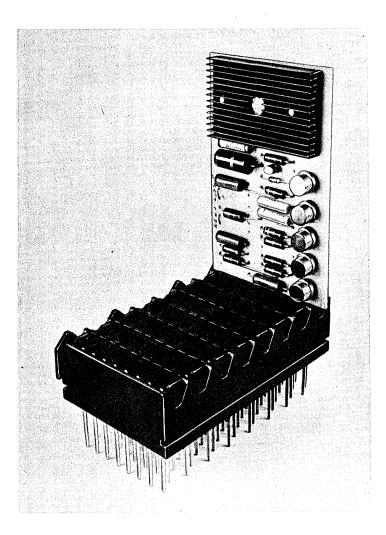

| TECHNOLOGIES.                              |       |

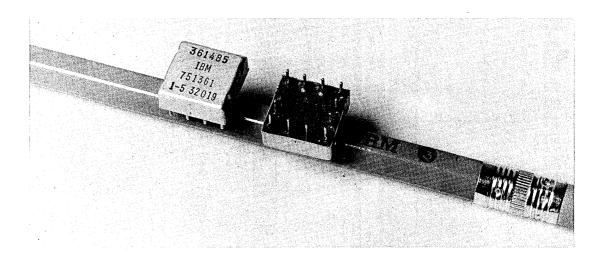

| Standard Modular System Packaging          | 14-1  |

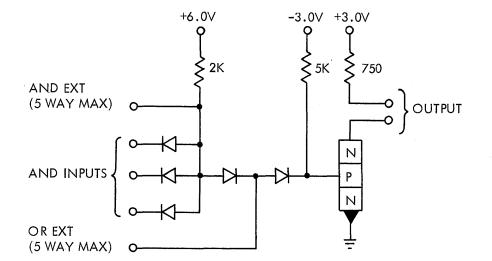

| Solid Logic Technology                     | 14-5  |

| WEIGHTS                                    | 14-7  |

|                                            |       |

)

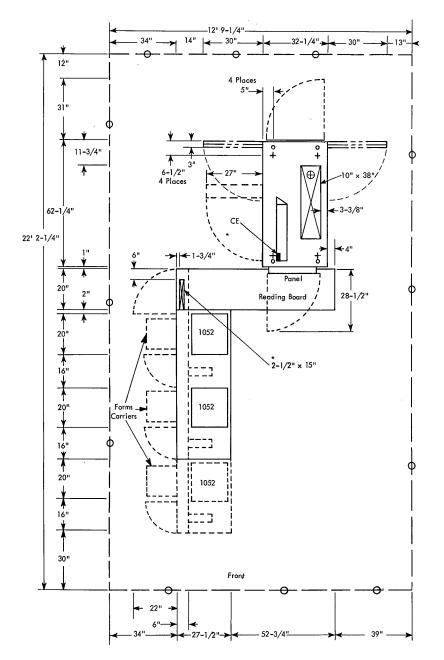

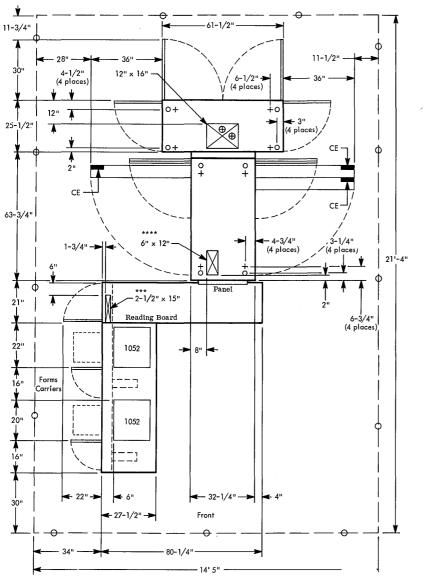

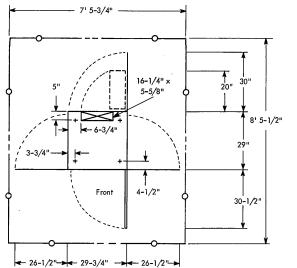

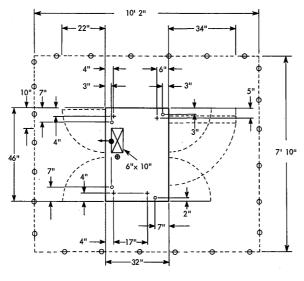

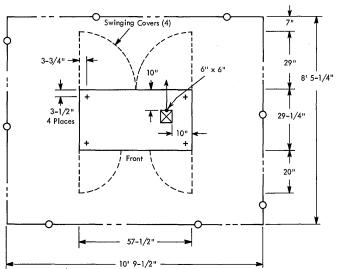

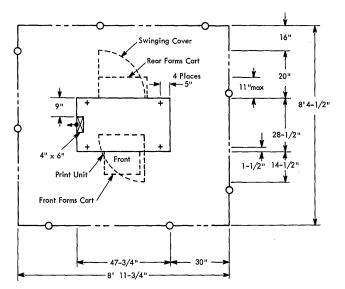

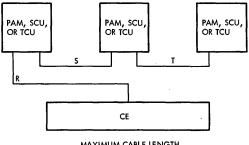

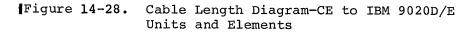

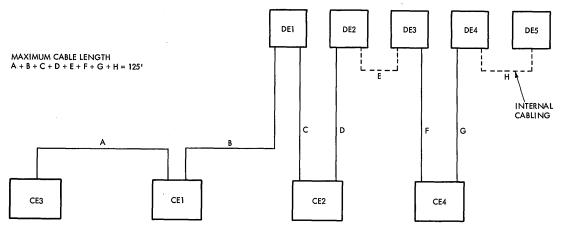

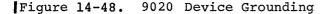

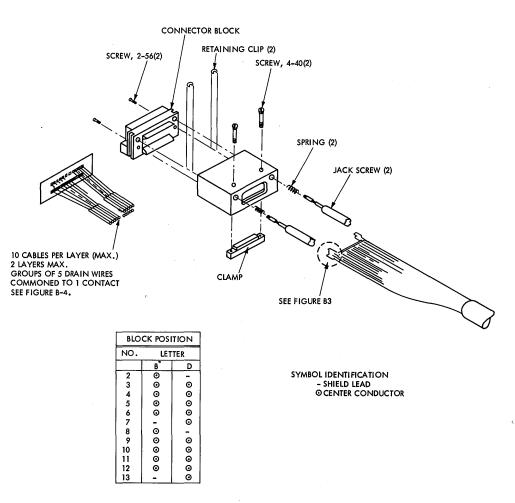

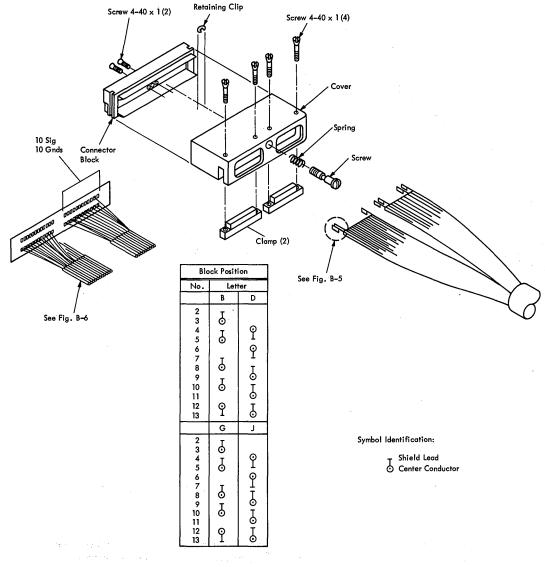

| OUTLINE DRAWINGS.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 14-8<br>14-26<br>14-36<br>14-38<br>14-48 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| APPENDIX A. APPLICABLE PORTIONS OF "IBM 9020D and 9020E<br>PRINCIPLES OF OPERATION"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A-1                                      |

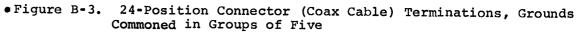

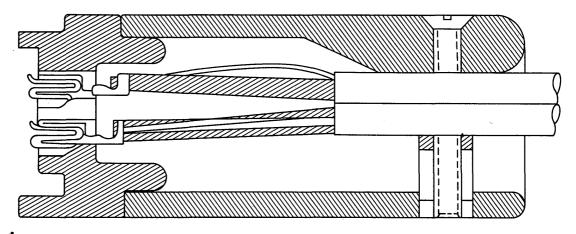

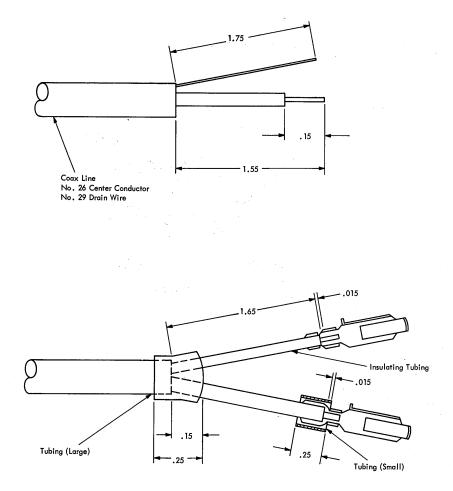

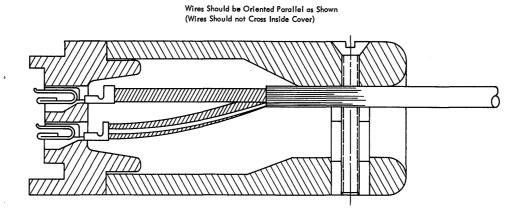

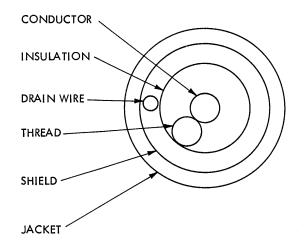

| APPENDIX B. EXTERNAL CABLE CONNECTORS AND CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>n</b> 1                               |

| OF COAX CABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B-1<br>B-1                               |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | в-1<br>В-1                               |

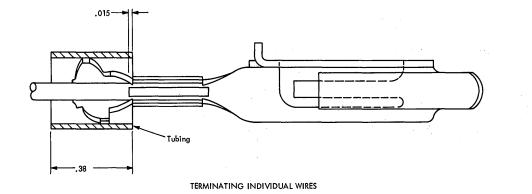

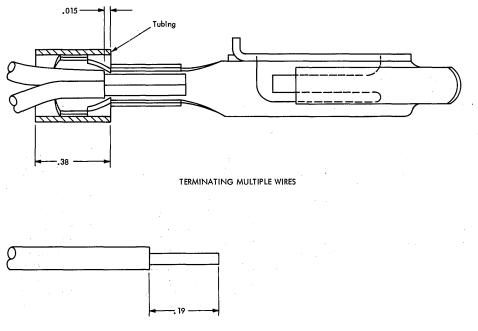

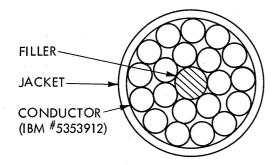

| Manufacturing Facilities for Cable Assemblies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | в-1<br>в-1                               |

| Serpent Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B-1 -                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| PAM Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B-9<br>B-9                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B-10                                     |

| Data Adapter Unit Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | B-10<br>B-10                             |

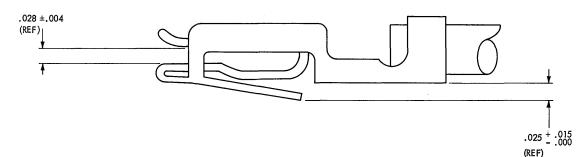

| CHARACTERISTICS OF COAX CABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| Bulk Cable, 20 Line, Coaxial.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B-12                                     |

| Burk Cable, 20 Line, Coaxial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D-12                                     |

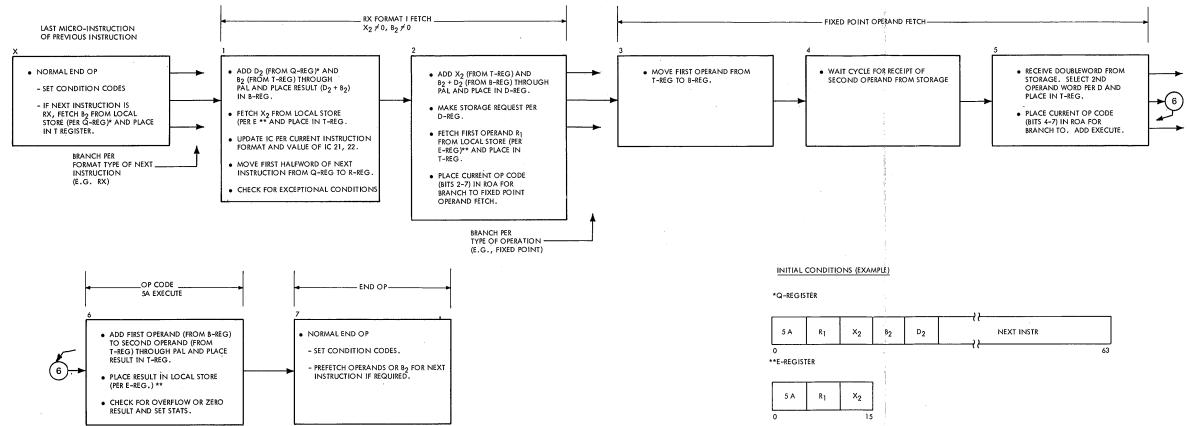

| APPENDIX C. EXAMPLE OF MICROPROGRAM CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C-1                                      |

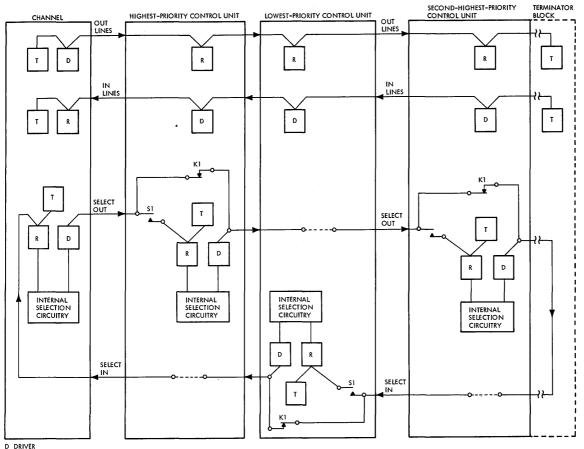

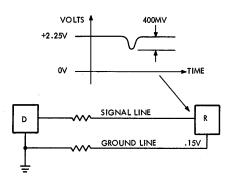

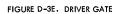

| APPENDIX D. INPUT/OUTPUT INTERFACE, CHANNEL TO DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |

| CONTROL UNIT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D-1                                      |

| PREFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D-1<br>D-1                               |

| INTRODUCTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| FUNCTIONAL DESCRIPTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          |

| ELECTRICAL SPECIFICATION, PHYSICAL REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-2<br>D-40                              |

| MECHANICAL REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D-46                                     |

| SYSTEM CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D-46                                     |

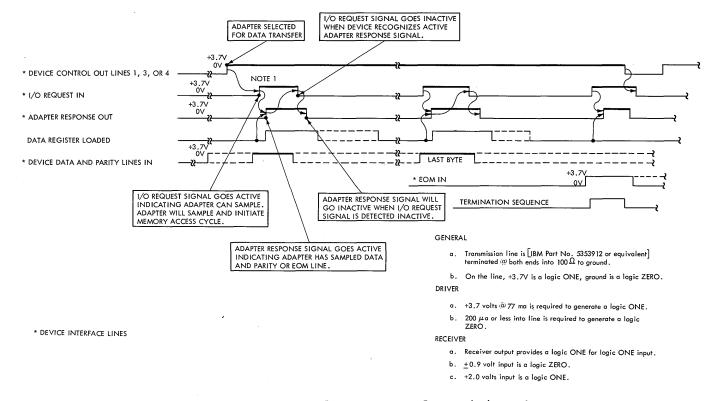

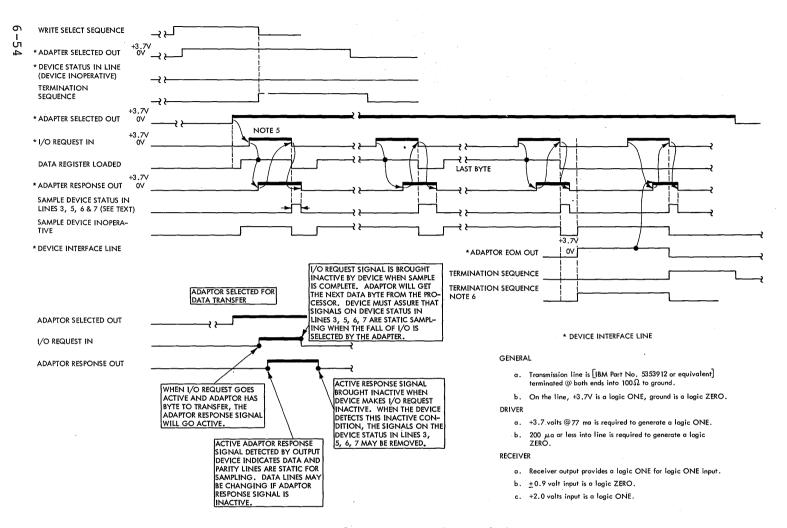

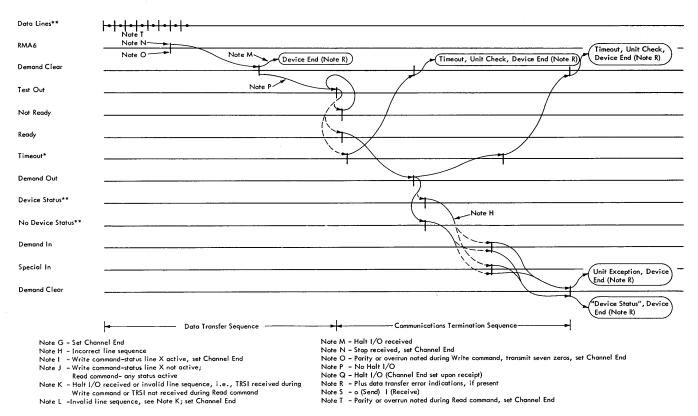

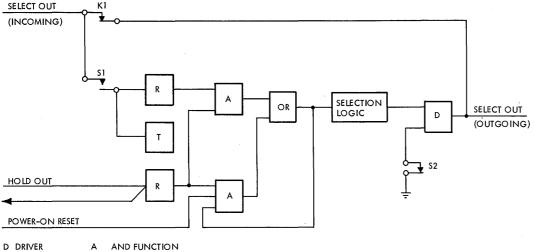

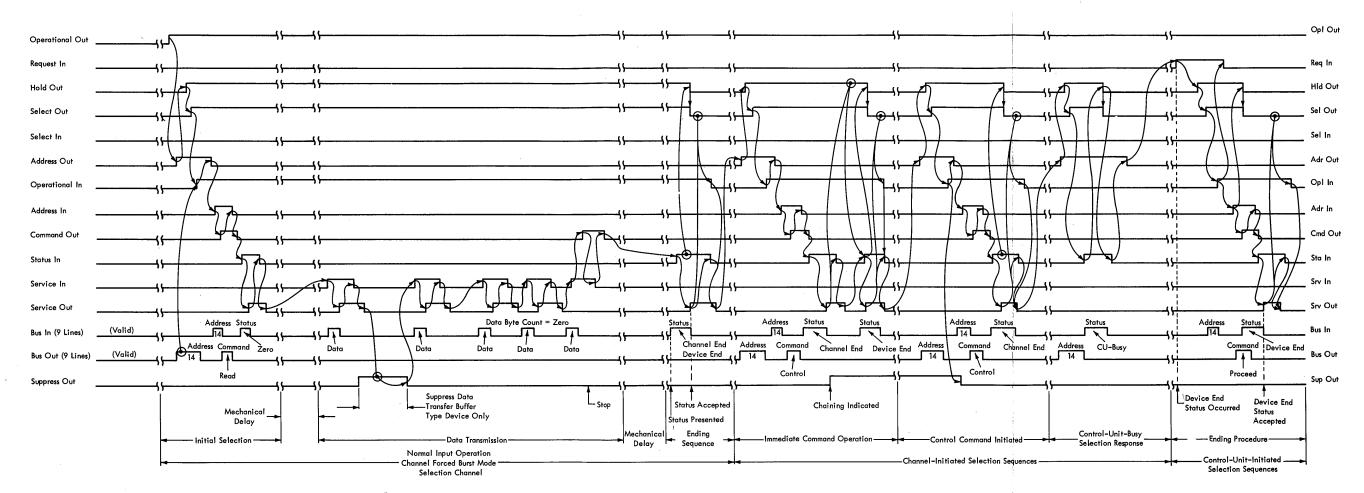

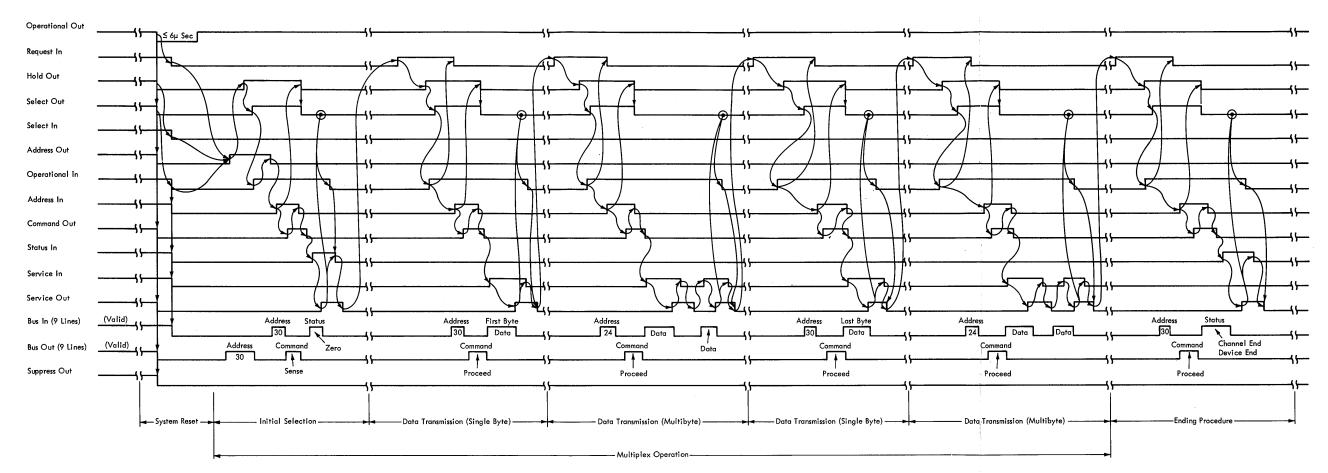

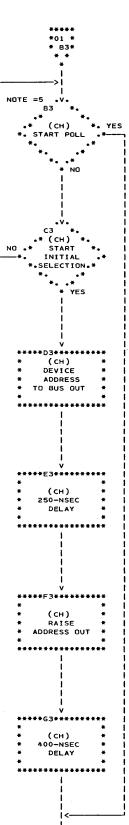

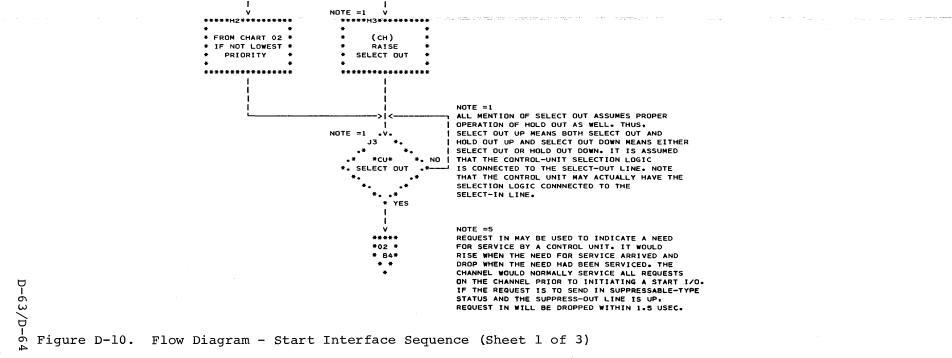

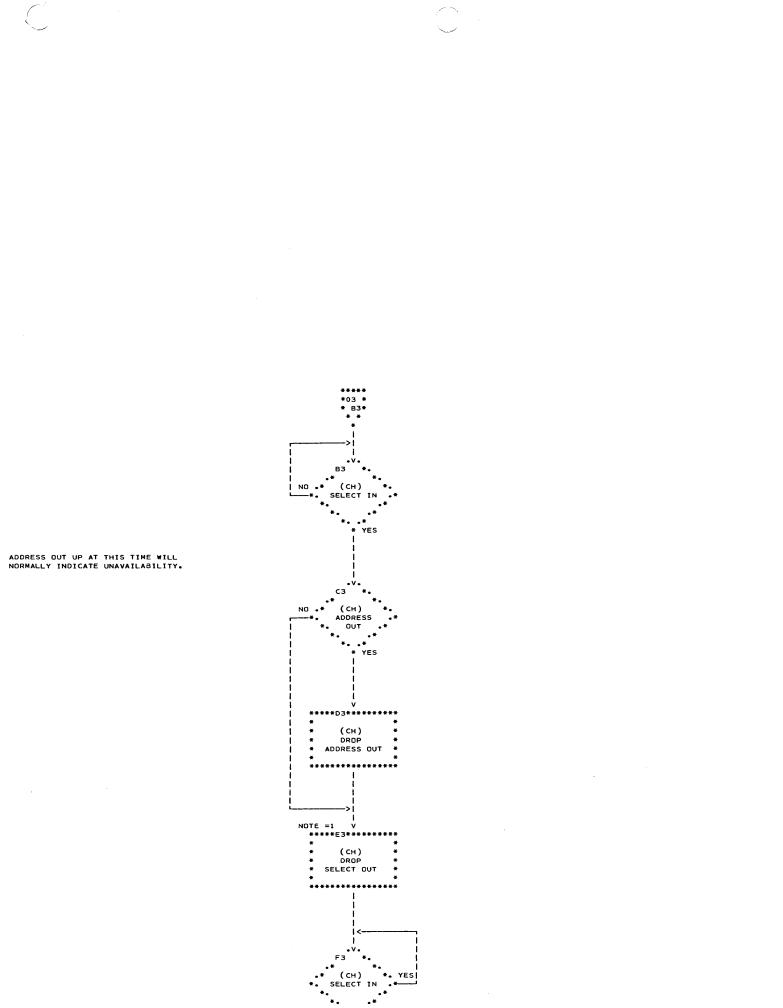

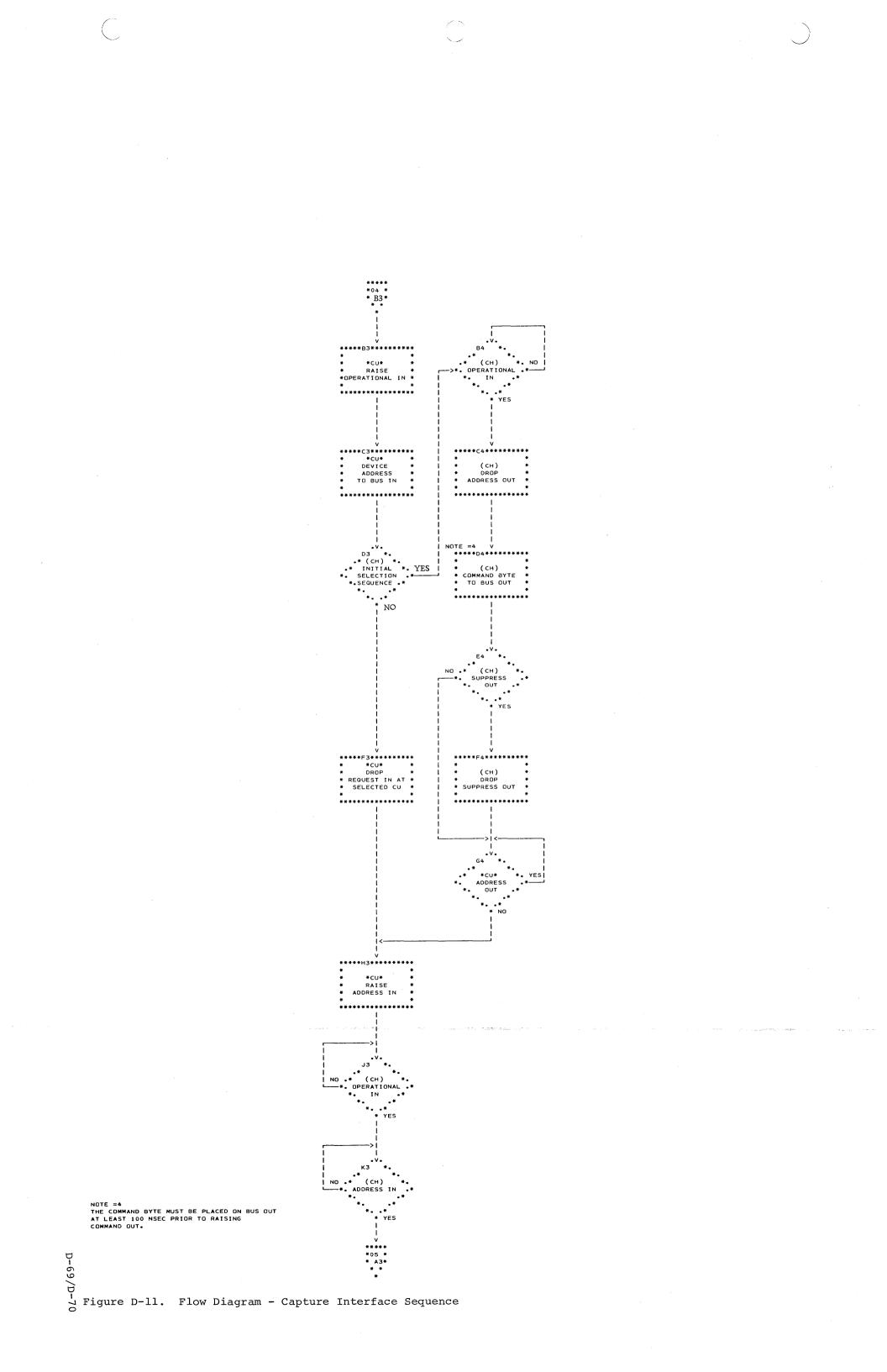

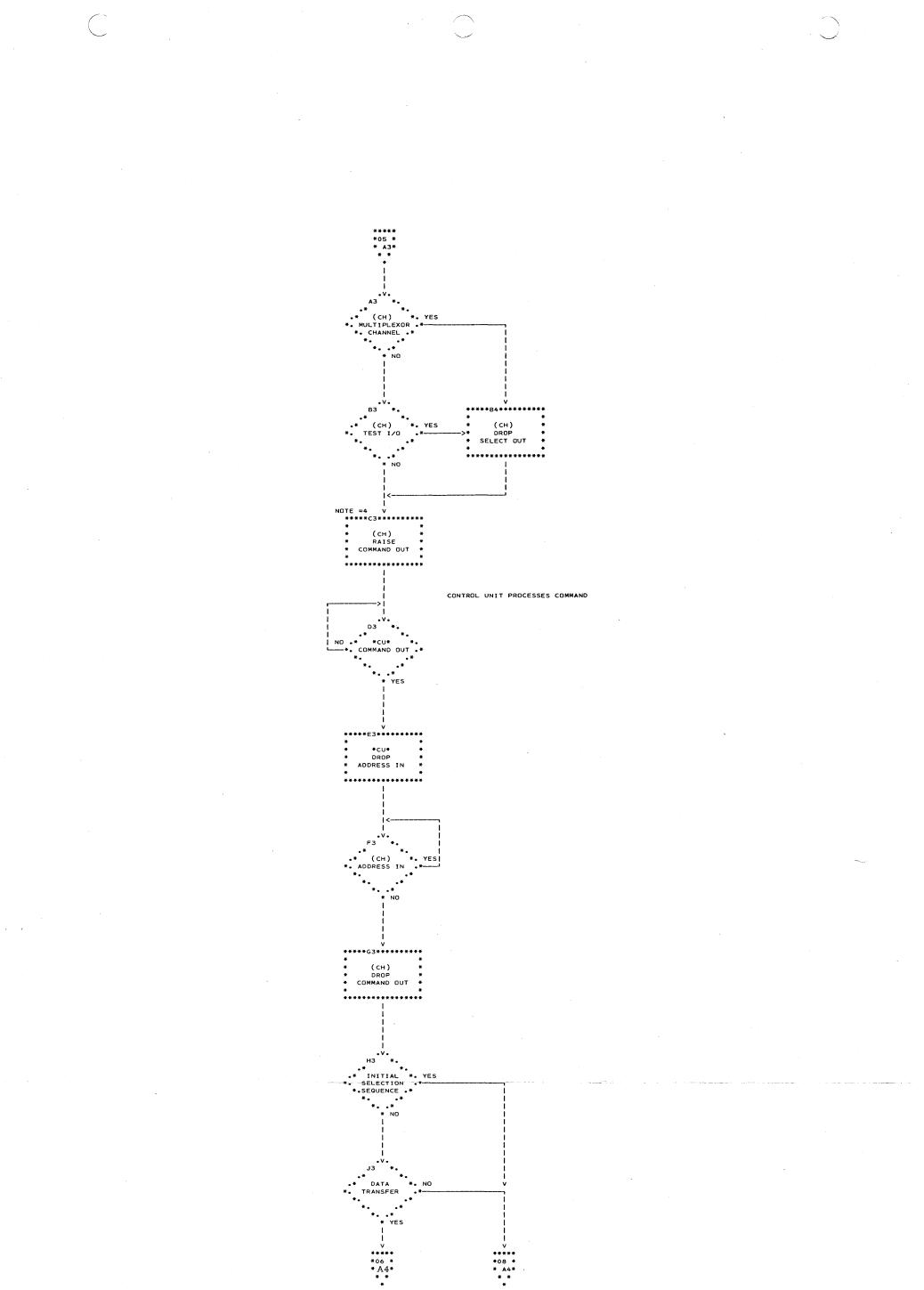

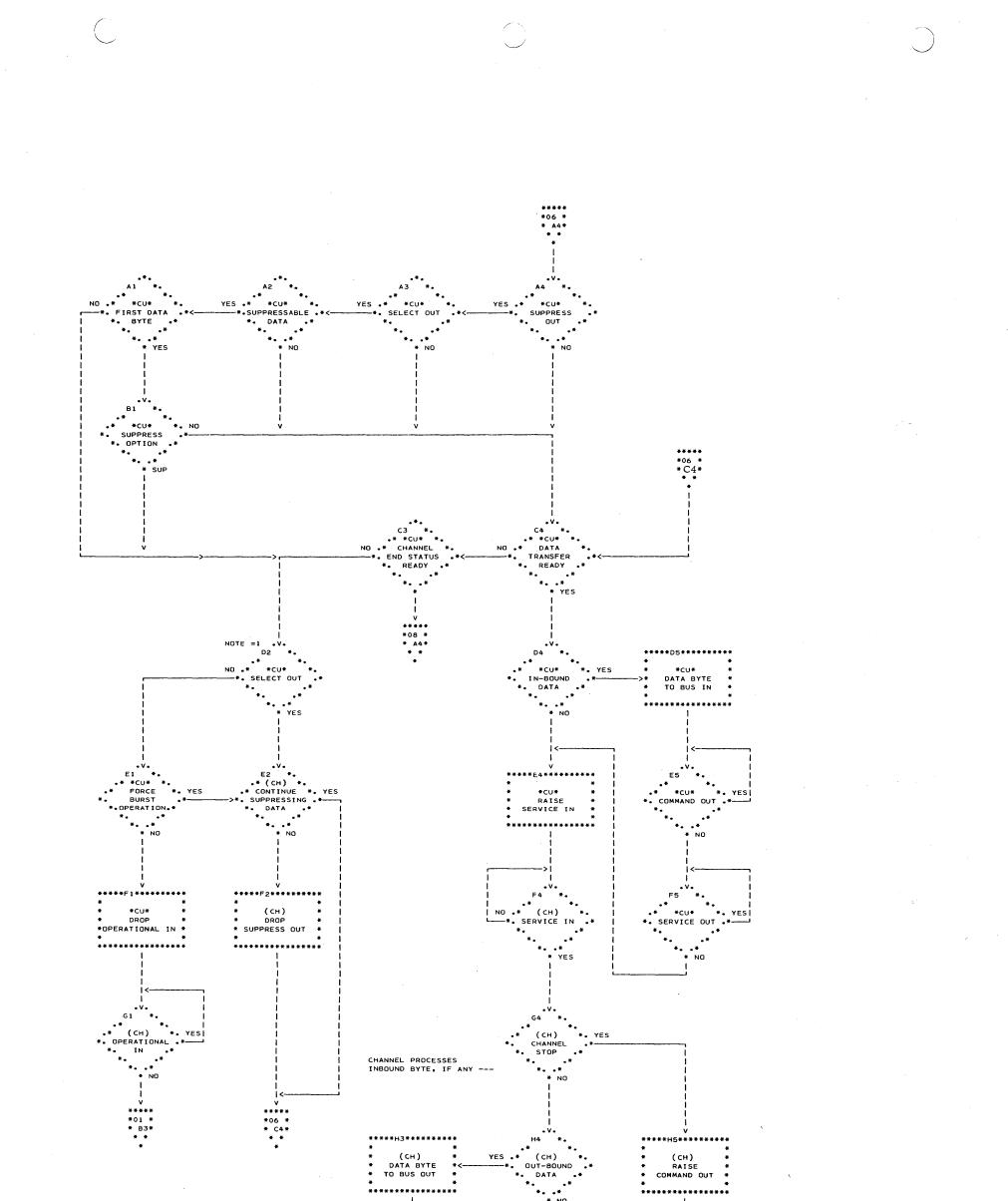

| I/O INTERFACE OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D-46<br>D-55                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

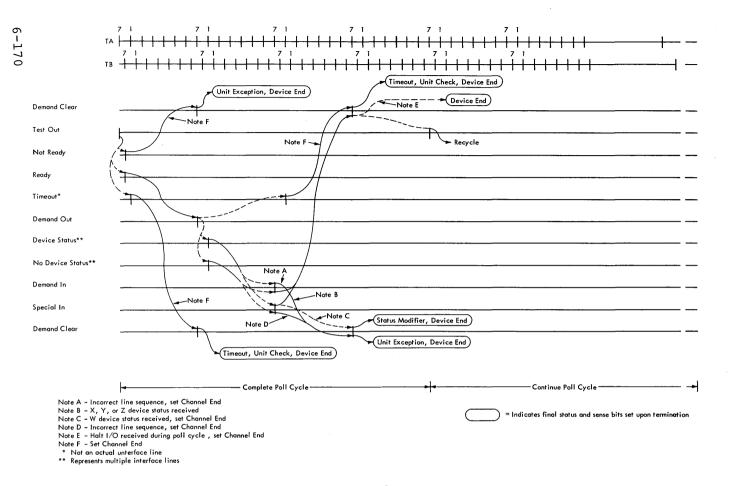

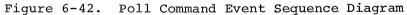

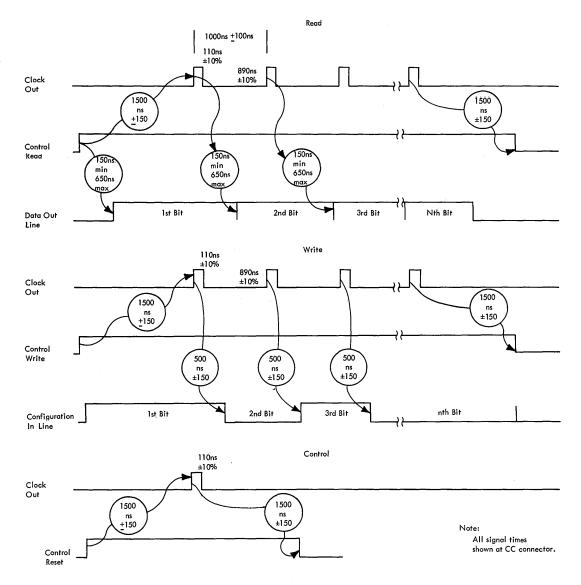

| Timing Charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D-55                                     |

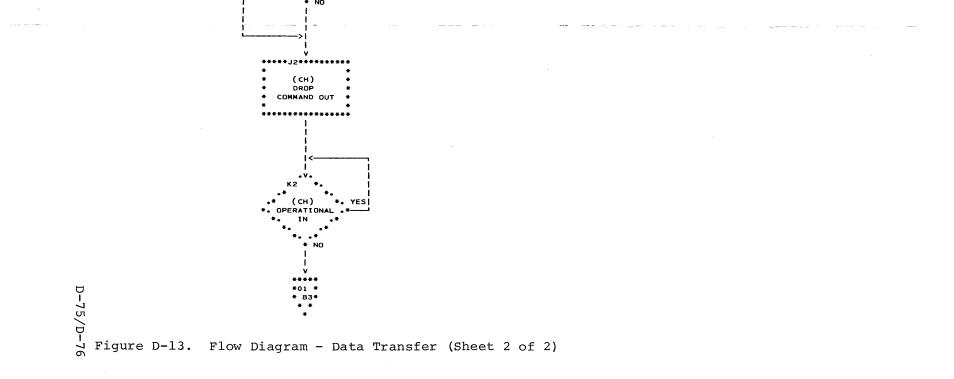

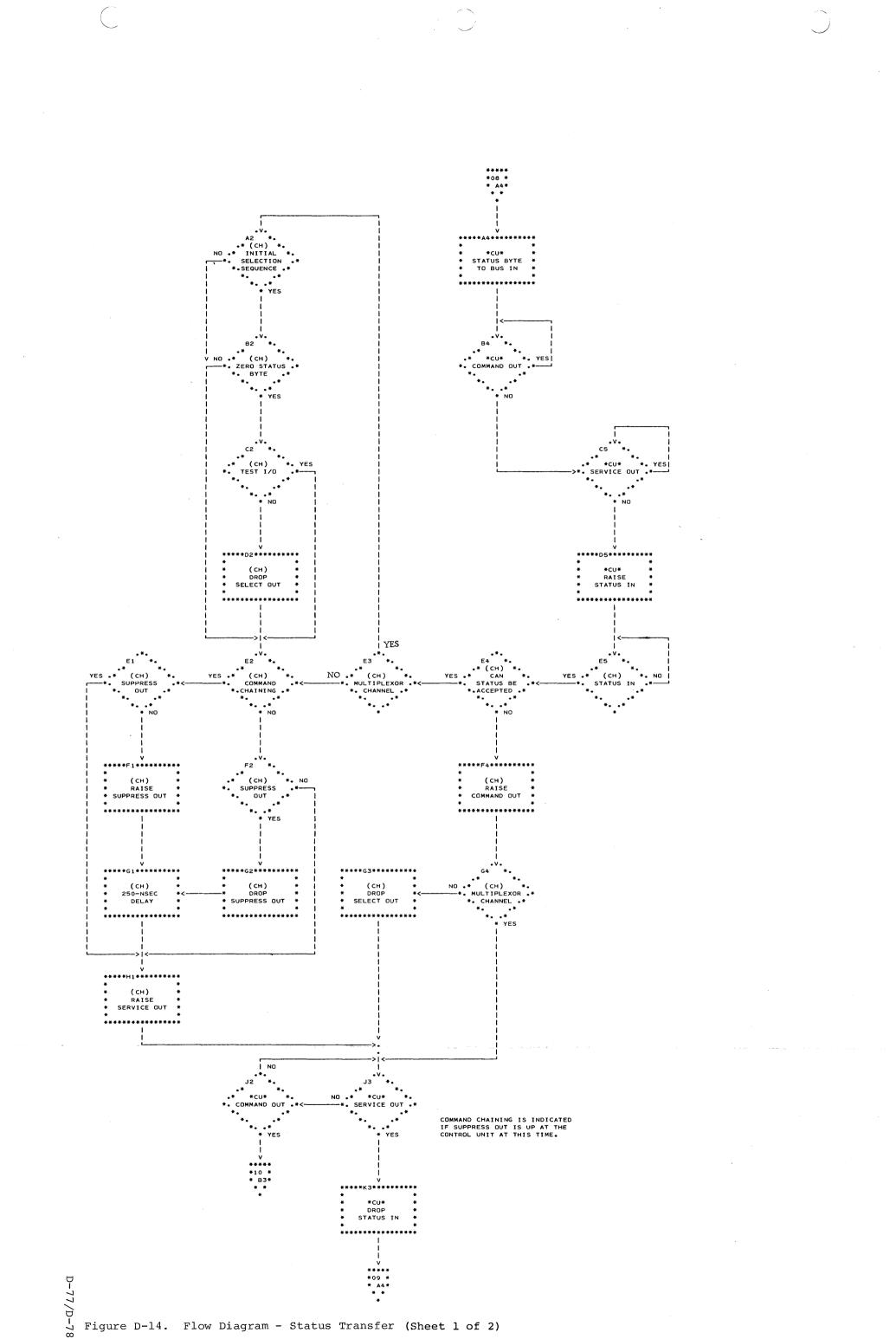

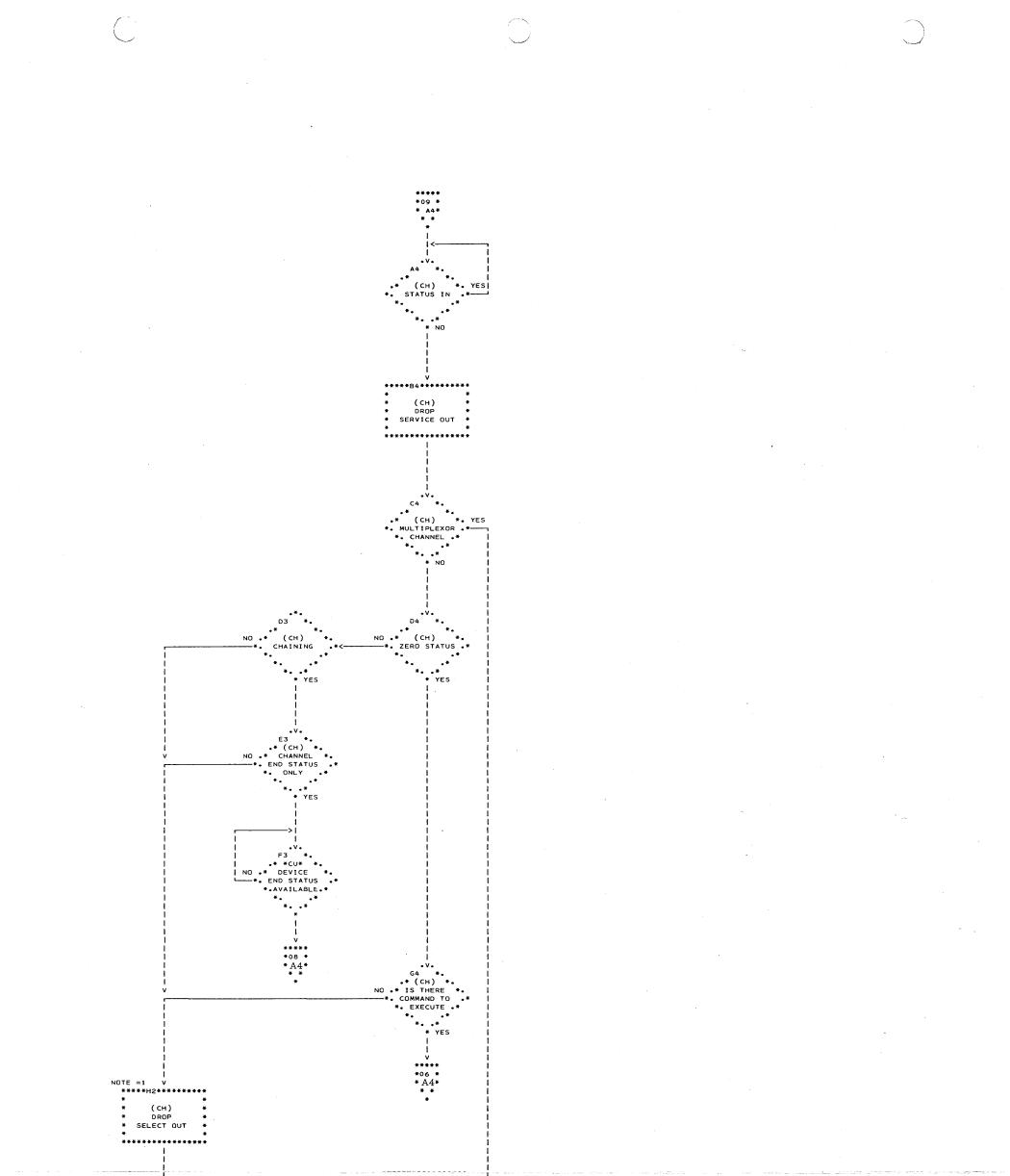

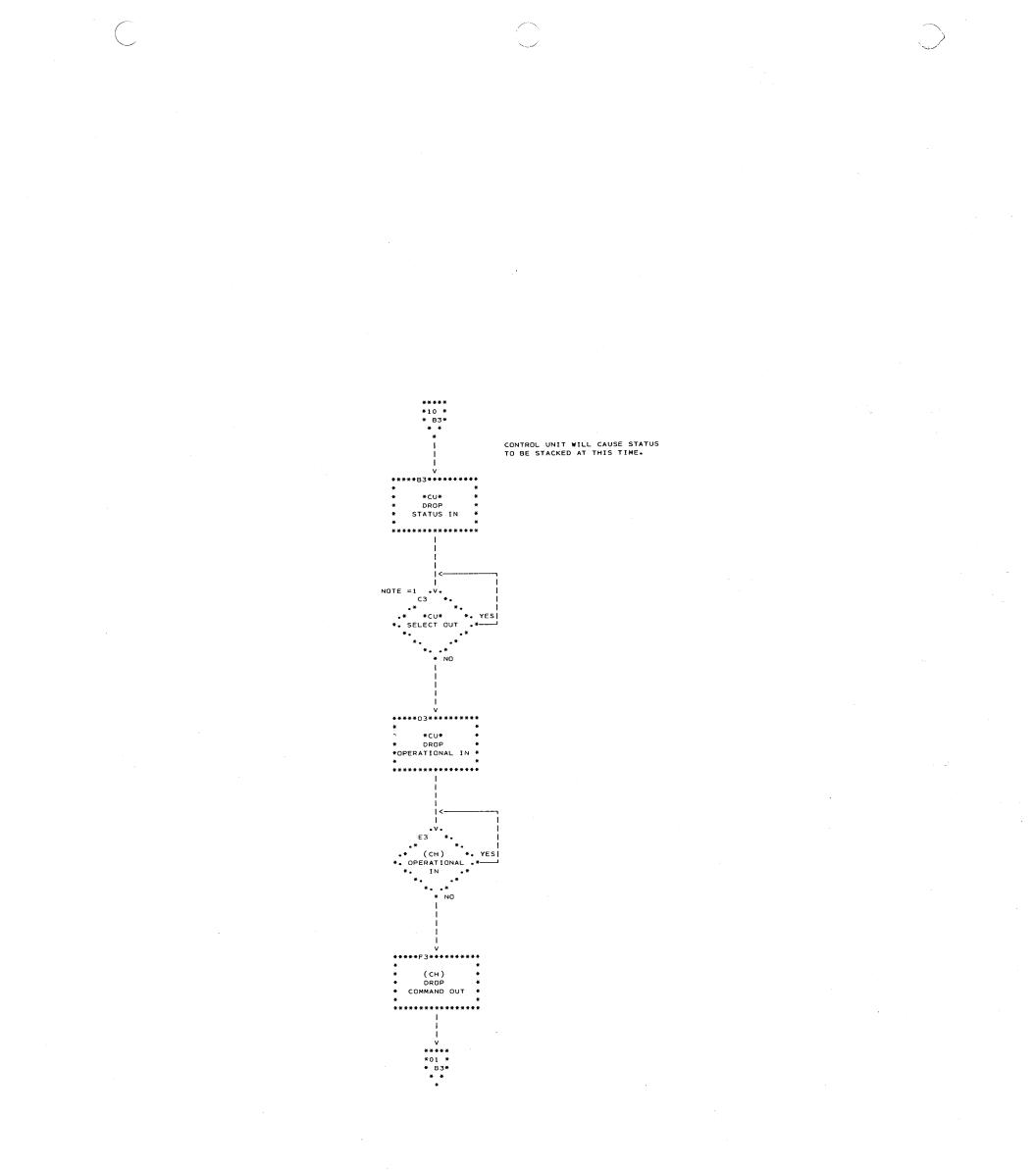

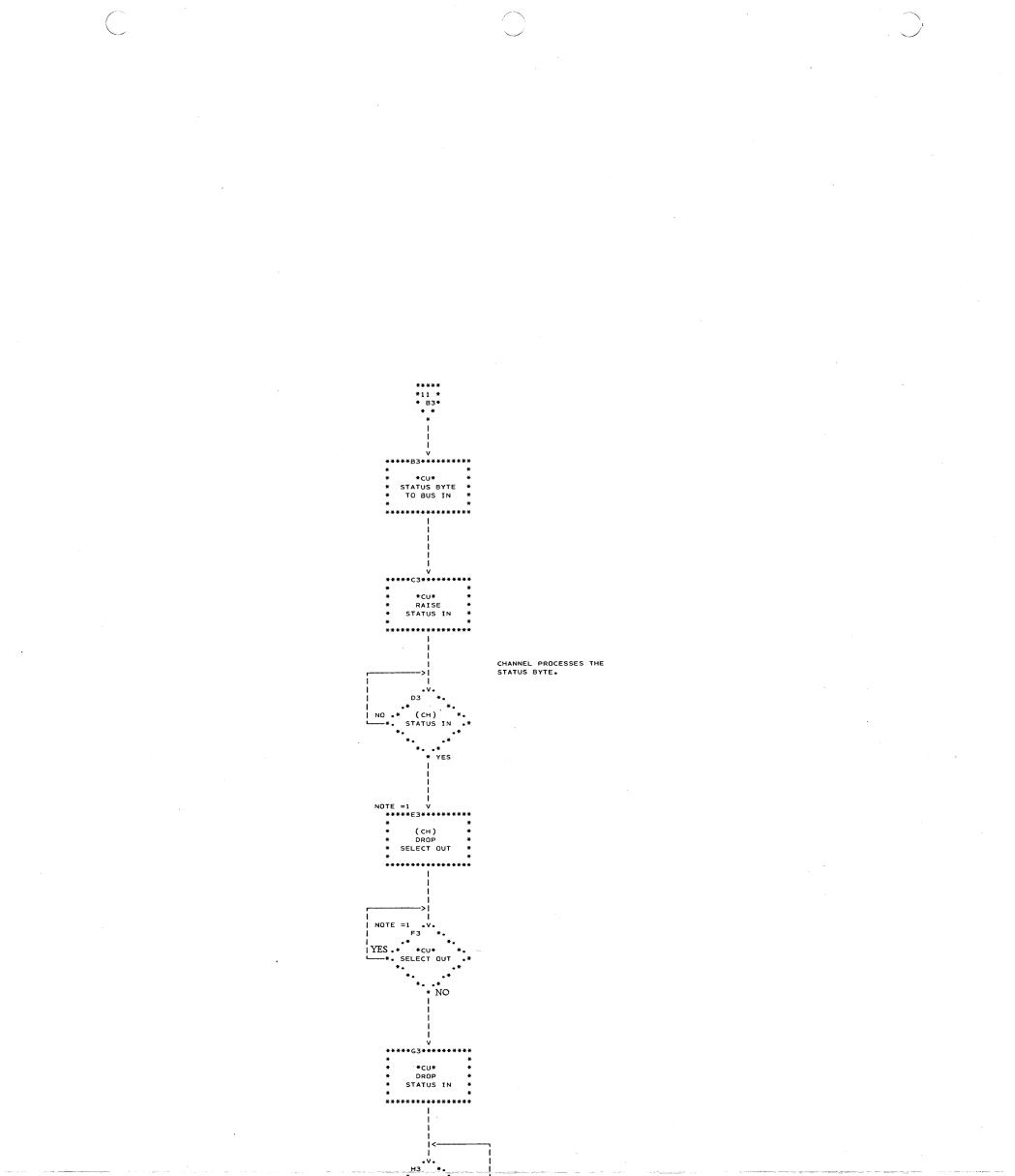

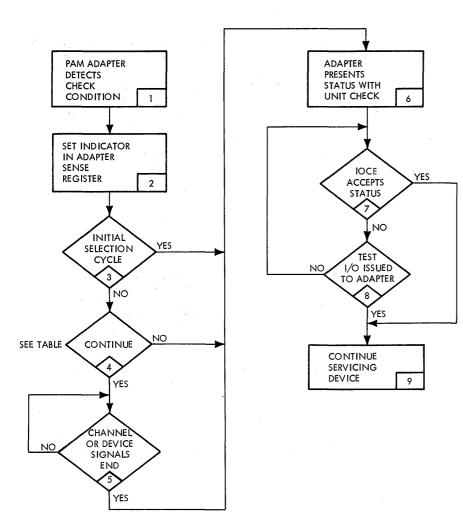

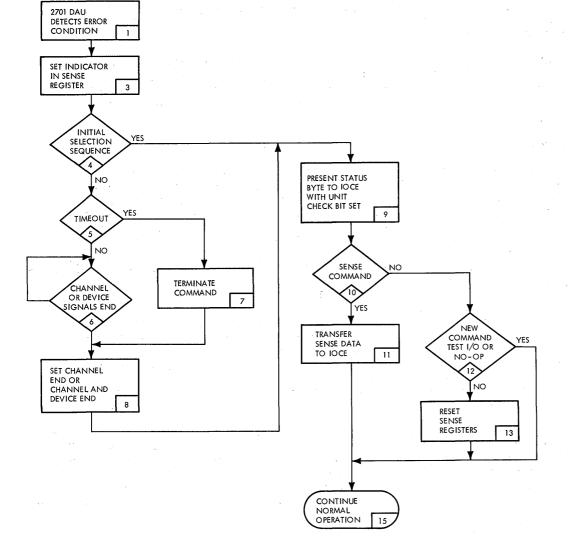

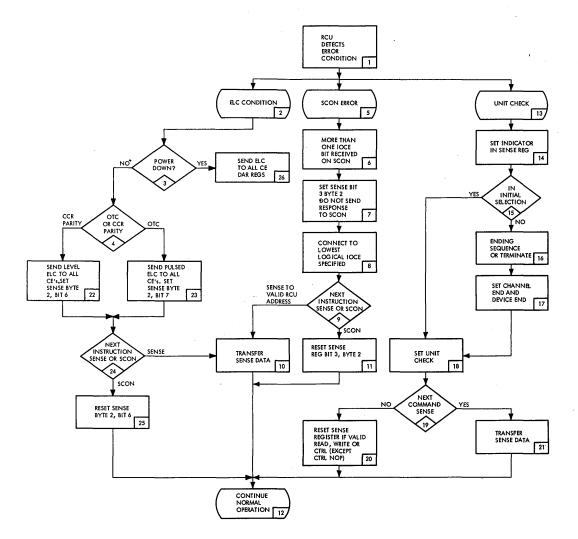

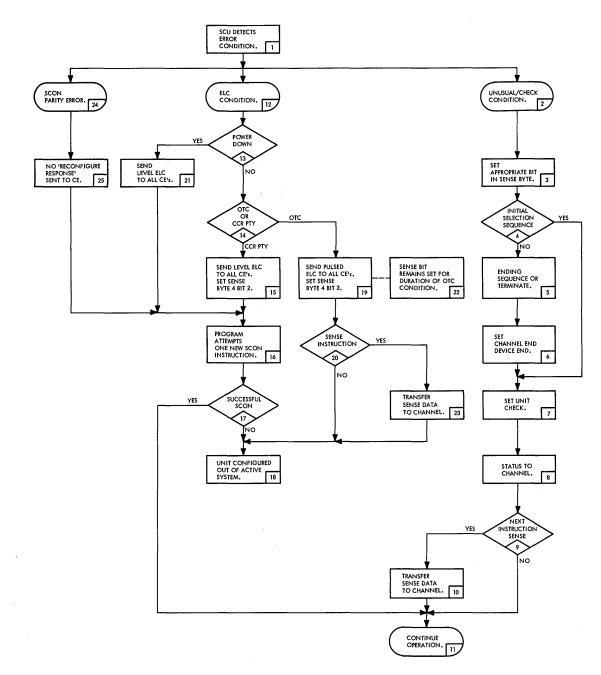

| Flow Charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D-55                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T. 1                                     |

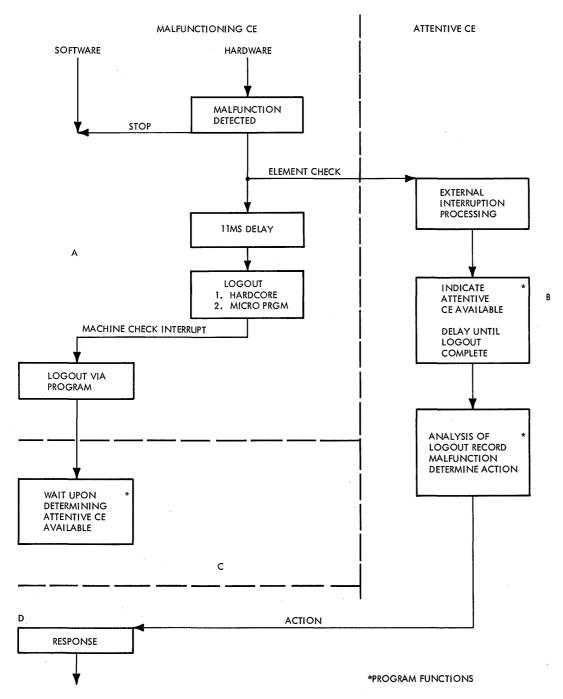

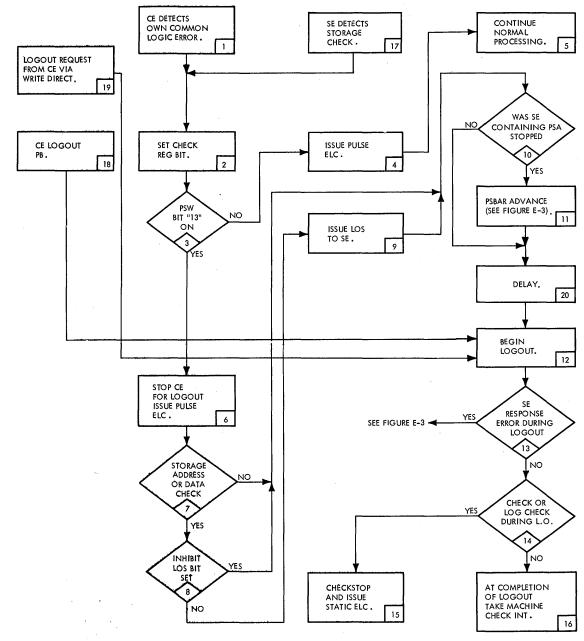

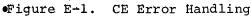

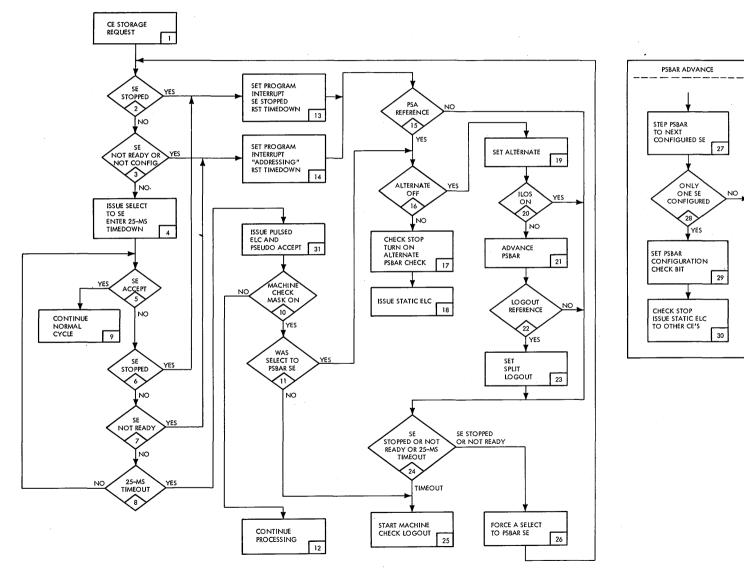

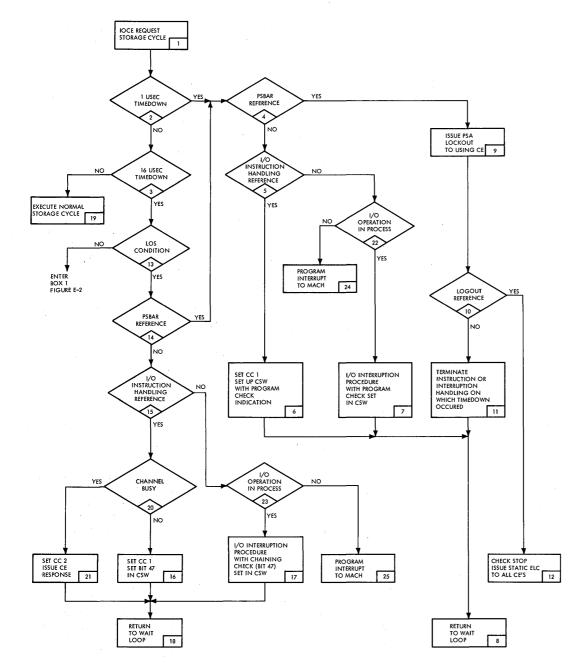

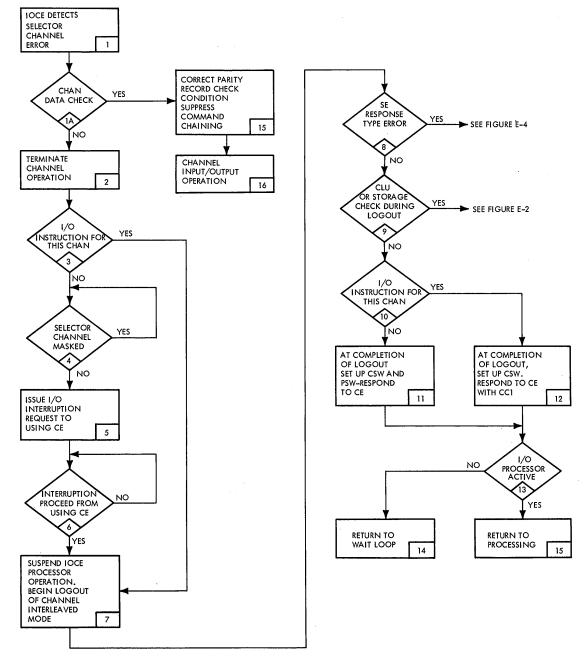

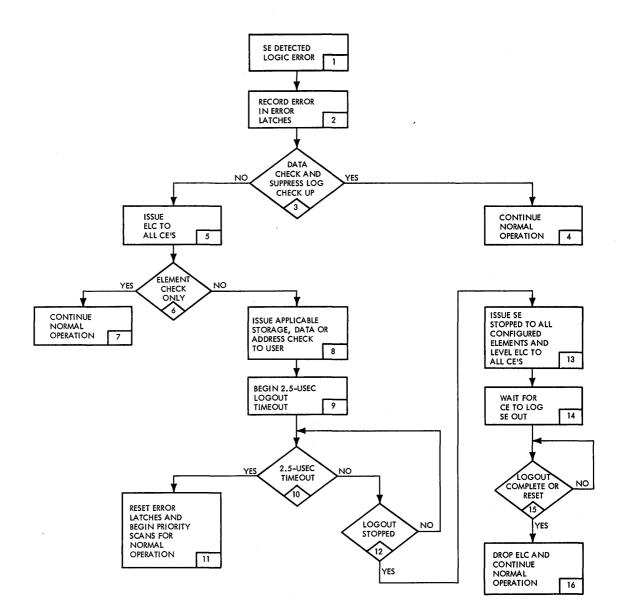

| APPENDIX E. 9020D/E MALFUNCTION HANDLING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | E-1                                      |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E-1                                      |